### DESIGN OF A FRONT-END ELECTRONICS AND USER INTERFACE BOARD FOR A COMPACT THERMAL IMAGER

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF THE MIDDLE EAST TECHNICAL UNIVERSITY

BY

FATİH IŞIK

110085

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

IN

THE DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

T.C. YÜKSEKÖĞRETIM KURULU BOKÜMANTASYON MERKEZI

Approval of the Graduate School of Natural and Applied Sciences.

Prof. Dr. Tayfur ÖZTÜRK Director

Ulprish

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof. Dr. Mübeccel DEMİREKLER Head of Department

mirehen

We certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree Master of Science.

Assoc. Prof. Dr. Cengiz BEŞİKCİ Supervisor

**Examining Committee Members:**

Assoc. Prof. Dr. Nevzat G. GENÇER

Assoc. Prof. Dr. Cengiz BEŞİKCİ

Assoc. Prof. Dr. Tayfun AKIN

Assoc. Prof. Dr. A. Aydın ALATAN

Assoc. Prof. Dr. Birsen SAKA

#### **ABSTRACT**

## DESIGN OF A FRONT-END ELECTRONICS AND USER INTERFACE BOARD FOR A COMPACT THERMAL IMAGER

Işık, Fatih

M.S., Department of Electrical and Electronics Engineering

Supervisor: Assoc. Prof. Dr. Cengiz Beşikci

December 2002, 92 pages

Infrared imaging systems have found increasing usage in various military and industrial branches. The analog front-end unit of an imager plays a considerable role in determining the system performance. In this thesis, a 4-input, 20 MHz mixed-signal front-end electronics board has been designed, implemented and tested by taking all necessary design techniques into consideration to make a system limited by the detector performance. The board functions including the analog processing of the detector output, readout integrated circuit (ROIC) interfacing, analog to digital conversion and user interface are controlled by a field programmable gate array. The board is controllable by a PC through an RS232 port.

After the implementation and testing, the front end electronics board is integrated with a video processing board and a detector/dewar assembly to form a prototype thermal imager. The system is configured to support 128x128 focal plane arrays. The maximum frame rate is 550 Hz for 128x128 focal plane arrays. The

system supports focal plane arrays up to a maximum format of 320x256 at 25 Hz frame rate.

Under the worst conditions, the noise level of the board is less than 650 e, and is comparable with that of a typical read-out integrated circuit (550 e) being several times smaller than the noise level of a typical cooled longwavelength infrared detector, which is about 4000 e. Under typical operating conditions, the noise level of the front-end electronics board is less than 50 e, and the performance of the system is limited by the ROIC and detector noise.

Keywords: Infrared Imaging, Focal Plane Array, Front-End Electronics

#### ÖZ

#### KOMPAKT TERMAL GÖRÜNTÜLEME SİSTEMİ İÇİN DEDEKTÖR ÖN ELEKTRONİĞİ VE KULLANICI ARAYÜZ KARTI TASARIMI

Işık, Fatih

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Cengiz Beşikci

Aralık 2002, 92 sayfa

Termal görüntüleme sistemleri, çeşitli askeri ve endüstriyel dallarda giderek artan bir şekilde kullanım alanları bulmuştur. Bu sistemlerde kullanılan analog önarabirimler sistem performansını belirlemede önemli bir rol oynamaktadır. Bu tezde, dedektör performansıyla sınırlı bir sistem oluşturabilmek için gerekli tüm tasarım teknikleri dikkate alınarak 4 girişli 20 MHz'te çalışabilen karışık sinyalli bir ön elektronik kartı tasarımlanmış, üretilmiş ve test edilmiştir. Dedektör çıkışının analog işlenmesi, okuma devresi arayüzü, analog-sayısal çevirim ve kullanıcı arayüzünü içeren kart fonksiyonları alan programlanabilir kapı dizinleri entegre devresi tarafından gerçekleştirilmektedir. Kart, RS232 portu üzerinden PC tarafından kontrol edilebilmektedir.

Geliştirme ve test aşamalarından sonra, ön elektronik kartı video işleme ve dedektör/soğutucu birimi ile entegre edilerek prototip bir termal görüntüleme sistemi oluşturulmuştur. Sistem, 128x128 dizinli odak düzlem dedektörler ile uyumlu olacak şekilde yapılandırılmıştır. Maksimum resim hızı 128x128 dizinli odak düzlem

dedektörler için 550 Hz'dir. Sistem, 25 resim/saniye hızda 320x256 formatına kadar odak düzlem matrislerini desteklemektedir.

En kötü koşullarda, kartın gürültü seviyesi 650 e<sup>-</sup>'dan küçüktür ve tipik bir okuma devresi çıkış gürültü seviyesi (550 e<sup>-</sup>) ile karşılaştırılabilir düzeyde olup, 4000 e<sup>-</sup> olan tipik soğutmalı uzundalga kızılötesi dedektör gürültü seviyesinden bir kaç kat düşük düzeydedir. Normal çalışma koşullarında, ön-elektronik sistemi gürültü seviyesi 50 e<sup>-</sup>'dan küçüktür ve sistem performansı okuma devresi ve dedektör gürültüleri ile sınırlıdır.

Anahtar Kelimeler: Termal Görüntüleme, Odak Düzlem Dedektör Dizini, Dedektör Ön-Arabirim Elektroniği

To My Family

#### **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude to my advisor Assoc. Prof. Dr. Cengiz Beşikci for his encouragement, valuable comments and continued support throughout this study.

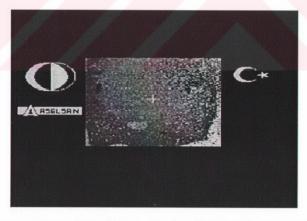

Special thanks to ASELSAN Inc. Microelectronics, Guidance and Electro-Optics division for providing technical support and laboratory environment in which we could develop our design.

I am thankful to all my friends in ASELSAN and METU who have helped me throughout this thesis. I would also like to thank Selçuk Özer for his support during the integration phase of the thesis.

Finally, I would like to express my appreciation to my family for their continued patience, understanding, encouragement, and support throughout the preparation of this study.

#### TABLE OF CONTENTS

| ÖZ                             | v                |

|--------------------------------|------------------|

| ACKNOWLEDGEMENTS               | viii             |

| TABLE OF CONTENTS              | ix               |

| LIST OF TABLES                 | xii              |

| LIST OF FIGURES                |                  |

| 1. INTRODUCTION                | 1                |

| 1.1 Overview                   |                  |

| 1.2 Aims                       | 2                |

| 1.2 Aims                       | ••••••           |

| 1.3 Organization of the Thesis |                  |

|                                | 4                |

| 1.3 Organization of the Thesis | 4<br>5           |

| 1.3 Organization of the Thesis | 4<br>5           |

| 1.3 Organization of the Thesis | 4<br>5<br>6      |

| 1.3 Organization of the Thesis | 4<br>5<br>6<br>9 |

| 1.3 Organization of the Thesis | 4 5 6 9          |

| 1.3 Organization of the Thesis |                  |

| 1.3 Organization of the Thesis |                  |

| 1.3 Organization of the Thesis | 4 5 6 9 12 13    |

| 1.3 Organization of the Thesis |                  |

| 1.3 Organization of the Thesis |                  |

|    |     | 3.3.1 Default Mode                                             | 18   |

|----|-----|----------------------------------------------------------------|------|

|    |     | 3.3.2 Command Mode                                             | 19   |

|    | 3.4 | Output Modes                                                   | .27  |

|    | 3.5 | Windowing                                                      | .27  |

|    | 3.6 | Readout Timing                                                 | . 28 |

|    | 3.7 | Integration Modes                                              | . 29 |

|    | 3.8 | Integration Time                                               | .30  |

|    | 3.9 | Summary                                                        | .31  |

| 4. | FRO | ONT END ELECTRONICS SYSTEM DESIGN                              | . 32 |

|    | 4.1 | Introduction                                                   | .32  |

|    | 4.2 | Operation and Interface                                        | .33  |

|    | 4.3 | Analog Section                                                 | .34  |

|    |     | 4.3.1 Buffering                                                | 35   |

|    |     | 4.3.2 Offset and Gain Amplifier and Control                    | 37   |

|    |     | 4.3.3 Clamper                                                  | 41   |

|    |     | 4.3.4 Differential Driver                                      | 42   |

|    |     | 4.3.5 Analog-to-Digital Conversion                             | 42   |

|    |     | 4.3.6 Bias and Reference Generation                            | 44   |

|    |     | 4.3.7 Integration Time Control and Temperature Data Monitoring |      |

|    | 4.4 | Digital Section                                                | . 48 |

|    |     | 4.4.1 Field Programmable Gate Array (FPGA)                     | 48   |

|    |     | 4.4.2 SRAM                                                     | 50   |

|    |     | 4.4.3 FPGA Configuration Memory                                |      |

|    |     | 4.4.4 RS232 Transceiver                                        |      |

|    |     | 4.4.5 4-Digit Seven Segment Display                            |      |

|    |     | 4.4.6 DIP Switches                                             |      |

|    | 4.5 | PCB Design                                                     |      |

|    | 4.6 | Normalization Algorithm                                        | . 53 |

|    | 4.7 | Summary                                                        | . 54 |

| 5. | SIM | MULATION AND TESTING OF THE FRONT-END ELECTRONICS              |      |

| B  | OAF | RD                                                             | . 55 |

|    | 5.1 | Introduction                                                   | . 55 |

|    | 5.2 | Bias and Reference Generation                                  | . 56 |

|    | 5.3 | Analog Processing of ROIC Output                               | . 56 |

|    |     | 5.3.1 Offset and Gain Setting                                  | 56   |

|                | 5.3.2 Clamping                             | 59 |

|----------------|--------------------------------------------|----|

|                | 5.3.3 Digitization                         | 60 |

| 5.4            | Temperature Data Monitoring                | 61 |

| 5.5            | HPVEE Test Pattern Generation              | 61 |

| 5.6            | Summary                                    | 62 |

| 6. SYS         | TEM INTEGRATION AND TESTING                | 63 |

| 6.1            | Introduction                               | 63 |

| 6.2            | Detector Dewar Assembly                    | 64 |

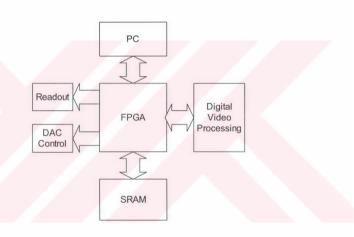

| 6.3            | Video Processing and System Control Board  | 64 |

| 6.4            | Monitoring Test and ROIC Data              | 66 |

| 6.5            | Normalization Coefficient Calculation      | 69 |

| 6.6            | Summary                                    | 74 |

| <b>7. CO</b> I | NCLUSION AND FUTURE WORK                   | 75 |

| REFE           | RENCES                                     | 77 |

| APPE           | NDICES                                     |    |

| A              | HPVEE USER INTERFACE                       | 79 |

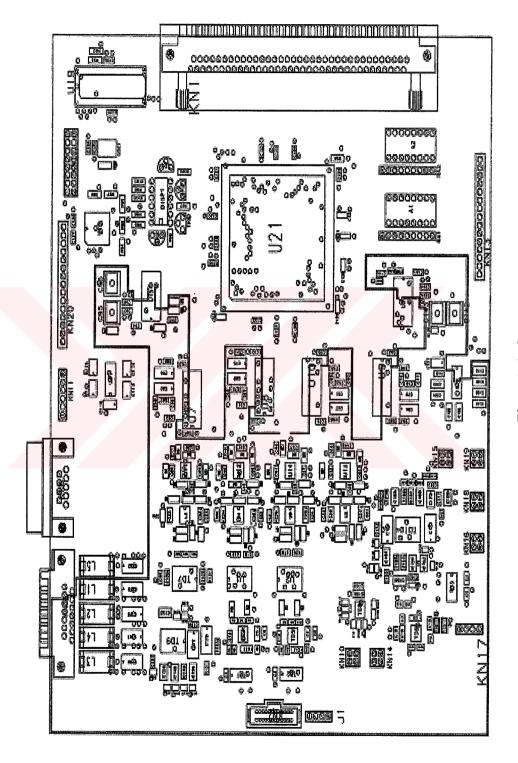

| В              | PCB LAYOUT OF FRONT-END ELECTRONICS        | 80 |

| C              | MATLAB CODES FOR NORMALIZATION COEFFICIENT |    |

|                | CALCULATION                                | 84 |

#### LIST OF TABLES

#### **TABLE**

| 2.1   | Infrared detector types.                                                   | 7  |

|-------|----------------------------------------------------------------------------|----|

| 2.2   | Thermal Imaging Applications.                                              | 11 |

| 3.1   | Pinout descriptions of the ISC9806 ROIC                                    | 17 |

| 3.2   | Gain states for internal amplifier of ROIC                                 | 21 |

| 5.1.a | Offset correction circuit calculated and measured values for -3.8V offset  | 58 |

| 5.1.b | Offset correction circuit calculated and measured values for -2.03V offset | 58 |

| 5.2.a | Gain applied ROIC data for -3.8V offset and -0.397V gain voltages          | 58 |

| 5.2.b | Gain applied ROIC data for -3.8V offset and -0.31V gain voltages           | 59 |

| 5.2.c | Gain applied ROIC data for -2.03V offset and -0.31V gain voltages          | 59 |

| 5.3   | Clamping amplifier input and output data                                   | 60 |

| 5.4   | ADC inputs, calculated and measured outputs and difference                 | 61 |

#### LIST OF FIGURES

#### **FIGURES**

| 1.1  | Block diagram of a basic infrared imaging system                                 | 1  |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | Blocks and interface of the front-end electronics board.                         | 3  |

| 1.3  | Front-end electronics board                                                      | 3  |

| 2.1  | Electromagnetic Spectrum.                                                        | 6  |

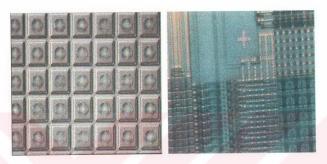

| 2.2  | (a) 128x128 detector array and Silicon ROIC (b) Schematics of flip-chip bonder   | æd |

|      | detector and ROIC                                                                | 8  |

| 2.3  | Block diagram of the IR imaging camera electronics.                              | 2  |

| 3.1  | Simplified unit cell schematic for ISC9806 input circuit, where direct injection | n  |

|      | method is used                                                                   |    |

| 3.2  | ISC9806 pinout schematic.                                                        | 16 |

| 3.3  | Block diagram for default mode operation in Indigo Systems' ROIC                 | 19 |

| 3.4  | Typical direct injection circuit                                                 | 19 |

| 3.5  | Serial control register                                                          | 20 |

| 3.6  | Command mode detector bias                                                       | 22 |

| 3.7  | Block diagram for command mode operation                                         | 24 |

| 3.8  | Serial Control Register Timing                                                   | 26 |

| 3.9  | Detailed Timing for Serial Control Register.                                     | 27 |

| 3.10 | Readout Timing                                                                   | 28 |

| 3.11 | Detailed Timing for Readout                                                      | 29 |

| 3.12 | Integrate-While-Read timing diagram                                              | 30 |

| 3.13 | Integrate-Then-Read timing diagram                                               | 30 |

| 3.14 | Detailed timings for digital control signals                                     | 31 |

| 4.1  | Simplified interface diagram of the front-end electronics board with the other | her |

|------|--------------------------------------------------------------------------------|-----|

|      | blocks in the system                                                           | 32  |

| 4.2  | Interface block diagram of the front-end electronics system                    | 33  |

| 4.3  | Major front-end electronics system blocks                                      | 34  |

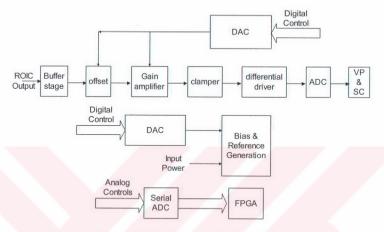

| 4.4  | Block diagram for the analog section                                           | 35  |

| 4.5  | Pinout for CLC114.                                                             | 36  |

| 4.6  | Divisor circuit for 7.5V supply generation                                     | 36  |

| 4.7  | Pinout for AD7888.                                                             | 38  |

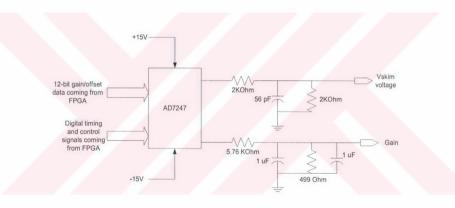

| 4.8  | DAC circuit producing vskim and gain signals                                   | 38  |

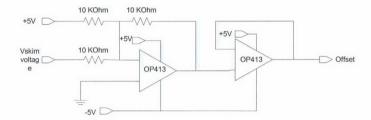

| 4.9  | 2.5V subtraction circuit from the divided vskim signal to obtain offset signal | 39  |

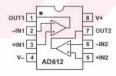

| 4.10 | Pinout for AD812 opamp                                                         | 39  |

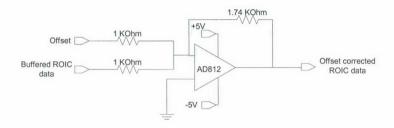

| 4.11 | The circuit used to add offset to the buffered ROIC data.                      | 39  |

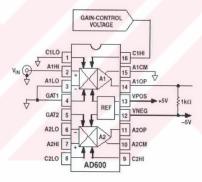

| 4.12 | AD602 input and output.                                                        | 40  |

| 4.13 | The circuit used for varible gain amplification                                | 41  |

|      | Pinout of CLC502.                                                              |     |

| 4.15 | Pinout of AD8138.                                                              | 42  |

| 4.16 | Pinout and pin descriptions for AD9220                                         | 43  |

| 4.17 | The analog-to-digital conversion circuit including the differential driv       | ver |

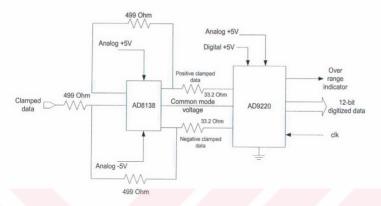

|      | AD8138.                                                                        | 44  |

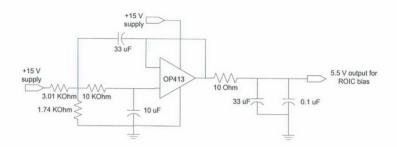

| 4.18 | 5.5V generation circuit                                                        | 44  |

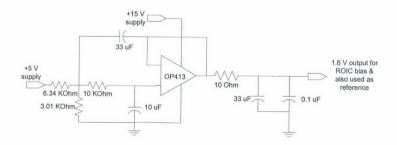

| 4.19 | 1.6V generation circuit                                                        | 45  |

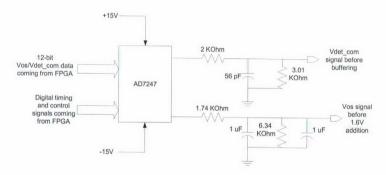

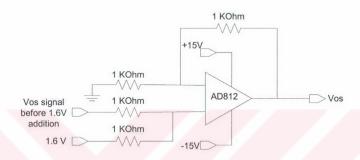

| 4.20 | Generation of Vos and Vdet_com biases before processing                        | 45  |

| 4.21 | Adder circuit to form Vos.                                                     | 46  |

| 4.22 | Buffer circuit to form Vdet_com                                                | 46  |

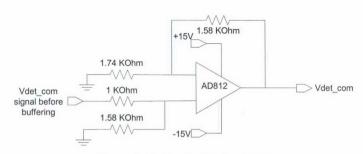

| 4.23 | Temperature sensor output flow.                                                | 47  |

| 4.24 | Block diagram for the digital section.                                         | 48  |

| 4.25 | Blocks of FPGA                                                                 | 49  |

| 4.26 | Pin diagram and functions of EDI816256CA                                       | 50  |

| 4.27 | Pinout of configuration memory                                                 | 51  |

| 4.28 | Pin assignment and description of DS232A                                       | 51  |

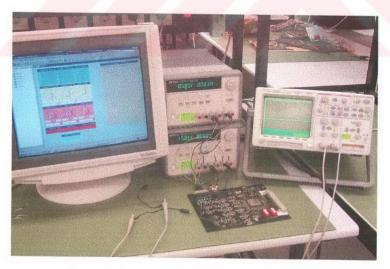

| 5.1  | The test-setup for the front-end electronics board                             | 55  |

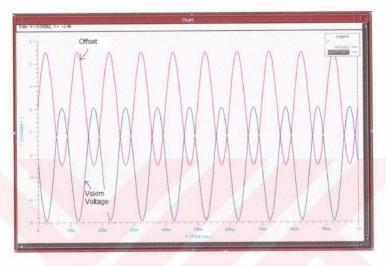

| 5.2  | Simulation results for Offset vs. Vskim voltage                                | 57  |

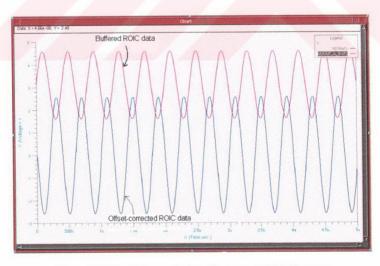

| 5.3        | Simulation results for offset-corrected ROIC output                         |

|------------|-----------------------------------------------------------------------------|

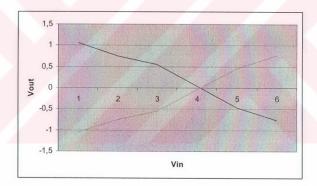

| 5.4        | Graph indicating the slight non-linearity                                   |

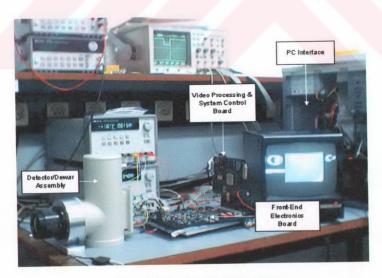

| 6.1        | Imaging system test setup                                                   |

| 6.2        | Detector Dewar Assembly                                                     |

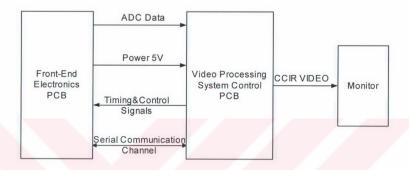

| 6.3        | Interfacing of the VP_SC with the other blocks                              |

| 6.4        | Test data increasing at every LSYNC rising edge                             |

| 6.5        | Test data increasing at every ADC_CLK rising edge                           |

| 6.6        | Test data sent from PC (hex 55)                                             |

| 6.7        | Raw infrared image taken from IRFPA, while the array is looking at 300K     |

|            | background                                                                  |

| 6.8        | View of taken frame data in MATLAB with the FPA looking at candle light 69  |

| 6.9        | Offset-corrected frame data viewed in MATLAB with the FPA looking at candle |

|            | light                                                                       |

| 6.10       | Gain-corrected frame data viewed in MATLAB with the FPA looking at candle   |

|            | light                                                                       |

| 6.11       | Offset and gain corrected frame data viewed in MATLAB with the FPA looking  |

|            | at candle light                                                             |

| 6.12       | Two-point correction disabled thermal image with the FPA looking at candle  |

|            | light                                                                       |

| 6.13       | Two-point correction enabled thermal image with the FPA looking at candle   |

|            | light                                                                       |

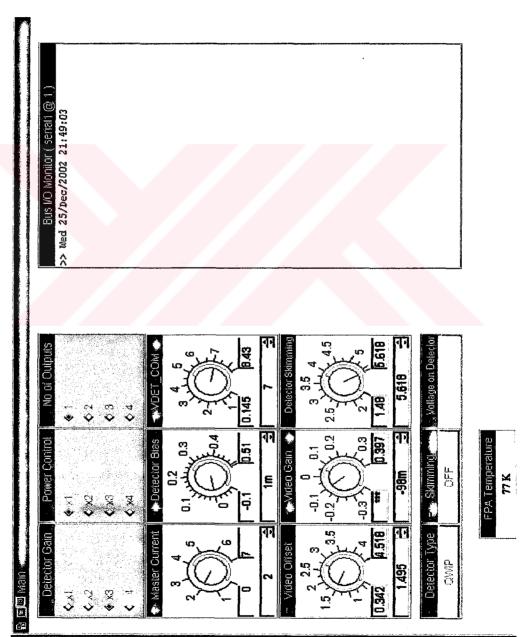

| Α          | HPVEE User Interface                                                        |

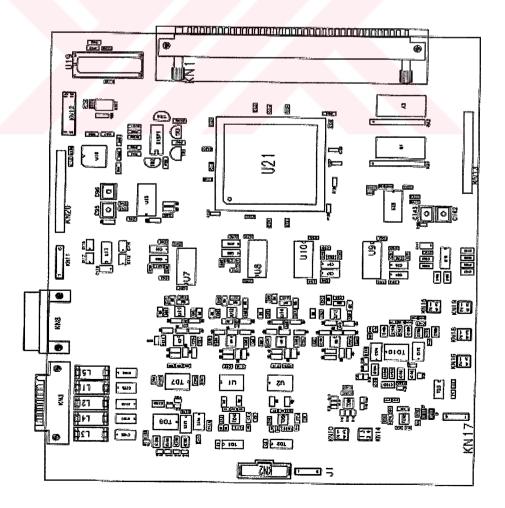

| <b>B</b> 1 | Component Layer 80                                                          |

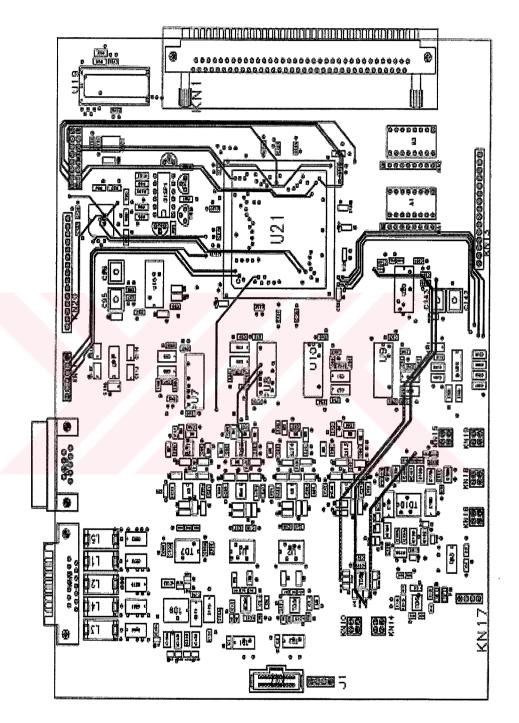

| B2         | Solder Layer                                                                |

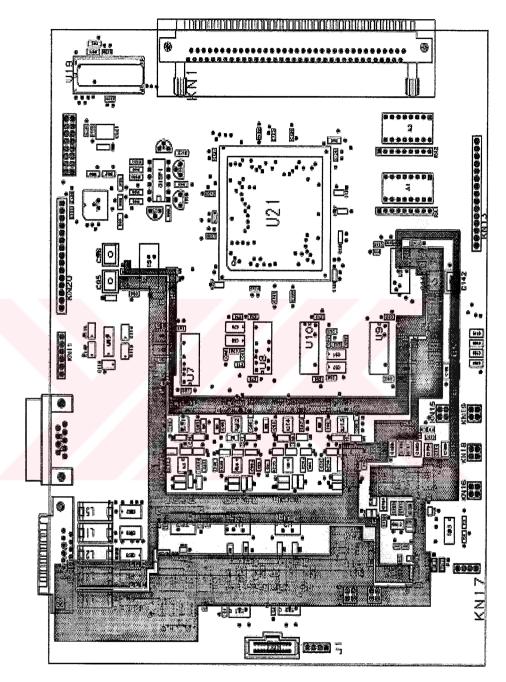

| В3         | Power Layer82                                                               |

| B4         | Ground Layer83                                                              |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Overview

Infrared imaging provides the means to convert the infrared energy, which is emitted from the objects and invisible to human eye, to electrical signals that may be then processed to obtain thermal images. Different from the cameras used in visible light, it is possible to get high contrast and detailed images using infrared cameras in day, night and bad weather conditions due to the nature of infrared energy.

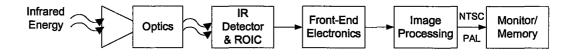

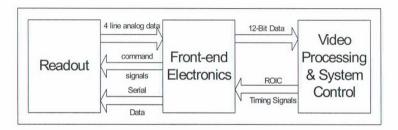

A basic infrared imaging system consists of many subsystems, each of which processes information differently. They may create artifacts or variations in the processed image that were not present in the original scene. Figure 1.1 illustrates five major subsystems: optics for focusing the radiation onto the detectors, IR detectors together with the readout integrated circuit (ROIC) for converting scene radiation into a measurable electrical signal, front-end electronics unit for digitizing detector output and producing necessary bias voltages with control signals for the detector, image processing unit for image enhancement, and the output stage for either displaying or storing.

Figure 1.1: Block diagram of a basic infrared imaging system.

This thesis reports the development of a multi-functional front-end electronics system for staring focal plane arrays (FPAs). Main tasks of this system include detector bias voltage and control signal generation, analog processing and digitization of detector output, and nonuniformity correction coefficient calculation. The performance of the front-end electronics has significant effect on the overall system performance, and inadequate quality of this block results in poor thermal images. Careful design and component selection insures a system with focal plane array limited performance [1].

#### 1.2 Aims

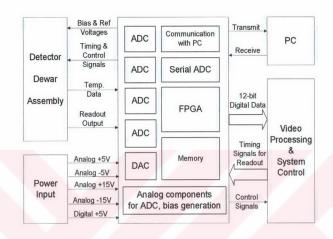

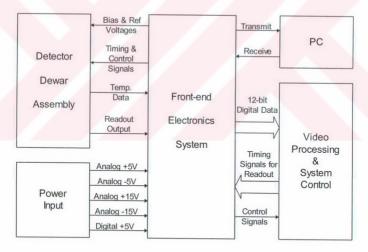

This thesis work focuses on the design and implementation of a front-end electronics system for a prototype thermal imaging system. The signals to the front-end electronics system come from a 128x128 InSb focal plane array coupled to an ROIC. The front-end electronics is designed to be compatible with the Indigo Systems' 980X series ROICs. The front-end electronics board is integrated with a video processing and system control board [2] for real time thermal imaging. This board generates timing signals for the detector, performs all image processing, and generates video signals for monitoring the real time thermal video. The video processing and system control board (VP\_SC) has been implemented through another M. Sc. Thesis [2]. The VP\_SC uses the nonuniformity correction coefficients calculated by the front-end electronics board to normalize the ROIC output. This board also converts the processed digital data to analog, and sends it to the monitor for display. A PC is used to control ROIC settings, to apply gain and offset for ROIC output, and monitor FPA temperature output.

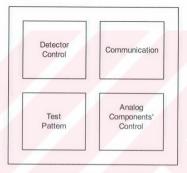

Main functions of the front-end electronics board include low-noise detector bias, reference and control signal generation, buffering, offset and gain control, clamping, differential driving, 12-bit digitization, FPA digital temperature measurement, PC communication, and normalization coefficient calculation. Figure 1.2 illustrates the blocks of the front-end electronics board and interface of the board

with the other units. Figure 1.3 shows a picture of the front-end electronics system board designed and implemented in this work.

Figure 1.2: Blocks and interface of the front-end electronics board.

Figure 1.3: Front-end electronics board.

The front-end electronics system was tested prior to integration with image processing board to ensure proper operation of board, and required flow of detector output through each integrated circuit on the board was checked. After the board was completely tested, it was integrated with the video processing and system control board to perform real time thermal imaging.

#### 1.3 Organization of the Thesis

This thesis is composed of seven chapters. Chapter 2 provides an overview of the status of the infrared imaging technology.

Chapter 3 describes the readout integrated circuit (ROIC) by Indigo Systems which was used with the 128x128 FPA to test the prototype thermal imaging system.

Chapter 4 contains detailed information on the front-end electronics system, including the functions implemented and the hardware design. This chapter also describes the normalization coefficient calculation algorithms applied to correct non-uniformities of the FPA. Chapter 5 presents the simulation and testing of the board.

Chapter 6 focuses on the integration of the front-end electronics system with the video processing and system control board, and testing the system. Finally, Chapter 7 gives the conclusion and future work.

#### **CHAPTER 2**

#### INFRARED IMAGING SYSTEMS

#### 2.1 Introduction

"Infra" is a prefix from the Latin meaning "below" or "beneath." Hence, infrared refers to the region beneath the red [3], lying between visible light and microwave portions of the electromagnetic spectrum. That region of the spectrum is also called as the heat region of the spectrum since objects radiate energy in the infrared region when they are heated. All objects, even the ones below 273K such as ice, radiate some energy in the infrared region.

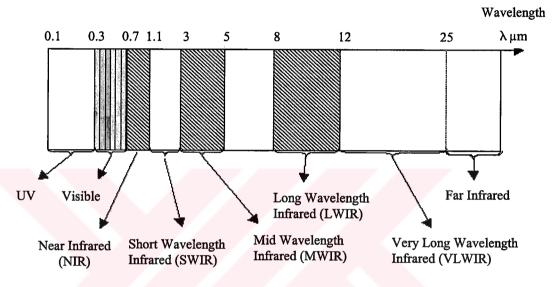

Infrared radiation (IR) is a form of electromagnetic radiation, and it mainly differs from the other forms of electromagnetic radiation such as visible light, radio waves, and x-rays in its wavelength. Infrared region spans the 0.7 - 1000 µm region of the electromagnetic spectrum. Figure 2.1 shows a portion of the electromagnetic spectrum. Detection systems can not use the whole IR emission spectrum due to the absorption of the radiation by water or carbon dioxide in the atmosphere. However, a number of wavelength bands have good transmission, which are given below.

- The long wavelength IR (LWIR) band extends from 8 μm to 14 μm, and 100 % transmission can be realized on the 9 12 μm band. Most of the terrestrial objects have perfect visibility in the LWIR band.

- The medium wavelength IR (MWIR or MIR) band is in the  $3.3-5.0~\mu m$  portion of the spectrum, and provides 100 % transmission. The ambient background

- noise is lower than that of the LWIR.

- Visible and short wavelength IR (SWIR or near IR, NIR) in the 0.35 2.5 μm region has a high atmospheric transmission and peak solar transmission, so that the IR detectors provide better clarity and resolution than LWIR or MWIR. However, objects at 300K can not be visualized without ambient or artificially introduced illumination in SWIR.

Figure 2.1 Electromagnetic Spectrum.

#### 2.2 General Classification of IR Detectors

An infrared detector is used to convert the radiant energy in the infrared into a measurable form [3]. Infrared detectors have a wide range of applications in the military, scientific, industrial, medical, security, and automotive areas. They provide the ability of seeing the objects in the dark or in the obscured visibility by detecting the infrared energy emitted by objects different from the visible light imagers. Thermal images are formed from the detected energy based upon the energy differences between the objects so that an obscured object in visible light can be visualized.

Two fundamental methods are used for IR detection: thermal and photon

detection. Both types respond to absorbed photons, but they use different response mechanisms [4]. In thermal detection, the absorbed photons cause a temperature change, and then a temperature-dependent property of the detector material is measured. In photon detection, the absorbed photons directly generate free electrons or holes. Most of the advanced IR imaging systems makes use of photon detectors due to the ease in fabrication of large 2D focal plane arrays. However, they require cooling to cyrogenic temperatures. Thermal-detection based infrared imaging systems are uncooled and lower cost systems, but their performance is limited. Table 2.1 shows classification of infrared detectors and their subtypes based on their detection mechanisms.

Table 2.1 Infrared detector types.

| <u>Photon</u>        | <u>Thermal</u> |

|----------------------|----------------|

| Photovoltaic         | Bolometer      |

| Photoconductive      | Pyroelectric   |

| Photoelectromagnetic | Thermocouple   |

| Phototransistor      | Pyromagnetic   |

| Photon Drag          | Golay Cells    |

| Quantum Counter      | Liquid Crystal |

|                      |                |

Infrared detectors are usually specified by the parameters of responsivity, cutoff wavelength, and detectivity. Responsivity is the ratio of electrical output to radiant input power. Cutoff wavelength is the longer of the two wavelengths at which the responsivity of the detector is half of its maximum. Detectivity is the figure of merit that takes responsivity, noise, and detector element size into account.

A number of formats are possible for the infrared detectors. Infrared detectors are available as single element detectors, long linear arrays, or 2D focal plane arrays [5]. Single element detectors can be in circular, rectangular, cruciform, and other geometries. Linear and 2D arrays are fabricated with different device architectures. Obtaining a thermal image from a single element detector or a long linear array requires the use of a scanning mechanism across the focused object.

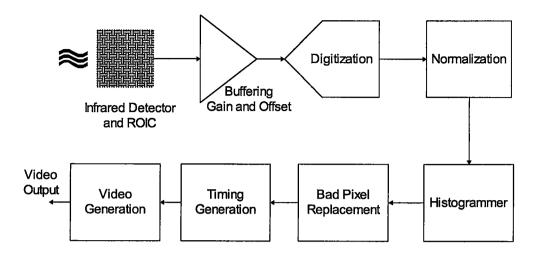

The electronic circuits used to transmit detector array signals to relevant terminals in an appropriate form are called Read Out Integrated Circuits (ROICs) or analog multiplexers. Figure 2.2.a shows a detector array and the Readout IC, and Figure 2.2.b shows the integration of them with flip-chip bonding technique.

Figure 2.2.a: 128x128 detector array and Silicon ROIC.

Figure 2.2.b: Schematics of flip-chip bonded detector and ROIC.

The readout element reads and transfers the signal from the image-sensing element to the output of the image sensor. Major functions of the ROICs can be summarized as,

providing impedance buffer between detector and integration node,

- providing and maintaining detector bias,

- providing detector current,

- providing first level of signal processing,

- providing multiplexed signal output of the image sensor.

There are different readout techniques developed for IR focal plane arrays with different materials and structures. The two fundamental types of readout integrated circuits are charge-coupled-device (CCD) based and metal-oxide semiconductor (CMOS) based ones. The readout integrated circuit ISC9806 used in this thesis is CMOS based.

#### 2.3 IR Imaging

Infrared imaging is the remote sensing and visual representation of the infrared energy emitted by all the objects. The variations in the visual representation are the result of the temperature variations across the scene. The detected radiation coming from the target and its background in the scene includes the self-emission, reflected emission, and atmospheric path radiance. Distinguishing a target from its background requires the detected radiation be different from its environment respectively.

There are a number of specifications to characterize an imaging system. Temperature resolution, the ability to measure small temperature differences, can be as fine as 0.01° C. Spatial resolution, the ability to measure temperatures on small areas, can be as fine as 15 microns. Temperature resolution is the smallest temperature difference in the scene that the system can resolve. Noise equivalent temperature difference (NETD) and minimum resolvable temperature difference (MRTD) are used to express the temperature resolution. NETD is the temperature difference for which the signal at the input equals the noise at the output. MRTD is the smallest temperature difference that can be recognized on the display. Angular resolution is the effective width of the detector element divided by the focal length of

the infrared optics. Angular resolution is also called instantaneous field of view (IFOV). System field of view, also referred as total field of view (TFOV), is the plane angel subtended by the scene imaged.

Infrared imaging technology has been developed for several applications. Hudson listed more than 100 different applications for thermal imaging systems in 1969 [6]. He categorized the list into four major divisions: military, industrial, medical, and scientific. Each division was then subdivided into (1) search, track and range, (2) radiometry, (3) spectroradiometry, (4) thermal imaging, (5) reflected flux, and (6) cooperative source.

Today, two broad categories are used: military and commercial. Table 2.2 indicates a few applications in each category. Military and commercial systems have similarities in their basic design; but each system is built for a specific purpose. As a result, different performance parameters should be used to describe military and commercial systems.

The recent tendency in infrared imaging systems is the integration of the infrared cameras with the personal computer (PC). The electronics are placed on a printed circuit board that can plug into a slot of the PC, and use the advantage of the high-resolution display, processing capability and mass storage. This integration prevents the cost overhead due to the separate displays, separate memory and enclosures.

New focal plane arrays based on thermal effects will result in high resolution cameras which can be fabricated in significantly smaller configurations and at much lower cost, however with lower performance. Focal plane arrays based on photon effects will also benefit from the reduced costs, and will be widely used in applications that need higher performance than that provided by the thermal detectors. These trends will further spur the growth in thermal imaging. The broad number of areas utilizing infrared imaging in new applications will be dramatic.

Table 2.2 Thermal Imaging Applications [7].

| COMMUNITY  | APPLICATIONS  Reconnaissance Target acquisition Fire control Navigation |                                                         |

|------------|-------------------------------------------------------------------------|---------------------------------------------------------|

| MILITARY   |                                                                         |                                                         |

|            | CIVIL                                                                   | Law enforcement<br>Fire fighting<br>Border patrol       |

|            | ENVIRONMENTAL                                                           | Earth resources Pollution control Energy conservation   |

| COMMERCIAL | INDUSTRIAL                                                              | Maintenance<br>Manufacturing<br>Non-destructive testing |

|            | MEDICAL                                                                 | Mammography Soft tissue injury Arterial constriction    |

#### 2.4 IR Imaging System Electronics

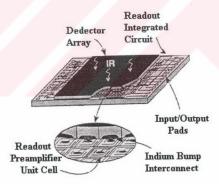

An IR imaging system is composed of optics, detector, front-end electronics, digital image processing and output stages. A scanning mechanism may be required if the used detector is of a single element or long linear array format. Depending on the type of the detector, cooled or uncooled, a cooler may also be necessary. Figure 2.3 shows the electronics portion of an infrared imaging system including major subblocks. Buffering, gain and offset, and digitization parts compose the front-end electronics section of the system. Normalization, histogrammer, bad pixel replacement, timing generation, and video generation are included in the digital image processing section. The output of this block is sent to either a monitor for display, or to a storage equipment.

Figure 2.3: Block diagram of the IR imaging camera electronics.

Basic functions of the infrared camera electronics can be summarized as;

- Clock, syncronization and control signal generation for the detector

- Low noise bias and reference voltage generation for detector elements and ROIC

- Offset/Gain correction of detector output

- Analog-to-digital conversion of detector output

- Digital image processing section for non-uniformity corrections (NUC)

- Histogrammer block for compression coefficient calculation

- Compression for video output

- Timing generation for synchronization with required output format

- Video signal generation and image display

#### 2.4.1 Front-End Electronics

Front-end electronics part of an infrared imaging system, following detector stage, plays an important role to designate the overall system performance. Detector interface requires careful design since bias generation must be low noise, frequently less than 100  $\mu$ V. The most important role of the front-end electronics is to digitize the ROIC output with minimum distortion. Therefore, it is necessary to use high

speed, high gain/bandwidth product, and low noise components during the analog processing section of the detector output flow. Allowed noise level and required sensivity determine the number of bits of the output of ADC, which is 12 in our case.

#### 2.4.2 Normalization for Infrared Imaging Systems

Images utilizing focal plane array detectors suffer from fixed pattern noise generated by non-uniformities in the response of the detector elements [8]. Fixed pattern noise is a result of variations in response from detector to detector in an IRFPA given a uniform input flux [9]. The presence of fixed pattern noise severely reduces the performance of the whole system, and its removal is essential.

The conventional approach to remove the nonuniformity, and hence increasing the accuracy of detector output data is to correct the detector data by calibrating, and periodically recalibrating, the detector array. While the signal processing system is off-line, a reference is introduced—such as a thermal reference source in the case of the exemplary thermal imaging systems—and the response of each detector in the detector array to the reference is recorded. Using these detector reference responses, a detector calibration error representative of deviation in detector reference response from the ideal can be computed for each detector of the detector array, and it can be used during on-line processing to correct detector output.

While the calibration correction for each detector will be different because of nonuniformities in detector-to-detector response to the reference, the reference output error for each detector can be characterized by a first order linear function ax + b, where a is a gain factor, and b is an offset level. That is, for each detector, detector response to a reference can be used to compute calibration gain (a) and offset (b) coefficients for correcting detector output. These calibration coefficients are then used to correct detector output errors during on-line operation.

#### 2.5 Summary

This chapter makes an introduction to thermal imaging systems. It overviews the classification of IR detectors, IR detector formats, IR imaging, and applications. The front-end electronics system developed in this work receives its input from a 128x128 photon detector array coupled to a commercial readout circuit, performs analog processing, converts the signal to digital format, and sends it to the video processing and system control board. Another function of the system developed in this work is to generate bias voltages and control signals for the commercial ISC9806 readout circuit, developed by Indigo Systems Inc. (Santa Barbara, USA). In the next chapter, ISC9806 readout integrated circuit will be introduced.

#### **CHAPTER 3**

#### INDIGO'S ISC9806 READOUT INTEGRATED CIRCUIT

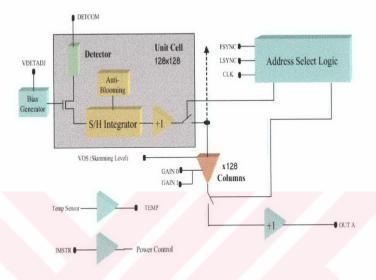

Read-out integrated circuit used for the 128x128 detector array in this thesis is ISC9806 from Indigo Systems Inc (www.indigosystems.com). The ISC9806 is a high performance, 128 x 128 ROIC for p on n detectors. The ROIC supports a wide range of applications from portable infrared imagers to high-speed industrial imagers with its flexible and advanced operation modes.

A 0.6 micron single poly, double metal process benefiting from high speed CMOS transistors is used in the fabrication of the ISC9806. The ISC9806 has a 38  $\mu$ m pixel pitch, and the input charge handling capacity of the unit cells are 6.2 x 10<sup>6</sup> electrons.

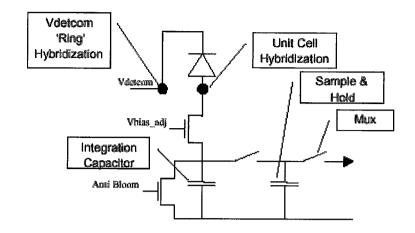

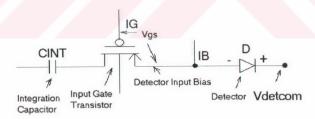

#### 3.1 Input Circuit of ISC9806 ROIC

Figure 3.1 shows the simplified unit cell schematic for ISC9806 input circuit, using direct injection method. Detector current passing through the input gate transistor integrates on the integration capacitor. The anti-bloom gate prevents the input circuit from saturating. The integrated voltage is read out and multiplexed to the column amplifier. The control of the detector bias is realized by applying a bias to the Vdet\_adj pad in default mode and by using the Serial Control Register of the ROIC in command mode.

Figure 3.1: Simplified unit cell schematic for ISC9806 input circuit, where direct injection method is used [10].

#### 3.2 Interface Connections

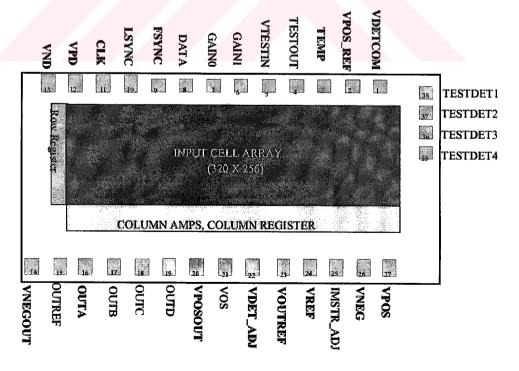

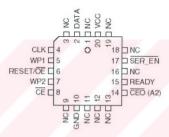

ISC9806 has a total of 38 interconnects and some of them are reserved for factory testing as shown in Figure 3.2. Table 3.1 gives the pinout descriptions of the ISC9806 ROIC.

Figure 3.2: ISC9806 pinout schematic [10].

Table 3.1 Pinout descriptions of the ISC9806 ROIC [10].

| Pin No | Signal Name | Description                                            |  |

|--------|-------------|--------------------------------------------------------|--|

| 6      | Gain0       | External Gain: These pins are used to control the gain |  |

| 7      | Gain1       | of the chip when operating in Default Mode             |  |

| 8      | Data        | Serial Control Register Data                           |  |

| 9      | Fsync       | Frame Sync                                             |  |

| 10     | Lsync       | Line Sync                                              |  |

| 11     | Clk         | Data Output and Command Data Stream Clock              |  |

| 16     | OutA        | Video Output A                                         |  |

| 17     | OutB        | Video Output B                                         |  |

| 18     | OutC        | Video Output C                                         |  |

| 19     | OutD        | Video Output D                                         |  |

| 15     | Outref      | Common Mode Reference Output                           |  |

| 3      | Temp        | Buffered Temperature Diode                             |  |

| 23     | Voutref     | Analog Output Reference Voltage                        |  |

| 21     | Vos         | Skimming Voltage                                       |  |

| 24     | Vref        | Analog Reference Voltage                               |  |

| 22     | VdetAdj     | Detector Bias Adjustment                               |  |

| 25     | ImstrAdj    | Master Current Adjustment                              |  |

| 1      | Vdetcom     | Detector Common                                        |  |

| 2      | VposRef     | Low Voltage Detector VDETCOM Supply                    |  |

| 27     | Vpos        | Analog Supply                                          |  |

| 12     | Vpd         | Digital Supply                                         |  |

| 20     | Vposout     | Output Supply                                          |  |

| 13     | Vnd         | Digital Return                                         |  |

| 15     | Vnegout     | Output Ground                                          |  |

| 26     | Vneg        | Analog Ground                                          |  |

#### 3.3 Operation Modes

The ISC9806 has two operation modes; a simplified Default Mode and a programmable Command Mode. In default mode, fewer external pad connections are required and only single output, full window, NTSC or PAL operation is supported. The Command Mode requires more external pad connections and enables the use of advanced features such as dynamic image transposition, dynamic windowing, high speed multiple output configurations and adjustable global offset.

#### 3.3.1 Default Mode

This mode has a simple interface with reduced external electronics and power dissipation. This mode is suitable for applications where advanced ROIC features or high-speed performance are not required. Serial Control Register is not used in the default mode. Therefore, advanced features of the ROIC such as windowing, invert/revert and multiple data outputs are not available in the Default Mode. The maximum input clock frequency is 3.07 MHz providing an output rate of 6.14 MSPS maximum for default mode. At power-up, the device defaults to operation as a standard 128x128 format imager. Figure 3.3 shows the block diagram for default mode operation. Default Mode operation of ROIC requires a total of 19 interconnects.

In default mode, the bias applied on the Vdet\_adj pad controls the detector bias. The detector bias is defined as the difference between the Vdetcom potential and the detector input bias potential as shown in Figure 3.4, which illustrates a typical direct injection ROIC circuit. Maximum forward detector bias is obtained by adjusting Vdet\_adj to 5.5V, and maximum reverse bias condition is achieved by setting the bias applied to this pad to 0 V.

Figure 3.3: Block diagram for default mode operation in Indigo Systems' ROIC [10].

Figure 3.4: Typical direct injection circuit [10].

#### 3.3.2 Command Mode

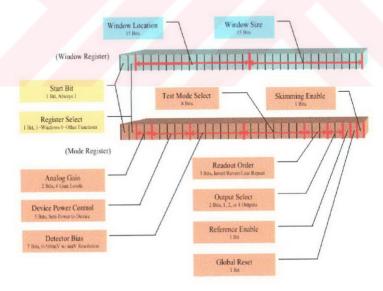

Command Mode operation makes use of the on chip Serial Control Register to control operation modes and advanced ROIC features. Figure 3.5 illustrates the

fields of the serial control register. The DATA pad is used to load control words into the serial control register to operate in this mode. The settings in this register determine the gain state, detector bias setting, power bias control, master current bias, skimming setting, output mode, window size, window position, image transposition and test mode. 16-20 interconnects are required, depending on the number of outputs and options invoked. There are 4 digital input signals:

- FSYNC : Controls frame start and integration time,

- LSYNC : Controls line readout timing,

- CLK: Master clock frequencies up to 5 MHz (10 MHz output rate) are supported when the ROIC is in the Command Mode.

- DATA: For command mode operation, IMSTR\_ADJ, VDET\_ADJ, GAIN0

and GAIN1 pads are controlled through command words shifted into the serial

control register via the DATA input pad. The DATA pad is driven as a clock

signal.

Figure 3.5: Serial control register [10].

The supply voltages are,

- VPOS: Positive supply for all analog circuits,

- VPD: Positive supply for all digital circuits,

- VNEG: Ground for all analog circuits,

- VNEGOUT: Ground for all analog circuits except output multiplexer and buffers.

- VND: Ground for all digital circuits,

- VREF, VOUTREF: Reference supply voltages

#### Other pads are as follows:

- VDETCOM: Detector substrate connection. Detector common bias is set by the voltage applied to this pad. The bias supplied to this pad may be in the range of 0 to 8.5 volts referenced to VNEG (at 0 volts). VDETCOM pad and VPOS\_REF pads are connected together using a floating off chip pad for low reverse bias voltage detectors such as InSb photodiodes. VPOS\_REF pad should not be applied any bias since VPOS\_REF pad is a low impedance voltage output pad from the readout to the system.

- VOS: Skimming control voltage,

- TEMP: Temperature monitoring pad, an ADC is needed to display the temperature sensor output,

- OUTA-D: Output pads,

- OUTR : Reference output pad.

GAIN0 and GAIN1 pads are used to adjust the amplifier gain. The four possible gain states are given in Table 3.2:

Table 3.2: Gain States for internal amplifier of ROIC [10].

| GAIN1(GC1) | GAINO(GC0) | Relative Signal Gain |

|------------|------------|----------------------|

| 0          | 0          | 1 (default)          |

| 0          | 1          | 1.33                 |

| 1          | 0          | 2                    |

| 1          | 1          | 3.8                  |

In the command mode operation, the amplifier gain is adjusted through the Serial Control Register field GC(1:0), and GAIN pads should be driven low or left floating.

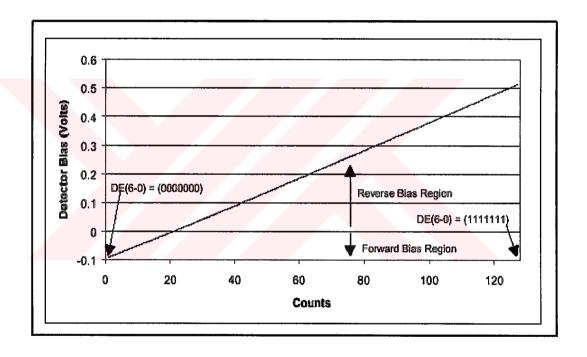

Detector bias adjustment is controlled through the Serial Control Register field DE(6:0) in command mode. When power is applied to the readout, the detector bias initializes to near the highest forward bias condition, also DE(6:0) is set to "0000000". Figure 3.6 shows that programming DE(6:0) to "1111111" will set the detector input bias to the maximum reverse bias condition. The detector bias can be read through the Vdet adj pad in the command mode.

Figure 3.6: Command mode detector bias [10].

The chip is in the single output mode with the lowest power setting and disabled output reference in the default power up state. The power may need to be increased according to the mode of the operation required. This is achieved by using the Serial Control Register field PW(1:0) and I(2:0).

The I(2:0) field allows adjustment of the master current source to cover the requirements for process variations or changes in current requirements due to the

operating temperature of the device. When power is applied to the chip, I(2:0) defaults to "100", which corresponds to approximately 100  $\mu$ A master current source. The master current can be increased by about 20% with a maximum setting of "111", and can be decreased by about 20% with the minimum setting of "000".

The PW(1:0) field is used to provide major current adjustments, that may be required for different clock rate applications. The two bits of the PW(1:0) field are sent to an on chip DAC which adjusts the transistor currents in the signal path. The default value at power up for PW(1:0) is "00", which corresponds to the minimum current condition. Adjusting the PW(1:0) field to "11" sets the bias to maximum current condition. The finest possible bias adjustment resolution with this method of current adjustment is equal to the minimum current with a maximum adjustment range of approximately 4 times the minimum current. Adjustments to the power settings have no effect on the power of the output driver circuitry. For a master clock frequency of 5 MHz, and 4 output mode, PWR(1:0) should be "11" and I(2:0) should be "000".

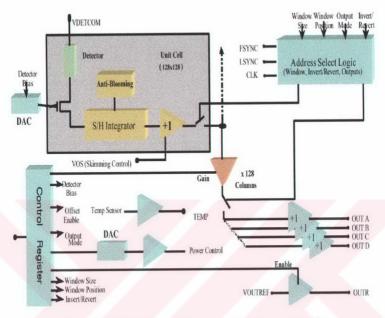

The skimming level adjustment is a global offset function utilized in the column amplifier circuit. Operating the skimming function requires the VOS pad be biased to a voltage greater than the voltage on the VREF pad. The VOS voltage is in the range of VREF to VPOS, which corresponds to offsetting from 0 to 100 % of full well. The skimming function is disabled by setting the OE bit in the Serial Control Register to 0. Setting the OE bit to 1 enables skimming. The setting of the skimming voltage is implemented through the VOS pad. Figure 3.7 describes the command mode operation.

Figure 3.7: Block diagram for command mode operation [10].

The advanced features of the readout, including windowing, invert/revert readout order, output selection, reference enable, global reset, skimming enable, test mode selection, detector bias adjustment, master current adjustment, device power control and analog gain settings, are controlled by the 32-bit Serial Control Register. The Serial Control Register can contain two types of data words: a window or a mode word. A window word includes the row and column starting address along with the size of the window. A mode word contains operation mode parameters and adjustments to control the readout.

All register bits, fields and functions are described below starting with the Window Data Word.

| Register Bit | <u>Field</u>    | <u>Function</u>                                 |

|--------------|-----------------|-------------------------------------------------|

| D29          | Start Bit       | Defines start of control word, 1 for valid word |

| D28          | Register Select | Determines window/mode word, window word = $1$  |

| D27-D24      | Unused bits     | Not used                                        |

| D23-D18      | WAX(5:0)        | Window start address for column                 |

| D17-D12      | WAY(5:0)        | Window start address for row                    |

| D11-D6       | WSX(5:0)        | Readout window size, # of columns               |

| D5-D0        | WSY(5:0)        | Readout window size, # of rows                  |

## For the Mode Data Word:

| roi the Moc  | ie Data                       | word.      |            |              |             |                     |

|--------------|-------------------------------|------------|------------|--------------|-------------|---------------------|

| Register Bit | <u>Field</u>                  |            | Fund       | ction        |             |                     |

| D29          | Start E                       | Bit        | Def        | ines start o | of control  | word, always=1 for  |

|              |                               |            | valid      | d word       |             |                     |

| D28          | Regist                        | er Selec   | et Dete    | ermines w    | indow/mo    | ode word, mode      |

|              |                               |            | word       | d = 0        |             |                     |

| D27-D26      | GC(1:                         | 0)         | Sets       | the ampli    | fier gain   | state               |

| D25-D24      | PW(1:                         | (0)        | Pow        | er control   | adjustme    | ent                 |

| D23-D21      | I(2:0)                        |            | Mas        | ter current  | t adjustme  | ent                 |

| D20-D14      | DE(6:                         | 0)         | Setti      | ing for det  | ector bias  | adjustment          |

| D13-D8       | TS(5:0                        | 0)         | Test       | t functions  | for facto   | ry characterization |

|              |                               |            | testi      | ng only      |             |                     |

| D7-D5        | RO(2:0) Selects readout order |            |            |              |             |                     |

|              | RO2                           | <u>RO1</u> | <u>RO0</u> | <b>XDIR</b>  | <b>YDIR</b> | Line Repeat         |

|              | 0                             | 0          | 0          | normal       | normal      | no                  |

|              | 0                             | 0          | 1          | normal       | normal      | yes                 |

|              | 0                             | 1          | 0          | normal       | invert      | no                  |

|              | 0                             | 1          | 1          | normal       | invert      | yes                 |

|              | 1                             | 0          | 0          | revert       | normal      | no                  |

|              | 1                             | 0          | 1          | revert       | normal      | yes                 |

|              | 1                             | 1          | 0          | revert       | invert      | no                  |

|              | 1                             | 1          | 1          | revert       | invert      | yes                 |

| D4-D3 | OM(1 | :0) | Selects number of outputs             |

|-------|------|-----|---------------------------------------|

|       | OM1  | OM2 | Number of Outputs                     |

|       | 0    | 0   | 1                                     |

|       | 0    | 1   | 2                                     |

|       | 1    | 0   | 3                                     |

|       | 1    | 1   | 4                                     |

| D2    | RE   |     | Reference output, 0=disable, 1=enable |

| D1    | RST  |     | Reset to power up conditions          |

| D0    | OE   |     | Skimming, 0=disable, 1=enable         |

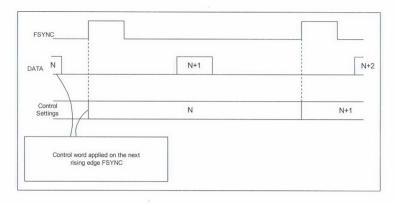

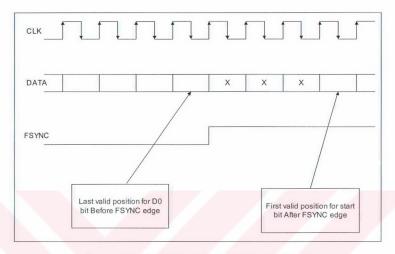

The Serial Control Register is loaded through the DATA input pad. Figure 3.8 shows the timing of valid DATA relative to the FSYNC signal. DATA is sampled on the falling edge of CLK. During a frame time, a control word is loaded once, and 32 clock cycles are required to load a control word. After a control word has been loaded, it is held to be applied on the next rising edge of FSYNC. A new control word is only required if settings need to be changed. If a new control word is not loaded before the rising edge of FSYNC, the existing settings are applied. A detailed view in Figure 3.9 shows that a valid control word has the rising edge of the start bit either at least 32 clock cycles before the rising edge of FSYNC or at least 3 clock cycles after the rising edge of FSYNC.

Figure 3.8: Serial Control Register Timing.

Figure 3.9: Detailed timing for Serial Control Register.

## 3.4 Output Modes

Readout can be adjusted to support one, two or four outputs with or without an output reference. The OM(1:0) bits of the Serial Control Register designate the number of outputs for the chip. In the single output configuration, all pixels are read out through OutA. In the multiple output configuration, pixels are allocated to a specific output channel, and will be read through only that channel, regardless of the image transposition (invert/revert), and windowing modes. When four-output mode is selected, the first pixel appears at OutA, the second pixel appears at OutB, the third pixel at OutC, and the forth at OutD. Alternating in four pixel increments, pixels appear at the A, B, C and D output channels, respectively. For four output mode, OM(1:0) should be "11".

## 3.5 Windowing

The readout full window size is 128 x 128, which is the default window size.

The window size can be changed in the Command Mode. The Serial Control Register

data bits WAX(5:0) and WAY(5:0) determine the column and row start addresses, respectively. The data bits WSX(5:0) and WSY(5:0) define the window size by the number of columns and the number of rows, respectively.

#### 3.6 Readout Timing

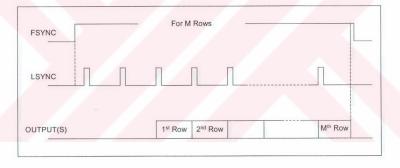

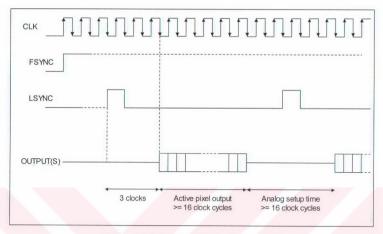

The readout time is dependent on pixel rate, number of outputs, window size, line repeat mode and line dead times. Setting the bit RO0 in the Serial Control Register controls the line repeat mode. The timing diagram in Figure 3.10 shows the readout timing.

Figure 3.10: Readout timing.

As shown in a more detailed timing in Figure 3.11, a line time is composed of the analog setup time plus the active pixel time plus any line dead time. The analog setup time is minimum 16 clock cycles, and the active pixel time is also minimum 16 clock cycles, resulting in a line time of minimum 32 clock cycles in the four output mode.

Figure 3.11: Detailed timing for readout.

#### 3.7 Integration Modes

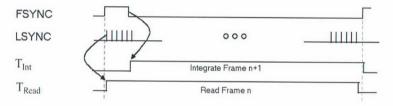

The ISC9806 ROIC samples all the pixels at the same time (snapshot integration) and the process is controlled by the FSYNC (Frame synchronization) clock of ROIC. There are two modes for this snapshot integration, Integrate-While-Read and Integrate-Then-Read modes.

A timing diagram related to the Integrate-While-Read mode is shown in Figure 3.12 next. Frame time starts with the rising edge of the FSYNC signal. Integration of the next frame starts after the falling edge of the FSYNC and occurs during current frame readout. Readout phase includes LSYNC (Line synchronization) pulses required for row and column synchronization. In this mode, frame time nearly equals the readout time.

Figure 3.12: Integrate-While-Read timing diagram [10].

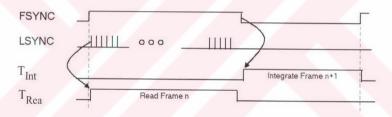

For the Integrate-Then-Read Mode, frame time starts with the rising edge of FSYNC. Figure 3.13 shows a timing diagram for the Integrate-Then-Read mode. In this mode, FSYNC clock remains high until the readout sequence has been completed. Since readout and integration parts are separated and follow each other, frame time is approximately equal to the readout time plus the integration time.

Figure 3.13: Integrate-Then-Read timing diagram [10].

## 3.8 Integration Time

For a predefined master clock frequency (MC) and frame time, variations on the ON and OFF time of the FSYNC clock pulse determines the integration time of the ROIC. The rising edge of the FSYNC clock starts the integration process and location of its falling edge controls the integration time. In order to provide synchronization between the FSYNC and the ROIC logic, FSYNC clock should be changed on the rising edge of the master clock. It is required that minimum OFF time of FSYNC clock must be at least one clock cycle per frame. Any change made on the FSYNC clock duty cycle will be applied to the logic circuitry on the next falling edge

of the master clock. Figure 3.14 shows the detailed timing of the rising and falling FSYNC edges with respect to the master clock.

| <b>Parameter</b> | Min   | Typ                | Max  | Comments                                   |

|------------------|-------|--------------------|------|--------------------------------------------|

| $T_r$            | -     | -                  | 10ns | 10-90% (All signals)                       |

| $T_f$            | -     | -                  | 10ns | 90-10% (All signals)                       |

| $T_{sh}$         | 5ns   | -                  | -    | Setup / Hold Time: All Signals to CLK Edge |

| T <sub>ep</sub>  | 200ns | -                  | -    | 10MHz Pixel Rate                           |

| $T_{hi}$         | -     | .5*T <sub>cp</sub> | -    | Clock Duty Cycle = 50%                     |

| T <sub>lo</sub>  | -     | .5*T <sub>ep</sub> |      | Clock Duty Cycle = 50%                     |

|                  |       |                    |      |                                            |

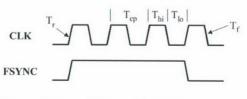

Figure 3.14: Detailed timings for digital control signals [10].

Approximate integration time for the Integrate-Then-Read Mode can be calculated approximately as

Tint

$$\approx$$

Tframe – (Tfsync – 25.5 MC cycles) (3.1)

where

Tint : Integration time, measured in MC cycles

Tframe: Frame time, measured in MC cycles

Tfsync: Width of fsync clock pulse, measured in MC cycles.

## 3.9 Summary

This chapter introduces the Indigo Systems' ISC9806 readout integrated circuit, presenting its circuit architecture, interface connections, operational modes and pad functions. Serial control register controlling readout circuitry is described with related timings. Detector signal output timings are also examined. The chapter concludes with integration modes and integration timings. The next chapter will present the design of the front-end electronics board implemented in this work.

#### **CHAPTER 4**

#### FRONT-END ELECTRONICS SYSTEM DESIGN

#### 4.1 Introduction

Front-end electronics system plays an important role in determining the imaging system's performance. This chapter describes the design of the front-end electronics board implemented in this thesis including the hardware design rules followed and the user interface program written with HPVEE.

Front-end electronics is the interface electronics between detector readout and video processing board. Figure 4.1 shows the simplified interface diagram of the front-end electronics board with the other blocks in the system. The main function of the system is to convert analog outputs of the detector to 12-bit digital data, to generate command signals for the readout and to generate some control signals for the video processing and system control electronics.

Figure 4.1: Simplified interface diagram of the front-end electronics board with the other blocks in the system.

The details of the functions of the front-end electronics board are given in the following sections. Section 4.2 describes the operation and interface. Section 4.3 explains the analog section of the board. Section 4.4 focuses on the digital section of the board. Section 4.5 overviews the printed circuit board (PCB) design rules followed. This chapter concludes with normalization algorithm given in Section 4.6.

## 4.2 Operation and Interface

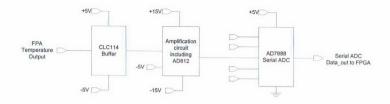

Figure 4.2 shows the interface block diagram of the front-end electronics system with the other blocks in the thermal imaging system. Figure 4.3 illustrates the major blocks of the front-end electronics system.

Figure 4.2: Interface block diagram of the front-end electronics system.

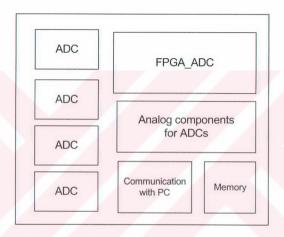

The system is composed of two parts: analog and digital. Functions of the analog section include low-noise readout bias and reference generation, detector signal unity gain buffering, DAC controlled global gain and offset level generation, clamping, differential ADC driving, 12-bit video digitization, DAC controlled gain

offset and readout temperature monitoring. Digital section provides sampling and multiplexing of digital data, PC communication with HPVEE user interface program, digital-to-analog converter control for global gain/offset levels and readout biases, serial ADC control for potentiometer-controlled settings and SRAM interface to store scene data for normalization coefficient calculation. The HPVEE user interface program controls the ROIC operation through the ROIC serial control register.

Figure 4.3: Major front-end electronics system blocks.

## 4.3 Analog Section

Analog section is the block where the analog processing of ROIC output, bias and reference generation for the ROIC and potentiometer controls are implemented. Figure 4.4 gives the block diagram for the analog section. The selection of the analog components used in this system is leaded by low-noise, sufficient bandwidth and fast settling time requirements. All of the components are industrial grade for better temperature dependance and surface-mount to reduce noise coupling and area related problems. The following sections describe the analog section of the front-end electronics board, including buffering, offset and gain amplifier and control, clamper,

differential driver, analog-to-digital conversion, bias and reference generation, and temperature data monitoring.

Figure 4.4: Block diagram for the analog section.

#### 4.3.1 Buffering

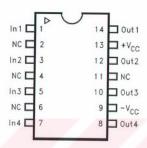

The first component in the analog data processing chain is the CLC114 [11], quad low-power video buffer from National Semiconductor. The ROIC output requires a minimum resistance of  $100K\Omega$  and a maximum capacitance of 25 pF as the load for a proper transmission. However, AD812, used for offset level correction at the next stage, has an impedance of  $65\Omega$  at the negative input, so a buffer stage is needed at the ROIC outputs, otherwise connecting the source directly to the load would result in significant signal attenuation. Hence, 4 pixel outputs of the readout are buffered first. Assuming the system will work at 10 MHz sampling rate, and examining other specifications of the buffer which are given below, CLC114 is selected to be used as a buffer. Figure 4.5 gives the pinout for CLC114.

Low supply current

16.5 mA

• Wide -3dB BW

>135 MHz

Fast slew rate 200 V/s

Gain flatness ±0.8dB

Equivalent Input Noise -155 dBm<sub>1Hz</sub>

Figure 4.5: Pinout for CLC114 [11].

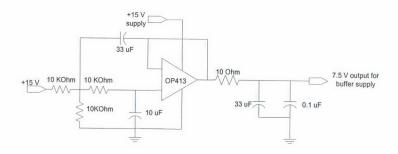

The output voltage range for CLC114 is 0 - 3.8V for a single +5V supply. Since ROIC output voltage is between 1.6V and 4.6V with 3V swing, use of 5V supply would clip the CLC114 output, so a higher supply is needed. For this purpose, a voltage divider circuit is used to obtain 7.5V from the 15V power input. The opamp used in this circuit is OP413 [12] from Analog Devices. The circuit used for this purpose is shown in Figure 4.6.

Figure 4.6: Divisor circuit for 7.5V supply generation.

#### 4.3.2 Offset and Gain Amplifier and Control

Analog gain and offset control provide scene dynamic range management [13]. The input signal range presented to the analog-to-digital converter can be optimized to a particular scene content by adjusting the gain and offset resulting in maximum sensivity. In this work, offset and gain level generation is controlled by an FPGA (Field Programmable Gate Array), which writes to a Digital-to-Analog Converter (DAC) to generate the required voltages. To change the gain and offset levels, either Hewlett-Packard Visual Engineering Environment (HPVEE) user interface program or potentiometers on the board connected to a serial ADC are utilized. HPVEE is an iconic programming language optimized for instrument control by Hewlett-Packard.

User inputs through the PC are first converted to binary to be sent to the board in RS232 format. The incoming serial data through the RS232 port is converted to CMOS level by a transceiver IC, and sent to the FPGA. The serial data is then converted to parallel to form 12-bit digital data and written to the digital-to-analog converter which outputs the analog signals required for gain and offset control. Front-end electronics board output to the PC is first converted from parallel to serial and then sent to the transceiver by the FPGA. PC monitor showing user interfacing through the HPVEE program is presented in Appendix A.

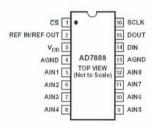

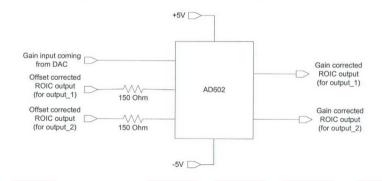

Offset and gain levels can also be controlled through the potentiometers on the board. Manual control of gain and offset settings are realized by an 8-channel, 125 kSPS, 12-bit serial ADC, AD7888 [14] from Analog Devices. Figure 4.7 gives the pinout for AD7888. The offset and gain inputs of the ADC are sampled and the result is sent to FPGA in serial form. This serial data is converted to parallel by the FPGA and the data is written to a DAC. The digital timing and control signals for conversion by the DAC are formed by the FPGA. Figure 4.8 shows the DAC circuit producing vskim and gain signals.

Figure 4.7: Pinout for AD7888 [14].

Figure 4.8: DAC circuit producing vskim and gain signals.

The output of the DAC generating the vskim and gain signals is between -5V and +5V, but a negative offset of 0 to -5V is needed to bring the ROIC output which is in the range of 1.6 - 4.6V to  $\pm 1.5V$  range, so that the ROIC output with the appropriate gain matches the ADCs' input range. Hence, the DAC output for vskim is divided by 2 and with the circuit shown in Figure 4.9, 2.5V is subtracted from the divided signal to obtain an offset voltage between 0 and -5V. The opamp used in this circuit is OP413.

Figure 4.9: 2.5V subtraction circuit from the divided vskim signal to obtain offset signal.

The buffered ROIC data is sent to an opamp configured to add the above offset in order to fit the video signal to the A/D converter's input range. The ROIC data is between 1.6V and 4.6V. Thus, an offset of -3.1V will convert the output to be in the range of  $\pm 1.5V$ . If we apply a gain of 1.67, then the output will be in the range of  $\pm 2.5V$ . AD812 [15], dual low-power opamp, from Analog Devices is used for the offset setting stage. Figure 4.10 shows the pinout of AD812. Figure 4.11 presents the circuit used to add offset and a gain of 1.67 to the buffered ROIC data.

Figure 4.10: Pinout for AD812 opamp [15].

Figure 4.11: The circuit used to add offset to the buffered ROIC data.

Gain level generation, one of the most significant functions of front-end electronics system, is similar to the offset level generation. It may be either through the HPVEE user interface program or through the potentiometers. The output of the DAC is sent to AD602 [16], dual low-noise wideband variable gain amplifier from Analog Devices as shown in Figure 4.12. The gain of AD602 can be calculated using the following equation:

Gain (dB) =

$$32 V_G + 10$$

(4.1)

where  $V_G$  is the variable gain amplifier output coming from the DAC output.  $V_G$  is set to be in the range of  $\pm 0.398V$  to make amplification by a factor of 14 possible.

Figure 4.12: AD602 input and output [16].

The other important parameters of the AD602 are its input resistance (100  $\Omega$ ), input capacitance (2pF), output impedance (2  $\Omega$ ) and the nominal maximum input signal (VINP). Maximum input signal should be 1 V rms. (1.4 V peak) when using the recommended  $\pm 5$  V supplies. In order to prevent any malfunction, a 100  $\Omega$  series resistance is put at the input side of the amplifier as an amplitude divider. Figure 4.13 shows the circuit used for variable gain amplification of the two ROIC outputs. A similar configuration is used for the other two outputs of the ROIC.

Ar

Figure 4.13: The circuit used for variable gain amplification.

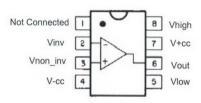

#### 4.3.3 Clamper

The amplified ROIC data is clamped to prevent the following stages of data flow from damage due to overvoltage. Clamping IC used here is CLC502 [17], which is an operational amplifier designed for low-gain applications, from National Semiconductor. This feature allows setting maximum positive and negative output voltage levels for the amplifier, thus allowing the CLC502 protect the following circuitry. The clamping voltages are selected to be  $\pm 2.5$ V. Figure 4.14 shows the pinout for CLC502.

Figure 4.14: Pinout of CLC502 [17].

Offset-added ROIC data changes polarity due to the adder circuit designed. Another polarity reversing operation must be done to have the original polarity. This is done by connecting the ROIC data to the inverting input of the clamping amplifier.

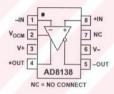

#### 4.3.4 Differential Driver

The next step is the AD8138 [18], low distortion differential ADC driver. A dramatic improvement in total harmonic distortion (THD) and spurious free dynamic range (SFDR) performance can be realized by operating the AD9220, the ADCs used on this board, in the differential mode. Therefore, to drive the ADCs differentially, AD8138 from Analog Devices is used. Figure 4.15 shows the pinout for AD8138.

Figure 4.15: Pinout of AD8138 [18].

## 4.3.5 Analog-to-Digital Conversion

A/D converter's analog input range, number of conversion bits, sampling frequency, conversion time, power dissipation and number of supplies were among the important considerations during the selection of the ADC. The ADC satisfying all our requirements is AD9220 [19], complete 12-bit 10 MSPS Monolithic A/D converter. The key specifications of the ADC can be summarized as;

Digitization 12 bits

Input Range 5V peak-to-peak,

Conversion rate 10 MSPS Input Capacitance 16 pF Input Resistance  $5 \text{ K}\Omega$

Power Supply Analog +5V and Digital +5V

Logic I/O +3 V or +5 V

Digital Outputs TTL/CMOS Outputs

Reference voltage preferred 2.5V

Effective Input Noise 0.09 LSBs rms

$Integral\ Nonlinearity \\ \qquad \pm 1.25\ LSB\ max$

Differential Nonlinearity ±0.75 LSB max

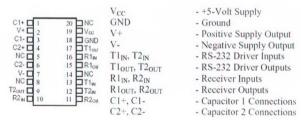

Figure 4.16 shows the AD9220 pinout and pin descriptions.

| CLK 1 DVDD                     | Pin<br>Number | Name   | Description                      |

|--------------------------------|---------------|--------|----------------------------------|

| LSB) BIT 12 2 27 DVSS          | 1             | CLK    | Clock Input Pin                  |

| BIT 11 3 26 AVDD               | 2             | BIT 12 | Least Significant Data Bit (LSB) |

| BIT 10 4                       | 3-12          | BIT N  | Data Output Bit                  |

| AD9ZZ11                        | 13            | BIT 1  | Most Significant Data Bit (MSB)  |

| BIT 9 5 AD9223/ 24 VINB        | 14            | OTR    | Out of Range                     |

| BIT 8 6 AD9220 23 VINA         | 15, 26        | AVDD   | +5 V Analog Supply               |

| BIT 7 TOP VIEW 22 CML          | 16, 25        | AVSS   | Analog Ground                    |

| BIT 6 8 (Not to Scale) 21 CAPT | 17            | SENSE  | Reference Select                 |

| BIT 5 9 20 CAPB                | 18            | VREF   | Reference I/O                    |

| BIT 4 10 19 REFCOM             | 19            | REFCOM | Reference Common                 |

|                                | 20            | CAPB   | Noise Reduction Pin              |

| BIT 3 11 18 VREF               | 21            | CAPT   | Noise Reduction Pin              |

| BIT 2 12 17 SENSE              | 22            | CML    | Common-Mode Level (Midsupply)    |

| ASB) BIT 1 13 16 AVSS          | 23            | VINA   | Analog Input Pin (+)             |

| OTR 14 IS AVDD                 | 24            | VINB   | Analog Input Pin (-)             |

|                                | 27            | DVSS   | Digital Ground                   |