## THE ANALYSIS OF A DYNAMIC VOLTAGE RESTORER BASED ON LOAD SIDE CONNECTED SHUNT CONVERTER TOPOLOGY

119041

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

**CAĞRI ACAR**

119041

T.C. YÜKSEKÖĞRETIM KURULU DOKÜMANTASYON MERKEZI

IN PARTIAL FULLFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

IN

THE DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

**DECEMBER 2002**

Approval of the Graduate School of Natural and Applied Sciences Prof. Dr. Tayfur Öztürk Director I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science. M. Demire Wo-Prof. Dr. Mübeccel Demirekler Head of Department This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science. Prof. Dr. Muammer Ermiş Supervisor **Examining Committee Members** Prof. Dr. Nevzat Özay Assoc. Prof. Dr. Işık Çadırcı Dr. Erbil Nalçacı M.Sc. Faruk Bilgin M.Enui

Prof. Dr. Muammer Ermiş

#### **ABSTRACT**

## THE ANALYSIS OF A DYNAMIC VOLTAGE RESTORER BASED ON LOAD SIDE CONNECTED SHUNT CONVERTER TOPOLOGY

#### ACAR, Çağrı

M.Sc., Department of Electrical and Electronics Engineering

Supervisor: Prof. Dr. Muammer Ermis

December 2002, 118 Pages

Complexity of the instruments used in the industry is increasing day by day due to the economic pressures to automate processes and improve efficiency, which results in the loads more sensitive to the voltage sags. Generally, voltage sags are caused by fault conditions on the system, therefore they may not be avoided completely. The Dynamic Voltage Restorer (DVR) is a series power electronics device which is designed to mitigate the voltage sags in the power systems. The primary advantage of the DVR is that, it is rated at a fraction of the total protected load, thereby yielding a very attractive cost versus benefit advantage.

The aim of this study is to describe the concept of the DVR and analyzing it with load side connected shunt converter topology which protects an 18MVA typical load. The successful operation of the DVR has been shown by simulations carried on PSCAD/EMTDC Software.

Keywords: Power Quality, Series Device, Dynamic Voltage Restorer, Voltage Sag

## YÜK TARAFINDAN ŞÖNT BAĞLI ÇEVİRİCİ TOPOLOJİSİ TABANLI BİR DİNAMİK GERİLİM İYİLEŞTİRİCİSİ ANALİZİ

#### ACAR, Çağrı

Yüksek Lisans, Elektrik-Elektronik Mühendisliği Bölümü Tez Yöneticisi: Prof. Dr. Muammer Ermiş

#### Aralık 2002, 118 sayfa

Gün ve gün ekonomik koşullar gereğince işlemlerin otomatize edilmesi ve verimliliğin arttırılması için endüstride gerilim düşümlerine daha duyarlı karmaşık cihazların kullanımı artmaktadır. Genellikle güç sistemlerinde meydana gelen arıza durumlarından kaynaklanan gerilim düşümlerinden tamamen kaçılması imkansızdır. Bu sebepten dolayı güç sistemlerindeki gerilim düşümlerini hafifletmek için, seri bağlantı yapılan bir güç elektroniği cihazı olan Dinamik Gerilim İyileştiricisi (DGİ) tasarlanmıştır. Cihazın temel avantajı, korunan toplam yükün bir kısmı değerinde olacağından dolayı getireceği eder ve kazanç avantajıdır.

Bu çalışmanın amacı, DGİ konusunu tanımlamak ve 18 MVA tipik bir yükü koruyan yük tarafından şönt bağlı çevirici topolojili GDİ'yi analiz etmektedir. Cihazın başarılı bir şekilde çalıştığı PSCAD/EMTDC yazılımında hazırlanan simulasyonlar ile gösterilmiştir.

Anahtar Kelimeler: Güç Kalitesi, Seri Cihaz, Dinamik Gerilim İyileştiricisi, Gerilim Düşümü

to my beloved wife, Feza

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere appreciation to Prof. Dr. Muammer Ermiş for his guidance and support in this research.

I would like to thank to all of the personnel of the Tubitak Bilten Power Electronics Group for their great help, friendship and the resources that are made available to complete this thesis.

I would like to thank to Aselsan A.Ş. for letting me to forward my precious time for this study.

Special thanks to my pet Pisigül for her great interest in Rashid's Book and some lost papers.

Finally I would like to thank my family and my beloved wife, Feza, for their great support and understanding.

## **TABLE OF CONTENTS**

| ABSTRACTiii                                            |

|--------------------------------------------------------|

| ÖZiv                                                   |

| ACKNOWLEDGEMENTSvi                                     |

| TABLE OF CONTENTSvii                                   |

| LIST OF TABLESx                                        |

| TABLEx                                                 |

| LIST OF FIGURESxi                                      |

| FIGURExi                                               |

| LIST OF ABBREVIATIONSxiv                               |

|                                                        |

| CHAPTER                                                |

|                                                        |

| 1. INTRODUCTION                                        |

| 2. POWER QUALITY                                       |

| 2.1 VOLTAGE SAGS                                       |

| 2.1.1 Causes of Voltage Sags                           |

| 2.1.2 Characterization of Voltage Sags                 |

| 2.1.3 Standards Associated with Voltage Sags           |

| 2.1.4 Mitigation Methods of Voltage Sags               |

| 3. OPERATION PRINCIPLES OF DYNAMIC VOLTAGE RESTORER 21 |

| 3.1 INTRODUCTION                                       |

| 3.2 BASIC PRINCIPLE OPERATION OF DVR22                 |

| 3.2.1 Steady State Operation of DVR                    |

| 3.2.1.1 Short Circuit Operation of DVR                 |

| 3.3 PROTECTION OF DVR                                  |

| 3.4 VOLTAGE INJECTION STRATEGY                         |

| 3.4.1      | Dynamic Voltage Restoration with Minimum Energy Injection | . 27 |

|------------|-----------------------------------------------------------|------|

| 3.5 CO     | NTROL OF DVR                                              | . 30 |

| 3.5.1      | Detection of Disturbances                                 | .31  |

| 3.5.2      | Phase Locked Loop                                         | . 31 |

| 3.5.3      | Extraction of dq components                               | . 32 |

| 3.5.4      | Dq components of the unsymmetrical set of voltages        | .36  |

| 3.5.5      | Voltage Controller                                        | 40   |

| 3.6 LOC    | CATION OF DVR                                             | 42   |

| 4. DVR TOP | OLOGIES AND COMPONENTS                                    | 44   |

| 4.1 TOP    | POLOGIES OF DVR                                           | 44   |

| 4.1.1      | DVR Topologies with No Energy Storage                     | 45   |

| 4.1.1.1    | Supply Side Connected Shunt Converter                     | 45   |

| 4.1.1.2    | Load Side Connected Shunt Converter                       | 46   |

| 4.1.2      | DVR Topologies with Energy Storage                        | 48   |

| 4.1.2.1    | 3                                                         |      |

| 4.1.2.2    | Constant DC-Link Voltage                                  | 49   |

| 4.1.3      | The Comparison of Topologies of DVR                       | 49   |

| 4.2 INJE   | ECTION TRANSFORMER OF DVR                                 | 50   |

| 4.2.1      | Primary Voltage Rating                                    |      |

| 4.2.2      | Primary Side Current Rating                               | 52   |

| 4.2.3      | The MVA Rating                                            | 52   |

| 4.2.4      | Turns-Ratio Selection                                     | 53   |

| 4.2.5      | Short-Circuit Impedance Considerations                    | 53   |

| 4.3 INV    | ERTER OF THE DVR                                          | 55   |

| 4.4 FILT   | TERING SCHEMES IN THE DVR                                 | 56   |

| 4.4.1      | Line Side DVR Filter                                      | 57   |

| 4.4.2      | Inverter Side DVR Filter                                  | 60   |

| 4.5 Harm   | nonic Voltage Drops on the DVR                            | 61   |

| 5. SYSTEM  | DESCRIPTION AND DESIGN                                    | 65   |

| 5.1 FIEI   | LD APPLICATIONS OF THE DVR                                | 65   |

| 5.2 THE    | APPLIED LOAD SIDE SHUNT CONNECTED CONVERTER               |      |

| TODOLOGY   | N7                                                        |      |

| 5.2.1      | The Power Circuit                                         | 66  |

|------------|-----------------------------------------------------------|-----|

| 5.2.2      | The DVR                                                   | 67  |

| 5.2.2.1    | Topology                                                  | 67  |

| 5.2.2.2    | Injection Transformer                                     | 68  |

| 5.2.2.3    | DC-Link                                                   | 69  |

| 5.2.2.4    | Attenuation of Harmonics                                  | 70  |

| 5.2.2.5    | Inverter and the Switching of the Semiconductors          | 70  |

| 5.2.2.6    | Control Issues                                            | 71  |

| 5.2.2.7    | Simulated DVR                                             | 72  |

| 5.2.2.8    | Summary of Design Procedure                               | 73  |

| 5.2.2.9    | Simulation Parameters                                     | 76  |

| 6. SIMULAT | ION RESULTS                                               | 77  |

| 6.1 EFF    | ECTS OF DVR PARAMETERS                                    | 78  |

| 6.1.1      | The switching Frequency of the Inverter                   | 78  |

| 6.1.2      | Effect of Leakage Inductance of the Injection Transformer | 80  |

| 6.1.3      | DC-link Capacitor Value                                   | 82  |

| 6.1.4      | Harmonic Voltage Drop on DVR                              | 84  |

| 6.2 DVR    | SIMULATIONS                                               | 85  |

|            | SIONS                                                     |     |

| REFERENCES | 5                                                         | 109 |

| APPENDIX   |                                                           |     |

| A.1 PSCAD  | SIMULATIONS                                               | 112 |

| A.2 MATLA  | B PROGRAMS                                                | 116 |

| A.2.1 MA   | ATLAB Program for Frequency Spectrum                      | 116 |

| A 2 2 M A  | TI AB Program for THD Calculation                         | 117 |

## LIST OF TABLES

## **TABLE**

| 2.1 Transformer Secondary Voltages with a SLGF on the Primary Side                | . 12 |

|-----------------------------------------------------------------------------------|------|

| 2.2 Sample voltage sag data [25]                                                  | . 16 |

| 2.3 Power Acceptability Curves.                                                   | . 19 |

| 5.1 The Simulation Parameters                                                     | .76  |

| 6.1 Switching Frequency Simulations                                               | . 78 |

| 6.2 Effects of switching frequency with constant filter capacitor value           | . 79 |

| 6.3 Effects of switching frequency with variable filter capacitor value           | . 79 |

| 6.4 Filter capacitor results at 1.5 kHz switching frequency                       | . 80 |

| 6.5 Filter capacitor results at 1 kHz switching frequency                         | . 80 |

| 6.6 Effects of Leakage inductance of the injection transformer                    | . 81 |

| 6.7 Effects of leakage inductance of the injection transformer at 3 kHz switching |      |

| frequency                                                                         | . 82 |

| 6.8 The effect of DC-link capacitor value                                         | . 83 |

| 6.9 The effect of DC-link capacitor value at 1 kHz switching frequency            | . 83 |

| 6.10 The effect of sag depth on the DC-link voltage magnitude                     | . 84 |

## **LIST OF FIGURES**

#### **FIGURE**

| 1.1 The origin of voltage sags                                        | 2  |

|-----------------------------------------------------------------------|----|

| 1.2 The operating principle of the DVR                                | 3  |

| 2.1 Typical distribution system with protection devices               | 9  |

| 2.2 Typical voltage sag due to starting of a large load               | 10 |

| 2.3 Typical voltage sag due to the energizing of a transformer        | 10 |

| 2.4 Typical voltage sag due an unbalanced fault                       | 11 |

| 2.5 Voltage sag at the Wye/Wye connected transformer secondary        | 13 |

| 2.6 Voltage sag at the Delta/Wye connected transformer secondary      | 14 |

| 2.7 Voltage sag at the Delta/Delta connected transformer secondary    | 14 |

| 2.8 Change in the phase of the non-faulted wrt single-phase sag level | 15 |

| 2.9 The CBEMA Curve                                                   | 17 |

| 2.10 The ITIC Curve                                                   |    |

| 2.11 Mitigation Methods of Voltage Sags                               | 20 |

| 3.1 Schematic of a DVR                                                | 22 |

| 3.2 Short Circuit Operation of DVR with DVR Semiconductors            | 24 |

| 3.3 Short circuit operation with Thyristors                           | 24 |

| 3.4 Voltage sag accompanied by phase displacement                     | 27 |

| 3.5 Phase-advance energy-saving voltage restoration                   | 29 |

| 3.6 Phase difference event at the end of the sag                      | 30 |

| 3.7 Phase Locked Loop output                                          | 32 |

| 3.8 αβ transformation of voltages                                     | 33 |

| 3.9 αβ transformed voltages                                           | 34 |

| 3.10 dq transformation of voltages                                    | 35 |

| 3.11 dq transformed voltages                                          | 36 |

|                                                                       |    |

| 3.12 dq transformation of unbalanced voltages                                       | 37   |

|-------------------------------------------------------------------------------------|------|

| 3.13 dq transformations in the negative and positive sequence SRF                   | 38   |

| 3.14 Extracted dq transformations in the negative and positive sequence SRF         | 39   |

| 3.15 The Control Block Diagram                                                      | 41   |

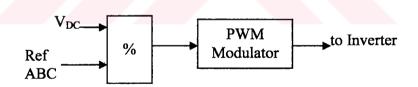

| 3.16 The generation of PWM signals                                                  | 41   |

| 3.17 The Location of DVR                                                            | 43   |

| 4.1 DVR with no energy storage and supply side connected converter                  | 45   |

| 4.2 DVR with no energy storage and load side connected converter                    | 47   |

| 4.3 DVR with energy storage and variable DC-Link                                    | 48   |

| 4.4 DVR with Constant DC-Link Voltage                                               | 49   |

| 4.5 Equivalent circuit of DVR with inverter side filter                             | 53   |

| 4.6 Further simplification of inverter side filter                                  | 54   |

| 4.7 Equivalent circuit with line side filter                                        | 54   |

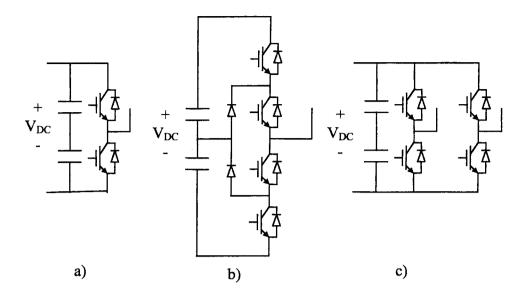

| 4.8 Basic inverter types for a DVR a) two-level half bridge                         |      |

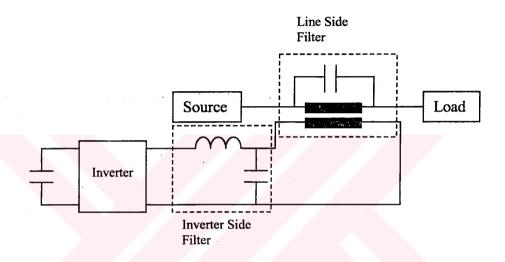

| 4.9 DVR Filtering Schemes                                                           |      |

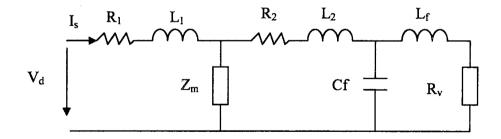

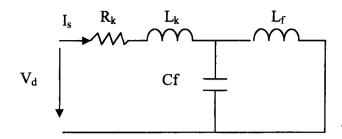

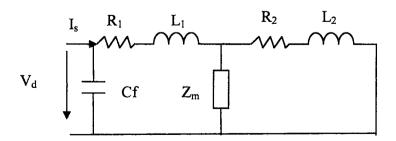

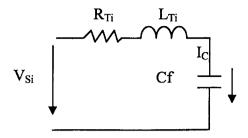

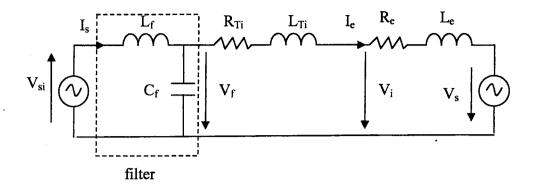

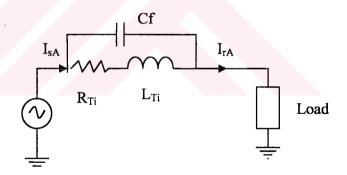

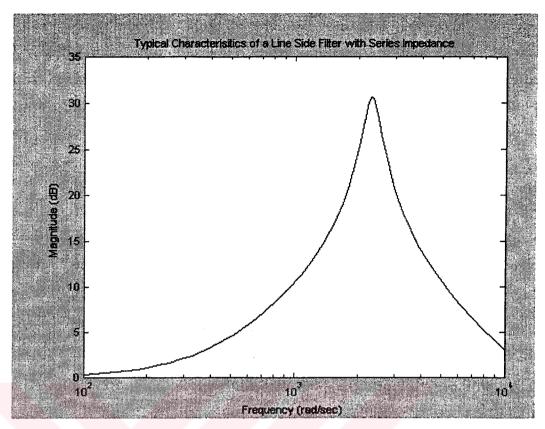

| 4.10 Equivalent circuit for line side filter                                        | . 58 |

| 4.11 Simplified circuit for line-side filter current calculations                   | . 60 |

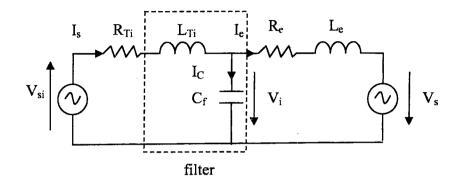

| 4.12 Inverter side filter circuit                                                   | . 61 |

| 4.13 The illustration of DVR with line side connected filter circuit during steady- |      |

| state                                                                               | . 62 |

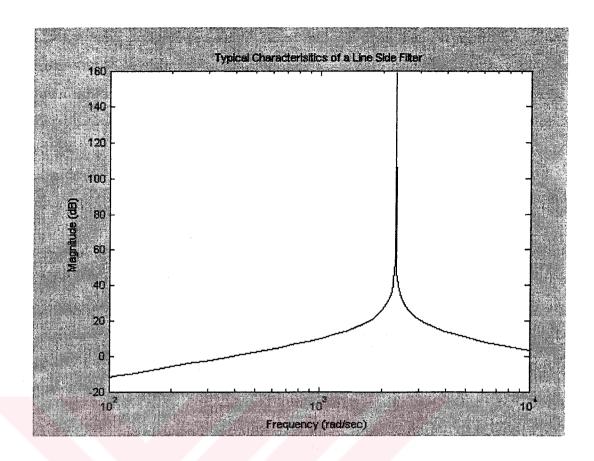

| 4.14 The frequency response of the DVR with line side connected filter with zero    |      |

| series resistance of injection transformer                                          | . 63 |

| 4.15 The frequency response of the DVR with line side connected filter with series  | s    |

| resistance of injection transformer                                                 | . 64 |

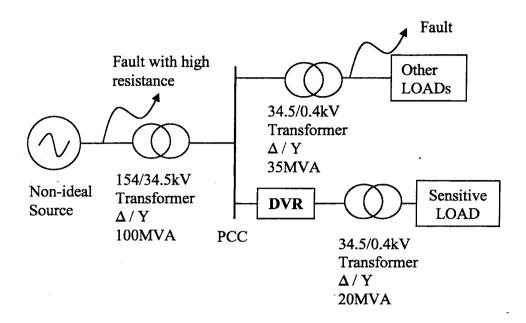

| 5.1 The Power Circuit Simulated                                                     | . 67 |

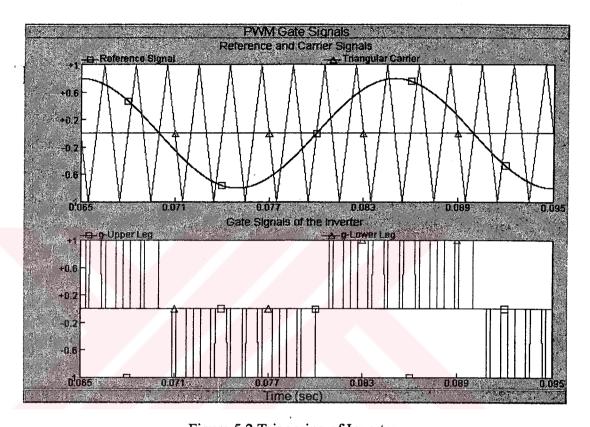

| 5.2 Triggering of Inverter                                                          | . 72 |

| 5.3 The Simulated DVR illustrated in one phase                                      | . 73 |

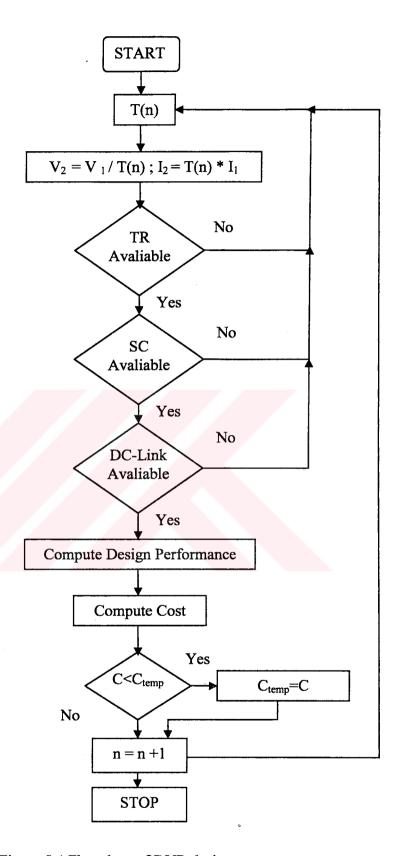

| 5.4 Flowchart of DVR design process                                                 | . 75 |

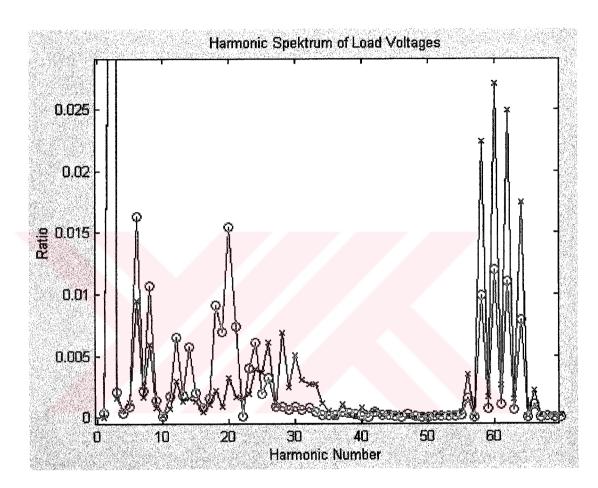

| 6.1 Harmonic Spectrum of Load Voltages with different tuned filters                 | . 85 |

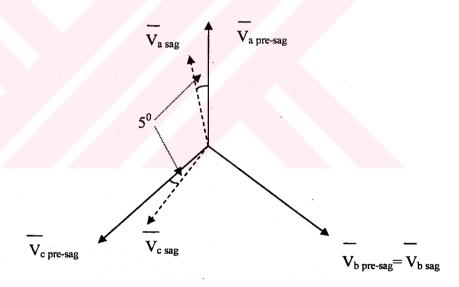

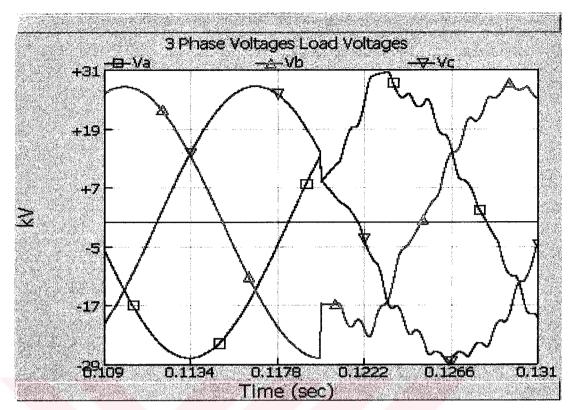

| 6.2 Unbalance voltage sag simulated                                                 | . 86 |

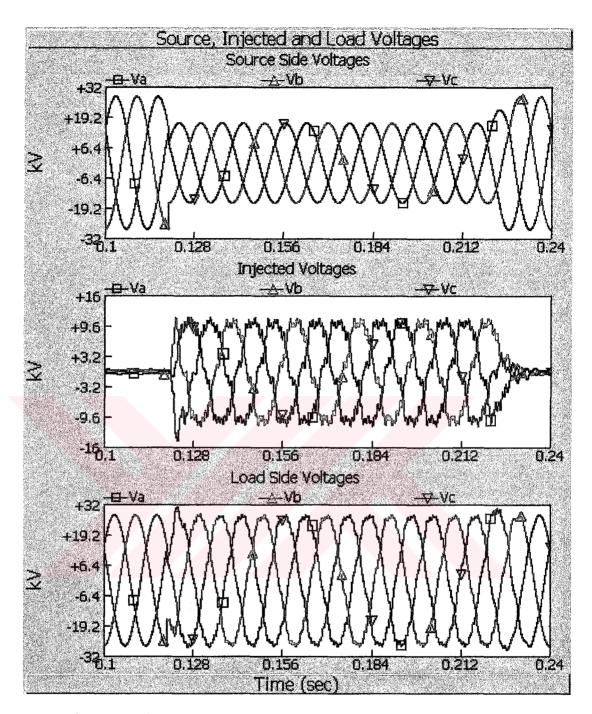

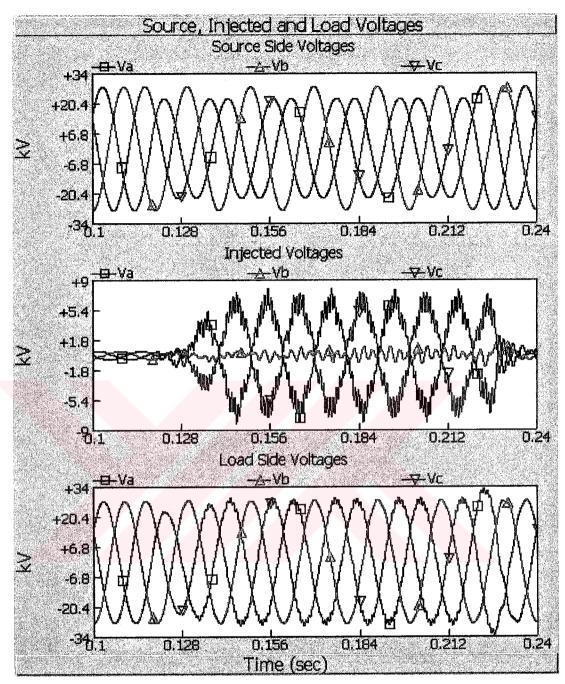

| 6.3 The Source, Injected and Restored Voltages (40% sag depth)                      | . 87 |

| 6.4 The Source, Injected and Restored Voltages for unbalanced voltage sag           | . 88 |

| 6.5 The dynamic response of the DVR                                        | 89  |

|----------------------------------------------------------------------------|-----|

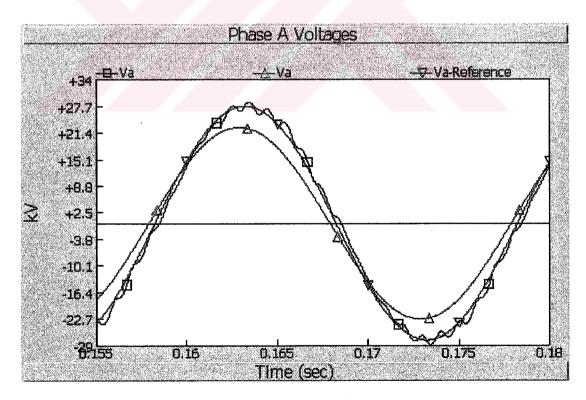

| 6.6 The Source, Injected and Restored Voltages of Phase A with phase-shift | 89  |

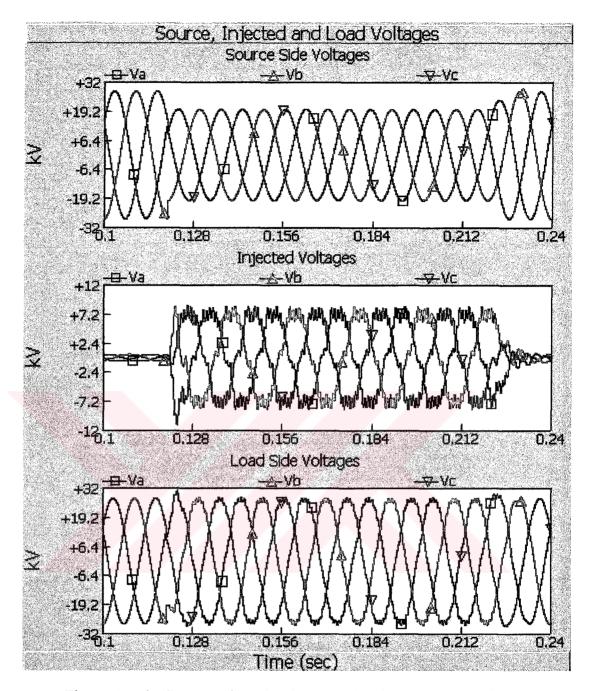

| 6.7 The Source, Injected and Restored Voltages (30% sag depth)             | 91  |

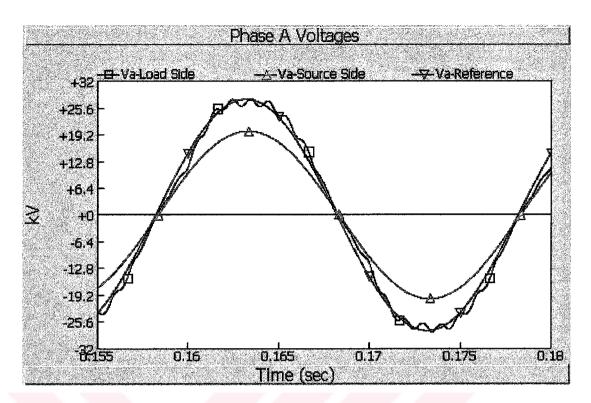

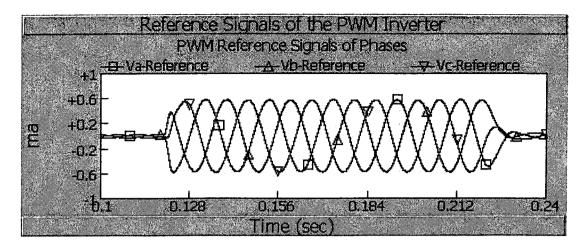

| 6.8 The Source, Injected and Restored Voltages of Phase A                  | 92  |

| 6.9 The THD of Load Voltages                                               | 92  |

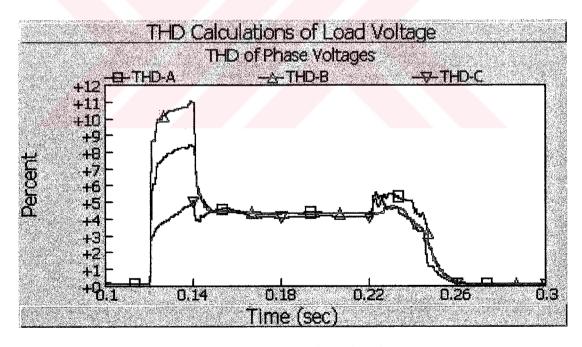

| 6.10 The transformed dq voltages of the source side                        | 93  |

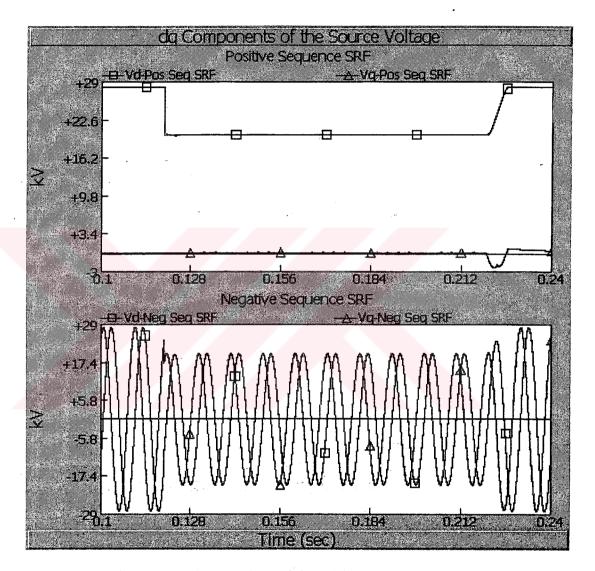

| 6.11 The reference signals calculated for the PWM Inverter                 | 94  |

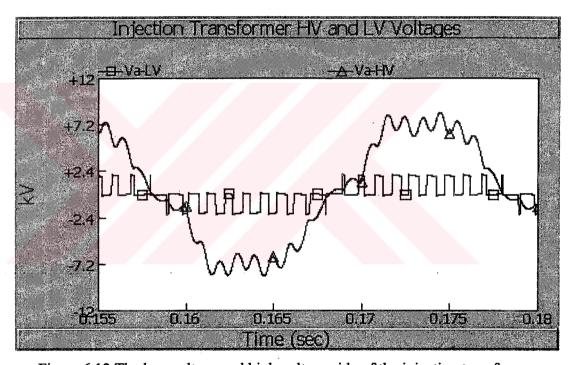

| 6.12 The low voltage and high voltage side of the injection transformer    | 94  |

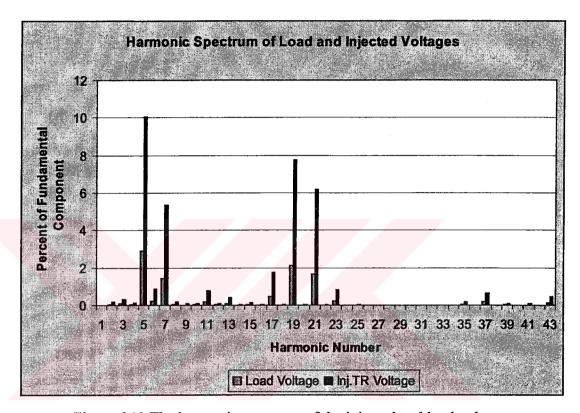

| 6.13 The harmonic spectrum of the injected and load voltages               | 95  |

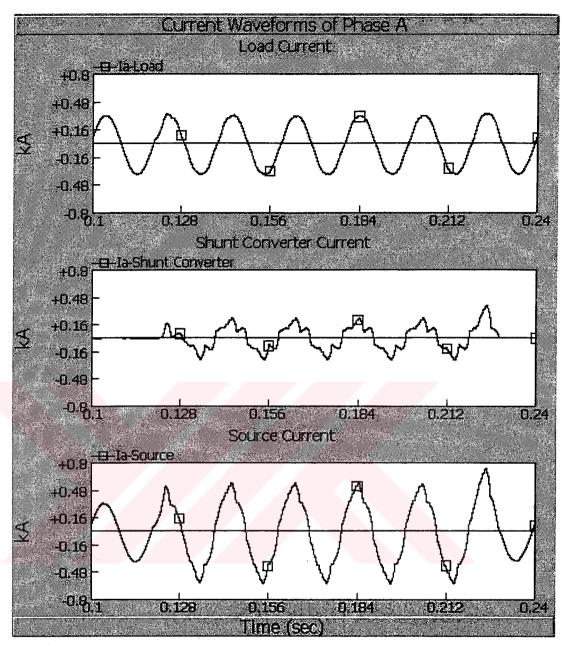

| 6.14 The Load, Source and Shunt Converter Currents                         | 96  |

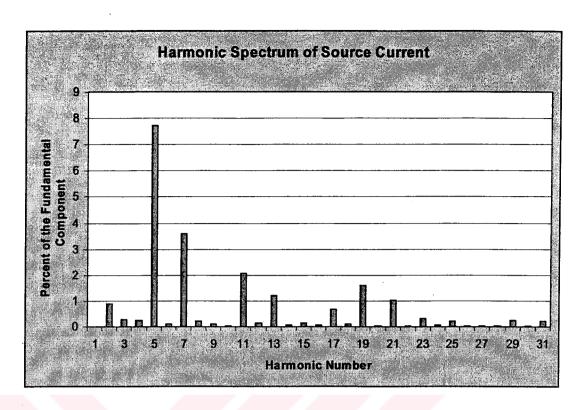

| 6.15 The harmonic spectrum of source current                               | 97  |

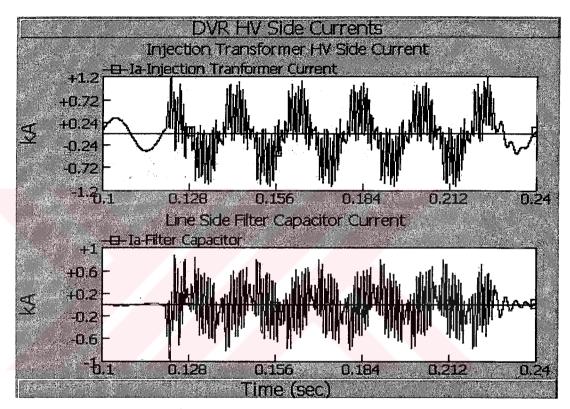

| 6.16 The Filter and Injection Transformer Primary Current                  | 98  |

| 6.17 Detailed view of Figure 6.16                                          | 99  |

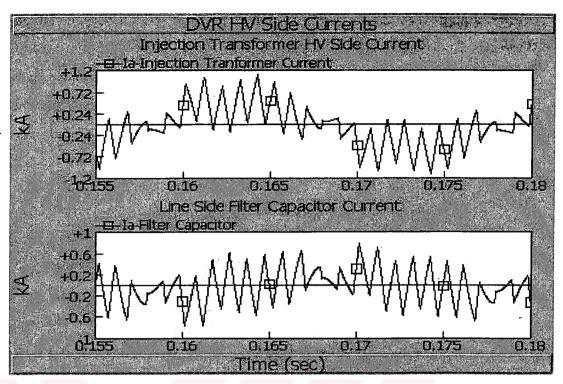

| 6.18 Harmonic spectrum of filter capacitor current                         |     |

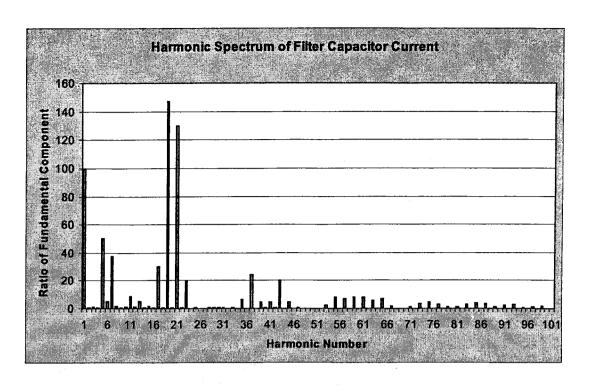

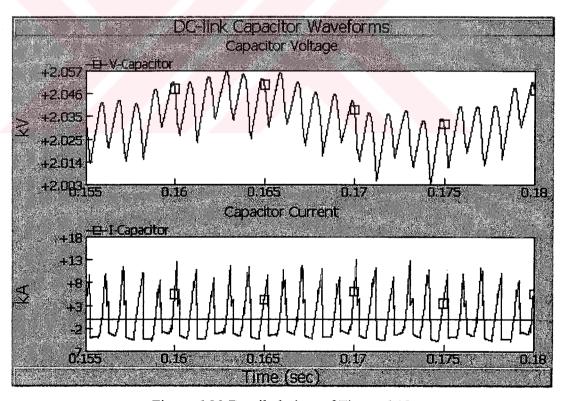

| 6.19 The DC-link capacitor waveforms                                       |     |

| 6.20 Detailed view of Figure 6.19                                          |     |

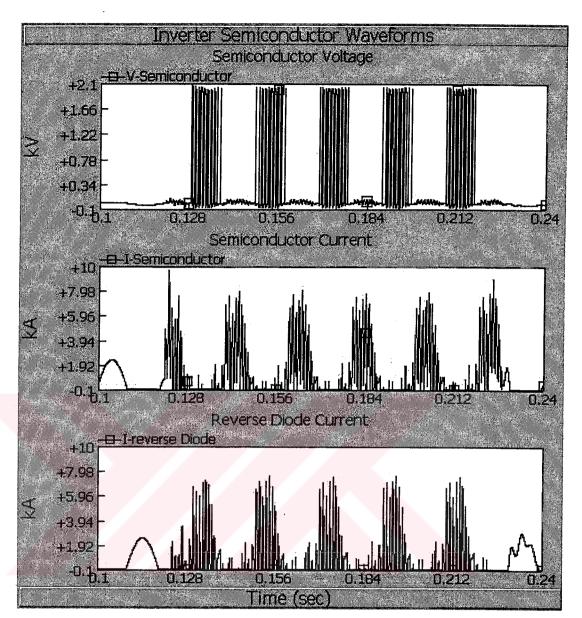

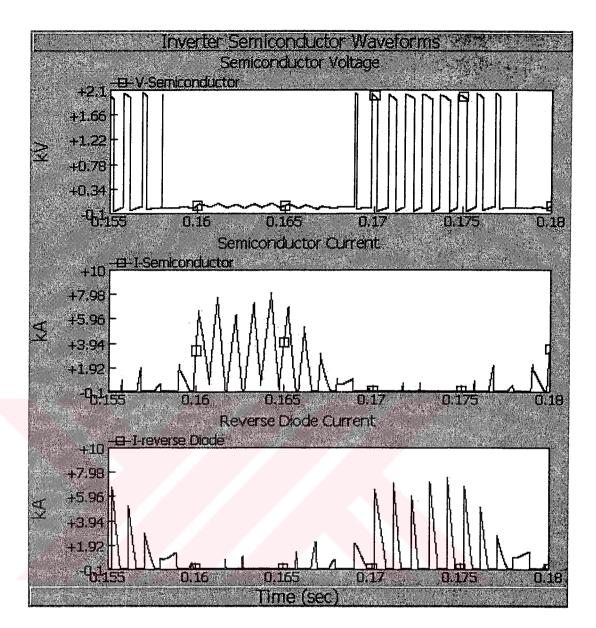

| 6.21 Semiconductor waveforms                                               |     |

| 6.22 Detailed view of Figure 6.21                                          |     |

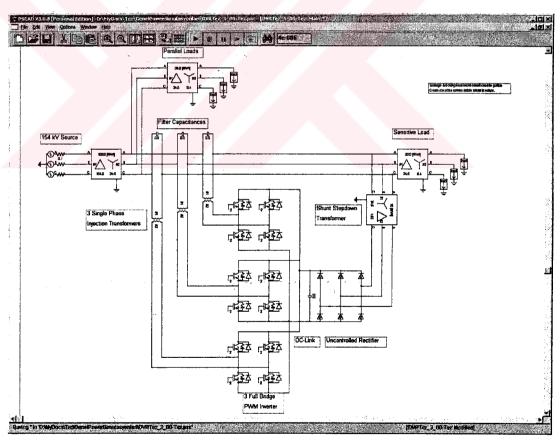

| A.1 PSCAD DVR simulation power circuit                                     | 112 |

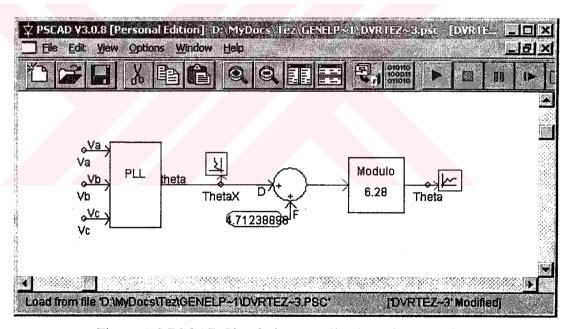

| A.2 PSCAD Simulation: Application of PLL Object                            | 113 |

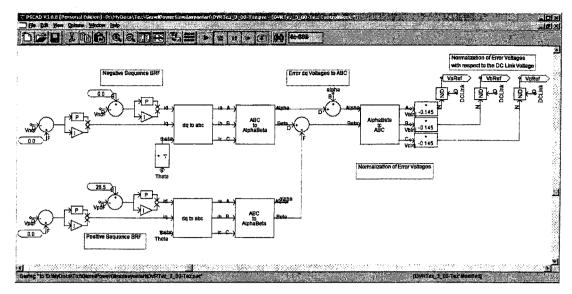

| A.3 PSCAD Simulation: Generation of Reference Signals                      | 114 |

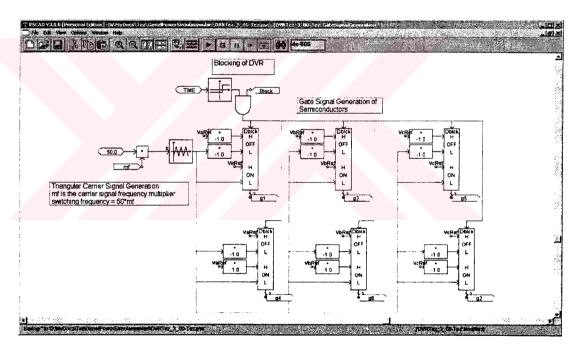

| A.4 PSCAD Simulation: Generation of PWM Gate Signals                       | 114 |

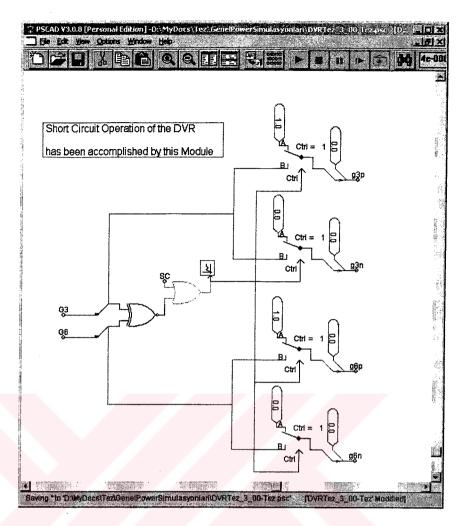

| A.5 PSCAD Simulation: SCO of DVR                                           | 115 |

#### LIST OF ABBREVIATIONS

DVR : Dynamic Voltage Restorer

IGCT: Integrated Gate Commutated Thyristor

PCC: Point of Common Coupling

PLC: Programmable Logic Controller

PLL: Phase Locked Loop

PWM: Pulse Width Modulation

rms : Root Mean Square

SLGF: Single phase line-to-ground fault

SCO: Short Circuit Operation

SRF : Synchronous Reference Frame

THD: Total Harmonic Distortion

VSI : Voltage Source Inverter

#### **CHAPTER 1**

#### INTRODUCTION

Introduction of sensitive loads to the power systems has changed the boundary conditions in the electrical supply industry towards the quality of the electrical supply. Users are deeply interested in the quality of the electrical supply while the utilities are concentrating on utilizing the existing transmission systems more efficiently.

Users need constant sine-wave shape, constant frequency and symmetrical voltage with a constant rms value to ensure the continuity of their production at their site. Among the disturbances that may be observed at a utility grid, the transient power supply interruptions and voltage sags are considered to be the most severe since many of the loads are susceptible and sensitive to temporary changes in the magnitude and phase of the power supply. Voltage depressions in the order of a few milliseconds may bring an entire production line to a standstill, and may cause a considerable amount of economic damage, furthermore the equipments may face the danger of breakdown.

A voltage sag can be loosely defined as a short-duration reduction in voltage magnitude generally caused by a fault somewhere in the system. Voltage sags can be characterized by magnitude and duration, and for many cases they are followed by an unbalance in the phase angle. Despite their short duration, with the increasing complexity of the instruments, voltage sags may effect various equipments seriously. The devices that are most sensitive to the sags are process-control equipment, computers and adjustable-speed drives [1].

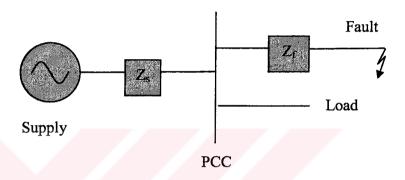

The primary reason for the voltage sags is a short-duration increase in current generally contributed by motor starting, transformer energizing and faults (earth faults and short-circuit faults). In Figure 1.1, a typical voltage sag at the Point of Common Coupling (PCC) due to a fault in the parallel line is illustrated. The loads may be affected from the voltage sags even if the fault occurs kilometers away from the area of interest. In such cases, the magnitude of the remaining voltage at PCC will be a function of fault and source impedances ( $Z_s$  and  $Z_t$ ) [2][3][4].

Figure 1.1 The origin of voltage sags

Even if the power system is designed for maximum reliability, disturbances, because of atmospheric influences and non-predictable component failures, may not be predicted and prevented. Therefore only additional measures taken in the power system or at the user's end can protect the critical loads from disturbances.

The most commonly used method is to install additional equipment at the system-load or system-customer interface which will guarantee a high-quality supply of electrical energy to the critical loads in cases of power system disturbances. UPS, the motor-generator set, the ferroresonance transformer and induction voltage regulator are conventional devices which solve the voltage sag problem. The static-transfer switch and Dynamic Voltage Restorer (DVR) are the latest examples of the equipments that may be installed to the system in order to increase the quality of the power system.

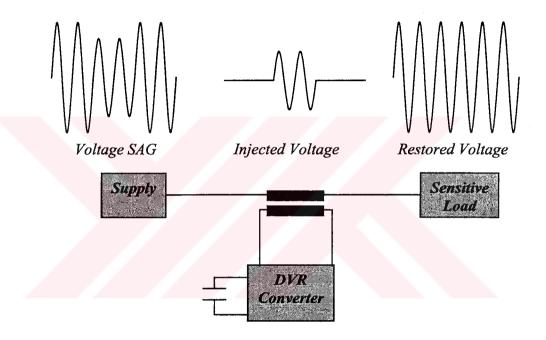

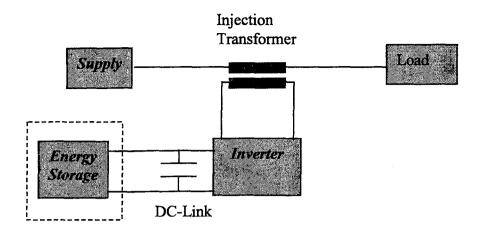

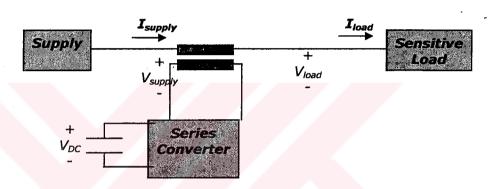

In order to protect industries from the voltage sags, a state-of-the-art device, the DVR which is introduced in the recent years constitutes a good solution for compensating the missing voltage during a voltage sag event. The very basic idea of the DVR is to inject a dynamically controlled voltage generated by a forced-commutated converter in series to the bus by means of an injection transformer which is connected in the distribution level (Figure 1.2). Such an implementation will eliminate most of the voltage sags and minimize the risk of load tripping even if at very deep sags, therefore the plant where the device is connected will continue production process and the economic damage caused by voltage sags will be avoided.

Figure 1.2 The operating principle of the DVR

For most of the time, the DVR will have "nothing to do" except monitoring the bus voltage. Therefore during the stand-by it should be ensured that the load is not disturbed by the DVR. The voltage drop caused by the injection transformer should be kept as low as possible and if this voltage drop degrades the load voltage requirement, the DVR may inject a small voltage in order to compensate the voltage drop it creates. The voltage drop on the DVR can be decreased by selecting an injection transformer with a relatively low leakage induction but the cost of the DVR will increase significantly.

When a disturbance is sensed in the bus voltage, the equivalent missing voltage will be generated by the inverter and injected to the line via the series injection transformer. Note that the DVR will not be designed to compensate total power supply interruptions, therefore it will be able to mitigate a certain amount of voltage sag and in case of deeper voltage sags or total power supply interruptions the DVR will not be treated.

The necessary energy for injection to the system by the DVR during the mitigation event may be supplied from either an energy storage device or directly from the grid that the DVR is connected. Operating with an energy storage device limits the performance of DVR for long duration sags and implementation costs will be rather high. Therefore topologies with shunt connected converter from the line itself or auxiliary supply have been proposed in the literature. Whereever the source of the energy of the DVR is fed, there exist strategies to decrease the energy absorbed in order to reduce the energy storage size. These strategies are called the "dynamic voltage restoration with minimum energy injection" which are based on advancing the phase of the injected voltage in order to utilize the source power more efficiently.

The DVR should sense the voltage magnitude and phase disturbance on the line quickly and generate the control signal for the pulse width modulated voltage sourced converters. In order to damp the harmonics generated by the PWM converter, a filtering scheme either to the line side or to the inverter side should be applied. The filtering scheme should ensure the remaining voltage at the supply side plus the injected voltage be within certain THD limits determined by the standards.

In this study, power quality problems will be discussed, necessary issues for DVR design will be covered and a DVR with the load side connected converter topology for a typical power system will be analyzed depending on the simulations carried on PSCAD/EMTDC software package.

The organization of the thesis is as follows:

➤ In Chapter 2, the most severe power quality problem, the voltage sag, is analyzed in depth. The voltage sags are characterized and the solutions are discussed.

- ➤ In Chapter 3, the operating principles of the DVR are introduced and the control issues are given.

- ➤ In Chapter 4, the topologies and components of the DVR are explained and analyzed in detail. The injection transformer, inverter and the filtering schemes are discussed.

- ➤ In Chapter 5, the system is described and the DVR design constraints are analyzed.

- > In Chapter 6, the simulation results are given.

- > In Chapter 7, the final conclusions on this study are made and the further work on this area is proposed.

#### **CHAPTER 2**

#### **POWER QUALITY**

Electric power quality can be defined as a measure of how well electric power service can be utilized by customers. From another point of view power quality is "having a bus voltage that closely resembles a sinusoidal waveform of required magnitude". IEC (1000-2-2/4) and CELENEC (EN 50160) define power quality as a physical characteristic of electrical supply provided under normal operating conditions which do not disturb or disrupt the customer's process.

Today, the expectations for power quality have increased. The companies do not want to suffer from poor quality power that feeds their plants. There are four major reasons for the growing requirements of power quality. First, the equipments are becoming more sensitive to power quality variations with the introduction of microprocessor-based controls and power electronics. Second, in order to reduce losses, adjustable-speed motor drives and shunt capacitors for power factor correction has been introduced for the overall system efficiency. Third, the end-users are more aware of power quality issues. Finally, since many things are interconnected via a network, the failure of any component has much more important consequences. All reasons listed above have just one aim, increased productivity for utility customers, such as more faster, productive and efficient machinery. The economics involved in solving the power quality problems is not always to eliminate the power quality variations but making a particular piece of sensitive equipment less sensitive to power quality variations.

Technically speaking, the following criteria quantify the power quality [6]:

- Constant sine-wave shape; the harmonics in the waveform should be kept in certain limits.

- > Constant frequency; unchanged nominal value

- > Symmetrical three-phase AC power system; the three phase voltages are with at phases shifted by 120°.

- > Constant rms value; the nominal power system voltage value unchanged over time.

- Fixed voltage; the power system voltage is unaffected by load variations.

- > Reliability; the energy required is available at all times.

All of the listed above does have numerical upper and lower limits and during the operation, these values should be kept between limits determined by standards if the power quality level is considered to be high. Among these quantities "constant rms value" requirement is the most important and severe one. In case of rms value lower than the specific value a voltage sag event occurs vice versa a voltage swell event occurs. While the voltage swells can be prevented by surge diverters, the voltage sags require special attention. In this chapter the general information on the voltage sags which is required for deciding the DVR design parameters will be given.

#### 2.1 VOLTAGE SAGS

A voltage sag is a momentary (i.e. 5-30 cycles) decrease in the rms voltage magnitude, usually caused by a remote fault somewhere else on the power system or within a customer facility. It is important to discriminate the interruptions and voltage sags. The former occurs when a protective device actually interrupts the circuit serving a particular customer when there is a fault on that circuit. But the latter occurs during the period of a fault on that circuit and there still remains a certain amount of voltage on the line. Faults on parallel feeders will cause voltage sags but will not result in interruptions.

IEC 1000-4-11 defines the voltage sags as "A sudden reduction of the voltage at a point in the electrical system, followed by voltage recovery after a short period of time, from half a cycle to a few seconds" while the interruptions are defined as

"The disappearance of the supply voltage for a period of time typically not exceeding one minute. Interruptions can be considered as voltage sags with 100% amplitude."

As the complexity of the electronics equipment used in the industrial plants increases, the equipments started to be more sensitive to the voltage sags. Today process controllers, Programmable Logic Controllers (PLC), adjustable speed drives, robotics, etc. are commonly used equipments which are very sensitive to voltage sags in the industrial plants. The frequency of the voltage sags is rather common than the interruptions which breeds the necessity of taking special measures to prevent unwanted voltage sag results.

#### 2.1.1 Causes of Voltage Sags

Voltage sags are typically caused by fault conditions. Motor starting and transformer energizing can also result in under voltages, but these are typically longer in duration than 30 cycles and the associated voltage magnitudes are not as low.

Faults resulting in voltage sags can occur within the plant or on the utility system. The duration of the sags are determined by the fault-clearing time of the protective devices, typically a fuse or a plant feeder breaker for a plant and a branch fuse or a substation breaker for the utility system.

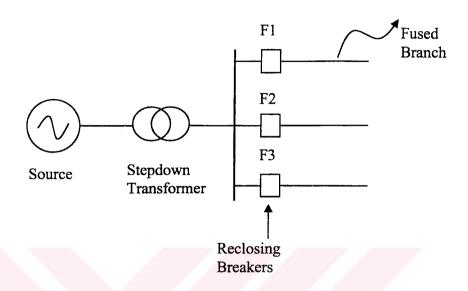

Utility system faults can occur on the distribution or transmission system. In Figure 2.1 a typical distribution system with a number of feeders supplied from a common bus is illustrated. A fault on feeder F1 will cause an interruption that will affect the customers on that feeder. However, the customer on the parallel feeders (F2 and F3) will experience a voltage sag while the fault is present on the system. Due to the reclosing breakers, the customers on the parallel feeders may experience more than one voltage sag lasting for durations ranging from a couple of cycles to more than ten cycles.

The consequences of the faults on the transmission system are more severe since such a fault can affect more customers fed from the system. Even the customers hundred kilometers away from the fault source still experience voltage sags.

The majority of the voltage sags are single phase line-to-ground (SLGF) faults that often result from weather conditions such as lightning, wind or ice.

Contamination of insulators, animal contacts and accidents during construction and transportation also cause faults. Three-phase faults are respectively are less common with respect to the single phase faults but the consequences will be more severe and harmful.

Figure 2.1 Typical distribution system with protection devices

Among the causes of the faults, lightning is the most common fault reason that effets the overhead transmission and distribution lines. Lightning can cause a fault by directly striking a phase conductor or by striking a ground object such as a shield wire or a tower. Although introduction of various protection measures and devices to the power system reduces the severity of the faults, there still happen events that will cause voltage sags.

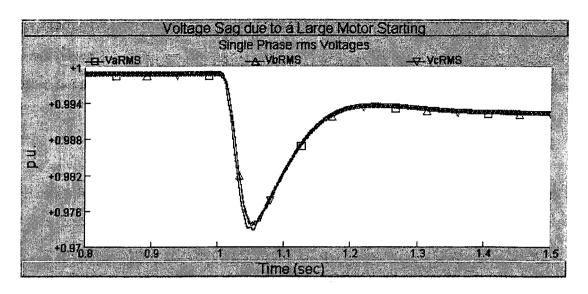

In Figure 2.2, the rms values of the phase voltages during a large motor starting have been illustrated. The motor has started at 1 sec. This type of voltage sag can be described as a rather small voltage drop followed by gradual recovery. The large motors are all-three phase balanced loads which results in balanced voltage drops for all phases.

Figure 2.2 Typical voltage sag due to starting of a large load

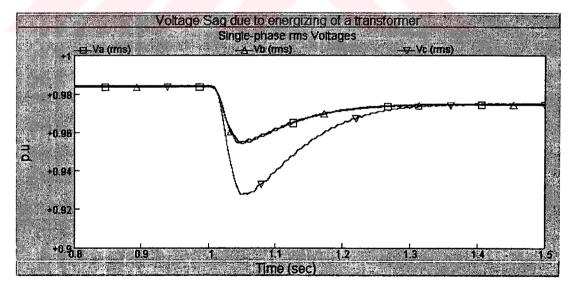

A typical illustration of voltage sags due to energizing of transformers is shown in Figure 2.3. The transformer has been energized at 0.5 sec. The waveform characteristic is a sudden drop followed by a slow recovery. From the figure, the voltage sag level for all three phases is different. This event is due to the energizing of a large transformer where the inrush currents are different in three phases.

Figure 2.3 Typical voltage sag due to the energizing of a transformer

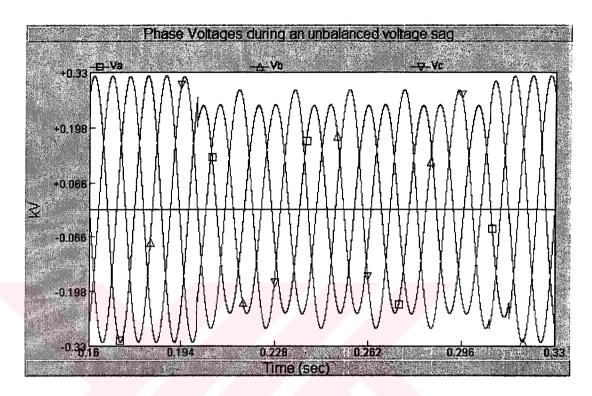

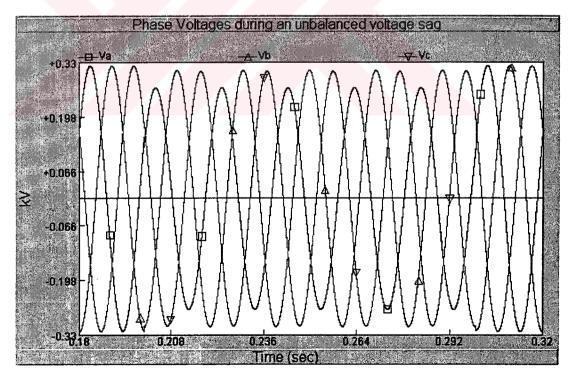

The majority of the voltage sags are caused by the fault conditions on the system. Figure 2.4 illustrates an unbalanced voltage sag caused by a fault in the parallel load.

Figure 2.4 Typical voltage sag due an unbalanced fault

#### 2.1.2 Characterization of Voltage Sags

The majority of the voltage sags due to faults are the single phase line-to-ground (SLGF) faults. Although SLGF can be prevented by proper isolation of the neutral, there still be faults that will cause voltage sags. The voltage on the faulted phase will go down to zero at the fault location. But the voltage level on the parallel feeders will depend on the distance of the fault which will be determined by the overall network impedances (Figure 1.1). The voltage sag level at the PCC can be calculated by:

$$\alpha = \frac{Z_f}{Z_f + Z_s} \tag{2.1}$$

where  $Z_f$  is the fault impedance and  $Z_s$  is the source equivalent impedance.  $\alpha$  will vary between 0 and 1 and usually for the industrial power distribution, it will be very close to unity.

Another parameter that will determine the fault voltage level is the transformer connections as shown in Table 2.1 [3]. The voltage sag characteristics are modified by the connection type of the transformer. The delta connected transformers will decrease the severity of the voltage sag but the un-faulted phases will also experience partial voltage sags.

Table 2.1 Transformer Secondary Voltages with a SLGF on the Primary Side

| Winding Connection | Phase to Phase Voltages |      |     | Phase to Neutral Voltages |      |      |

|--------------------|-------------------------|------|-----|---------------------------|------|------|

|                    | AB                      | BC   | CA  | A                         | В    | C    |

| Yn/yn, Yn/y        | 58%                     | 100% | 58% | 0%                        | 100% | 100% |

| Y/y, Y/yn          | 58%                     | 100% | 58% | 33%                       | 88%  | 88%  |

| Dyn, Dy            | 33%                     | 88%  | 88% | 58%                       | 58%  | 100% |

Table 2.1 also shows that with respect to the type of transformer windings, some phases are not affected by the voltage sags (Yy connected) or all of the phases are partially affected (Delta/Delta). Note that the transformers with delta-connected windings act as a filter for the zero-sequence components by inducing symmetry and reducing the consequences of a fault. The phase voltage values of the non-faulted phases decrease slightly, so that the degree of asymmetry also decreases in comparison with the voltage system on the primary. For example in case of a voltage sag of 0.5 p.u. at phase A, filtering of the zero phase-sequence system on the secondary leads to a phase A voltage of approximately 66%. The voltages in phases not affected by the fault decrease in value about 8% and the phase displacement will about 8 degrees (Figure 2.7).

The duration of the voltage sags will be determined by the reclosing operation of the contactors and the reclosing breakers. This operation will require about 5 or 6 cycles (100 - 120 ms) for 50Hz to operate during which time a voltage sag occurs.

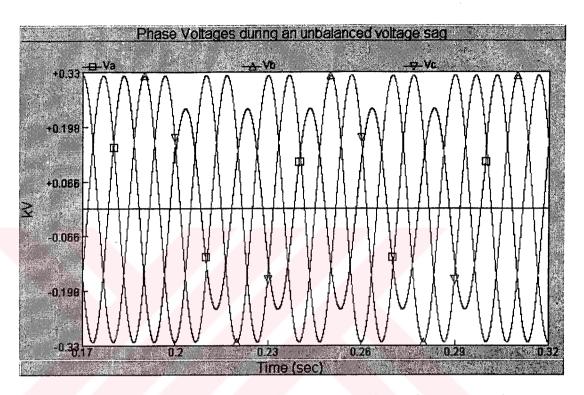

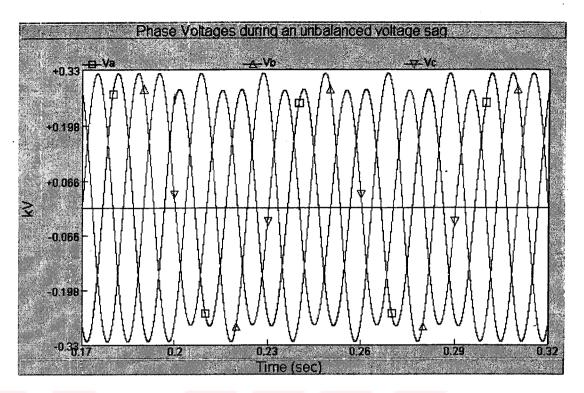

Figure 2.5, Figure 2.6 and Figure 2.7 illustrate voltage levels at the secondary of the transformer caused by a SLGF on the primary for different connection types.

Figure 2.5 Voltage sag at the Wye/Wye connected transformer secondary

Figure 2.6 Voltage sag at the Delta/Wye connected transformer secondary

Figure 2.7 Voltage sag at the Delta/Delta connected transformer secondary

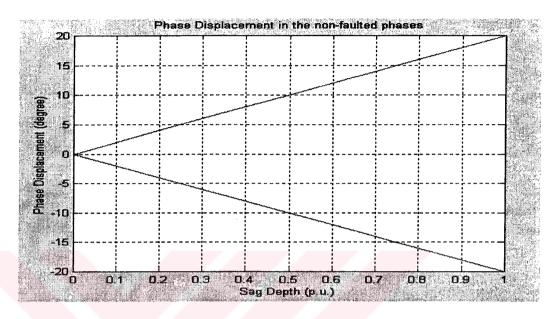

Even with a single-phase voltage reduction of 0.5 p.u., phase displacements about 10% may take place in the three-phase AC system which are not affected by the fault [8]. The voltage phase displacement in the non-faulted phases with respect to the single-phase fault level is shown in Figure 2.8.

Figure 2.8 Change in the phase of the non-faulted wrt single-phase sag level

In Table 2.2, sample data taken from 222 distribution feeders in United States between 1993 and 1994 is given [25]. The table expresses the voltage sag occurrences for specific remaining voltage magnitude intervals versus the sag duration intervals (bin: between interval). For example there existed 6.8 sags per site per year with magnitudes between 70% and 80% and duration less than 200 ms. From the table it is clear that majority of the voltage sags (75% to 80%) are shorter than 200 msec and the sag magnitudes are below 50%.

Table 2.2 Sample voltage sag data [25]

| Magnitude | Time in Bin seconds (sec) |           |           |           |       |

|-----------|---------------------------|-----------|-----------|-----------|-------|

| Bin       | 0.0 < 0.2                 | 0.2 < 0.4 | 0.4 < 0.6 | 0.6 < 0.8 | >=0.8 |

| >80%-90%  | 53.1                      | 4.8       | 1.9       | 0.7       | 2.9   |

| >70%-80%  | 14.1                      | 1.7       | 0.2       | 0.2       | 0.4   |

| >60%-70%  | 6.8                       | 0.9       | 0.1       | 0.1       | 0.2   |

| >50%-60%  | 3.5                       | 0.9       | 0.2       | 0.0       | 0.3   |

| >40%-50%  | 1.4                       | 0.4       | 0.2       | 0.0       | 0.3   |

| >30%-40%  | 1.5                       | 0.1       | 0.1       | 0.0       | 0.3   |

| >20%-30%  | 1.2                       | 0.3       | 0.2       | 0.2       | 0.4   |

| >10%-20%  | 1.0                       | 0.1       | 0.0       | 0.0       | 0.5   |

| 0%-10%    | 1.9                       | 0.7       | 0.7       | 0.2       | 6.4   |

#### 2.1.3 Standards Associated with Voltage Sags

During a voltage sag, the single phase devices may not be affected by the sag as shown in Table 2.1. But the three-phase devices and some of the single-phase devices will be affected. The sensitivity of the various equipments to the voltage sags is determined by the standards. But these equipments may be produced with different standards and may have significantly different sensitivity to voltage sags.

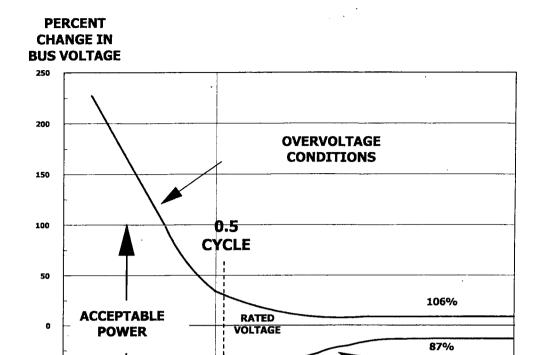

One of the most important equipment sensitive to voltage sags is the computers. The document associated with the voltage sags for the computers is the CBEMA curve [3] which was developed by the Computer Business Manufacturers Association. This applies primarily to data processing equipment.

-50

0.0001

0.001

8.33 ms

Figure 2.9 The CBEMA Curve

0.1

TIME IN SECONDS

UNDERVOLTAGE CONDITIONS

1000

The CBEMA limits suggest a standard sensitivity to voltage sags for the data processing equipments but the equipment in a plant may have different characteristics to the voltage sags. For example the motor contactors and electromechanical relays, adjustable speed drives and programmable logic controllers' sensitivity level will be different.

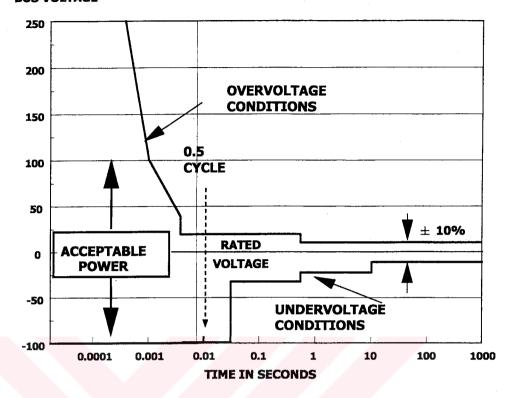

## PERCENT CHANGE IN BUS VOLTAGE

Figure 2.10 The ITIC Curve

Another standard is the Information Technology Industry Council (ITIC) curve (Figure 2.10). The main difference between the CBEMA curve and the ITIC curve is that the latter curve describes an acceptable operating region in steps rather than as a smooth curve. Instrumentation to check compliance with the ITIC curve is more easily designed.

Finally, Table 2.3 shows the standards associated with the voltage sags, the power acceptability curves.

Table 2.3 Power Acceptability Curves

| Curve                                    | Year | Application                                     | Source                                    |

|------------------------------------------|------|-------------------------------------------------|-------------------------------------------|

| FIPS power acceptability curve           | 1978 | Automatic data<br>processing (ADP)<br>equipment | U.S. federal government                   |

| CBEMA curve                              | 1978 | Computer business equipment                     | Computer Business Equipment Manufacturers |

| ITIC curve                               | 1996 | Information<br>technology<br>equipment          | Information Technology Industry Council   |

| Failure rate curves for industrial loads | 1972 | Industrial loads                                | IEEE Standard<br>493                      |

| AC line voltage tolerances               | 1974 | Mainframe computers                             | IEEE Standard<br>446                      |

| IEEE Emerald<br>Book                     | 1992 | Sensitive electronic equipment                  | IEEE Standard<br>1100                     |

### 2.1.4 Mitigation Methods of Voltage Sags

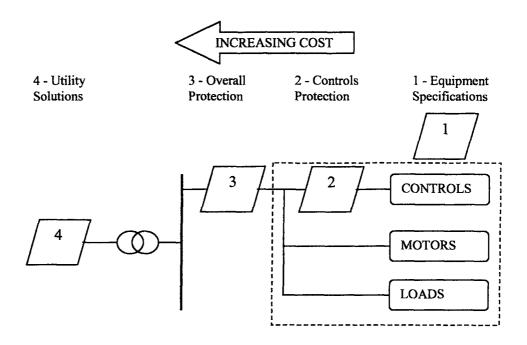

Several measures may be taken by the utility, end user and equipment manufacturer to reduce the number and severity of voltage sags. We may reduce the number of events, improve our power system, mitigate the sag at the interface between system and load or finally improve our end-use equipment. Figure 2.11 illustrates the voltage sag solution alternatives and their relative costs [1][6].

Figure 2.11 Mitigation Methods of Voltage Sags

Reducing the number of events is not an easy task and the cost can be very high since voltage sags at a location may be due to the faults kilometers away. Improving the power system does not reduce the number of events but makes them less severe. Again this may require large investments. Improving the end-use equipment seems to be the less costly but the manufacturers of the end-use equipments try to avoid this issue. Finally, the customers are left with one option: installing mitigation equipments.

Up to now, many methods have been proposed for the mitigation of voltage sags. UPS, motor-generator sets, ferroresonant transformers and induction voltage regulators are some commonly applied conventional methods that solve the problem partially. The state-of-the-art solution of the voltage sag problem is the application of the Dynamic Voltage Restorer (DVR) to compensate the missing voltages on the line.

#### **CHAPTER 3**

#### OPERATION PRINCIPLES OF DYNAMIC VOLTAGE RESTORER

#### 3.1 INTRODUCTION

Since the voltage sags are considered to be one of the most severe disturbances among the power quality criteria, in order to mitigate the voltage sags in the power system, a series connected Custom Power device which consists of a voltage sourced inverter and a dc-link storage, the Dynamic Voltage Restorer, has been developed and integrated to the systems as a power quality device.

The primary function of the DVR is to eliminate or reduce voltage sags seen by sensitive large loads. Furthermore the device may be used in order to reduce phase unbalance seen by load and compensate voltage harmonics in the supply voltage. A DVR is schematically drawn in Figure 3.1 (Note that the energy storage of the DVR shown is optional and by application of different DVR topologies, the *Energy Storage* approach will vary).

Figure 3.1 Schematic of a DVR

With the aid of the DVR, the industrial plants that come to a standstill during voltage sags will not suffer from the loss of money and time. Beyond the benefits of the DVR, the main drawbacks are the standby losses and equipment costs. Because of the large investments required for design and implementation of a DVR, a survey on the customers attitude show that customers suffering from voltage sag are tend to prefer a utility-provided solution with the cost included to their power bill as an alternative to the purchase, installation and operation of their own on-site equipment for the mitigation of power line disturbances. Therefore the DVR has been developed as part of a utility Custom Power device to provide a solution [30].

#### 3.2 BASIC PRINCIPLE OPERATION OF DVR

The very basic idea of the DVR is to inject a dynamically controlled voltage generated by a forced-commutated converter in series to the bus by means of an injection transformer. Such an implementation will eliminate most of the sags and minimize the risk of load tripping at very deep sags.

From the practical point of view, for the DVR to perform proper operation, following criteria should be handled with care:

> During the normal utility system conditions, the DVR should not degrade the power system parameters.

- > Voltage restoration for both short and long term voltage sags should be handled with proper design. During the restoration, the dc-link voltage should be maintained at certain level to ensure proper voltage injection. A trade-off between choosing a large capacitor bank or inserting a high rated rectifier circuit should be considered.

- > The DVR must lock into the supply phase and must detect supply voltage distortions accurately.

- > A PWM modulation scheme will be applied to synthesize the injected voltage, thus the switching frequency harmonics must be prevented from entering into the utility and customer system. For this purpose a filtering scheme should be introduced.

# 3.2.1 Steady State Operation of DVR

Under normal utility system steady-state conditions, the DVR may either inject only a small voltage to compensate for the voltage drop on the series reactance of the injection transformers and losses or go into a short circuit operation. If the load is not disturbed by the voltage drop on the DVR, the short circuit operation may be applied during the steady-state operation. Injection of a small voltage during steady-state may be necessary for weak utility distribution circuits without introducing and additional voltage drop for the voltage-drop-limited circuit.

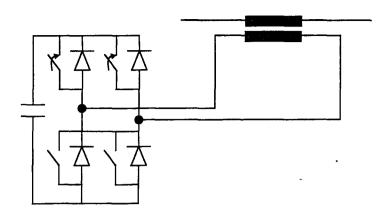

#### 3.2.1.1 Short Circuit Operation of DVR

If the voltage drop caused by the DVR does not affect the load requirements, the secondary of the injection transformer may be short circuited during steady-state operation in two ways [8]. One method is triggering the individual converter legs such as to establish a short-circuit path for the transformer low voltage leg. Note that no switching of semiconductors occurs in this type of operation. Therefore, only the comparatively low conduction losses of the semiconductors in this current loop contribute to losses. The switching of semiconductors may be seen in Figure 3.2 during short circuit operation (SCO).

Figure 3.2 Short Circuit Operation of DVR with DVR Semiconductors

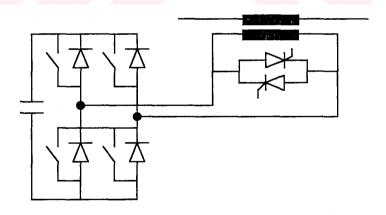

Another method to short circuit the transformer secondary is achieved by introducing a solid state bypass switch between the inverter and the transformer secondary. Furthermore since the Dynamic Voltage Restorer is connected in series, it will see the full load current as well as any currents due to downstream faults. In case of any temporary abnormal condition (i.e. load current overloads, etc.) the DVR will go into bypass until the load current returns normal conditions. Thyristors may be applied for the short-circuit device in order to protect the semiconductors to be thermally destroyed in case a downstream fault. Figure 3.3 illustrates the location of the short circuit device.

Figure 3.3 Short circuit operation with Thyristors

#### 3.3 PROTECTION OF DVR

Another important point that should be considered during the implementation and production process of the DVR is the protection measures. The primary concern will be the increment in the current on the load side. The reason for this increment in the current magnitude may either be a downstream fault due to a short circuit on the load or drawing of large inrush currents such as connection of large AC loads and transformers. This may cause the DVR to go into a current limit to prevent damage to its power semiconductors. During the over current period, the control system of the DVR should remove itself from the line if the application of current limiting techniques such as output voltage reduction do not work. The DVR should have clever bypass schemes so as not to create additional disturbances onto the system which will affect the load. Solid-state bypass schemes as stated in (3.2.1.1) for the over current periods which exceed the DVR rating and/or electromechanical bypass systems for the long duration over current overloads, fault currents and for the isolation of DVR during maintenance may be applied. Note that the electromechanical bypass switches will be able to close typically at 4 to 6 cycles therefore a protection with thyristors should also be applied.

The transformer saturation is another problem during the recovery of a voltage sag. If the transformer saturates due to a lack of flux "headroom", the magnetizing currents will become very large such that they may damage the power semiconductors [9]. Again the control of the system should detect this situation and take the proper measures in order to avoid this problem. If the transformer is sized to handle two times the normal steady-state flux requirement at maximum rms injection voltage without saturation, this problem will be naturally solved but the cost of the injection transformer will surely increase.

#### 3.4 VOLTAGE INJECTION STRATEGY

The aim of the DVR is not the restoration of full supply voltage but partial boosting of supply voltage during the mitigation of voltage sags. This results in a voltage injection limit on the DVR and the injection transformer. It is clear that

maximum single-phase voltage sag depth to be corrected will determine the primaryside voltage rating of the injection transformer.

Basically there exist two voltage injection strategies. First method is voltage injection in phase with the supply side voltage that is the mitigated voltage will be inphase with the source side sag voltage. In this method the magnitude of the injected voltage will be minimized but the there will exist a phase-shift between the source side sag voltage and the pre-sag voltage in case of unbalanced voltage sags.

In this type of injection strategy, let the rated rms voltage of the primary feeder be  $V_p$  (per phase) and let the maximum voltage sag that our DVR will compensate is D p.u. Then a very rough estimation of required voltage injection magnitude can be calculated as:

$$V_i = DV_n \tag{3.1}$$

Where  $V_i$  is the required rms magnitude of injection voltage, D is the maximum per unit voltage to be injected and  $V_s$  is the rms phase voltage of the feeder.

As stated before, during the voltage sags, the amplitude and the phase-angle of the supply voltage varies according to the characteristics of the power system and the fault conditions. The voltage amplitude reduction can be accompanied by a significant phase-angle shift, such as illustrated in Figure 3.4. Thus another method which can be explained as compensating the difference between the sag and the presag voltages may be applied. This strategy will be valid for both balanced and unbalanced voltage sags, and the restored voltage will be the same as the pre-sag voltage. Surely this method will require a voltage injection magnitude greater than the first method and normally a greater energy storage.

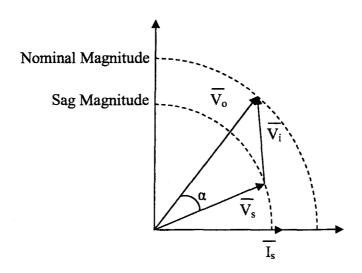

In Figure 3.4, the phase-shift on the source voltage  $(V_s)$  is denoted as  $\alpha$  during a voltage sag. The load voltage  $(V_o)$  is restored to the pre-sag value by properly determined injected voltage  $(V_i)$

Figure 3.4 Voltage sag accompanied by phase displacement

In case of application of this voltage injection strategy, the steady-state voltage magnitude requirement will be:

$$V_{i} = \sqrt{V_{o}^{2} + (1 - D)^{2} V_{p}^{2} - 2V_{o}(1 - D)V_{p} \cos \alpha}$$

(3.2)

Where  $\alpha$  is the largest possible phase-angle difference between restored voltage  $V_o$  and source-side voltage  $V_s$ .

Besides these two methods, recently another method for decreasing the energy storage capacity has been proposed called the dynamic voltage restoration with minimum energy injection.

# 3.4.1 Dynamic Voltage Restoration with Minimum Energy Injection

One of the recent topics studied on the DVR is on the energy storage optimization concept. The aim of the studies is optimizing the real power spent by the DVR thus minimizing the energy storage capacity. Mitigation of voltage sags by injection of appropriate series voltage component will surely require a certain amount of real and reactive power supplied by the DVR. However this amount of required power will be determined by the type of voltage disturbance and the voltage injection scheme.

The idea behind the dynamic voltage restoration with minimum energy injection concept is modifying the voltage injection scheme with respect to the conventional injection schemes so as to reduce the real power injected to the system by advancing the phase of the injected voltage [10][11]. In other words, with this method we decrease the power angle between the source voltage and the current thus forcing the power flow uphill from source to load. Since there is a phase difference between the input and output voltages, the magnitude of the injected voltage will surely be larger than the in-phase injection method. But the cost of this minimization will be in increased magnitude of injected voltage, phase-shift experienced in load voltage and the complexity of the control system. The phase-shift that will be experienced by the load voltage may result in voltage waveform discontinuity, inaccurate voltage zero-crossing and load power swing.

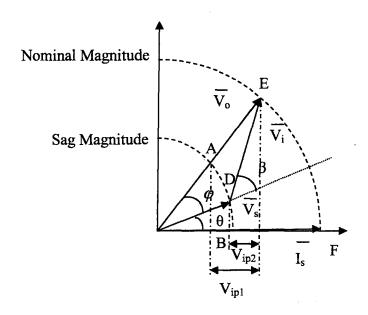

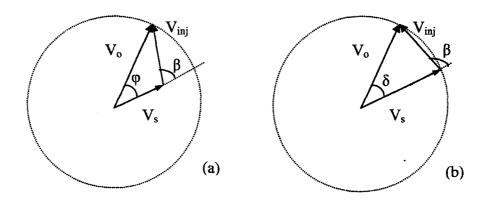

If our concern is only keeping the magnitude of the load voltage in some limits, minimum energy injection goal may be reached. To illustrate the idea, as shown in Figure 3.5, the locus of the load side voltage can lie anywhere on a circle with radius  $V_0$ . However the source voltage and the voltage injection limit of the DVR will determine the minimum energy injection operating point. The operating point in Figure 3.5 is denoted by D. The load voltage  $(V_0)$  is restored by a phase-advance angle of  $\beta$  with respect to source voltage  $(V_s)$  during a voltage sag by properly determined injected voltage  $(V_i)$ . At this case the angle between the source voltage and the load voltage becomes  $\varphi$ .

If  $V_S < V_0 cos \varphi$  and there is no injection limit, the operating point can lie anywhere on the arc AB. When  $\theta = 0$ , the injected real power  $V_{ip2}I$  approaches minimum. If  $V_S > V_0 cos \varphi$  then the operating point may be on the arc EF and operating point F is the zero power injection point. From Figure 3.5, in order to decrease  $\theta$ , we should increase the magnitude of the injected voltage.

Figure 3.5 Phase-advance energy-saving voltage restoration

In this type of injection strategy, the magnitude of the injection voltage is the primary limiting factor for the economic considerations. Normally the higher the magnitude of the injected voltage the higher the rating of the DVR thus a trade-off between the rating of the DVR and minimum energy injection can be solved by a partial boosting strategy. The required magnitude of injected voltage can be calculated with:

$$V_{i} = \sqrt{V_{o}^{2} + (1 - D)^{2} V_{p}^{2} - 2V_{o}(1 - D) V_{p} \cos \varphi}$$

(3.3)

This equation is similar with (3.2). The phase-shift angle  $\alpha$  is switched with the phase-advanced angle  $\varphi$  which is greater than  $\alpha$ .

Another point to be paid attention occurs at the end of the voltage sag where the phase-advance method may result in a sudden phase difference as shown in Figure 3.6. In order to overcome this problem a progressive phase advance method should be implemented.

Figure 3.6 Phase difference event at the end of the sag

This method will start to work only after a time a voltage sag occurs since all of the methods for calculating the parameters of the supply voltage (magnitude and phase) requires a time delay. Fast Fourier Transformer (FFT) and Discrete Fourier Transform (DFT) algorithms have been applied to many important areas of waveform analysis of power systems but suffer from certain limitations such as number of samples per cycle to be an integer number and stationary input signal. These limitations can be overcome by Kalman filtering approach [11].

#### 3.5 CONTROL OF DVR

The control strategy of the DVR should be designed to detect of the voltage sags in the supply voltage and apply the necessary missing voltage as soon as possible. In order to minimize the response time and maximize the dynamic performance, generally a direct feed-forward-type control architecture is applied.

Rms value calculation of the voltages can be considered for the first approach for the detection of the voltage sags. But the calculation of rms voltage will require at least one half period at the line frequency and this delay degrades the performance during the transients. Besides the transient operation of the DVR, the phase-shift associated with the voltage sags should also be considered while mitigating the voltage sags and this method is again very weak to this kind of problem.

Another important point is the presence of an inverter-side filtering scheme which will require special attention since this kind of filtering scheme will introduce a voltage drop and additional phase shift in the injected voltage.

#### 3.5.1 Detection of Disturbances

In order to detect the voltage disturbance on the source side, three- to two-phase transformation is applied. This type of transformation will increase the fault detection time of the DVR and also will be valid for the unbalanced voltages. The two-phase values obtained will be separated into positive and negative sequence components and then will be compared with the proper reference values. For this type of operation the phase-angle information of the source voltages should be calculated.

Note that the zero sequence components can be ignored since the DVR will be located to the three wire distribution system and the zero sequence components will be filtered in the delta connected step-down transformers.

# 3.5.2 Phase Locked Loop

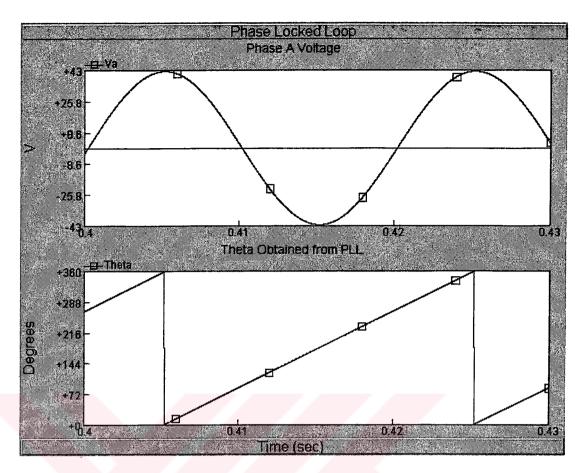

The detection of the phase-angle of the source voltage is critical for the DVR. The method should not be affected from the unbalanced voltages, flicker, harmonics and frequency variations. Considering these requirements, a Phase Locked Loop (PLL) algorithm for the detection of phase-angle should be implemented. The quality of the PLL operation will have an important impact on the control performance of the system.

The output of the PLL is as shown in Figure 3.7. The output of PLL is 0° when phase A is in the positive peak. The PLL tracks the phase of the source voltage and from the figure, reaches 360° when phase A reaches the second peak. The output of the PLL will be used while extracting the dq components of the three-phase source voltages. A method in [12] is proposed for the implementation of the PLL.

Figure 3.7 Phase Locked Loop output

# 3.5.3 Extraction of dq components

In the control of the DVR, the accurate phase voltages' magnitudes and phases should be obtained. One method to obtain this information is transforming the phase voltages to the synchronous rotating frames in order to obtain DC values for the required information. This method is called the instantaneous symmetrical components method.

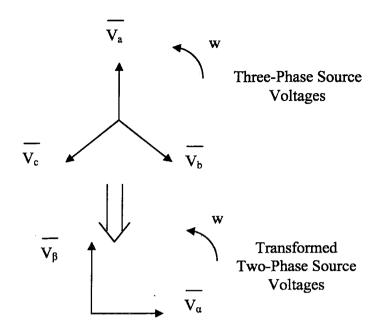

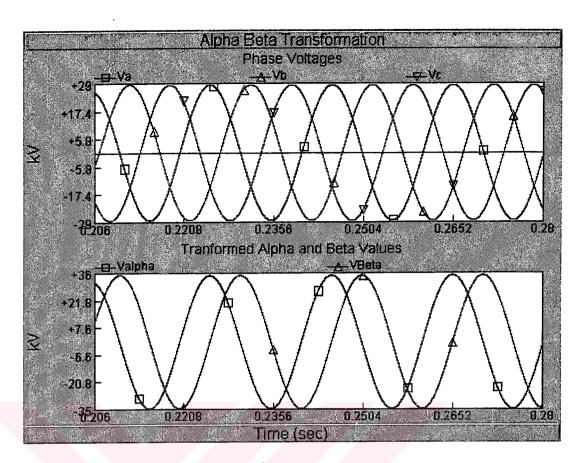

In the first step, the three-phase source side voltages are transformed into two-phase  $\alpha\beta$  voltages which are fixed with the source side voltage vector  $V_s$  as shown in Figure 3.8. With this transformation, the three-phase voltages are shown in two-axis coordinate system.

Figure 3.8 αβ transformation of voltages

If the define the source side voltage vector  $V_s$  with the instantaneous source side phase voltages  $V_{sA}$ ,  $V_{sB}$  and  $V_{sC}$  as:

$$\overline{V_S} = V_{s\alpha} + jV_{s\beta} = \sqrt{\frac{2}{3}}(V_{sA} + \alpha V_{sB} + \alpha^2 V_{sC})$$

(3.4)

Where  $\alpha = e^{j2\pi/3}$ ,  $\alpha^2 = e^{-j2\pi/3}$  then the three-phase to two-phase  $\alpha\beta$  transformation matrix can be written as:

$$\begin{bmatrix} V_{s0} \\ V_{s\alpha} \\ V_{s\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1/\sqrt{2} & 1/\sqrt{2} & 1/\sqrt{2} \\ 1 & -1/2 & -1/2 \\ 0 & -1/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} V_{sA} \\ V_{sB} \\ V_{sC} \end{bmatrix}$$

(3.5)

Figure 3.9 αβ transformed voltages

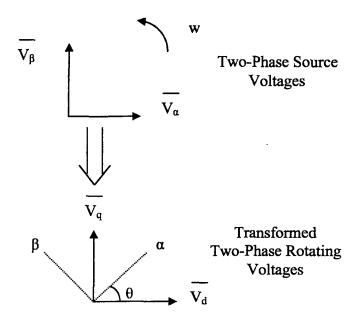

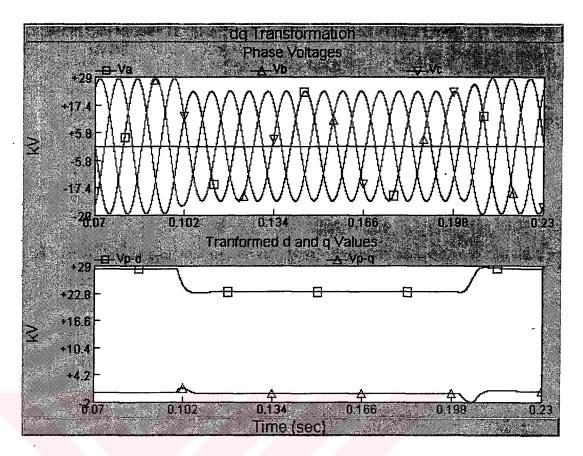

In the second step, the two phase values are transformed into rotating dq-coordinate system (Figure 3.10). With this transformation, it will be possible to obtain constant DC values of voltage components which is a great advantage in the control of the inverter.

Figure 3.10 dq transformation of voltages

With the phase-angle information of  $\theta$  obtained from the PLL, the stationary two-phase  $\alpha\beta$  vector can be converted into a rotating reference frame called as the dq transformation. The dq transformation equation and matrix are defined as:

$$V_{sd} + jV_{sq} = (V_{s\alpha} + jV_{s\beta})e^{-j\theta}$$

(3.6)

$$\begin{bmatrix} V_{sd} \\ V_{sq} \end{bmatrix} = \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix} \begin{bmatrix} V_{s\alpha} \\ V_{s\beta} \end{bmatrix}$$

(3.7)

When the utility voltages are ideal and balanced, the dq components of the source voltage  $V_s$  appear as DC values (Figure 3.11) in the rotating reference frame.

Figure 3.11 dq transformed voltages

# 3.5.4 Dq components of the unsymmetrical set of voltages

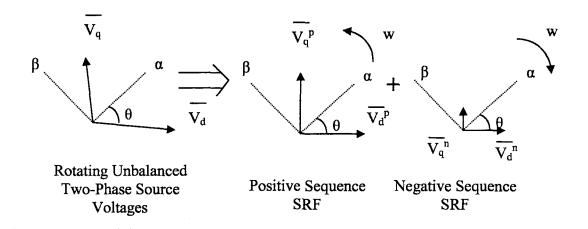

The unsymmetrical set of voltages (in case of source voltage unbalance), two rotating coordinate systems should be used for proper operation of the controller. The former will rotate counterclockwise direction, denoted as  $V^{(p)}$  and called as the positive sequence synchronous reference frame (SRF), while the latter will rotate in the clockwise direction, denoted as  $V^{(n)}$  and called as the negative sequence SRF, with the angular frequency of the system in the stationary reference frame (Figure 3.12).

Figure 3.12 dq transformation of unbalanced voltages

The positive sequence SRF will be composed of positive sequence which is a DC component and negative sequence which is an AC component with the frequency twice of the angular frequency. The positive sequence SRF can be extracted when  $\theta = wt$  in (3.6) (Figure 3.13).

Considering the negative sequence SRF, this time the negative sequence becomes DC component and the positive sequence becomes the AC component. The negative sequence SRF can be extracted when  $\theta = -wt$  in (3.6) (Figure 3.13).

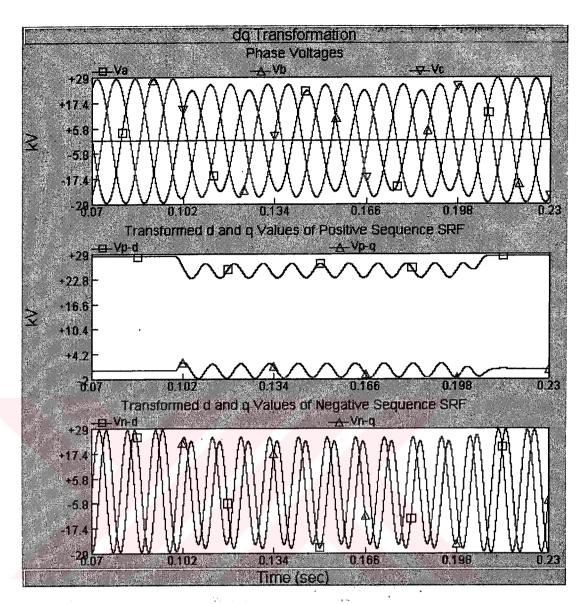

Figure 3.13 dq transformations in the negative and positive sequence SRF

For the effective control without phase shift in the steady state, the DC values of the positive and negative sequence SRF should be calculated accurately. Among the methods of this extraction, application of a low pass filter (LPF) may be considered. Application of a filter will introduce a delay in the control system. Furthermore the AC values in the negative sequence SRF is large with respect to the DC values thus a LPF will not be able to filter out the AC components. This problem may be solved by decreasing the cut-off frequency of the LPF but the controller response will be very slow.

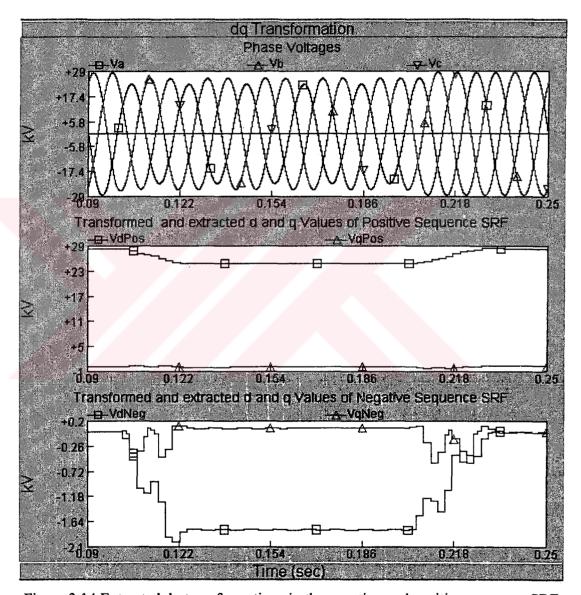

In the literature, two methods for the extraction of the DC values are proposed. One proposes a differential controller method while the other proposes a mathematical solution which is based on extracting the signal with the T/4 delayed signal thus obtaining the AC values. To illustrate, the DC components of the positive and negative sequence components are extracted via the FFT transformation. The DC components of the unbalanced voltages are as shown in Figure 3.14 [13][14].

Figure 3.14 Extracted dq transformations in the negative and positive sequence SRF

# 3.5.5 Voltage Controller

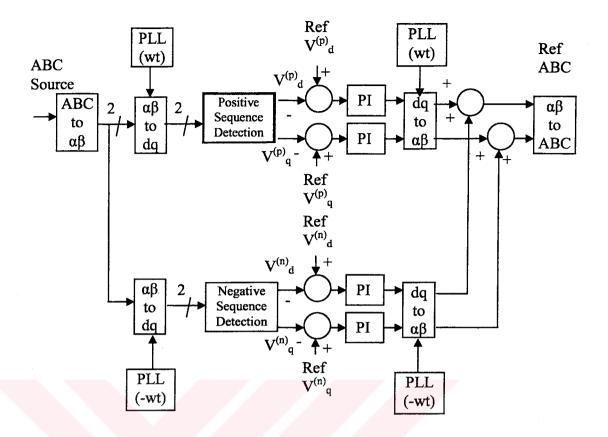

The aim of the voltage controller is supply the load with a balanced set of voltages of desired amplitude resulting in the following components of the desired load voltage vector:

Positive sequence voltage in d-direction  $V^{(p)}_{d} = 0$

Positive sequence voltage in q-direction  $V_{q}^{(p)} = V_{l-r}$

Negative sequence voltage in d-direction  $V^{(n)}_{d} = 0$

Negative sequence voltage in q-direction  $V^{(n)}_{q} = 0$

Where  $V_{l-r}$  is the rated phase-phase load voltage.

The components of the desired load voltage vector are compared with the above corresponding values in order to obtain positive and negative sequence components of the voltage to be injected. They are transformed back into the  $\alpha\beta$ -coordinate system and added and then transformed into the three-phase domain and the reference signal for the PWM inverter is obtained (Figure 3.15). For the symmetrical balanced faults, there is no need to extract the positive and negative sequence SRF components. Therefore the controller response to the balanced voltage sags will rather quick with respect to the unbalanced voltage sags. In order to reduce the error between the reference and the actual voltage values, PI controllers are inserted before the "dq to  $\alpha\beta$ " transformations.

Figure 3.15 The Control Block Diagram

Figure 3.16 The generation of PWM signals

Another control issue that may be added to optimize the controller is the DC link voltage magnitude. During a voltage the energy on the DC-link will be transferred to the load, changing the magnitude of the DC-link voltage. Even if for the topologies that feed the DC-link during the compensation, there still be variations in the DC-link voltage related with the voltage sag depth. Therefore the controller

should ensure proper voltage injection magnitude considering the DC-link voltage (Figure 3.16).

Note that as introduced before the application of inverter side filter and the injection transformer will degrade the performance of the controller and thus will require special considerations

In this type of control strategy the DVR will inject voltage with the fundamental positive and the negative sequence. The advantage of this strategy is that the compensated voltage will be in phase with the pre-sag voltage. The disadvantage is the magnitude of the injected voltage should be greater than the inphase injection strategy during an unbalanced voltage sag.

After obtaining the reference voltages, the PWM signals for triggering the each leg of the inverter should be calculated. Sinusoidal PWM method [24] is one of the simplest and effective methods which can be applied to the inverter of the DVR.

#### 3.6 LOCATION OF DVR

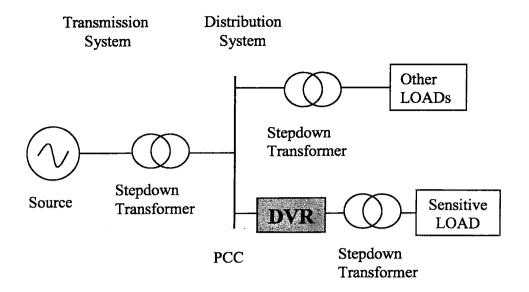

The DVR will cope with voltage sags caused by faults in the transmission or distribution systems. In custom power applications, the DVR is connected in the utility primary distribution feeder via a series injection transformer. By this connection location, a voltage sag in the point of common coupling (Figure 3.17) caused by faults on the adjacent feeders or on the transmission system that would affect a certain group of customers will be mitigated.

Another advantage of this location is that the zero sequence components in case of an unbalanced voltage variation are filtered in the delta connected transformers therefore the DVR will not deal with the zero sequence components.

Figure 3.17 The Location of DVR

#### **CHAPTER 4**

#### **DVR TOPOLOGIES AND COMPONENTS**

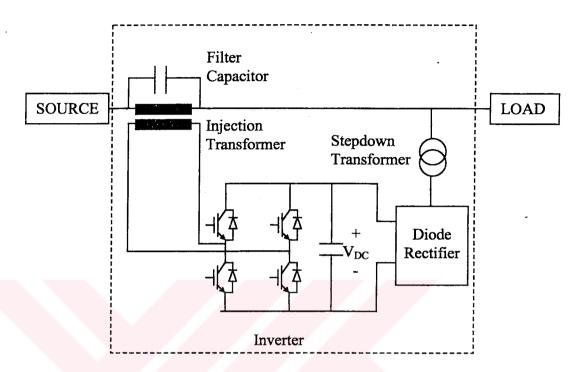

The DVR is mainly composed of an inverter to generate the injection voltage, a filter to damp the harmonics generated by the inverter, an energy storage unit to supply the necessary active power during the mitigation of voltage sags and a series injection transformer to couple the generated voltage to the system. Different schemes and topologies exist for these components. In this chapter of the study, basic topologies of for charging energy storage unit, the parameters of the injection transformer, the inverter schemes that can applied and the filtering schemes will be introduced and analyzed.

#### 4.1 TOPOLOGIES OF DVR

The most critical issue in designing a DVR is the source of energy to be supplied to the DVR. Compensating of voltages effectively in large voltage reductions requires active power which will be supplied from a storage system, the grid itself or from an auxiliary supply. The topologies proposed can be divided into two main groups following two sub-groups for each [15]:

- > Topologies with no energy storage

- o Energy taken from the existing supply with a passive shunt converter connected to the supply side.

- o Energy taken from the existing supply with a passive shunt converter connected to the load side.

#### > Topologies with energy storage

- o Stored energy in the DC-link and a variable DC-link voltage

- O Arbitrary kind of energy storage with a controllable DC-link, which can be held constant.

# 4.1.1 DVR Topologies with No Energy Storage

During voltage sags, there still remains a significant part of the supply voltage. If the DVR is connected to a strong grid, the necessary power to the load can still be obtained from the source by increasing the supply current by a shunt converter.

A passive shunt converter is applied since only uni-directional power flow is assumed necessary.

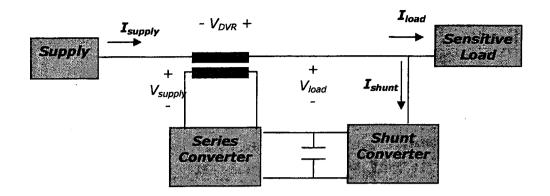

#### 4.1.1.1 Supply Side Connected Shunt Converter

The supply side connected converter is shown in Figure 4.1. The uncontrollable DC-Link voltage and the passive converter will charge the DC-Link capacitor to the actual state of the supply voltage.

Figure 4.1 DVR with no energy storage and supply side connected converter

If no step-down transformer is introduced, the DC-Link voltage is approximately equal to the peak phase-phase value of the supply voltage. During a

voltage sag, the DC-Link voltage will drop with respect to the remaining sag voltage according to:

$$V_{DC} \cong \sqrt{6} * V_{Supply} \cong \sqrt{6} * V_{Sag}$$

(4.1)

where  $V_{DC}$  and  $V_{Supply}$  are the DC-Link Voltage and the rms supply voltage respectively.  $V_{Sag}$  is the phase voltage during a sag. The power and current handled by the converters can be approximated to:

$$P_{Shunt} = P_{Serie} \cong 3*(1-V_{Sag}/V_{Rated})*P_{Load}$$

(4.2)

$$I_{Serie} = I_{Load} \tag{4.3}$$

$$I_{Shunt} \cong \frac{(1 - V_{Sag} / V_{Rated})}{V_{Sag} / V_{Rated}} * I_{Load}$$

(4.4)

$P_{Shunt}$  and  $P_{Serie}$  are the three-phase powers handled by the shunt and series converter respectively.  $V_{Rated}$  is the rated supply voltage and  $I_{Load}$  is the rated load current.

In this topology the power handled by the shunt converter is proportional to the missing voltage and in case of severe sags the current drawn by the converter rises significantly. For example in case of a 50% voltage sag, the current through the shunt converter increases at a rate of 100%, that is  $I_{Shunt} = I_{Load}$ .

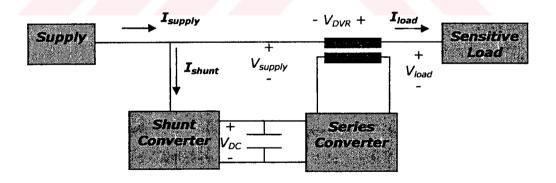

#### 4.1.1.2 Load Side Connected Shunt Converter

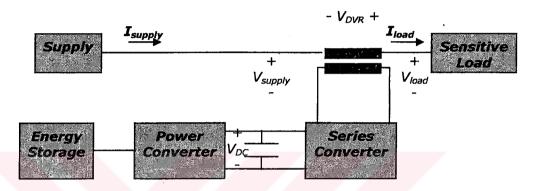

In load side connected shunt converter topology (Figure 4.2), the DC-Link voltage is almost constant by injecting sufficient voltage ( $V_{DVR}$ ).

$$V_{DC} \cong \sqrt{6} * V_{Load} \cong \sqrt{6} * (V_{Sag} + V_{DVR})$$

$$\tag{4.5}$$

Figure 4.2 DVR with no energy storage and load side connected converter

The current relationships are approximately as:

$$P_{Shunt} = P_{Serie} = \frac{(1 - V_{Sag} / V_{Rated})}{V_{Sag} / V_{Rated}} * P_{Load}$$

(4.6)

$$I_{Serie} = I_{Supply} \cong \frac{P_{Load}}{3 * V_{Sap}} \tag{4.7}$$

$$I_{Shunt} \cong \frac{(1 - V_{Sag} / V_{Rated})}{V_{Sag} / V_{Rated}} * I_{Load}$$

(4.8)

The relationships show the main drawback of the topology, that is the high current through the series converter. For example in case of a 50% voltage sag the current through the series converter increases at a rate of 200% (required supply current doubles) and through the shunt converter, current equal to  $I_{Load}$  is drawn. This topology not only provides a clean an controlled voltage input to the rectifier, but also results in an overload rating for the inverter during non-sagged voltage conditions.

Another important drawback of the topology is the distorted current drawn by the passive shunt converter, which will significantly degrade the quality of the load voltage.

# 4.1.2 DVR Topologies with Energy Storage

Storage of energy requires a great cost, but the strain on the grid connection is lower. If the grid that the DVR is connected is weak, than topologies with energy storage should be applied in order to increase the performance of the DVR.

#### 4.1.2.1 Variable DC-Link Voltage

Storage of energy in the DC-Link capacitors as shown in Figure 4.3 is a common solution for DVRs. The topology is simple and the DC-Link voltage is variable.

Figure 4.3 DVR with energy storage and variable DC-Link

The energy stored in the capacitor is calculated with the common equation:

$$E_{Storage} = \frac{1}{2} C_{DC} V_{DC}^2 \tag{4.9}$$

During a voltage sag, the voltage on the DC-Link capacitor decays exponentially such that in case of a long voltage sag the performance of the DVR decreases significantly.

$$P_{Serie} \cong (1 - V_{Sag} / V_{Rated}) * P_{Load}$$

(4.10)

This solution proposes a relatively simple power topology. The charging of the DC-Link may be supplied either from a low rated auxiliary charging converter or from the series converter. In this topology the efficiency of the energy storage is lower than the constant DC-Link voltage topology.

# 4.1.2.2 Constant DC-Link Voltage

In the constant DC-Link voltage topology (Figure 4.4), the DC-Link voltage is held constant by transferring necessary energy from a large storage to a small rated DC-Link. Super Magnetic Energy Storage (SMES), batteries or super capacitors with a highly rated energy conversion converter supplies the DC-Link with necessary energy.

Figure 4.4 DVR with Constant DC-Link Voltage

The DC-Link voltage is almost held constant and the ratings of the converter can be calculated to:

$$V_{DC} = constant (4.11)$$

$$P_{PowerConverter} = P_{Serie} (4.12)$$

$$P_{Serie} \cong (1 - V_{Sag} / V_{Rated}) * P_{Load}$$

(4.13)

In performance is improved with respect to the variable DC-Link solution, but the equipment costs and the complexity of the power circuit increases.

# 4.1.3 The Comparison of Topologies of DVR

The topologies that may be applied to the DVRs have been covered and the advantages and disadvantages with respect to each other have been given. The analysis shows that the topology with load side connected shunt converter has been ranked as the best topology to be applied with low cost and complexity. But note that

negative grid effects and high rated series converter requirements may disqualify the solution for certain applications. For example a DVR with this kind of topology will not be suitable for weak grids.