## A DEPENDABLE COMPUTING APPLICATION

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

UĞUR GÜNGÖR

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

APRIL 2005

Approval of the Graduate School of Natural and Applied Sciences

Prof. Dr. Canan ÖZGEN Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof. Dr. İsmet ERKMEN Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

| Prof. Dr. Hasan Cengiz GÜRAN |

|------------------------------|

| Supervisor                   |

## **Examining Committee Members**

| Doç. Dr. Gözde BOZDAĞI AKAR     | (METU,EEE) |  |

|---------------------------------|------------|--|

| Prof. Dr. Hasan Cengiz GÜRAN    | (METU,EEE) |  |

| Yrd. Doç. Dr. Cüneyt BAZLAMAÇCI | (METU,EEE) |  |

| Dr. Şenan Ece SCHMIDT           | (METU,EEE) |  |

| Gökhan GÖKSÜGÜR (M.Sc.)         | (ASELSAN)  |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Uğur GÜNGÖR

## ABSTRACT

#### A DEPENDABLE COMPUTING APPLICATION

Güngör, Uğur

M.S., Department of Electric and Electronics Engineering Supervisor : Prof. Dr. Hasan Cengiz Güran

April 2005, 129 pages

This thesis focuses on fault tolerance which is kind of dependable computing implementation. It deals with the advantages of fault tolerance techniques on Single Event Upsets (SEU) occurred in a Field Programmable Gate Array (FPGA). Two fault tolerant methods are applied to floating point multiplier. Most common SEU mitigation method is Triple Modular Redundancy (TMR). So, two fault tolerance methods, which use TMR, are tested.

There are three printed circuit boards (PCBs) and one user interface software in the setup. By user interface software running on a computer, user can inject fault or faults to the selected part of the system, which uses TMR with voting circuit or TMRVC TMR with voting and correction circuits on floating point multiplier. After inserting fault or faults, user can watch results of the fault injection test by user interface software. One of these printed circuit boards is called as a Test Pattern Generator. It is responsible for communication between the Fault Tolerant Systems and the user interface software running on a computer. Fault Tolerant Systems is second PCB in the setup. It is used to implement fault tolerant methods on fifteen bits floating point multiplier in the FPGA. First one of these methods is TMR with voter circuit (TMRV) and second one is TMR with voter and correction circuits (TMRVC). Last PCB in the setup is Display PCB. This PCB displays fault tolerant test result and floating point multiplication result. All

the functions on Test Pattern Generator and Fault Tolerant Systems are implemented through the use of a Field Programmable Gate Array (FPGA), which is programmed using the Very High Speed IC Description Language (VHDL).

Implementation results of the used methods in FPGA are evaluated to observe the performance of applied methods for tolerating SEU.

# ÖΖ

## YÜKSEK GÜVENİLİRLİKLİ BİLGİSAYAR DONANIM UYGULAMASI

Güngör, Uğur

Yüksek Lisans, Elektrik-Elektronik Mühendisliği Bölümü Tez Yöneticisi : Prof. Dr. Hasan Cengiz Güran

Nisan 2005, 129 sayfa

Bu tez, yüksek güvenilirlikli bilgisayar uygulamalarından birisi olan hata toleransı uygulamasının üzerinde durmaktadır. Bu tezde Alan Programlanabilir Kapı Dizini (FPGA) içinde oluşan Tekli Hata Oluşumlarına (SEU) karşı uygulanan hata tolerans metodlarının avantajları ile ilgilenilmiştir. Bunun için, 2 tane hata tolerans metodu, kayan noktalı çarpıcı üzerine uygulanmıştır. En yaygın SEU azaltma metodu Üçlü Modüler Yedekleme'dir (TMR). Bu nedenle, TMR kullanan iki çeşit hata tolerans metodu test edilmiştir.

Düzenekte 3 tane Baskı Devre Kartı (PCB) ve 1 tane kulanıcı arayüz yazılımı bulunmaktadır. Bilgisayar üzerinde çalışan kullanıcı arayüz yazılımı ile kullanıcı, oylama devreli yada oylama ve düzeltme devreli TMR kullanan systemin seçilen bir bölgesine hata veya hatalar enjekte edebilir. Hata veye hataları enjekte ettikten sonra , kullanıcı hata enjekte etme testinin sonuçlarını kullanıcı arayüz yazılımından izleyebilir. Düzenekteki PCB'lerden birisi Test Örüntüsü Yaratıcı'dır. Bu PCB, Hata Tolere Edebilir Sistemler ve kullanıcı arayüz yazılımı arasındaki konuşmadan sorumludur. Düzenekteki ikinci PCB, Hata Tolere Edebilir Sistemler'dir. Bu PCB, hata tolere edebilir metotları, kayan noktalı çarpıcı üzerine FPGA'de gerçekleştirmekle sorumludur. Bu metodlardan birincisi oylama devreli TMR (TMRV), ikincisi ise oylama ve düzeltme devreli TMR'dır (TMRVC). Düzenekteki son PCB Gösterge PCB'sidir. Bu PCB, test sonucunu ve çarpma isleminin sonucunu gösterir.

Test Örüntüsü Yaratıcı ve Hata Tolere Edebilir Sistemler üzerindeki fonksiyonlar, Çok Yüksek Hızlı Entegre Devre Tanımlama Dili (VHDL) kullanılarak programlanan Alan Programlanabilir Kapı Dizinleri içine gerçekleştirilmiştir.

FPGA içerinde gerçekleştirilen metotların sonuçları değerlendirilerek, uygulanan metotların performansları irdelenmiştir.

To My Family

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my supervisor Prof. Dr. Hasan Cengiz Güran for his supervision and guidance.

Special thanks to ASELSAN Inc. Microelectronics, Guidance and Electro-Optics division for providing technical support and laboratory environment in which I could develop my design.

Also, I am thankful to all my family and my friends for their continued patience, understanding, and encouragement throughout the preparation of this study.

# **TABLE OF CONTENTS**

| PLAGIARISMiii                       |

|-------------------------------------|

| ABSTRACTiv                          |

| ÖZvi                                |

| ACKNOWLEDGEMENTSix                  |

| ABBREVIATIONSxiv                    |

| LIST OF TABLESxv                    |

| LIST OF FIGURESxvi                  |

| CHAPTERS                            |

| INTRODUCTION                        |

| 1.1 INTRODUCTION TO FAULT TOLERANCE |

| 1.2 SHORT DESCRIPTION OF THE THESIS APPLICATION  | 3  |

|--------------------------------------------------|----|

| 1.2.1 SOFTWARE PART                              | 4  |

| 1.2.2 TEST PATTERN GENERATOR PART                | 4  |

| 1.2.3 FAULT TOLERANT SYSTEMS PART                | 5  |

| 1.2.4 DISPLAY PCB                                | 5  |

| 1.3 ORGANIZATION OF THE THESIS                   | 6  |

| 2 FAULT TOLERANCE                                | 7  |

| 2.1 FUNDAMENTAL DEFINITIONS                      | 8  |

| 2.1.1 CHARACTERISTICS OF A FAULT                 | 9  |

| 2.1.2 PRIMARY SYSTEM IMPROVEMENT TECHNIQUES      | 11 |

| 2.2 DESIGN TECHNIQUES TO ACHIEVE FAULT TOLERANCE | 12 |

| 2.3 REDUNDANCY                                   | 12 |

| 2.3.1 HARDWARE REDUNDANCY                        | 13 |

| 2.3.1.1 PASSIVE HARDWARE REDUNDANCY              | 13 |

| 2.3.1.2 ACTIVE HARDWARE REDUNDANCY               | 15 |

| 2.3.1.3 HYBRID HARDWARE REDUNDANCY               |    |

| 2.3.2 SOFTWARE REDUNDANCY                        | 18 |

| 2.3.2.1 CONSISTENCY CHECKS                       | 18 |

| 2.3.2.2 CAPABILITY CHECKS                        | 18 |

| 2.3.2.3 N-VERSION PROGRAMMING                    | 18 |

| 3.1 FPGA.       20         3.2 SINGLE EVENT UPSET (SEU)       23         3.3 FPGA FAULT TOLERANCE TECHNIQUES FOR TOLERATING SEU       25         4 IMPLEMENTED PCBs IN THE SETUP       28         4.1 INTRODUCTION       28         4.2 CRITICAL PCB COMPONENTS       28         4.2.1 TEST PATTERN GENERATOR PCB CRITICAL COMPONENTS       28         4.2.1.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       28         4.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)       29         4.2.1.3 OSCILLATOR       30         4.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS       31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       MEMORY (EEPROM)         4.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS       31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       MEMORY (EEPROM)         4.2.2.1 FIELD PROGRAMMABLE GATE ARRAY (FPGA)       32         4.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)       32         4.2.3.1 LED       32         4.3 PCB DESIGN CONSIDERATIONS       33         5 FPGA DESIGN CONSIDERATIONS       33         5 I FAULT TOLERANT SYSTEMS FPGA       39         5.1.1 TMR WITH VOTER CIRCUIT       41         5.1.1 TMR WITH VOTER CIRCUIT       43         5.1.1 I MOULLE INPUT FAULT INJECTION CIRC | 3 FPGA FAULT TOLERANCE                                 |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----|

| 3.2 SINGLE EVENT UPSET (SEU)       23         3.3 FPGA FAULT TOLERANCE TECHNIQUES FOR TOLERATING SEU       25         4 IMPLEMENTED PCBs IN THE SETUP       28         4.1 INTRODUCTION       28         4.2 CRITICAL PCB COMPONENTS       28         4.2.1 TEST PATTERN GENERATOR PCB CRITICAL COMPONENTS       28         4.2.1 TEST PATTERN GENERATOR PCB CRITICAL COMPONENTS       28         4.2.1.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       28         4.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)       29         4.2.1.3 OSCILLATOR       30         4.2.1 4 RS232 TRANSCEIVER       30         4.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS       31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       MEMORY (EEPROM)         MEMORY (EEPROM)       31         4.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)       32         4.2.3 DISPLAY PCB CRITICAL COMPONENTS       32         4.2 3 PCB DESIGN CONSIDERATIONS       33         5 FPGA DESIGN CONSIDERATIONS       33         5 I FAULT TOLERANT SYSTEMS FPGA       39         5.1.1 TMR WITH VOTER CIRCUIT       41         5.1.1 MODULE INPUT FAULT INJECTION CIRCUIT       43                                                                                                         |                                                        | •  |

| 3.3 FPGA FAULT TOLERANCE TECHNIQUES FOR TOLERATING SEU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |    |

| 4 IMPLEMENTED PCBs IN THE SETUP.       28         4.1 INTRODUCTION.       28         4.2 CRITICAL PCB COMPONENTS.       28         4.2.1 TEST PATTERN GENERATOR PCB CRITICAL COMPONENTS.       28         4.2.1 TELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       28         4.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA).       29         4.2.1.3 OSCILLATOR.       30         4.2.1 4 RS232 TRANSCEIVER.       30         4.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS.       31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       31         4.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA).       32         4.2.3 DISPLAY PCB CRITICAL COMPONENTS.       32         4.2.3 ILED       32         4.3 PCB DESIGN CONSIDERATIONS.       33         5 FPGA DESIGN       39         5.1 FAULT TOLERANT SYSTEMS FPGA.       39         5.1.1 TMR WITH VOTER CIRCUIT.       41         5.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT.       43                                                                                                                                                                             |                                                        |    |

| 4.1 INTRODUCTION       28         4.2 CRITICAL PCB COMPONENTS       28         4.2.1 TEST PATTERN GENERATOR PCB CRITICAL COMPONENTS       28         4.2.1.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       28         4.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)       29         4.2.1.3 OSCILLATOR       30         4.2.1.4 RS232 TRANSCEIVER       30         4.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS       31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       31         MEMORY (EEPROM)       31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       31         4.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)       32         4.2.3 DISPLAY PCB CRITICAL COMPONENTS       32         4.2.3 I LED       32         4.3 PCB DESIGN CONSIDERATIONS       33         5 FPGA DESIGN       39         5.1 FAULT TOLERANT SYSTEMS FPGA       39         5.1.1 TMR WITH VOTER CIRCUIT       41         5.1.1 I MODULE INPUT FAULT INJECTION CIRCUIT       43                                                                                                                                                                                                                                                                               | 3.3 FPGA FAULT TOLERANCE TECHNIQUES FOR TOLERATING SEU | 25 |

| 4.2 CRITICAL PCB COMPONENTS.284.2.1 TEST PATTERN GENERATOR PCB CRITICAL COMPONENTS.284.2.1.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY284.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA).294.2.1.3 OSCILLATOR.304.2.1.4 RS232 TRANSCEIVER.304.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS.314.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY314.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY314.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA).324.2.3 DISPLAY PCB CRITICAL COMPONENTS.324.2.3 I LED.324.3 PCB DESIGN CONSIDERATIONS.335 FPGA DESIGN.395.1 FAULT TOLERANT SYSTEMS FPGA.395.1.1 TMR WITH VOTER CIRCUIT.415.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT.43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4 IMPLEMENTED PCBs IN THE SETUP                        | 28 |

| 4.2.1 TEST PATTERN GENERATOR PCB CRITICAL COMPONENTS.284.2.1.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY284.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA).294.2.1.3 OSCILLATOR.304.2.1.4 RS232 TRANSCEIVER.304.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS.314.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY314.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA).324.2.3 DISPLAY PCB CRITICAL COMPONENTS.324.2.3.1 LED.324.3 PCB DESIGN CONSIDERATIONS.335 FPGA DESIGN.395.1 FAULT TOLERANT SYSTEMS FPGA.395.1.1 TMR WITH VOTER CIRCUIT.415.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT.43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.1 INTRODUCTION                                       | 28 |

| 4.2.1.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY<br>MEMORY (EEPROM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.2 CRITICAL PCB COMPONENTS                            | 28 |

| MEMORY (EEPROM)284.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)294.2.1.3 OSCILLATOR304.2.1.4 RS232 TRANSCEIVER304.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS314.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY31MEMORY (EEPROM)314.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)324.2.3 DISPLAY PCB CRITICAL COMPONENTS324.2.3.1 LED324.3 PCB DESIGN CONSIDERATIONS335 FPGA DESIGN395.1 FAULT TOLERANT SYSTEMS FPGA395.1.1 TMR WITH VOTER CIRCUIT415.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.2.1 TEST PATTERN GENERATOR PCB CRITICAL COMPONENTS   | 28 |

| 4.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)294.2.1.3 OSCILLATOR304.2.1.4 RS232 TRANSCEIVER304.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS314.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY<br>MEMORY (EEPROM)314.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)324.2.3 DISPLAY PCB CRITICAL COMPONENTS324.2.3.1 LED324.3 PCB DESIGN CONSIDERATIONS335 FPGA DESIGN395.1 FAULT TOLERANT SYSTEMS FPGA395.1.1 TMR WITH VOTER CIRCUIT415.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.2.1.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY   |    |

| 4.2.1.3 OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MEMORY (EEPROM)                                        | 28 |

| 4.2.1.4 RS232 TRANSCEIVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.2.1.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)           | 29 |

| 4.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS.       .31         4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY       .31         MEMORY (EEPROM)       .31         4.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)       .32         4.2.3 DISPLAY PCB CRITICAL COMPONENTS.       .32         4.2.3.1 LED.       .32         4.3 PCB DESIGN CONSIDERATIONS.       .33         5 FPGA DESIGN       .39         5.1 FAULT TOLERANT SYSTEMS FPGA.       .39         5.1.1 TMR WITH VOTER CIRCUIT.       .41         5.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT.       .43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.2.1.3 OSCILLATOR                                     | 30 |

| 4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY         MEMORY (EEPROM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.2.1.4 RS232 TRANSCEIVER                              | 30 |

| MEMORY (EEPROM)314.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)324.2.3 DISPLAY PCB CRITICAL COMPONENTS324.2.3.1 LED324.3 PCB DESIGN CONSIDERATIONS335 FPGA DESIGN395.1 FAULT TOLERANT SYSTEMS FPGA395.1.1 TMR WITH VOTER CIRCUIT415.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.2 FAULT TOLERANT SYSTEMS PCB CRITICAL COMPONENTS   | 31 |

| 4.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.2.2.1 ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY   |    |

| 4.2.3 DISPLAY PCB CRITICAL COMPONENTS324.2.3.1 LED324.3 PCB DESIGN CONSIDERATIONS335 FPGA DESIGN395.1 FAULT TOLERANT SYSTEMS FPGA395.1.1 TMR WITH VOTER CIRCUIT415.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MEMORY (EEPROM)                                        | 31 |

| 4.2.3.1 LED.324.3 PCB DESIGN CONSIDERATIONS.335 FPGA DESIGN.395.1 FAULT TOLERANT SYSTEMS FPGA.395.1.1 TMR WITH VOTER CIRCUIT.415.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT.43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.2.2 FIELD PROGRAMMABLE GATE ARRAY (FPGA)           | 32 |

| 4.3 PCB DESIGN CONSIDERATIONS.335 FPGA DESIGN.395.1 FAULT TOLERANT SYSTEMS FPGA.395.1.1 TMR WITH VOTER CIRCUIT.415.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT.43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2.3 DISPLAY PCB CRITICAL COMPONENTS                  | 32 |

| 5 FPGA DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.3.1 LED                                            | 32 |

| 5.1 FAULT TOLERANT SYSTEMS FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.3 PCB DESIGN CONSIDERATIONS                          | 33 |

| 5.1.1 TMR WITH VOTER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5 FPGA DESIGN                                          | 39 |

| 5.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1 FAULT TOLERANT SYSTEMS FPGA                        | 39 |

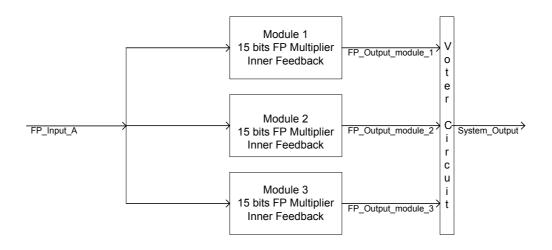

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.1.1 TMR WITH VOTER CIRCUIT                           | 41 |

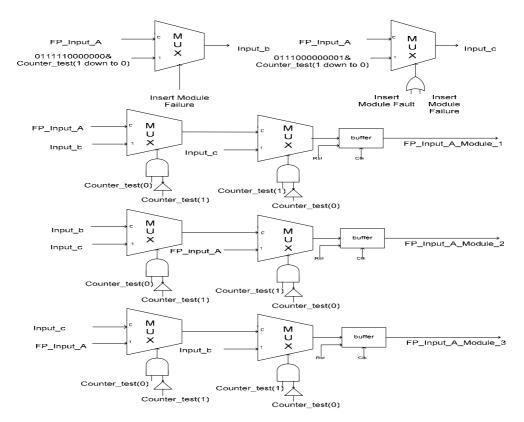

| 5.1.1.2 FP MULTIPLIER INNER FEEDBACK CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.1.1.1 MODULE INPUT FAULT INJECTION CIRCUIT           | 43 |

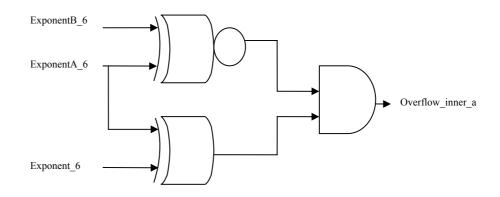

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.1.1.2 FP MULTIPLIER INNER FEEDBACK CIRCUIT           | 44 |

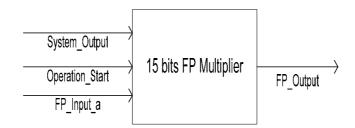

| 5.1.1.3 15 BITS FP MULTIPLIER                            | 45   |

|----------------------------------------------------------|------|

| 5.1.1.4 VOTER CIRCUIT                                    | 56   |

| 5.1.2 TMR WITH VOTER AND CORRECTION CIRCUITS             | 58   |

| 5.1.2.1 MODULE INPUT FAULT INJECTION CIRCUIT             | 59   |

| 5.1.2.2 15 BITS FP MULTIPLIER                            | 59   |

| 5.1.2.3 VOTER AND CORRECTION CIRCUITS                    | 60   |

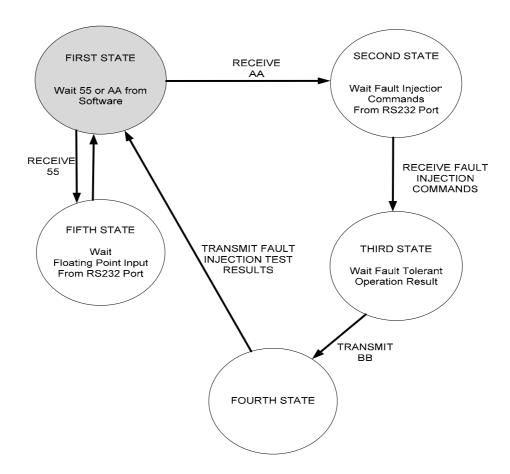

| 5.2 TEST PATTERN GENERATOR FPGA                          | 61   |

| 5.2.1 TEST PATTERN GENERATOR FPGA RS232 INTERFACE        | 61   |

| 6 IMPLEMENTATION RESULTS OF APPLIED ALGORITHMS           | 65   |

| 6.1 IMPLEMENTATION RESULTS OF TMR WITH VOTER CIRCUIT     | 67   |

| 6.2 IMPLEMENTATION RESULTS OF TMR WITH VOTER AND CORRECT | TION |

| CIRCUIT                                                  | 68   |

| 6.3 ADVANTAGES AND DISADVANTAGES OF APPLIED ALGORITHMS   | 70   |

| 7 CONCLUSIONS                                            | 72   |

| REFERENCES                                               | 74   |

| APPENDIX A: SETUP COMPONENTS                             | 76   |

| APPENDIX B: PCB LAYOUT                                   | 79   |

| APPENDIX C: TEST PATTERN GENERATOR VHDL CODES            | 89   |

| APPENDIX D: FAULT TOLERANT SYSTEMS VHDL CODES            | 108  |

# **ABBREVIATIONS**

| ALU    | Arithmetic Logic Unit                                   |

|--------|---------------------------------------------------------|

| ASIC   | Application Specific Integrated Circuit                 |

| BGA    | Ball Grid Array                                         |

| CLB    | Configurable Logic Blocks                               |

| CMOS   | Complementary Metal Oxide Silicon Technology            |

| DSP    | Digital Signal Processor                                |

| PROM   | Programmable Read Only Memory                           |

| EEPROM | Electrically Erasable Programmable Read Only Memory     |

| FP     | Floating Point                                          |

| FPGA   | Field Programmable Gate Array                           |

| GRM    | General Routing Matrix                                  |

| IC     | Integrated Circuit                                      |

| IOB    | Input/Output Block                                      |

| I2C    | Inter Integrated Circuit Control                        |

| LED    | Light Emitting Diode                                    |

| LUT    | Look-up Table                                           |

| NMR    | N-Modular Redundancy                                    |

| PCB    | Printed Circuit Board                                   |

| PGA    | Pin Grid Array                                          |

| PROM   | Programmable Read Only Memory                           |

| QFP    | Quad Flat Package                                       |

| SEU    | Single Event Upset                                      |

| TMR    | Triple Modular Redundancy                               |

| TTL    | Transistor-Transistor Logic                             |

| VHDL   | Very High Speed Integrated Circuit Description Language |

| TMRV   | TMR with voter circuit                                  |

| TMRVC  | TMR with voter and correction circuits                  |

# LIST OF TABLES

## TABLE

| 4.1 | LAYER STACK-UP OF TEST PATTERN GENERATOR PCB          | 37 |

|-----|-------------------------------------------------------|----|

| 4.2 | LAYER STACK-UP OF FAULT TOLERANT SYSTEMS PCB          | 37 |

| 4.3 | LAYER STACK-UP OF DISPLAY PCB                         | 38 |

| 6.1 | TMR WITH VOTER CIRCUIT FPGA PLACEMENT REPORT SUMMARY. | 67 |

| 6.2 | TMR WITH VOTER AND CORRECTION CIRCUIT FPGA PLACEMENT  |    |

|     | REPORT SUMMARY                                        | 69 |

# **LIST OF FIGURES**

### FIGURE

| 2.1  | RELATIONSHIPS BETWEEN FAULT, ERROR AND FAILURE | 8        |

|------|------------------------------------------------|----------|

| 2.2  | FAULT CHARACTERISTICS                          | 10       |

| 2.3  | SYSTEM PERFORMANCE IMPROVEMENT TECHNIQUES BAR  | RIERS11  |

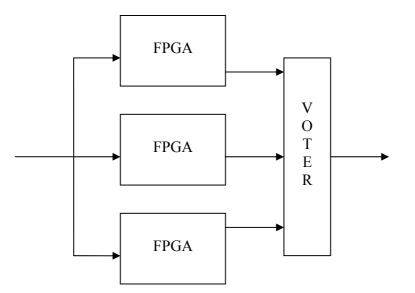

| 2.4  | BLOCK DIAGRAM OF TMR                           | 14       |

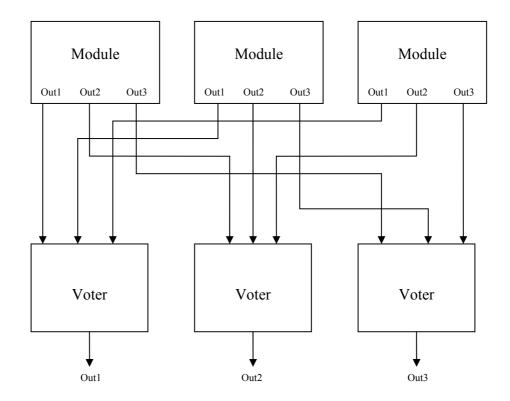

| 2.5  | BLOCK DIAGRAM OF TMR WITH THREE VOTER CIRCUIT  | 14       |

| 2.6  | BLOCK DIAGRAM OF NMR                           | 15       |

| 2.7  | BLOCK DIAGRAM OF DUPLICATION WITH COMPARISON   | 16       |

| 2.8  | BLOCK DIAGRAM OF STANDBY SPARING               | 17       |

| 2.9  | BLOCK DIAGRAM OF PAIR-AND-A-SPARE TECHNIQUE    | 17       |

| 3.1  | FPGA STRUCTURE                                 | 21       |

| 3.2  | CONFIGURABLE LOGIC BLOCK STRUCTURE             |          |

| 3.3  | PROGRAMMABLE STORAGE ELEMENTS                  |          |

| 3.4  | DEVICE LEVEL TMR                               | 25       |

| 3.5  | MODULE LEVEL TMR                               | 26       |

| 3.6  | MODULE LEVEL TMR WITH FEEDBACK                 | 27       |

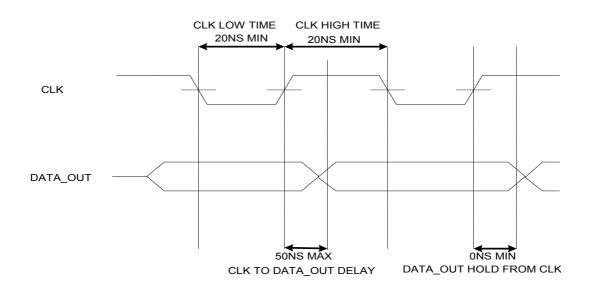

| 4.1  | EEPROM PROGRAM TIMING DIAGRAM                  | 29       |

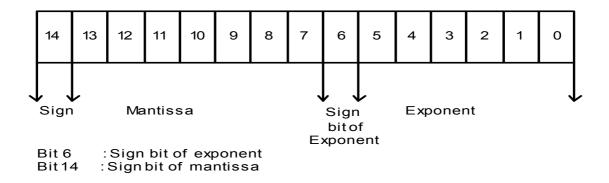

| 5.1  | 15 BITS FLOATING POINT REPRESENTATION          | 40       |

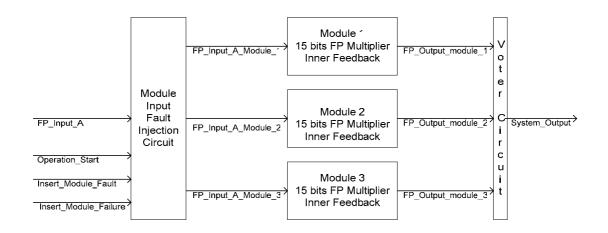

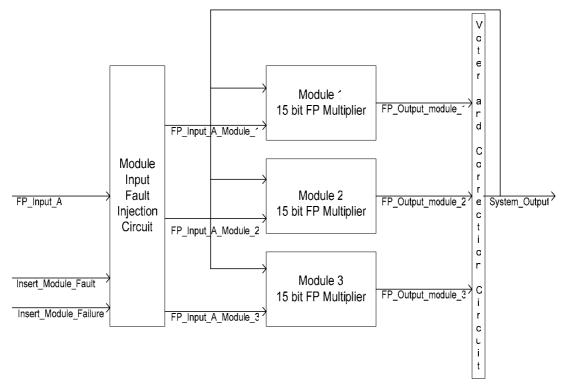

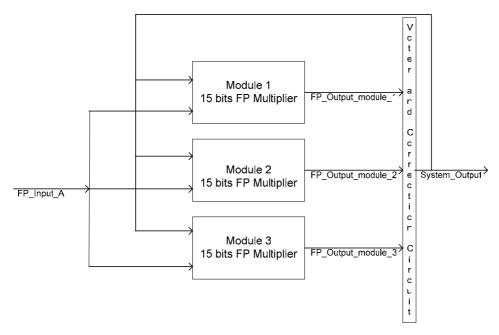

| 5.2  | MAIN DIAGRAM OF TMR WITH VOTER CIRCUIT         | 42       |

| 5.3  | IMPLEMENTATION OF MODULE INPUT FAULT INJECTION |          |

|      | CIRCUIT                                        |          |

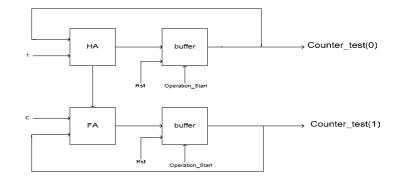

| 5.4  | COUNTER_TEST GENERATIONS                       | 44       |

| 5.5  | 15 BITS FP MULTIPLIER INNER FEEDBACK CIRCUIT   | 44       |

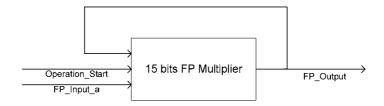

| 5.6  | FLOATING POINT MULTIPLIER                      | 45       |

| 5.7  | FLOATING POINT MULTIPLIER BLOCK 1              | 46       |

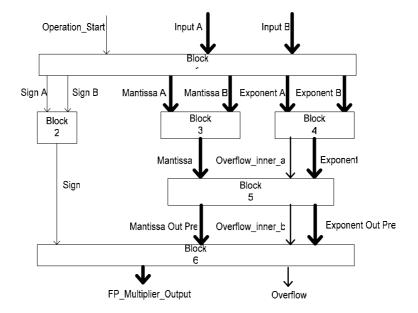

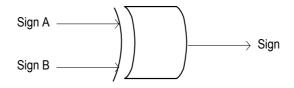

| 5.8  | FLOATING POINT MULTIPLIER BLOCK 2              | 47       |

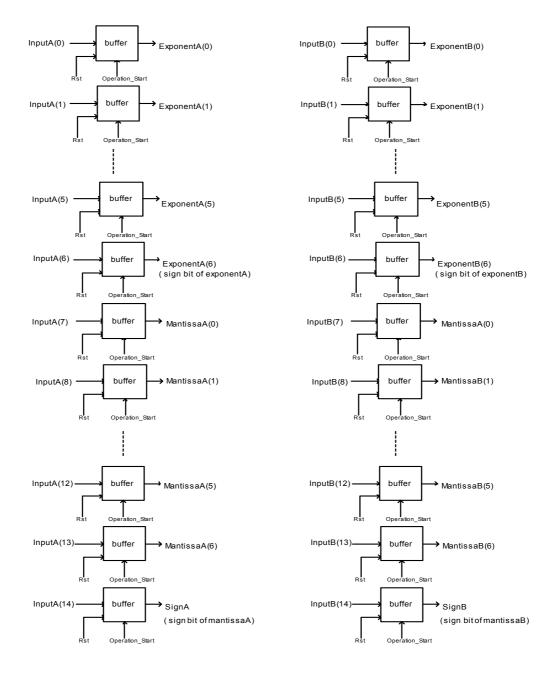

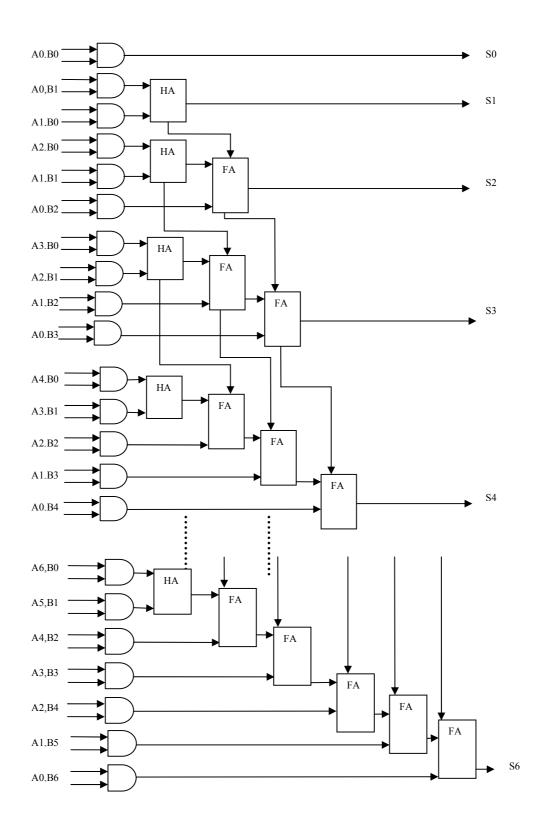

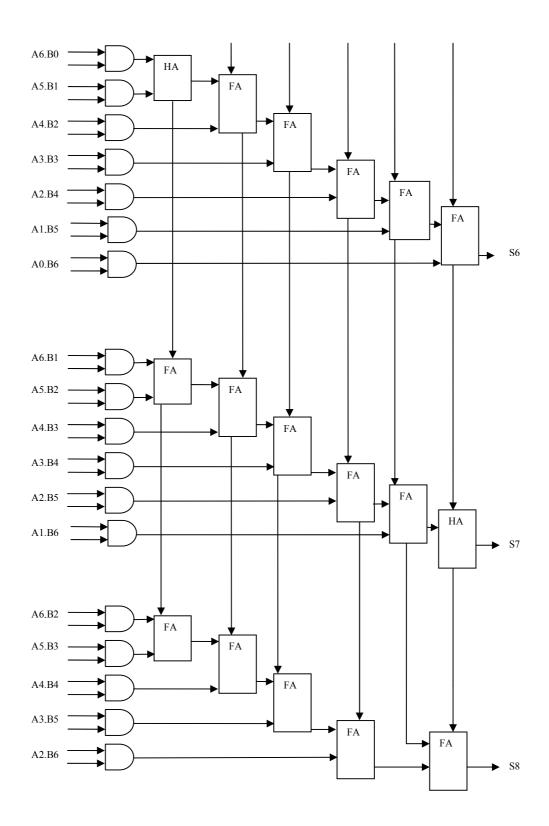

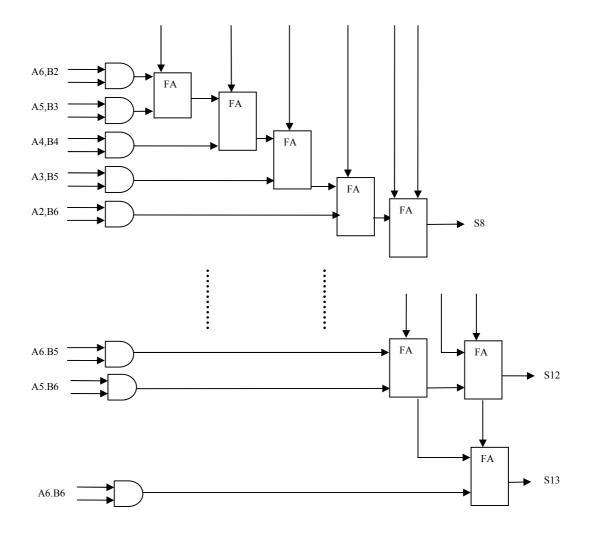

| 5.9  | FLOATING POINT MULTIPLIER BLOCK 3              | 48,49,50 |

| 5.10 | FLOATING POINT MULTIPLIER BLOCK 4              | 51       |

|      | •                                              |          |

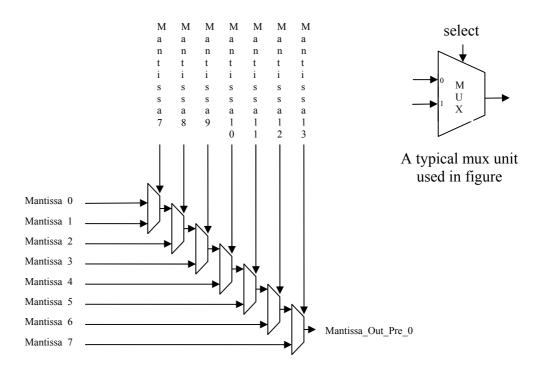

| 5.11 | MANTISSA_OUT_PRE_0                                     |  |

|------|--------------------------------------------------------|--|

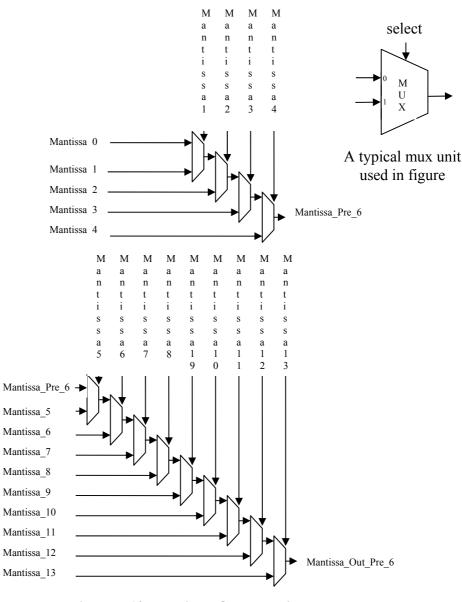

| 5.12 | MANTISSA_OUT_PRE_653                                   |  |

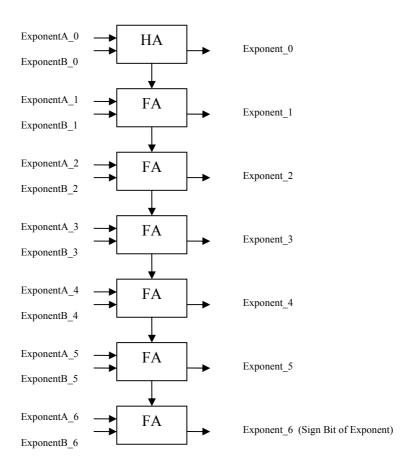

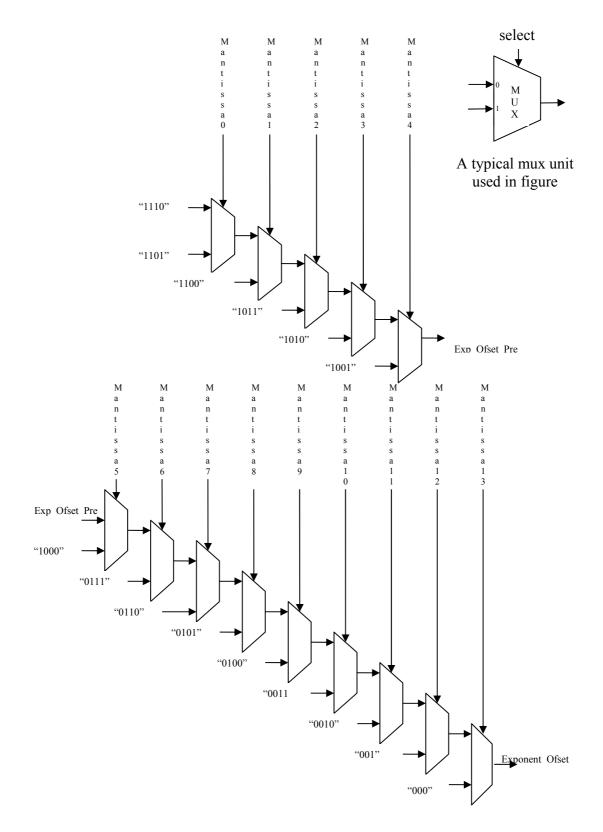

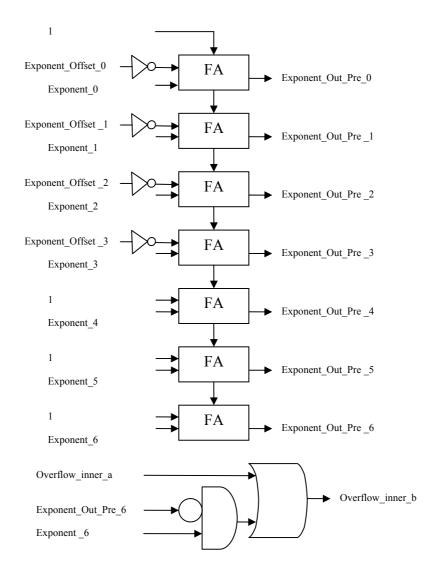

| 5.13 | EXPONENT_OFFSET GENERATION FOR NORMALIZATION54         |  |

| 5.14 | EXPONENT OUT PRE GENERATION55                          |  |

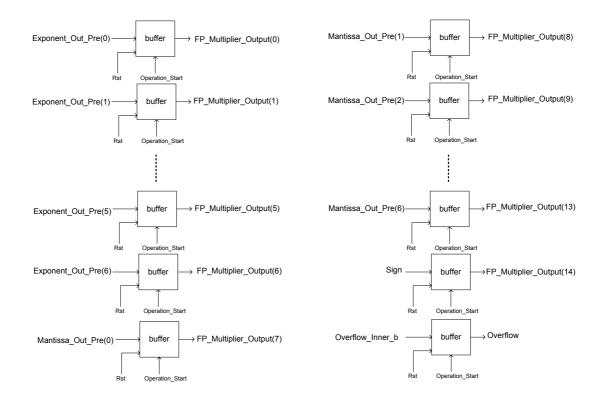

| 5.15 | FLOATING POINT MULTIPLIER BLOCK 6                      |  |

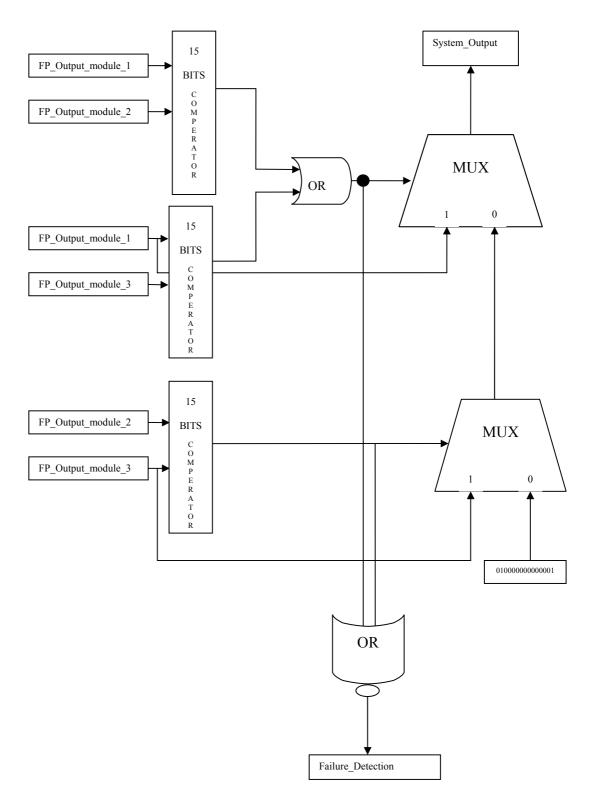

| 5.16 | VOTER CIRCUIT                                          |  |

| 5.17 | MAIN DIAGRAM OF TMR WITH VOTER AND CORRECTION          |  |

|      | CIRCUIT                                                |  |

| 5.18 | 15 BITS FP MULTIPLIER BLOCK DIAGRAM60                  |  |

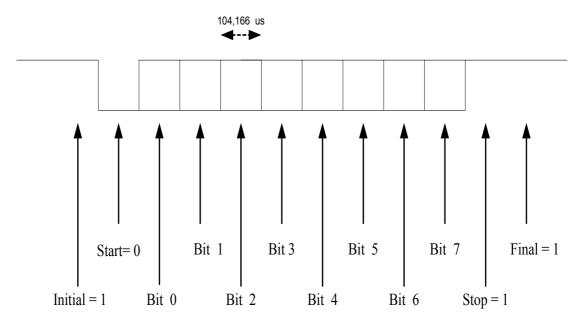

| 5.19 | BYTE TRANSFER PROTOCOL                                 |  |

| 5.20 | STATE DIAGRAM FOR RS232 INTERFACE63                    |  |

| 6.1  | TMR WITH VOTER CIRCUIT                                 |  |

| 6.2  | TMR WITH VOTER AND CORRECTION CIRCUITS                 |  |

| A.1  | SOFTWARE USER INTERFACE OF THESIS APPLICATION76        |  |

| A.2  | TEST PATTERN GENERATOR77                               |  |

| A.3  | FAULT TOLERANT SYSTEMS77                               |  |

| A.4  | DISPLAY PCB                                            |  |

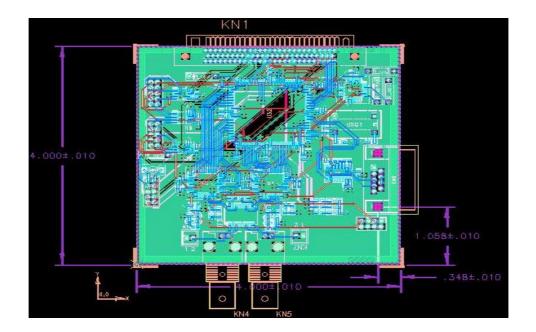

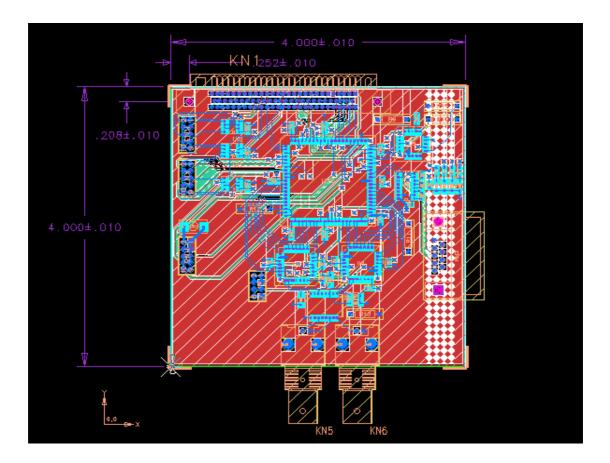

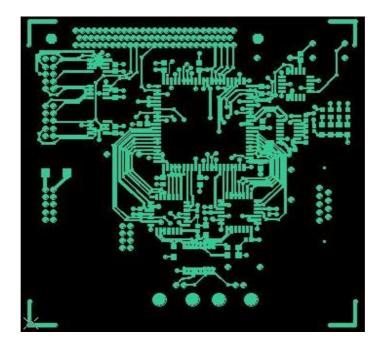

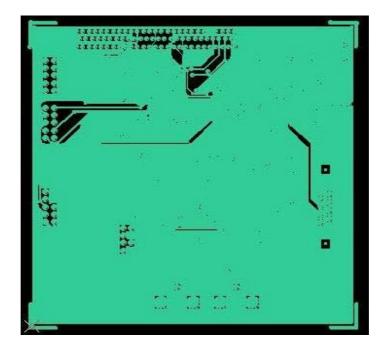

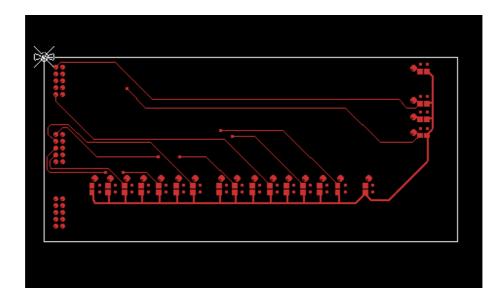

| B.1  | TEST PATTERN GENERATOR COMPONENTS, SIGNAL ROUTINGS AND |  |

|      | DIMENSIONS                                             |  |

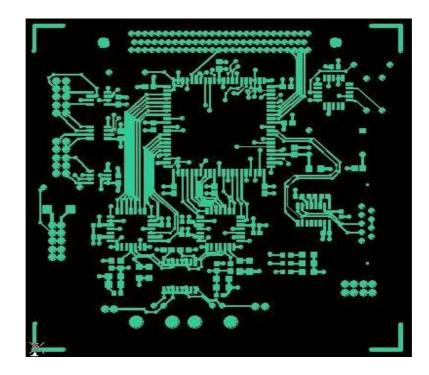

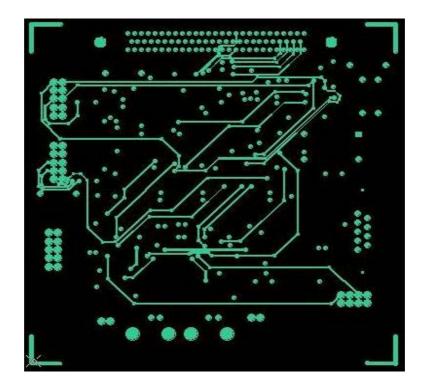

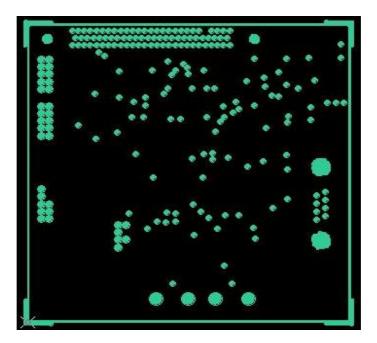

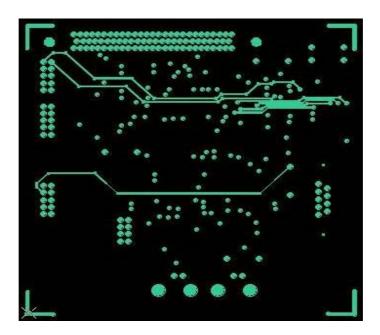

| B.2  | TEST PATTERN GENERATOR FIRST LAYER                     |  |

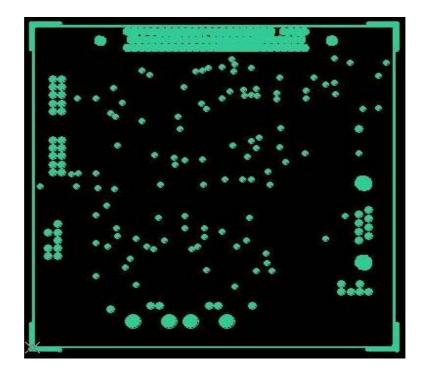

| B.3  | TEST PATTERN GENERATOR SECOND LAYER (GROUND LAYER)80   |  |

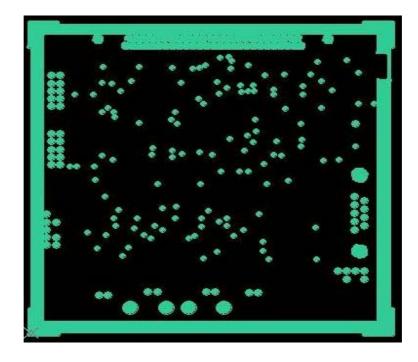

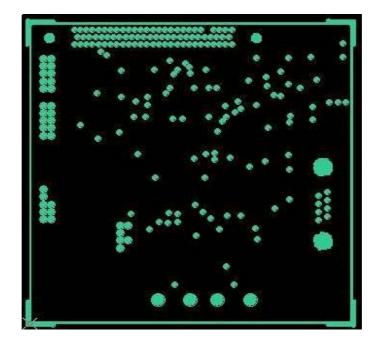

| B.4  | TEST PATTERN GENERATOR THIRD LAYER (POWER LAYER)       |  |

| B.5  | TEST PATTERN GENERATOR FOURTH LAYER                    |  |

| B.6  | TEST PATTERN GENERATOR FIFTH LAYER                     |  |

| B.7  | TEST PATTERN GENERATOR SIXTH LAYER                     |  |

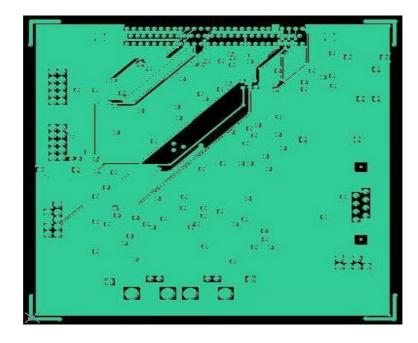

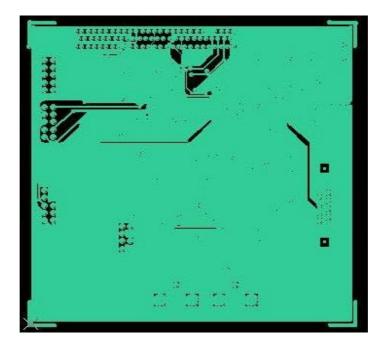

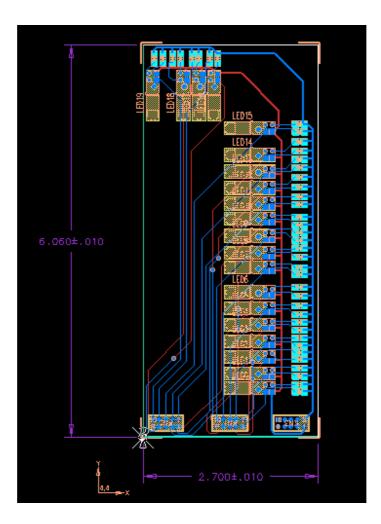

| B.8  | FAULT TOLERANT SYSTEMS COMPONENTS, SIGNAL              |  |

|      | ROUTINGS AND DIMENSIONS                                |  |

| B.9  | FAULT TOLERANT SYSTEMS FIRST LAYER                     |  |

| B.10 | FAULT TOLERANT SYSTEMS SECOND LAYER (GROUND LAYER)84   |  |

| B.11 | FAULT TOLERANT SYSTEMS THIRD LAYER (POWER LAYER)       |  |

| B.12 | FAULT TOLERANT SYSTEMS FOURTH LAYER                    |  |

|      |                                                        |  |

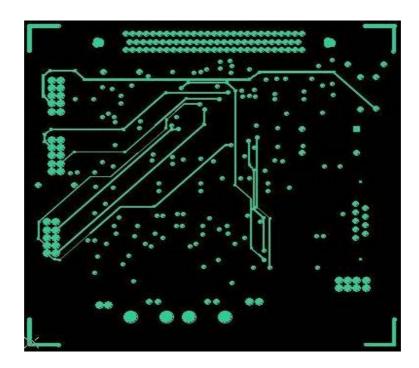

| B.13 | FAULT TOLERANT SYSTEMS FIFTH LAYER          | 86 |

|------|---------------------------------------------|----|

| B.14 | FAULT TOLERANT SYSTEMS SIXTH LAYER          | 86 |

| B.15 | DISPLAY PCB COMPONENTS, SIGNAL ROUTINGS AND |    |

|      | DIMENSIONS                                  | 87 |

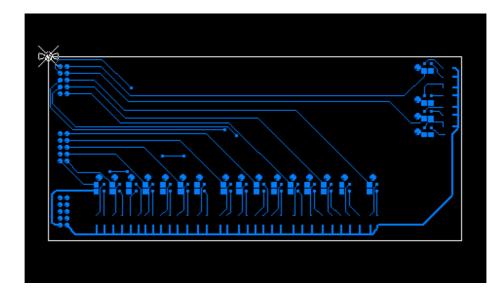

| B.16 | DISPLAY PCB FIRST LAYER                     |    |

| B.17 | DISPLAY PCB SECOND LAYER                    |    |

# **CHAPTER 1**

# **INTRODUCTION**

#### **1.1 INTRODUCTION TO FAULT TOLERANCE**

A Fault tolerant system can perform its specified tasks in the presence of hardware faults and software errors. Fault tolerance tries to prevent negative effects of these faults on the system operation. Fault tolerance is very important in mission critical applications. Most popular applications where fault tolerance is used are listed below. This list shows only most popular applications but there are many other systems which need fault tolerance.

- Space based applications

- Process control systems

- Missile guidance systems

- Medical applications

Fault tolerance can be classified into sub-classes which are listed below [1].

- Fault Detection

- Fault Diagnosis

- Fault Containment

- Fault Masking

- Fault Compensation

• Fault Repair

Fault Detection determines the occurrence of a fault.

Fault Diagnosis determines the reason of a fault. It also specifies which subsystem is faulty.

Fault Containment prevents the propagation of faults from one subsystem to other subsystems.

Fault Masking ensures that only correct values get passed to the system boundary in spite of a failed component.

Fault Compensation provides a response to compensate for output of the faulty subsystem.

Fault Repair is a process, which removes faults in the systems and repair faulty modules.

Redundancy is the addition of resources, time, or information beyond what is needed for normal system operation. There are some forms of redundancy, which are listed below.

- Hardware redundancy

- Software redundancy

- Information redundancy

- Time redundancy

Hardware redundancy is the addition of extra hardware. Software redundancy is the addition of extra software, beyond what is needed to perform a given function. Information redundancy is the addition of extra information beyond that required to implement a given function. Time redundancy is the usage of additional time to perform

the functions of a system. Hardware redundancy and software redundancy are most common forms of redundancy [1].

#### **1.2 SHORT DESCRIPTION OF THE THESIS APPLICATION**

Field Programmable Gate Arrays (FPGAs) are high performance data processing devices. They provide to construct highly parallel architectures for processing data. They are reprogrammable. This decreases design period. Functional changes can be implemented in a short time. As a result, they are preferred in most of the applications today.

Charged particles can provoke a transient pulse, when it hits the silicon. This pulse can change the state of a memory cell on integrated circuits. This phenomenon is known as a Single Event Upset (SEU). SEU is a very serious problem in mission critical applications. FPGAs are also potentially sensitive to SEU. As a result, fault tolerant algorithms must be implemented into FPGAs in mission critical applications [2] [3].

SEU is very serious problem in FPGAs. There are some fault tolerant methods to decrease the probability of a system failure due to these SEUs. Most popular fault tolerant method for FPGA applications is Triple Modular Redundancy (TMR) with voter circuit. TMR uses three identical circuits, which perform the same task in parallel. Their outputs are compared through a majority voter circuit [4].

Fault injection is a widely used technique for dependability estimation of fault tolerant systems. It is an intentional activation of faults in order to observe the system under fault behavior.

In this thesis, there are two methods applied to floating point multiplier. One of them is TMRV. This method is used for detecting faults and correcting output of a system. It does not correct the faulty module. Second one is TMRVC. It is used for detecting

faults, correcting output of a system and correcting the faulty module. Second one is more powerful than first one. But, it uses extra logic for correction circuit.

The aim of this work initially was to design a fault tolerant floating point multiplier circuit with correction property. But the algorithm to be used was not suitable for a parallel multiplication operation with correction. So, our application multiplies input and the previous value of the floating point multiplier output. By this way, we can apply fault tolerant methods with correction circuit to our circuit.

In our application, faults are injected into sub-modules, which are implemented in XC4010 family FPGA, and responses are observed.

Fault injection test composes of 4 main parts.

#### 1.2.1 Software Part:

By the software user interface running on a computer, user can inject fault or faults to the selected part of the system, which uses TMRV or TMRVC. After inserting fault or faults, user can watch the result of the fault injection test by the software user interface.

#### **1.2.2 Test Pattern Generator Part:**

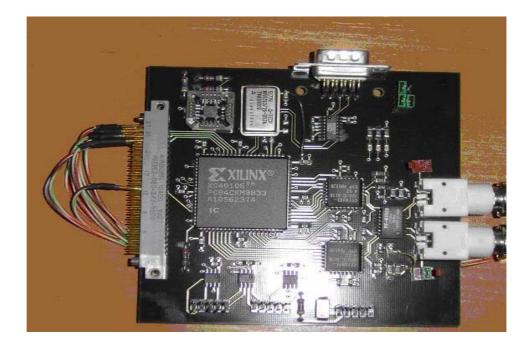

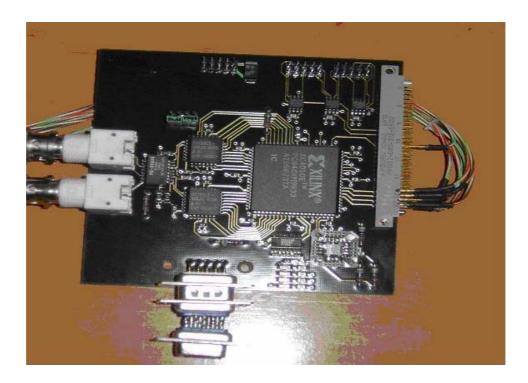

There are three PCBs in this thesis setup. One of them is called as Test Pattern Generator. This PCB is responsible for communication between the Fault Tolerant Systems and the software user interface running on a computer. Fault Tolerant Systems is second PCB in the system and responsible for fault tolerant system implementations.

Test Pattern Generator communicates with the software via RS232 port of the computer. Test Pattern Generator transfers fault injection commands, which come from RS232 port, to the Fault Tolerant Systems by a specified protocol. Then, it takes responses from the Fault Tolerant Systems and sends them to the software part of the setup.

#### 1.2.3 Fault Tolerant Systems Part:

Second PCB in the setup is called as Fault Tolerant Systems. This PCB is used to implement 2 fault tolerant methods on floating point multiplier in the FPGA. First one of these methods is TMRV and second one is TMRVC. As said, there are two systems but they don't operate in parallel. By changing FPGA configuration data, which is stored in EEPROM, of Fault Tolerant Systems, operating fault tolerant method on the system is selected. Fault injection commands, which come from Test Pattern Generator, are applied to selected fault tolerant method on the system, and test results send back to Test Pattern Generator. These test results are also sending to Display PCB, which is the last PCB on the thesis setup.

#### **1.2.4 Display PCB:**

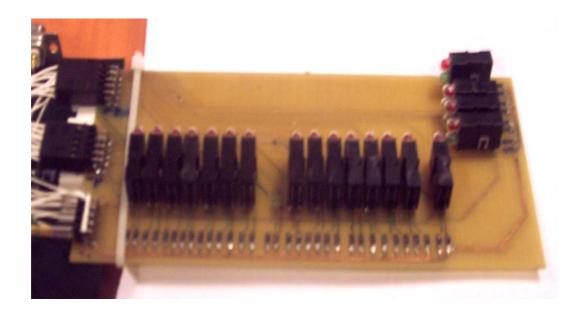

Third PCB in the setup is called as Display PCB. This PCB displays fault tolerant test result and floating point multiplication result.

Finally, advantages and disadvantages of the applied fault tolerant methods on floating point multiplier are explained. These explanations are proven by synthesis and implementation reports of the thesis application.

#### **1.3 ORGANIZATION OF THE THESIS**

This thesis is composed of 7 chapters.

Chapter 2 provides general information about fault tolerance. Fundamental definitions on fault tolerance are given. Design goals and methodologies on fault tolerance are explained in this chapter.

Chapter 3 focuses on the FPGA fault tolerance. Single Event Upset (SEU) is specified. FPGA fault tolerance techniques for tolerating SEU are explained.

Chapter 4 explains high speed PCB design rules, which are considered during the design of PCBs in this setup. PCB components used in these PCBs are also explained in this chapter.

Chapter 5 is focused on FPGA design in Test Pattern Generator and Fault Tolerant Systems.

Chapter 6 presents advantages and disadvantages of the applied fault tolerant methods. These explanations are proven by implementation reports of Fault Tolerant Systems FPGA.

Chapter 7 gives the conclusion.

## **CHAPTER 2**

## FAULT TOLERANCE

A **fault tolerant system** is one that can continue to correctly perform its specified tasks in the presence of hardware failures and software errors. Fault tolerance is an attribute that is designed into a system to achieve some design goals. These design goals are, reliability, availability, safety, performability, maintainability, testability and dependability.

Below, we explain each term separately [1] [13],

**Reliability**, R(t): The conditional probability that a system performs correctly throughout an interval of time [t0, t], given that the system was performing correctly at time t0.

Availability, A(t): The probability that a system is operating correctly and is available to perform its functions at the instant of time t.

**Safety**, *S(t)*: The probability that a system will either perform its functions correctly or will discontinue its functions in a well defined, safe manner. Discontinue its functions in a manner that does not disturb the operation of other systems or compromise the safety of any people associated with the system.

**Performability**, P(L, t): The probability that a system is performing at or above some level of performance L at the instant of time t.

Maintainability, M(t): The probability that an inoperable system will be restored to an operational state within the time t.

Testability: The ability to test for certain attributes within a system.

**Dependability:** The quantity of service that a particular system provides. Reliability, availability, safety, maintainability, performability and testability are measures used to quantify the dependability of a system.

#### **2.1 FUNDAMENTAL DEFINITIONS**

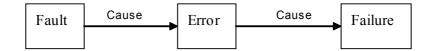

Three fundamental terms in fault tolerant design are fault, error and failures. There is a cause and affect relationship between them.

A fault is a physical defect, imperfection, or flaw that occurs within some hardware or software component. An error is an occurrence of an incorrect value in some unit of information within a system. A failure is a deviation in the expected performance of a system. The relationships between fault, error and failure are shown in Figure 2.1 [13].

Figure 2.1 Relationships between fault, error and failure

#### **2.1.1 CHARACTERISTICS OF A FAULT**

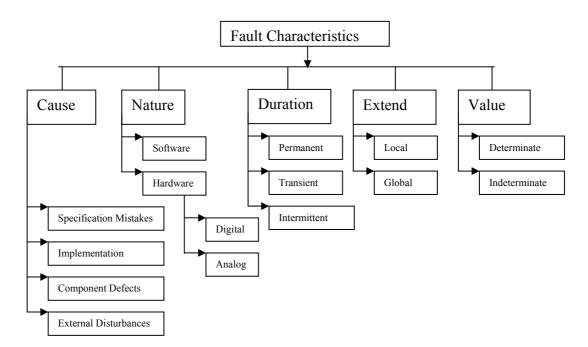

Faults can be characterized by five attributes, which are cause, nature, duration, extend and value. Figure 2.2 illustrates each of these basic characteristics of faults.

Possible fault causes can be associated with problems in four areas.

#### **Specifications mistakes:**

These include incorrect algorithms, architectures, or hardware and software design specifications.

#### **Implementation mistakes:**

The implementation can introduce faults due to poor design, poor component selection, poor construction, or software coding mistakes.

#### **Components defects:**

These include random device defects, manufacturing imperfections, and component wear-out.

#### **External disturbance:**

These include operator mistakes, radiation, electromagnetic interference, and environment extremes.

The **fault nature** specifies the type of fault, which is hardware fault or software fault. If hardware faults, it specifies analog fault or digital fault.

The **fault duration** specifies the length of time that a fault is active. There are three types of fault durations.

#### **Permanent fault:**

It is a fault, which remains in existence indefinitely if no corrective action is taken.

#### **Transient fault:**

It is a fault, which can appear and disappear within a very short period of time.

#### **Intermittent fault:**

It is a fault, which appears, disappears, and reappears repeatedly.

The **fault extend** specifies whether the fault is localized to a given hardware or software module or whether it globally affects the hardware, the software, or both.

The **fault value** can be either determinate or indeterminate. A determinate fault is one whose status remain unchanged throughout time unless external action upon. An indeterminate fault is one whose status at some time t may be different from its status at another time [1].

**Figure 2.2 Fault Characteristics**

#### **2.1.2 PRIMARY SYSTEM IMPROVEMENT TECHNIQUES**

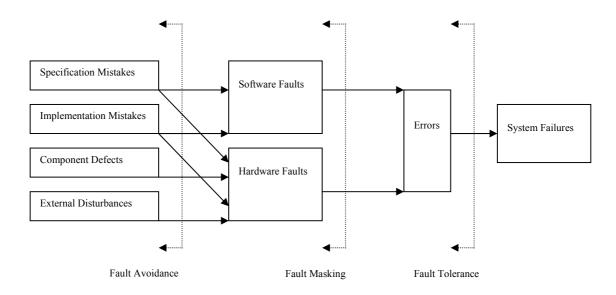

There are three primary techniques for attempting to improve or maintain a system's normal performance. They are fault avoidance, fault masking and fault tolerance.

**Fault avoidance** is any technique that attempts to prevent the occurrence of faults. It can include design reviews, component screening, testing and other quality control methods. Figure 2.3 illustrates the barriers that are constructed by each of the available techniques.

Fault masking is the process of preventing faults from introducing errors.

**Fault tolerance** is the ability to correct performance of functions in the presence of faults. (In fact, failure is directly related to error tolerance but we can use fault tolerance instead of error tolerance.)

Fault tolerance can be achieved by many techniques. Fault masking is one approach to tolerating faults. Another approach is to detect and locate the fault that has occurred and reconfigure the system to remove the faulty component.

Figure 2.3 System performance improvement techniques barriers

As shown in Figure 2.3, by fault avoidance occurrence of faults, which is caused by specification mistakes, implementation mistakes, component defects and external disturbances is tried to be prevented. Fault masking tries to prevent error occurrence due to software and hardware faults. Fault tolerance tries to prevent system failure due to errors.

#### 2.2 DESIGN TECHNIQUES TO ACHIEVE FAULT TOLERANCE

**Fault masking** achieves fault tolerance by hiding faults that occur. Systems that use fault masking do not require fault detection before tolerating them. Fault masking makes faults local. It prevents the effects of faults from spreading throughout the system. Fault masking is a method of achieving fault containment.

Systems that do not use fault masking require **fault detection**, **fault location** and **fault recovery** to achieve fault tolerance. Fault detection is essential to fault location and fault recovery processes. Fault location is required to identify exactly which component is faulty. Fault recovery involves some form of reconfiguration that is usually accomplished by disabling, either physical or logically, a faulty component and enabling, again either physically or logically, a replacement component.

Before dealing with techniques for achieving fault detection, fault location, fault recovery and fault masking, we are interested in redundancy. Some forms of redundancy are required for all of these techniques.

#### **2.3 REDUNDANCY**

Redundancy is an addition of resources, time, or information beyond what is needed for normal system operation. There are some forms of redundancy, which are listed below.

Hardware redundancy Software redundancy Information redundancy Time redundancy

Hardware redundancy is an addition of extra hardware beyond what is needed to perform a given function. Software redundancy is the addition of extra software, beyond what is needed to perform a given function. Information redundancy is an addition of extra information beyond that required to implement a given function. Time redundancy is the usage of additional time to perform the functions of a system [1].

#### 2.3.1 HARDWARE REDUNDANCY

There are three forms of hardware redundancy that are **passive**, **active**, and **hybrid** [1]. Passive techniques use fault masking. Passive approaches are designed to achieve fault tolerance without requiring any action on any part of the system.

Active techniques (dynamic methodologies) achieve fault tolerance by detecting the existence of faults and performing some actions to remove the faulty hardware from the system. In other words, active hardware redundancy uses fault detection, fault location, and fault recovery to achieve fault tolerance.

Hybrid techniques combine the attractive features of both active and passive techniques.

#### 2.3.1.1 PASSIVE HARDWARE REDUNDANCY

Most of the passive approaches are developed around the concept of majority voting. In passive approaches, fault detection and system reconfiguration is not required.

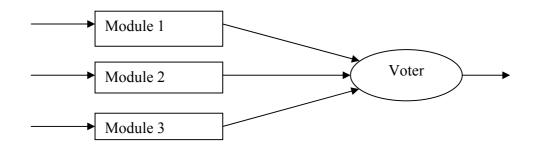

#### **Triple Modular Redundancy (TMR)**

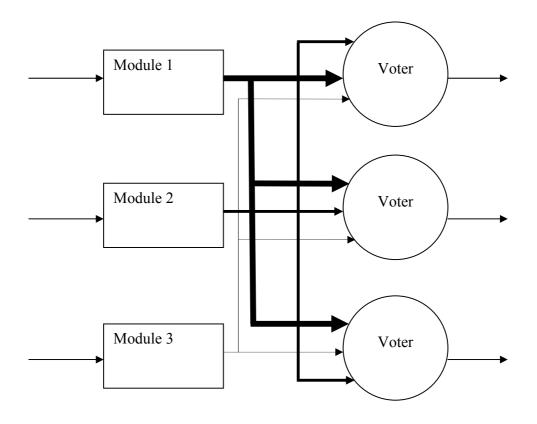

TMR uses triplication of the hardware and it performs majority vote to determine the system output. Block diagram of TMR is shown in Figure 2.4.

Figure 2.4 Block diagram of TMR

If one of these modules becomes faulty, other two modules mask the fault by a majority voting mechanism.

If the voter fails, the complete system fails. This must be prevented. This can be achieved by increasing number of voters as shown in Figure 2.5. If there are 3 voters, receiver side must have 3 input channels to get information from fault tolerant module. Receiver side needs voter circuit to get information.

Figure 2.5 Block diagram of TMR with three voter circuit

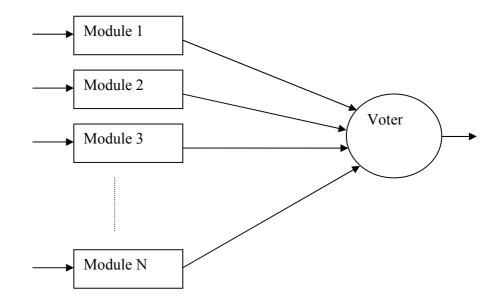

#### N-Modular Redundancy (NMR)

NMR is the generalization of the TMR approach. It uses same principles but number of modules is not three. N is chosen as an odd number to use majority vote arrangement.

By using NMR, more module faults can be tolerated. Block diagram of NMR is shown in Figure 2.6.

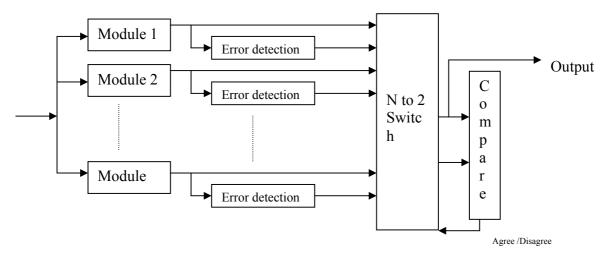

Figure 2.6 Block Diagram of NMR

#### 2.3.1.2 ACTIVE HARDWARE REDUNDANCY

Active hardware redundancy techniques achieve fault tolerance by fault detection, fault location and fault recovery. This approach does not try to prevent faults from producing errors. So that, active hardware redundancy is common in applications that can be tolerated temporary.

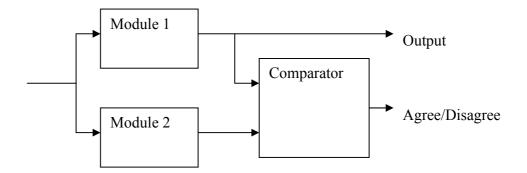

#### **Duplication with Comparison**

In this scheme, two modules operate in parallel and their results are compared. If they are different, an error message is generated. This is fundamental fault detection technique in an active redundancy approach. Block diagram of duplication with comparison is shown in Figure 2.7.

Figure 2.7 Block diagram of duplication with comparison

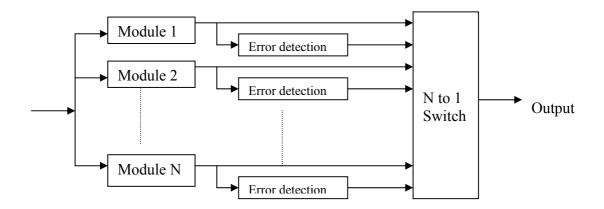

#### Standby Sparing (Standby replacement)

In standby sparing, one of n modules is used to provide the system's output, and the remaining n-1 modules serve as spares. Error detection techniques identify faulty modules so that a fault-free module is always selected to provide the system's output. Block diagram of standby sparing is shown in Figure 2.8.

Figure 2.8 Block diagram of standby sparing

#### Pair-and-a-Spare Technique

It combines the features of both standby and duplication with comparison techniques. Block diagram of pair-and-a-spare technique is shown in Figure 2.9.

In Pair-and-a-Spare Technique, two of n modules are used to provide inputs to the compare circuit, and the remaining n-2 modules serve as spares. If compare circuit gives disagree output, these two modules are identified as faulty modules and another two modules are selected to provide inputs to the compare circuit.

Figure 2.9 Block diagram of pair-and-a-spare technique

#### 2.3.1.3 HYBRID HARDWARE REDUNDANCY

Hybrid hardware redundancy combines the attractive features of both the active and the passive approaches. By fault masking, it tries to prevent erroneous results. Fault detection, fault location, and fault recovery are used to reconfigure the system in the event of a fault. Hybrid redundancy is very expensive in terms of hardware required to implement a system.

#### 2.3.2 SOFTWARE REDUNDANCY

Software redundancy is an addition of extra software, beyond what is needed to perform a given function.

## 2.3.2.1 CONSISTENCY CHECKS

It uses priori knowledge about the characteristics of information to verify correctness of this information.

Example: In processor system, each sensor's output is in some range. These outputs can be checked for correctness by the software.

#### 2.3.2.2 CAPABILITY CHECKS

It is performed to verify that a system processes the capability expected. Example: Memory test, ALU test, processor communication test.

#### 2.3.2.3 N-VERSION PROGRAMMING

Up to now, we deal with software to detect faults occur in hardware. Software faults are the result of incorrect software designs or coding mistakes. So, simple duplication and comparison technique will not detect software faults. Design mistake will appear in both modules.

N-version programming is developed for software fault tolerance. Same functional software module is programmed by N different programmers. Hopefully all of them don't do the same mistake. Then outputs are compared. And fault can be detected easily.

## **CHAPTER 3**

# **FPGA FAULT TOLERANCE**

#### 3.1 FPGA

Field programmable gate array (FPGA) is a general purpose integrated circuit. Application specific integrated circuit (ASIC) performs similar functions but it can not be reprogrammed. FPGA can be reprogrammed after it has been deployed into a system. It is programmed by FPGA system designer.

It is programmed by downloading configuration data (bit stream) into static on-chip random-access memory. This configuration data is the product of compilers. These compilers translate the high level abstractions produced by FPGA system designer into something equivalent but low level and executable code. There are many compilation tools in the industry. Most popular of them are Precision, Leonardo Spectrum and XST [14].

FPGAs are high performance signal processing devices. They provide to construct highly parallel architectures for processing signal. FPGA performance is derived from this ability. Microprocessor or DSP processor performance is tied to the clock rate at which the processor can run, but, FPGA performance is tied to the amount of parallelism to implement algorithms making up a signal processing system. Now, FPGAs can operate up to clock frequencies of 500 mega hertz. It seems to be slow, but FPGAs operate with parallelism. FPGA and DSP represent two very different approaches to signal processing. Each one is good at different things. There are many high sampling

rate applications that FPGA can do easily, while DSP can not. Equally, there are many complex software problems that FPGA cannot address. As a result, the ideal system is often splits the work between FPGAs and DSPs [15].

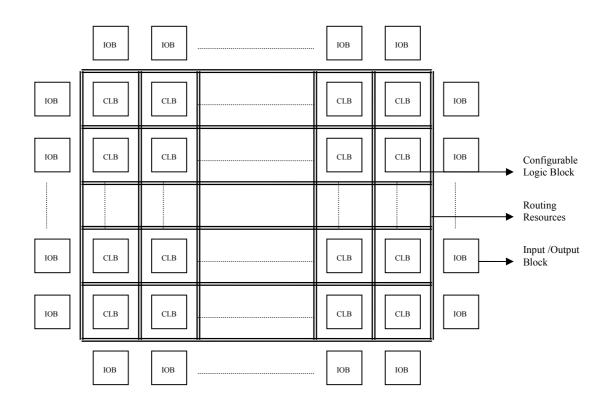

FPGAs are implemented with a regular, flexible programmable architecture of configurable logic blocks (CLBs), interconnected by versatile routing resources (routing channels), and surrounded by programmable input/output blocks (IOBs), as seen in Figure 3.1 [5]. This implementation is a basic structure; some FPGA families have extra components such as, dedicated multipliers, dual port memories, digital clock managers, etc...

Figure 3.1 FPGA structure

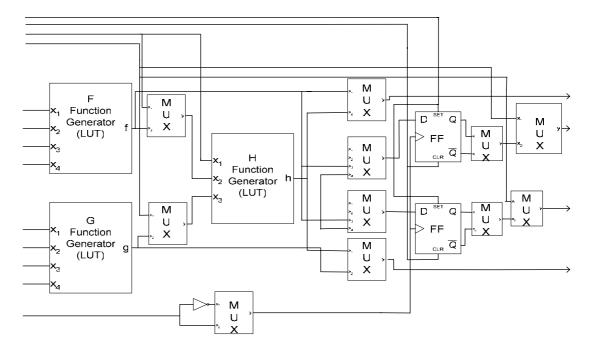

Most of the logic in FPGA is implemented by configurable logic blocks. Internal structure of CLBs changes with FPGA family and FPGA manufacturer. Basic diagram of CLB for XC4000 family Xilinx FPGA that is used in this thesis is shown in Figure 3.2. There are two 4-input function generators (Function generator is called as look-up table (LUT) in some documents.) which are labeled as F and G in Figure 3.2 [6]. Third function generator (H) is also provided. H function generator has three inputs as shown in Figure 3.2.

Each CLB contains two storage elements (d type flip-flops (ff)) that can be used to store function generator outputs and direct inputs coming from outside the CLB as shown in Figure 3.2.

Thirteen CLB inputs and four CLB outputs provide access to the function generators and storage elements. These inputs and outputs connect to the programmable interconnect resources outside the CLB.

Figure 3.2 Configurable Logic Block Structure

There are 13 FPGA producers today. They are listed below.

Actel Corporation Altera Corporation AMI Semiconductor Amphion Semiconductor, Inc. Aptix Corporation Atmel Corporation Kawasaki LSI U.S.A., Inc. Nallatech, Inc. Nallatech, Inc. Pentek, Inc. SiQUEST, Inc. Tekmos, Inc. Transtech Parallel Systems Xilinx, Inc.

#### **3.2 SINGLE EVENT UPSET (SEU)**

Fault tolerance on digital circuits has been a meaningful matter since upsets were first experienced in space applications. The digital circuits located in the space environment are affected by the charged particles, which are generated by the solar flares. Charged particles can provoke a transient pulse, when it hits the silicon. This pulse can change the state of a memory cell. This phenomenon is known as a Single Event Upset (SEU). A charged particle can also hit the combinational logic. This generates current pulse. This pulse may be propagated by the combinational logic and latched by memory cells. This event also causes SEU [2] [3].

Integrated circuits are becoming more sensitive to radiation effects. High density devices require smaller feature size, this means less capacitance and hence information

is stored with less charge. Lower voltage or lower power devices mean that less charge or current is required to store information.

Due to these requirements, integrated circuits become much more vulnerable.

FPGAs are composed of an array of configurable logic blocks (CLBs) surrounded by programmable input/output blocks (IOBs). All of them are interconnected by routing resources. The CLBs provide functional elements for constructing logic. The IOBs provide the interface between the package pins and the CLBs. The CLBs are interconnected through a general routing matrix (GRM) that comprises an array of routing switches located at the intersections of horizontal and vertical routing channels.

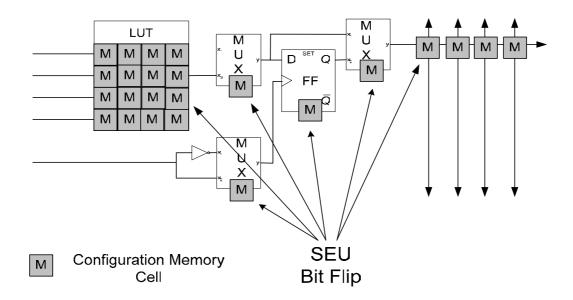

FPGAs are programmed using a bit stream, which contains all the information to configure the programmable storage elements in the matrix located in the Look-up Tables (LUT) and flip-flops (ff), CLBs configuration cells and interconnections. All these configuration bits are potentially sensitive to SEU. Figure 3.3 shows programmable storage elements.

**Figure 3.3 Programmable Storage Elements**

## 3.3 FPGA FAULT TOLERANCE TECHNIQUES FOR TOLERATING SEU

There are some FPGA fault tolerance techniques for tolerating SEU. These techniques are explained below.

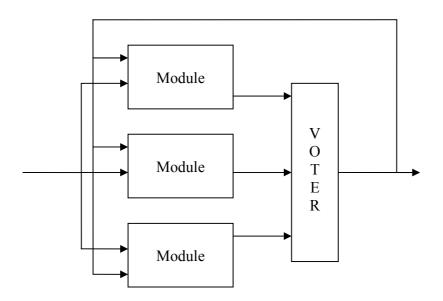

Most common SEU mitigation method is Triple Modular Redundancy (TMR) with voting circuit. TMR uses three identical circuits, which perform the same task in parallel. Their outputs are compared through a majority voter circuit. TMR can be applied at module level or at device level [4] [7].