## DESIGN AND IMPLEMENTATION OF FIR DIGITAL FILTERS WITH VARIABLE FREQUENCY CHARACTERISTICS

A THESIS SUBMITTED TO

#### THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

OF

#### MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

HATİCE PİŞKİN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2005

Approval of the Graduate School of Natural and Applied Sciences

Prof. Dr.Canan ÖZGEN Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science

Prof. Dr.İsmet ERKMEN

Head of the Department

This is to certify that we have read this thesis and in our opinion it is fully adequate, in scope and quality, as a thesis for a degree of Master of Science.

Prof. Dr. Zafer ÜNVER Supervisor

**Examining Committee Members**

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Hatice PİŞKİN

Signature :

## ABSTRACT

## DESIGN AND IMPLEMENTATION OF FIR DIGITAL FILTERS WITH VARIABLE FREQUENCY CHARACTERISTICS

PİŞKİN, Hatice

M.S., Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. Zafer ÜNVER

December 2005, 85 pages

Variable digital filters (VDF) find many application areas in communication, audio, speech and image processing. This thesis analyzes design and implementation of FIR digital filters with variable frequency characteristics and introduces two design methods. The design and implementation of the proposed methods are realized on Matlab software program. Various filter design examples and comparisons are also outlined.

One of the major application areas of VDFs is software defined radio (SDR). The interpolation problem on sample rate converter (SRC) unit of the SDR is solved by using these filters. Realizations of VDFs on SRC are outlined and described. Simulations on Simulink and a specific hardware are examined.

**Keywords**: Variable digital filter, least squares, software defined radio, sample rate converter, interpolation.

# ÖZ

## DEĞİŞKEN FREKANS KARAKTERİSTİKLİ FIR FİLTRE TASARIMI VE UYGULAMASI

PİŞKİN, Hatice Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Prof. Dr. Zafer ÜNVER

Aralık 2005, 85 Sayfa

Değişken frekans karakteristikli sayısal filtreler haberleşme, ses ve görüntü işleme çalışmalarında uygulama alanları bulmaktadır. Bu tez çalışmasında değişken frekans karakteristikli FIR filtre tasarımı ve uygulaması çözümlenmiş ve gerçeklenmiştir. Filtre tasarımı iki farklı yöntem kullanılarak Matlab yazılımı üzerinde uygulanmıştır. Çeşitli filtre tasarımları örnek olarak verilmiş ve karşılaştırılmıştır.

Değişken frekans karakteristikli filtrelerin en önemli uygulama alanlarından biri yazılım tanımlı radyodur. Yazılım tanımlı radyonun örnekleme hızı çeviricisi biriminde görülen enterpolasyon problemi bu tür filtreler kullanılarak çözülebilmektedir. Değişken frekans karakteristikli filtrelerin, örnekleme hızı çeviricisindeki kullanımı tanımlanmıştır. Simulink programı üzerindeki benzetimler ve belirli bir donanım üzerinde elde edilen sonuçlar incelenmiştir.

Anahtar Kelimeler: Değişken sayısal süzgeç, en az kareler, yazılım tanımlı radyo, örnekleme hızı çeviricisi, enterpolasyon.

# ACKNOWLEDGEMENTS

I appreciate Prof. Dr.Zafer Ünver for his guidance, support and valuable contributions throughout the study.

I express my deepest gratitude to my mother, my father and my brother for their trust and encouragements throughout my education life.

# **TABLE OF CONTENTS**

| PLAGIA  | RISM    |                                                    | III        |

|---------|---------|----------------------------------------------------|------------|

| ABSTRA  | ст      |                                                    | IV         |

| ÖZ      | •••••   |                                                    | V          |

| ACKNO   | WLEDG   | EMENTS                                             | VI         |

| TABLE   | OF CON  | TENTS                                              | VIII       |

| LIST OF | TABLE   | ES                                                 | X          |

|         |         | ES                                                 |            |

| CHAPTI  |         |                                                    |            |

| INTROE  | ουςτιο  | N                                                  | 1          |

| 1.1     | Intro   | DUCTION                                            | 1          |

| 1.2     | Studi   | ES CARRIED OUT IN THIS THESIS                      | 4          |

| 1.3     | OUTLI   | NE OF THE THESIS                                   | 5          |

| VARIAB  | BLE FIR | FILTER DESIGN WITH DIRECT INTEGRATION METHOD       | 6          |

| 2.1     | Gener   | RAL                                                | 6          |

| 2.2     | DESIG   | N METHOD                                           | 6          |

| 2.3     | ILLUS   | frative Examples                                   | 10         |

| 2.3.    | 1 Tur   | nable Linear-Phase FIR Low-Pass Filter             |            |

| -       | 2.3.1.1 | Mathematical Derivations                           |            |

|         | 2.3.1.2 | Design Results and Comparisons                     |            |

| 2.3.    | 2 Tur   | nable Linear-Phase Band-Pass Filter                | 17         |

|         | 2.3.2.1 | Mathematical Derivations                           |            |

| 2       | 2.3.2.2 | Design Results and Comparisons                     |            |

| 2.3.    | 3 Tur   | nable Fractional Delay Low-Pass FIR Digital Filter | 22         |

|         | 2.3.3.1 | Mathematical Derivations                           |            |

| -       | 2.3.3.2 | Design Results and Comparisons                     |            |

|         |         | FILTER DESIGN WITH SINGULAR VALUE BASED VECTOR     |            |

| DECOM   | rusifi  | ON METHOD                                          | <i>L</i> 1 |

| 3.1   | Gen          | NERAL                                                     |                  |

|-------|--------------|-----------------------------------------------------------|------------------|

| 3.2   | DES          | SIGN METHOD                                               |                  |

|       | 3.2.1        | Vector Array Decomposition Algorithm                      |                  |

| 3.3   | ILLU         | USTRATIVE EXAMPLES                                        |                  |

|       | 3.3.1        | Tunable Linear-Phase Low-Pass FIR Filter                  |                  |

| 3.4   | Compari      | ISON OF DIRECT INTEGRATION AND SINGULAR VALUE DECOMPOSITI | ION BASED VECTOR |

| Arf   | RAY DECO     | OMPOSITION METHODS                                        |                  |

| APPL  | ICATIO       | N ON SOFTWARE DEFINED RADIO                               | 40               |

| 4.1   | Gen          | NERAL                                                     |                  |

| 4.2   | SOF          | TWARE DEFINED RADIO DESCRIPTION                           |                  |

| 4.3   | SOF          | FTWARE SIMULATIONS                                        |                  |

|       | 4.3.1        | Simulink Model of Proposed Method                         |                  |

|       | 4.3.2        | Simulink Model of Traditional Method                      |                  |

|       | 4.3.3        | Simulation Results                                        |                  |

| 4.4   | Wo           | DRK ON RAD-2                                              | 58               |

| CONC  | LUSIO        | N                                                         | 66               |

| 5.1   | Con          | NCLUSION                                                  | 66               |

| 5.2   | Pro          | DPOSED FUTURE WORK                                        | 67               |

| REFE  | RENCE        | S                                                         | 68               |

| APPE  | NDIX         |                                                           |                  |

| A. RA | D-2 HAI      | RDWARE SPECIFICATION                                      | 71               |

|       | <b>D</b> 4 3 |                                                           |                  |

|     |                                              | -  |

|-----|----------------------------------------------|----|

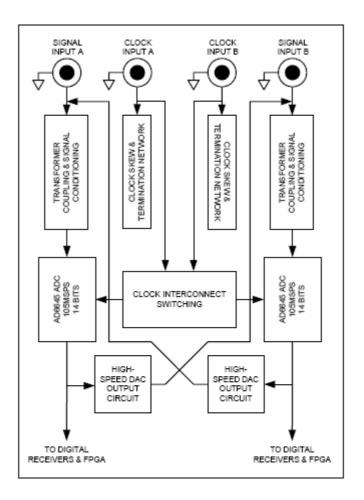

| A.1 | RAD-2 ANALOG INPUT AND ACQUISITION SUBSYSTEM | 72 |

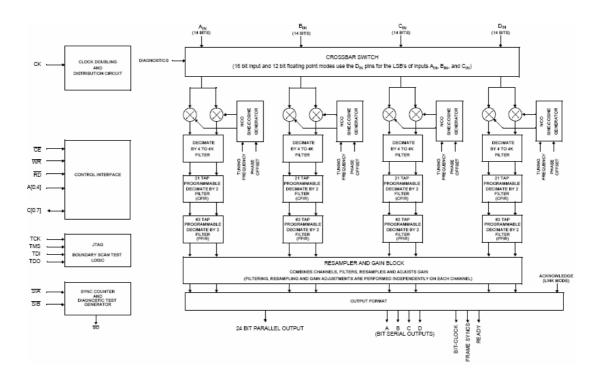

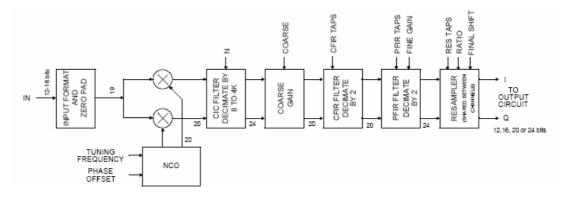

| A.2 | RAD-2 DIGITAL DOWNCONVERSION SUBSYSTEM       | 74 |

| A.3 | RAD-2 FLOW CONTROL                           | 83 |

| A.4 | RAD-2 DATA MANAGEMENT AND BUFFERING          | 84 |

| A.5 | RAD-2 PMC INTERFACE                          | 84 |

|     |                                              |    |

# LIST OF TABLES

| Table 2-1 Parameters for tunable low pass filter.    13                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2-2 Characteristic values for tunable low pass filter for various values of $K_p$ ; for Ks = 1, Filter order = 10, Interpolation order = 3, $\phi = 0$                                   |

| Table 2-3 Characteristic values for tunable low pass filter for various values of K <sub>s</sub> ; for Kp = 1, Filter order = 10, Interpolation order = 3, $\phi = 0$                          |

| Table 2-4 Characteristic values for tunable low pass filter for various values of filter order; for Kp = 1000, Kp = 1000, Interpolation order = 3, $\phi = 0$                                  |

| Table 2-5 Characteristic values for tunable low pass filter for various values of interpolation order; for Kp = 1000, Kp = 1000, Filter order = 31, $\phi = 0$ 16                              |

| Table 2-6 Parameters for tunable band pass filter                                                                                                                                              |

| Table 2-7 Characteristic values for tunable band pass filter for various values of filter order; for Kp = 1000, Kp = 1000, Interpolation order = 3, $\phi = 0$ , w <sub>c</sub> = 0.5 $\pi$ 20 |

| Table 2-8 Characteristic values for tunable low pass filter for various values of interpolation order; for Kp = 1000, Kp = 1000, Interpolation order = 31, $\phi = 021$                        |

| Table 2-9 Parameters for tunable fractional delay low pass filter.    24                                                                                                                       |

| Table 2-10 Characteristic values for tunable fractional delay filter for various values of filter order; for Kp = 1000, Kp = 1000, Interpolation order = 3, $\phi = 0$ 24                      |

| Table 2-11 Characteristic values for tunable fractional delay filter for various values                                                                                                        |

of interpolation order; for Kp = 1000, Kp = 1000, Filter order = 31,  $\phi = 0$ .....25

Table 3-2 Characteristic values for tunable low pass filter for various values of filter order; for frequency band sample points = 500, Interpolation order = 3,  $\phi = 0$ . ...... 37

# LIST OF FIGURES

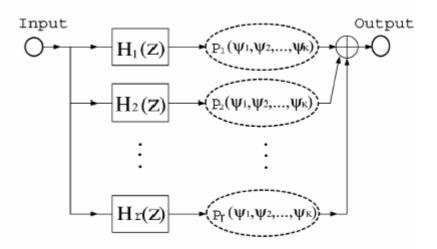

| Figure 2.1 Proposed variable digital filter structure                               | 8    |

|-------------------------------------------------------------------------------------|------|

| Figure 2.2 Frequency response of variable lowpass FIR linear phase filter even      |      |

| sampled in range $\phi = [0,1]$ .                                                   | . 17 |

| Figure 2.3 Frequency response of variable bandpass FIR linear phase filter even     | -    |

| sampled in the range $\phi = [0,1]$ .                                               | . 22 |

| Figure 2.4 Group delay response of variable lowpass FIR filter evenly sampled       |      |

| range $\phi = [-0.5, 0.5]$                                                          | . 26 |

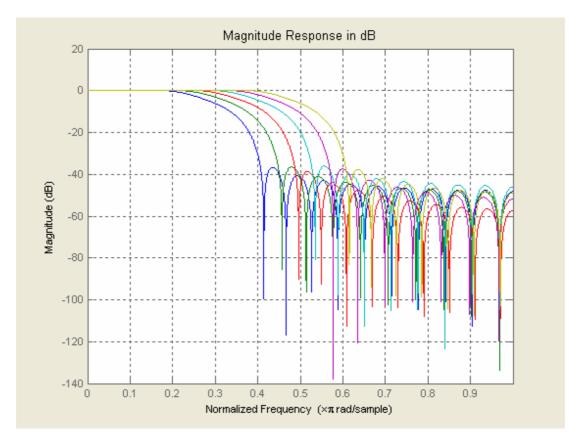

| Figure 3.1 Proposed vector array decomposition based filter structure               | . 30 |

| Figure 3.2 Frequency response of variable lowpass FIR linear phase filter even      | nly  |

| sampled in the range $\phi = [0,1]$ .                                               | -    |

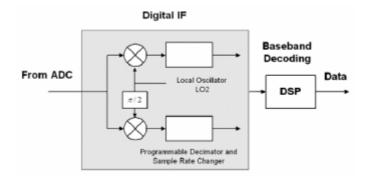

| Figure 4.1 Conventional software defined radio receiver structure                   | . 42 |

| Figure 4.2 Conventional programmable decimator and sample rate converter            | . 42 |

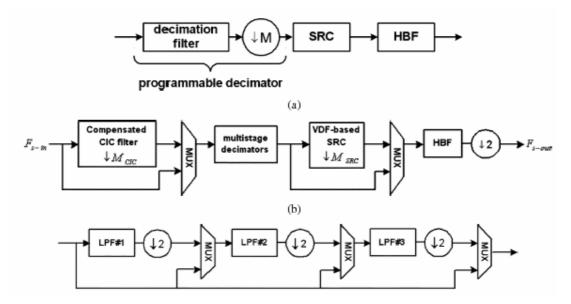

| Figure 4.3 (a) Proposed architecture of the programmable decimator and sample r     | rate |

| converter, (b)Architecture of the proposed software radio receiver, (c)Architecture | e of |

| the multistage decimators                                                           | . 43 |

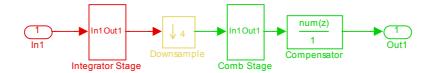

| Figure 4.4 Simulink CIC Stage.                                                      | . 44 |

| Figure 4.5 Integrator Stage of CIC                                                  | . 45 |

| Figure 4.6 CombStage of CIC                                                         | . 45 |

| Figure 4.7 Simulink Implementation of Proposed Method                                                 | . 46 |

|-------------------------------------------------------------------------------------------------------|------|

| Figure 4.8 Simulink Multistage Decimator Stage                                                        | . 46 |

| Figure 4.9 Simulink Implementation of Traditional Method                                              | . 48 |

| Figure 4.10 Output Data for Proposed Method for Fractional Delay of 0.15                              | . 49 |

| Figure 4.11 Magnitude of FFT of Output Data for Proposed Method for Fractio Delay of 0.15.            |      |

| Figure 4.12 Output Data for Traditional Method for Fractional Delay of 0.15                           | . 51 |

| Figure 4.13 Magnitude FFT of Output Data for Traditional Method for Fractio Delay of 0.15.            |      |

| Figure 4.14 Difference of Output Data of Traditional and Proposed Methods<br>Fractional Delay of 0.15 |      |

| Figure 4.15 Output Data for Proposed Method for Fractional Delay of 0.5                               | . 54 |

| Figure 4.16 Magnitude of FFT of Output Data for Proposed Method for Fractio Delay of 0.5.             |      |

| Figure 4.17 Output Data for Traditional Method for Fractional Delay of 0.5                            | . 56 |

| Figure 4.18 Magnitude of FFT of Output Datafor Traditional Method for Fractio Delay of 0.5.           |      |

| Figure 4.19 Difference of Output Data of Traditional and Proposed Methods Fractional Delay of 0.5.    |      |

| Figure 4.20 RAD-2 and PCI to PMC Card Assembly (Front Side)                                           | . 60 |

| Figure 4.21 RAD-2 and PCI to PMC Card Assembly (Back Side).                                           | . 61 |

| Figure 4.22 SMC to BNC Connection.                                                                    | . 62 |

| Figure 4.23 Custom Driver Program Snapshot.                                                           | . 62 |

| Figure 4.24 PCI Card Message Snapshot                                                                 | . 63 |

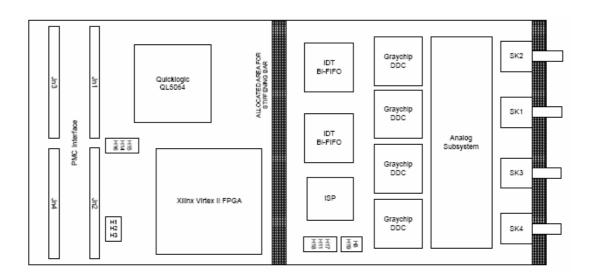

| Figure A.1 Funcional Block Diagram of RAD-2                                                           | . 71 |

| Figure A.2 Board layout of RAD-2.                   | 72 |

|-----------------------------------------------------|----|

| Figure A.3 Input Conditioning Diagram of RAD-2      | 73 |

| Figure A.4 Block Diagram of GC4016.                 | 75 |

| Figure A.5 Block Diagram of Down Converter Channel. | 76 |

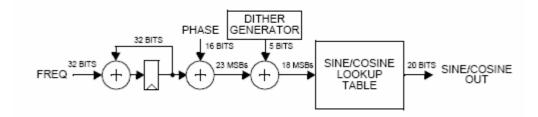

| Figure A.6 NCO Block Diagram.                       | 77 |

| Figure A.7 Block Diagram of CIC filter.             | 78 |

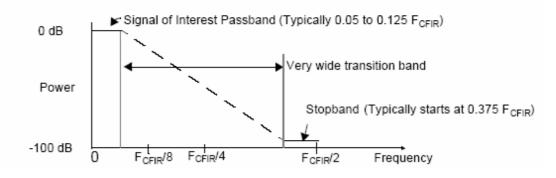

| Figure A.8 CFIR Specifications                      | 79 |

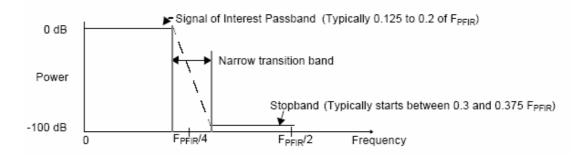

| Figure A.9 PFIR Specifications.                     | 79 |

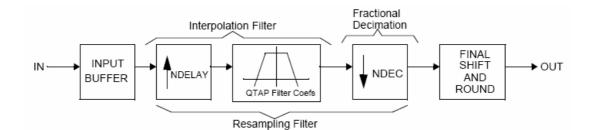

| Figure A.10 Resampler Channel Block Diagram.        | 81 |

| Figure A.11 Resampler's Spectral Response           | 82 |

| Figure A.12 RAD-2 ADC to Graychip Connection        | 83 |

## **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 Introduction

Variable digital filters are digital filters with controllable spectral characteristics such as variable cutoff frequency response, adjustable pass band width, controllable fractional delay, etc. They have been found useful in various signal processing applications such as telecommunication, audio, speech, and image processing, where the frequency response of digital filters are required to be adjustable. Generally, variable digital filters can be classified into two main categories. The first one includes the digital filters with variable magnitude responses such variable filters can be efficiently utilized for implementing variable filters with variable phase response especially those with variable fractional-delay responses, which are widely useful in the applications such as timing adjustment in digital receiver, speech coding and synthesis, reduction of channel timing-error effects in time-interleaved analog-to-digital converters, and other applications, whenever new sample values at arbitrary time instants between the existing discrete-time samples need to be interpolated. [6], [7], [10], [11], [12], [13].

Methods for designing variable digital filters can be broadly classified into two categories: transformation [9], and spectral parameter approximation [8] methods. In the former, a prototype filter with certain design characteristics is first designed. Certain transformations such as the all pass transformation method is then applied to the prototype filter to obtain the final variable digital filter. In general, transformation method is applicable to variable digital filters with variable cutoff frequencies; it is not applicable for variable characteristics such as variable fractional delay. Additionally, if the filter is infinite impulse response type, these kinds of transformations may produce delay-free loops in the filter structure, which cannot be implemented digitally.

The spectral parameter method is more general in the sense it assumes that either the impulse responses or the poles and zeros of the filters are polynomials of certain spectral parameters. Typically, the transfer function of a variable digital filter contains a number of spectral parameters that can be used to tune the frequency response of the digital filter. Thus the main objective in the design of a variable digital filter is to find a parameterized transfer function which in a certain sense best approximates a given set of frequency response characteristics that vary with the parameters in a desired manner. The spectral parameter method was proposed by Zaraour and Fahmy [8] where the poles and zeros of an infinite impulse response filter are assumed to be polynomials of the spectral or tuning parameters. The proposed method utilizes a nonlinear optimization method to design a set of digital filters corresponding to the sampled variable frequency domain characteristics. Then the coefficients of a general variable digital filter are assumed to be multidimensional polynomials of spectral parameters such as cutoff frequency, pass band width and transition band width, which define the frequency domain characteristics, and the optimal multidimensional coefficient polynomials are found to best fit the fixed filter coefficients determined before by using a nonlinear optimization method. In practical applications, once the spectral parameters are given, the coefficients of the variable filter can be readily calculated from the determined multidimensional polynomials. However, the technique has two drawbacks; since many fixed constant digital filters have to be designed first by using a nonlinear optimization method, and then a lot of multidimensional polynomials have to be approximated, the technique is not computationally efficient. Moreover, since the denominator coefficients of the designed variable digital filters are also multidimensional polynomials of a set of spectral parameters and are varied during the course of signal processing, the stability of variable filters cannot be guaranteed.

Most of the works on variable digital filters reported after Zaraour and Fahmy's method focused on the design of infinite impulse response variable digital filters and the methods for guaranteeing their stability. More recently the design of variable finite impulse response digital filters has received considerable attention due to their simple design procedure and good filtering performance. Among the design methods developed for finite impulse response variable digital filters defined by spectral parameters, the Lagrange multiplier method seems to be the most attractive due to its simplicity, but the frequency response of the resulting Lagrange interpolator cannot be uniformly balanced in the entire frequency band, i.e., the frequency response in the low-frequency region is superior to that in the high-frequency region. Thus it is difficult to achieve a satisfactory design with low filter orders in the whole frequency band by using the Lagrange multiplier method. To solve this problem, a general technique using the weighted least squares method is proposed, which can yield a more satisfactory design with lower order than the Lagrange interpolator. Design of finite impulse response variable digital filters is generalized to a linear combination of basis functions. Optimal least squares solution can also be obtained by solving a system of linear equations. The resulting variable digital filters can be implemented using the Farrow [14] structure.

Another direct method for designing finite impulse response variable digital filters is the weighted least squares method, which assumes that the variable filter coefficients are multidimensional polynomials of the spectral parameters, and then the optimal polynomial coefficients are determined through minimizing the weighted squarederror between the desired and actual variable frequency responses. However, the computational complexity of the weighted least squares design is rather heavy especially when the number of the spectral parameters increases. Moreover, the discretization of frequency band is required during the computations.

If only the pass band linear-phase characteristics is required, optimal design problem can be formulated as a semi definite programming problem, which is a versatile framework for designing finite and infinite impulse response filters. Although the design time required for semi definite programming is more than that of the least squares case, the method is considerable since it offers lower system delay in the pass band.

As an application area of variable digital filters software defined radio takes more attention nowadays. Software defined radio is a general hardware/software platform for supporting inter-communication systems. Sample rate converter units are employed in software defined radios to isolate the desired user's channel from the signal spectrum and convert to an appropriate sampling rate for further processing. Sample rate converter unit can be realized by variable digital filters which reduces the implementation complexity of the software defined radio system.

### **1.2 Studies Carried Out in This Thesis**

Throughout this thesis previous studies on design and implementation of finite and infinite impulse response digital filters are examined in detail. After gaining knowledge by this literature survey, various methods for the design of variable finite impulse response are implemented. These methods are investigated and compared for various design criteria. Illustrative examples for various filter types are studied and corresponding frequency responses are given.

Implementation areas for variable digital filters are investigated; and in particular implementation on software defined radio is studied.

Hardware implementation of variable digital filters on software defined radio is investigated. Comparison between the traditional, and the proposed hardware structures is made.

### **1.3** Outline of the Thesis

Introduction for this thesis is given within this chapter (Chapter1) in which the general information about variable digital filters, previous studies and the objectives for this thesis are stated.

In Chapter 2, the variable finite impulse response digital filter design with direct integration method is described. Mathematical derivations and illustrative examples are given.

In Chapter 3, the variable finite impulse response digital filter design with singular value decomposition based vector array decomposition method is described. Mathematical derivations and illustrative examples are given.

In Chapter 4, the variable digital filter application on software defined radio application is considered. A brief information about software defined radio is given. Variable filter application on the software defined radio is described. The hardware implementation on software defined radio is investigated. The advantage of usage of the variable digital filters on software defined radio is outlined and the comparison of the traditional and the proposed methods is given.

Conclusion is given in Chapter 5.

## **CHAPTER 2**

# VARIABLE FIR FILTER DESIGN WITH DIRECT INTEGRATION METHOD

### 2.1 General

In this chapter variable finite impulse response (FIR) filter design by direct integration method is described. Mathematical derivations for this method are outlined. Illustrative examples for variable low pass, band pass and fractional delay filters and design results for these types of filters are given.

### 2.2 Design Method

The parameters that used to change spectral, frequency, characteristics of the filters are called spectral parameters. In spectral parameter method, the impulse response or the poles and the zeros of the variable digital filters (VDF) are assumed to be a polynomial function of the tuning parameters. Since direct tuning of the poles and zeros yields undesirable transient response during tuning, tuning of impulse response will be considered.

The impulse response of the variable FIR digital filter  $h(n, \Phi)$  is assumed to be a linear combination of functions  $\psi_m(\Phi)$  of the spectral parameters  $\Phi$ ,

$$h(n, \Phi) = \sum_{m=0}^{M-1} c_{m}[n] \psi_{m}(\Phi)$$

(2.1-a)

where

$$\psi_{\rm m}(\Phi) = a + b\phi + c\phi^2 + ...$$

(2.1-b)

$c_m[n]$ 's are the coefficients of expansion. The design objective is to determine  $c_m[n]$  given  $\psi_m(\Phi)$  so that the frequency response  $h(n, \Phi)$  will approximate the desired frequency responses as a function of  $\Phi$ .

The z-transformation of the specified variable digital FIR filter of length N is,

$$H(z,\phi) = \sum_{n=0}^{N-1} h(n,\phi) z^{-n} = \sum_{n=0}^{N-1} \sum_{m=0}^{M-1} c_m [n] \psi_m(\phi) z^{-n}$$

(2.2)

Interchanging the order of summations, the above equation can be rewritten as

$$H(z,\phi) = \sum_{m=0}^{M-1} C_m(z) . \psi_m(\phi)$$

(2.3-a)

where

$$C_{m}(z) = \sum_{m=1}^{N-1} c_{m}[n] z^{-n}$$

(2.3-b)

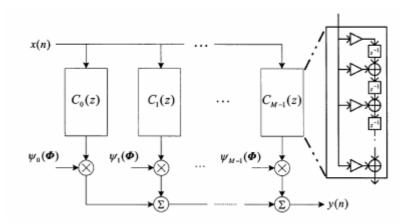

(2.3-a) can be implemented by the structure shown in Figure 2.1.

Figure 2.1 Proposed variable digital filter structure.

This structure can be viewed as a generalization of the Farrow structure for implementing a fractional delay digital filter where  $h(n, \Phi)$  is approximated by a polynomial in the delay parameter  $\Phi = \phi$ , that is  $\psi_m(\Phi) = \phi^m$ .

If the desired frequency response is  $H_i(e^{jw}, \Phi)$ , then the approximation error is

$$E(w,\phi) = H_{I}(e^{jw},\phi) - \sum_{m=0}^{M-1} \sum_{n=0}^{N-1} c_{m}[n]\psi_{m}(\phi)e^{-jnw}$$

(2.4)

The L<sub>2</sub> norm of  $E(w, \Phi)$  is given by

$$E = \int_{\phi_{s}} \int_{\Omega_{s}} W(e^{jw}, \Phi) |E(w, \Phi)|^{2} dwd \Phi$$

(2.5)

where  $W(e^{jw}, \Phi)$  is a positive weighting function used to control the amount of approximation error in frequency and tuning spaces.  $\Omega_S$  is the frequency support over which  $H_I(e^{jw}, \Phi)$  is to be approximated, and  $\Phi_S$  is the parameter space over which the spectral parameter vector  $\Phi$  is to be varied.

Letting k = n + Nm and  $z = e^{jw}$ , the desired frequency response takes the form

$$H(e^{jw}, \phi) = \sum_{k=0}^{NM-1} a_{k} \phi_{k}(w, \phi)$$

(2.6)

where  $a_k = c_m[n]$  and  $\Phi_k(w, \Phi) = \psi_m(\Phi) e^{-jnw}$ .

Substituting (2.) into (2.5) and simplifying gives

$$E = a^T Q a - 2b^T a + c$$

(2.7)

where

$$a = \begin{bmatrix} a_0 & a_1 & \dots & a_{NM-1} \end{bmatrix}^T$$

$$b = \begin{bmatrix} b_0 & b_1 & \dots & b_{NM-1} \end{bmatrix}^T$$

$$\begin{bmatrix} Q \end{bmatrix}_{ij} = \int_{\phi_s} \int_{\Omega_s} W(e^{jw}, \phi) . \phi_i(w, \phi) \overline{\phi_j(w, \phi)} dw d\phi$$

$$\begin{bmatrix} b \end{bmatrix}_k = \int_{\phi_s} \int_{\Omega_s} W(e^{jw}, \phi) . \operatorname{Re} \{ H_1(e^{jw}, \phi) . \overline{\phi_k(w, \phi)} \} dw d\phi$$

$$c = \int_{\phi_s} \int_{\Omega_s} W(e^{jw}, \phi) . | H_1(e^{jw}, \phi) |^2 dw d\phi$$

Differentiating with respect to 'a' and setting derivatives to zero, one gets the following system of linear equations follows as

$$Q.a_{LS} = b$$

then the optimal least squares solution, aLS

$$a_{LS} = Q^{-1}b$$

(2.9-b)

(2.9-a)

#### 2.3 Illustrative Examples

#### 2.3.1 Tunable Linear-Phase FIR Low-Pass Filter

As an illustrative example, the design of variable cutoff FIR digital filter design is worth considering. Letting the passband cutoff frequency be denoted by  $w_p$  and the stopband cutoff frequency be denoted by  $w_s$ , assuming the passband and stopband cutoff frequencies vary linearly with spectral parameter  $\Phi = \phi$ , the variable passband and stopband cutoff frequencies could be defined as:

$$w_{p}(\phi) = \phi(w_{p2} - w_{p1}) + w_{p1}$$

$$w_{s}(\phi) = \phi(w_{s2} - w_{s1}) + w_{s1}$$

$$\Phi_{s} : \phi \in [0,1]$$

(2.10)

Frequency support of the filter is defined as combination of passband and stopband regions, which are defined by the spectral parameter,

$$\Omega_{s} = \Omega_{p} + \Omega_{s}$$

$$\Omega_{p} = \{ w : w \in (0, w_{p}(\phi)) \}$$

$$\Omega_{s} = \{ w : w \in (w_{s}(\phi), \pi) \}$$

$$10$$

The desired impulse response is denoted by  $H_I(e^{jw}, \phi)$  and defined as:

$$H_{I}(e^{jw}, \phi) = \begin{cases} e^{-j\pi w}, |w| \le w_{p}(\phi) \\ 0, w_{S}(\phi) \le |w| \le \pi \end{cases}$$

(2.12)

where  $\tau$  is the group delay which is assumed to be constant and equal to (N-1)/2 where N is the order of the subfilters.

h(n,  $\phi$ ) is approximated by a polynomial; and the function  $\psi_m(\phi)$  is given by  $\phi^m$ .

The weighting function is defined as

$$W(e^{jw}, \Phi) = \begin{cases} K_{p}, w \in S_{p} \\ K_{s}, w \in S_{s} \end{cases}$$

(2.13)

#### 2.3.1.1 Mathematical Derivations

Letting  $\Phi_i(w,\phi) = \psi_p(\phi)e^{-jnw} = \phi^p e^{-jkw}$  and i = k + Np, j = n + Nm, where N is the order of the subfilters

$$\begin{bmatrix} Q_{ij} \end{bmatrix} = \int_{\Phi_{s}\Omega_{s}} \int_{W} W(e^{jw}, \Phi) \Phi_{i}(w, \Phi) \overline{\Phi_{j}(w, \Phi)} dw d\Phi$$

$$= \int_{\Phi_{s}} \phi^{p+m} \int_{\Omega_{s}} W(e^{jw}, \phi) (\cos((n-k)w) + j\sin((n-k)w)) dw d\phi$$

(2.14)

By considering a symmetrical integration interval since sinus function odd, the sinus term will disappear in the equation. Moreover, since cosines term is an even function, the above equation can be rearranged as follows

$$\begin{split} \left[ Q_{ij} \right] &= 2 \int_{\Phi_s} \phi^{p+m} \left( \int_{0}^{w_p(\phi)} K_p \cos((n-k)w) dw d\phi + \int_{w_s(\phi)}^{\pi} K_s \cos((n-k)w) dw \right) d\phi \\ &= 2 \int_{\Phi_s} \phi^{p+m} \left( \frac{K_p}{(n-k)} \sin((n-k)w_p(\phi)) dw d\phi - \frac{K_s}{(n-k)} \sin((n-k)w_s(\phi)) \right) d\phi \end{split}$$

(2.15)

If n=k the above equation will take the form,

$$\left[\mathbf{Q}_{ij}\right] = 2 \int_{\Phi_s} \phi^{p+m} (\mathbf{K}_p \mathbf{w}_p(\phi)) + \mathbf{K}_s (\pi - \mathbf{w}_s(\phi))) d\mathbf{w} d\phi)$$

(2.16)

where  $w_{p}(\phi)$ ,  $w_{s}(\phi)$  and  $\Phi_{s}$  are defined by (2.10).

Similarly,

$$\begin{bmatrix} \mathbf{b} \end{bmatrix}_{i} = \int_{\phi_{s}} \int_{\Omega_{s}} \mathbf{W}(\mathbf{e}^{jw}, \mathbf{\Phi}) \cdot \mathbf{Re} \{ \mathbf{H}_{I}(\mathbf{e}^{jw}, \mathbf{\Phi}) \cdot \overline{\phi_{i}(w, \mathbf{\Phi})} \} dw d\mathbf{\Phi}$$

$$= 2 \int_{\phi_{s}} \phi^{p} \frac{\mathbf{K}_{p}}{(\mathbf{k} - \tau)} \sin((\mathbf{k} - \tau) \mathbf{w}_{p}(\phi)) d\phi$$

(2.17)

If  $k = \tau$  the above equation will take the form

$$\left[\mathbf{b}\right]_{i} = 2 \int_{\phi_{s}} \phi^{p} \mathbf{K}_{p} \mathbf{w}_{p}(\phi) \mathrm{d}\phi$$

(2.18)

where  $w_{p}(\phi)$  and  $\Phi_{s}$  are defined by (2.10).

Putting (2.15), (2.16), (2.17) and (2.18) into (2.9) gives weighted least squares solution for variable FIR digital filter with Farrow structure shown in Figure 2.1.

#### 2.3.1.2 Design Results and Comparisons

For evaluation of proposed method a variable lowpass filter with the specifications given in Table2-1 is designed.

| Specification                    | Value              |

|----------------------------------|--------------------|

| Spectral Parameter ( $\phi$ )    | $0 \le \phi \le 1$ |

| Passband Edge1( $w_{p1}(\phi)$ ) | $0.2\pi$           |

| Passband Edge2( $w_{p2}(\phi)$ ) | $0.4 \pi$          |

| Stopband Edge1( $w_{s1}(\phi)$ ) | $0.4 \pi$          |

| Stopband Edge2( $w_{s2}(\phi)$ ) | $0.6\pi$           |

Table 2-1 Parameters for tunable low pass filter.

In order to give a figure of merit to show the quality of the designed filter, some comparisons should be made among them. The quality figures are the maximum ripple in the passband, the maximum ripple in stopband, and error which is calculated according to (2.4).

The weight values specified for pass and stop band regions play an important role for error and ripple values. For the sake of comparison error and ripple values for designed filters for different values of  $K_p$  are given in Table 2-2.

| K <sub>p</sub> | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|----------------|------------------------------------|---------------------------------------|------------|

| 1              | -32.5012                           | -22.0005                              | -3.826     |

| 10             | -29.4875                           | -19.814                               | -3.6263    |

| 100            | -35.7768                           | -8.6555                               | 17.3016    |

| 1000           | -45.5163                           | -6.6874                               | 26.9476    |

Table 2-2 Characteristic values for tunable low pass filter for various values of  $K_p$ ; for Ks = 1, Filter order = 10, Interpolation order = 3,  $\phi = 0$ .

As it could be seen from Table 2-2, the higher values for  $K_p$  while keeping other filter parameters constant results in reduction in passband ripples, however, the total error and stop band ripple increase rapidly in order to ensure high  $K_p$  value.

The comparision of error and ripple values for designed filters for different values of  $K_s$  are given in Table 2-3.

| Table 2-3 Characteristic values for tunable low pass filter for various values of $K_s$ ; for $Kp = 1$ , |

|----------------------------------------------------------------------------------------------------------|

| Filter order = 10, Interpolation order = 3, $\phi$ = 0.                                                  |

|                | Maximum Ripple | Maximum       |            |

|----------------|----------------|---------------|------------|

| K <sub>s</sub> | in Passband    | Ripple in     | Error (dB) |

|                | (dB)           | Stopband (dB) |            |

| 1              | -32.5012       | -22.0005      | -3.826     |

| 10             | -25.1572       | -20.5383      | -1.7793    |

| 100            | -13.8608       | -26.3409      | 20.518     |

| 1000           | -12.6678       | -43.6452      | 24.3755    |

It is clearly seen from Table 2-3 that for increasing values of  $K_s$ , the stopband ripple of the designed filter decreases considerably, while the passband ripple values and the total error values increase. This result stems from the fact that in order to ensure

high  $K_s$  values the other filter parameters become less considerable in the error equations.

The comparision of error and ripple values for designed filters for different values of filter orders are given in Table 2-4.

| Filter order | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|--------------|------------------------------------|---------------------------------------|------------|

| 10           | -32.5012                           | -22.0005                              | -3.826     |

| 20           | -36.4305                           | -29.9151                              | -20.9615   |

| 30           | -46.0334                           | -31.9205                              | -33.437    |

| 40           | -50.4494                           | -33.2996                              | -41.4992   |

Table 2-4 Characteristic values for tunable low pass filter for various values of filter order; for Kp = 1000, Kp = 1000, Interpolation order = 3,  $\phi = 0$ .

From Table 2-4 it can be seen that the passband, the stopband and the total error values for increasing filter order reduces rapidly. This is a direct and expected result as the increasing filter order always accompanied with reduction in ripples and error values.

The comparison of error and ripple values for designed filters for different values of interpolation orders are given in Table 2-5.

| Interpolation<br>order | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|------------------------|------------------------------------|---------------------------------------|------------|

| 3                      | -46.0334                           | -31.9205                              | -33.437    |

| 5                      | -48.4577                           | -46.7176                              | -60.5496   |

| 7                      | -54.8899                           | -46.9443                              | -76.5439   |

| 9                      | -60.7898                           | -42.0663                              | -75.4524   |

Table 2-5 Characteristic values for tunable low pass filter for various values of interpolation order; for Kp = 1000, Ks = 1000, Filter order = 31,  $\phi = 0$ .

From Table 2-5 it can be seen that the passband, the stopband and the total error values for increasing interpolation order reduces upto interpolation order of 7. Above this value while passband ripples reduces, stopband ripple and total error values increases. As the interpolation order increases the number of sub filters increases. However with increasing interpolation, for added filter branch multiplication value gets smaller values. This results in corresponding filter branch be less significant in total filter characteristic.

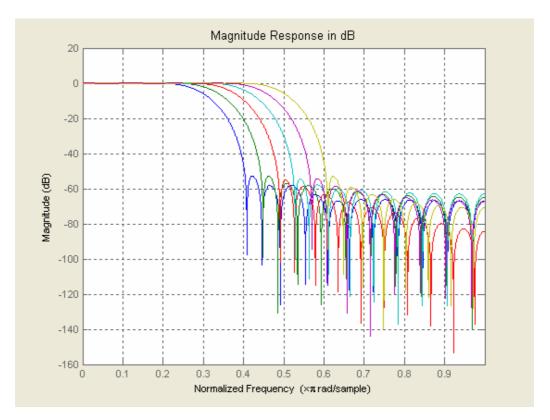

Magnitude responses for evenly sampled values of  $\phi$  are given in Figure 2.2.

Figure 2.2 Frequency response of variable lowpass FIR linear phase filter evenly sampled in range  $\phi = [0,1]$ .

#### 2.3.2 Tunable Linear-Phase Band-Pass Filter

The design of variable finite impulse response band-pass digital filter design is also worth considering. Letting the passband cutoff frequency be denoted by  $w_p$  and the stopband cutoff frequency be denoted by  $w_s$ , assuming the passband and the stopband cutoff frequencies vary linearly with spectral parameter  $\Phi = \phi$ , the variable passband and stopband cutoff frequencies could be defined as:

$$w_{p}(\phi) = w_{c} \pm (\phi(w_{p2} - w_{p1}) + w_{p1})/2$$

$$= w_{c} \pm w_{pp}(\phi)$$

$$w_{s}(\phi) = w_{c} \pm (\phi(w_{s2} - w_{s1}) + w_{s1})/2$$

$$= w_{c} \pm w_{ss}(\phi)$$

$$\Phi_{s} : \phi \in [0,1]$$

(2.19)

Frequency support of the filter is defined as combination of passband and stopband regions, which are defined by spectral parameter.

$$\Omega_{s} = \Omega_{p} + \Omega_{s}$$

$$\Omega_{p} = \{ w : w \in (w_{p1}(\phi), w_{p2}(\phi)) \}$$

$$\Omega_{s} = \{ w : w \in \{ (0, w_{s1}(\phi)) \cup (w_{s2}(\phi), \pi) \}$$

(2.20)

The desired impulse response is denoted by  $H_{I}(e^{jw}, \phi)$  and defined as:

$$H_{1}(e^{jw}, \phi) = \begin{cases} e^{-j\pi w}, w_{p1}(\phi) \le |w| \le w_{p2}(\phi) \\ 0, w_{s2}(\phi) \le |w| \le \pi \cup 0 \le |w| \le w_{s1}(\phi) \end{cases}$$

(2.21)

where  $\tau$  is the group delay which is assumed to be constant and equal to (N-1)/2 where N is the order of the sub filters.

#### 2.3.2.1 Mathematical Derivations

(2-15) can be rearranged as in (2-22)

$$\begin{bmatrix} Q_{ij} \end{bmatrix} = 2 \int_{\Phi_{s}} \phi^{p+m} \left( \frac{K_{p}}{(n-k)} (\sin((n-k)(w_{c} + w_{pp}(\phi))) - \sin((n-k)(w_{c} - w_{pp}(\phi)))) dw d\phi + 2 \int_{\Phi_{s}} \phi^{p+m} \left( \frac{K_{s}}{(n-k)} (\sin((n-k)(w_{c} - w_{ss}(\phi))) - \sin((n-k)(w_{c} + w_{ss}(\phi)))) dw d\phi + 2 \int_{\Phi_{s}} \phi^{p+m} \left( \frac{K_{s}}{(n-k)} (\sin((n-k)(w_{c} - w_{ss}(\phi))) - \sin((n-k)(w_{c} + w_{ss}(\phi))) \right) dw d\phi$$

(2.22)

If n=k the above equation will take the form as in (2-16)

$$\left[\mathbf{Q}_{ij}\right] = 2 \int_{\Phi_{s}} \phi^{p+m} (2\mathbf{K}_{p} \mathbf{w}_{pp}(\phi)) + \mathbf{K}_{s} \pi) d\mathbf{w} d\phi)$$

(2.23)

(2-17) can be rearranged as in (2-24)

$$[b]_{i} = 2 \int_{\phi_{s}} \phi^{p} \frac{K_{p}}{(k-\tau)} (\sin((k-\tau)(w_{c} + w_{pp}(\phi))) - \sin((k-\tau)(w_{c} - w_{pp}(\phi)))) d\phi$$

(2.24)

If  $k = \tau$  the above equation will take the form as in (2-25)

$$\left[b\right]_{i} = 4 \int_{\phi_{s}} \phi^{p} K_{p} W_{pp}(\phi) d\phi$$

(2.25)

where  $w_{pp}(\phi)$  and  $w_{ss}(\phi)$  are defined by (2-19).

#### 2.3.2.2 Design Results and Comparisons

For evaluation of the proposed method, a variable filter with the specifications given in Table 2-6 is designed.

| Specification                     | Value              |

|-----------------------------------|--------------------|

| Spectral Parameter ( $\phi$ )     | $0 \le \phi \le 1$ |

| Passband Edge1( $w_{ph1}(\phi)$ ) | 0.6 π              |

| Passband Edge2( $w_{ph2}(\phi)$ ) | $0.7\pi$           |

| Passband Edge3( $w_{pl1}(\phi)$ ) | $0.4\pi$           |

| Passband Edge4( $w_{pl2}(\phi)$ ) | $0.3 \pi$          |

| Stopband Edge1( $w_{sh1}(\phi)$ ) | $0.7\pi$           |

| Stopband Edge1( $w_{sh2}(\phi)$ ) | $0.8\pi$           |

| Stopband Edge3( $w_{s11}(\phi)$ ) | $0.3 \pi$          |

| Stopband Edge4( $w_{sl2}(\phi)$ ) | $0.2\pi$           |

Table 2-6 Parameters for tunable band pass filter.

The comparison of error and ripple values for designed filters for different values of filter orders are given in Table 2-7.

Table 2-7 Characteristic values for tunable band pass filter for various values of filter order; for Kp = 1000, Ks = 1000, Interpolation order = 3,  $\phi = 0$ , w<sub>c</sub> = 0.5  $\pi$ .

| Filter order | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|--------------|------------------------------------|---------------------------------------|------------|

| 10           | Inf                                | -6.5315                               | 67.1928    |

| 20           | -21.5864                           | -14.3465                              | 67.4243    |

| 30           | -17.8884                           | -17.6304                              | 67.5264    |

| 40           | -34.2529                           | -19.2417                              | 67.3992    |

From Table 2-7 it can be concluded that for increasing values of filter order the ripple values decrease to some extent. The error values are approximately the same.

The comparison of error and ripple values for designed filters for different values of interpolation orders are given in Table 2-8.

| Interpolation<br>order | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|------------------------|------------------------------------|---------------------------------------|------------|

| 3                      | -17.8884                           | -17.6304                              | 67.5264    |

| 5                      | -19.0114                           | -16.9435                              | 67.4988    |

| 7                      | -19.0461                           | -16.7118                              | 67.4935    |

| 9                      | -19.0162                           | -16.7626                              | 67.4951    |

Table 2-8 Characteristic values for tunable low pass filter for various values of interpolation order; for Kp = 1000, Ks = 1000, Interpolation order = 31,  $\phi = 0$ .

For increasing values of interpolation order, the pass band and stop band ripples get lower values; however, after the order 5 the decrease in not considerable. The error values are approximately the same for all of the values of interpolation order.

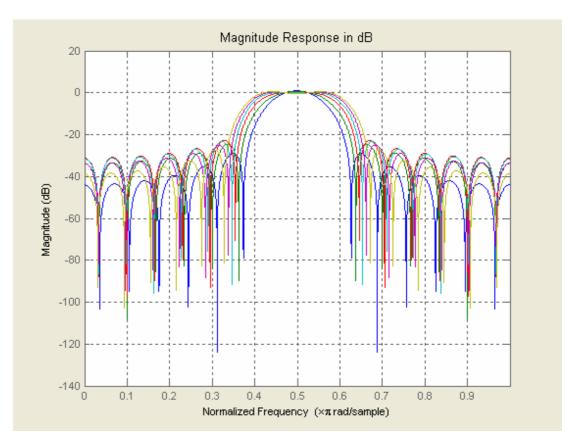

Magnitude responses for evenly sampled values of  $\phi$  are given in Figure 2.3.

Figure 2.3 Frequency response of variable bandpass FIR linear phase filter evenly sampled in the range  $\phi = [0,1]$ .

#### 2.3.3 Tunable Fractional Delay Low-Pass FIR Digital Filter

Variable fractional delay digital filters have important application areas especially when timing adjustment is required. For this reason an example of variable fractional delay digital filter is worth considering.

The desired impulse response of variable fractional delay digital filter is denoted by  $H_I(e^{jw}, \phi)$  and defined as:

$$H_{1}(e^{jw}, \phi) = \begin{cases} e^{-j\tau(\phi)w}, 0 \le |w| \le w_{p} \\ 0, w_{s} \le |w| \le \pi \\ \tau(\phi) = (N-1)/2 + \phi \\ \phi \in [-0.5, 0.5] \end{cases}$$

(2.26)

2.3.3.1 Mathematical Derivations

(2-15) can be rearranged as in (2-27)

$$\left[Q_{ij}\right] = 2 \int_{\Phi_{s}} \phi^{p+m} \left(\frac{K_{p}}{(n-k)} \sin((n-k)w_{p}) - \frac{K_{s}}{(n-k)} \sin((n-k)w_{s})\right) d\phi$$

(2.27)

If n=k, the above equation will take the form,

$$\left[Q_{ij}\right] = 2 \int_{\Phi_{s}} \phi^{p+m} (K_{p} w_{p} + K_{s} (\pi - w_{s})) d\phi$$

(2.28)

(2-17) can be rearranged as in (2-29)

$$[b]_{i} = 2 \int_{\phi_{s}} \phi^{p} \frac{K_{p}}{(k - (N - 1)/2 - \phi)} \sin(k - (N - 1)/2 - w_{p}) d\phi$$

(2.29)

If  $k=(N-1)/2+\phi$ , the above equation will take the form as in (2-30)

$$[b]_{i} = 2K_{p}W_{p}\phi$$

(2.30)

where N is the order of the subfilters.

#### 2.3.3.2 Design Results and Comparisons

For evaluation of proposed method, a variable filter with the specifications given in Table 2-9 is designed.

| Specification                  | Value                   |

|--------------------------------|-------------------------|

| Spectral Parameter ( $\phi$ )  | $-0.5 \le \phi \le 0.5$ |

| Passband Edge(w <sub>p</sub> ) | $0.2\pi$                |

| Stopband Edge(w <sub>s</sub> ) | $0.4\pi$                |

Table 2-9 Parameters for tunable fractional delay low pass filter.

The comparison of error and ripple values for designed filters for different values of filter orders are given in Table 2-10.

Table 2-10 Characteristic values for tunable fractional delay filter for various values of filter order; for Kp = 1000, Ks = 1000, Interpolation order = 3,  $\phi = 0$ .

| Filter order | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|--------------|------------------------------------|---------------------------------------|------------|

| 10           | -34.692                            | -18.6928                              | -5.9603    |

| 20           | -38.646                            | -34.2072                              | -39.6818   |

| 30           | -58.7456                           | -46.1449                              | -77.8958   |

| 40           | -67.3453                           | -63.3082                              | -111.7469  |

From Table2-10 it can be concluded that all of the characteristic values get lower values as filter order incereases. The decrease in parameters are more considerable

because in this case the spectral parameter is the fractional delay, meaning that, there is no difference in magnitude characteristics. This fact results in a considerable decrease in all of the characteristic parameters.

The comparison of error and ripple values for designed filters for different values of interpolation orders are given in Table 2-11.

| Interpolation<br>order | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|------------------------|------------------------------------|---------------------------------------|------------|

| 3                      | -58.7456                           | -46.1449                              | -77.8958   |

| 5                      | -58.583                            | -46.1438                              | -77.8974   |

| 7                      | -58.5829                           | -46.1438                              | -77.8974   |

| 9                      | -58.5829                           | -46.1438                              | -77.8974   |

Table 2-11 Characteristic values for tunable fractional delay filter for various values of interpolation order; for Kp = 1000, Ks = 1000, Filter order = 31,  $\phi$  = 0.

After interpolation order of 5, the ripple values and the total error does not change for this example.

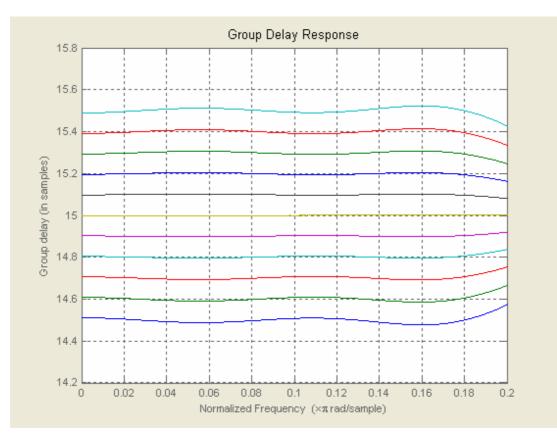

Group delays in pass band region for evenly sampled values of  $\phi$  are given in Figure 2.4 for the filter specificified in Table 2-9. Here the filter order 30, therefore the group delay is chosen to be 15, and fractional delay is assumed to change in between -0.5-0.5.

Figure 2.4 Group delay response of variable lowpass FIR filter evenly sampled in range  $\phi = [-0.5, 0.5]$ .

# **CHAPTER 3**

# VARIABLE FIR FILTER DESIGN WITH SINGULAR VALUE BASED VECTOR ARRAY DECOMPOSITION METHOD

### 3.1 General

In this chapter the variable FIR filter design by singular value decomposition based vector array decomposition method is described and the mathematical derivations method are given. Illustrative examples for variable single spectral parameter low pass and design results for these types of filters are given.

## 3.2 Design Method

Let  $H_I(w, \psi_1, \psi_2, ..., \psi_K)$  be the ideal variable frequency response specification, where

$$\psi_{1} \in [\psi_{1\min}, \psi_{1\max}]$$

$$\psi_{2} \in [\psi_{2\min}, \psi_{2\max}]$$

$$\vdots$$

$$\psi_{K} \in [\psi_{K\min}, \psi_{K\max}]$$

(3.1)

are the spectral parameters that are use to tune magnitude and/or phase responses. By sampling the parameters  $w, \psi_1, \psi_2, ..., \psi_K$  uniformly as

$$w(n) = -\pi + \frac{2\pi(n-1)}{N-1}, n = 1, 2, ..., N$$

$$\psi_1(m_1) = \psi_{1\min} + \frac{(\psi_{1\max} - \psi_{1\min})(m_1 - 1)}{M_1 - 1}, m_1 = 1, 2, ..., M_1$$

$$\psi_2(m_2) = \psi_{2\min} + \frac{(\psi_{21\max} - \psi_{2\min})(m_2 - 1)}{M_2 - 1}, m_2 = 1, 2, ..., M_2$$

$$\vdots$$

$$\psi_K(m_K) = \psi_{K\min} + \frac{(\psi_{K\max} - \psi_{K\min})(m_K - 1)}{M_K - 1}, m_K = 1, 2, ..., M_K$$

(3.2)

Equally spaced samples of  $H_I(w, \psi_1, \psi_2, ..., \psi_K)$  are

$$\widetilde{a}(n, m_1, m_2, ..., m_K) = H_I [w(n), \psi_1(m_1), \psi_2(m_2), ..., \psi_K(m_K)]$$

(3.3)

These samples can be used to construct a (K+1) dimensional complex array  $\widetilde{A}$  as

$$\widetilde{A} = \left[\widetilde{a}(n, m_1, m_2, ..., m_K)\right]$$

(3.4)

If one spectral parameter is used, K = 1,  $\widetilde{A}$  is a 2-D complex array, if K = 2,  $\widetilde{A}$  is a 3-D complex array, and  $\widetilde{A}$  is a hyper cube if  $K \ge 3$ .

Here the design consideration is to decompose  $\widetilde{A}$  as

$$\approx \sum_{i=1}^{r} C_{i} \otimes R_{i}$$

(3.5)

under the following constraints:

$\checkmark$  C<sub>i</sub> are complex conjugate-symmetric vectors, and R<sub>i</sub> are K-D real arrays

Ã

✓ Mean-squared decomposition error

$$e_{r} = \left\| \widetilde{A} - \sum_{i=1}^{r} C_{i} \otimes R_{i} \right\|^{2}$$

=  $\sum_{n=1}^{N} \sum_{m_{1}=1}^{M_{1}} \dots \sum_{m_{K}=1}^{M_{K}} \left| \widetilde{a}(n, m_{1}, m_{2}, ..., m_{K}) - \sum_{i=1}^{r} C_{i}(n) R_{i}(m_{1}, m_{2}, ..., m_{K}) \right|^{2}$

(3.6)

is minimized, where  $\|\cdot\|$  is the Euclidian norm (l<sub>2</sub> norm), the notation  $\otimes$  denotes a special product between the complex vector C<sub>i</sub> and the K-D real array R<sub>i</sub>, and the decompostion in (3-5) means

$$\widetilde{a}(n, m_1, m_2, ..., m_K) \approx \sum_{i=1}^r C_i(n) R_i(m_1, m_2, ..., m_K)$$

(3.7)

The first constraint is imposed for the reason that the complex symmetric vectors  $C_i$  can be regarded as the desired frequency responses of constant 1-D digital filters with real coefficients and that the K- dimensional real arrays  $R_i$  can be regarded as the desired values of K-D polynomials of the spectral parameters  $\psi_1, \psi_2, ..., \psi_K$ .

The filter structure of specified variable FIR filter would be as in Figure 3.1.

Figure 3.1 Proposed vector array decomposition based filter structure.

Here once the vector array decomposition is obtained, the constant 1-D filters  $H_i(z)$  can be designed by approximating the complex vectors  $C_i$ , and the K-D polynomials  $P_i(\psi_1, \psi_2, ..., \psi_K)$  can be found for approximating the K-D real arrays  $R_i$ , the variable 1-D filter

$$H(z,\psi_1,\psi_2,...,\psi_K) = \sum H_i(z)P_i(\psi_1,\psi_2,...,\psi_K)$$

(3.8)

can be indirectly obtained by connecting H<sub>i</sub>(z) with P<sub>i</sub>( $\psi_1, \psi_2, ..., \psi_K$ ).

#### 3.2.1 Vector Array Decomposition Algorithm

In order vector array decompositon algorithm to be applied first (K+1)-D array should be reduced to matrix form. Based on one-to-one index mappings

$$\begin{array}{c} n \to n \\ (m_1, m_2, \dots, m_K) \to m \end{array}$$

(3.9)

where

$$m = (m_1 - 1) \prod_{k=2}^{K} M_K + (m_2 - 1) \prod_{k=3}^{K} M_K + \dots + (m_{K-1} - 1) M_K + m_K$$

(3.10)

such that

$$a(n,m) = \tilde{a}(n,m_1,m_2,...,m_K)$$

(3.11)

Sigular value decomposition of A is

$$A = U \sum V^{*} = \sum_{i=1}^{R} \sigma_{i} u_{i} v^{*}_{i} = \sum_{i=1}^{R} \widetilde{u}_{i} \widetilde{v}^{*}_{i}$$

(3.12)

where R is the rank of A.

$$U = \begin{bmatrix} u_1 & u_2 & \cdots & u_R \end{bmatrix}$$

$$V = \begin{bmatrix} v_1 & v_2 & \cdots & v_K \end{bmatrix}$$

(3.13)

are unitary matrices and

$$\sum = \operatorname{diag}(\sigma_1 \quad \sigma_2 \quad \cdots \quad \sigma_R)$$

(3.14)

is a diagonal matrix with the singular values  $\sigma_i$  as its diagonal entries;  $\sigma_1 \ge \sigma_2 \ge \cdots \ge \sigma_R \ge 0$  and

$$\widetilde{\mathbf{u}}_{i} = \sqrt{\sigma_{i}} \mathbf{u}_{i}$$

$$\widetilde{\mathbf{v}}_{i} = \sqrt{\sigma_{i}} \mathbf{v}_{i}$$

(3.15)

Singular value decomposition always guarantees that the mean squared error is minimum for any  $r \leq R$  .

When it comes to the design of constant filters  $H_i(z)$  from vectors  $C_i$ , assuming equally spaced samples of the frequency response  $H_i(e^{jw})$

$$H_{i}(k) = \sum_{n=N_{1}}^{N_{2}} a_{n} e^{-jw(k)n}$$

(3.16)

where k = 1,2,...,K. The design objective here is to find the optimal coefficients  $a_n$  such that the mean squared error is minimum. That is

$$e_{H} = \sum_{k=1}^{K} |H_{i}(k) - C_{i}(k)|^{2}$$

=

$$\sum_{k=1}^{K} [H_{i}(k) - C_{i}(k)] [H_{i}(k) - C_{i}(k)]^{*}$$

(3.17)

where  $H_i(k)$  is given in (3-16) and  $C_i(k)$  values are obtained from singular value decomposition.

Putting e<sub>H</sub> values into the matrix form and after some manipulations, one can obtain

$$\operatorname{Re}[\operatorname{E}^{*}\operatorname{Ea}] = \operatorname{Re}[\operatorname{E}^{*}\operatorname{C}_{i}]$$

(3.18)

where

$$\mathbf{E} = \begin{bmatrix} \mathbf{e}(1, \mathbf{N}_{1}) & \mathbf{e}(1, \mathbf{N}_{1} + 1) & \cdots & \mathbf{e}(1, \mathbf{N}_{2}) \\ \mathbf{e}(2, \mathbf{N}_{1}) & \mathbf{e}(2, \mathbf{N}_{1}) & \dots & \mathbf{e}(2, \mathbf{N}_{2}) \\ \vdots & \vdots & \vdots & \vdots \\ \mathbf{e}(\mathbf{L}, \mathbf{N}_{1}) & \mathbf{e}(\mathbf{L}, \mathbf{N}_{1}) & \cdots & \mathbf{e}(\mathbf{L}, \mathbf{N}_{2}) \end{bmatrix}$$

(3.19)

elements e(k,n) defined as

$$e(k,n) = e^{-jw(k)n}, \begin{cases} k = 1, 2, ..., K\\ n = N_1, N_1 + 1, ..., N_2 \end{cases}$$

(3.20-a)

$$\begin{bmatrix} a_{N_1} \end{bmatrix} \begin{bmatrix} C_i(1) \end{bmatrix}$$

$$a = \begin{bmatrix} a_{N_1} \\ a_{N_L+1} \\ \vdots \\ a_{N_2} \end{bmatrix}, C_i = \begin{bmatrix} C_i(1) \\ C_i(2) \\ \vdots \\ C_i(K) \end{bmatrix}$$

(3.20-b)

The optimal coefficient vector **a** can be determined as

$$\mathbf{a} = \left\{ \operatorname{Re}\left[\operatorname{E}^{*}\operatorname{E}\right] \right\}^{-1} \cdot \operatorname{Re}\left[\operatorname{E}^{*}\operatorname{C}_{i}\right]$$

(3.21)

The K-D polynomials  $P_i(\psi_1, \psi_2, \dots, \psi_K)$  can be obtained by using the polynomial fitting technique. The values of  $P_i(\psi_1, \psi_2, \dots, \psi_K)$  are

$$P[\psi_{1}(m_{1}),\psi_{2}(m_{2}),...,\psi_{K}(m_{K})] = \sum_{l_{1}=0}^{L_{1}} \sum_{l_{2}=0}^{L_{2}} \cdots \sum_{l_{K}=0}^{L_{K}} c(l_{1},l_{2},...,l_{K}).\psi_{1}^{l_{1}}(m_{1})\psi_{2}^{l_{2}}(m_{2})...\psi_{K}^{l_{K}}(m_{K})$$

(3.22)

Letting the desired values of  $P[\psi_1(m_1), \psi_2(m_2), ..., \psi_K(m_K)]$  be denoted by  $d(m_1, m_2, ..., m_K)$  and the optimal coefficients for  $P[\psi_1(m_1), \psi_2(m_2), ..., \psi_K(m_K)]$  by  $c(l_1, l_2, ..., l_K)$  for minimizing the approximation error linearly following steps should be followed:

✓ Map the K-D index  $(m_1, m_2, ..., m_K)$  to 1-D index as

$$m = (m_1 - 1)M_2M_3 \cdots M_K + (m_2 - 1)M_3M_4 \cdots M_K + \dots + (m_{K-1} - 1)M_K + m_K$$

(3.23)

where

$$m_i \in \{1, 2, \dots, M_i\}$$

$$i \in \{1, 2, \dots, K\}$$

$$m \in \{1, 2, \dots, M\}$$

$$M = M_1 M_2 \cdots M_K$$

(3.24)

✓ Map the M-D index  $(l_1, l_2, ..., l_K)$  to the 1-D index l as

$$l = l_1(L_2 + 1)(L_3 + 1)\cdots(L_K + 1) + l_2(L_3 + 1)(L_4 + 1)\cdots(L_K + 1) + \cdots + l_{K-1}(L_K + 1) + (l_K + 1)$$

(3.25)

where

$$l_i \in \{0, 1, \dots, L_i\}$$

$i \in \{1, 2, \dots, K\}$

$l \in \{1, 2, \dots, L\}$

$L = (L_1 + 1)(L_2 + 1) \cdots (L_K + 1)$

(3.26)

Based on above index mappings, one gets

$$C(l) = c(l_1, l_2, \dots, l_K)$$

$$a(m) = d(m_1, m_2, \dots, m_K)$$

$$\Phi_{ml} = \psi_1^{l_1}(m_1)\psi_2^{l_2}(m_2)\cdots\psi_K^{l_K}(m_K)$$

(3.27)

The error is now defined as

$$E_{p} = \sum_{m=1}^{M} \left[ \sum_{l=1}^{L} C(l) \Phi_{ml} - a(m) \right]^{2}$$

(3.28)

In order to minimize  $E_p$ , differentiating  $E_p$  with respect to each coefficient C(l) and setting the derivatives to zero, one gets simultaneous linear equations

$$AC = b$$

(3.29)

where

$$A = \Phi^{t} \Phi$$

$$\Phi = \begin{bmatrix} \Phi_{11} & \Phi_{12} & \cdots & \Phi_{1L} \\ \Phi_{21} & \Phi_{22} & \cdots & \Phi_{2L} \\ \vdots & \vdots & \vdots & \vdots \\ \Phi_{M1} & \Phi_{M2} & \cdots & \Phi_{ML} \end{bmatrix}$$

$$C = \begin{bmatrix} C(1) & C(2) & \cdots & C(L) \end{bmatrix}^{t}$$

$$b = \Phi^{t} a$$

$$a = \begin{bmatrix} a(1) & a(2) & \cdots & a(M) \end{bmatrix}$$

(3.30)

Solving the linear equations, the optimal coefficient vector  $\mathbf{C}$  can be obtained. Finally, the coefficients  $c(l_1, l_2, ..., l_K)$  can be determined from the resulting vector  $\mathbf{C}$  in the reverse order.

### **3.3** Illustrative Examples

#### 3.3.1 Tunable Linear-Phase Low-Pass FIR Filter

For evaluation of proposed method a variable lowpass filter with the specifications given in Table 2-1 is designed.

The comparison of error and ripple values for designed filters for different values of frequency band sample points are given in Table 3-1.

Table 3-1 Characteristic values for tunable low pass filter for various values of band sample points; for spectral parameter sample points =9, Filter order = 10, Interpolation order = 3,  $\phi = 0$ .

|               | Maximum       | Maximum       |            |

|---------------|---------------|---------------|------------|

| Sample points | Ripple in     | Ripple in     | Error (dB) |

|               | Passband (dB) | Stopband (dB) |            |

| 50            | -30.7469      | -24.0659      | -1.6167    |

| 100           | -30.7646      | -24.1245      | -1.6524    |

| 500           | -30.6607      | -24.1092      | -1.54      |

| 1000          | -30.6535      | -24.1111      | -1.5299    |

It can be concluded from Table 3-1 that increasing the number of frequency band sampling points have no considerable effect on the characteristic values of the designed filter, especially after 100 sample points.

The comparison of error and ripple values for designed filters for different values of filter orders are given in Table 3-2.

| Filter order | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|--------------|------------------------------------|---------------------------------------|------------|

| 10           | -30.6607                           | -24.1092                              | -1.54      |

| 20           | -39.1081                           | -31.8706                              | -24.9873   |

| 30           | -40.7246                           | -27.2175                              | -19.7707   |

| 40           | -46.9886                           | -27.4835                              | -20.4907   |

Table 3-2 Characteristic values for tunable low pass filter for various values of filter order; for frequency band sample points = 500, Interpolation order = 3,  $\phi = 0$ .

With the increasing number of filter order the ripple values in pass band, stop band and the error values decrease considerably. This is an expected result with an increase of filter order of subbranches.

The comparison of error and ripple values for designed filters for different values of interpolation orders are given in Table 3-3.

| Interpolation<br>order | Maximum Ripple<br>in Passband (dB) | Maximum<br>Ripple in<br>Stopband (dB) | Error (dB) |

|------------------------|------------------------------------|---------------------------------------|------------|

| 3                      | -40.7246                           | -27.2175                              | -19.7707   |

| 5                      | -38.3223                           | -31.4681                              | -34.2726   |

| 7                      | -39.2236                           | -30.6817                              | -35.827    |

| 9                      | -39.2149                           | -30.6978                              | -35.8503   |

Table 3-3 Characteristic values for tunable low pass filter for various values of filter order; for frequency band sample points = 500, Filter order = 30,  $\phi = 0$ .

From Table 3-3 it can be concluded that, when the interpolation order is increased up to 7 the error and ripple values decrease considerably. After that point a little change can be observed. This result stems from the fact that with increasing number of interpolation order, the multiplication values for each branch also decreases so the difference becomes negligible.

Magnitude responses for evenly sampled values of  $\phi$  are given in Figure 3.2.

Figure 3.2 Frequency response of variable lowpass FIR linear phase filter evenly sampled in the range  $\phi = [0,1]$ .

# **3.4 Comparison of Direct Integration and Singular Value Decomposition Based Vector Array Decomposition Methods**

The basic difference between the two methods is the computation times. Since the direct integration method requires integrations to be performed numerically, the required computation time is considerably more than that of the singular value decomposition based vector array decomposition.

When ripple values and errors are considered, it is seen that the performances of the the two methods are not so different.

From these considerations it is concluded that singular value decomposition based method would be preferrable in applications where the computation time is important.

# **CHAPTER 4**

# **APPLICATION ON SOFTWARE DEFINED RADIO**

### 4.1 General

One of the typical application areas of the variable digital filters is software defined radio. In this chapter, brief information about software defined radio will be given and usage of variable digital filters on software defined radios will be outlined.

Software application to show the implementation of proposed and traditional method will be considered. The obtained results from these implementations will be compared.

A hardware application on software defined radio will be discussed. The PCB (Printed Circuit Card) which will be used to realize traditional structure will be introduced. Operating system requirements in order to communicate with the application card will be discussed.

### 4.2 Software Defined Radio Description

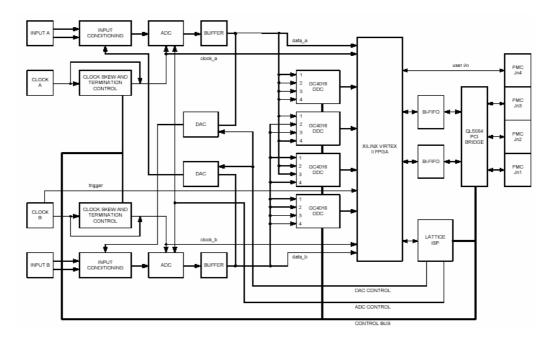

Software defined radio is a general hardware/software platform for supporting intercommunication between different wireless communication systems. The basic idea of an ideal software defined receiver is to digitize the received signal using highspeed analog-to-digital converters and to process it by a programmable system, consisting of combination of hardware and software that is reconfigurable or programmable. Due to limitations of current technology and signal converters, most software radio architectures considered digitize the decimated signal at the intermediate frequency.

Since different communication standards are based on different master clock rates it is mainly necessary to provide these different clock rates. However, due to strong requirements for clock quality, it is reasonable to assume that only one fixed master clock will be provided in practical sofware radio applications. A solution to this is to provide different clock rates virtually by means of digital sample rate conversion. Hence, with software defined radio a new functionality is introduced: sample rate converters. Sample rate conversion is the task of converting the sample rate while a certain amount of information, usually in a limited frequency band, is preserved. Actually, the main concern in sample rate conversion is is not interpolation but antialiasing.

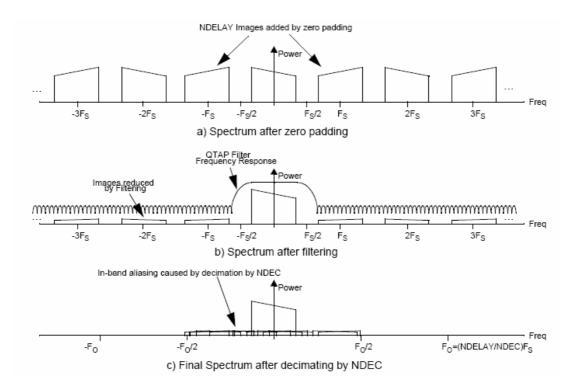

A conventional software defined radio receiver structure could be seen in Figure 4.1. In this general structure a programmable digital decimator and a sample rate converter are employed to isolate the desired user's channel from the signal spectrum and convert it to an appropriate sampling rate for further processing.

Figure 4.1 Conventional software defined radio receiver structure.

Moreover the programmable digital decimator usually consists of multiple stages of decimators to reduce implementation complexity and power dissipation as shown in Figure 4.2.

Figure 4.2 Conventional programmable decimator and sample rate converter.

As the sampling rate of the baseband signal is much lower than that of the intermediate frequency, each stage in the decimator will consist of a bandlimiting (anti-aliasing) digital filter and a downsampler (decimator) to filter out the unwanted signals and lower sampling rate. By selecting an appropriate number of stages, different integer downsampling ratios can be implemented. The programmable finite impulse response filter is used to remove the residual interference from adjacent channels. It is because the sampling rate is usually not an integer multiples of the channel spacing. Together with sample rate converter, which provides the necessary arbitrary rate-change factor, it is possible to accomodate signals with a wide variety of bandwidths.

One drawback of this conventional structure is that the output of the multistage decimators, which is obtained by downsampling the high-rate conversion, has to be upsampled again in order to carry out the arbitrary sample rate conversion. Recently authors [3] have proposed a new digital intermediate frequency architecture for software radio receivers shown in Figure 4.3-a.

Figure 4.3 (a) Proposed architecture of the programmable decimator and sample rate converter, (b)Architecture of the proposed software radio receiver, (c)Architecture of the multistage decimators.

The sample rate converter which is realized using Farrow based variable digital filter is inserted immediately after the multistage decimators. The basic idea of the variable digital filter based sample rate converter is to provide variable fractional delay in the pass band and additional attenuation in the stop band. This allows replacing programmable finite impulse response filter by a half band filter with fixed coefficients, if the arbitrary rate-change factor is properly chosen.

This architecture eliminates the need for the programmable finite impulse response filter, which is usually a bottleneck of software defined radio application for wideband signals.

### 4.3 Software Simulations

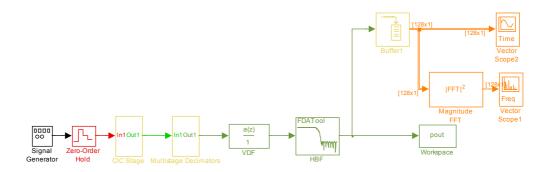

#### 4.3.1 Simulink Model of Proposed Method

The proposed method is implemented on Matlab Simulink according to Figure 4.3 and overall model could be seen in Figure 4.6. In the figure different sample rates are represented by different colors.

Here as input signal 500 Hz square wave generator is used. The generated signal is then discretized by zero-order hold unit with sampling time 0.00001 seconds.

The CIC, Cascade Comb Integrator, stage is implemented with 4 stage integrator and 4 stage decimator with downsampling ratio of 4. The structure of CIC stage is given in Figure 4.21.

Figure 4.4 Simulink CIC Stage.

The CIC stage consists of an integrator and a comb stage, a downsampler unit is inserted in between. The basic CIC filters [22] are commonly used when large downsampling ratios are required, because of its reasonable performance and low hardware complexity. One drawback of the CIC filter is the pass band droop that limits the quality of the anti-aliasing filters. In [3], a second order CIC compensator

with the following transfer function is applied after the comb stage, realized by 'Compensator' block in Figure 4.4.

$$P(z) = a + bz^{-1} + az^{-2}$$

(4.1)

'a' and 'b' are real-valued constants to be determined, in particular, for this simulation these values are determined by using Parks-McClellan algorithm. This compensator can be viewed as the equalizer in the interpolated FIR filters [23].

The integrator and comb filter structures could be seen in Figure 4.5 and Figure 4.6 respectively.

Figure 4.5 Integrator Stage of CIC.

Figure 4.6 CombStage of CIC.

Figure 4.7 Simulink Implementation of Proposed Method.

CIC stage is followed by multistage decimator block. Multistage decimator block consists of three low pass filters and three downsampler units with downsampling ratio of 2. Multistage decimator unit is given in Figure 4.8.

Figure 4.8 Simulink Multistage Decimator Stage.

Multistage decimator is followed by VDF based filter stage. This filter stage coefficients are computed by the direct integration method algorithm, detailed in Section 2, and loaded to filter as an external parameter. The filter pass band cut off frequency is at 0.4 and stop band frequency is at 0.7. Subfilter order is 41 and group delay is capable of changing in between 19.5 to 20.5.

In the proposed method, the VDF stage is followed by half band stage. Here again FIR type half band filter is designed using filter design tool of Simulink.

'To Workspace' block is used to store data for further comparison that will be done using Matlab software.

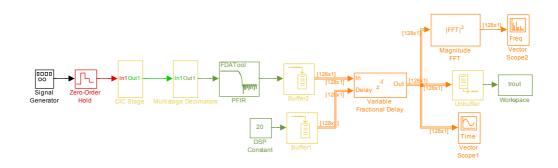

### 4.3.2 Simulink Model of Traditional Method

In traditional SDR model CIC and multistage decimator units are used, as they are in proposed method. After multistage decimator stage a programmable FIR, PFIR, filter is used. This filter coefficients are capable of changing their values during operation on request.

After PFIR section SDR unit comes, which is implemented by interpolator unit. For proper operation of interpolator unit input samples should be upsampled. In Matlab Simulink 'Variable Fractional Delay' block is designed to operate in the same manner, input sample values are first upsampled and then interpolation is done together with filtering. Finally decimation is done on samples to reduce the sample rate again.

The output data produced by the simulation is stored for comparison and corresponding model could be seen in Figure 4-9.

Figure 4.9 Simulink Implementation of Traditional Method.

### 4.3.3 Simulation Results

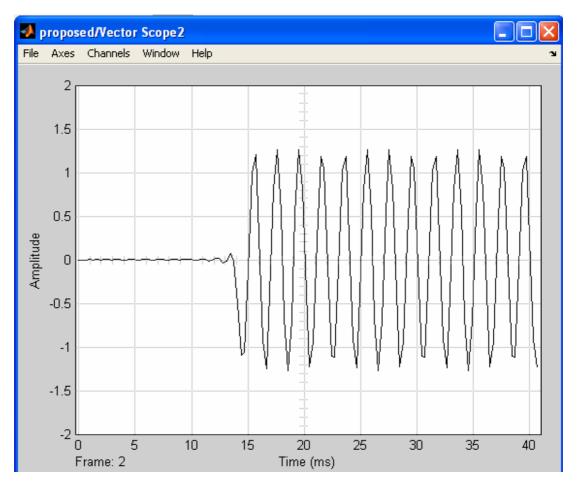

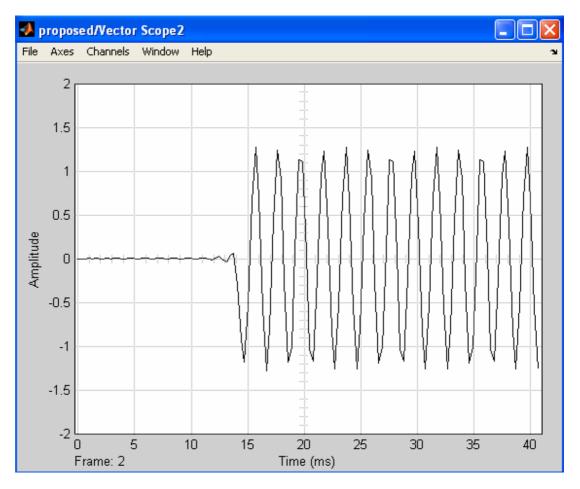

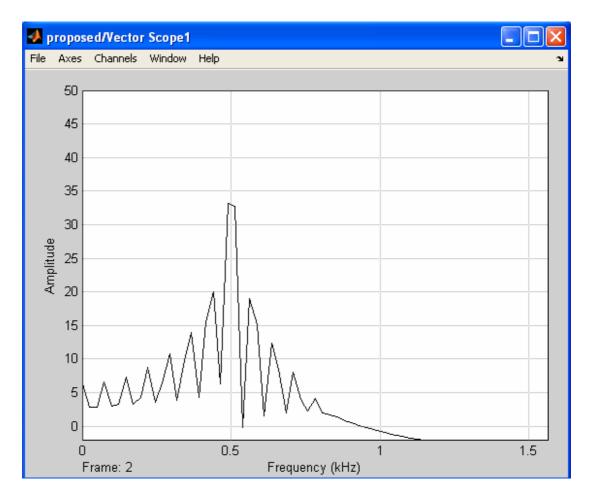

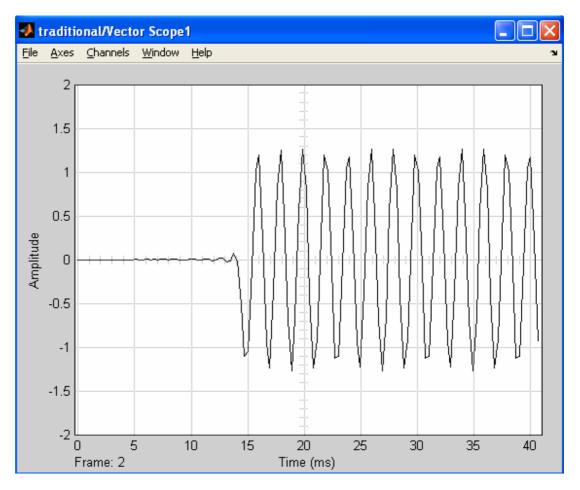

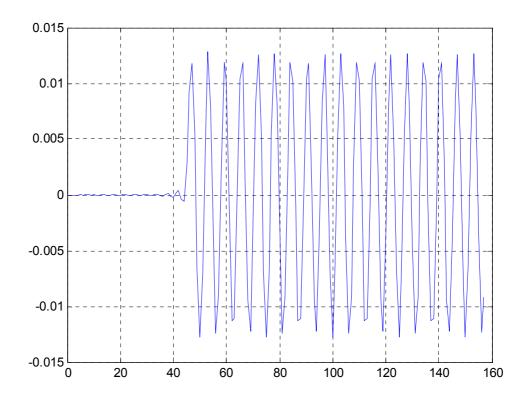

Simulation on Matlab Simulink is performed on proposed and traditional methods. Simulation time for both of them is arranged to be 0.05 seconds. The fractional delays are chosen to be 0.15 for both of the cases. The output data waveform and magnitude of fast fourier transform could be seen in Figure 4-10 and Figure 4-11 respectively.

Figure 4.10 Output Data for Proposed Method for Fractional Delay of 0.15.

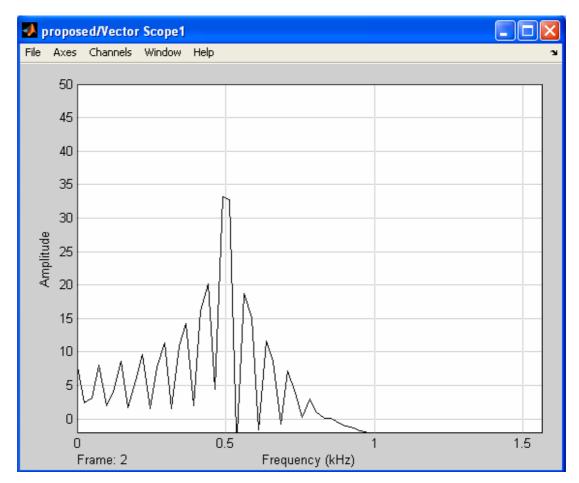

Figure 4.11 Magnitude of FFT of Output Data for Proposed Method for Fractional Delay of 0.15.

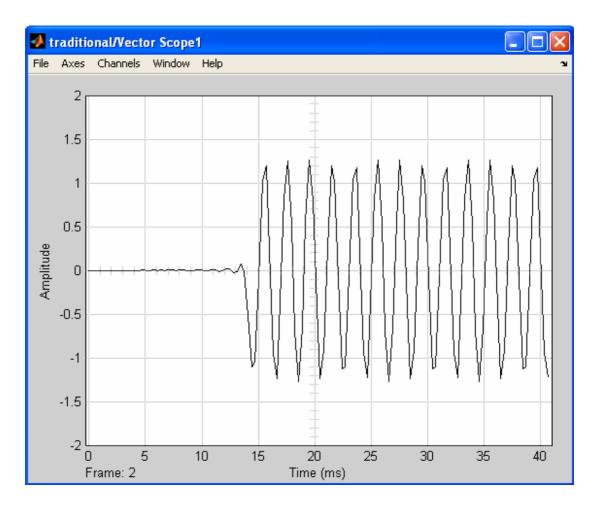

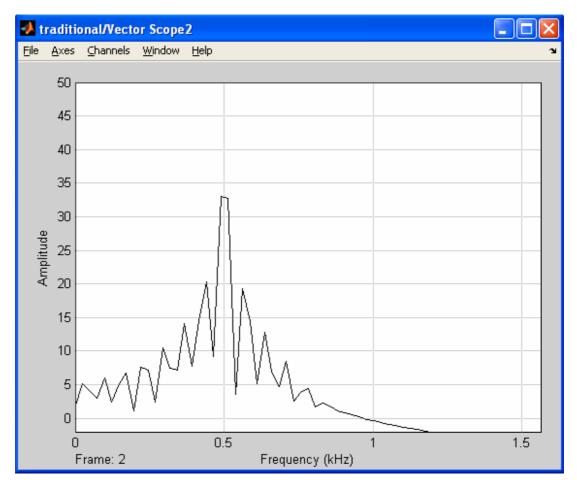

The output data waveform and magnitude of FFT for traditional method for fractional delay of 0.15 could be seen in Figure 4-12 and Figure 4-13 respectively.

Figure 4.12 Output Data for Traditional Method for Fractional Delay of 0.15.

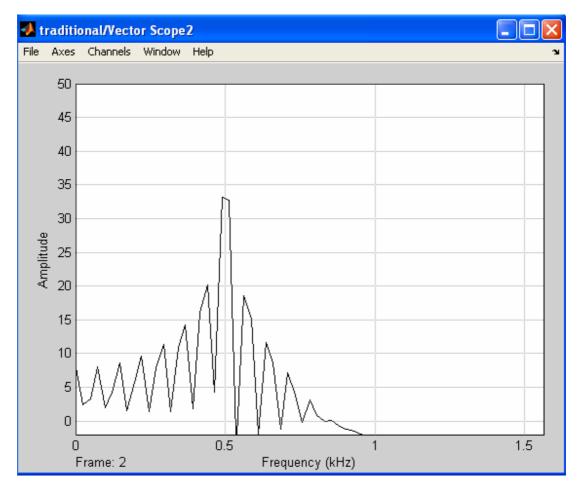

Figure 4.13 Magnitude FFT of Output Data for Traditional Method for Fractional Delay of 0.15.

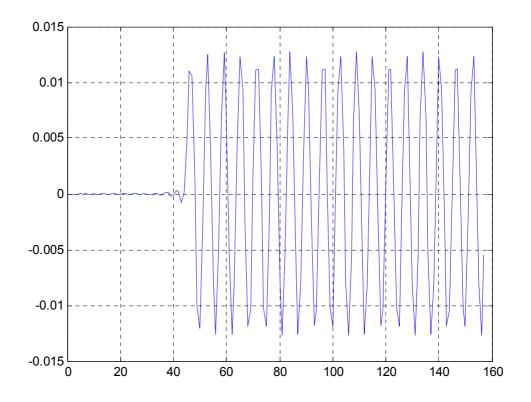

The difference of the output data that of traditional and proposed method for fractional delay of 0.15 is given in Figure 4-14.

Figure 4.14 Difference of Output Data of Traditional and Proposed Methods for Fractional Delay of 0.15.

From these results, it can be concluded that there is approximately 20dB difference between proposed and traditional method between output values whereas magitude of FFT are nearly the same.

As another example point 0.5 fractional delay is considered. Corresponding waveforms for traditional method output data could be seen in Figure 4-15 and Figure 4-16 respectively.

Figure 4.15 Output Data for Proposed Method for Fractional Delay of 0.5.

Figure 4.16 Magnitude of FFT of Output Data for Proposed Method for Fractional Delay of 0.5.

The output data waveform and magnitude of FFT for traditional method for fractional delay of 0.5 could be seen in Figure 4-17 and Figure 4-18 respectively.

Figure 4.17 Output Data for Traditional Method for Fractional Delay of 0.5.

Figure 4.18 Magnitude of FFT of Output Datafor Traditional Method for Fractional Delay of 0.5.

The difference of the output data that of traditional and proposed method for fractional delay of 0.5 is given in Figure 4-19.

Figure 4.19 Difference of Output Data of Traditional and Proposed Methods for Fractional Delay of 0.5.

Hera again the difference between porposed and traditional method outputs are approximately 20dB for worst case.

### 4.4 Work on RAD-2

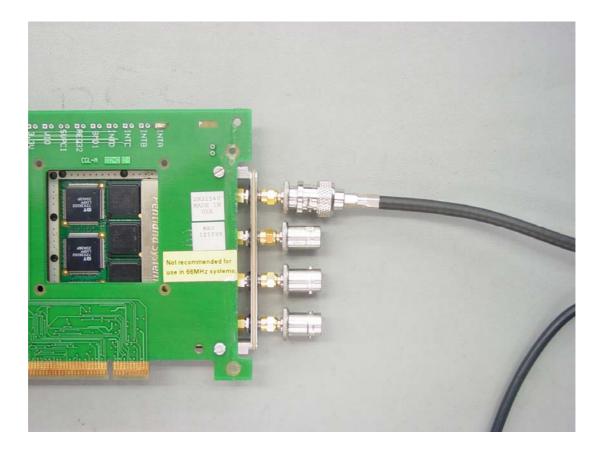

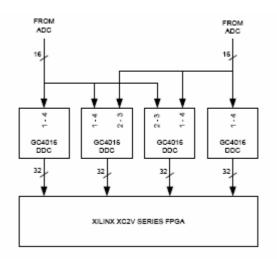

To give a specific example of hardware Pentland Systems RAD2 card is considered, whose detailed operational and functional description is given in Appendix A.

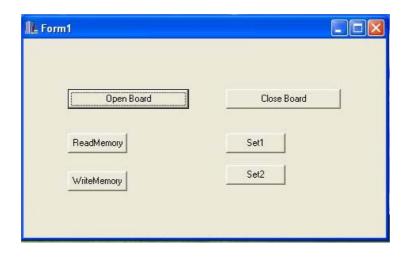

In order RAD-2 to operate in a desired manner, user should specify necessary operating requirements. These need to be set via PCI communication bus. Since PCI is a very complex communication protocol an operating system is necessary for this communication. RAD-2 has capability of communicating over VxWorks, Linux and WinXP.

Since VxWorks needs a proper operating case and Linux is not a commonly used operating system, WinXP is chosen for operation.

For different operating conditions different settings should be done on RAD-2. For this reason custom drivers are needed, though Pentland System supplies drivers for all of these operating systems.