### DESIGN OF A SINGLE-PHASE FULL-BRIDGE DIODE RECTIFIER POWER FACTOR CORRECTOR EDUCATIONAL TEST SYSTEM

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

TEOMAN ÜNAL

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2006

Approval of the Graduate School of Natural and Applied Sciences.

Prof. Dr. Canan ÖZGEN Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof. Dr. İsmet ERKMEN Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Prof. Dr. Yıldırım ÜÇTUĞ Supervisor

# **Examining Committee Members**

| Prof. Dr. Muammer ERMİŞ       | (METU, EEE) |  |

|-------------------------------|-------------|--|

| Prof. Dr. Yıldırım ÜÇTUĞ      | (METU,EEE)  |  |

| Prof. Dr. H. Bülent ERTAN     | (METU,EEE)  |  |

| Asst. Prof. Dr. Ahmet M. HAVA | (METU,EEE)  |  |

| Dr. İsmet ARSAN               | (KAREL)     |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : TEOMAN ÜNAL

Signature :

#### ABSTRACT

### DESIGN OF A SINGLE-PHASE FULL-BRIDGE DIODE RECTIFIER POWER FACTOR CORRECTOR EDUCATIONAL TEST SYSTEM

Ünal, Teoman M.S., Department of Electrical and Electronics Engineering Supervisor : Prof. Dr. Yıldırım Üçtuğ

December 2006, 227 pages

In this thesis an educational test bench for studying the power quality attributes of the commonly used single-phase full-bridge diode rectifiers with power factor correction (PFC) circuits is designed and tested. This thesis covers the active and passive power factor correction methods for single-phase bridge rectifier. Passive filtering approach with dc side inductor and tuned filter along with active filtering approach via single-switch boost converter is considered. Analysis, simulation, and design of a single phase rectifier and PFC circuits is followed by hardware implementation and tests. In the active PFC approach, various control methods is applied and compared. The educational bench is aimed to useful for undergraduate and graduate power electronics course, power quality related laboratory studies.

Keywords: Power Factor Correction, passive filter methods, active PFC control topologies.

# ÖZ

# TEK FAZLI, TAM KÖPRÜ DİYOTLU DOĞRULTUCU İÇİN GÜÇ KATSAYISI DÜZELTİCİ EĞİTİM TEST SİSTEMİ TASARIMI

Ünal, Teoman

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Prof. Dr. Yıldırım Üçtuğ

Aralık 2006, 227 sayfa

Bu tezde, yaygın olarak kullanılan güç katsayısı düzeltmeli tek faz tam köprü diyotlu doğrultucuların güç kalitesi özelliklerini incelemek için eğitim test seti tasarlanmış ve gerekli test düzenekleri geliştirilmiştir. Eğitim amaçlı olarak da kullanılabilecek bu sistem tek fazlı diyotlu doğrultucular için aktif ve pasif çözümleri içermektedir. Pasif çözümler olarak DC tarafa yerleştirilen endüktans filtre ile tuzak filtre yöntemleri incelenmiş ve kullanılmıştır. Aktif yöntem olarak tek anahtarlı gerilim yükseltici dönüştürücü devresi kullanılmıştır. Yapılan bütün uygulamalar için teorik ve bilgisayar benzeşimine dayanan analizler, donanımsal olarak gerçekleştirilmiş ve üzerinde ölçümler alınabilecek seviyeye getirilmiştir. Aktif güç katsayısı düzeltici devresinde çeşitli denetim yöntemleri uygulanmış ve karşılaştırılmıştır. Geliştirilen eğitim seti lisans ve lisansüstü güç elektroniği derslerinde güç kalitesi ile ilgili inceleme uygulamalarında kullanılabilir niteliktedir.

Anahtar Kelimeler: Güç katsayısı düzenleme, pasif filtre uygulamaları, aktif PFC kontrol yöntemleri.

To My Parents

who always support me in all aspects of my life

### ACKNOWLEDGMENTS

I would like to express my sincerest thanks to Prof. Dr. Yıldırım Üçtuğ for his guidance, support and encouragements throughout the preparation of this thesis.

I would also like to thank Asst. Prof. Dr. Ahmet Hava for his suggestions and comments.

I express my deepest gratitude to my parents, my father Halis, my mother Refika, my brother Çağlar and all my family members for their encouragements throughout my education life. Their love, care and encouragement has given me a great inner strength to success. This work is dedicated to them.

I would also like to thank YILDIRIM ELEKTRONIK TIC.SAN. LTD. STI, especially to Mr. Süleyman Alkan for their supports during my study period.

I am grateful to my friends in Middle East Technical University for all the support they gave me throughout my study.

# TABLE OF CONTENTS

| PLAGIARISM                                              | iii   |

|---------------------------------------------------------|-------|

| ABSTRACT                                                | iv    |

| ÖZ                                                      | v     |

| DEDICATION                                              | . vi  |

| ACKNOWLEDGEMENTS                                        | . vii |

| OF CONTENTS                                             | viii  |

| LIST OF FIGURES                                         | . xii |

| LIST OF TABLES                                          | xvi   |

| CHAPTER                                                 |       |

| 1. INTRODUCTION                                         | 1     |

| 1.1 Background                                          | 1     |

| 1.2 Definitions                                         | 4     |

| 1.3 Harmonics and Effects on the Mains                  | 7     |

| 1.4 Harmonic Current Emission Standards                 | 8     |

| 1.5 Power Factor Correction Methods                     | . 17  |

| 1.5.1 PFC Design Criteria                               | . 18  |

| 1.5.2 Passive Approach                                  | . 19  |

| 1.5.3 Active PFC                                        | . 20  |

| 1.5.3.1 Active Two-Stage Approach                       | . 22  |

| 1.5.3.2 Active Single-Stage Approach                    | . 24  |

| 1.5.4 Comparison of PFC Solutions                       | . 25  |

| 1.6 Objective and Organization                          | . 27  |

| 2. PASSIVE POWER FACTOR CORRECTION                      | . 28  |

| 2.1 Single Phase Full-Wave Rectifier                    | . 28  |

| 2.2 Passive Power Factor Correction Methods             | . 35  |

| 2.2.1 LC Filter Method                                  | . 35  |

| 2.2.1.a Experimental Implementation of LC Filter Method | . 46  |

| 2.2.2 Series Connected Parallel Resonant Filter         | . 56  |

| 2.2.2.a Experimental Evaluation of 3rd Harmonic Filter  | .58   |

|                                                         |       |

| 2.2.3 Variable Inductance LC Filter Method                  | 60  |

|-------------------------------------------------------------|-----|

| 2.2.3.a Saturated Core Inductors                            |     |

| 2.2.3.b Step-Gap Variable Inductor                          | 65  |

| 2.2.3.c Sloped Air-Gap Inductor                             | 67  |

| 2.2.3.d Design of Sloped Gap Inductance                     | 70  |

| 2.2.3.e Experimental Evaluation of SAG LC Filter Method     | 73  |

| 2.3 Limitations of Passive PFC Circuits                     | 76  |

| 3. AVERAGE CURRENT CONTROL OF PFC                           | 77  |

| 3.1 Description of Average Current Mode Control of PFC      | 77  |

| 3.2 Power Balance Analysis of the PFC Circuit               | 79  |

| 3.3 Input Voltage Feed-Forward                              | 83  |

| 3.4 Control Loop Design                                     | 89  |

| 3.4.1 Current Loop Design                                   | 90  |

| 3.4.2 Voltage Loop Design                                   |     |

| 3.5 Simulation of Average Current Controlled PFC            |     |

| 3.6 Hardware Implementation of Average Current Control PFC  | 105 |

| 3.6.1 Functional Description of the Power Circuit           | 105 |

| 3.6.2 Functional Description of the Control Circuit         | 106 |

| 3.7 Design of the Average Current Controlled PFC            | 108 |

| 3.8 Experimental Results                                    | 118 |

| 3.9 Conclusion                                              | 124 |

| 4. CRITICAL CONDUCTION MODE CONTROL OF PFC                  | 125 |

| 4.1 Introduction                                            | 125 |

| 4.2 Operation of Critical Conduction Mode                   | 126 |

| 4.3 Analysis of Switching Characteristics                   | 129 |

| 4.4 Simulation of Boundary Conduction Mode PFC              | 133 |

| 4.5 Hardware Implementation of Boundary Conduction Mode PFC | 137 |

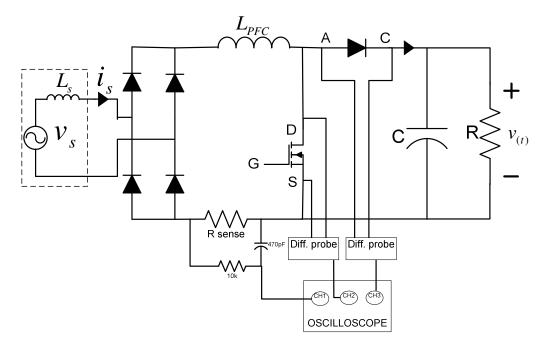

| 4.5.1 Functional Description of the Power Circuit           | 138 |

| 4.5.2 Functional Description of the Control Circuit         | 138 |

| 4.6 Design of the Boundary Conduction Mode PFC              | 140 |

| 4.7 Experimental Results                                    | 148 |

| 4.8 Conclusion                                              | 153 |

| 154 |

|-----|

| 154 |

| 155 |

| 158 |

| 162 |

| 163 |

| 163 |

| 165 |

| 174 |

| 176 |

| 177 |

| 177 |

| 178 |

| 185 |

| 185 |

| 187 |

| 188 |

| 192 |

| 193 |

| 194 |

| 194 |

| 194 |

| 194 |

| 197 |

| 198 |

| 198 |

| 199 |

| 205 |

| 206 |

| 206 |

| 206 |

| 206 |

|     |

| 6.9 Experiment 4– Variable Inductance (SAG Inductor) Method |     |

|-------------------------------------------------------------|-----|

| 6.9.1 Introduction                                          |     |

| 6.9.2 Procedure                                             |     |

| 6.9.3 Study Questions                                       |     |

| 6.10 Experiment 5– Active Power Factor Correction           |     |

| 6.10.1 Introduction                                         |     |

| 6.10.2 Procedure                                            |     |

| 6.10.3 Study Questions                                      |     |

| 7.CONCLUSIONS AND FURTHER WORK                              |     |

| REFERENCES                                                  | 221 |

| APPENDIX                                                    |     |

# LIST OF FIGURES

# FIGURES

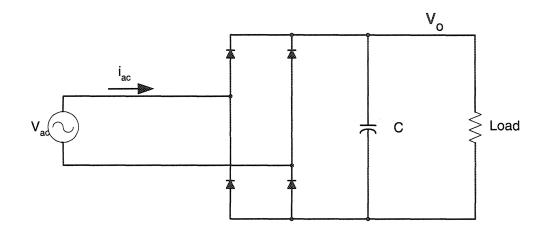

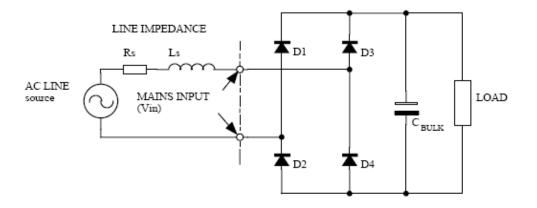

| 1.1    | Single Phase Rectifier with Capacitive Smoothing                            | 2    |

|--------|-----------------------------------------------------------------------------|------|

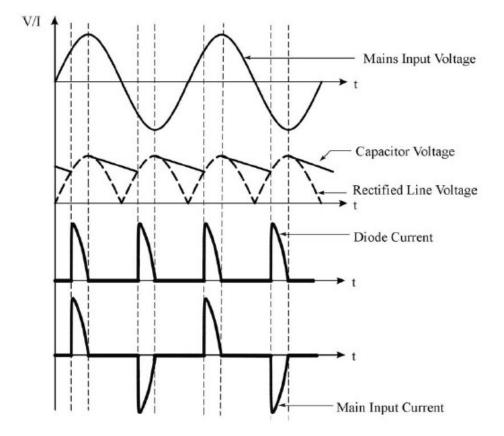

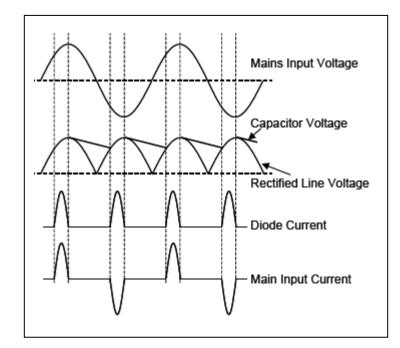

| 1.2    | Waveforms for Single Phase Rectifier with Capacitive Smoothing              | 2    |

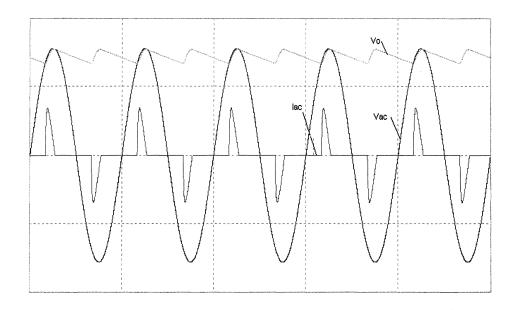

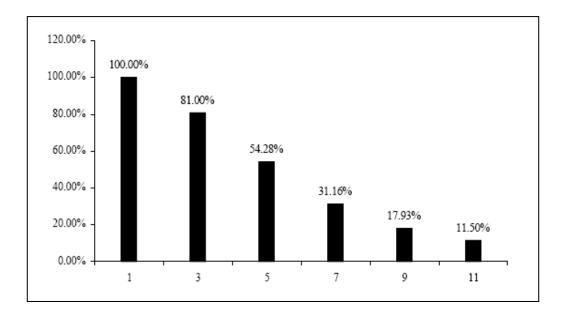

| 1.3    | Input Current Harmonics of Single Phase Rectifier with Capacitive Smoothing | 3    |

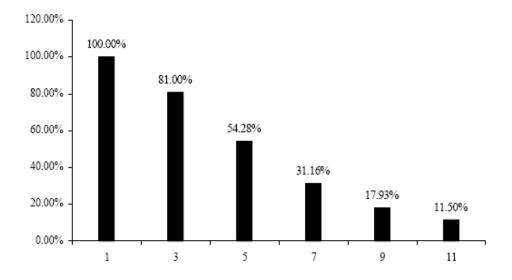

| 1.4    | Different Current and Voltage waveforms of Single Phase Rectifier           | 6    |

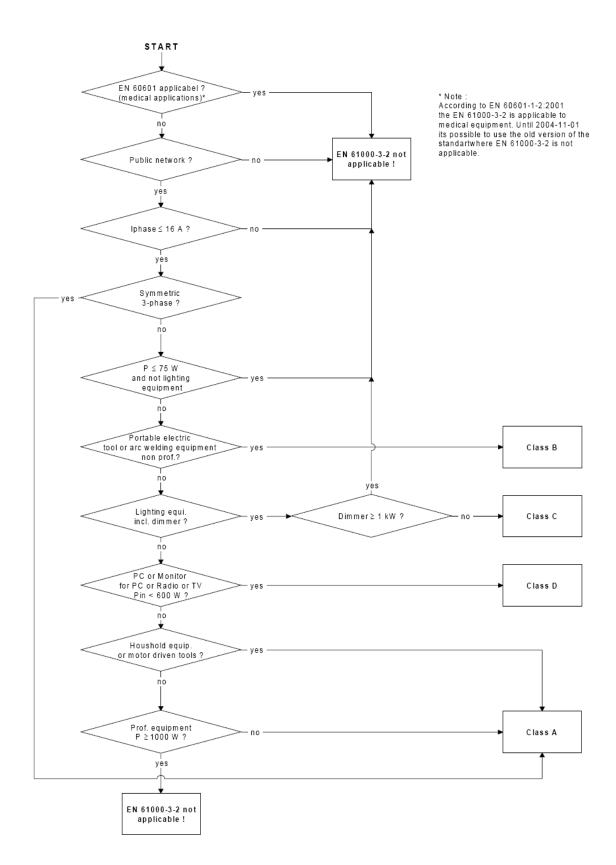

| 1.5    | Equipment Classification Chart according to IEC 61000-3-2, A14              |      |

|        | Standard                                                                    | . 13 |

| 1.6    | Envelope of the input current used to classify Class D equipment, as        |      |

|        | defined in the first edition of IEC 61000 -3-2                              | . 14 |

| 1.7    | Simple passive PFC circuit                                                  | . 19 |

| 1.8    | a) two-stage PFC b) single-stage PFC                                        | . 22 |

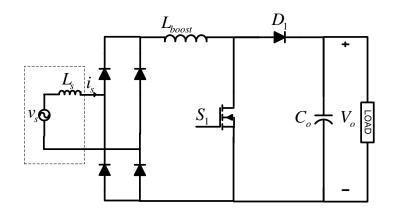

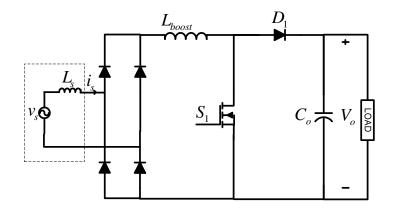

| 1.9    | Boost Type Active PFC                                                       | . 23 |

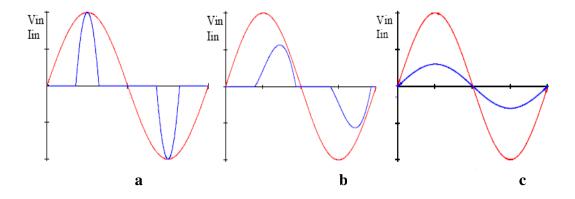

| 1.10   | Waveforms without/with PFC a) Without PFC b) Passive PFC c)Active PFC       | . 25 |

| 2.1    | Typical single phase rectifier                                              | . 28 |

| 2.2    | Current and Voltage Waveforms                                               | . 29 |

| 2.3    | Current Harmonics                                                           | . 30 |

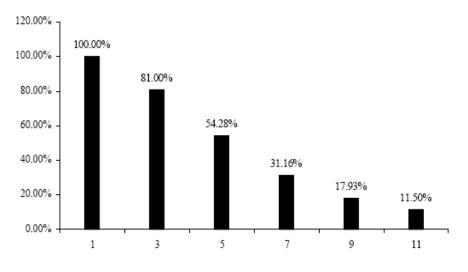

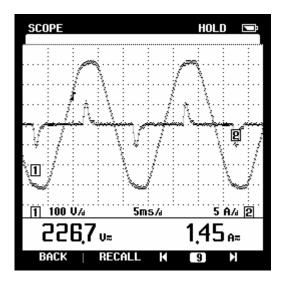

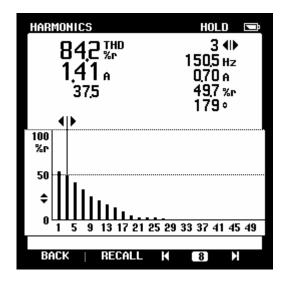

| 2.4.1  | I Input current and voltage waveforms for single phase rectifier            | 31   |

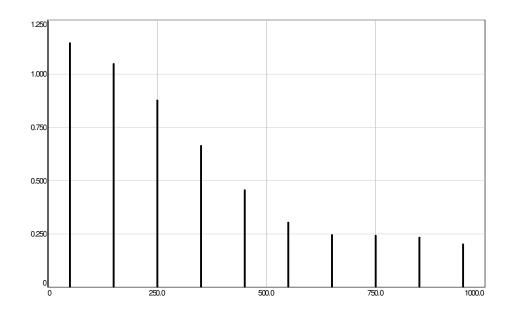

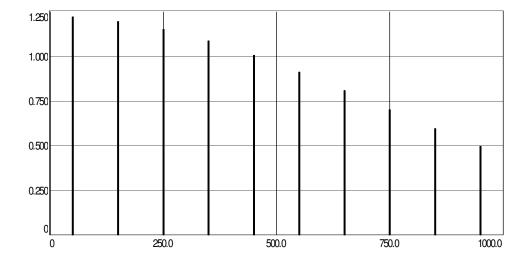

| 2.4.2  | 2 Input Current Harmonics                                                   | . 32 |

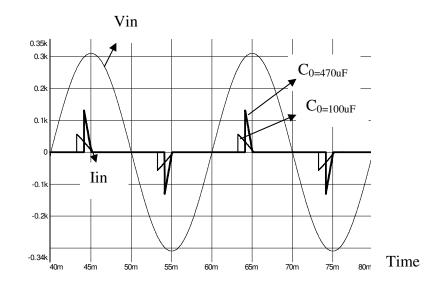

| 2.5    | Simulated input voltage and current waveforms with capacitive filter        | . 33 |

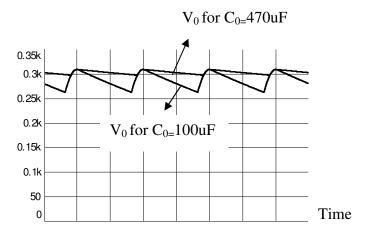

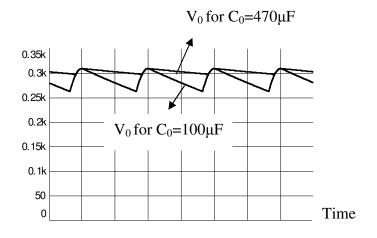

| 2.6    | Simulated output voltage ripple with capacitive filter                      | . 33 |

| 2.7    | Current harmonics spectrum for Co=100uF                                     | . 34 |

| 2.8    | Current harmonics for Co=470uF                                              | . 34 |

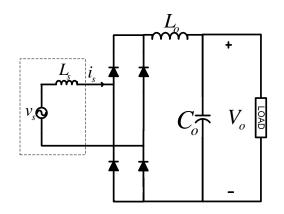

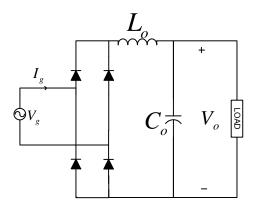

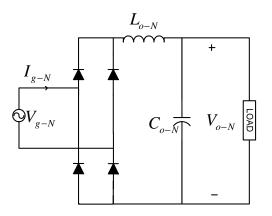

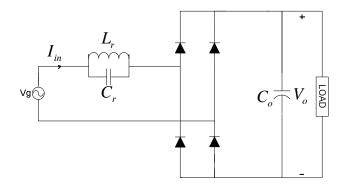

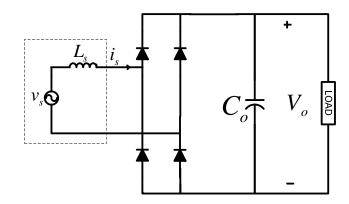

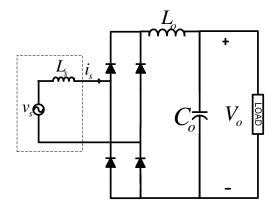

| 2.9 \$ | Single Phase Rectifier with LC Filter                                       | . 36 |

| 2.10   | Normalized single phase rectifier                                           | . 37 |

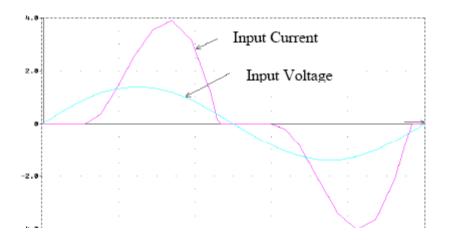

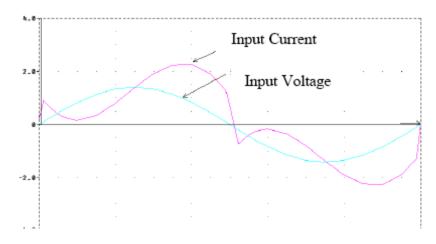

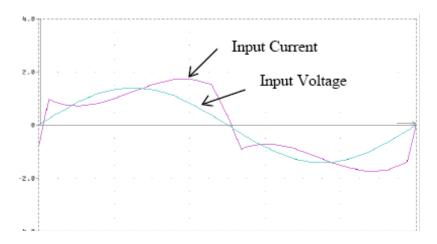

| 2.11   | Simulated waveform for Lo-N=0.01                                            | . 39 |

| 2.12   | Simulated waveform for Lo-N=0.043                                           | 40   |

| 2.13   | Simulated waveform for Lo-N=0.09mH                                          | 40   |

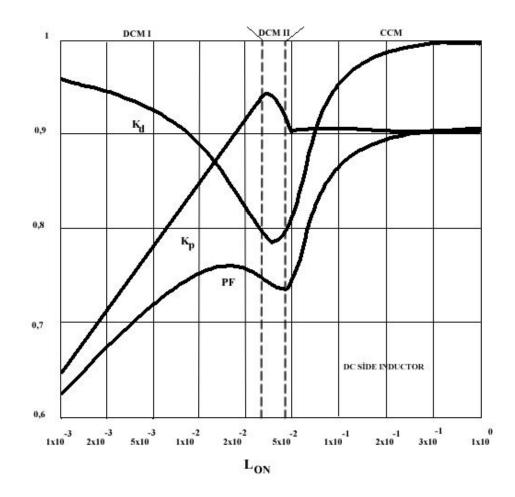

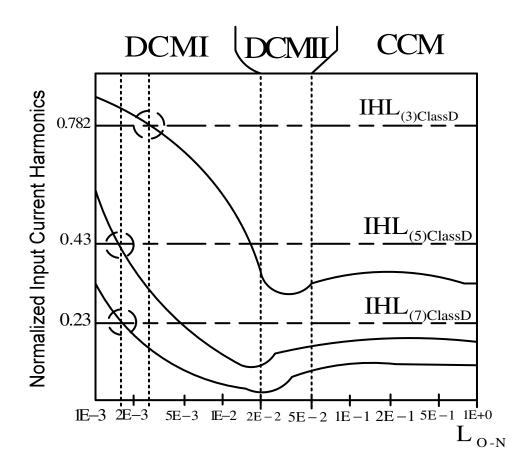

| 2.14   | PF, DF and DP as function of $L_{O-N}$                                      | . 41 |

|        |                                                                             |      |

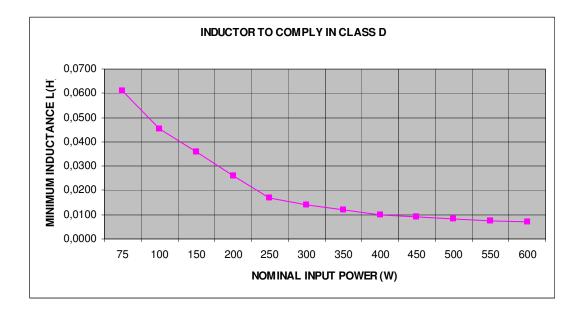

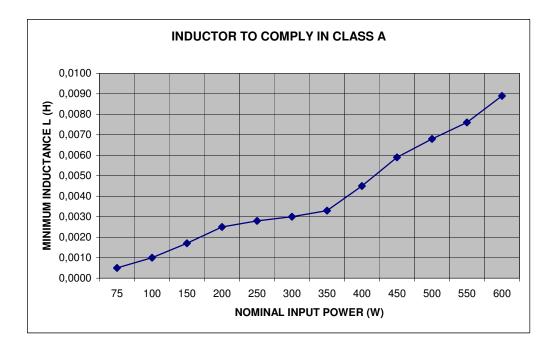

| 2.15 Normalized Class D harmonic limits and Normalized input current                 |      |

|--------------------------------------------------------------------------------------|------|

| harmonics versus normalized filter inductance $L_{O-N}$                              | 43   |

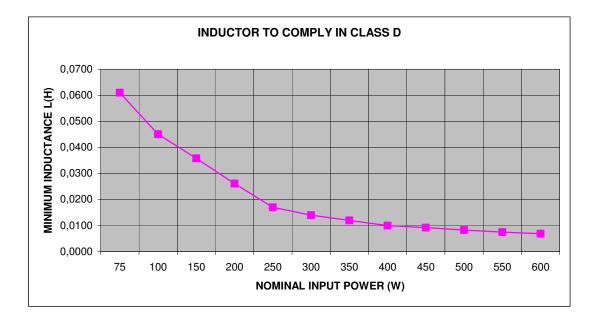

| 2.16 Minumum required inductance to comply with En 61000- 3-2 Class D                |      |

| harmonic limits                                                                      | 44   |

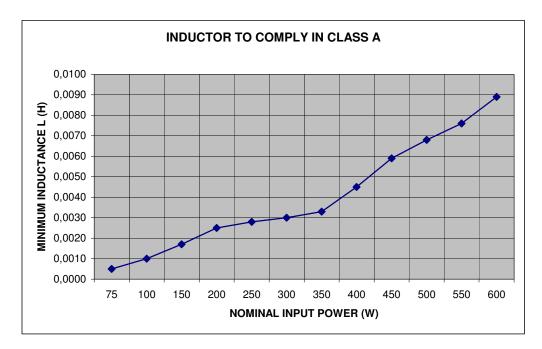

| 2.17 Minumum required inductance to comply with En 61000- 3-2 Class A                |      |

| harmonic limits                                                                      | . 45 |

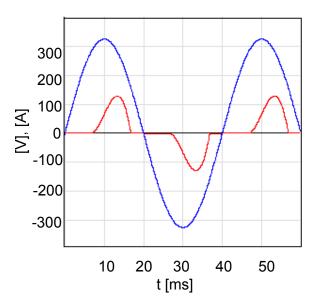

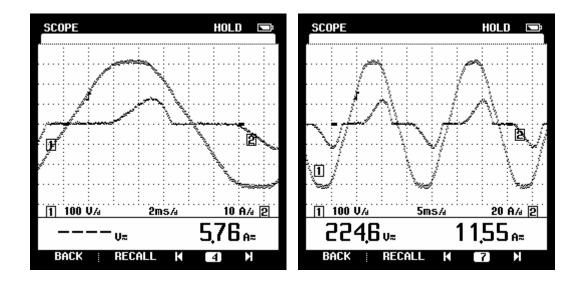

| 2.18 Simulated Input Current and Voltage Waveform for Class D-100W                   | . 47 |

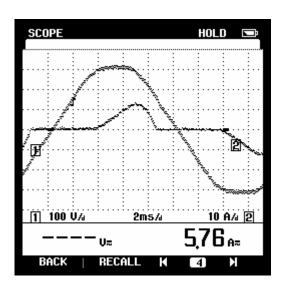

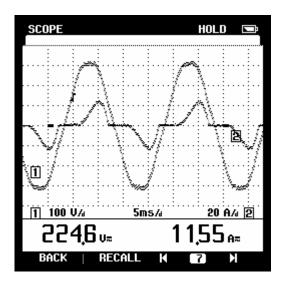

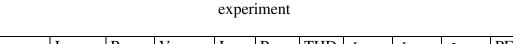

| 2.20 Measured Input voltage and Current for Class D-100W                             | . 47 |

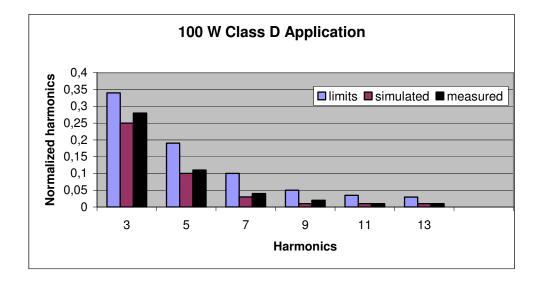

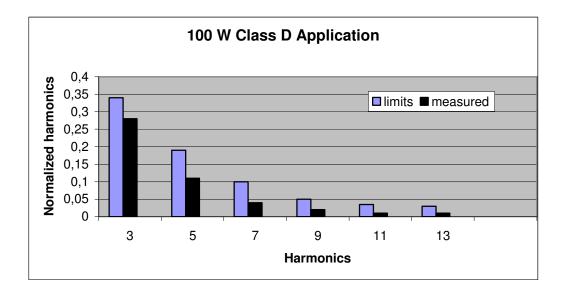

| 2.21 Harmonic Spectrum for Input Current For Class D – 100W                          | 48   |

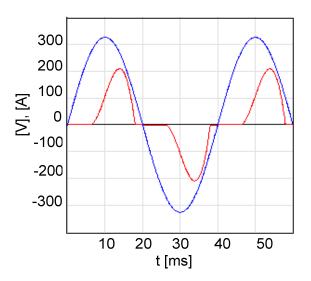

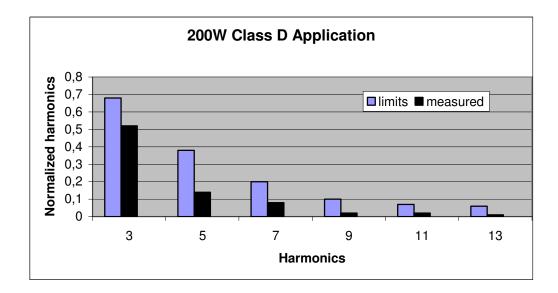

| 2.22 Simulated Input Current and Voltage Waveform for Class $D - 200W$               | . 49 |

| 2.23 Measured Input voltage and Current for Class D – 200W                           | . 50 |

| 2.24 Harmonic Spectrum for Input Current for Class D – 200W                          | 50   |

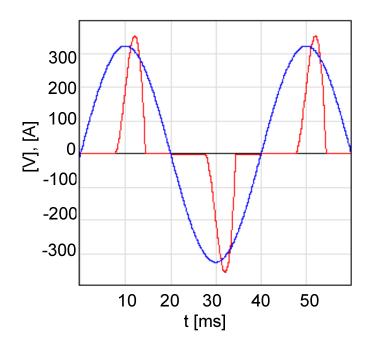

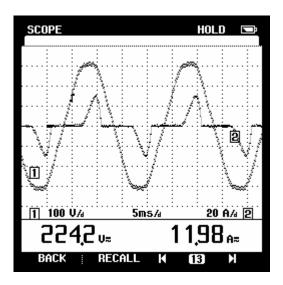

| 2.25 Simulated Input Current and Voltage Waveform for Class A – 100W                 | 52   |

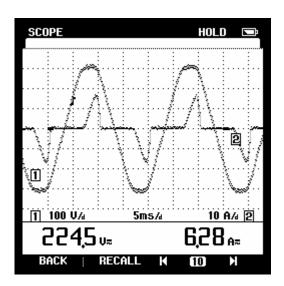

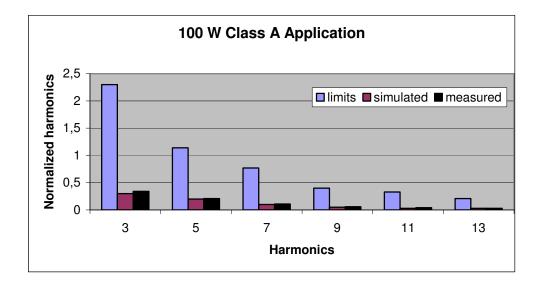

| 2.26 Measured Input Current Harmonics For Class A-100W                               | 52   |

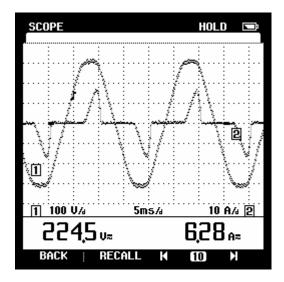

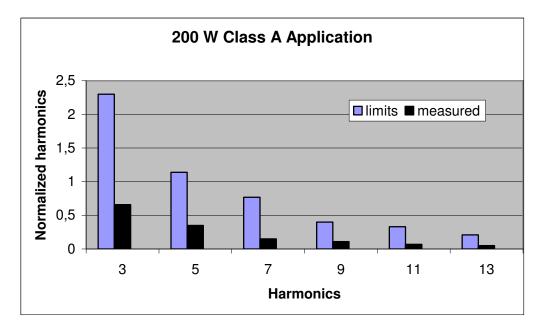

| 2.27 Harmonic Spectrum for Input Current for Class A – 100W                          | 53   |

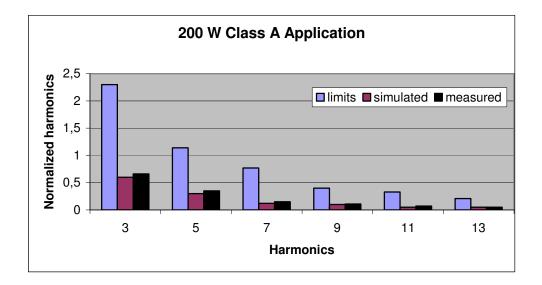

| 2.28 Simulated Input Current and Voltage Waveform for Class A – $200W$               | . 54 |

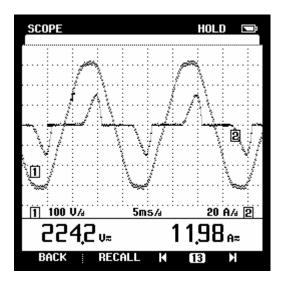

| 2.29 Measured Input voltage and Current for Class A – 200W                           | . 54 |

| 2.30 Harmonic Spectrum for Input Current for Class A – 200W                          | . 55 |

| 2.31 Series Connected Parallel Resonant Filter                                       | . 56 |

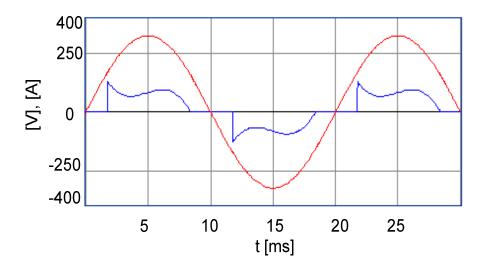

| 2.32 Input Current and Voltage Waveform for Series Connected Paralel Filter          | 58   |

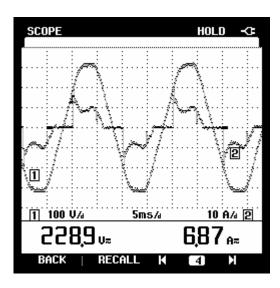

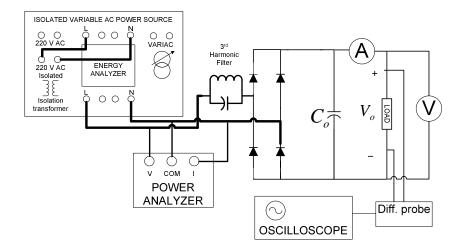

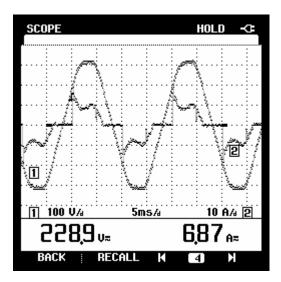

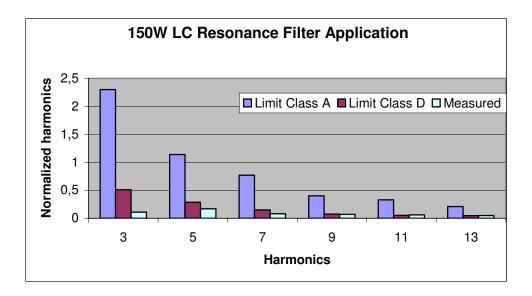

| 2.33 Measured current of series connected parallel resonant filter for 150W System . | 59   |

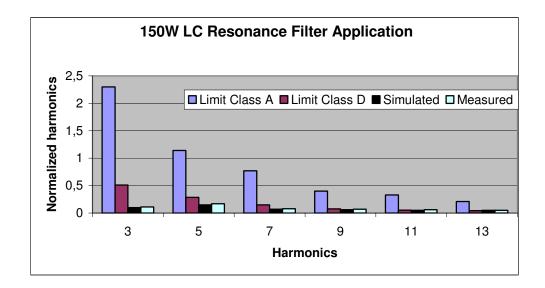

| 2.34 Input current harmonics for series connected parallel resonant filter           | 59   |

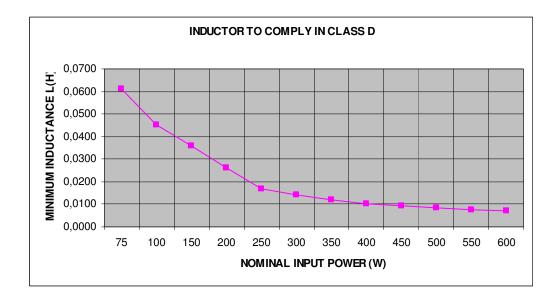

| 2.35 Required minimum Inductance for Class D                                         | 60   |

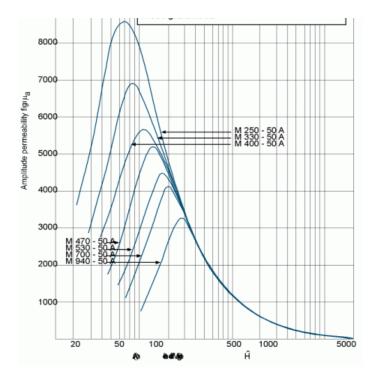

| 2.36 Relative Permeability versus magnetization force                                | 62   |

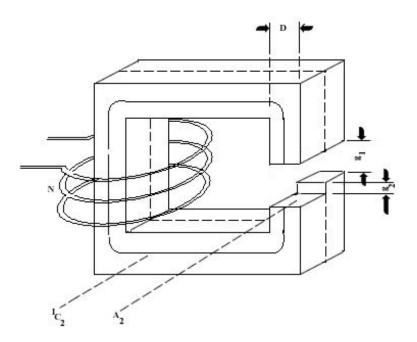

| 2.37 Constant Air-Gap Inductor                                                       | 63   |

| 2.38 Constant gap Variable Inductor                                                  | 64   |

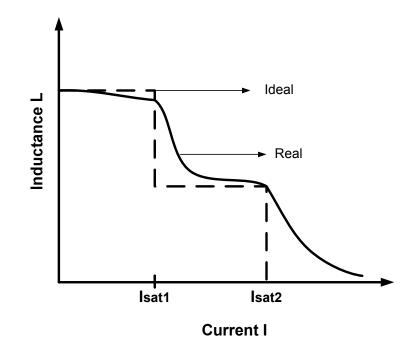

| 2.39 Swinging Inductor                                                               | 65   |

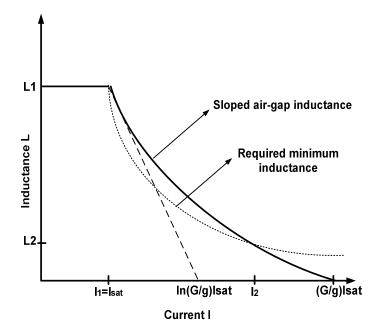

| 2.40 Swinging inductance variations                                                  | . 66 |

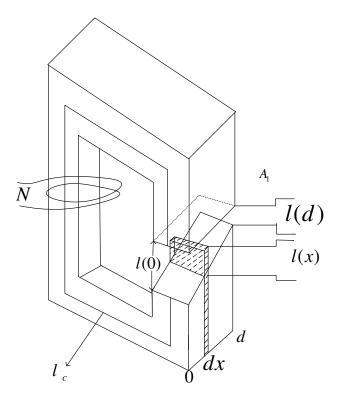

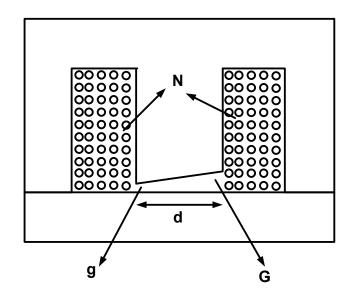

| 2.41 Sloped Air-Gap Inductance                                                       | . 67 |

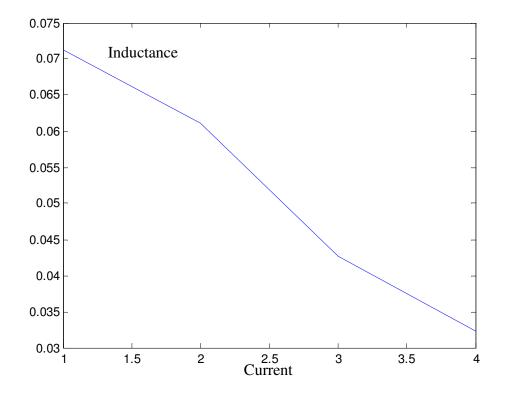

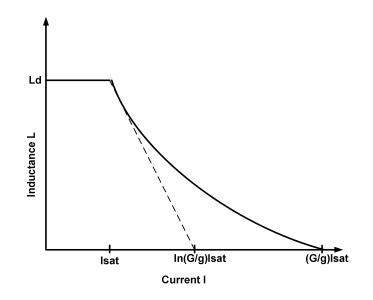

| 2.42 Inductance Variations of Sloped Air-Gap Inductor                                | 69   |

| 2.43 Inductance Variations of Sloped Air-Gap Inductor                                | . 70 |

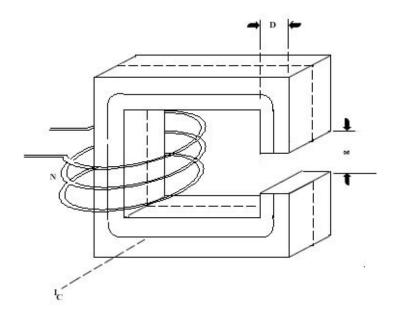

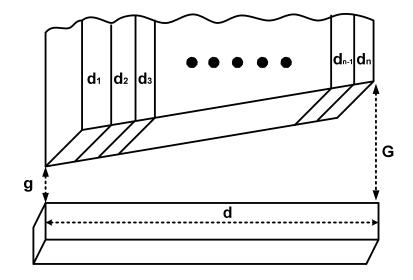

| 2.44 Construction of Sloped Air-Gap Inductor with EI Silicon Steel                   | . 71 |

| 2.45 Detailed view of the Sloped Air-Gap72                                             |

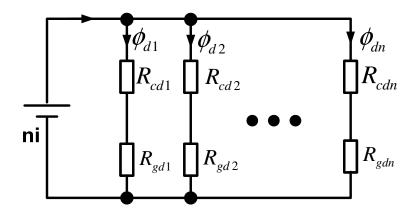

|----------------------------------------------------------------------------------------|

| 2.46 Magnetic Circuit of the Sloped Air-Gap Inductance                                 |

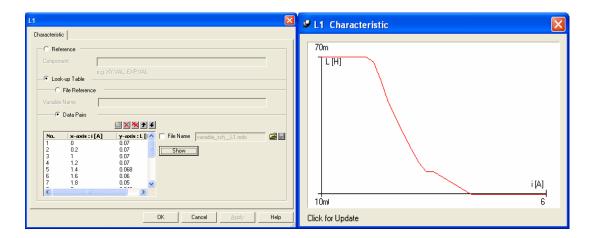

| 2.47 Variable Inductance Model used in Simulations                                     |

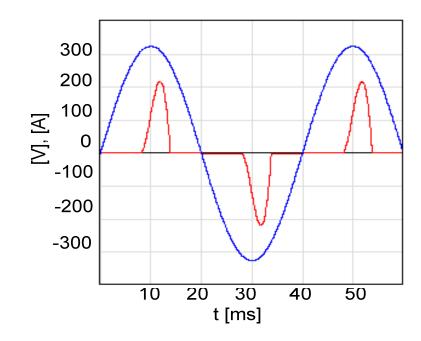

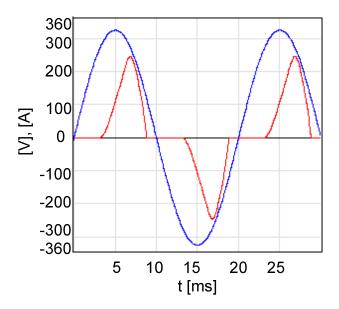

| 2.48 Simulation results for input voltage and current                                  |

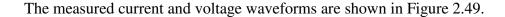

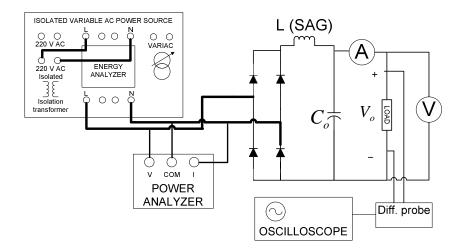

| 2.49 Experimental results for input voltage and current                                |

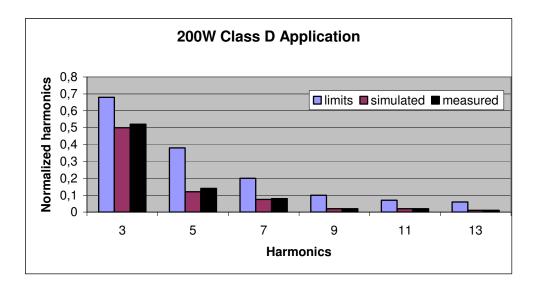

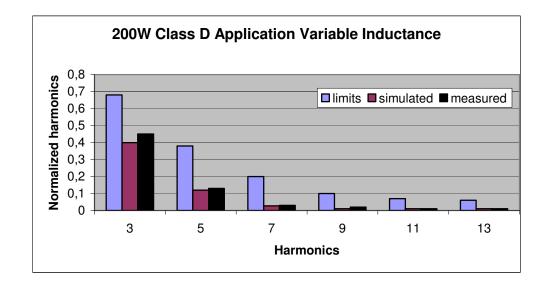

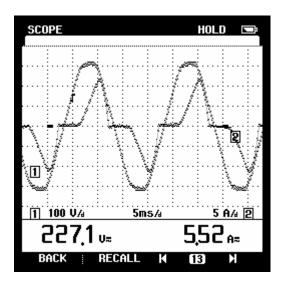

| 2.50 Input Current Harmonics for 200W Class-D Application                              |

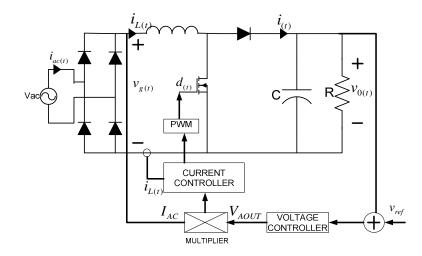

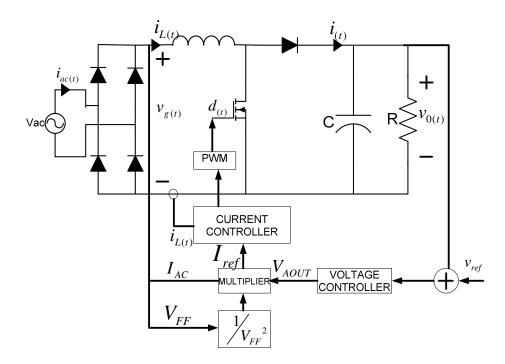

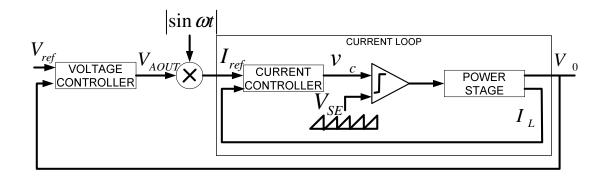

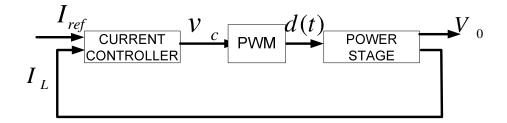

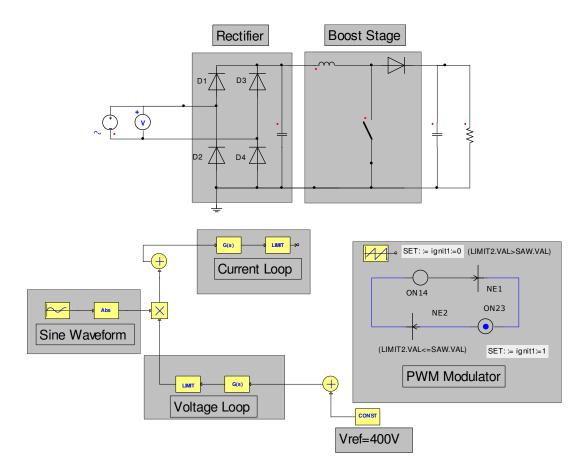

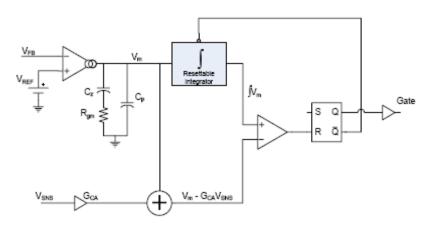

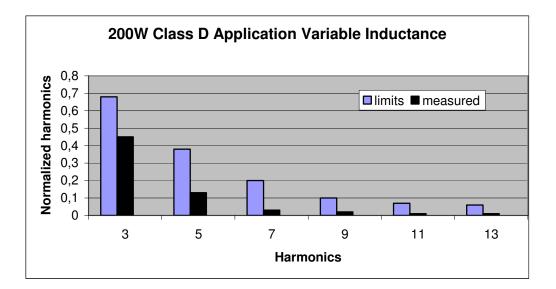

| 3.1 Average current mode control of PFC                                                |

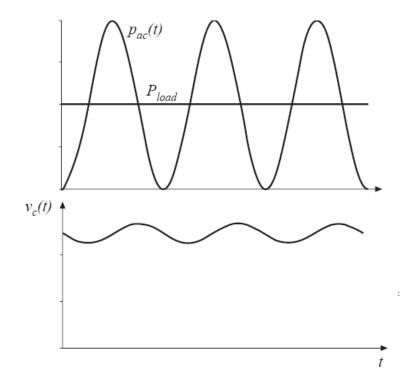

| 3.2 Variation on the capacitor voltage                                                 |

| 3.3 Multiplier based control                                                           |

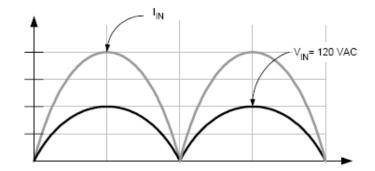

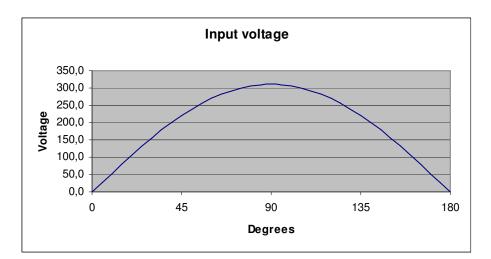

| 3.4 Rectified line voltage and current for 120-Vac line voltage                        |

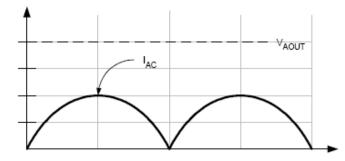

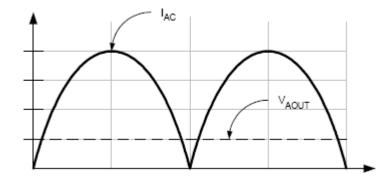

| 3.5 Multiplier inputs $I_{AC}$ and $V_{AOUT}$ at 120-Vac line voltage                  |

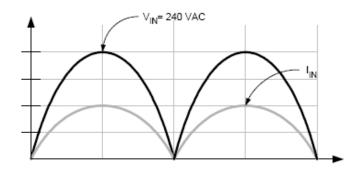

| 3.6 Rectified line voltage and current for 240-Vac line voltage                        |

| 3.7 Multiplier inputs $I_{AC}$ and $V_{AOUT}$ at 240-Vac line voltage                  |

| 3.8 Block diagram of the average current PFC with feed-forward                         |

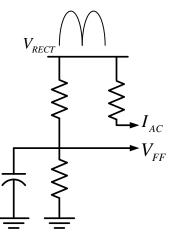

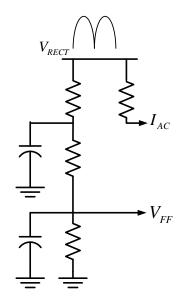

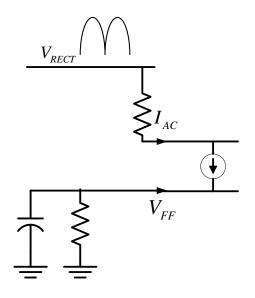

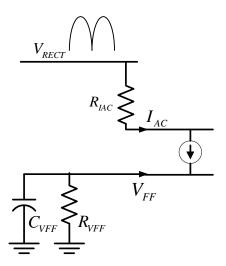

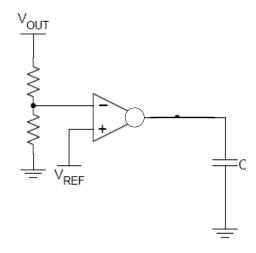

| 3.9 First order input voltage feed-forward sensing scheme                              |

| 3.10 Second order input voltage feed-forward sensing scheme                            |

| 3.11 First order input voltage feed-forward sensing scheme                             |

| 3.12 PFC control loops                                                                 |

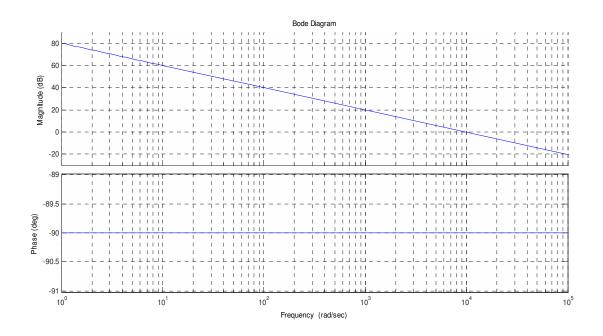

| 3.13 PFC current loop                                                                  |

| 3.14 Laplace domain block-schema of the current loop                                   |

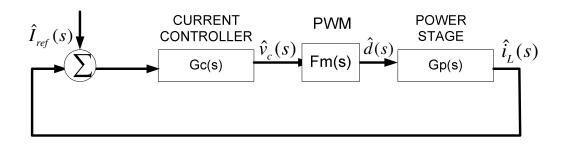

| 3.15 Linearized model of the PFC boost converter                                       |

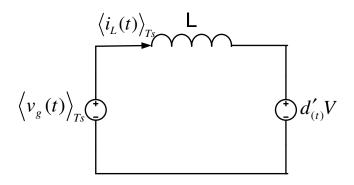

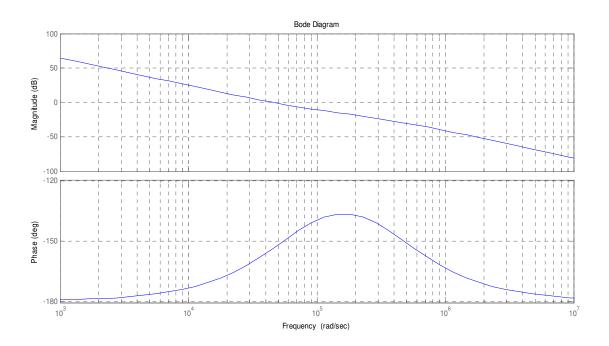

| 3.16 Magnitude and phase plots of the converter transfer function $G_{id}(s)$          |

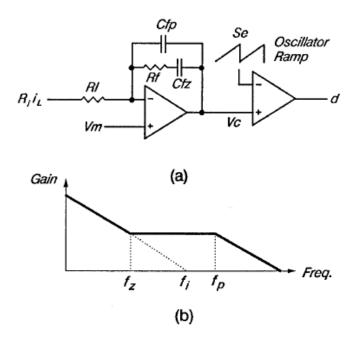

| 3.17 a) Circuit Diagram (b) Gain response of current compensator                       |

| 3.18 Compensated loop gain and phase plots of the inner current loop                   |

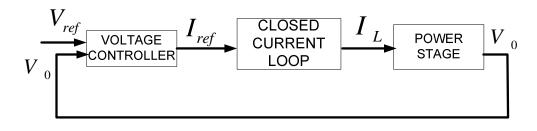

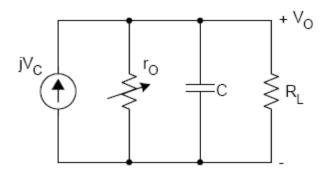

| 3.19 Voltage control loop                                                              |

| 3.20 Small signal model of outer loop                                                  |

| 3.21 Simulation block diagram of average current mode PFC99                            |

| 3.22 S-Transfer function for the voltage and current controller used in simulation 101 |

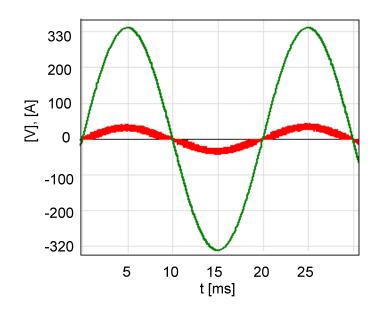

| 3.23 Line voltage and line current simulation waveforms for 220-V input voltage at     |

| 250-W PFC system 101                                                                   |

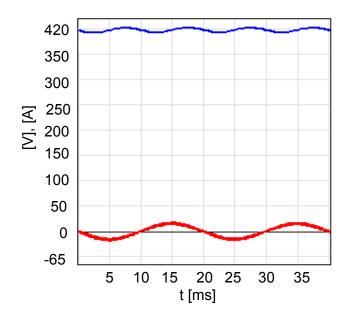

| 3.24 Output voltage and input current simulation waveforms for 220 V input voltage     |

| at 250-W PFC system                                                                    |

| 3.25 Line voltage and line current simulation waveforms for 120 V input voltage at   |

|--------------------------------------------------------------------------------------|

| 250-W PFC system                                                                     |

| 3.26 Output voltage and input current simulation waveforms for 120V input voltage    |

| at 250W PFC system                                                                   |

| 3.27 Step response for output voltage and input current simulation waveforms for     |

| 220 V input voltage at half-load to full-load step                                   |

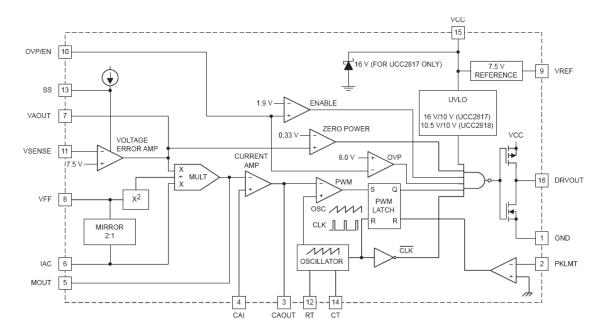

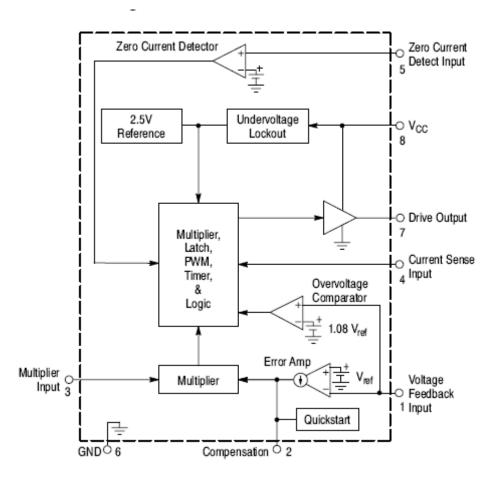

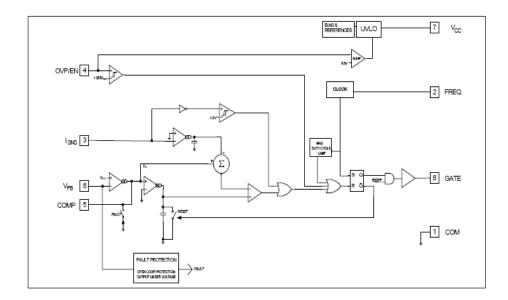

| 3.28 Block diagram of the UCC3818 controller IC                                      |

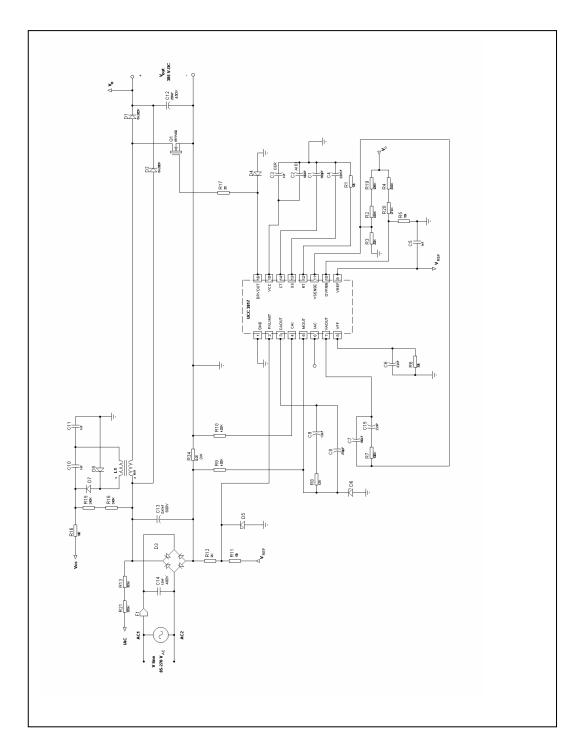

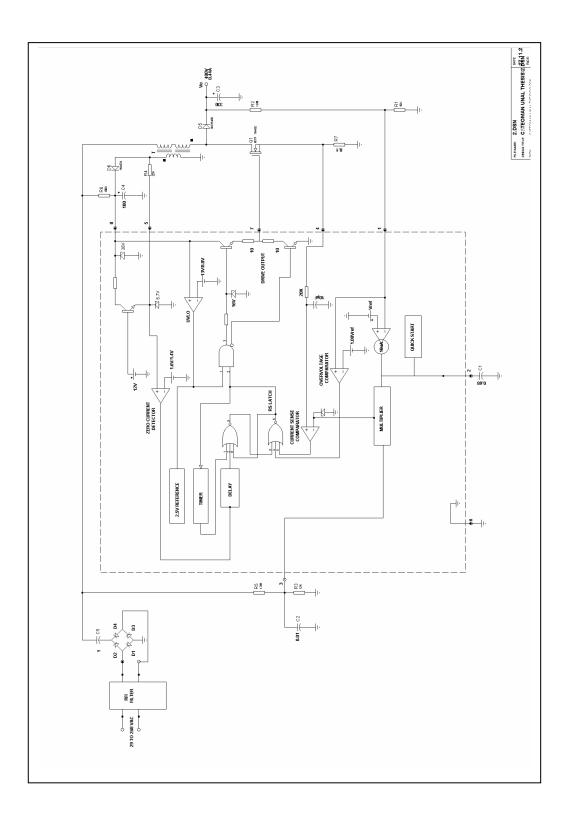

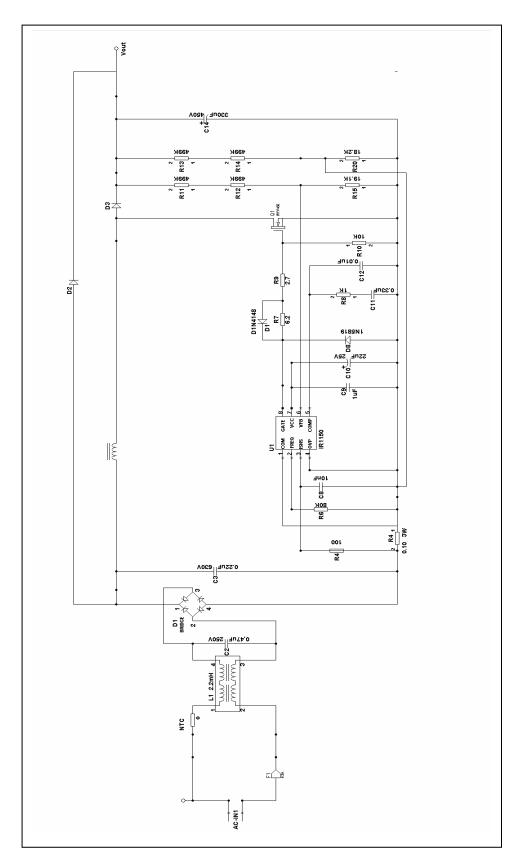

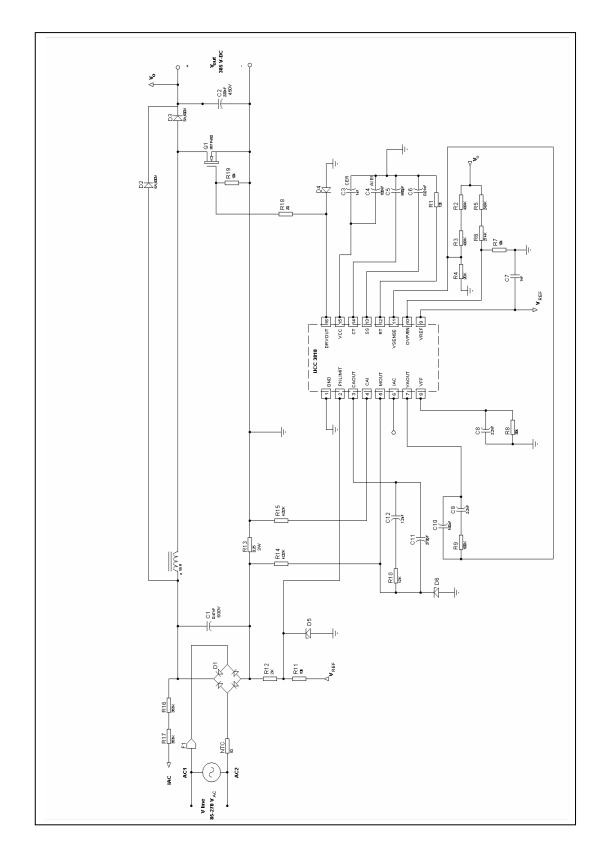

| 3.29 Schematic diagram of the 250-W, average current controlled PFC 110              |

| 3.30 Feed-forward circuit for the UCC3818 IC                                         |

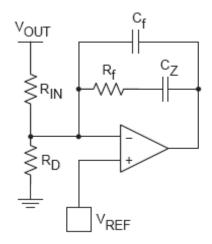

| 3.31 Output voltage compensator configuration                                        |

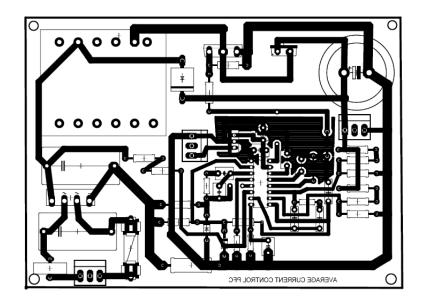

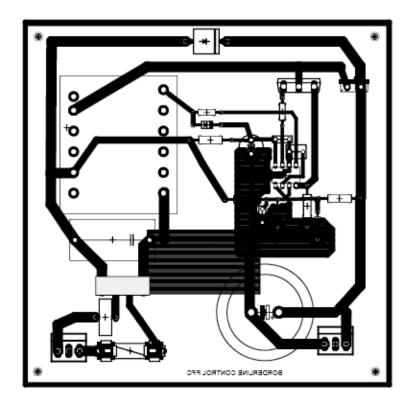

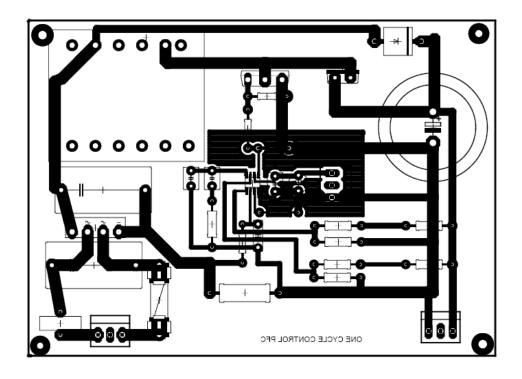

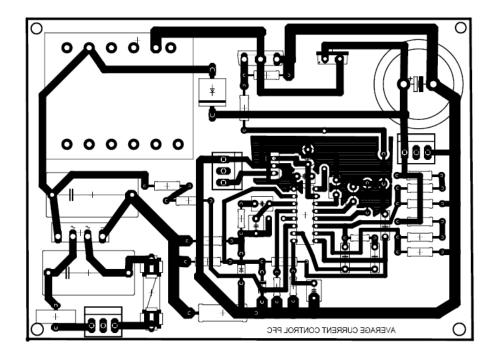

| 3.32 PCB layout of the average current mode PFC circuit                              |

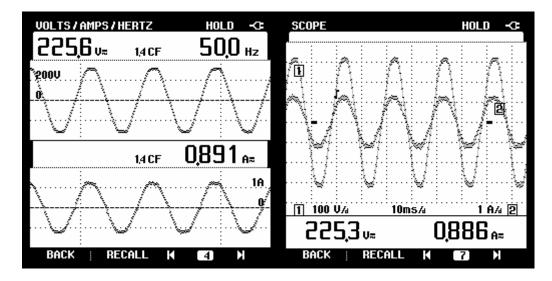

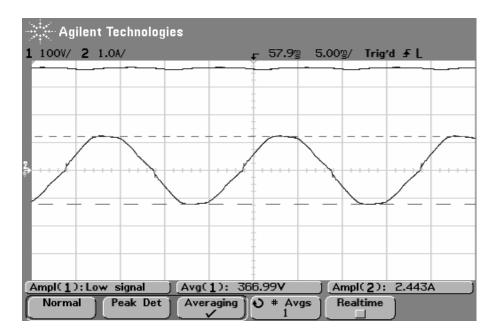

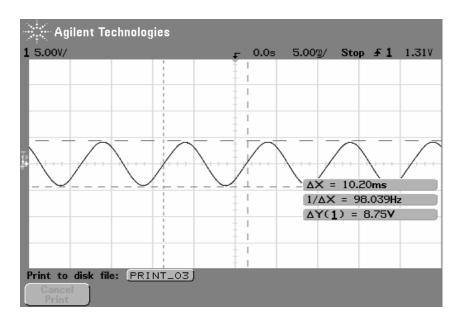

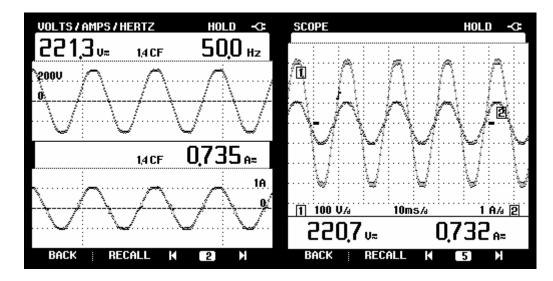

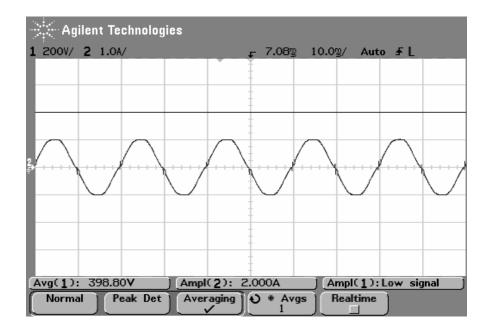

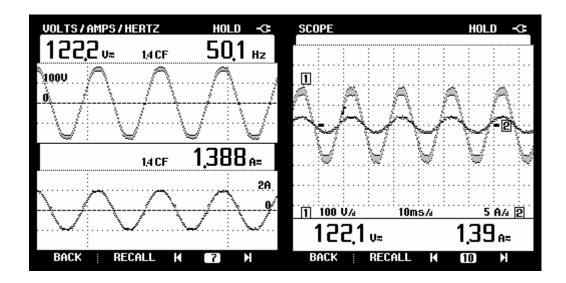

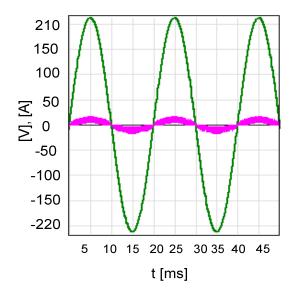

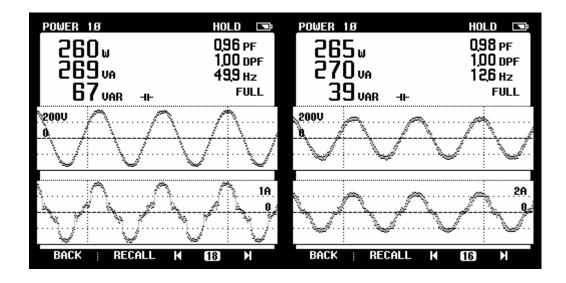

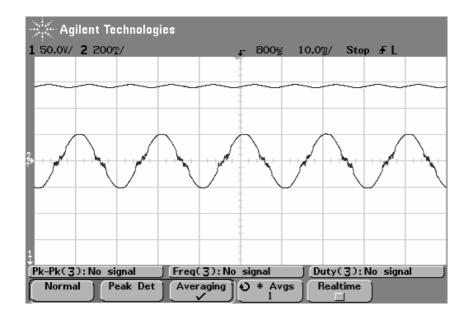

| 3.33 Input voltage and input current waveforms                                       |

| 3.34 Input current harmonic spectrum                                                 |

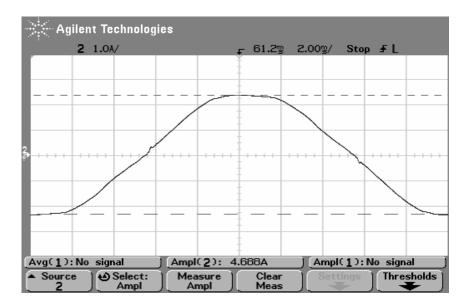

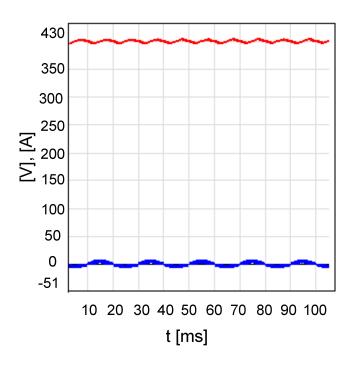

| 3.35 Output voltage and input current waveform                                       |

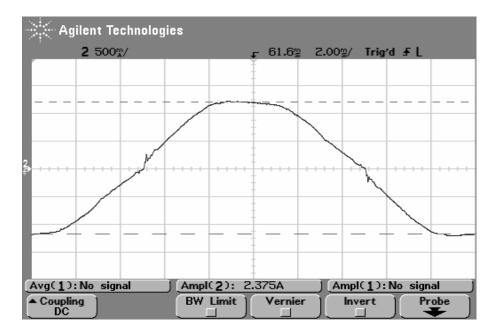

| 3.36 Input current distortions around zero crossings                                 |

| 3.37 Input voltage and input current waveforms                                       |

| 3.38 Input current harmonic spectrum                                                 |

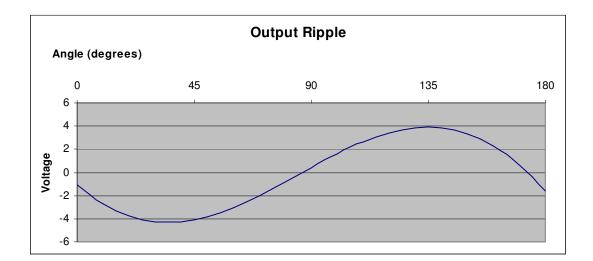

| 3.39 Output voltage ripple waveform                                                  |

| 3.40 Input current distortions around zero crossings                                 |

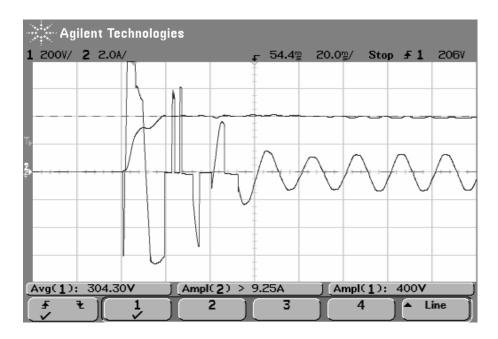

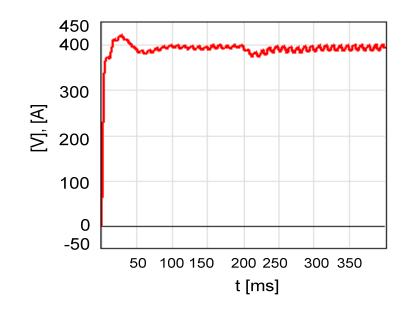

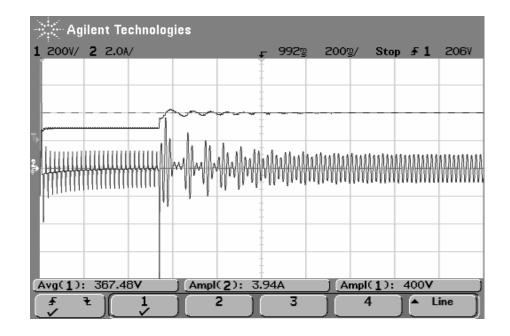

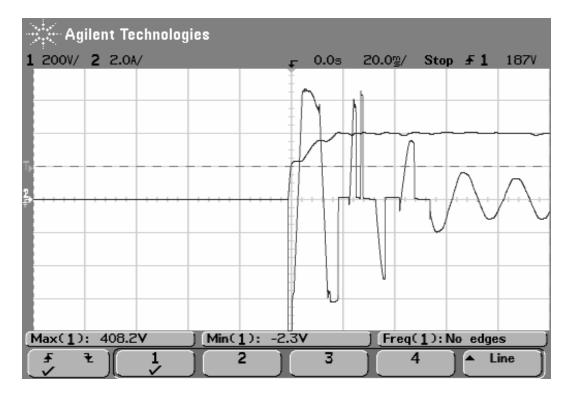

| 3.41 Start-up behavior of the input current and output voltage                       |

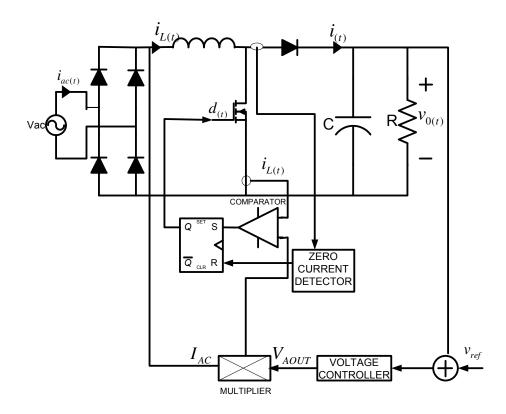

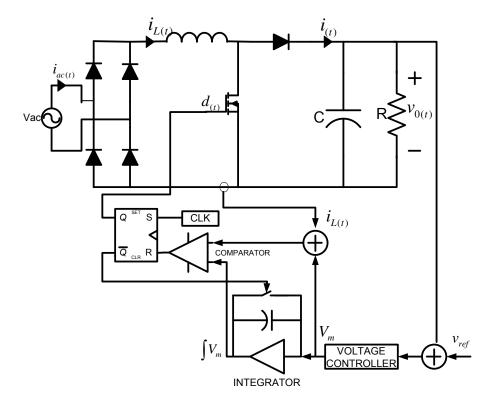

| 4.1 Block diagram of a BCM boost converter                                           |

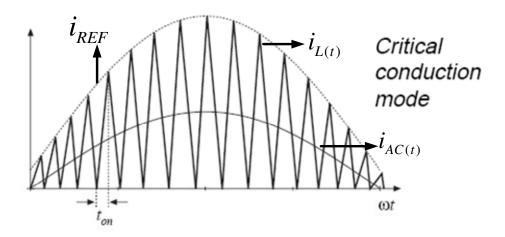

| 4.2 Current waveforms during half of an AC line cycle                                |

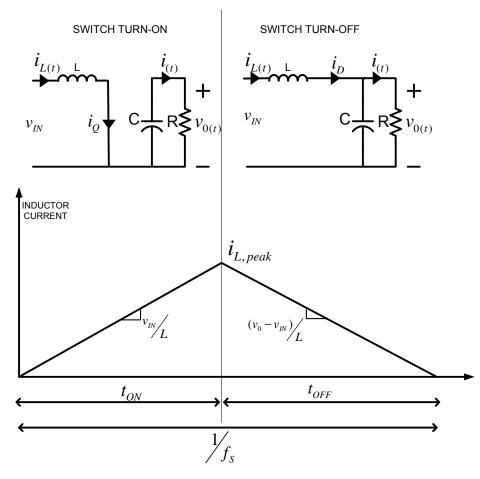

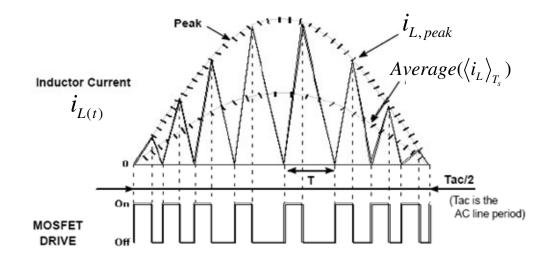

| 4.3 Switching sequences of PFC Stage                                                 |

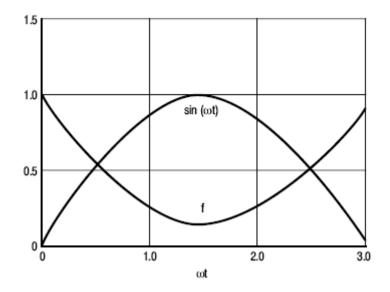

| 4.4 Inductor Current and Corresponding Gate Signals                                  |

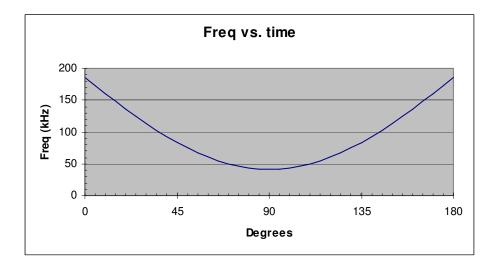

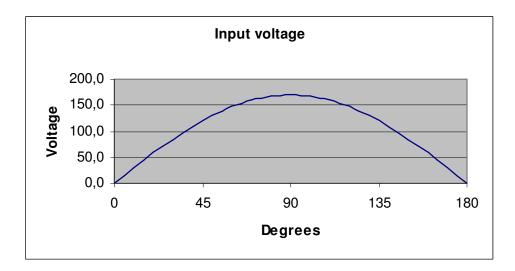

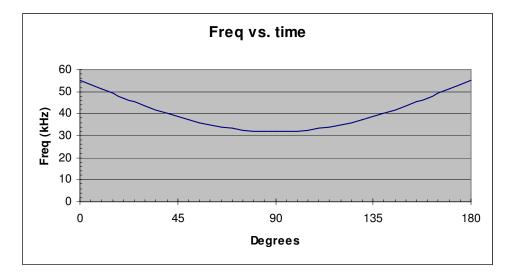

| 4.5 Switching frequency over the AC line cycle                                       |

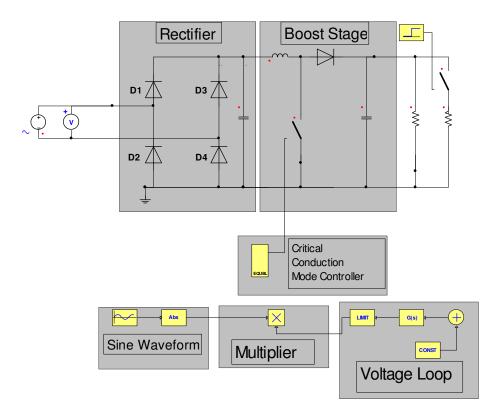

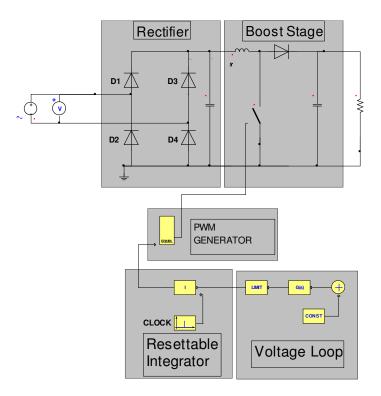

| 4.6 Block diagram of simulation circuit                                              |

| 4.7 Voltage controller s-transfer function and current controller equation block 135 |

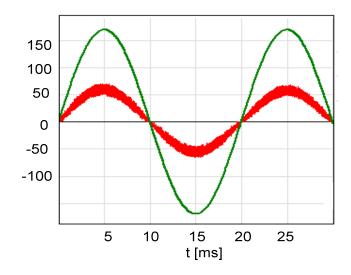

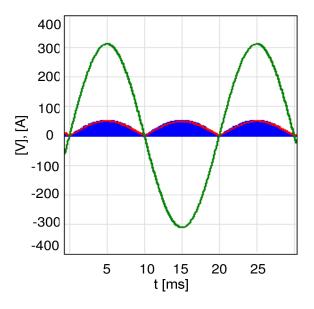

| 4.8 Line voltage, reference inductor current and actual inductor current simulation  |

| waveforms for 220 V input voltage at 150 W PFC 135                                   |

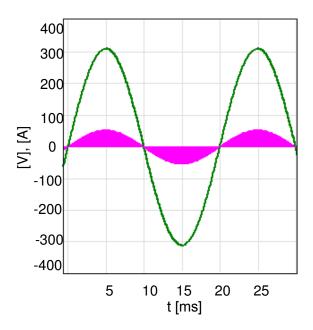

| 4.9 Line voltage and input current simulation waveforms for 220 V input voltage at   |

| 150 W PFC system                                                                     |

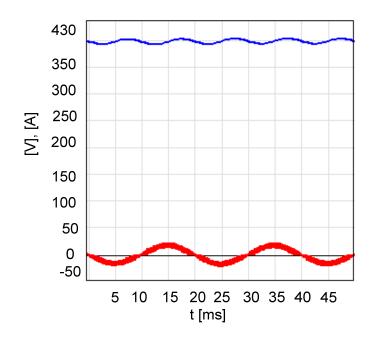

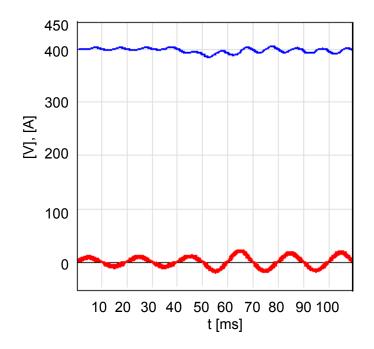

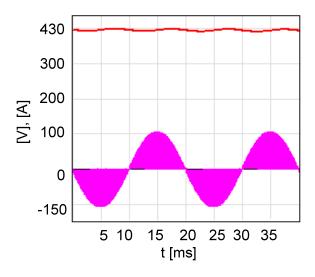

| 4.10 Output voltage and input current simulation waveforms for 220 V input voltage    |

|---------------------------------------------------------------------------------------|

| at 150 W PFC system                                                                   |

| 4.11 Transient response for output voltage simulation waveforms for                   |

| 220 V input voltage at start-up and half-load to full-load step                       |

| 4.12 Block diagram of the MC34262 controller IC                                       |

| 4.13 Schematic diagram of the 150W, critical current mode PFC 142                     |

| 4.14 Switching frequency for 220VAC line voltage for critical current mode PFC 144    |

| 4.15 Switching frequency for 120VAC line voltage for critical current mode PFC 145    |

| 4.16 Output voltage ripple                                                            |

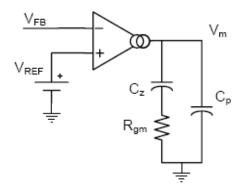

| 4.17 Transconductance type amplifier configuration                                    |

| 4.18 PCB layout of the critical conduction mode PFC circuit148                        |

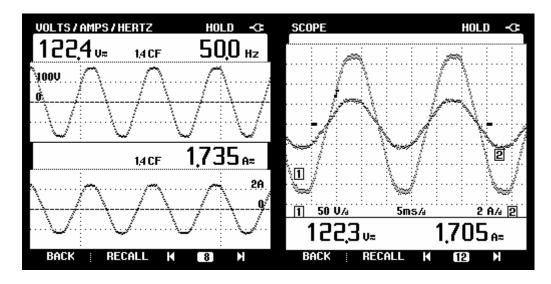

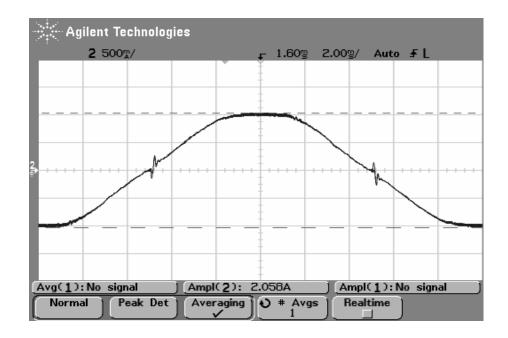

| 4.19 Input voltage and input current waveforms                                        |

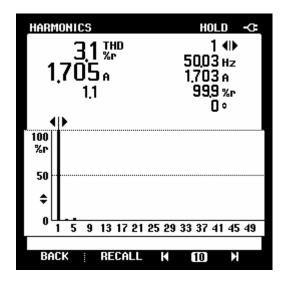

| 4.20 Input current harmonic spectrum                                                  |

| 4.21 Output voltage and input current waveforms                                       |

| 4.22 Input current distortions around zero crossings                                  |

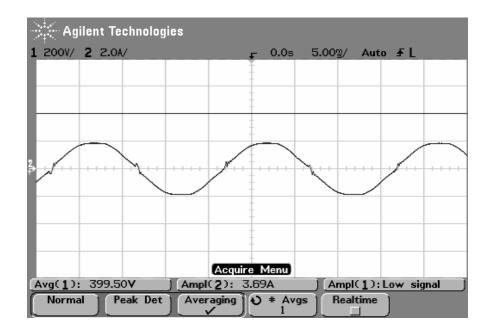

| 4.23 Input voltage and input current waveforms                                        |

| 4.24 Input voltage and input current waveforms                                        |

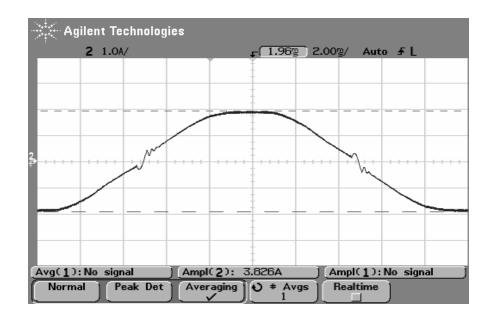

| 4.25 Output voltage and input current waveforms                                       |

| 4.26 Input current distortions around zero crossings                                  |

| 4.27 Start-up behavior of the input current and output voltage                        |

| 5.1 One cycle control of PFC                                                          |

| 5.2 Transconductance type error amplifier                                             |

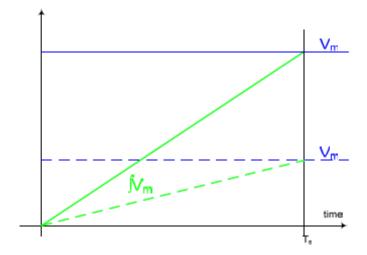

| 5.3 Resettable integrator characteristics                                             |

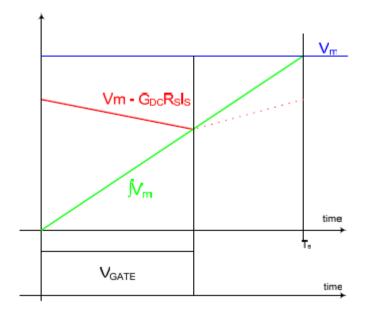

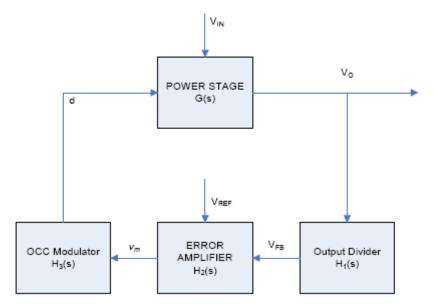

| 5.4 Block diagram of OCC                                                              |

| 5.5 PWM signal generation                                                             |

| 5.6 Simulation circuit of one cycle control                                           |

| 5.7 Simulation blocks a) Output voltage controller b) Resettable integrator 160       |

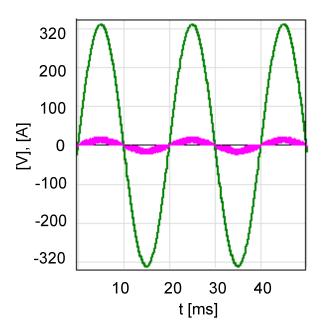

| 5.8 Input voltage and current simulation waveforms for 220Vac input voltage 161       |

| 5.9 Input voltage and input current simulation waveforms for 150Vac input voltage 161 |

| 5.10 Input voltage and input current simulation waveforms for 150Vac input voltage162 |

| 5.11 Block diagram of IR1150 PFC controller                                           |

| 5.12 Schematic of 250W PFC converter with IR1150                                      |

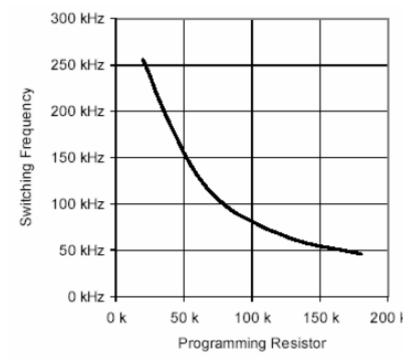

| 5.13 Switching frequency vs. programming resistor.                                  | 168 |

|-------------------------------------------------------------------------------------|-----|

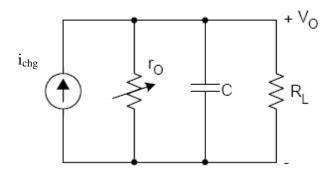

| 5.13 Outer voltage loop                                                             | 170 |

| 5.14 Small signal model of outer loop                                               | 171 |

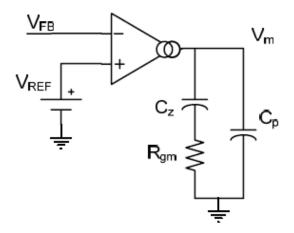

| 5.15 Voltage error amplifier                                                        | 173 |

| 5.16 PCB layout of one cycle control PFC converter.                                 | 174 |

| 5.17 Input voltage and input current waveforms a) 220Vac                            | 175 |

| 5.18 Output voltage and input current waveforms                                     | 176 |

| 6.1 Single-phase diode rectifier with bulk capacitive filter                        | 179 |

| 6.2 Waveforms for single-phase rectifier with capacitive smoothing                  | 180 |

| 6.3 Input current harmonics for a single-phase rectifier with capacitive smoothing  | 181 |

| 6.4 Simple passive PFC circuit.                                                     | 183 |

| 6.5 Boost type active PFC                                                           | 184 |

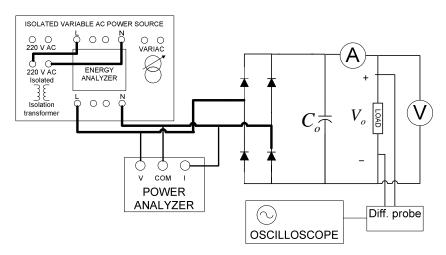

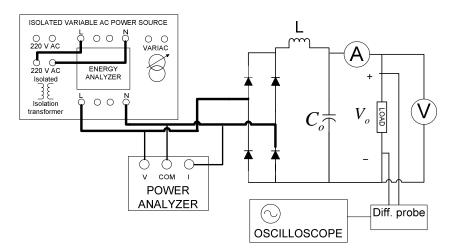

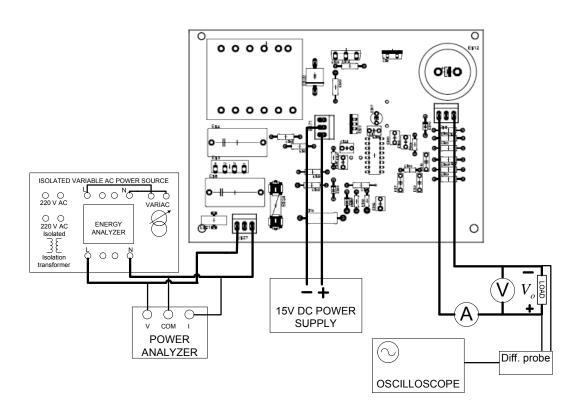

| 6.6 Experiment system for single-phase power factor correction                      | 185 |

| 6.7 Isolated, variable AC power supply                                              | 186 |

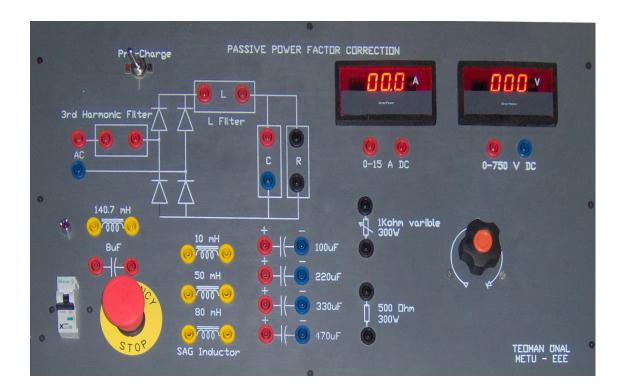

| 6.8 Passive power factor correction unit                                            | 187 |

| 6.9 Active power factor correction circuit                                          | 189 |

| 6.10 Circuit layout                                                                 | 189 |

| 6.11 Schematic diagram of 250W average current control PFC                          | 190 |

| 6.12 Single Phase diode rectifier test circuit                                      | 195 |

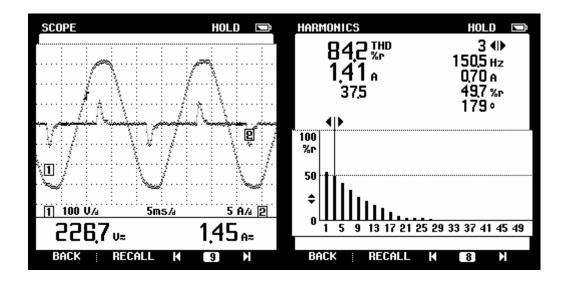

| 6.13 a) Input voltage and Current waveforms b) Input current harmonics              | 196 |

| 6.14 Output voltage waveforms for different capacitance values                      | 197 |

| 6.15 Minimum required inductance to comply with EN 61000- 3-2 Class A limits        | 198 |

| 6.16 Minimum required inductance to comply with EN 61000- 3-2 Class D limits        | 199 |

| 6.17 Single phase diode rectifier with L filter test circuit                        | 200 |

| 6.18 Input voltage and current waveforms for 100W Class A with 10mH filter          | 201 |

| 6.19 Harmonic spectrums for input current for Class A – 100W.                       | 201 |

| 6.20 Input voltage and current waveforms for 200W Class A with 10mH filter          | 202 |

| 6.21 Harmonic spectrums for input current for Class A – 200W.                       | 203 |

| 6.22 Measured input voltage and current for Class D a) 100W                         | 204 |

| 6.23 Harmonic spectrums for input current for Class D – 100W.                       | 204 |

| 6.24 Harmonic spectrums for input current for Class D – 200W.                       | 205 |

| 6.25 Single phase diode rectifier with 3 <sup>rd</sup> harmonic filter test circuit | 207 |

| 6.26 Current of 3 <sup>rd</sup> harmonic filter for 150W system                                 | 208 |

|-------------------------------------------------------------------------------------------------|-----|

| 6.27 Harmonic spectrums for input current for 150W 3 <sup>rd</sup> harmonic filtered rectifier. | 208 |

| 6.28 Single phase diode rectifier with variable inductance filter test circuit                  | 211 |

| 6.29 Experimental results for input voltage and current.                                        | 212 |

| 6.30 Input current harmonics for 200W Class-D SAG application                                   | 212 |

| 6.31 Block diagram of average current mode PFC                                                  | 213 |

| 6.32 Connection diagram for active PFC experiments                                              | 214 |

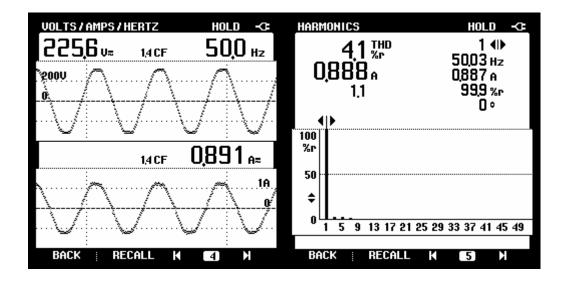

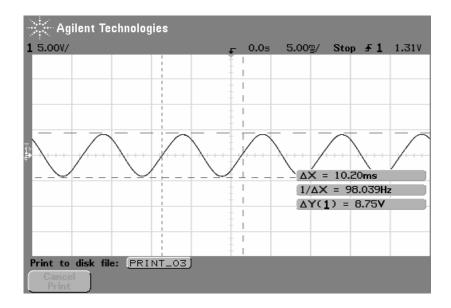

| 6.33 a) Input current and voltage waveforms (b) Input current harmonics                         | 215 |

| 6.34 Output voltage ripple for 220 V AC input voltage                                           | 215 |

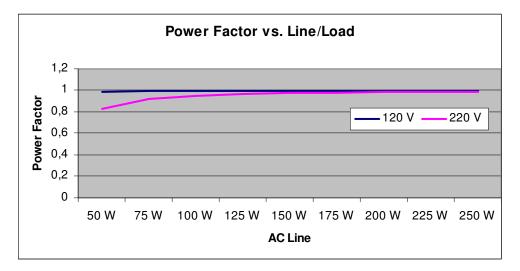

| 6.35 Power Factor vs. Line/Load.                                                                | 216 |

| 6.36 Start-up behavior of the input current and output voltage                                  | 217 |

| 6.37 Measurement method of switching characteristics.                                           | 218 |

# LIST OF TABLES

# TABLES

| 1.1. Class A absolute maximum harmonic limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2. Class B absolute maximum harmonic limits10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.3. Class C absolute maximum harmonic limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.4. Class D absolute maximum harmonic limits11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.5. IEC 61000-3-2 changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.6. Comparison of three solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.1. Experimental parameters of 200W rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.2. Experimental results for 200W rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.3. Class D absolute maximum harmonic limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.4. Class A absolute maximum harmonic limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.5. Parameters for 100W-Class D application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.6. Measured data for 100W Class-D application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.7. Circuit parameters for 200W-Class D Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.7. Circuit parameters for 200 w -Class D Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.8 Measured result for 200W Class-D application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.8 Measured result for 200W Class-D application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.8 Measured result for 200W Class-D application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.8 Measured result for 200W Class-D application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.8 Measured result for 200W Class-D application502.9 Parameters for 100W-Class A Application512.10 Measured results for 100W-Class A application532.11 Parameters for 200W-Class-A Application53                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.8 Measured result for 200W Class-D application502.9 Parameters for 100W-Class A Application512.10 Measured results for 100W-Class A application532.11 Parameters for 200W-Class-A Application532.12 Measured results for 200W-Class A application55                                                                                                                                                                                                                                                                                                                                                 |

| 2.8 Measured result for 200W Class-D application502.9 Parameters for 100W-Class A Application512.10 Measured results for 100W-Class A application532.11 Parameters for 200W-Class-A Application532.12 Measured results for 200W-Class A application552.13. Simulation parameters of series connected parallel resonant filter58                                                                                                                                                                                                                                                                       |

| 2.8 Measured result for 200W Class-D application502.9 Parameters for 100W-Class A Application512.10 Measured results for 100W-Class A application532.11 Parameters for 200W-Class-A Application532.12 Measured results for 200W-Class A application552.13. Simulation parameters of series connected parallel resonant filter582.14. Measured data for 150W series connected parallel resonant filter60                                                                                                                                                                                               |

| 2.8 Measured result for 200W Class-D application502.9 Parameters for 100W-Class A Application512.10 Measured results for 100W-Class A application532.11 Parameters for 200W-Class-A Application532.12 Measured results for 200W-Class A application552.13. Simulation parameters of series connected parallel resonant filter582.14. Measured data for 150W series connected parallel resonant filter602.15. Simulation parameters of Variable Inductance LC Filter Method73                                                                                                                          |

| 2.8 Measured result for 200W Class-D application502.9 Parameters for 100W-Class A Application512.10 Measured results for 100W-Class A application532.11 Parameters for 200W-Class-A Application532.12 Measured results for 200W-Class A application552.13. Simulation parameters of series connected parallel resonant filter582.14. Measured data for 150W series connected parallel resonant filter602.15. Simulation parameters of Variable Inductance LC Filter Method732.16 Parameters of sloped air-gap inductance74                                                                            |

| 2.8 Measured result for 200W Class-D application502.9 Parameters for 100W-Class A Application512.10 Measured results for 100W-Class A application532.11 Parameters for 200W-Class-A Application532.12 Measured results for 200W-Class A application552.13. Simulation parameters of series connected parallel resonant filter582.14. Measured data for 150W series connected parallel resonant filter602.15. Simulation parameters of Variable Inductance LC Filter Method732.16 Parameters of sloped air-gap inductance742.17. Measured data for the variable inductance filter for the single phase |

| 4.1 Simulation parameters of critical conduction mode PFC 134                                  |

|------------------------------------------------------------------------------------------------|

| 4.2 Design parameters of current conduction PFC 141                                            |

| 5.1 Simulation parameters of active PFC 159                                                    |

| 5.2 Design parameters of active PFC 165                                                        |

| 5.3 Comparison of control topologies                                                           |

| 6.1 Classification of electronic equipments by EN 61000-3-2 harmonic Standard 182              |

| 6.2 Maximum harmonic limits for each class type defined by EN 61000-3-2 182                    |

| 6.3 Bill of materials                                                                          |

| 6.4 Single-phase diode rectifier experiment parameters                                         |

| 6.5 Measurement results for single-phase diode rectifier experiment                            |

| 6.6 Experiment parameters for 100W L filter application - Class A 200                          |

| 6.7 Measurement results for 100W single-phase diode rectifier L filter experiment 201          |

| 6.8 Measurement results for 200W single-phase diode rectifier L filter experiment 202          |

| 6.9 Experiment parameters for L filter application - Class D 203                               |

| 6.10 Experiment parameters for 3 <sup>rd</sup> harmonic filter                                 |

| 6.11 Measurement results for 150W single-phase diode rectifier 3 <sup>rd</sup> harmonic filter |

| experiment                                                                                     |

| 6.12 Experiment parameters for variable inductance filter application                          |

| 6.13 Measurement results for single-phase diode rectifier SAG filter experiment 211            |

| 6.14 Measured PF for different input voltage level                                             |

| 8.1.List of Commercially Available PFC Controllers                                             |

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Background

The usage of electronic equipments is increasing rapidly in the daily life as consumer or industrial needs. All these electronic equipments have power supplies that obtain required energy from utility grid. These electronic systems generally use one or more switch mode power supplies that draw a non-sinusoidal current. This causes current and voltage distortions that effect other equipments connected to the same power grid, thus, lowering the capability of the power source. In order to overcome these problems, new standards have been developed for limiting the harmonic content of the input current. Manufacturers should find solutions for meeting these standards` requirements.

Most of power supplies consist of AC\DC converter stages based on diode or thyristor rectifier circuits. Conventionally, this stage consists of a diode rectifier with an output capacitor. These rectifier circuits constitute a major cause of mains harmonic distortion. Line-frequency diode rectifiers convert AC voltage into DC output voltage in an uncontrolled way. For low power applications (such as PCs, TVs, home appliances, etc...) single-phase diode rectifiers are chosen owing to low cost and simple structure. For high power applications (such as industrial equipments and motor drives) three-phase diode or thyristor rectifiers are used.

A typical offline switch mode power supply contains full-wave bridge rectifier with a large smoothing capacitor. This combination is one of the easiest and lowest cost

solutions for AC-DC conversion. This input rectifier with capacitive filter draws nonsinusoidal input current from utility. The pulsating current waveform is rich of harmonics [6], [7], [8]. A typical single-phase rectifier with capacitive smoothing and its output voltage and input current waveforms are shown in Figure 1.1 and Figure 1.2.

Figure 1.1 Single-phase rectifier with capacitive smoothing.

Figure 1.2 Waveforms for single-phase rectifier with capacitive smoothing.

This AC-DC peak detector circuit has some disadvantages. Mainly the input current has higher harmonic content (with an especially dominant third harmonic) and a low power factor due to distorted current waveform. A general harmonic content and THD of single-phase diode bridge rectifier is given below in Figure 1.3. This type of rectifier has some disadvantages such as creating harmonics and EMI, causing high power losses due to higher rms current, requiring over rated components and reducing power line capability.

Figure 1.3 Input current harmonics of single-phase rectifier with capacitive smoothing.

This behavior of this circuit has negative effects on the utility line and on the PCC such as deterioration of the line voltage, unbalanced currents on star windings; power loses over line impedances, overheating and EMC problems. In the general usage, different load groups are supplied by different phases. If one of the phases is loaded with nonlinear loads, unbalanced currents flow through the neutral line of star configuration. These unbalanced currents cause heating and power loss in the conductors and voltage distortion and EMC problems occur. Moreover the harmonic content of this pulsating current causes additional losses and dielectric stresses in capacitors and cables, increasing currents in windings of rotating machinery and transformers and noise emissions in many products, and bringing about early failure

of fuses and other safety components. Harmonics can affect other devices that are connected to the same system.

In order to reduce these harmonic polluting effects, international standards such as IEC 61000-3-2 have been developed for limiting harmonic currents. The International Electrotechnical Commission (IEC) sets limits for harmonics in the current of small single-phase or three-phase loads, less than 16 A per phase, in *Electromagnetic compatibility (EMC) - Part 3-2: Limits - Limits for harmonic current emissions* (IEC 61000-3-2) [1]. The circuit classifications and harmonic limits are given in this standard. The power supply manufacturers use different solutions for complying with the specifications. The techniques for reduction of current harmonics are called Power Factor Correction (PFC) solutions. The aim of PFC is providing a resistive load behavior of all power supplies.

#### **1.2 Definitions**

Power factor shows how effectively energy is transmitted to load. It also represents a measure of distortion of the line voltage and line current and phase shift between them. PF has range between 0 and 1 and is defined as the ratio of the real power to the apparent power.

Power Factor (PF) =

$$\frac{\text{Real Power (Average)}}{\text{Apparent Power}}$$

(1.1)

The real power is defined as the product of the fundamental voltage and fundamental current and the phase displacement between the two.

$$P_{real} = V_{1,rms} \cdot I_{1,rms} \cdot \cos \varphi \tag{1.2}$$

where  $V_{1,rms}$ ,  $I_{1,rms}$  are the rms values of the fundamental line current and the fundamental line voltage, respectively, and  $\varphi$  is the phase shift between line current and line voltage.

The apparent power is the product of rms voltage and rms current.

$$P_{app} = V_{rms} \cdot I_{rms} \tag{1.3}$$

In a linear load system, the power factor depends on phase difference between  $V_{rms}$  and  $I_{rms}$ . Then, the power factor can be expressed as.

$$PF = \frac{V_{rms} \cdot I_{rms} \cdot \cos\varphi}{V_{rms} \cdot I_{rms}} = \cos\varphi$$

(1.4)

It is shown that in the case of both sinusoidal voltage and current waveform systems with no phase difference between fundamental component of the current and voltage achieve unity power factor. This situation appears in resistive load circuits.

In a nonlinear load system with distorted current waveform, the rms values of the input current and the fundamental frequency component of the input current are not the same. The various harmonic components of the current appear as distorted power on the line. Then the power factor expression in the case of stable line voltage can be written as.

$$PF = \frac{I_{1,rms}}{I_{rms}} \cos \varphi = k_{distortion} \cdot k_{displacement}$$

(1.5)

Where  $k_{distortion} = \frac{I_{1,rms}}{I_{rms}}$  is the distortion factor and  $k_{displacement} = \cos \varphi$  is the displacement factor. Distortion factor describes harmonic content of the current. It shows the difference between fundamental component of the current and actual waveform.

Total Harmonic Distortion (THD) shows the ratio of the rms value of the waveform (not including the fundamental component) to the rms value of the fundamental component.

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} I_{n,rms}^2}}{I_{1,rms}}$$

(1.6)

Then distortion factor can be written by using THD definition in Eq. (1.6):

.

$$k_{distortion} = \frac{1}{\sqrt{1 + (THD)^2}}$$

(1.7)

In Figure 1.4, it can be seen that the different voltage and current waveforms result in different PF and THD due to distortion factor and displacement factor.

Figure 1.4 Different current and voltage waveforms of single phase rectifier.

#### 1.3 Harmonics and Their Effects on the Mains

Harmonics are the components of any waveform at multiple frequencies of the fundamental component. For a 50-Hz system the harmonic components occur in even and odd multiples of the mains frequency. Generally, non-linear loads draw distorted currents with higher harmonic content that consists of fundamental frequency component plus harmonic components.

Most electrical equipments are designed to operate under ideal sinusoidal environment. In the case of a harmonically polluted system the power line loses its ideal characteristic. The practical problems that may arise from excessive harmonic levels are [4], [5]:

- Harmonic currents flowing in the supply network generate additional energy losses and cause distortion of supply voltage.

- Higher frequency harmonic currents cause power losses (copper and iron losses) which result in an increase in the heating of elements. Equipment ratings must take the presence of harmonics into account. The higher rated neutral conductor is required to carry the added high frequency currents.

- Distorted waveforms result in poor power factor.

- Interference to equipment which is sensitive to voltage waveform

- Damage to power factor correction capacitors. Malfunction of ripple control and other mains signaling systems, protective relays and, possibly, in other control systems. Additional losses in capacitors and rotating machines. Additional acoustic noise from motors and other apparatus, reducing the efficiency of motors.

The diode bridge input circuit in a single-phase AC drive is the same as used in a very wide range of electronic equipment such as personal computers and domestic appliances. All of these cause similar current harmonics. Their effect is cumulative if they are all connected to the same low voltage (e.g. 230V) supply system. This means that to estimate the total harmonic current in an installation of single-phase units, the harmonics have to be added directly.

The power system is designed for predefined current values and all components belonging to this system have standard ratings and protection elements. Low power factor devices that draw higher current from the mains reduce the efficient power supplied by the mains. This means that low power nonlinear loads are reflected to the mains side with higher power ratings. Since the power line system is designed for fixed values, available power at the load side is decreased because of low power factor loads.

Harmonic currents in the AC distribution network require higher current carrying capacity that results in extra cost and power losses. This increasing capacity first affects the device and then the electric utility. The wire sizes and ratings should be increased. In residences and offices, energy meters cannot measure the reactive power that affects dissipative circuit elements so the user is not directly penalized in terms of utility costs for the reactive component of the power.

In ideal case the voltage at the utility side is assumed to be an ideal sinusoidal waveform. But actually AC source has small source impedance. Highly distorted current loads affect power line, resulting in distorting AC source voltage. The movement of the source voltage towards to non sinusoidal waveform can affect other equipments which are connected to the same power system.

### **1.4 Harmonic Current Emission Standards**

The harmonic polluting effects of conventional AC rectification must be limited and this is done in accordance with the standards of electricity utility network. To maintain power system quality, compliance requirements for current harmonic distortion are being enforced by national and international bodies [1], [2], [3].

The EN 61000-3-2 standard defines measurement requirements, ac power source requirements and limits for testing the harmonic current emissions of electronic and electrical equipment. The purpose of EN 61000-3-2 is limitation of harmonic currents injected to the power system. After some changes, this standard applies to any equipment with rated current up to 16 A RMS per phase for 50-Hz, 230-V single-phase systems or 400-V three-phase mains network.

There are 4 different classes in the EN 61000-3-2 that have different limit values. This classification is made according to:

- Number of pieces of equipment in use (how many are being used by consumers)

- Duration of use (number of hours in operation)

- Simultaneity of use (the same types of equipment used on the same time frame)

- Power consumption

- Harmonics spectrum, including phase (how clean or distorted is the current drawn by the equipment)

There are no limits for:

- Equipment with input power  $P \le 75$  W.

- Professional equipment with input power P > 1 kW.

- Symmetrical controlled heating elements with input power  $P \le 200$  W.

- Independent dimming devices for light bulb

- Non-public networks.

- Medical equipment (see also 6.)

- Equipment for rated voltages less than 230 VAC (limit not yet been considered).

Equipment can be grouped into 4 classes based on the above criteria as evaluated by the IEC committee members:

<u>Class A:</u> Balanced 3-phase equipment, and all other equipment, except those stated in one of the following classes. Also all equipment does not fall into Class B, C, and D. The maximum odd and even harmonics limits are given in Table 1.1.

| Harmonic order<br>n | Maximum permissible<br>harmonic current<br>(A) |  |  |

|---------------------|------------------------------------------------|--|--|

| Odd harmonics       |                                                |  |  |

| 3                   | 2.30                                           |  |  |

| 5                   | 1.14                                           |  |  |

| 7                   | 0.77                                           |  |  |

| 9                   | 0.40                                           |  |  |

| 11                  | 0.33                                           |  |  |

| 13                  | 0.21                                           |  |  |

| $15 \le n \le 39$   | 2.25/n                                         |  |  |

| Even harmonics      |                                                |  |  |

| 2                   | 1.08                                           |  |  |

| 4 0.43              |                                                |  |  |

| 6                   | 0.30                                           |  |  |

| $8 \le n \le 40$    | 1.84/n                                         |  |  |

Table 1.1 Class A absolute maximum harmonic limits

<u>Class B:</u> Portable tools, arc welding equipment that is not professional equipment. Harmonic current limits are absolute maximum values and are approximately 1.5 times Class A limits. The limits are given in Table 1.2.

| Harmonic order<br>n | Maximum permissible<br>harmonic current<br>(A) |  |  |

|---------------------|------------------------------------------------|--|--|

| Odd harmonics       |                                                |  |  |

| 3                   | 3.45                                           |  |  |

| 5                   | 1.71                                           |  |  |

| 7                   | 1.155                                          |  |  |

| 9                   | 0.60                                           |  |  |

| 11                  | 0.495                                          |  |  |

| 13                  | 0.315                                          |  |  |

| $15 \le n \le 39$   | 3.375/n                                        |  |  |

| Even harmonics      |                                                |  |  |

| 2                   | 1.62                                           |  |  |

| 4                   | 0.645                                          |  |  |

| 6 0.45              |                                                |  |  |

| $8 \le n \le 40$    | 2.76/n                                         |  |  |

Table 1.2 Class B absolute maximum harmonic limits

<u>Class C:</u> Lighting equipment containing dimmers and gas discharge lamps. There are limits on the second harmonic and also all odd harmonics. The limits are expressed in terms of a percentage of the fundamental current.

| Harmonic order<br>n | Maximum permissible<br>harmonic current<br>(% of fundamental) |  |

|---------------------|---------------------------------------------------------------|--|

| 2                   | 2                                                             |  |

| 3                   | 30 x circuit power factor                                     |  |

| 5                   | 10                                                            |  |

| 7                   | 7                                                             |  |

| 9                   | 5                                                             |  |

| $11 \le n \le 39$   | 3                                                             |  |

Table 1.3 Class C absolute maximum harmonic limits

<u>Class D:</u> PC, PC monitors, radio or TV receivers. Input power  $P \le 600$  W.

| Harmonic order<br>n | 75 W < P < 600 W<br>Maximum permissible<br>harmonic current<br>(mA/W) | P > 600 W<br>Maximum permissible<br>harmonic current<br>(A) |

|---------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|

| 3                   | 3.4                                                                   | 2.30                                                        |

| 5                   | 1.9                                                                   | 1.14                                                        |

| 7                   | 1.0                                                                   | 0.77                                                        |

| 9                   | 0.5                                                                   | 0.40                                                        |

| 11                  | 0.35                                                                  | 0.33                                                        |

| 13                  | 0.296                                                                 | 0.21                                                        |

| $15 \le n \le 39$   | 3.85/n                                                                | 2.25/n                                                      |

Table 1.4 Class D absolute maximum harmonic limits

Class D limits are very strict to meet as seen in Table 1.4. These limits depend on the equipments' power rating and apply to equipments that are connected to the utility network for a significant part of its life cycle, resulting in great impact on the power supply network. PCs and TVs are examples of such equipment. The current limits for

class D are expressed in terms of mA per Watt of the power consumed. Low-power equipment has very low absolute limits of harmonic current.

All rectifier based power supplies that are directly connected to the mains are generally classified as Class A or Class D. Such converters that have highly distorted current waveform and used more frequently are classified as in Class D. The lower distorted converters fall into Class A. In the power level less than 600 W, Class A has advantages of having higher harmonic limit values (Table 1.1). So designing the converter according to Class A limits is easier than Class D limits (Table 1.4).

Figure 1.5 Equipment classification chart according to IEC61000-3-2, A14 standard.

The harmonic standards have witnessed some changes during the last decade. At first, The International Electrotechnical Committee- IEC developed the standard IEC 555-2 at 1982. This standard is adapted as European standard as EN 60555-2 at 1987 by the European Committee for Electrotechnical Standardization - GENELEC. Standard IEC 555-2 has been replaced by standard IEC 1000-3-2 in 1995 and this standard is adapted as European standard EN 61000-3-2 by GENELEC.

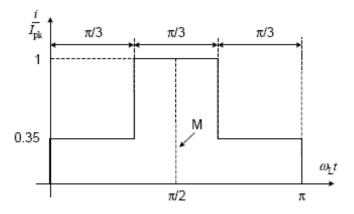

The version of the standard EN 61000 -3-2 in 1995 has some different classification aspects, especially on Class D equipments. Class D equipments were classified for equipments having an active input power less than or equal to 600 W and a special current waveform. An input current waveform – normalized to its peak value,  $I_{\rm pk}$  – which stays within the envelope shown in Figure 1.6 for at least 95% of the duration of each half-period, assuming that the peak of the line current waveform coincides with the center line.

Figure 1.6 Envelope of the input current used to classify Class D equipment, as defined in the first edition of IEC 61000 -3-2.

The standard IEC/EN61000-3-2 has been changed in 2000 and in 2001 with amendment A14. Now the amendment A14 is completely in force. These new changes bring the following specifications:

- Class D is no longer defined by a 'special waveform', and applies now only to television receivers and desktop computers. (Clearly, a switch-mode power supply (SMPS) intended for use in a PC would need to take that into account). In the future, other products may have to be added, but only after a full investigation.

- No limits for equipment using 75 W or less.

- Test configuration with expected maximum THC (Total Harmonic Current, no worst-case search).

- Limits apply only to the power lines, not to the neutral.

- New average power measurement method for fluctuating loads.

| Table 1.5 IEC 61000-3-2 changes | S |

|---------------------------------|---|

|---------------------------------|---|

|                                       | IEC61000-3-2:1995                                                    | IEC61000-3-2:2001                                                                                                 | IEC61000-3-2:2005                                                                                                |

|---------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                                       | EDITION 1.0                                                          | EDITION 2.1                                                                                                       | EDITION 3.0                                                                                                      |

| CLASS D DEFINITION                    | Special waveform envelope (75W to 600W)                              | TV, PC and Monitor (75W to 600W)                                                                                  | TV, PC and Monitor (75 to 100W)                                                                                  |

| MEASUREMENT<br>METHODS                | Steady and transitory                                                | Transitory only Transitory only                                                                                   | Transitory only                                                                                                  |

| MEASUREMENT<br>METHODS                | 16 cycles (320/267ms@50/60Hz)                                        | 200 ms (10/12 cycles@50/60 HZ) (16<br>cycles permitted through 2004)                                              | 200 ms (10/12 cycles@50/60 HZ)                                                                                   |

| DATA MANIPULATION                     | Transitory only                                                      | All data must be smoothed using the 1.5s first order filter                                                       | All data must be smoothed using the 1.5s first order filter                                                      |

| PASS/FAIL FOR<br>INDIVIDUAL HARMONICS | Every window result <150% of<br>limit of test time >100% permitted   | Every window result <150% of limit<br>10% of test time >100% permitted                                            | Every window result <150% of<br>limit 10% of test time >100%                                                     |

| CLASS A RELAXATION*                   | No special provision                                                 | No special provision                                                                                              | <200 time of limit only IF >150%<br>for 10% of test time AND average                                             |

| ODD HARMONICS 21-39*                  | No special provision                                                 | Provision for POHC calculation<br>permitting the average of some<br>individual harmonics to >100%                 | Provision for POHC calculation<br>permitting the average of some<br>individual harmonics to >100%                |

| CLASS C&D LIMITS                      | Proportional to measured power<br>(Class D) or current & PF ,Class C | Allows manufacturer o specify test<br>power or current level provided it is<br>within ±10% of the measured value  | Allows manufacturer o specify test<br>power or current level provided it is<br>within ±10% of the measured value |

| TEST/OBSERVATION<br>PERIOD            | Not specially defined but to find the max. harmonics emission        | Specified to be significantly long<br>enough to acquire ±5% repeatability.<br>If to long select the 2.5 min. max. | Specified to be significantly long<br>enough to acquire ±5%<br>repeatability.                                    |

| TEST CONDITIONS                       | Specified to some products                                           | Detailed test procedure for certain product categories                                                            | Detailed test procedure for certain<br>product categories. Amended<br>procedure for testing TV from 2001.        |

### **1.5 Power Factor Correction Methods**

The need for Power Factor Correction brings a lot of new PFC methods and applications. The most important issue is finding optimum PFC solution according to needed application. There are several survey papers in order to help to find the best solution for power factor correction [9], [10], [11], [12], [13]. The Power Factor Correction methods can be classified according to following specifications:

- System level classification (passive, active)

- Number of stages (single stage, two stage)

- Circuit based classification (isolated, non isolated)

- Type of power stages (buck, boost, fly back etc...)

- Waveform based classification (sinusoidal, non-sinusoidal)

- Control methods (current mode, voltage mode)

- The other aspects (power level, cost, complexity, etc...)

Generally, two PFC approaches are commonly used in current power supply products with high power features, i.e., passive approach and active PFC approach. Each one has its merits and limitations and applicable field.

Passive PFC approaches are used in low-power, low-cost applications. Generally, in this approach, an L-C filter is inserted between the AC mains line and the input port of the diode rectifier of ac-to-dc converter. Passive PFC method is simple and low cost but has bulky size and heavy weight and low power factor.

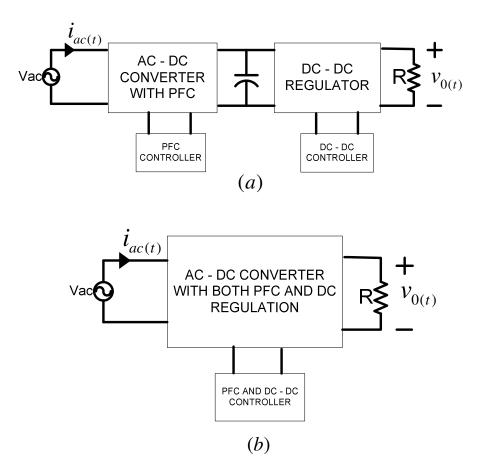

Active solutions are used at high power levels with high PF and low harmonic distortion. We can classify active PFC methods as two stage and single stage by considering number of conversion stages. The most commonly used active approach is the two-stage approach with higher quality. Generally two-stage PFC systems consist of a pre-regulator cascaded with a dc/dc converter. In the first stage, generally called as pre-regulator, a non-isolated boost converter has the role of power factor correction. This front end PFC stage converter generally operates for low harmonic

input current and intermediate dc bus voltage. The second stage operates for required dc voltage level with higher bandwidth. The second stage generally has isolation. The two-stage systems have higher quality with higher PF and low harmonic distortion. However, the two-stage approach causes an increase in the total system cost and manufacturing complexity. Especially in low-power applications, two-stage solutions have higher cost. For reducing system cost and component count, single-stage solutions have been introduced. In the single-stage systems, PFC, isolation and dc voltage regulation are performed in one stage with lower component number.

## 1.5.1 PFC Design Criteria

Selection of the best PFC method is very important according to application. The following factors are the main selection criteria for a PFC application for selecting right configurations and specifications:

- What standards and class of equipment needs will the system be required to meet.

- 2. Required PF, THD, and the other factors

- 3. Output power level

- 4. Power flow (unidirectional, bidirectional)

- 5. Required DC voltage level

- 6. Input voltage range

- 7. Isolated or non-isolated

- 8. Type of load

- 9. Size and Weight

- 10. Efficiency

- 11. Dynamic characteristics such as holding time, ripples, transient, regulation, etc...

- 12. Environmental effects (temperature, duration, pollution, humidity)

- 13. Noise level (EMC, EMI, RFI, etc...)

- 14. Cost