# CASCADED, REACTIVELY TERMINATED, SINGLE STAGE DISTRIBUTED 2-18 GHZ AMPLIFIER

#### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

OĞUZHAN EFE

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

JULY 2008

Approval of the thesis:

### CASCADED, REACTIVELY TERMINATED, SINGLE STAGE DISTRIBUTED 2-18 GHZ AMPLIFIER

submitted by OĞUZHAN EFE in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Oğuzhan EFE

Signature :

## ABSTRACT

# CASCADED, REACTIVELY TERMINATED, SINGLE STAGE DISTRIBUTED 2-18 GHZ AMPLIFIER

EFE, Oğuzhan

M.S., Department of Electrical and Electronics Engineering Supervisor : Assoc. Prof. Dr. Şimşek DEMİR

July 2008, 76 pages

In this thesis work, a 3-stage ultra broadband amplifier operating in 2-18 GHz frequency band with gain 23  $\pm$  1.5 dB is designed, simulated and fabricated. The amplifier is based on cascaded, reactively terminated single stage distributed amplifier (CRTSSDA) concept. The idea of including reactive terminations to achieve ultra broadband gain is investigated and simulated. The simulated design is fabricated and measurements of the fabricated amplifier are compared with simulation results. Also practical experience on working at high frequencies with surface mount components is presented in this thesis work.

Keywords: Broadband Amplifier, Distributed Amplifier, CRTSSDA, Reactive Termination

## ÖΖ

### SERİ BAĞLI, REAKTİF SONLANDIRILAN TEK AŞAMADA DAĞITILMIŞ 2–18 GHZ YÜKSELTEÇ TASARIMI

EFE, Oğuzhan Yüksek Lisans Tezi, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Şimşek DEMİR

Temmuz 2008, 76 sayfa

Bu tez çalışmasında, 2–18 GHz bandında  $23 \pm 1,5$  dB kazançlı 3 aşamalı çok geniş bant yükselteç tasarımı, benzetimleri ve üretimi yapılmıştır. Tasarlanan yükselteç, seri bağlı, reaktif sonlandırılan, tek aşamada dağıtılmış (SRSTADY) devre tasarımı tekniği kullanılarak tasarlanmıştır. Benzetim sonucu elde edilen tasarım gerçeklenmiştir. Gerçeklenen yükselteçte alınan ölçümler benzetim sonuçlarıyla kıyaslanmıştır. Ayrıca, bu tez çalışmasında yüksek frekanslarda yüzeye monte edilen elemanlarla çalışırken elde edilen pratik tecrübeler sunulmuştur.

Anahtar Kelimeler: Çok Geniş Bant Yükselteç, Dağıtılmış Yükselteç, SRSTADY, Reaktif Sonlandırma To my fiancée Canan

## ACKNOWLEDGMENTS

I would like to thank Assoc. Prof. Dr. Şimşek Demir for his valuable supervision, support and tolerance throughout the development and improvement of this thesis.

I am grateful to Dr. Mustafa Akkul and Tuncay Erdöl for their support throughout the development and the improvement of this thesis. I would like to thank to clean room staff of Aselsan Inc., especially to Tülay Can for her unlimited patience during the fabrication process. I am also grateful to Aselsan Electronics Industries Inc. for the resources and facilities that I use throughout thesis.

I would like to thank my parents for bringing me up and trusting in me. I also thank to my lovely brother Orhun for his encouragement throughout my thesis study.

Last, but not least, I would like to thank my fiancée Canan Bayram, for giving me the strength and courage to finish this work.

## TABLE OF CONTENTS

| ABSTRACT                                                                 | iv  |

|--------------------------------------------------------------------------|-----|

| ÖZ                                                                       | v   |

| ACKNOWLEDGMENTS                                                          | 'ii |

| TABLE OF CONTENTS                                                        | 11  |

| LIST OF TABLES                                                           | X   |

| LIST OF FIGURES                                                          | xi  |

| LIST OF ABBREVIATIONS                                                    | iii |

| CHAPTERS                                                                 |     |

| 1. INTRODUCTION                                                          | 1   |

| 1.1 Microwave Amplifiers                                                 | 1   |

| 1.2 Distributed Amplifiers                                               | 2   |

| 1.3 Cascaded, Reactively Terminated, Single Stage Distributed Amplifier  | 3   |

| 1.4 Description of the Thesis                                            | 4   |

| 1.5 Outline of the Thesis                                                | 4   |

| 2. BROADBAND AMPLIFIERS                                                  | 5   |

| 2.1 Review of Broadband Amplifiers                                       | 5   |

| 2.1.1 Feedback Amplifiers                                                | 6   |

| 2.1.2 Reactively Matched Amplifiers                                      | 7   |

| 2.1.3 Traveling Wave Distributed Amplifiers                              | 8   |

| 2.1.4 Cascaded, Reactively Terminated Single Stage Distributed Amplifier |     |

| (CRTSSDA)1                                                               | 0   |

| 3. DESIGN OF THE BROADBAND AMPLIFIER 1                                   | .3  |

| 3.1 Introduction                                                         | 3   |

| 3.2 Principles of CRTSSDA 1                                              | 3   |

| 3.2.1 Theory of Reactive Terminations                                    | .4  |

| 3.3 Design of the Proposed CRTSSDA 1                                     | . 8 |

| 3.3.1 Brief description about the transistors used in the design:        | .9  |

| FPD200 1                                                                 | .9  |

| FPD6836                                             |    |

|-----------------------------------------------------|----|

| FPD750                                              |    |

| 3.3.2 Design Procedure:                             | 21 |

| 3.4 Analysis and Simulation                         | 25 |

| 3.4.1 Simulation Results                            |    |

| 3.4.1.1 1 <sup>st</sup> Trial                       |    |

| 3.4.1.2 2 <sup>nd</sup> Trial                       |    |

| 4. FABRICATION AND MEASUREMENT                      |    |

| 4.1 Choosing the Appropriate Substrate              |    |

| 4.2 Assembling the Components on PCB                |    |

| 4.3 Measurement Setup and DC Biasing of Transistors |    |

| 4.4 Layout of the First Amplifier                   |    |

| 4.5 Measurements of the First Amplifier             |    |

| 4.6 Layout of the Second Amplifier                  | 50 |

| 4.7 Measurements of the Second Amplifier            | 54 |

| 4.8 Comparisons between the Fabricated Amplifiers   | 60 |

| 5. CONCLUSIONS                                      |    |

| REFERENCES                                          | 65 |

| APPENDIX A                                          | 67 |

| A.1 TriQuint TOM3 Scalable Nonlinear FET Model      | 67 |

| A.2 TOM3 Model of FPD200                            | 71 |

| A.3 TOM3 Model of FPD6836                           | 72 |

| A.4 TOM3 Model of FPD750                            | 75 |

## LIST OF TABLES

| Table 3-1 Component Values of Figure 3.2                                     | 17   |

|------------------------------------------------------------------------------|------|

| Table 3-2 Electrical Specifications of FPD200                                | 19   |

| Table 3-3 Electrical Specifications of FPD6836                               | 20   |

| Table 3-4 Electrical Specifications of FPD750                                | 21   |

| Table 3-5 Resistor Values of Reactive Terminations of the Designed Amplifier | 23   |

| Table 3-6 Inductor Values of Reactive Terminations of the Designed Amplifier | 24   |

| Table 4-1 Biasing Current and Voltage Values of Transistors                  | 37   |

| Table 4-2 Estimated Dimensions For Transmission Lines in Figure 4.4          | 41   |

| Table 4-3 Resistors Included to Prevent Low Frequency Oscillation            | 43   |

| Table 4-4 Transmission Lines Representing Inductors and Corresponding Bond V | Wire |

| Lengths                                                                      | 51   |

| Table 4-5 Estimated Dimensions For Transmission Lines in Figure 4.4          | 52   |

| Table A-1 TOM3 Model Parameters                                              | 68   |

| Table A-2 TOM3 Model Parameters-Continued                                    | 69   |

| Table A-3 TOM3 Model Parameters-Continued                                    | 70   |

| Table A-4 TOM3 Model Parameters of FPD200                                    | 72   |

| Table A-5 TOM3 Model Parameters of FPD6836                                   | ~ 4  |

|                                                                              | 74   |

## LIST OF FIGURES

| Figure 2.1 Feedback Amplifier                                                     | 6     |

|-----------------------------------------------------------------------------------|-------|

| Figure 2.2 Reactively Matched Amplifier                                           | 7     |

| Figure 2.3 Traveling Wave Distributed Amplifier                                   | 8     |

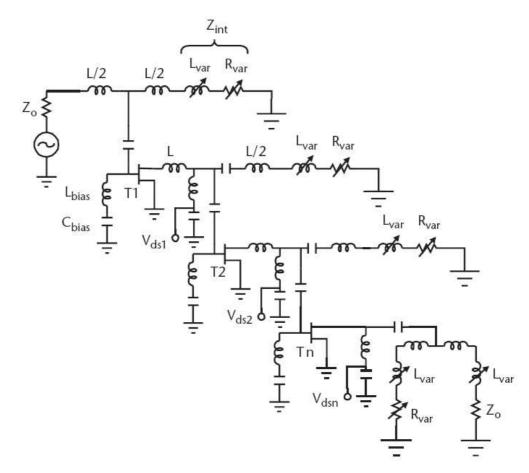

| Figure 2.4 Cascaded Reactively Terminated Single Stage Distributed Amplifier.     | 11    |

| Figure 3.1 Block Diagram of a CRTSSDA                                             | 14    |

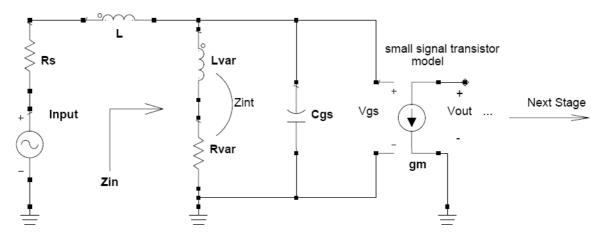

| Figure 3.2 Small Signal Model of a Transistor with Reactive Terminations          | 15    |

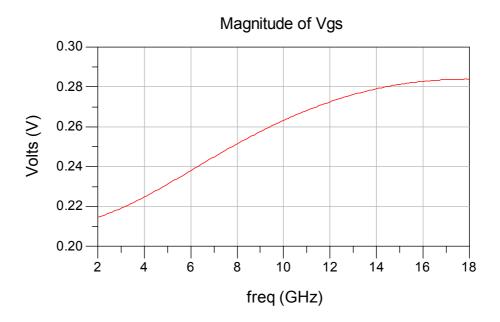

| Figure 3.3 Enhancement of Voltage Swing Across $C_{gs}$ With Reactive Termination | ons17 |

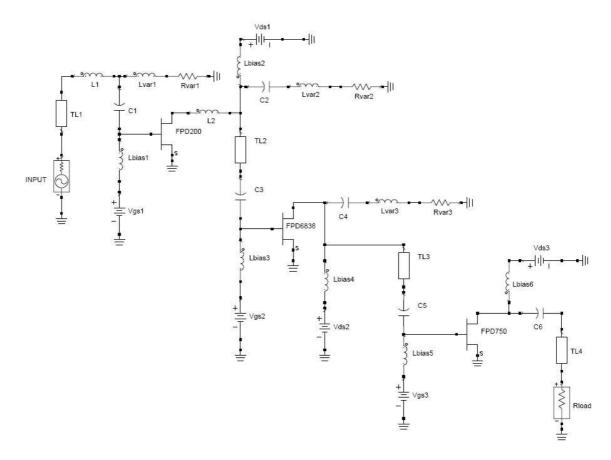

| Figure 3.4 Schematic of the Proposed Amplifier                                    | 18    |

| Figure 3.5 The General Transistor Amplifier Circuit                               | 24    |

| Figure 3.6 Schematic of the Firstly Designed CRTSSDA                              | 26    |

| Figure 3.7 S21 Plot of The First CRTSSDA                                          | 27    |

| Figure 3.8 S11 and S22 Plots of The CRTSSDA                                       | 27    |

| Figure 3.9 Voltage Swing Enhancement of The First Stage                           | 28    |

| Figure 3.10 Voltage Swing Enhancement of The Second Stage                         | 29    |

| Figure 3.11 Voltage Swing Enhancement of The Third Stage                          | 29    |

| Figure 3.12 Schematic of The Second CRTSSDA                                       | 30    |

| Figure 3.13 S21 Plot of The Second CRTSSDA                                        | 31    |

| Figure 3.14 S11 and S22 Plots of Second CRTSSDA                                   | 31    |

| Figure 4.1 Ball Bonder Kulicke Soffa AG 4124                                      | 35    |

| Figure 4.2 An Air Core Coil, A Shelled Tip, And Wedge Bonding On A Capacit        | or 36 |

| Figure 4.3 Measurement Setup                                                      | 38    |

| Figure 4.4 Schematic of the First Designed CRTSSDA                                | 40    |

| Figure 4.5 Layout of the First Designed CRTSSDA                                   | 42    |

| Figure 4.6 First Fabricated CRTSSDA                                               | 43    |

| Figure 4.7 Gate Biasing of The First Stage                                        | 44    |

| Figure 4.8 Oscillation Caused By Biasing Inductor                                 | 45    |

| Figure 4.9 S-Parameters After Eliminating Oscillation                             | 45    |

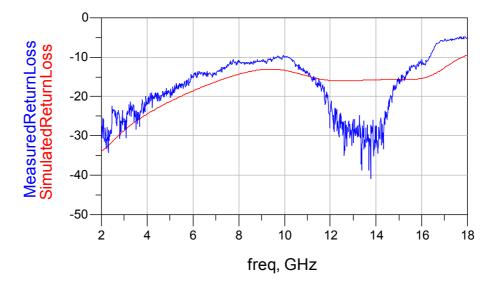

| Figure 4.10 S-Parameters After Improved Grounding of Connectors               | 47    |

|-------------------------------------------------------------------------------|-------|

| Figure 4.11 Input Return Loss After Improved Grounding of Connectors          | 47    |

| Figure 4.12 Final Response of the First Fabricated Amplifier                  | 48    |

| Figure 4.13 Comparison of Simulation and Measurement Gains                    | 50    |

| Figure 4.14 Schematic of The Second CRTSSDA                                   | 51    |

| Figure 4.15 Layout of The Second CRTSSDA                                      | 53    |

| Figure 4.16 Fabricated Circuit of The Second CRTSSDA                          | 53    |

| Figure 4.17 Gate Biasing of the First Stage of the 2nd CRTSSDA                | 54    |

| Figure 4.18 S-Parameters of the 2nd CRTSSDA Before Tunings                    | 55    |

| Figure 4.19 Copper Plates Soldered to Improve Grounding                       | 56    |

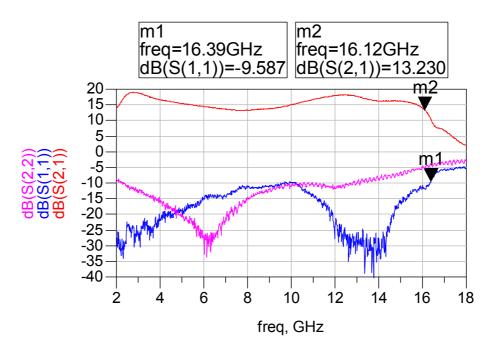

| Figure 4.20 Effects of Including Copper Paltes on Input Return Loss           | 56    |

| Figure 4.21 Gain of the Second CRTSSDA Before and After First Tuning          | 57    |

| Figure 4.22 Final Response of the Second CRTSSDA After All Tunings            | 58    |

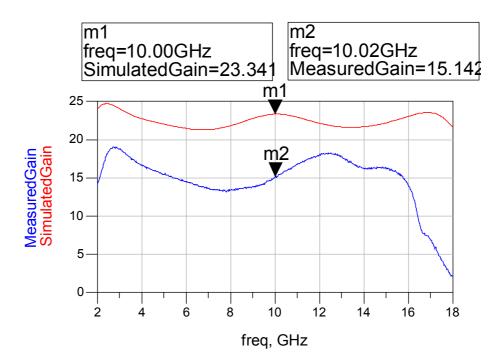

| Figure 4.23 Comparison of Gains Between Simulated And Measured Amplifier      | 59    |

| Figure 4.24 Comparison of Input Return Loss Between Simulated And Measure     | d     |

| Amplifier                                                                     | 59    |

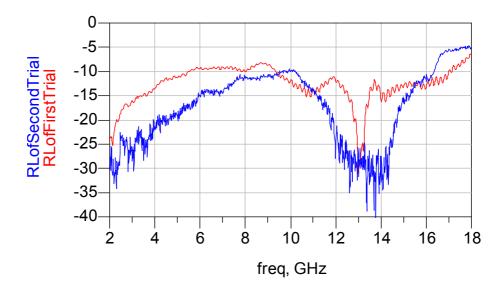

| Figure 4.25 Comparison of Gains of First and Second Fabrications              | 60    |

| Figure 4.26 Comparison of Input Return Losses of First and Second Fabrication | 1s.61 |

| Figure A.1 TOM3 Model with External Parasitic of FPD200                       | 71    |

| Figure A.2 TOM3 Model with External Parasitic of FPD6836                      | 73    |

| Figure A.3 TOM3 Model with External Parasitic of FPD750                       | 75    |

## LIST OF ABBREVIATIONS

| ADS     | : Advanced Design System                                     |

|---------|--------------------------------------------------------------|

| CRTSSDA | : Cascaded, Reactively Terminated, Single Stage Distributed  |

|         | Amplifier                                                    |

| DPHEMT  | : Double-Heterojunction Pseudomorphic High-Electron-Mobility |

|         | Transistor                                                   |

| FET     | : Field Effect Transistor                                    |

| MESFET  | : Metal-Semiconductor Field Effect Transistor                |

| MMIC    | : Monolithic Microwave Integrated Circuit                    |

| PHEMT   | : Pseudomorphic High-Electron-Mobility Transistor            |

| TWA     | : Traveling Wave Amplifier                                   |

| TWDA    | : Traveling Wave Distributed Amplifier                       |

| VSWR    | : Voltage Standing Wave Ratio                                |

|         |                                                              |

## **CHAPTER 1**

## INTRODUCTION

## 1.1 Microwave Amplifiers

Researches on amplifiers date back to A. G. Clavier [1] who established a radio link between England and France in 1931. His successful experiment motivated researches on amplifiers from 1930s to nowadays. Because of shortage of technology of that time, implemented amplifiers were narrow banded. Invention of distributed amplifier concept presented a new viewpoint to engineers and shed light on the design of wide band amplifiers. Invention of junction bipolar transistors, than FETs and MESFETs accelerated the researches on broadband amplifiers.

Today, microwave amplifiers are used in various fields of microwave engineering such as in electronic warfare systems, radars, satellite communications, optical communications, networks and instrumentation. An amplifier is used to amplify received signals from an antenna in order to be able to process it, to amplify a signal that is going to be transmitted from an antenna in a radar system or to maintain a robust communication with a satellite or in a network. In conclusion, amplifiers are one of the necessary components in microwave systems.

In order to meet today's technological requirements, researches are focused on widening the gain bandwidth of an amplifier. Several circuit techniques are developed to have stable, high gain and efficient broadband amplifiers. These amplifiers are realized in hybrid or monolithic forms which have advantages or disadvantages on each other for different constraints. For example, high output power and noise figure are always in a trade-off for a designer, or linearity is an expense of efficiency. The best design method should be chosen according to the requirements.

Concept of distributed amplifiers is one of the circuit techniques developed to widen operating frequency band. The amplifier designed in this thesis work is based on distributed amplifier concept. In order to have an insight of distributed amplifiers, the following section is given.

## 1.2 Distributed Amplifiers

The concept of distributed amplifiers dates back to the 1940s [2]. W. S. Percival [3] found that bandwidth of an amplifier is determined by the capacitance and transconductance of the conventional electronic valve. He separated capacitance of the valve from its transconductance and absorbed the separated capacitance into artificial transmission lines. Now the gain bandwidth of the valve is limited to the cut-off frequency of those artificial lines. Separating capacitance and absorbing it into artificial transmission lines is the first insight of distributed amplifiers.

Switching from electronic tube valve technology to junction bipolar transistors increased researches on distributed amplifiers. Publications about distributed amplifiers appeared on television broadcasting, radar and networking areas [4]. Between 1970 and 1980 GaAs FET and MESFET researches gave additional acceleration on distributed amplifiers [5-6]. Afterwards, the development of monolithic microwave integrated circuit technology (MMIC) improved the researches on distributed amplifiers.

Distributed amplifiers are advantageous because of eliminating the gain bandwidth limiting effect of transistor's gate and drain line capacitances. They give successful gain, matching and noise figure over a wide bandwidth. These attributes of distributed amplifier are used for the proposed amplifier of this thesis work, together with cascading transistors and including reactive terminations.

## 1.3 Cascaded, Reactively Terminated, Single Stage Distributed Amplifier

Conventional traveling wave amplifiers (TWA) are used for broadband amplification since the last 2 decades. Ayasli, et al. [7] presented a TWA which operates in 2-20 GHz band. Attenuation at gate and drain lines and mismatches in phase velocities of the successive stages in a TWA structure makes it difficult to obtain high gain in broad bandwidth. In order to overcome these deficiencies, cascaded, reactively terminated single stage distributed amplifier concept is developed.

A cascaded, reactively terminated, single stage amplifier (CRTSSDA) is firstly presented by Virdee [8]. Bandwidth of distributed amplifiers is limited to the cut-off frequencies of the artificial transmission lines, which are realized by inductors. In order to improve the bandwidth of the amplifier, which is limited to the cut-off frequencies of artificial lines, reactive terminations are included at the input of each stage of a CRTSSDA. Together with selecting resonance-free values for biasing components, reactive terminations provide broadband matching and gain flattening.

It is stated in [8] that a CRTSSDA exhibits a substantial gain and superior efficiency compared to a conventional traveling wave amplifier (TWA). A three-stage TWA can give 8-9 dB gain maximum, however Virdee [8] achieved more than 20 dB gain in 2-18 GHz frequency band with a three-stage CRTSSDA. Another advantage of CRTSSDA is that it is easier to design than designing a conventional TWA since there is no need for phase velocity equalization of gate and drain lines.

DPHEMT transistors are used in Virdee's [8] ultra broadband amplifier. The amplifier proposed in [8] is realized on alumina substrate which has a permittivity  $\varepsilon_r$  = 9.8 and height of 0.381 mm. In this thesis work, the designed amplifiers are fabricated on Rogers4350 and Rogers4003 substrates, having permittivities  $\varepsilon_r$  = 3.48 and  $\varepsilon_r$  = 3.38 respectively. DPHEMT transistors are used in the proposed amplifiers as in Virdee's work.

## 1.4 Description of the Thesis

In this thesis work, a 3-stage ultra broadband amplifier in 2-18 GHz frequency band, having gain of 23  $\pm$  1.5 dB is designed, simulated and fabricated. The proposed amplifier is a cascaded, reactively terminated, single stage distributed amplifier (CRTSSDA). Two different amplifiers with the same topology are designed and presented in this thesis work. The first trial of the CRTSSDA is realized on Rogers4350 substrate. Having tunings and observations on the firstly fabricated amplifier inspirited a second design of CRTSSDA to achieve a better gain flatness and input and output match. The secondly designed ultra broadband amplifier is fabricated of Rogers4003 substrate. The theory of designing a broadband amplifier, simulations, analysis and measurements of the proposed amplifiers are given within this thesis study in detail in the next chapters. Experience gained during fabrication and measurements are also noted and comparisons between simulation results and measurements are presented.

## 1.5 Outline of the Thesis

This thesis is organized as follows: In Chapter 2, brief theoretical knowledge about designing broadband amplifiers is given. Comparisons between the circuit techniques are presented and an introduction to CRTSSDA topology is given.

In Chapter 3, designing a CRTSSDA is given step by step together with the designed amplifiers. Simulations regarding the theory of reactive terminations of a CRTSSDA and results of the designed amplifiers are also presented in Chapter 3.

In Chapter 4, fabrication and measurement techniques are given. Simulation results are compared to the measurements in this chapter. Experience about using surface mount components at high frequencies are also explained in this chapter.

Finally, conclusions about design and fabrication of an ultra broadband CRTSSDA are made in Chapter 5.

## **CHAPTER 2**

## **BROADBAND AMPLIFIERS**

Development in the fields of instrumentation, electronic warfare, optical communication and microwave motivated studies in multi octave amplifiers [4]. These researches resulted several circuit techniques to achieve broadband amplifiers. These different methods of designing broadband amplifiers have advantages and disadvantages compared to each other. Brief description about these topologies and comparisons between them are presented in this chapter.

## 2.1 Review of Broadband Amplifiers

Broadband amplifiers' power-added efficiencies are usually lower than narrowband amplifiers. There is a trade-off between achieving multi octave gain and efficiency. Broadband amplifiers' power-added efficiencies are generally in the range of 8% to19% [4]. High power-added efficiency is one of the strict requirements of broadband amplifiers. The other requirements for broadband amplifiers are high stability, high gain and acceptable output power. In order to meet these requirements several circuit techniques are developed.

Some of the circuit techniques developed for designing broadband amplifiers can be listed as follows [4]:

- Feedback circuit

- Reactively matched circuit

- Traveling wave distributed circuit

- > Cascaded, reactively terminated single stage distributed circuit

Brief description about the circuit techniques listed above is given in the following sections. More emphasis is employed on traveling distributed amplifier (TWA) and cascaded, reactively terminated single stage distributed amplifier (CRTSSDA) circuits.

#### 2.1.1 Feedback Amplifiers

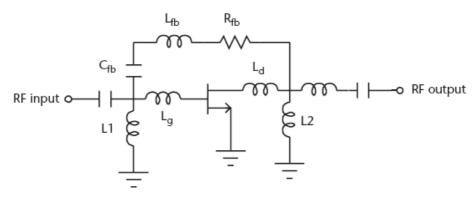

In a feedback amplifier, shown in Figure 2.1 [4], broadband is achieved by a feedback path, comprising  $R_{fb}$ ,  $L_{fb}$  and  $C_{fb}$ . The capacitor  $C_{fb}$  blocks the DC biasing of gate and drain lines, which should be resonant free in band with biasing inductors,  $L_1$  and  $L_2$ . The inductor in the feedback path,  $L_{fb}$ , cuts the feedback path for high frequencies to adjust gain flatness and  $R_{fb}$  determines the gain and bandwidth of the amplifier.  $L_g$  and  $L_d$  are used to compensate intrinsic gate and drain capacitance respectively to achieve broadband gain.

Figure 2.1 Feedback Amplifier [4]

Niclas, et al. [9] proposed a feedback amplifier that achieves multi octave band with one active device. Niclas achieved broadband gain by adjusting  $L_g$ ,  $L_d$  and  $L_{fb}$  in Figure 2.1 [9].

Feedback amplifier circuit is not a complex configuration compared to traveling wave amplifier and CRTSSDA. Feedback amplifiers have good input and output

matching over a multi octave band. They also have excellent unconditional stability and a flat gain in broadband.

Disadvantages of feedback amplifiers are that they have very high noise figures because of including a resistor in the feedback path. They are also very sensitive to frequency, therefore realizing a feedback amplifier in a hybrid circuit is difficult to achieve. Feedback amplifiers are usually realized in MMIC circuits.

#### 2.1.2 Reactively Matched Amplifiers

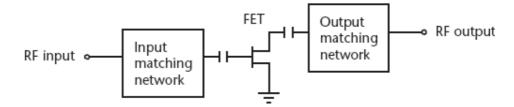

As the name implies, reactively matched amplifiers consist of input and output matching circuits which are composed of reactive components as shown in Figure 2.2 Reactively Matched Amplifier [4]. Input matching circuit provides a high gain and output matching circuit provides maximum output power which enhances power-added efficiency.

Figure 2.2 Reactively Matched Amplifier [4]

Tserng, et al. [10] presented a reactively matched amplifier operating in 2-18 GHz frequency band. The output power of Tserng's reactively matched amplifier is 23 dBm with efficiency 15%. Tserng used wideband impedance transformers to maintain input and output match; however, voltage standing wave ratio (VSWR) was poor in the band.

Palmer, et al. [11], realized the first reactively matched amplifier in MMIC circuit technology. Palmer's amplifier is operating in 6-18 GHz band, with output power of 27 dBm and efficiency of 19%. The amplifier is a two stage amplifier with driver

circuits at input and output, where he paralleled the active devices to decrease source inductance.

Multi octave matching of this type of broadband amplifier is not an easy task since the reactive matching circuits are dependent on frequency. One can design a matching circuit for a moderate band of frequencies; however, the performance of the matching circuit degrades with increasing bandwidth. Several methods are developed for improving broadband performance [10-11]; however, these methods increase the cost and size of the amplifier.

#### 2.1.3 Traveling Wave Distributed Amplifiers

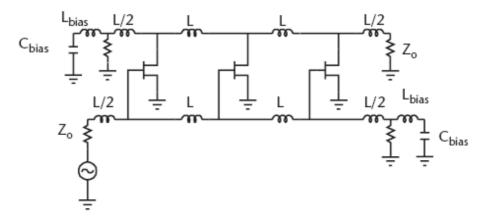

In a traveling wave distributed amplifier (TWDA), gate and drain capacitances are absorbed in artificial transmission lines by lumped inductors. The conventional schematic of a TWDA is given in Figure 2.3 [4].

Figure 2.3 Traveling Wave Distributed Amplifier [4]

Each transistor is excited at their gates and transistors conduct the input signal to their drain ports through their transconductance. The amplified signals from each transistor are added in forward direction to the output. Equalizing phase velocities is the vital point in designing TWDA, since any mismatch of phase velocities will degrade the amount of signal transmitted to load. The reverse directed traveling waves are absorbed in drain lines which are terminated to characteristic impedance by the inclusion of artificial transmission lines.

Since the artificial transmission lines are terminated with the characteristic impedance, a constant resistance at the input and output is observed. Constant input and output impedance provides a broadband matching. Cut-off frequency of the artificial line determines the highest operating frequency of the amplifier, which depends on the capacitance of the active devices and lumped inductors of the artificial line.

Gain expression of a TWDA is given by [12]:

$$G_{TWDA} = \frac{1}{4} g_m n^2 Z_0^2$$

(2-1)

where  $g_m$  is the transconductance of the transistors, n is the number of active components used and  $Z_0$  is the characteristic impedance of the artificial lines.

Since the given gain expression for TWDA is independent of frequency, it is possible to have multi octave response by this circuit technique. The only limiting factor is the cut-off frequency of artificial transmission lines, hence gate and drain capacitance and lumped inductors.

In a lossless system, one can get higher gain by simply increasing the number of stages. However, gate and drain line attenuations will limit the gain that one can get from traveling wave amplifiers.

Traveling wave distributed amplifiers exhibit good matching since the artificial transmission lines are terminated to characteristic impedance. The only limiting factor of bandwidth is the cut-off frequencies of the gate and drain lines of the transistors. This characteristic of TWDAs also allows designers to cascade gain modules to get higher gained amplifiers. Constant resistance through the wide band also rivets stability when cascading gain modules and decrease tendency to oscillations.

Since the gain of a TWDA is the addition of in-phase currents from drain lines of each transistor, it is essential to equate the phase velocities of the forward directed signals from each active component. Any mismatch of phase velocities will cause degradation in gain. Also, if there is a failure in one stage, this failure will affect the whole response of the amplifier. Attenuation in gate lines decreases the available output power from the amplifier when the number of stages is increased. These deficiencies are solved by CRTSSDA topology which is explained in the next section.

## 2.1.4 Cascaded, Reactively Terminated Single Stage Distributed Amplifier (CRTSSDA)

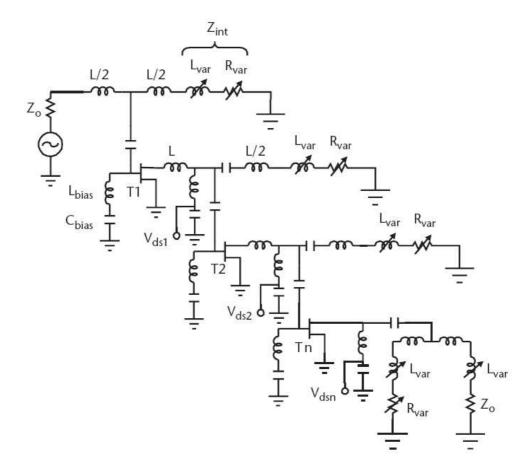

In cascaded, reactively terminated single stage distributed amplifier (CRTSSDA), the transistors are cascaded unlike the conventional traveling wave amplifier. Since CRTSSDA is also a distributed amplifier, gain and drain capacitances are absorbed into artificial transmission lines. The schematic of a CRTSSDA is given in Figure 2.4 [4].

Since the cut-off frequency of the artificial transmission lines limits the upper frequency of operation of the amplifier, reactive terminations are included in the topology as seen in Figure 2.4.

Transistors have 6 dB/octave gain roll off because of their intrinsic properties. To achieve broadband response, this roll off must be eliminated. If the cut-off frequencies of the artificial transmission lines are selected higher than the upper operating frequency, reactive terminations can be used to widen the band by removing gain roll off.

Figure 2.4 Cascaded Reactively Terminated Single Stage Distributed Amplifier [4]

Eliminating gain roll off is achieved by enhancing voltage swing at gate-to-source capacitance of each transistor. Resistors  $R_{var}$  and inductors  $L_{var}$  of Figure 2.4 form the reactive termination. Note that reactive terminations at gate terminals of each stage are responsible for voltage swing enhancement of the corresponding stage. Also, the reactive termination at the output helps for optimum match at the output for maximum power transfer to the load.

The impedance of reactive termination, labeled as  $Z_{int}$  in Figure 2.4 depends on frequency. Since the impedance of  $Z_{int}$  increases at higher frequencies because of the contribution of  $L_{var}$ , higher voltage will be coupled to the gate-to-source capacitance of the transistor. The coupled voltage than will be amplified through the transconductance of the active element and conducted to the next stage. After amplification through successive stages, a broadband gain is achieved at the output. Gain expression for an n-stage CRTSSDA is given as follows [4]:

$$G_{CRTSSDA} = \frac{1}{4} g_m^{2n} Z_{\text{int}}^{2(n-1)} Z_0^2$$

(2-2)

where  $g_m$  is the transconductance of the transistor,  $Z_{int}$  is the impedance of the reactive termination and  $Z_0$  is the characteristic impedance of the artificial transmission lines.

Gain of a CRTSSDA is an exponential function as seen from (2-2). This equation claims that the gain of a CRTSSDA is higher than the gain of TWDA given in (2-1) with equal number of stages.

Another advantage of CRTSSDA is that, it does not need any phase velocity equalization as in TWDA since the transistors are cascaded. The only constraint to achieve broadband is to design reactive terminations properly to adjust voltage swing at the gate of the stages. The number of stages is limited due to the gate and drain line attenuations in TWDA topology, however, there is not a limit for number of stages in CRTSSDA design.

Disadvantage of a CRTTSDA amplifier is that it is very sensitive to oscillation problems. Also biasing of each stage should be achieved individually and isolated from each other.

A 2-18 GHz broadband amplifier in CRTSSDA topology is designed and fabricated in this thesis study. Filtronic's FPD200, FPD6836 and FPD750 DPHEMT transistors are used in the design. Two trials of amplifiers are realized in Rogers4003 and Rogers4350 substrates and surface mount elements are used on fabrication. Details of the designed amplifiers are given in Chapter 3 where the fabrication and measurement sections are in Chapter 4.

## **CHAPTER 3**

## **DESIGN OF THE BROADBAND AMPLIFIER**

## 3.1 Introduction

Various design methods given in Chapter 2 are used to design broadband amplifiers recently. Among these circuit techniques, cascaded, reactively terminated, single stage distributed amplifier (CRTSSDA) design method [8] is used to design a 3-stage broadband amplifier, operating in 2-18 GHz band with gain  $23 \pm 1.5$  dB.

In this chapter, principles of a CRTSSDA design are given in detail. Afterwards, the proposed amplifiers are explained with design steps. Simulations and their results regarding to the designed amplifiers are also given in this chapter.

## 3.2 Principles of CRTSSDA

In a CRTSSDA structure, the transistors that constitute the amplifier are cascaded as the name implies. Cascading transistors eliminates the need for equalizing phase velocities of the stages as in conventional traveling wave amplifiers (TWA). Theory of CRTSSDA is basically based on conveying the signal from preceding stage to next together with amplifying. In order to achieve broadband response, voltage swing enhancements are made on gate-to-source voltages by including reactive terminations at each stage. Necessary matching networks at input, output and between stages are also included in a CRTSSDA topology as the other types of broadband amplifiers have.

Figure 3.1 Block Diagram of a CRTSSDA [4]

Transistors have 6dB/octave gain roll off because of their intrinsic properties. The crucial point for a CRTSSDA design is to overcome the gain roll off of the transistors. For a 3-stage and 3 octaves amplifier, gain roll off totals 54dB decrease in gain at the upper operating frequency. In order to eliminate this roll off and get a flat gain across the band, reactive terminations are included in CRTSSDA design.

### 3.2.1 Theory of Reactive Terminations

Block diagram of a CRTSSDA given in Figure 2.4 is redrawn in Figure 3.1 for convenience. The components; resistor Rvar and inductor  $L_{var}$  in Figure 3.1 are the reactive terminations. The impedance of the reactive termination,  $R_{var} + j\omega L_{var}$  is denoted as  $Z_{int}$  [8]:

$$Z_{\rm int} = R_{\rm var}(\omega) + j\omega L_{\rm var}(\omega)$$

(3-1)

Reactive termination  $Z_{int}$  has higher values when the frequency increases as seen in (3-1). This characteristic of reactive termination is used to adjust the voltage swing at the gate of transistors in a CRTSSDA. Having a frequency dependent voltage across the gate-to-source capacitance can be applied to compensate the intrinsic gain roll off. Analyzing a small signal model of a transistor with reactive termination helps to visualize the behavior of reactive termination. Figure 3.2 shows the small signal model of a single transistor with reactive terminations.

Figure 3.2 Small Signal Model of a Transistor with Reactive Terminations

The circuit given in Figure 3.2 shows the inclusion of reactive termination to enhance the voltage swing across gate-to-source capacitance  $C_{gs}$  for a single stage network. The transistor will amplify the voltage  $V_{gs}$  across  $C_{gs}$  by its transconductance  $g_m$ . Including reactive termination makes  $V_{gs}$  tend to be higher at higher frequencies than lower frequencies. It is suggested that, if the slope of  $V_{gs}$  is adjusted so as to equalize the roll off of the transistor, a flat gain will be achieved in broadband.

The output voltage  $V_{out}(\omega)$  is given in (3-2). Transconductance,  $g_m$ , is assumed to be constant with frequency, therefore, manipulations on the gate voltage will be enough to have rigorous solutions.

$$V_{out}(\omega) = g_m \times V_{gs}(\omega) \tag{3-2}$$

Since reactive termination is the key point for a flat gain in broadband, its characteristics must be exposed clearly. From DC to 1 GHz,  $L_{var}$  has negligible effect on the value of  $Z_{int}$  whereas  $R_{var}$  is the dominant contributor. The impedance of the reactive termination  $Z_{int}$  in Figure 3.2 can be expressed as in (3-3) for frequencies  $\leq 2$  GHz.

$$Z_{\rm int}(\omega) = R_{\rm var} \tag{3-3}$$

On the other hand, the impedance of  $L_{var}$  will be effective on  $Z_{int}$  at higher frequencies (>2 GHz).  $R_{var}$  is negligible compared to the impedance of  $L_{var}$ .  $L_{var}$  is the component that determines the amount of voltage at the gate of the transistor in the whole frequency band. (3-3) is rewritten as in (3-4) for frequencies > 2 GHz.

$$Z_{\rm int}(\omega) = j\omega L_{\rm var}(\omega) \tag{3-4}$$

It is obvious from (3-4) that  $L_{var}$  is effective on the gain of the amplifier in the full range of the band.  $L_{var}$  should be chosen very carefully in order to adjust the amount of the voltage that is to be amplified by the transconductance of each transistor.

In order to see the effect of reactive termination in Figure 3.2, a simulation using a CAD program named Advanced Design System 2006A (ADS) is performed. The values of the components shown in Figure 3.2 are chosen same as the ones of the first stage of the designed CRTSSDA. Those values for the components are given in Table 3-1.

|                                    | Symbol           | Value | Units |

|------------------------------------|------------------|-------|-------|

| Source Impedance                   | R <sub>s</sub>   | 50    | Ω     |

| Series inductor of artificial line | L                | 0.2   | nH    |

| Inductor of reactive termination   | L <sub>var</sub> | 1     | nH    |

| Resistor of reactive termination   | R <sub>var</sub> | 50    | Ω     |

| Gate-to-source capacitance         | C <sub>gs</sub>  | 0.2   | pF    |

| Transconductance of transistor     | g <sub>m</sub>   | 80    | mS    |

#### Table 3-1 Component Values of Figure 3.2

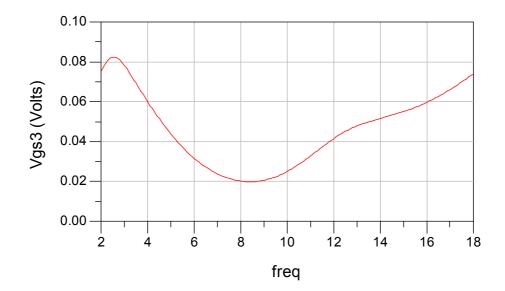

The input signal has a power of 0 dBm in the frequency range of 2-18 GHz and the corresponding simulation result is given in Figure 3.3

Figure 3.3 Enhancement of Voltage Swing Across  $C_{\rm gs}$  With Reactive Terminations

Figure 3.3 shows that including reactive termination provides an increasing  $V_{gs}$  in the band. So the gain roll off of the transistors can be eliminated and gain flatness in broadband is provided.

## 3.3 Design of the Proposed CRTSSDA

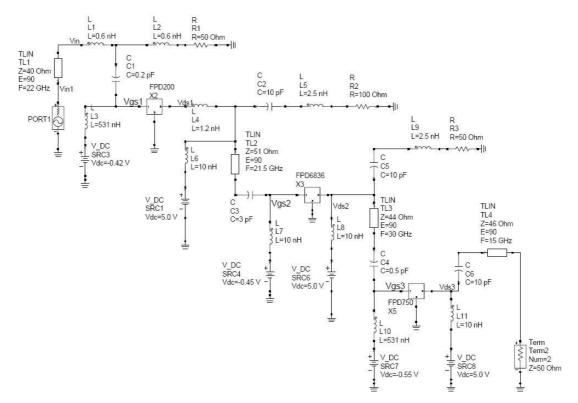

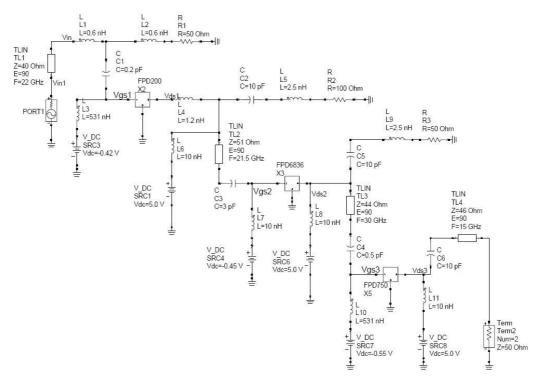

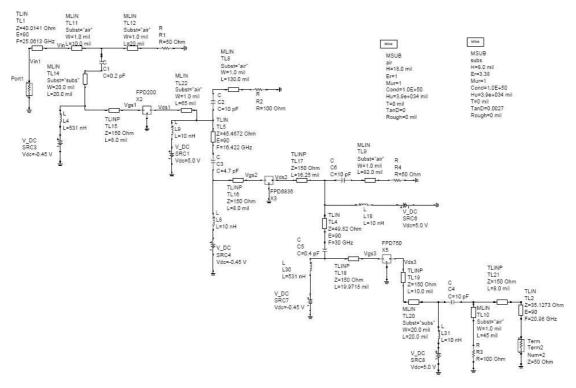

Cascaded, reactively terminated, single stage distributed amplifier, having 2-18 GHz band with gain 23  $\pm$  1.5 dB and VSWR<2 is designed in this thesis study. The transistors used in the design are Filtronic's FPD200, FPD6836 and FPD750 AlGaAs/InGaAs pseudomorphic high electron mobility (DPHEMT) transistors. The simulations during the design are performed on Advanced Design System 2006A (ADS). The schematic of the designed CRTSSDA is given in Figure 3.4

Figure 3.4 Schematic of the Proposed Amplifier

## 3.3.1 Brief description about the transistors used in the design:

#### **FPD200**

The FPD200 is an AlGaAs/InGaAs pseudomorphic High Electron Mobility Transistor (pHEMT), featuring a 0.25 µm by 200 µm Schottky barrier gate, defined by high-resolution stepper-based photolithography. The recessed gate structure minimizes parasitic to optimize performance. The epitaxial structure and processing have been optimized for reliable medium-power applications [13].

FPD200 is used in die form to avoid package parasitic in the design. It is biased to - 0.42 Volts at the gate and +5 Volts at the drain. The drain-to-source current ( $I_{ds}$ ) is 30 mA. The transconductance of FPD200 is 80 mS. Electrical specifications of FPD200 are given in Table 3-2.

|                                | Min  | Тур | Max | Units |

|--------------------------------|------|-----|-----|-------|

| Maximum Stable Gain            | 16   | 17  |     | dB    |

| Saturated Drain-Source Current | 45   | 60  | 75  | mA    |

| Transconductance               |      | 80  |     | mS    |

| Power at 1dB Gain Compression  | 18   | 19  |     | dBm   |

| Power Gain at P1dB             | 10.5 | 12  |     | dB    |

| Gate-Source Breakdown Voltage  | 12   | 14  |     | V     |

| Gate-Drain Breakdown Voltage   | 14.5 | 16  |     | V     |

Table 3-2 Electrical Specifications of FPD200

#### **FPD6836**

The FPD6836 is an AlGaAs/InGaAs pseudomorphic High Electron Mobility Transistor (PHEMT), featuring a 0.25 µm by 360 µm Schottky barrier gate, defined by high -resolution stepper-based photolithography. The recessed gate structure minimizes parasitic to optimize performance. The epitaxial structure and processing have been optimized for reliable high-power applications [14].

FPD6836 is used same as FPD200 in die form to avoid package parasitic in the design. It is biased to -0.5 Volts at the gate and +5 Volts at the drain. The drain-to-source current ( $I_{ds}$ ) is 32 mA. The transconductance of FPD6836 is 140 mS. Electrical specifications of FPD6836 are given in Table 3-3.

|                                | Min  | Тур  | Max | Units |

|--------------------------------|------|------|-----|-------|

| Maximum Stable Gain            | 15.5 | 16.5 |     | dB    |

| Saturated Drain-Source Current | 90   | 110  | 135 | mA    |

| Transconductance               |      | 140  |     | mS    |

| Power at 1dB Gain Compression  | 24.5 | 25.5 |     | dBm   |

| Power Gain at P1dB             | 9    | 10   |     | dB    |

| Gate-Source Breakdown Voltage  | 12   | 14   |     | V     |

| Gate-Drain Breakdown Voltage   | 14.5 | 16   |     | V     |

Table 3-3 Electrical Specifications of FPD6836

#### **FPD750**

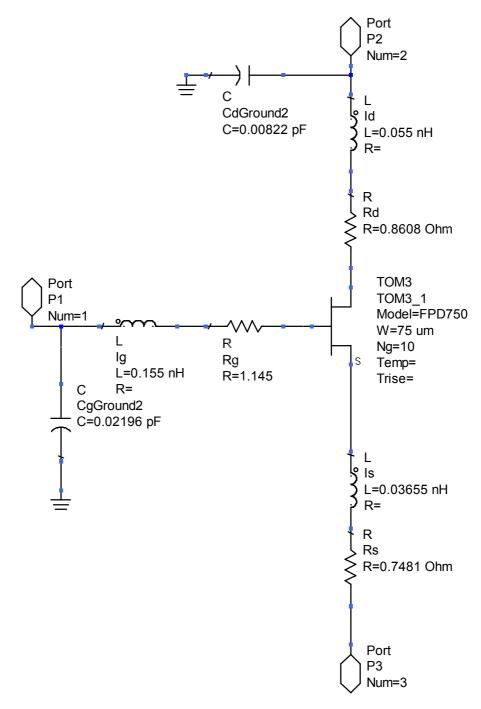

The FPD750 is an AlGaAs/InGaAs pseudomorphic High Electron Mobility Transistor (PHEMT), featuring a 0.25  $\mu$ m by 750  $\mu$ m Schottky barrier gate, defined by high-resolution stepper-based photolithography. The recessed gate structure minimizes parasitic to optimize performance. The epitaxial structure and processing have been optimized for reliable high-power applications. The FPD750 also features Si<sub>3</sub>N<sub>4</sub> passivation [15].

FPD750 is used in die form like FPD200 and FPD6836 to avoid package parasitic in the design. It is biased to -0.55 Volts at the gate and +5 Volts at the drain. The drain-to-source current ( $I_{ds}$ ) is 35 mA. The transconductance of FPD750 is 200 mS. Electrical specifications of FPD750 are given in Table 3-4.

|                                | Min  | Тур  | Max | Units |

|--------------------------------|------|------|-----|-------|

| Maximum Stable Gain            | 13.5 | 14.5 |     | dB    |

| Saturated Drain-Source Current | 185  | 230  | 280 | mA    |

| Transconductance               |      | 200  |     | mS    |

| Power at 1dB Gain Compression  | 26.5 | 27   |     | dBm   |

| Power Gain at P1dB             | 13.5 | 14.5 |     | dB    |

| Gate-Source Breakdown Voltage  | 12   | 14   |     | V     |

| Gate-Drain Breakdown Voltage   | 14.5 | 16   |     | V     |

Table 3-4 Electrical Specifications of FPD750

#### 3.3.2 Design Procedure:

As mentioned in the previous section, reactive terminations are used to enhance the voltage swing at the gate of each transistor that will be amplified. Designing these reactive terminations is the vital point in design of the amplifier since the theory of CRTSSDA is based on this issue.

In Chapter 2, it is mentioned that gain of a CRTSSDA is higher than a conventional traveling wave amplifier (TWA) with the same number of stages [4]. Comparing the gains of CRTSSDA and TWA will give the constraint for  $Z_{int}$ .

Gain of an ideal lossless n-stage conventional TWA is given by [12]:

$$G_{TWA} = \frac{1}{4} g_m n^2 Z_0^2$$

(3-5)

where n is the number of stages,  $Z_0$  is the characteristic impedance of the system and  $g_m$  is the transconductance.

In CRTSSDA structure, transistors are cascaded and the preceding transistor's output is input for the next transistor. Gain expression for CRTSSDA is given by [16]

$$G_{CRTSSDA} = \frac{1}{4} g_m^{2n} Z_{\text{int}}^{2(n-1)} Z_0^2$$

(3-6)

where  $Z_{int}$  is the internal characteristic impedance of the n-stage cascaded system and  $g_m$  and  $Z_0$  are as before.

The following equation can be derived in order for the gain of CRTSSDA to be higher than the gain of TWA.

$$G_{CRTSSDA} \ge G_{TWA}$$

(3-7)

(3-5) and (3-6) are substituted in (3-7) and after the simplifications, an expression for  $Z_{int}$  can be derived for n>1.

$$Z_{\rm int} \ge \frac{n^{\frac{1}{n-1}}}{g_m} \tag{3-8}$$

(3-8) shows that the impedance of reactive termination is dependent only on the number of stages, n, and the transconductance of the devices.

To estimate the value of  $Z_{int}$  for an amplifier including FPD200 transistors is done by substituting the value of transconductance of FPD200 into (3-8). If the designed amplifier is a 3-stage amplifier it will yield  $Z_{int} > 21.65 \Omega$ .

Remember that (3-3) claims  $Z_{int}$  is equal to  $R_{var}$  at low frequencies. Therefore, since  $R_{var}$  is independent of frequency, one may choose  $R_{var}$  to be greater than 21.65  $\Omega$ . The final value of  $R_{var}$  is determined after the optimizations to meet a good VSWR. Another point that should be taken into account while choosing the values of  $R_{var}$  is that, in order to be able to fabricate the designed amplifier, it is required to choose standard resistor values. Thin-film resistors are used in fabrication of this thesis work; therefore, the values chosen for  $R_{var1}$ ,  $R_{var2}$  and  $R_{var3}$  of Figure 3.4 are given in Table 3-5.

|                                                      | Symbol            | Value | Units |

|------------------------------------------------------|-------------------|-------|-------|

| Resistor of the 1 <sup>st</sup> Reactive Termination | R <sub>var1</sub> | 50    | Ω     |

| Resistor of the 2 <sup>nd</sup> Reactive Termination | R <sub>var2</sub> | 100   | Ω     |

| Resistor of the 3 <sup>rd</sup> Reactive Termination | R <sub>var3</sub> | 50    | Ω     |

Table 3-5 Resistor Values of Reactive Terminations of the Designed Amplifier

Designing the reactive terminations will be completed after determination of  $L_{var}$ . (3-4) is used to determine the value of  $L_{var}$  at high frequencies (>2 GHz). Substituting (3-4) into (3-8) will give the expression for  $L_{var}$ .

$$L_{\rm var} \ge \frac{n^{\frac{1}{n-1}}}{\omega g_m} \tag{3-9}$$

(3-9) suggests that Lvar depends on the number of the stages of the amplifier, the transconductance of the devices used and also on frequency.  $L_{var}$  not only determines the amount of voltage at the gate of each transistor to be amplified, but also plays critical role in input and output return loss and matching between stages. Therefore, choosing the most proper value of  $L_{var}$  is important.

Unfortunately, (3-9) is not enough to choose the value of  $L_{var}$ . The most appropriate values of  $L_{var}$  in the reactive terminations of Figure 3.4 are determined during the optimizations. Estimated values of  $L_{var}$  in the proposed amplifier are listed in Table 3-6.

|                                                        | Symbol            | Value | Units |

|--------------------------------------------------------|-------------------|-------|-------|

| Inductance of the 1 <sup>st</sup> Reactive Termination | L <sub>var1</sub> | 0.6   | nH    |

| Inductance of the 2 <sup>nd</sup> Reactive Termination | L <sub>var2</sub> | 2.4   | nH    |

| Inductance of the 3 <sup>rd</sup> Reactive Termination | L <sub>var3</sub> | 1.5   | nH    |

Table 3-6 Inductor Values of Reactive Terminations of the Designed Amplifier

In a broadband amplifier design, it is required to include matching networks at input, output ports and between stages of the amplifier. Conventional schematic of a 2-stage amplifier with matching networks is given in Figure 3.5

Figure 3.5 The General Transistor Amplifier Circuit

Input matching circuit determines how much of the input power is coupled to the first stage. In order to have a reasonable VSWR, successful input matching is required. This is achieved by including a transmission line (TL<sub>1</sub>) for impedance transformation, inductor  $L_1$ , capacitor  $C_1$  and the reactive termination  $R_{var1}$  and  $L_{var1}$  in Figure 3.4.

Intermatching network between FPD200 and FPD6836 in Figure 3.4 is constructed by the transmission line  $TL_2$ , inductor  $L_2$  and capacitor  $C_3$ . Capacitor  $C_3$  not only

provides matching between the stages, but also isolates DC biasing of the transistors from each other. In addition, the combination of  $L_2$ ,  $C_3$  and  $TL_2$  supports enhancement of voltage swing at the input of FPD6836 transistor with reactive termination  $R_{var2}$  and  $L_{var2}$ .

The second intermatching circuit is between the second and last stage, which are FPD6836 and FPD750 transistors. This matching circuit includes the capacitor  $C_5$  and transmission line TL<sub>3</sub>. These components also play a role on adjusting the voltage swing at the last stage with  $R_{var3}$  and  $L_{var3}$ .

Finally, an output matching circuit is included in the design of the proposed CRTSSDA. Output matching network is important because it determines the amount of power transmitted to the load and the output return loss. Inappropriate output matching can cause oscillations and also minimize the efficiency of the amplifier. As seen in Figure 3.4, transmission line  $TL_4$  is used for impedance transformation between FPD750 and R<sub>load</sub>, which is 50  $\Omega$  in the simulations.

## 3.4 Analysis and Simulation

The circuit given in Figure 3.4 is designed and analyzed using Advanced Design System 2006A. The components used in the circuit are ideal and lossless. TriQuint TOM3 Scalable Nonlinear FET Models [17] used to model FPD200, FPD6836 and FPD750 transistors in the simulations. TOM3 models for these transistors are given in Appendix A in detail.

There are two simulations performed for designing the proposed amplifier. In the first simulation, the components used are lossless and ideal and also, bond wires and other layout constraints applied on fabrication are not included in the simulation. These deficiencies cause unexpected results on fabricated amplifier measurements. In the second simulation, the experience gained throughout fabrication is used and more robust amplifier is designed considering experience on fabrication process. The layout constraints mentioned are the effect of pads left for mounting surface mount capacitors, thin-film resistors, bond wires that cause additional inductances and the

position of the components that are not included in simulations. These layout constraints and experience gained during fabrication will be explained detailed in the next chapter.

### 3.4.1 Simulation Results

## 3.4.1.1 1<sup>st</sup> Trial

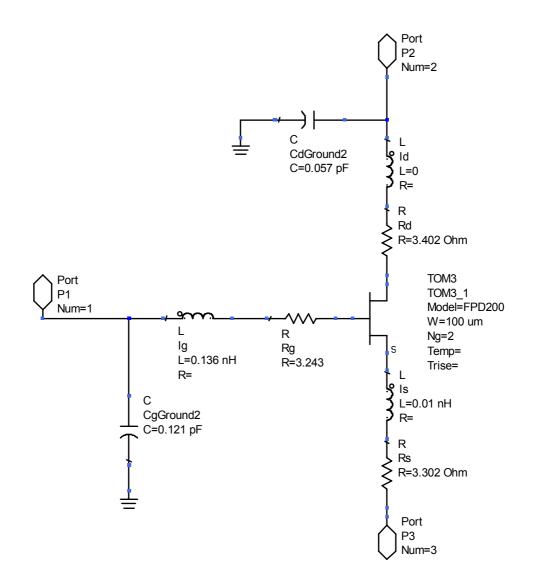

In the first design, the proposed CRTSSDA is constructed with ideal and lossless components. TOM3 models are used to simulate the transistors. The schematic of the finalized design is given in Figure 3.6.

Figure 3.6 Schematic of the Firstly Designed CRTSSDA

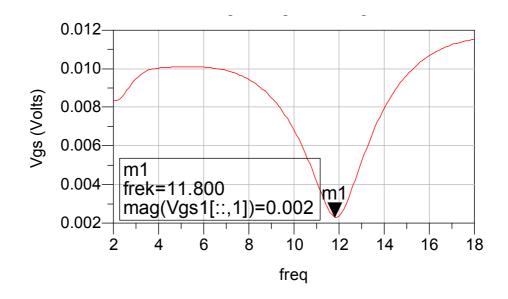

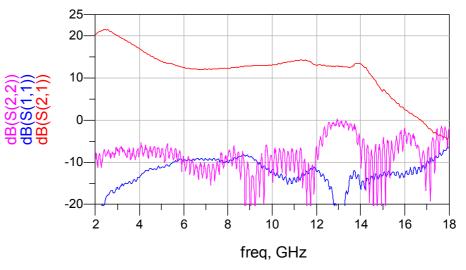

Simulations of the circuit given in Figure 3.6 are performed by s-parameter analysis on ADS. Figure 3.7 and Figure 3.8 give S21, S11 and S22 plots of simulation results respectively.

Figure 3.7 S21 Plot of The First CRTSSDA

Figure 3.8 S11 and S22 Plots of The CRTSSDA

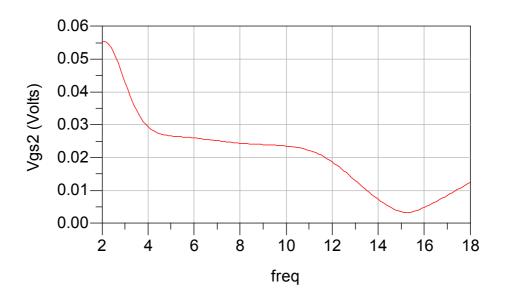

In order to see the enhancement of voltage swing provided by reactive terminations at the gate terminals of each transistor, harmonic balance simulation is ran on ADS. The nodes representing  $V_{gs}$  of each transistor are labeled in Figure 3.6. The following plots clearly show the aimed enhancements at these nodes.

Figure 3.9 Voltage Swing Enhancement of The First Stage

Figure 3.9 gives the voltage across the gate of FPD200 at the first stage with respect to frequency. Reactive termination for the first stage seems to compensate the gain roll off of the transistor, however, there is a resonance at f = 11.8 GHz as seen from the marker on the plot. The source of the resonance is thought to be the combination of the inductor L<sub>4</sub> in Figure 3.6 and gate-to-source capacitance C<sub>gs1</sub>. Simulations performed to see the reason of that resonance showed that changing the value of L<sub>4</sub> slides the frequency of resonance. However, despite of the resonance at 11.8 GHz, there is no resonance in the overall gain of the amplifier, because the voltage swing enhancements at the remaining stages compensate the notch of first stage at 11.8 GHz. This assertion is also proved by fabrication and measurement experience, where the existing oscillations are removed by tuning L<sub>4</sub>, which is explained in the next chapter in detail.

Enhancements on voltage swing of the second and the third transistor gate voltages are given in Figure 3.10 and Figure 3.11 respectively.

Figure 3.10 Voltage Swing Enhancement of The Second Stage

Figure 3.11 Voltage Swing Enhancement of The Third Stage

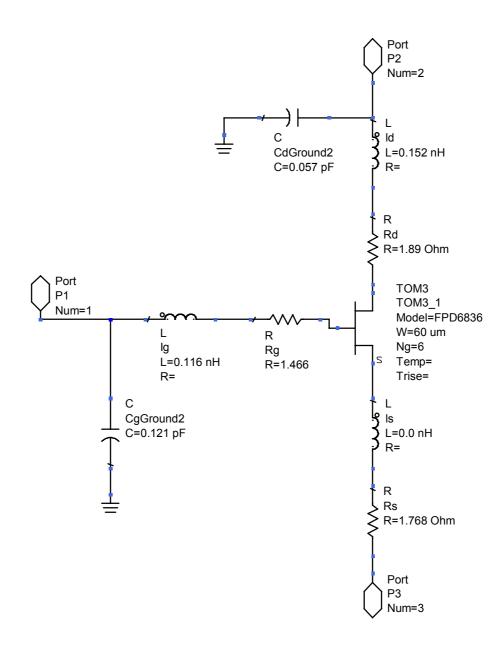

# 3.4.1.2 2<sup>nd</sup> Trial

In the first simulation, the gain obtained from CRTSSDA is  $22\pm4$  dB as given in Figure 3.7. There is a dramatic decrease of gain between 2-7 GHz which has to be improved. These results are also observed during the measurements of the fabricated amplifier. Having the layout experience, which will be mentioned in the next chapter,

the reasons for these deficiencies are noted and a second simulation is performed to solve these problems.

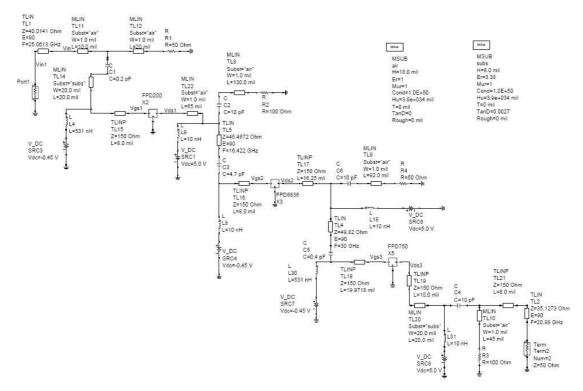

Second simulation contains all the contributing effects to the response of the amplifier such as layout pads, parasitic of the transistors and possible additional inductances caused by wire bonding. The schematic of the second design is given in Figure 3.12.

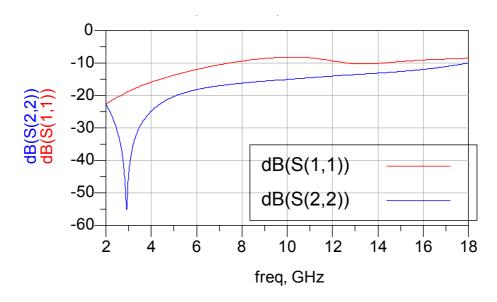

Figure 3.12 Schematic of The Second CRTSSDA

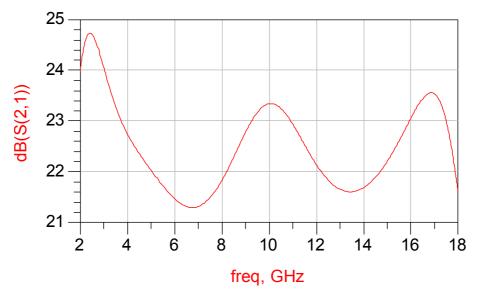

Note that the inductors except the choking coils in the first simulation are replaced with equivalent transmission lines, since these inductors are realized by wire bonding during fabrication. Replacing the inductors with transmission lines gives the ability to tune their values easily while making measurements on the fabricated amplifier. Transmission lines  $TL_{14}$  and  $TL_{20}$  of Figure 3.12 represent the pads left for mounting capacitors  $C_1$  and  $C_4$ , which cause extra capacitance that is not taken into account for the first simulation. Results of the simulations are given by the following plots.

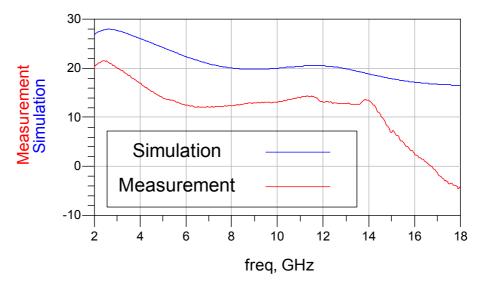

Figure 3.13 gives the s-parameter simulation result for the gain expression of the amplifier. Gain of this amplifier is  $23 \pm 1.5$  dB which is more successful than the first design in terms of gain flatness.

Figure 3.13 S21 Plot of The Second CRTSSDA

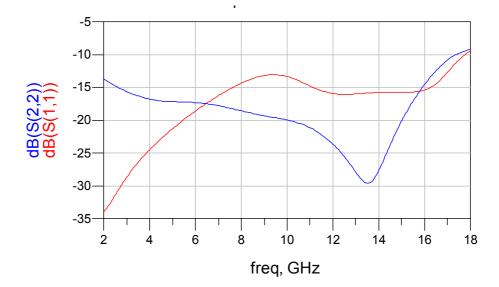

Input and output return loss for the second CRTSSDA is given in Figure 3.14.

Figure 3.14 S11 and S22 Plots of Second CRTSSDA

The second trial of CRTSSDA is better than the first trial in terms of gain flatness and input and output return loss. Also experience gained during fabrication of the first amplifier is employed on simulations of the second amplifier to get similar responses of the simulation and measurement of the second amplifier.

## **CHAPTER 4**

## FABRICATION AND MEASUREMENT

Fabricating an operating broadband amplifier is as difficult as designing it. There are many contributors to the response of the amplifier that cannot be observed during simulations on CAD programs. The components used in simulations are usually ideal components. Unfortunately, non ideal models of components are not always successful to model components exactly. Parasitic of both active and passive devices add up with additional layout pads left for mounting components and wire bonds for connections and result in a deviation of expected response of the amplifier.

Two different CRTSSDA amplifiers are designed in this thesis work as mentioned in the previous chapter. The first design is simulated using ideal components. Package parasitic of transistors are included in TOM3 models, where they should not be included, since the transistors used are in die form in this design. When the designed amplifier is fabricated, unexpected results are observed during measurements. The differences between simulation results and measurements are observed carefully to identify the reasons of failures. After determining the factors of unexpected results, a second design is performed. The second design includes effects of bond wires used for connections, additional layout pads, and package parasitic are not included in TOM3 models.

## 4.1 Choosing the Appropriate Substrate

Apart from component models or parasitic, the choice of substrate used on fabrication is also one of the most important tasks that must be taken into consideration.

The substrate used in high frequency applications, i.e.  $f \ge 2$  GHz, should be chosen carefully. The attenuation of substrate plays one of the main roles in these applications. The width of the substrate and tangent loss are the other factors that affect the performance of the substrate.

In Virdee's CRTSSDA [8], alumina substrate with  $\varepsilon_r = 9.8$  and height = 0.318 mm is used for the microstrip medium. On the other hand, the designed amplifiers of this thesis work are realized on Rogers4350 and Rogers4003 with permittivity  $\varepsilon_r = 3.48$ and  $\varepsilon_r = 3.38$  respectively. The substrate height for Rogers4350 is 0.254mm where the height of Rogers4003 is 0.2032 mm. Choosing lower height for dielectric thickness is important since the attenuation caused by the substrate increases proportionally with the height of dielectric. Dielectric loss affects the response of the amplifier in terms of a decrease in gain at higher frequencies.

Dielectric constant of a substrate varies with temperature. Amplifiers dissipate heat in a small area which causes high temperatures on board. If the substrate used on fabrication is very sensitive to temperature changes, it may result unpredictable results. Characteristic impedances of transmission lines evaluated in room temperature may change after a few minutes from power on. Change in characteristic impedance of transmission lines causes impedance mismatches that results decrease in gain and ruined input return loss. Rogers4350 substrate used in the first fabrication possesses a dielectric constant change by 0.8% between -50°C to 150°C. In the realization of the secondly designed amplifier, the substrate used is Rogers4003 and its dielectric constant changes 0.3% between -50°C to 150°C.

Another attribute of a substrate that affects the performance of the dielectric is the dissipation factor or tangent loss. Dissipation factor of Rogers 4350 is 0.037 where it is 0.027 for Rogers 4003.

## 4.2 Assembling the Components on PCB

The fabrication of the amplifier starts with the assembly of transistors on PCB. An appropriate amount of electrically conductive epoxy-adhesive is applied on the relevant points on PCB that the transistors lay on. After applying epoxy, the transistors are located on the epoxy-adhesive. The purpose of the epoxy-adhesive is to hold the components on PCB mechanically and to support heat and electrical conductivity. In order for epoxy to function properly, the PCB is kept in an oven at 80°C for 1.5 hours. Keeping the circuit in the oven hardens the epoxy and makes it conductive.

Wire-bonds of the transistors from source pads to ground and from drain and gate to the relevant pads are applied by a ball bonder machine after taking the amplifier out of the oven. The connections of the transistors are realized by golden wire bonds of diameter 18 um. The other wire bonds applied on the circuit to connect capacitors or resistors are realized by golden wire bonds of diameter 25 um. The reason for using thinner wire bonds for transistors is that the pads on transistors are not large enough for 25 um wire bonds. Figure 4.1 shows the ball bonder machine Kulicke Soffa AG 4124 used in fabrication of the designed amplifiers.

Figure 4.1 Ball Bonder Kulicke Soffa AG 4124

After assembling the transistors, remaining components are mounted on PCB. These remaining components are thin-film resistors, parallel plate capacitors and biasing coils. Thin-film resistors and parallel plate capacitors are laid on epoxy-adhesive like the transistors and then the PCB is kept in the oven at 80°C for 1.5 hours for the second time.

After bonding the capacitors and thin-film resistors, the biasing coils are added in the circuit. The coil tips are Teflon-plated where Teflon is a non conductive material. In order to acquire conductance on the tips, the covered Teflon is removed by a lancet. Attention must be paid while shelling the coil in order not to harm the copper of the wire.

Figure 4.2 An Air Core Coil, A Shelled Tip, And Wedge Bonding On A Capacitor

The coils are connected by Unitex Equipment Wedge Bonder machine. Figure 4.2 shows an air core biasing coil of 10 nH, a coil tip that is shelled and a coil wedge bonded on a capacitor.

After mounting all the components on board, RF connectors are soldered. RF connector's ground must be in touch in an as large as area for a good input reflection loss. Capacitors used for filtering the bias sources are also soldered to source pads left on PCB design. Wire bonds can be applied only to the gold plated areas on PCB, therefore, solder used for mounting filtering capacitors or connectors must not spread over the gold plated areas.

#### 4.3 Measurement Setup and DC Biasing of Transistors

Measurement of an amplifier consisting of die-form transistors is a challenge. The transistors are very sensitive to electrostatic discharge (ESD). Handling precautions should be taken during the measurements in order to prevent ESD problems. Another point that should be paid attention on is that biasing of the transistors should be done in the appropriate order.

Transistors FPD200, FPD6836 and FPD750 are n-channel transistors. Therefore, gate-to-source ( $V_{gs}$ ) biasing voltages are negative for these transistors. Drain-to-source voltages ( $V_{ds}$ ) are positive and should not be applied before  $V_{gs}$  is on. It is given in the datasheets of the transistors [13-15] that  $0 > V_{gs} > -3V$ . In order to prevent drain port to pull high currents,  $V_{gs}$  is hold at -3V at start up.

After switching  $V_{gs}$  on at -3V,  $V_{ds}$  is gradually increased from 0V to +5V. The required drain currents are approximately 30 mA at each transistor as designed and simulated. During these steps, the gate-to-source current should be 0 mA. If there is any current drawn from gate ports, there seems to be problem about the transistors. At the moment where  $V_{gs} = -3V$  and  $V_{ds} = 5V$ , the expected drain current (I<sub>ds</sub>) is 0 mA. Now, to make the channel of the transistor on,  $V_{gs}$  is gradually increased until I<sub>ds</sub> = 30mA. The biasing voltages and corresponding currents are given in Table 4-1.

|            | 1 <sup>st</sup> Fabricated Amplifier |             | 2 <sup>nd</sup> Fabricated Amplifier |                     | mplifier    |                      |

|------------|--------------------------------------|-------------|--------------------------------------|---------------------|-------------|----------------------|

| Transistor | V <sub>gs</sub> (V)                  | $V_{ds}(V)$ | I <sub>ds</sub> (mA)                 | V <sub>gs</sub> (V) | $V_{ds}(V)$ | I <sub>ds</sub> (mA) |

| FPD200     | -0.45                                | 5           | 26                                   | -0.42               | 5           | 25                   |

| FPD6836    | -0.60                                | 5           | 32                                   | -0.60               | 5           | 30                   |

| FPD750     | -0.66                                | 5           | 37                                   | -0.70               | 5           | 29                   |

Table 4-1 Biasing Current and Voltage Values of Transistors

Limiting current that is drawn from DC supplies is an effective way to prevent transistors from burning out. DC power supplies are limited to 10mA at the terminals that supply gates of the transistors and to 50mA that supply drain ports.

Unfortunately, unexpected high currents do not always mean that there is a problem about the transistors. High current and unstable voltage values usually mean that the amplifier faces oscillation problems. It is usually hard to find the source of oscillations. During measurements, various oscillations are observed and how to remove these oscillations are explained in the next sections.

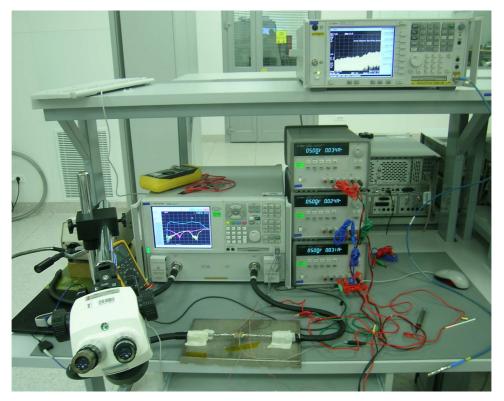

Measurements of the fabricated amplifiers are performed using Agilent Technologies E8364B PNA Network Analyzer, Agilent Technologies E3631A Triple Output DC Power Supplies and a microscope of Cambridge Instruments. The measurement setup is given in Figure 4.3.

Figure 4.3 Measurement Setup

While measuring the fabricated amplifiers, attenuators of 10dB, operating between DC-40 GHz are included both at the input and output of the amplifiers. The reason of including attenuators is to prevent any damage to the measurement devices in case of any oscillation. The calibration applied on network analyzer before measurement consists of these attenuators.

Agilent Technologies 85052 B 3.5mm calibration kit is used to calibrate the network analyzer. A successful calibration is one of the important tasks that must be performed to have accurate results. Since the measured device is an amplifier, it has a high tendency to oscillate. In order not to damage PNA in case of any oscillation, port input power is adjusted to -40 dBm. The number of points of calibration is set to 1601 points in order to have a good resolution on the response.

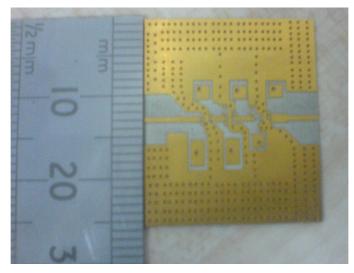

## 4.4 Layout of the First Amplifier

Layout of the first designed amplifier is fabricated on Rogers 4350 substrate with height 0.254 mm and relative permittivity  $\varepsilon_r = 3.48$ . The first designed amplifier is given in Figure 3.6. Figure 3.6 is redrawn as Figure 4.4 below for convenience.

Figure 4.4 Schematic of the First Designed CRTSSDA

Inductors of Figure 4.4 are all packaged inductors except  $L_1$  and  $L_2$  at the input of the first stage. The packaged inductors are in 201 geometry, which are thought to operate at 18 GHz.  $L_1$  and  $L_2$  are realized by wire bonding during fabrication. It is observed from simulations that values of  $L_1$  and  $L_2$  affect the gain and VSWR in the whole band. Tuning  $L_1$  and  $L_2$  is done by changing the length of the bonds or bending to make far or near to the ground plane. Inductance of a wire bond is calculated as follows:

$$L(nH) = 2 \times l \times (\ln(l/d) + 0.5 + 0.22 \times 2 \times d/l) / 10000$$

(4-1)

where L is the resultant inductance in nH; l is the length and d is the diameter of wirebond both in um.

Diameter of the wirebond used in fabrication is 25 um. In order to have 0.6 nH inductance for  $L_1$  and  $L_2$  in Figure 4.4, it is estimated that the required length of the wirebond is approximately 770 um from (4-1).

Capacitors  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ ,  $C_5$  and  $C_6$  in Figure 4.4 are parallel-plate 254um x 254um surface mount capacitors. They are stick on the board by epoxy at one side and then held in oven for an hour at 80°C. The other side of the capacitor is the area where the necessary wire bondings are applied.

FPD200, FPD6836 and FPD750 transistors are also mounted on board like capacitors. These transistors' source-pads are not grounded by default. Therefore, their source-pads are connected to ground plane of board via wire bonding. Wire bonding made from the transistors' source-pads must be as short as possible in order not to have additional inductance from source to ground. Any inductance from source-pad of a transistor to ground results loss in gain which is observed during simulations. The length of wire bonds from source pads of transistors to ground are a few micrometers length in the fabricated amplifiers of this thesis work.

Transmission lines seen in Figure 4.4 are realized as microstrip lines. The width of a microstrip line is determined by its impedance value, relative permittivity and height of the substrate used. The length of a microstrip line is determined by frequency and electrical length of the transmission line. The values of impedance and the frequency where the electrical length of the line is 90° are listed in Table 4-2.

|                 | Impedance(Ω) | Frequency @<br>E=90° | Width(mm) | Length(mm) |

|-----------------|--------------|----------------------|-----------|------------|

| TL <sub>1</sub> | 40           | 22 GHz               | 0.81      | 2          |

| TL <sub>2</sub> | 51           | 21.5 GHz             | 0.56      | 2.01       |

| TL <sub>3</sub> | 46           | 15 GHz               | 0.65      | 2.98       |

Table 4-2 Estimated Dimensions For Transmission Lines in Figure 4.4

After determining the dimensions of the transmission lines, the task is now to locate the components on board carefully for connecting the components at minimum distance from each other. The length of wire bonds between components must be minimized to avoid additional inductances. In order to be able to solder connectors,  $50\Omega$  microstrip lines with length 4mm is left at the input and output of the amplifier. Also as seen in Figure 4.5, the edged board is gold plated to be able to make wire bonds available.

Figure 4.5 Layout of the First Designed CRTSSDA

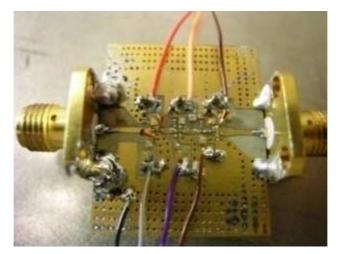

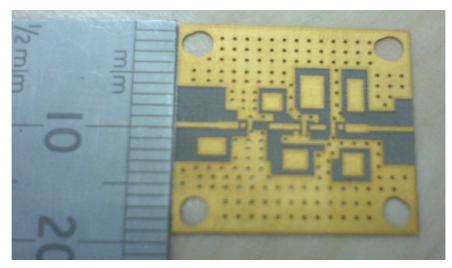

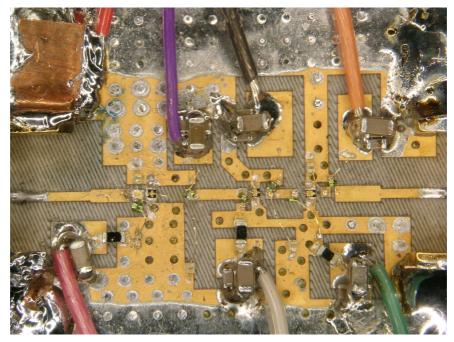

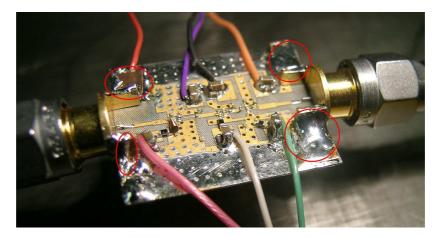

The components are assembled on PCB in clean room facility of ASELSAN Inc. The fabricated amplifier is given in Figure 4.6.

Figure 4.6 First Fabricated CRTSSDA

After the assembling of the amplifier, measurements are performed. These measurements are compared with the simulations of the first design.

## 4.5 Measurements of the First Amplifier

The amplifier given in Figure 4.6 is measured. In the first measurement of the amplifier, there are observed oscillations at  $f \leq 200$  MHz. These low frequency oscillations are seen because the matching of the transistors is valid for 2-18 GHz. Low frequency oscillations are removed by adding serial resistors to the gate biasing of the transistors. The values of resistors connected to the gate biasing are determined by the gate peripheries of the transistors. These values are listed in Table 4-3.

|                                      | Symbol          | Value | Units |

|--------------------------------------|-----------------|-------|-------|

| Resistor of the 1 <sup>st</sup> Bias | R <sub>b1</sub> | 50    | Ω     |

| Resistor of the 2 <sup>nd</sup> Bias | R <sub>b2</sub> | 30    | Ω     |

| Resistor of the 3 <sup>rd</sup> Bias | R <sub>b3</sub> | 15    | Ω     |

Table 4-3 Resistors Included to Prevent Low Frequency Oscillation

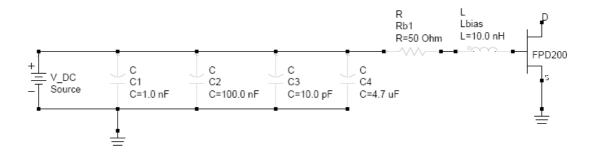

Therefore, the biasing circuit is applied as in Figure 4.7 for the first stage. Same biasing circuits with the values of the resistors in Table 4-3 are applied at each stage.

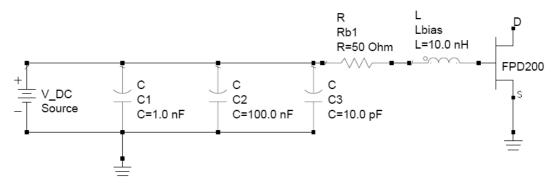

Figure 4.7 Gate Biasing of The First Stage

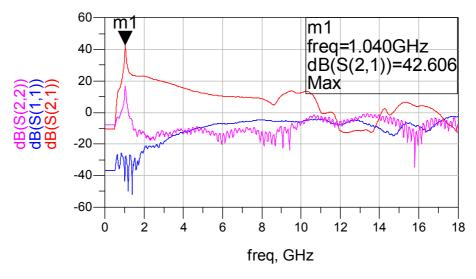

After eliminating low frequency oscillations by including series resistor as shown in Figure 4.7, s-parameter measurement is performed. In this measurement there appeared another oscillation at f = 2 GHz. Inductor  $L_{bias}$  of Figure 4.7 is an air cored inductor. During tunings on the amplifier, when the turnings of the inductor are loosened, the oscillation frequency shifts to 1.04 GHz. Shifting of oscillation frequency shows that the source of oscillation is the biasing coil. The oscillation can be observed in Figure 4.8.

Figure 4.8 Oscillation Caused By Biasing Inductor

The oscillation seen in Figure 4.8 is eliminated by changing  $L_{bias}$  to a conical biasing inductor of value 531 nH as seen in Figure 4.4. The s-parameter result of the amplifier after eliminating oscillation is given in Figure 4.9.

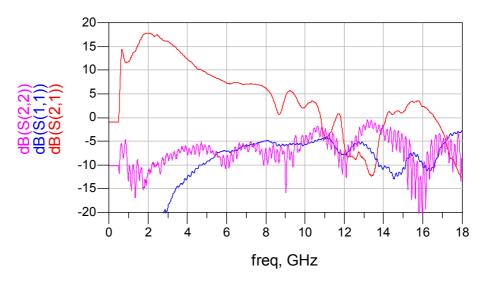

Figure 4.9 S-Parameters After Eliminating Oscillation

Despite that the oscillations are eliminated, the gain and input and output matching of the amplifier seem to be unsuccessful according to the simulation results given in Figure 3.7 and Figure 3.8. Tunings and improvements are applied on the circuit to correct the response of the amplifier.

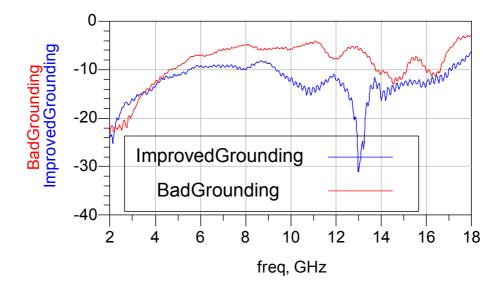

Grounding in high frequency applications is one of the important tasks that an engineer must pay attention. Via holes seen in Figure 4.5 are placed at 0.6 mm away from each other. Distance between vias should be  $\lambda/10$  conventionally, where  $\lambda$  is the wavelength of the signal. The expression to calculate wavelength is given in (4-2)

$$\lambda = \frac{c}{f\sqrt{\varepsilon_r}} \tag{4-2}$$

Where c is the velocity of light in m/s; f is the frequency in Hertz and  $\varepsilon_r$  is the dielectric constant of the substrate.

Wavelength,  $\lambda$ , for f = 18 GHz is estimated to be 8.9 mm for Rogers 4350. Therefore, minimum distance between via holes should be 0.89 mm. 0.6 mm distance between via holes therefore seems to be acceptable.

However, a good grounding is not only related with the distance of via holes. The ground of connectors should be in touch with PCB's ground at the largest area it can. A copper plate is soldered to the ground area of the connector and the other end of the copper plate is soldered to the PCB in Figure 4.6. In order to see the effect of good grounding of the connectors the following measurement result is given in Figure 4.10

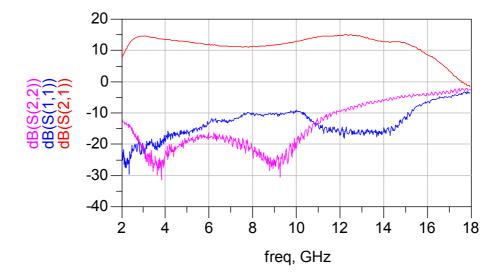

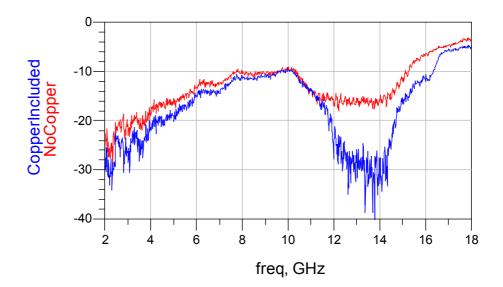

Figure 4.10 S-Parameters After Improved Grounding of Connectors

Input return losses, S(1,1) of Figure 4.9 and Figure 4.10 are redrawn in Figure 4.11 to see the effect of grounding:

Figure 4.11 Input Return Loss After Improved Grounding of Connectors

Although the input return loss is improved it is still not acceptable for the designed amplifier. The aimed VSWR of the amplifier is less than 2.0, therefore it is required

to have a input return loss that is better than 9.5 dB. Gain and the output return loss also seem to be unsuccessful from Figure 4.10.

In order to have the expected response of the fabricated amplifier in Figure 4.6, tunings are performed on the components. It is observed from the tunings that biasing coils should be as near as to the gate and drains of the related transistors. In other words, the RF path to the biasing DC sources must be very short. In the first measurements given before, the biasing coils are wire bonded on the capacitors and then connected to the related port of the transistor via wire bonding. That wire bonds connecting biasing coils to the transistors behave like small valued inductors in a few nH values. These inductances demolish the input and inter stage matching. Therefore these extra inductances cause a decrease in gain and a bad VSWR.

In order to improve the gain and matching of the amplifier, the biasing coils are reconnected to the related terminals to shorten the RF paths toward DC sources. The improved circuit is measured and the following response is obtained.

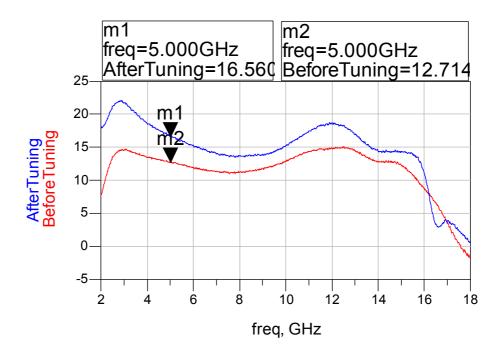

Figure 4.12 Final Response of the First Fabricated Amplifier

Figure 4.12 shows that the input return loss is improved to an acceptable level. Fabricated amplifier operates up to 14 GHz; however its gain is not as high as in the simulation results. Tunings on biasing coils and shortening the length of wire bonds are not enough to improve the whole response. There are also extra pads left for mounting capacitors on the PCB. For example a square of 20milx20mil area is left for a 10milx10mil parallel plate capacitor. The pad area also exhibits as an additional capacitor that is not included in the simulation. Therefore, the expected result differs than the simulation results.