# COST-EFFECTIVE FAULT TOLERANT ROUTING IN NETWORKS ON CHIP

VENERA ADANOVA

SEPTEMBER 2008

# COST-EFFECTIVE FAULT TOLERANT ROUTING IN NETWORKS ON CHIP

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

#### VENERA ADANOVA

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

COMPUTER ENGINEERING

SEPTEMBER 2008

## Approval of the thesis

# COST-EFFECTIVE FAULT TOLERANT ROUTING IN NETWORKS ON CHIP

submitted by Venera Adanova in partial fulfillment of the requirements for the degree of Master of Science in Computer Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Science</b>   | - |      |

|----------------------------------------------------------------------------------------|---|------|

| Prof. Dr. Volkan Atalay<br>Head of Department, <b>Computer Engineering</b>             |   |      |

| Assoc.Prof. Dr. Ali Hikmet Dogru<br>Supervisor, <b>Computer Engineering Department</b> |   |      |

| Examining Committee Members                                                            |   |      |

| Prof.Dr.Müslim Bozyigit<br>Computer Engineering Dept., METU                            |   | <br> |

| Assoc.Prof. Dr. Ali Hikmet Doğru<br>Computer Engineering Dept., METU                   |   |      |

| Prof.Dr.Adnan Yazıcı<br>Computer Engineering Dept., METU                               |   |      |

| Assoc.Prof.Dr.Ahmet Cosar<br>Computer Engineering Dept., METU                          |   | <br> |

| Dr.Sevgi Özkan<br>Graduate School of Informatics, METU                                 |   | <br> |

|                                                                                        |   |      |

Date:

| I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work. |                                 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

|                                                                                                                                                                                                                                                                                                           |                                 |  |

|                                                                                                                                                                                                                                                                                                           |                                 |  |

|                                                                                                                                                                                                                                                                                                           | Name, Last name: Venera Adanova |  |

|                                                                                                                                                                                                                                                                                                           | Signature :                     |  |

|                                                                                                                                                                                                                                                                                                           |                                 |  |

|                                                                                                                                                                                                                                                                                                           |                                 |  |

#### **ABSTRACT**

# COST-EFFECTIVE FAULT TOLERANT ROUTING IN NETWORKS ON CHIPS

Adanova, Venera

M.Sc., Department of Computer Engineering

Supervisor: Assoc.Prof. Dr. Ali Hikmet Doğru

September 2008, 87 pages

Growing complexity of Systems on Chip (SoC) introduces interconnection problems. As a solution for communication bottleneck the new paradigm, Networks on Chip (NoC), has been proposed. Along with high performance and reliability, NoC brings in area and energy constraints. In this thesis we mainly concentrate on keeping communication-centric design environment fault-tolerant while considering area overhead. The previous researches suggest the adoption solution for fault-tolerance from multiprocessor architectures. However, multiprocessor architectures have excessive reliance on buffering leading to costly solutions. We propose to reconsider general router model by introducing central buffers which reduces buffer size. Besides, we offer a new fault-tolerant routing algorithm which effectively utilizes buffers at hand without additional buffers out of detriment to performance.

Keywords: Networks on Chip, Fault-Tolerant Routing, Wormhole Routing

## YONGALARDA MALİYETİ UYGUN HATAYA DAYANIKLI YÖNLENDİRME AĞI

Adanova, Venera

Yüksek Lisans, Bilgisayar Mühendisliği Bölümü

Tez Yöneticisi: Doç. Dr. Ali Hikmet Doğru

Eylül 2008, 87 sayfa

Yonga Üstü Sistem'in (YÜS) artan karmaşıklığı bağlantı sorunlarına yol açmaktadır.İletişimdeki bu darboğaza çözüm olarak yeni bir model olan Yonga Üstü İletişim Ağ (YÜİA) ileri sürülmüştür. Yüksek performans ve güvenilirliği yanında, YÜİA alan ve enerji kısıtlaması kazandırmaktadır. Bu tezde esas olarak, alanı sabit tutmayı gözetirken, iletişim merkezli tasarım çevresini hataya dayanıklı olarak tutmaya odaklandık. Önceki araştırmalar, çokişlemci mimarilerden hataya dayanıklı çözümler uyarlamayı öneriyorlar. Fakat, çoğu zaman çok işlemci mimariler pahalı çözümlere yol açan tampon belleklemeye dayanırlar. Tampon bellek boyutunu küçülten merkezi tampon bellekleri tanıtarak genel yönlendirici modeli yeniden ele almayı öneriyoruz. Bunun yanında, performansı düşürmeyen ek tampon belleksiz, eldeki tampon belleklerden etkili biçimde yararlanan hataya dayanıklı yeni bir yönlendirici algoritma sunuyoruz.

Anahtar Kelimeler: Yonga Üstü İletişim Ağı, Hataya Dayanıklı Yönlendirme, Solucan

Yönlendirme

Апама арналат

Dedicated to my mother

### **ACKNOWLEDGEMENTS**

I am deeply grateful to my thesis supervisor, Assoc. Prof. Dr. Ali Hikmet Dogru, for his guidance, support and encouragement throughout my thesis work.

I would like to thank my friend Rita Ismailova for her invaluable support and assistance both in my thesis work and in my life.

# TABLE OF CONTENTS

| ABSTRACT                               | iv   |

|----------------------------------------|------|

| ÖZ                                     | v    |

| DEDICATION                             | vi   |

| ACKNOWLEDGEMENTS                       | vii  |

| TABLE OF CONTENTS                      | viii |

| LIST OF FIGURES                        | xi   |

| LIST OF TABLES                         | xiii |

| LIST OF ABBREVIATIONS                  | xiv  |

| CHAPTERS                               |      |

| 1. INTRODUCTION                        | 1    |

| 2. BACKGROUND                          | 5    |

| 2.1 NETWORK TOPOLOGY                   | 6    |

| 2.1.1 Octagon                          | 6    |

| 2.1.2 CLICHÉ                           | 7    |

| 2.1.3 2D Torus                         | 8    |

| 2.1.4 Tree Architectures               | 10   |

| 2.1.5 Comparison of Network Topologies | 11   |

| 2.2 SWITCHING TECHNIQUES               | 12   |

| 2.2.1 Circuit Switching                | 12   |

| 2.2.2 Packet Switching                 | 13   |

| 2.2.3 Virtual Cut-Through              |      |

| 2.2.4 Wormhole Switching                                        | 14 |

|-----------------------------------------------------------------|----|

| 2.2.5 Virtual Flow Control                                      | 15 |

| 2.2.6 Comparison of Switching Techniques                        | 17 |

| 2.3 ROUTING ALGORITHMS                                          | 17 |

| 2.3.1 Deadlock, Livelock and Starvation                         | 18 |

| 2.3.2 Oblivious Routing Algorithms                              | 20 |

| 2.3.3 Adaptive Routing Algorithms                               | 24 |

| 2.4 FAULT TOLERANT ROUTING                                      | 29 |

| 2.4.1 Fault Models                                              | 30 |

| 2.4.2 Fault-Tolerant Routing Using SAF and VCT Techniques       | 31 |

| 2.4.3 Fault-Tolerant Routing Using Wormhole Switching Technique | 32 |

| 2.4.4 Dynamic Recovery                                          | 37 |

| 2.5 Traffic Generator Models                                    | 39 |

| 3. NETWORK SIMULATOR AND SIMULATION ANALYSIS                    | 43 |

| 3.1 Network Simulator                                           | 43 |

| 3.1.1 Embedded Protocols                                        | 44 |

| 3.2 ROUTER MODEL                                                | 45 |

| 3.3 NETWORK SIMULATION                                          | 46 |

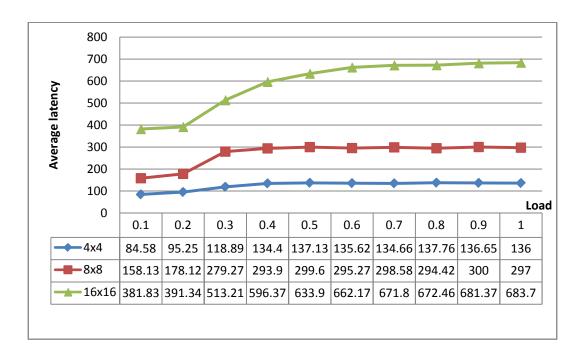

| 3.3.1 Effect of Network Size                                    | 49 |

| 3.3.2 Effect of Packet Size                                     | 50 |

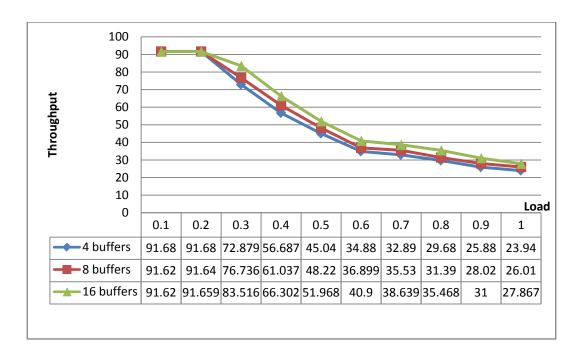

| 3.3.3 Effect of Buffer Depth                                    | 52 |

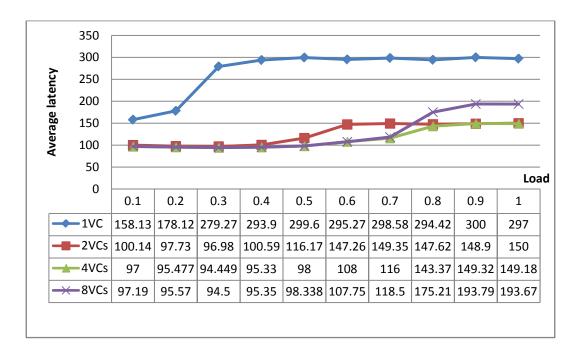

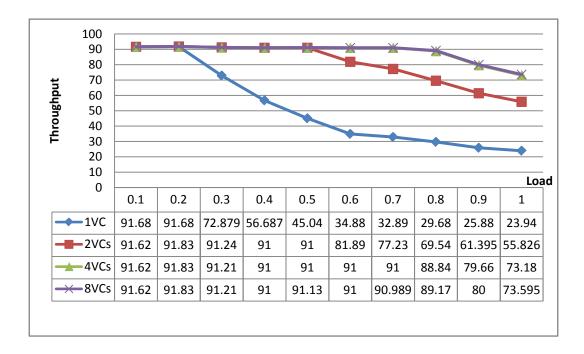

| 3.3.4 Effect of VC Size                                         | 55 |

| 4. FAULT-TOLERANT ROUTING ALGORITHMS AND SIMULATION             |    |

| RESULTS                                                         | 57 |

| 4.1 Fault Model                                                 | 57 |

| 4.1.1 Formation of f-rings and f-chains                         | 58 |

| 4.2 F-Cube4 Algorithm                             | 59 |

|---------------------------------------------------|----|

| 4.2.1 Performance Evaluation of f-Cube4 Algorithm | 61 |

| 4.3 Shared Buffer Algorithm                       | 64 |

| 4.3.1 Performance Evaluation of SB algorithm      | 68 |

| 4.4 GENERAL VIEW ON ALGORITHMS                    | 73 |

| 4.4.1 Efficiency level of buffer utilization      | 77 |

| 4.4.2 Comparison of algorithms                    | 78 |

| 5. CONCLUSION AND FUTURE WORK                     | 81 |

| REFERENCES                                        | 83 |

## LIST OF FIGURES

#### **FIGURES**

| Figure 1 Octagon [22]                                                       | 7         |

|-----------------------------------------------------------------------------|-----------|

| Figure 2 CLICHÉ [22]                                                        | 8         |

| Figure 3 2D Torus [22]                                                      | 9         |

| Figure 4 Folded Torus [22]                                                  | 9         |

| Figure 5 SPIN [22]                                                          | 10        |

| Figure 6 BFT [22]                                                           | 11        |

| Figure 7 Virtual channels                                                   | 16        |

| Figure 8 An example of deadlock [12]                                        | 19        |

| Figure 9 A possible path from source to destination using 3-phase ROMM      | 1 on a 2- |

| dimensional mesh                                                            | 23        |

| Figure 10 The channels for an adaptive plane $A_i$                          | 25        |

| Figure 11 (a) 8 possible turns, (b) 4 turns allowed by XY-routing, (c) 2 pr | ohibited  |

| turns in West-First routing [18]                                            | 28        |

| Figure 12 West-First routing [18]                                           | 28        |

| Figure 13 f-rings, f-chain and overlapping f-rings                          | 34        |

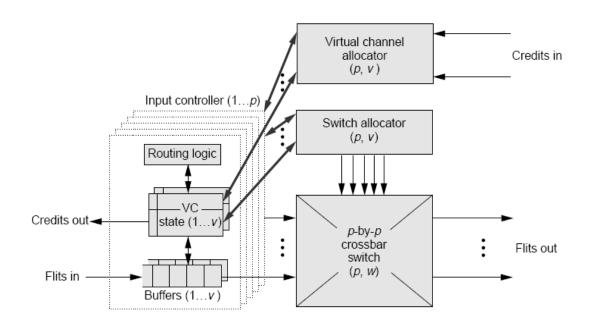

| Figure 14 Canonical virtual channel router architecture [52]                | 45        |

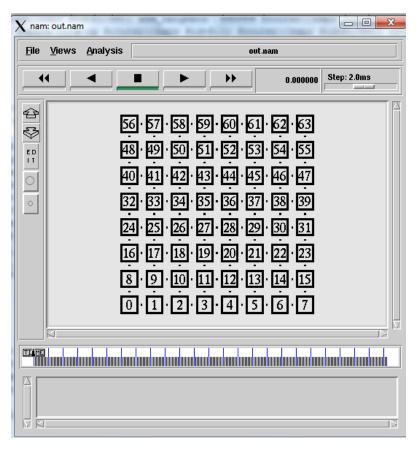

| Figure 15 Visual graphic of a network in ns-2                               | 48        |

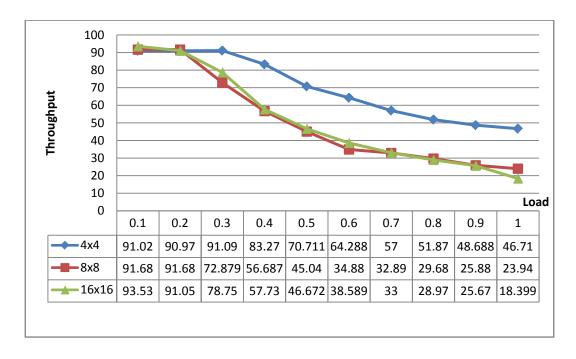

| Figure 16 Average latency under different network sizes                     | 49        |

| Figure 17 Throughput under different network sizes                          | 50        |

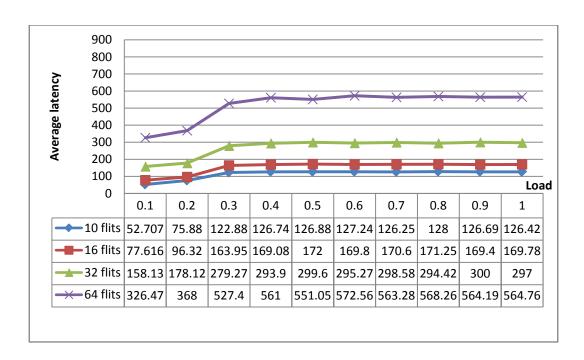

| Figure 18 Average latency under different packet sizes                      | 51        |

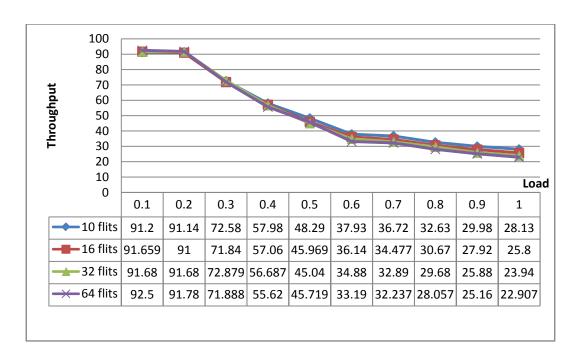

| Figure 19 Throughput under different packet sizes                           | 52        |

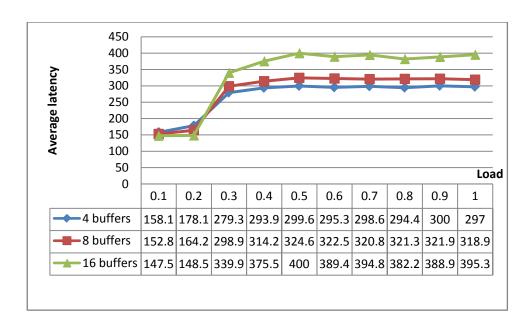

| Figure 20 Average latency under different buffer depth                      | 53        |

| Figure 21 Throughput under different buffer depth                           | 54        |

| Figure 22 Average latency under different VC sizes                          | 55        |

| Figure 23 Throughput under different VC sizes                               | 56        |

|                                                                             |           |

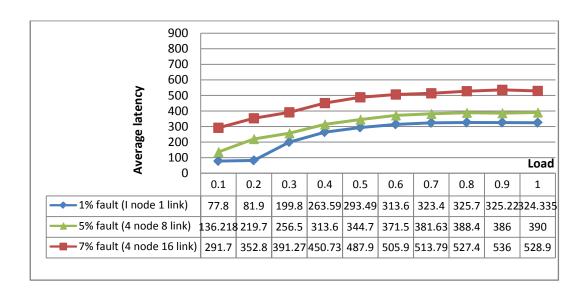

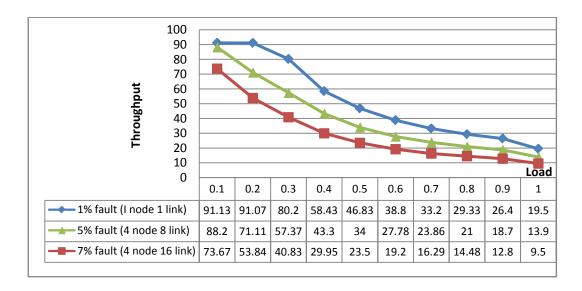

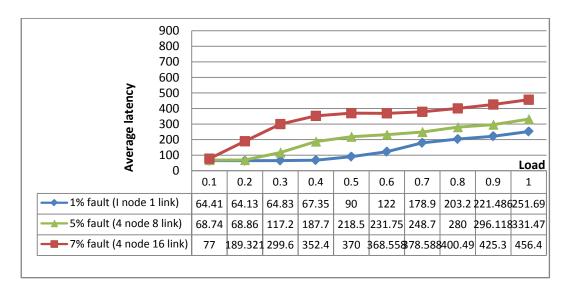

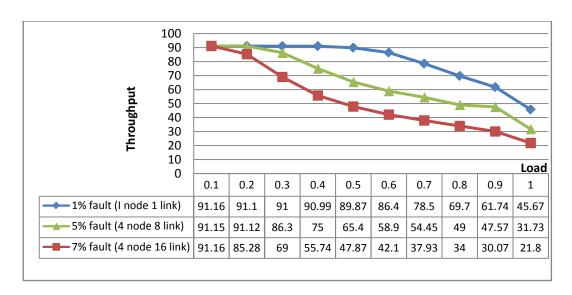

| <b>Figure 24</b> Average latency of f-Cube4 under various fault patterns       | 62 |

|--------------------------------------------------------------------------------|----|

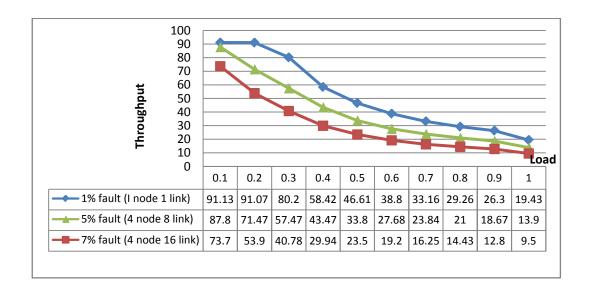

| Figure 25 Throughput of f-Cube4 under various fault patterns                   | 62 |

| Figure 26 Average latency of f-Cube4 under localized fault sets                | 63 |

| Figure 27 Throughput of f-Cube4 under localized fault sets                     | 63 |

| <b>Figure 28</b> Overlapping f-rings sharing <i>y</i> -axis and <i>x</i> -axis | 65 |

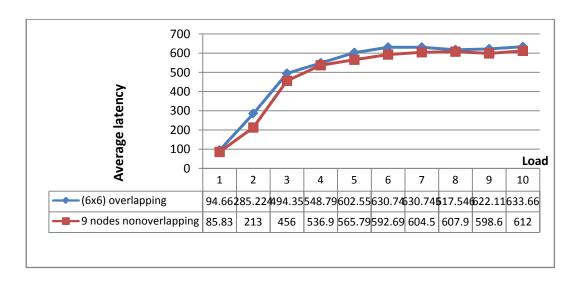

| Figure 29 Average latency of SB algorithm under random fault                   | 68 |

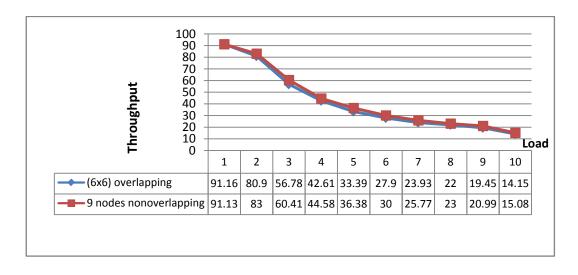

| Figure 30 Throughput of SB algorithm under random faults                       | 69 |

| Figure 31 Average latency of SB algorithm under localized faults               | 70 |

| Figure 32 Throughput of SB algorithm under localized faults                    | 70 |

| Figure 33 Average latency of SB with 4 VCs under random faults                 | 71 |

| Figure 34 Throughput of SB with 4 VCs under random faults                      | 72 |

| Figure 35 Average latency of SB with 4 VCs under local faults                  | 72 |

| Figure 36 Throughput of SB with 4 VCs under local faults                       | 73 |

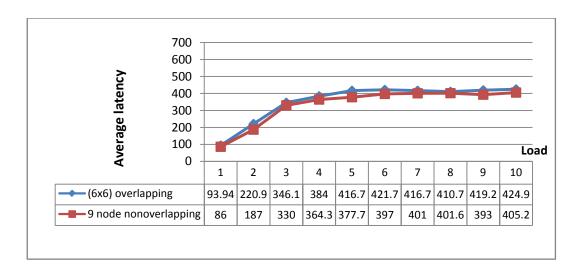

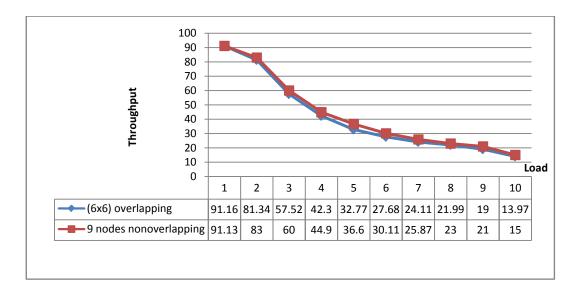

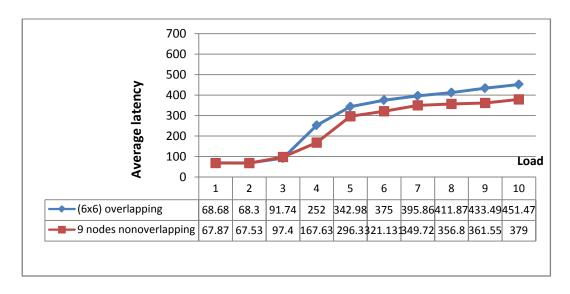

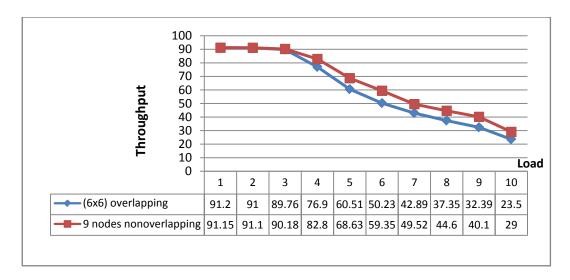

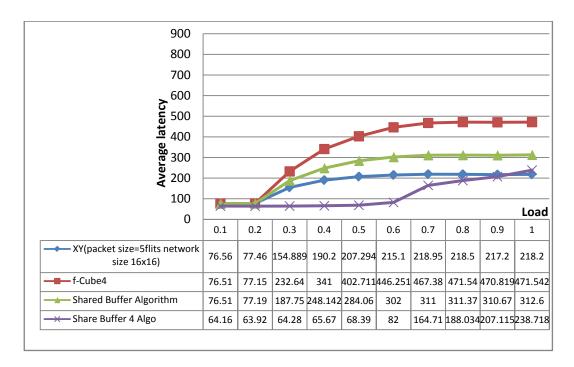

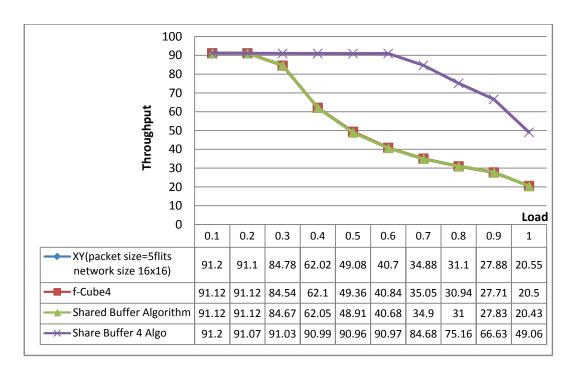

| Figure 37 Average latency of algorithms under fault free conditions            | 74 |

| Figure 38 Throughput of algorithms under fault free conditions                 | 75 |

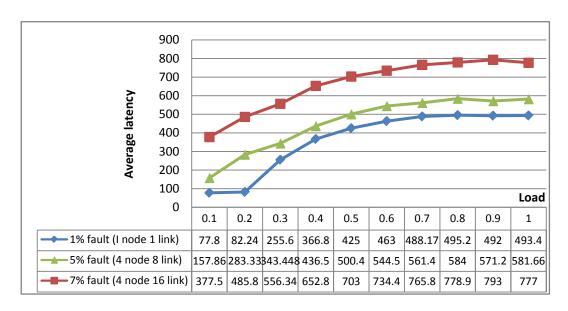

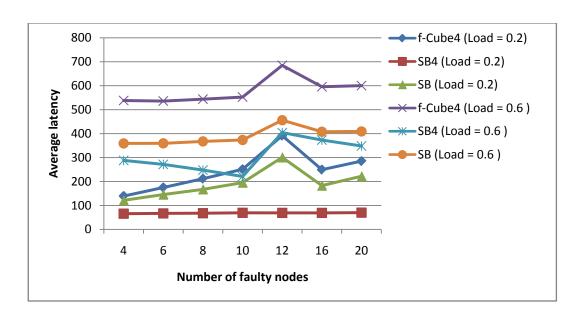

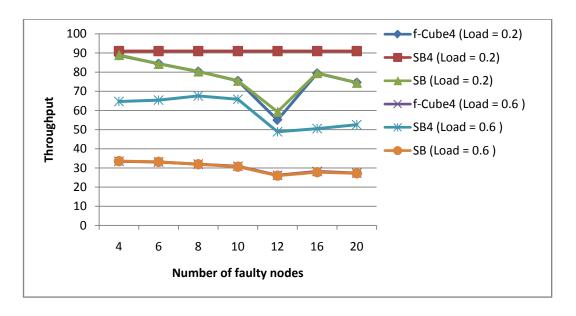

| Figure 39 Average latency as a function of node failures                       | 76 |

| <b>Figure 40</b> Throughput as a function of node failures                     | 76 |

## LIST OF TABLES

| TABLES                                          |    |

|-------------------------------------------------|----|

| Table 1 Comparison of fault-tolerant algorithms | 79 |

#### LIST OF ABBREVIATIONS

**2D** Two Dimensional

**BFT** Butterfly Fat Tree

**CLICHÉ** Chip-Level Integration of Communicating

Heterogeneous Elements

**DIM** Dimension

**DOR** Dimension Ordered Routing

**DSP** Digital Signal Processor

**EW** East-West

**f-chain** Faulty chain

**FPGA** Field-Programmable Gate Array

**f-ring** Faulty ring

IC Input Controller

IP Intellectual Property

**LAN** Local Area Network

MIN Multistage Interconnection Networks

**MTBF** Mean Time Between Failures

**MTTR** Mean Time To Repair

**NAM** Network AniMator

**NoC** Network on Chip

NS North-South

OTcl Object Tool command line

**PE** Processing Element

**ROMM** Randomized, Oblivious, Multi-Phase, Minimal

**SAF** Store-and-Forward

SB Shared Buffer

SN South-North

**SoC** System on Chip

**SPIN** Scalable Programmable Integrated Network

TCP Transmission Control Protocol

**UDP** User Datagram Protocol

VC Virtual Channel

**VCID** Virtual Channel Identifier

VCT Virtual Cut-Through

WAN Wide Area Network

WE West-East

#### **CHAPTER 1**

#### INTRODUCTION

The rapid advance in semiconductor technology has opened new advantages which allow placing many resources into single chip. This approach is known as Systems on Chip (SoC). It is predicted [1] [2] that further improvements in silicon technology will allow tens or even hundreds of processing elements (PEs) to fit into single chip. A PE can be a processor core, a DSP core, an FPGA block, memory block etc. However, as the number of PEs in SoC increases, complexity of interconnection architecture of the SoC also increases [3]. The up to now solutions that are used as communication infrastructures (point-to-point, shared-medium architectures) considered to be not enough for data exchange among PEs because of growing system size and non-scalable wire delay [4]. Although point-to-point communication maximizes chip performance, its design complexity takes high development cost [3]. Widely used shared communication architectures have limited scalability and poor performance when the number of PEs becomes more than ten. Besides, general buses have high energy consumption because of its broadcast data transfer nature. This means that data need great energy in order to reach each possible receiver [5].

Because of limitations introduced by communication infrastructure, the on chip design methodology became communication-centric rather than computation-centric [6]. This led to a new design methodology called Network on Chip (NoC). NoC efficiently decouples communication infrastructure from computation. Decoupling gives more structured architecture and modularity. The performance

increases due to increase in bandwidth and support of concurrent communication [4].

Models and techniques used in NoC are generally borrowed from computer networks and parallel processing. Scalability of computer networks and its steady success over many years motivate researchers to adopt switch-based (router) networks and packet-based communication. NoC provides PEs with communication infrastructure, where PEs are connected to the network via intelligent switches (routers). The communication is done by message-passing between PEs. The message may take multiple hops through intermediate routers in order to reach its destination. Thus, PEs are independent from each other and do not require global arbiter to access the network enabling highly utilized of network bandwidth.

NoC is much like interconnection networks for high performance parallel computers in which each processor is an individual chip [3]. However, NoC have a number of characteristics that make their design quit different than the inter-chip (inter-board) networks. Firstly, wires are more abundant [7]. Second, they have energy and area constraints. This limits the buffer usage since they significantly impact the area overhead.

The design of NoC requires the consideration over network topology, switching technique and routing algorithm to be used [8].

The right topology selection is important since it defines the ability of the network to efficiently disseminate information. Its importance extends when considering the network latency, throughput, area, fault-tolerance, power consumption, and designing the routing strategy and mapping cores to the network nodes. It is desirable to have rich set of predefined topologies that can be reused. This significantly reduces the time required for system design [9] [10].

While the topology defines only the static aspects of network-based communication, routing algorithms and switching technique governs the actual movement of messages along the network. Routing algorithm greatly influences the network performance and power consumption, since more complicated

algorithms require larger design. The switching technique defines when the routing decision is made and how the packets are transferred between switches. It introduces trade-offs between area overhead that results from larger buffer sizes and performance [11].

Along with the described requirements, it is important to keep communication-centric design environment fault-tolerant and reliable. It must at least guarantee that the particular fault will not cause the entire chip to fail. The solutions for fault-tolerant can be adopted from multiprocessor architectures. However, they should be evaluated in terms of throughput, latency, area overhead, and energy dissipation [4].

Our research is motivated mainly by the possible prospects of NoC, since it is considered to be a solution for communication bottleneck. NoC is still in its infancy. Despite lots of researches conducted in this area, few problems have been faced and still more left for the future. We mainly focus on fault-tolerance, since even less researches were conducted on this area. It is not of less importance to keep system working under various fault patterns. Possibly with degraded performance. Fault-tolerance requires redundancy in terms of buffers. Since faulty components introduce additional dependencies between channels while routing messages around faulty regions, the number of required virtual channels increases. However, NoC constraints the area used by buffers. Thus, it is desirable to have fault-tolerant algorithms with less buffer requirements. This situation again leads to trade-offs between area and performance.

Our main concern is to decrease the number of used virtual channels while tolerating faults. Since NoC restricts buffer size it is important to be able to take advantage of buffers that are in hand rather than using additional buffers. This requires dynamic allocation of these buffers that are idle. Besides, we make some changes to router organization, i.e. to the location of buffers.

Chapter 2 gives an idea about the main aspects of NoC. Proposed traffic models are also described briefly in this chapter.

Chapter 3 describes the general-purpose simulator, ns-2, and our router model. The various simulation results on parameterizable aspects of NoC are given and analyzed.

Chapter 4 deals with our fault-tolerant algorithm and compares the simulation results with fCube4 algorithm.

Conclusion and future work is presented in Chapter 5.

#### **CHAPTER 2**

#### **BACKGROUND**

NoC consists of routers, buffers and links. While considering the design of a system it is important to choose the right topology, so that the applications match onto topology in such a manner that the performance will be the best. Since buffer usage is limited the right switching technique that requires the limited buffers size must be chosen. It depends on application if the messages are sent packet by packet or divided into smaller units called *flits*. The right buffer utilization has big impact on the system performance. The complexity of a router is determined by the routing algorithm. Although deterministic algorithms are simple and fast, they do not have the flexibility of adaptive algorithms.

This chapter describes the proposed topologies, switching techniques and routing algorithms. The differences between them and their comparisons are presented. We also give a general view of faults and how the literature proposes to handle them.

#### 2.1 Network Topology

The topology of a network is a graph that defines how the nodes are interconnected by channels. In general, NoC adopts the interconnection architecture of high performance parallel computing, where Intellectual Property (IP) blocks are connected to the network via routers, thus providing a communication between functional IP blocks. However, SoC design paradigm introduces some constraints, as compared to high performance parallel computing. Along with the desirable characteristics, such as high throughput and low latency, SoC also considers energy consumption and the area overhead of proposed interconnection architecture. It is also desirable for interconnection architecture to be scalable, making the design of SoC even more difficult since the latency of a message should still be kept low as the number of IP blocks increase [12]. Since, the system performance is highly dependent on communication, the right topology selection is important.

[13] argues that the topology should be application specific since the system will consist of heterogeneous nodes. However, predefined, regular topologies are generally suggested [14] [1] [15], since they reduce the system design time.

Below we present some of the proposed architectures. Here, functional IP blocks are shown as white squares and the routers are shown as black squares.

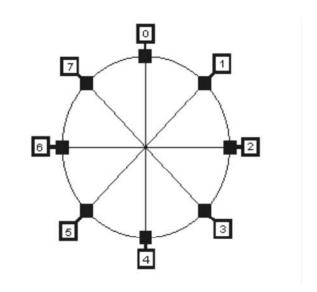

#### 2.1.1 Octagon

The octagon architecture was proposed by Karim et al. [16] for network processor SoCs. It is a special case of more general class of networks called Spidergon [17]. In this architecture each node is associated with a processing element (PE or otherwise IP) and a switch. The basic octagon consists of eight nodes and 12 bidirectional links (Fig.1), and the communication between any two nodes takes at most two hops within it. As the number of nodes increase the octagon is extended to a multidimensional space.

Unlike the traditional shared buses and crossabars [18] the octagon architecture has much higher throughput, is easy in implementation, and has less wiring complexity. It implements simple shortest path algorithm. However, as the number of nodes increase the implementation complexity also increases. It also requires an implementation of network arbiter and a good scheduler, since nodes share the single communication point at the center of an octagon.

Figure 1 Octagon [22]

#### **2.1.2 CLICHÉ**

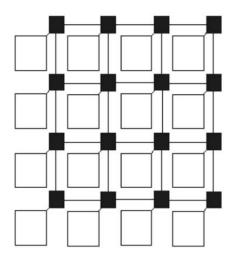

The CLICHÉ (Chip-Level Integration of Communicating Heterogeneous Elements) was proposed by Kumar et al. [14]. It is a simple 2D-mesh [18], where each IP is connected to a switch and each switch, except the edge switches, is connected to four other switches (Fig. 2). Here, the IP to switch and switch to switch interconnection is done via bidirectional links.

Figure 2 CLICHÉ [22]

CLICHÉ was proposed as a basic topology for NoC, since it is simple from layout perspective and scalable. It allows addition of resources, thus increasing the network, without reintroducing any changes in communication protocols, while increasing the network bandwidth.

#### 2.1.3 2D Torus

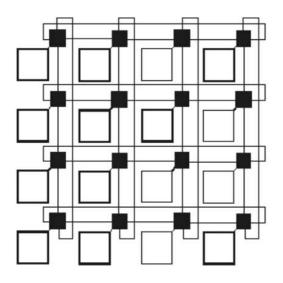

Dally and Towels [7] proposed 2D torus, which is also mesh-based architecture. The only difference from 2D mesh is that the edge switches are connected via wraparound channels. Thus, every switch is connected to an IP block and four neighboring switches (Fig. 3). The number of switches is the same as for CLICHÉ and equal to the number of IP blocks.

Figure 3 2D Torus [22]

The wraparound channels are very long and still increases with the number of IP blocks, thus the link delay increases. Long channels require repeaters to be placed within a link, so that the packet propagation fits within one clock cycle. As a solution, folded torus was proposed [19]. In a folded torus the wraparound channels are divided into approximately fixed length by shifting the position of nodes (Fig. 4). Hence, the channel length between any switches is now equal and considerably shorter.

Figure 4 Folded Torus [22]

#### 2.1.4 Tree Architectures

The tree-based architectures are derived from multistage interconnection networks (MIN) [18], where IP blocks communicate with each other by sending a message through a number of switch stages. Hence, IP block can communicate simultaneously without contention.

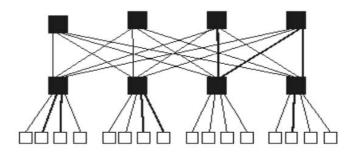

Guerrier and Greiner [20] proposed a SPIN (Scalable, Programmable, Integrated Network), which has a fat-tree architecture. In this architecture, every node has four children and the parent is replicated four times in every level (Fig. 5). The IP blocks are placed at the leaves of the tree and switches are at the vertices.

Figure 5 SPIN [22]

The size of a network grows as (NlogN)/8, where N is the number of IP blocks. Since, the SPIN architecture provides multi-path between any pair of IP blocks the wiring complexity increases with the number of IPs.

Another tree-based architecture, BFT (Butterfly Fat-Tree), was proposed by Pande et al. [21]. Here, again IP blocks are at the leaves and switches are at the vertices (Fig. 6). Each node is labeled by a pair of coordinates, (l, p), where l indicates a node's level and p indicates its position in that level. As the IP blocks reside at the lowest level of tree, their addresses are indicated as (0, N), where N ranges from 0 to (N-1). Each switch has four child ports and two parent ports, and IPs are connected to N/4 switches at the first level. At the j<sup>th</sup> level of a tree the number of

switches is  $N/2^{j+1}$ , and the total number of switches approaches to N/2 as N increases. Thus, there is one switch for every two IP blocks.

Figure 6 BFT [22]

#### 2.1.5 Comparison of Network Topologies

Pande et al. [22] compared all these proposed interconnect architectures relative to throughput, latency, energy and area overhead. Under uniform traffic SPIN and Octagon show good performance in terms of throughput and latency. This is due to the fact that both of them have more links between two pairs of nodes than do the others. However, it was show that SPIN and Octagon have higher energy dissipation because of the higher degree of connectivity they provide.

When considering area overhead the Folded Torus and CLICHÉ are favored because of their simplicity. The inter-switch wires are of equal sizes and fit within one clock cycle in both of them. When the wires do not have equal sizes these with longer length require repeaters in order to be able to work at the same speed with others or force others to become longer. In BFT and SPIN wire length between switches depends on the levels of the switches. In Octagon, the inter-switch wires connecting IPs from disjoin Octagon units also require repeaters.

#### 2.2 Switching Techniques

The network performance is highly dependent on a switching technique that is being used. Switching techniques determine when and how internal switches are set to connect router inputs to router outputs [18]. It does not decide which channel should be used by a message, but performs the actual mechanism that removes data from an input channel and puts it on the output channel. Various kind of switching techniques were proposed. These techniques are coupled with *flow control* mechanism in order to move messages through the network [23]. Since the network consists of channels and buffers, the flow control mechanism deals with the allocation of channels and buffers. The ideal flow control mechanism reduces the channel and buffer congestion while decreasing message latency.

#### 2.2.1 Circuit Switching

In a circuit switching the path from source to destination is reserved before the message is injected into the network. The reservation is done by a routing probe that is send along the network. Routing probe contains the destination address and some control information. It progresses toward the destination reserving physical links. Thus, when routing probe reaches the destination the complete path is set up. The acknowledgment is sent to the source and a message is injected into the network. Since, the path is already set the message is transmitted at the full bandwidth of a path and does not required to be stored at an intermediate routers. The path is released either by destination node or by a few last bits of a message itself.

However, this technique is very conservative. Since physical path is reserved for the entire duration of a message and blocks other message. If a routing probe is blocked itself the physical path that was reserved by it up to now cannot be used by other messages, thus channels remain idle. This leads to a channel underutilization. The circuit switching is advantageous when the message size is long compared to a set up time and infrequent.

#### 2.2.2 Packet Switching

The packet switching technique was borrowed from computer networks [12]. In this technique the message is divided into fixed-length packets and every packet is sent to the network individually. First few bytes of a packet are allocated for packet header which contains routing information. This technique is also called store-and-forward (SAF) switching technique, since the packet should be entirely stored at an intermediate router before being forwarded to the next router.

In a networks that use packet switching the message latency is directly proportional to the distance between source and destination, and can be represented as (L/B)\*D, where L is a message length, B is a channel bandwidth and D is a distance between source and destination. Every packet is independent of each other and needs to be routed at every intermediate router. Besides, packets can arrive out of order to the destination, thus producing additional overhead.

The packet switching is advantageous when the messages are short and frequent. In compare to circuit switching the resources are fully utilized and packets may be injected into the network simultaneously. However, if the packet size becomes large routers should provide buffers in order to be able store the entire packet.

#### 2.2.3 Virtual Cut-Through

The packet switching requires entire packet to be stored in a router before routing decision is made. Since the packet size is usually bigger than the link bandwidth, it takes several cycles to transfer entire packet through the link. However, the header of a packet is available after a few cycles. Virtual cut-through (VCT) switching technique was introduced in order to decrease the message latency. The routing is

done as soon as the packet header arrives and if the next router has available buffer, cut-through to the input of a next router before the entire packet arrives. The message is send after the header in a pipelined manner. When there is no congestion in the network, the latency of a header is the routing latency, and the propagation delay through the router and physical channel. However, if a header blocks then the entire packet is stored at a router. Thus, each router still will have to be able to store the entire packet. At high network loads VCT acts like SAF switching technique. The latency is defined as  $(L_h/B)*D+L/B$ , where  $L_h$  is the length of a header. When,  $L_h << L$  the distance, D, will not have big effect on a latency.

#### 2.2.4 Wormhole Switching

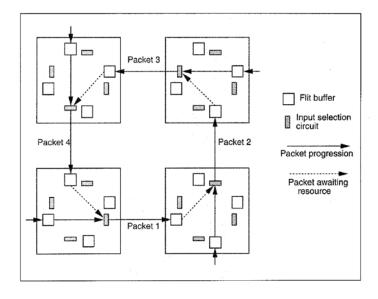

In a SoC environment the routers should consume small silicon area compared to IP blocks [22]. However, SAF and VCT switching techniques require the large buffers in order to be able to store entire packet, making it difficult in construction of small, fast and compact routers. As a solution wormhole switching technique was proposed [24]. The message is divided into small units called flits. The size of a flit depends on system parameters and generally is equal to *phit*, where phit is a unit of information that can be transferred across the channel in a single cycle. The message contains three types of flit: header, data and tail. The header flit contains the routing information and reserves resources toward the destination. Data flits and tail flit does not contain routing information and simply follow the header flit in a pipelined manner. Resources are released by tail flit, which indicates the end of a message. In compare to VCT where the blocked packet is stored in one router completely removing a message from network channels, wormhole technique blocks flits in place. Thus, the blocked message occupies buffers in several routers. This enables routers to have smaller buffer size, one or two flits.

Since the data flits do not contain routing information and simply use these resources that are reserved by header flit, different messages cannot interleave. Thus, if a buffer or channel was allocated for one message it is held for the entire

message duration. The latency of a message is defined as  $((L_f/B)*D+L/B)$ , where  $L_f$  is a length of a flit. When  $L_f << L$  the distance between the source and destination, D, does not have much impact on a latency, unless D is very large. [12] indicates that in the absence of contention a message that is wormhole routed is shown to be nearly independent of the distance between source and destination.

#### 2.2.5 Virtual Flow Control

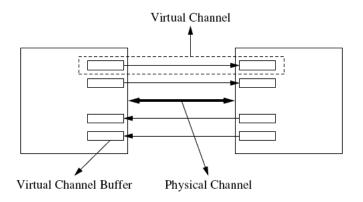

There are two resource types in a network: buffers and channels. Usually, one channel is related to one buffer. If a packet A has allocated a buffer  $b_i$ , the associated channel  $c_i$  remains idle until A releases  $b_i$ . In networks that use flit-level flow control, where channels are reserved for the duration of a packet, if a packet is blocked then all the channels held by this packet remain idle. This situation leads to an inefficient use of physical channels and may lead to deadlocks (see Section 2.3) as well. In order to cope with this problem virtual channels (VC) [25] are adopted.

A virtual channel consists of a private buffer that can hold one or more flits [25]. Several virtual channels may share the bandwidth of a single physical channel. This property provides each channel in the network with multiple buffers. If a blocked packet holds one buffer associated with channel  $c_i$ , another buffer is available allowing other packets to pass.

Figure 7 Virtual channels

Figure 7 illustrates two unidirectional virtual channels in each direction. This can be seen as if virtual channels are using two distinct physical channels at half the speed.

Virtual channel assignment is made at the packet level, meaning that, if a packet is assigned to a particular virtual channel than this assignment is fixed for the duration of the packet. It assures that different packets will not interleave, as data flits does not contain routing information. However, physical channel is allocated at the flit level.

Virtual channels were initially introduced for deadlock avoidance in [19]. However, lately they are suggested to be used also for performance improvement purposes.

Adding virtual channels increase network throughput, since physical channel utilization increases. However, virtual channel usage is limited. With every new VC the probability of a message being granted physical channel decreases, thus increasing message latency. Large number of VCs also has a big impact on router performance. Routers become complex, arbitrating between VCs and multiplexing them over one physical channel, thus increasing the hardware cycle time.

#### 2.2.6 Comparison of Switching Techniques

There is no unique solution to all problems. Although wormhole switching is the most popular switching technique and significantly improves network performance, individual messages may block other messages, and lead to resource underutilization. SAF and VCT switching techniques consume network bandwidth proportional to network load and fully utilizes the network bandwidth. However, they require large buffer sizes to store packets. Circuit switching is very conservative and allocates the entire physical path, thus blocking other messages.

Wormhole technique can be improved by adding virtual channels. But the latency of individual messages may vary, because of contention for small buffers, in compare to SAF, which has predictable latency characteristics. At low loads wormhole routing performs better, but at high loads SAF is much better. VCT achieves the performance of wormhole switching at low loads and of SAF at high loads.

The SAF allows error detection and retransmission at link-by-link basis. It if flexible and easily avoids faulty components. Pipelining reduces buffer size, but introduces unique challenges in deadlock and fault avoidance, since the message is pipelined over several routers and form dependence between these buffers.

#### 2.3 Routing Algorithms

The routing algorithm determines the path that must be taken by a message in order to reach its destination. Various kinds of algorithms were introduced in the literature. These are differentiated according to the place where the decision is taken about the path that should be traversed by a message and the routing flexibility to different network conditions. The decision of an entire path can be done by source node prior to message injection. This is called source routing. In this case, the packet carries the whole routing information, thus increasing the

packet size. Furthermore, the path is fixed and cannot be changed after the packet injection into the network. Alternatively, the path can be determined at every intermediate router using distributed routing. In this case, the decision is distributed through the network. Every router, upon receiving the packet, decides whether to deliver it to the local node or forward it to the neighboring node. The decision of a right neighboring node, where the packet should be delivered, is also implemented in an intermediate router. The routing algorithm can be implemented in adaptive way so that the path traversed by a message is dependent on the network traffic, or can be oblivious. In latter case, the path by a message is independent of network traffic.

Routing algorithm also has a big impact on network performance. The routing decision must be fast thus decreasing the message latency and be easily implemented in hardware. Complex routing algorithms increase the routing complexity and may require additional hardware. Besides, as it was indicated before, routers must be small and compact. That is the reason why the knowledge of network's global state information is not favored, since it requires additional storage space in each router. Among these requirements, routing algorithms should also be able to preserve deadlock, livelock and starvation freedom.

#### 2.3.1 Deadlock, Livelock and Starvation

Unrestricted routing algorithms may lead to situations where a message can never reach its destination. These are caused by deadlock, starvation or livelock.

Livelock happens when a packet wonders across the network never reaching its destination. It happens when the resources requested by a packet are occupied by other packets. Adaptive algorithms are usually livelock-prone, since they allow messages to go away from their destinations. Hot potato [] is one example for livelock-prone algorithms. In this algorithm, if a channel required by a packet is busy, it is send through any other available channel, although that channel moves a message to the different path. Thus, livelock enforces some restrictions to routing

algorithm. This may be achieved by several techniques, such as minimal path, restricted non-minimal path, probabilistic avoidance [18].

The packet may also block permanently because resources requested are never granted to it and lead to starvation. The avoidance of starvation requires correct resource assignment scheme.

The most difficult problem in routing algorithm implementation is to preserve deadlock freedom. It is a situation when several packets are blocked permanently in the network. Deadlock occurs when the packets are allowed to allocate resources while holding others [12]. In VCT and SAF resources are buffers and in a wormhole and circuit switching resources are channels. The most deadlock-prone network is a network that uses wormhole switching technique since the packet holds several router buffers simultaneously.

**Figure 8** An example of deadlock [12]

Figure 8 represents a deadlocked situation where four routers and four packets are blocked. Here, packets are requesting for a channel while holding a channel requested by other message.

The most common technique is deadlock avoidance that is implemented by routing algorithm. Channels are granted in strictly monotonic order so that the packet is granted a resource only if the resulting global state is safe. The channel dependency graph [18] is used in implementation of deadlock-free routing algorithm. In this graph the vertices are unidirectional channels and the edges are connected channels. Two unidirectional channels are connected if the routing algorithm allows the usage of second channel (output) after the first (input). If all these connections form a cycle then the algorithm is deadlock-prone. Hence, some restriction should be embedded into the routing algorithm. Generally, it is done by disallowing some turns in a packet's path.

#### 2.3.2 Oblivious Routing Algorithms

An oblivious routing does not consider the network state. The path taken by messages is only dependent on the source and destination of the messages. It may contain routing table that includes several options for an output channel based on the destination address. This may give some level of adaptivity, however the routing algorithm is independent of network state. They are used for general-purpose routing as they are easy to implement and considerably perform well. Oblivious algorithms can be deterministic or randomized according to the variations of options of output channels supplied at any intermediate router.

#### 2.3.2.1 Deterministic Routing Algorithms

Deterministic algorithms always supply the message from particular source to particular destination with the same path. This means that every intermediate router always grants the same output channel for the same destination.

The deterministic routing became popular with the wormhole switching technique. As wormhole switching technique is heavily pipelined, it is extremely important that all the stages work at the same speed in order for it to be efficient. This requires the routing algorithm to be implemented in hardware. Deterministic algorithm is usually preferable due to its simplicity [18].

The most popular deterministic routing algorithm is Dimension Ordered Routing (DOR), which is also known as XY (YX) routing when used in 2D-meshes and ecube routing when used in hypercube. The DOR algorithm routes packets first in one dimension. When it arrives to the proper coordinate of the other dimension, proceeds in that dimension.

In XY-routing the message first travels on x-dimension. When the offset of x-dimension becomes zero, i.e. the message reaches the router that is on the same x coordinate with destination, it starts moving on y-dimension. Messages always are routed along the minimal path.

DOR algorithm is deadlock-free when used in 2D-mesh and does not require additional virtual channels. It preserves its deadlock freedom by allocating channels in strictly monotonic order. This restricts some kind of turns that could lead to deadlock.

#### 2.3.2.2 Randomized Routing Algorithms

DOR algorithm is simple and fast, however when the system is heavily loaded it may act poorly. Because of its poor worst case behavior, a few algorithms using randomization were proposed. Randomization helps using the network bandwidth efficiently when the minimality constraints for routing algorithm are relaxed to some extend.

The oblivious algorithm, named Valiant, was introduced by Valiant and Brebner [27] and it is the best known randomized algorithm. This algorithm works in two phases. In both first and second phases, it uses dimension-order routing, at first phase - to route a packet from its source to randomly selected node, at the second phase it routes the packet from that random node to its destination. As Valiant is non-minimal, it tries to avoid congestion in the network. Packets with the same source and destination have different intermediate nodes, which are selected

randomly, thus they cannot take the same path. In order to avoid deadlocks buffers are needed, and as in a mesh topology, it requires two sets of independent buffers per communication link, so, this algorithm requires the buffers of O(n) depth in each node and does not preserve data locality. If livelocks are considered, the packet in the algorithm reaches its destination, even it may take longer path than actually required and so, in Valiant routing algorithm livelock cannot occur. The negative aspect of this algorithm is the path taken, because it increases depending on the topology being used. For example, in a mesh, the packet path may be doubled, resulting in longer routing times of Valiant routing, and so, doubling the demand on network bandwidth.

Randomized, Oblivious, Multi-phase, Minimal (ROMM) [28] algorithm is another routing algorithm which uses randomization. From dimension-order routing algorithm it inherits properties of minimality, which is to preserve data locality and to assure that the path taken by a packet will be minimal, and from Valiant – randomization, which is to assure that packets with same source and destination will not take the same path. These properties are combined to avoid congestion. Since the algorithm is oblivious, it is easy to implement it, in contrast to adaptive algorithms, which are more complex. As ROMM algorithms use the minimal path, it is constrained in randomization compared to Valiant that uses full randomization.

ROMM algorithms select random nodes within the range of a minimal path which a message is required to follow in order to reach the destination. A packet is routed in p-phases. In p-phase ROMM algorithm there are p-l randomly selected nodes  $Z_1, Z_2, ..., Z_{p-l}$  between source and destination, and all  $Z_i$  's (i=1,...,p-1) must be on minimal path from source to destination.

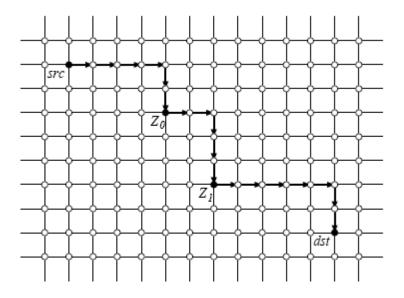

**Figure 9** A possible path from source to destination using 3-phase ROMM on a 2-dimensional mesh.

Fig.9 shows a possible path from source to destination in a 3-phase ROMM. In this example source node establishes the path taken by message by means of dimension-order routing and chooses a random node that lies within that path, which is  $Z_0$  in our case. Next, message is routed from src to  $Z_0$  using dimension-order routing. In the same way, a new source node, which is now  $Z_0$ , sends a message using dimension-order routing having chosen another random node that lies along the minimal path from  $Z_0$  to dist, in this case  $Z_1$ .  $Z_1$  in its turn routes a message to dist again using dimension-order routing.

In order to avoid deadlock in *p*-phases ROMM algorithms *p*-virtual channels for wormhole routed mesh network is needed. Also, due to wrap-around links, it requires 2*p* virtual channels for wormhole routed torus network. As *p* increases the algorithm becomes very costly, since it increases memory usage adding virtual channels and complicates routing with additional logics required to manage virtual channels.

## 2.3.3 Adaptive Routing Algorithms

Another option in implementing a routing algorithm is to consider the network state. Every intermediate router supplies a message with several output channels based on the current node or buffer and the destination node. One of these output channels are then selected according to its status at the current node. Thus, a path of a message from source to destination is adaptive, allowing avoid busy channels. Adaptivity makes the routing more flexible however the hardware becomes more slow and complex.

Adaptive algorithm can be minimal or non-minimal. Minimal algorithms supply a message with a set of channels that always bring it closer to destination. Non-minimal algorithms may misroute a message by sending it away from its destination. It relies on the optimistic assumption that misrouting can bring a message to another set of minimal channels.

The further classification of adaptive algorithms is: fully adaptive and partially adaptive. The fully adaptive algorithms can use all the physical paths in its class, while partially adaptive algorithms can use only subset of them.

#### 2.3.3.1 Planar-Adaptive Routing

The aim of planar adaptive routing algorithms, proposed by Chien and Kim [29] for *n*-dimensional meshes and hyper cubes, is to provide adaptivity in only two dimensions at a time and is considered to be minimal. While being adaptive they limit the routing direction in a series of 2-D planes, and as the packet moves toward its destination the routing dimensions change so that the packet is routed in all dimensions in its way to destination. By this the network cost is reduced while deadlock-freedom is maintained.

In order to avoid deadlocks, in a *k*-ary *n*-cube with no loop paths, planar-adaptive routing requires three virtual channels for each physical channel in meshes.

Let  $A_0$  to  $A_{n-2}$  denote n-1 adaptive planes, each of them defined as the combination of several sets of virtual channels.

$$A_i = d_{i,2} + d_{i+1,0} + d_{i+1,1} \tag{1}$$

Each adaptive plane involves only two dimensions. To support the n-1 adaptive planes three virtual channels in each dimension are needed.

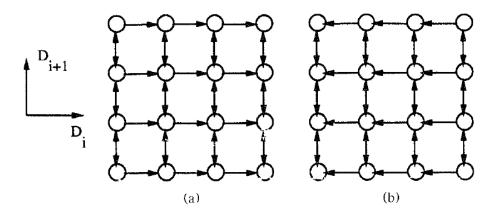

Figure 10 The channels for an adaptive plane  $A_i$ . The increasing (a) and decreasing (b) networks are logically decoupled as they contain disjoint sets of virtual channels [29]

The algorithm conditionally can be divided into high level (between adaptive planes) and low-level (within adaptive plane  $A_i$ ). In high-level each routing in adaptive plane  $A_i$  reduces the distance in  $d_i$  to zero. The packet reaches its destination when it is routed in all of the adaptive planes. Since for VC  $d_{n-1}$ , there is no adaptivity left for a minimal router, the packet is routed directly to its destination. In low-level routing, within each adaptive plane multiple paths can be chosen and the packet completes its routing in at least one dimension. If in plane  $A_i$ , the  $d_{i+1}$  the offset is reduced to zero first, routing continues in  $d_i$  until the  $d_i$  distance is reduced to zero.

The overlapping adaptive planes require only three virtual channels per physical channel for an n-dimensional network. VCs  $d_{i,2}$ ,  $d_{i+1,0}$  and  $d_{i+1,1}$  belong to adaptive plane  $A_i$  and inside the plane, a packet is routed adaptively with respect to dimensions  $d_i$  and  $d_{i+1}$  by choosing the channels which directs close to the destination. In order to prevent deadlock, the traffic is divided into increasing and decreasing virtual networks which are completely disjoint: increasing network is

formed by VCs  $d_{i,2}$  + and  $d_{i+1,0}$  with packets which need to increase their  $d_i$  address while decreasing network formed by VCs  $d_{i,2}$ -,  $d_{i+1,1}$ , where packets cross dimension  $d_i$  in negative direction.

If decompose the network into the adaptive planes, it can be seen that routing in each plane in deadlock-free, and that cycles cannot form between planes. Consequently, the planar-adaptive routing algorithm is free from deadlocks.

#### 2.3.3.2 Dimension-Reversal

In non-minimal adaptive routing packets can temporarily move away from their destination, but eventually achieve their destination. Due to misrouting, the distance a packet travels may not be minimal. This technique is fully adaptive and requires two VCs per physical channel. Two non-minimal routing algorithms for mesh networks were proposed by Dally et al. [30]. In the first of them, named static dimension reversal routing algorithm, every two adjacent nodes are connected by r pairs of channels. Thus, the network is divided into r sub-networks and all the i<sup>th</sup> pair channels are contained in the i<sup>th</sup> sub-network. Each packet header stores additional value c, the numbers to break the dependency cycle, which is initially set to zero. The packet with c < r-1 can move in any direction in its own sub-network, except when the packet moves from high dimensional channel to low dimensional channel the value of c is increased by one. If c reaches the value c-1 then the packet must switch into the deterministic dimension-ordered routing algorithm. The packets can be also misrouted, but the parameter c restricts the number of times it can happen.

The second algorithm is called dynamic dimension reversal routing algorithm. In this algorithm the channels are divided into two classes: adaptive and deterministic. At first, packets are sent through adaptive channels and can move in any direction. However, when a packet reaches a node, it must switch to the deterministic channels as at node all output channels are busy by packets with values of c smaller or equal to its own. Once a packet enters the deterministic channels, it cannot return to adaptive channels. The algorithm is deadlock-free.

#### 2.3.3.3 Turn Model

Turn model, proposed by Glass and Ni [31], is partially adaptive algorithm, both minimal and nonminimal. It is based on the idea that deadlocks occur because the packet routes contain turns that form cycles. Deadlock cannot occur if there is no cyclic dependency between channels [18]. The turn in the packet route occurs when it is routed from one dimension to another. If packet changes its direction without moving to another dimension it is considered to have 180-degree turn. When physical channel is split into several virtual channels, moving from one virtual channel to another in the same dimension and direction is considered as 0-degree turn. Different turns when combined form cycles. The main concept of the proposed algorithm is to prohibit smallest number of turns so that the cycles are prevented. In order to develop a maximally adaptive routing algorithm in *n*-dimensional meshes and *k*-ary *n*-cubes following six steps are presented:

- 1- Classify channels according to the directions in which they route packets.

- 2- Identify the turns that occur between one direction and another.

- 3- Identify simple turns that may occur.

- 4- Prohibit one turn in each cycle.

- 5- Incorporate as many turns as possible that involve wraparound channels, without reintroducing cycles (in the case of *k*-ary *n*-cubes).

- 6- Add 0-degree and 180-degree turns without reintroducing cycles. 180-degree turns are needed when there are multiple channels in the same direction and for nonminimal routing.

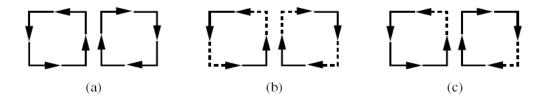

The Figure 11(a) shows eight possible turns and two possible abstract cycles that may occur in 2-D mesh.

**Figure 11** (a) 8 possible turns, (b) 4 turns allowed by XY-routing, (c) 2 prohibited turns in West-First routing [18]

XY- routing allows only four turns as shown in Figure 11(b), thus the deadlock cannot occur. Figure 11(c) presents turns that are prohibited in the algorithm presented by [31]. It is West-First routing, where two turns to the west are prohibited, thus in order to travel west packet must begin in that direction and then adaptively south, east and north.

Figure 12 West-First routing [18]

Figure 12 illustrates how this algorithm works. Here, unavailable channel is either blocked or faulty channel.

Also some other algorithms can be derived from turn model, such as north-last and negative-first routing. The north-last routing algorithm does not allow turns from north to east or from north to west. The negative-first routing algorithm does not allow turns from north to west or from east to south.

## 2.4 Fault Tolerant Routing

The design of NoC is not limited by performance improvement issues. The second dominant issue is fault tolerance, which is the ability of the network to function in the presence of faulty components. The implementation of fault tolerance into the system may degrade its performance considerably. Moreover, the faulty network may lead the communication into deadlock and livelock, thus making routing algorithms implemented for fault free network ineffective.

From first glance it might appear that the adaptive algorithms can tolerate faults and move messages along faulty components. However, even the single link failure can demolish the deadlock-freedom property of adaptive algorithm. If adaptive algorithm provides several channels to a message and all these channels are occupied by other messages that have encountered a fault and cannot make a progress, this message blocks even if its destination does not lie along the faulty component. This means that the deadlock might occur even though cyclic dependencies between resources do not exist [18]. Since, these messages that encounter faulty component cannot make a progress and are holding buffer and channel resources, the other messages that do not require to traverse the faulty component, but need these resources that are held by blocked messages are also blocked. This leads to a *wait chain* that might block the whole system [18].

The deadlock might also occur due to dynamic faults, where a message in progress is interrupted by fault. In this case, if data flits lose their header flit they cannot make a progress without routing information and hold resources indefinitely. The recovery mechanism should be able to resolve wait chains, clean the network from interrupted messages, and recover corrupted messages or notify the source node about loss so that a new copy of a message is sent.

#### 2.4.1 Fault Models

The fault tolerant algorithm is implemented according to faulty component patterns introduced, and the ability of a system to diagnose these faults. Diagnose can be conducted on different levels. Generally, only two classes of faults are diagnosed: either, the entire PE and its associated router fails (*node failure*), or any channel fails (*link failure*).

Faults may be *static* or *dynamic*, where static faults already exist when the system is powered on while dynamic faults occur on run time of a system. Both of them are considered as permanent faults and remain in the system until repaired. Permanent fault avoidance is much easier than transient fault avoidance. Transient faults cannot be reproduced and are not amenable to prediction.

The fault tolerance technique can be implemented in the system according to the fault occurrence rate. If the mean time between failures (MTBF) is much bigger than the mean time to repair (MTTR) then the system can utilize lower-cost fault tolerance approaches. However, if MTTR is much bigger than MTBF, as it can be seen in space-borne systems, then the fault tolerance approach should be more expensive so that the system will work, possibly with degraded performance, until the repair is conducted.

The fault model of a system should also define the behavior of a faulty nodes and the fault information that is available at a node. The faulty node should stop sending or receiving messages in order to avoid deadlock in a system. Faults are generally considered to be non-malicious, thus making fault tolerance much easier in implementation. The fault information available at a node may be global or local. In global fault information, every node knows the status of every other node, thus making the best decision in routing. However, this technique leads to synchronization problems in conducting global information updates, and increase storage requirements at a node. In local fault information, every node knows the status of only neighboring node. This technique may force messages to take longer path, but the network implementation becomes easier.

## 2.4.2 Fault-Tolerant Routing Using SAF and VCT Techniques

In SAF and VCT networks the deadlock is avoided by right buffer management, since packets form deadlock only when there are no available buffer at an adjacent router. Fault-tolerant routing assumes packet misrouting, so the main issue is to avoid livelock. Usually SAF and VCT techniques are used in high-dimensional networks because in these techniques message latency depends on distance [12].

Chien and Shin [32] introduced a fault-tolerant routing algorithm that is used in binary hypercube (k=2). In binary hypercube messages traverse only one link in each dimension, so if the destination address differs in m bits from source address the shortest path will take m dimensions. They presented a new concept called as spare dimension, which is the dimension that is not on the shortest path. When all the dimensions that lie on a shortest path are blocked the message is misrouted and sent to spare dimension. Since in n-dimensional binary hypercube there is n disjoint path between any pair of nodes, it is assumed that n-1 faults cannot disconnect the network. So, the algorithm can tolerate up to (n-1) faults. By this assumption where a network can have only n-1 faults, Chien and Shin [32] asserts that there is always one spare dimension that can be used by blocked messages.

Another approach in order to avoid faulty components in a network is to use randomization. Some routers use this technique to avoid deadlocks [33]. If a message holds an input buffer for a long time, it is removed from input buffer and stored in a local buffer in a node. They are re-injected into the network later when

the output buffers become available. As the local buffer size is also limited and implemented as a queue, when the queue becomes full and there is some message that should also be stored, the random message is selected and misrouted. Thus, every message has a nonzero probability to avoid misrouting.

## 2.4.3 Fault-Tolerant Routing Using Wormhole Switching Technique

In compare the networks that use VCT and SAF switching techniques, wormhole switching introduces some unique challenges. The wormhole switching is deadlock-prone and even in fault-free networks requires a deep consideration in routing algorithm implementation. This is because the message is divided into flits and the blocked message occupies several routers, thus blocking other messages that are also competing for the same virtual channel. It is suggested to implement good routing algorithm rather than recovery mechanism, since recovery is expensive in terms of time and resources [18]. The general solution is to route messages around faulty regions as with VCT and SAF without introducing cyclic dependency between channels. The fault-tolerant routing algorithm is determined by the shape of a fault region and the base routing algorithm upon which it was implemented. Fault-tolerance requires additional virtual channels and the routing restrictions among their usage.

#### 2.4.3.1 Fault Regions

The concept of *regions* was firstly defined by S.Kumar et al. [14], where the region *G* is defined as an area inside the NoC, that is insulated from the network and may have different internal topology and communication mechanism. A region may be some resource that is of larger size than the atomic slots in the mesh. They are connected to the rest of the network with special IO wrappers. The concept of region adds several advantages to NoC:

- A set of resources can be dedicated to a specific task.

- The communication between the resources inside the region can have different communication capacity.

- The resources inside the region are insulated from external traffic.

- NoC can accommodate a specific technology inside these regions.

However, these regions are constrained to have convex boundaries.

The concept of regions was further adopted by Chien et al. [29], where faulty components were insulated into region and messages are routed around that region. The fault region is also constrained to have convex boundaries. This constrained implies that the faulty components must form a block fault, so that every nonfaulty component that is on the boundary of a fault region can have a faulty link only from one side. Since concave faults may also occur, they are transferred to convex faults by deactivating some non-faulty components.

The algorithm intoduced in [29] is a planar-adaptive routing (see Section 2.3), where the network is divided into two virtual netwoks: decreasing and increasing. There is one additional virtual channel in vertical direction. These messages that are traveling in increasing (decreasing) *x*-coordinates use increasing (decreasing) virtual network. When a message, that is traveling in increasing (respectively in decreasing) network, encounters a fault it is misrouted in *y*-coordinate using virtual channel 0 (respectively 1). Thus, cyclic dependency is prevented by using totally three virtual channels. The algorithm is adaptive and a message can use either dimension adaptively. The message is only misrouted when it is on the same row or column with destination and encounters a fault.

Planar-adaptive routing marks non-faulty components as faulty, thus decreasing the number of good links and nodes. If a faulty node is on the boundary of a network the message cannot be routed around the fault region and have to traverse backward. This bring new channel dependency between increasing and decreasing networks. As a solution the entire row or column is marked as faulty. The same situation can be seen for concave regions, where a message will need to traverse back, thus message are no longer monothonically increasing or decreasing. The convex faulty region simplifies the routing algorithm and deadlock avoidance, thus

any kind of region is desired to have convex boundaries. However, this constrain leads to unefficient usage of non-faulty nodes.

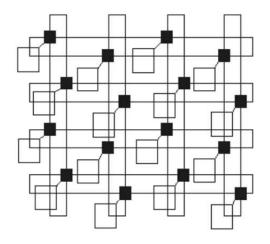

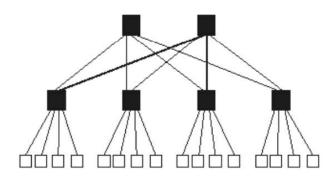

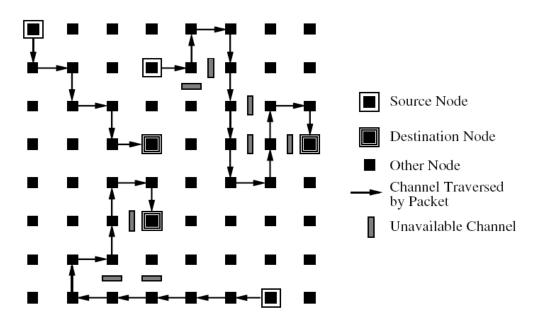

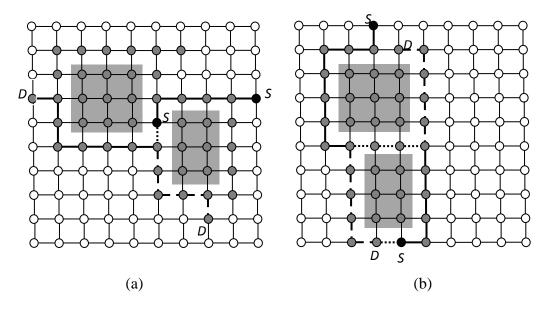

Chalasani et. al. [34] improved the concept of faulty region presented by [29]. In their fault-tolerant routing algorithm non-faulty nodes are not marked as faulty in order to obtain convex fault. They introduced a new concept of *fault rings* (f-ring).

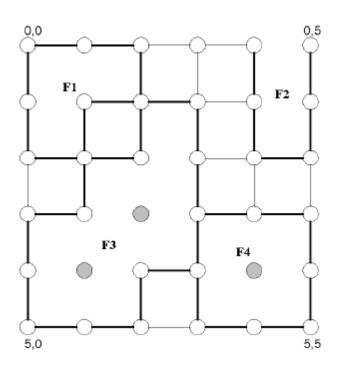

F set contains all faulty links and nodes. The faulty region is considered to be rectangular faulty block (convex) if all the fault-free nodes around the faulty region connect and form rectangle and all the nodes lying in the rectangle are faulty. The block-fault-model assumes that each fault belongs to exactly one faulty block. If all non-faulty nodes around the f-region connect and form a ring this is called f-ring. When a fault region touch boundaries of a network non faulty nodes cannot form ring so this is called f-chain (F2 in Fig. 13). The nodes at which f-chain touches the boundaries of a network are called end-nodes. F-rings are said to be overlapped if two or more f-rings share one or more links (F3 and F4 in Fig.13).

Figure 13 f-rings, f-chain and overlapping f-rings

[34] implemented their fault-tolerant algorithm upon the DOR algorithm, which is also called e-cube algorithm. Since DOR is deterministic algorithm it cannot tolerate even one faulty component. They divided the messages into column and row messages. The column and row messages are further divided into West-East (WE), East-West (EW), North-South (NS), and South-North (SN) messages, where WE and EW messages are row messages and NS and SN messages are column messages. A message that is still taking row hops is called row message, and a message that only requires column hops in order to reach its destination is called column messages. The row messages may change their status into column, but column messages never change their status into row messages. Two algorithms were presented: f-Cube2 and f-Cube4.

f-Cube algorithm uses 2 VC's and considers only non-overlapping block-faults. Row messages use  $c_0$  VC and column messages use only  $c_1$  VC. A message may have normal or misrouted status. The message's status is changed to misrouted if its next DOR hop is not available. Each time a message status is changed its direction is set, and its direction will not change throughout that f-ring. A misrouted NS (SN) message's direction is set to clockwise (counter clockwise). The EW message's direction is set to counter-clockwise (clockwise) if a destination is a row above (row below) than the current node. The same for WE messages.

The algorithm above proposed for non-overlapping fault-blocks is proved to be deadlock-free, since WE messages use only west boundaries and EW messages only east boundaries of f-ring. But when fault-blocks overlap, they share common columns or rows. Hence, the channels used by WE and EW messages are no longer disjoint. The similar issue arises in routing messages along f-chain, since messages that reach end-nodes are either stuck or make u-turn making channel utilization disjoint. In order to avoid deadlock f-Cube2 algorithm was modified to f-cube4 algorithm which uses 4 VCs. The algorithm divides the network into 4 disjoint networks WE, EW, NS and SN messages use  $c_0$ ,  $c_1$ ,  $c_2$ , and  $c_3$  VC's respectively. Here, again the row messages can become column messages but not vice versa.

Many other proposed fault-tolerant algorithms [35] [36] [37] [38] are generally derivatives of f-Cube4 with various attempt to decrease the number of virtual channels to be used in routing around f-regions. These fault tolerant algorithms are recommended to be used as a backup algorithm in adaptive networks. Since, adaptive networks lose their adaptivity in last dimension left and messages are not guaranteed to be delivered if they encounter faults, with additional four VC the adaptive algorithm can tolerate any number of faults.

## 2.4.3.2 Fault-Tolerant Routing Without VCs

In order to make wormhole routed meshes fault tolerant, usually additional virtual channels are used. However, virtual channels come at expanse as they require extra control lines, buffer space and switching hardware. Ni et al. [39] uses turn model in their one-fault-tolerant routing algorithm which does not require additional virtual channels. However, this algorithm is (n-1) fault-tolerant, which means that in 2D mesh it can tolerant only one faulty component. The authors argue that misrouting should be used only to increase fault-tolerance degree and never just for increasing adaptiveness, since misrouting increase communication latency

One-fault-tolerant algorithm is based on the negative-first routing algorithm, where packets are first routed in the negative directions (west and south) of dimensions 0 and 1 then in the positive directions (east and south) of dimensions 0 and 1. The result of the modifications of the negative-first routing algorithm:

- 1. Route the packet west and south to the destination or farther west and south than the destination. Avoid routing the packet to a negative edge for as long as possible. If a packet encounters a fault along the negative edge, route the packet one hop perpendicular to the edge.

- 2. Route the packet east and north to the destination, avoiding routing the packet as far east or north as the destination for as long as possible. If a faulty node on a negative edge of the mesh blocks the path to a destination on the edge, route the packet one hop perpendicular to the edge, two hops toward the destination and one hop back to the edge.

Another algorithm that does not require additional VCs was presented by Duato et al. [40]. It is software based fault tolerant routing. In fault-free cases the messages are routed using DOR algorithm. A packet that encounters a fault is ejected from the network and passed to messaging layer of the local node's operating system. The messaging layer further decides whether to send the packet along a non-minimal path or send it via intermediate node. Thus, the packet is re-injected into the network with modified header. However, the message reinjection complicates the messaging layer of a node, since it has to make right decisions upon message reinjection. As the messaging layer should know what paths has the message taken, the header flit size increases because of routing information. Along with introduced overhead in messaging layer, reinjection also increases message latency.

Both algorithms are considered for environments where fault rates are relatively low. The goal is to keep the system functioning, with possibly degraded performance. They try to keep the feature of deterministic router designs, i.e. compactness and speed, thus avoiding additional virtual channels. So, these messages that do not encounter faults are minimally impacted.

#### 2.4.4 Dynamic Recovery

As it can be seen from the previous chapters, wormhole routing is more difficult in avoiding deadlock. Since messages are sent in pipelined fashion, flits of one message occupy several routers. The destination information is stored only in header flit, so the data flits are heavily dependent on it. However, dynamic faults that occur on runtime may corrupt a link separating data flits from header flit. Since data flits cannot be routed without routing information, they remain in the network holding resources and thus leading to deadlock. The recovery from these faults should be held on run time.

### 2.4.4.1 Flit-Level Recovery

For a packet switching networks recovery can be easily constructed, so that the exactly-one injection is guaranteed. They are amenable to a link-level error detection and retransmission. However, the wormhole switching is not amenable to a link-level retransmission, since flits are spread over several routers. One solution for a wormhole switching technique that guarantees end-to-end delivery was presented by [41]. It implements link-level monitoring of flits. The copy of every flit is kept in a router until it receives acknowledgment that it was successfully received, which means that at least to copies of a flit remains in the network. Thus, if a flit encounters a fault while passing a link its copy can be retrieved from the last router it has leaved. The message is constructed from header, data, tail flits and a token. When a link fault occurs and the data flits lost their header flit a new header is generated for them. The message token is kept the same that was appended to original message. Thus, every router keeps the copy of header flit until token releases it. Those data flits that are on the other side of corrupted link with header flit will continue on the same way after the new token is appended to them. At the destination header flits are distinguished according to tag which indicates if the message is original or restart and the token according to replica or unique type.