#### LINEAR STATIC ANALYSIS OF LARGE STRUCTURAL MODELS ON PC CLUSTERS

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

SEMİH ÖZMEN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN CIVIL ENGINEERING

JULY 2009

#### Approval of the thesis:

#### LINEAR STATIC ANALYSIS OF LARGE STRUCTURAL MODELS ON PC CLUSTERS

submitted by SEMİH ÖZMEN in partial fulfillment of the requirements for the degree of Master of Science in Civil Engineering Department, Middle East Technical University by,

Prof. Dr. Canan Özgen \_\_\_\_\_\_ Dean, Graduate School of Natural and Applied Sciences

Prof. Dr. Güney Özcebe Head of Department, **Civil Engineering**

Asst. Prof. Dr. Özgür Kurç Supervisor, **Civil Engineering Dept.**, **METU**

#### **Examining Committee Members:**

Assoc. Prof. Dr. Uğur Polat Civil Engineering Dept., METU

Asst. Prof. Dr. Özgür Kurç Civil Engineering Dept., METU

Asst. Prof. Dr. Ayşegül Askan Gündoğan Civil Engineering Dept., METU

Inst. Dr. Afşin Sarıtaş Civil Engineering Dept., METU

Asst. Prof. Dr. Nilay Sezer Uzol Mechanical Engineering Dept., TOBB ETU

Date:

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Semih Özmen

Signature :

## ABSTRACT

#### LINEAR STATIC ANALYSIS OF LARGE STRUCTURAL MODELS ON PC CLUSTERS

Özmen, Semih M.S, Department of Civil Engineering Supervisor: Asst. Prof. Dr. Özgür Kurç

July 2009, 106 pages

This research focuses on implementing and improving a parallel solution framework for the linear static analysis of large structural models on PC clusters. The framework consists of two separate programs where the first one is responsible from preparing data for the parallel solution that involves partitioning, workload balancing, and equation numbering. The second program is a fully parallel finite element program that utilizes substructure based solution approach with direct solvers.

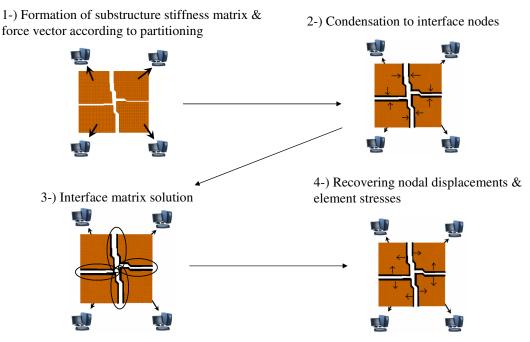

The first step of data preparation is partitioning the structure into substructures. After creating the initial substructures, the estimated imbalance of the substructures is adjusted by iteratively transferring nodes from the slower substructures to the faster ones. Once the final substructures are created, the solution phase is initiated. Each processor assembles its substructure's stiffness matrix and condenses it to the interfaces. The interface equations are then solved in parallel with a block-cyclic dense matrix solver. After computing the interface unknowns, each processor calculates the internal displacements and element stresses or forces. Comparative tests were done to demonstrate the performance of the solution framework.

Keywords: Linear Static Analysis, High Performance Computing, Substructuring, Workload Balancing, Direct Solvers

## ÖΖ

#### BİLGİSAYAR KÜMELERİ KULLANILARAK BÜYÜK YAPI MODELLERİNİN DOĞRUSAL STATİK OLARAK ÇÖZÜMLENMESİ

Özmen, Semih

Yüksek Lisans, İnşaat Mühendisliği Bölümü Tez Yöneticisi: Yard. Doç. Dr. Özgür Kurç

Temmuz 2009, 106 sayfa

Bu çalışma, bilgisayar kümeleri kullanılarak büyük yapı modellerinin doğrusal statik çözümlemesini yapabilen bir yazılımın geliştirilmesini hedeflemektedir. Çözümleme yazılımı iki ayrı yazılımdan oluşmaktadır. İlk yazılım, paralel çözümleme yazılımına veri hazırlamaktadır. İkinci yazılım ise alt-yapılar üzerinde direk çözümleme tekniği kullarak bütünüyle paralel çözümleme yapabilen bir sonlu elemanlar programıdır.

Veri hazırlama yazılımı alt-yapıları çözüm için olabilecek en uygun şekilde oluşturmaya çalışır. Alt-yapıların ilk sefer parçalanmasının ardından, alt-yapıların çözümlenmesi için gerekecek işlem adedi, her bir bilgisayarın işlem gücü ve o alt-yapıyı oluşturan elemanların adedi kullanılarak alt-yapılar arası iş yükü farkı hesaplanır ve bu fark yavaş çözümlenen alt-yapılardan hızlı çözümlenenlere doğru düğüm noktası aktarılarak dengelenmeye çalışılır. Alt-yapıların oluşturulmasından sonra direngenlik matrisi denklemleri en uygun şekilde sıralanır ve paralel çözümlemeye başlanır. Öncelikle, alt-yapı direngenlik matrisleri oluşturulur ve bu matrisler sınır düğümlerine indirgenir. Sonrasında, sınır denklemlerinin çözümü paralel olarak blok-çevrimsel yoğun matris çözücü ile gerçekleştirilir ve her bilgisayar bu çözümün sonuçlarını kullanarak düğüm deplasmanlarını ve eleman kuvvetlerini hesaplar. Çözüm yazılımının bütününün başarımını irdelemek amacıyla örnek problemler çözülmüş ve sonuçları değerlendirilmiştir.

Anahtar Kelimeler: Doğrusal Statik Çözümleme, Yüksek Başarımlı Hesaplama, Altyapılara Bölme, İş Yükü Bölüştürme, Direk Çözümleme To my dearest love

## ACKNOWLEDGMENTS

I would like to express my deepest gratitude to my supervisor, Asst. Prof. Dr. Özgür Kurç, because of his great guidance, support, and complete confidence in me during the whole research, publications, and presentations. Without his existence and experience, this research could not be completed.

Another person that supports this research in collaboration with his thesis research is my dear friend Tunç Bahçecioğlu. In any obstacle, I always felt comfortable with his support.

I wish to thank Asst. Prof. Dr. Julien Langou for his assistance about the LAPACK and ScaLAPACK routines, their optimizations, and binary compilations.

Another friend that gave a hand indirectly is Lasse Reinhold with his compression algorithm and suggestions on optimization of it.

Thanks to Eyyüp Volkan Çektimur, for his suggestions and comments on some critical points of the algorithm.

I would like to thank ComoSYS developers and especially Mr. Ateeq Ahmad for their understanding and support due to the fact that I spent some of my working hours to this study.

I want to exhibit my special thanks to my wife Özlem for her support and patience during this heavy work and also for her existence which gives me strength.

Moreover, I wish to thank my friends and my family for their existence, thus, I could find the opportunity to relax.

Thanks to *Scientific and Technological Research Council of Turkey* (TÜBİTAK), because of their financial support during this research.

This study is supported by Grant No: BAP-2007-03-03-09 from Middle East Technical University Scientific Research Program.

## TABLE OF CONTENTS

| ABSTRACT                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ÖZv                                                                                                                                                                  |

| ACKNOWLEDGMENTS vii                                                                                                                                                  |

| TABLE OF CONTENTS viii                                                                                                                                               |

| LIST OF FIGURES                                                                                                                                                      |

| LIST OF TABLES                                                                                                                                                       |

| CHAPTERS                                                                                                                                                             |

|                                                                                                                                                                      |

| 1 INTRODUCTION 1                                                                                                                                                     |

| 1.1 Problem Definition                                                                                                                                               |

| 1.2 Related Work $\ldots$ 3                                                                                                                                          |

| 1.2.1 Matrices and Matrix Storage Schemes                                                                                                                            |

| 1.2.2 Solution Methods for System of Linear Equations                                                                                                                |

| 1.2.3 Direct Solution Methods $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ |

| 1.2.3.1 Background                                                                                                                                                   |

| 1.2.3.2 Direct Solvers for Dense Matrices                                                                                                                            |

| 1.2.3.2.1 Cholesky Factorization in LAPACK                                                                                                                           |

|                                                                                                                                                                      |

| 1.2.3.2.2 Cholesky Factorization in ScaLAPACK                                                                                                                        |

|                                                                                                                                                                      |

| 1.2.3.3 Direct Solvers for Sparse Matrices                                                                                                                           |

| $1.2.4$ Substructuring $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $17$                                                                                             |

| 1.2.4.1 Partitioning                                                                                                                                                 |

| 1.2.4.2 Workload Balancing                                                                                                                                           |

| 1.2.4.3 Substructure based Solution Methods                                                                                                                          |

| 1.2.5 PC Clusters and Communication Interfaces                                                                                                                       |

|                                                                                                                                                                      |

|   | 1.3 Objectives and Scope                             | 24       |

|---|------------------------------------------------------|----------|

|   | 1.4 Thesis Outline                                   | 24       |

| 2 | AN OVERVIEW OF THE PARALLEL SOLUTION FRAMEWORK       | 26       |

|   | 2.1 Introduction                                     | 26       |

|   | 2.2 Algorithm                                        | 26       |

|   | 2.3 Mathematical Background                          | 27       |

|   | 2.3.1 Condensation                                   | 28       |

|   | 2.3.2 Substructure based solution                    | 29       |

| 3 | DATA PREPARATION                                     | 33       |

|   | 3.1 Introduction                                     | 33       |

|   | 3.2 Overview                                         | 33       |

|   | 3.2.1 Partitioning Libraries                         | 35       |

|   | 3.2.1.1 METIS                                        | 36       |

|   | 3.2.1.2 PARMETIS                                     | 37       |

|   | 3.3 Workload Balancing Algorithm                     | 37       |

|   | 3.4 Test Results                                     | 40       |

|   | 3.4.1 Illustrative Example                           | 41       |

|   | 3.4.2 Actual Testing Models                          | 42       |

| 4 | PARALLEL SOLUTION                                    | 48       |

|   | 4.1 Introduction                                     | 48       |

|   | 4.2 Parallel Solution Algorithm                      | 48       |

|   | 4.3 Condensation                                     | 51       |

|   | 4.3.1 Algorithm                                      | 51       |

|   | 4.3.2 Test Results                                   | 53       |

|   | 4.4 Interface System                                 | 55       |

|   | 4.4.1 Interface System Assembly                      | 56       |

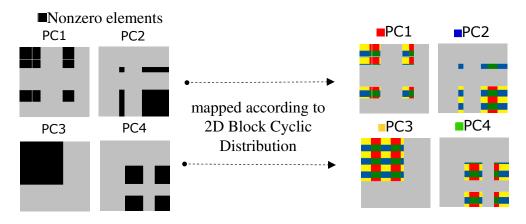

|   | 4.4.1.1 Data Mapping                                 | 58       |

|   | 4.4.1.1.1 Block Cyclic Data Distribution             |          |

|   |                                                      | 59       |

|   | 4.4.1.1.2 Data Mapping for Block Cyclic Distribution | 00       |

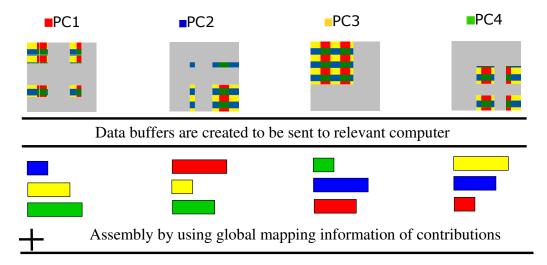

|   | 4.4.1.2 Communication Scheme                         | 60<br>64 |

|   | 4.4.1.2 Communication Scheme                         | υ4       |

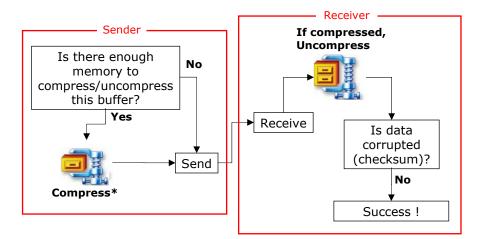

|      | 4.4.1.3 Data Compression                                                                             | 65  |

|------|------------------------------------------------------------------------------------------------------|-----|

|      | 4.4.2 Interface System Solution                                                                      | 66  |

|      | 4.4.2.1 Implementation                                                                               | 66  |

|      | 4.4.2.2 Improvements for Speed-up                                                                    | 67  |

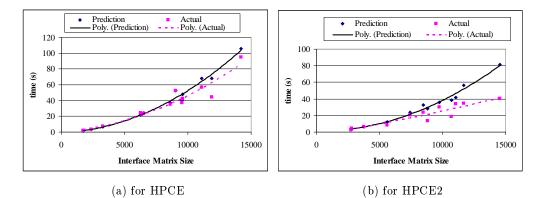

|      | 4.4.2.3 Execution Time and Communication Volume Estimations                                          | 68  |

|      | 4.4.3 Test Results                                                                                   | 69  |

|      | 4.4.3.1 Performance of The Interface System Assembly                                                 | 70  |

|      | 4.4.3.1.1 Performance Improvement by Runtime Data Compres-                                           |     |

|      | sion                                                                                                 |     |

|      |                                                                                                      | 71  |

|      | 4.4.3.2 Performance of The Interface System Solution                                                 | 71  |

|      | 4.4.3.2.1 Execution Time Estimation and Comparison with Ac-                                          |     |

|      | tual Timings $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                   | 71  |

|      | 4.4.3.2.2 Speed-up and Efficiency                                                                    |     |

|      |                                                                                                      | 73  |

| 5    | OVERALL PERFORMANCE OF PARALLEL SOLUTION FRAMEWORK                                                   | 76  |

|      | 5.1 Method $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 76  |

|      | 5.2 Test Results                                                                                     | 77  |

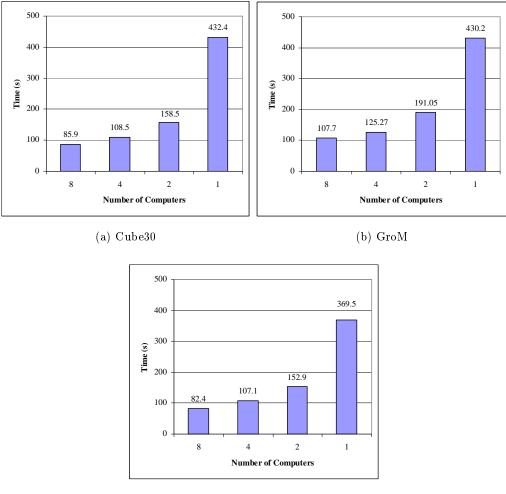

|      | 5.2.1 Cube $30$                                                                                      | 77  |

|      | 5.2.2 GroM                                                                                           | 79  |

|      | 5.2.3 StRegis $\ldots$ $\ldots$                                                                      | 81  |

|      | 5.2.4 Shared Memory Simulation                                                                       | 83  |

|      | 5.3 Discussion of Overall Results                                                                    | 85  |

| 6    | CONCLUSION AND FUTURE PLANS                                                                          | 87  |

|      | 6.1 Conclusion                                                                                       | 87  |

|      | 6.2 Future Plans                                                                                     | 89  |

| REFE | ERENCES                                                                                              | 91  |

| APPE | ENDICES                                                                                              |     |

| А    | PERFORMANCE ASSESSMENT OF PARALLEL ALGORITHMS                                                        | 99  |

|      | A.1 General features of parallel processing                                                          | 99  |

|      | A.2 Time measures                                                                                    | 100 |

|      | A.3 Computational speed                                                                              | 101 |

|   | A.4 Parallel measurement                     | 101 |

|---|----------------------------------------------|-----|

| В | STRUCTURAL MODELS USED FOR PERFORMANCE TESTS | 104 |

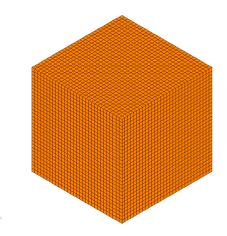

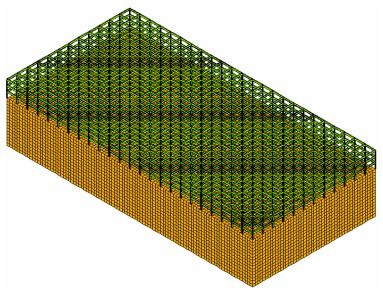

|   | B.1 Cube30                                   | 104 |

|   | B.2 GroM                                     | 105 |

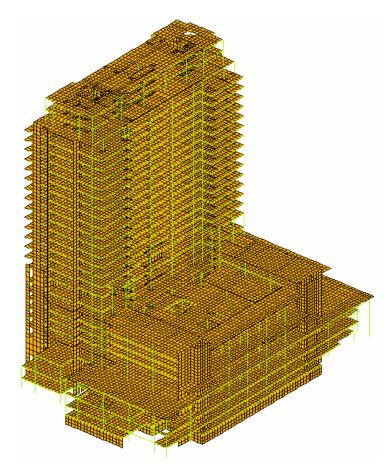

|   | B.3 StRegis                                  | 106 |

## LIST OF FIGURES

#### FIGURES

| Figure 1.1 | Memory access patterns for variants of Cholesky Decomposition $% \mathcal{A}$ . | 8  |

|------------|---------------------------------------------------------------------------------|----|

| Figure 1.2 | ScaLAPACK Software Hierarchy [1]                                                | 11 |

| Figure 1.3 | A snapshot of block Cholesky factorization[2]                                   | 13 |

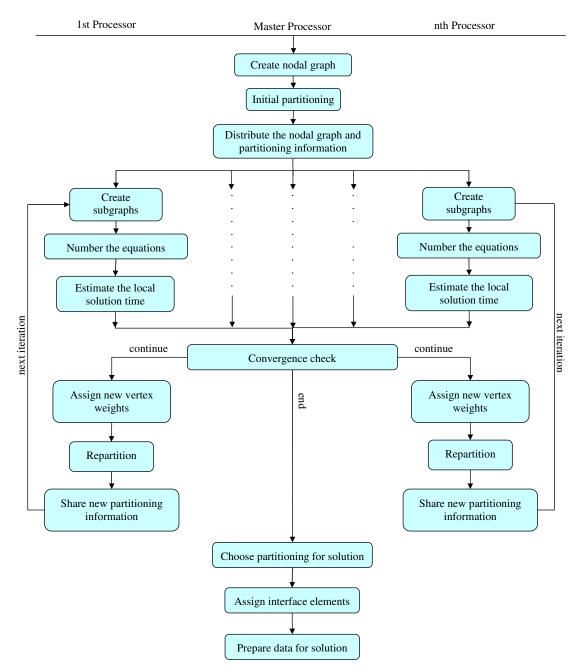

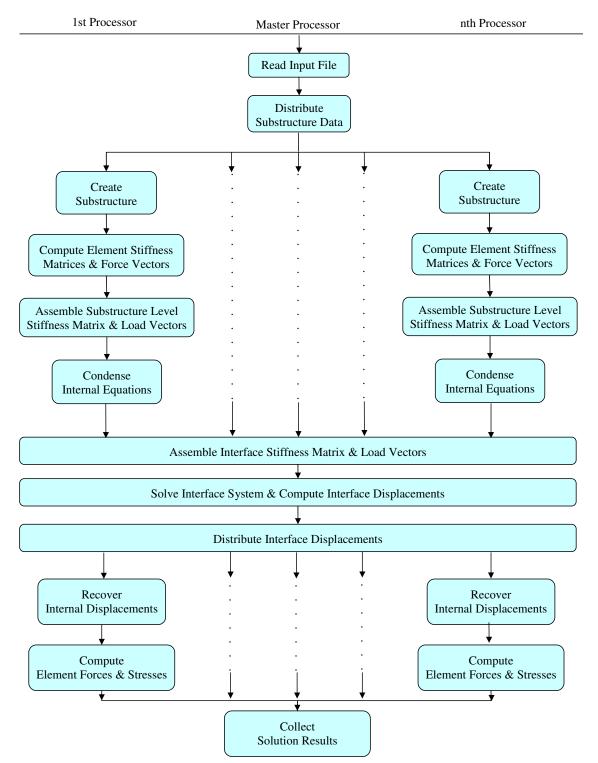

| Figure 2.1 | Parallel Solution Flow Chart Demonstration                                      | 27 |

| Figure 2.2 | An Example Profile of a Stiffness Matrix Assembled for Condensation             | 28 |

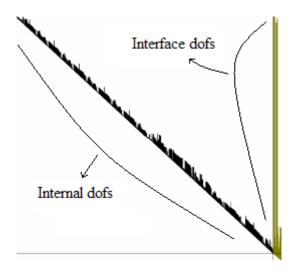

| Figure 2.3 | Internal and Interface dofs of Substructures                                    | 30 |

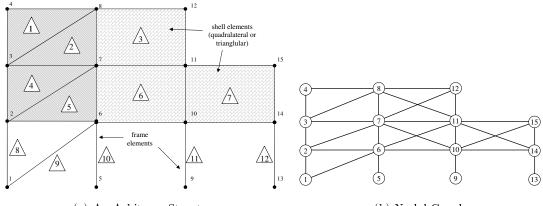

| Figure 3.1 | Graph Representation of an arbitrary structure                                  | 36 |

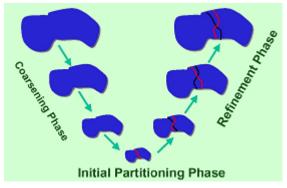

| Figure 3.2 | Multilevel Approach $[3]$                                                       | 37 |

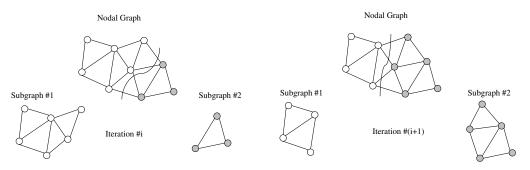

| Figure 3.3 | Nodal Graph and Subgraphs during iterations                                     | 38 |

| Figure 3.4 | The Flow Chart of the Workload Balancing Algorithm                              | 39 |

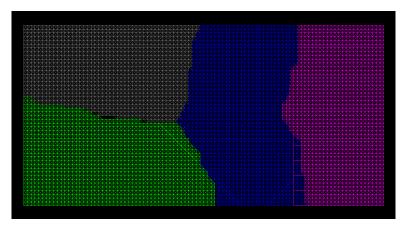

| Figure 3.5 | Substructures of 2DMesh Model at each workload balancing step                   | 43 |

| Figure 3.6 | Substructures of 2DMesh Model at each workload balancing step                   |    |

|            | $(cont.)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $      | 44 |

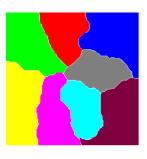

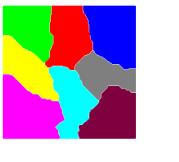

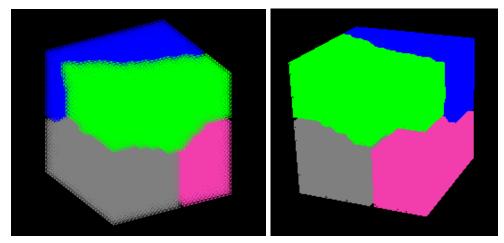

| Figure 3.7 | Final Partitioning of Cube30 Model                                              | 45 |

| Figure 3.8 | Final Partitioning of GroM Model                                                | 46 |

| Figure 3.9 | Final Partitioning of StRegis Model                                             | 47 |

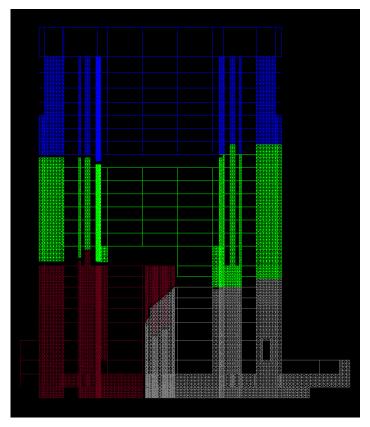

| Figure 4.1 | Parallel Solution Flow Chart                                                    | 50 |

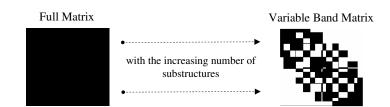

| Figure 4.2 | Non-zero element pattern for interface stiffness matrix $\ldots$ .              | 56 |

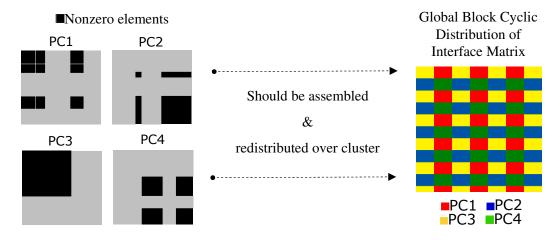

| Figure 4.3 | The contributions of each substructure to interface stiffness matrix            | 56 |

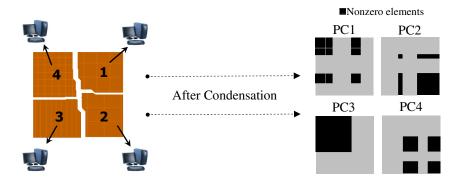

| Figure 4.4 | Redistribution over cluster                                                     | 57 |

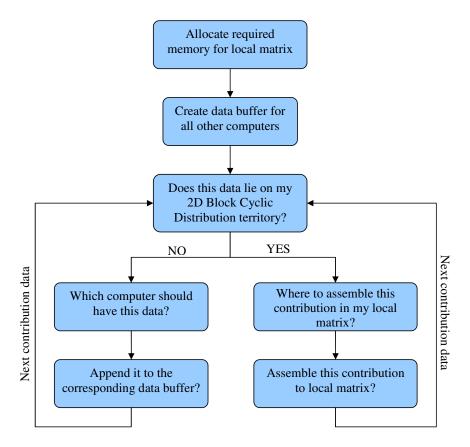

| Figure 4.5 | On the Fly Assembly                                                             | 58 |

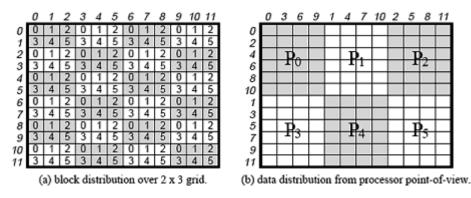

| Figure 4.6 | Example of a block cyclic data distribution $[2]$                               | 60 |

| Figure 4.7 | 2D Block Cyclic Mapping Parameters                                              | 61 |

| Figure 4.8  | 2D Block Cyclic Mapping                                                     | 63  |

|-------------|-----------------------------------------------------------------------------|-----|

| Figure 4.9  | Data buffers to be sent to relevant computers $\ldots \ldots \ldots \ldots$ | 63  |

| Figure 4.10 | Runtime Data Compression                                                    | 65  |

| Figure 4.11 | Interface Solution Prediction vs Actual Timings                             | 73  |

| Figure 4.12 | Interface Solution Speed-Up Graphs                                          | 74  |

| Figure 4.13 | Interface Solution Efficiency Graphs                                        | 75  |

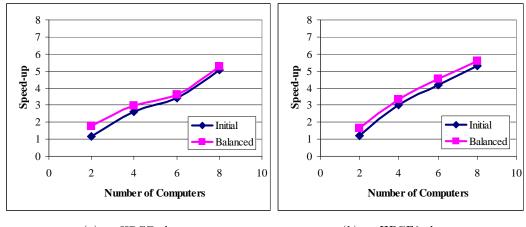

| Figure 5.1  | Test Results for Cube30 Model on HPCE cluster                               | 78  |

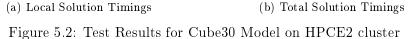

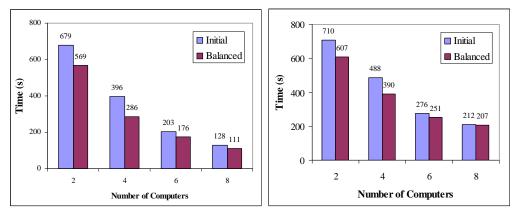

| Figure 5.2  | Test Results for Cube30 Model on HPCE2 cluster                              | 78  |

| Figure 5.3  | Speed-ups for Cube30 Model                                                  | 79  |

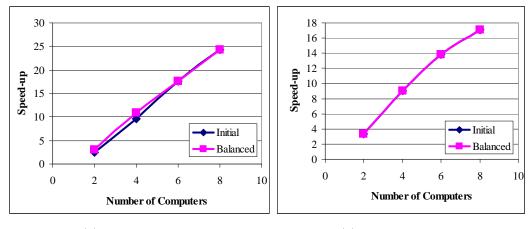

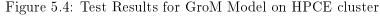

| Figure 5.4  | Test Results for GroM Model on HPCE cluster                                 | 80  |

| Figure 5.5  | Test Results for GroM Model on HPCE2 cluster                                | 80  |

| Figure 5.6  | Speed-up Graphs for GroM Model                                              | 81  |

| Figure 5.7  | Test Results for StRegis Model on HPCE cluster                              | 82  |

| Figure 5.8  | Test Results for StRegis Model on HPCE2 cluster                             | 82  |

| Figure 5.9  | Speed-up Graphs for StRegis Model                                           | 83  |

| Figure 5.10 | Total Solution Times on a Multi-processor Computer in HPCE2                 |     |

|             | Cluster                                                                     | 84  |

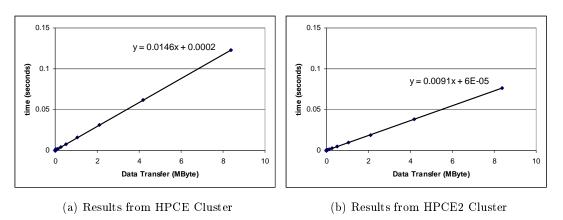

| Figure A.1  | Data Transfer vs Time Graphs                                                | 100 |

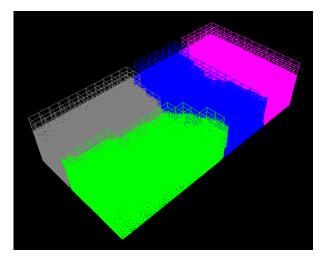

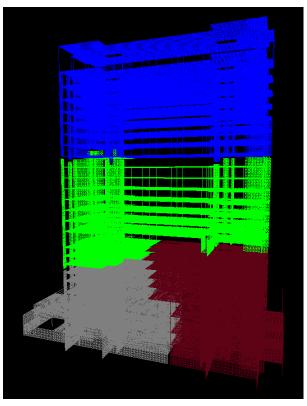

| Figure B.1  | Cube30 Model                                                                | 105 |

| Figure B.2  | GroM Model                                                                  | 105 |

| Figure B.3  | StRegis Model                                                               | 106 |

## LIST OF TABLES

#### TABLES

| Table 1.1 | Matrix Storage Schemes                                           | 4  |

|-----------|------------------------------------------------------------------|----|

| Table 3.1 | Workload Balancing Iteration Results for 2DMesh Model            | 41 |

| Table 3.2 | Workload Balancing Iteration Results for StRegis Model           | 42 |

| Table 3.3 | Workload Balancing Iteration Results for GroM Model              | 45 |

|           |                                                                  |    |

| Table 4.1 | Condensation Timings                                             | 53 |

| Table 4.2 | Condensation Speeds for HPCE Computers                           | 54 |

| Table 4.3 | Condensation Speeds for HPCE2 Computers                          | 55 |

| Table 4.4 | Forming Communication Scheme                                     | 64 |

| Table 4.5 | Interface System Assembly Timings for HPCE2                      | 70 |

| Table 4.6 | Speed-up obtained by Runtime Data Compression                    | 71 |

| Table 4.7 | Execution time and communication volume estimations on 4 comput- |    |

|           | ers of HPCE                                                      | 72 |

| Table 4.8 | Execution time and communication volume estimations on 4 comput- |    |

|           | ers of HPCE2                                                     | 72 |

## CHAPTER 1

## INTRODUCTION

#### 1.1 Problem Definition

A few decades ago, like any other discipline, structural engineers and companies started to use computers for structural analyses as computers and related software became more available. At that time, considerable amount of time was spent to input the mathematical model to the computer and the computation could last hours or even nights for medium size structural models, having 100-1000 nodes. In time, computers got faster in clock time speeds and had larger memory capacities. Such technological developments improved the computational experiences of engineers. Initially, increasing computational capabilities of computers allowed software developers to build graphical user interfaces which were not only allowed inputting very complex structures with many elements but also capable of rendering objects in 3D. In addition, increase in the speed of processors shortened overnight analysis to seconds for medium size models. In this case, however, structural engineers felt more comfortable to create larger models by using advanced graphical user interfaces and also they tended to utilize more advanced and complex finite elements, more load combinations, and even more detailed analysis methods. Today, it is very common to see structural models having hundreds of thousands of nodes created for analysis and design of structures. Moreover, for very special projects, structural engineers could create models that required the solution of billion equations [4]. Thus, the computation demand of engineers keeps increasing together with the improvement in the computer technology.

Just a few years ago, the increase in the clock speeds of processors almost stopped due to the space limitations, power, and cooling requirements for processors. As Herb Sutter says "*light isn't getting any faster, free lunch is over.*" [5]. These physical limitations forced the processor manufacturers to change their direction. They started to produce processors having more than one processing unit rather than trying to increase the clock speed of a single one. Therefore, to balance the expectations of the structural engineers, new solution strategies that can utilize the available multi-processor systems more efficiently are necessary. Thus, although it appears for more than two decades, parallel computing techniques are one of the remedy to this problem. These techniques are mainly composed of using the power of more than one processor to solve a single problem.

The necessity for new solution strategies become more apparent when the design of a structure is investigated in detail. The design of a structure is an iterative process of analysis and design stages. This process can be subjected to more repetitions due to the possible modifications in architectural, economical, and manufacturing requirements. For each of these modifications, the structural model may need to be updated, reanalyzed and re-designed. Analysis step is the one that consumes considerable amount of computational resource. When the size and the details of the model become larger, the finite element procedure requires more time to solve the system. Depending on the problem, different kinds of solution techniques are implemented with finite element methods. Most of the analysis methods, have the similar solution procedure that can be grouped into three major steps [6]. First one is the generation of element stiffness matrices, and equivalent nodal loads and assembling them into structural stiffness and force matrices. Besides, if dynamic analysis is performed, mass and damping matrices must also be computed. Second step is the solution of the following linear system of equations;

$$[K] . \{u\} = \{F\} \tag{1.1}$$

for u. In this linear system of equations, K is the  $n \times n$  positive-definite symmetric stiffness matrix, F is a vector of size n, alternatively right hand side (RHS) vector, representing the loading at each DOF, and u is a vector of size n, respresenting the unknown displacements corresponding to each loading. The final step is the computation of element forces and stresses using the calculated displacements.

In order to decrease the time spent during analysis step, readily available systems can be utilized. When the structural engineering design offices are considered, the readily available systems are usually the network of PC's running Windows OS. A parallel solution system that can use this system can be considerably useful for them. This way, not only the time required for the analysis will decrease but also existing computational power in these offices will be utilized more efficiently, without purchasing any additional hardware [6].

As a result, the structural engineering industry will benefit significantly from a solution algorithm that utilizes the existing computational power of the design offices, which is optimized for linear static solutions with multiple loading conditions and which is able to decrease the analysis time notably. Because of that, this study will focus on a parallel linear static solution of large structures on PC clusters.

#### 1.2 Related Work

Linear system of equations can be represented by matrices and corresponding load vectors. These matrices and load vectors are stored in the computer's memory with different storage schemes. The storage scheme is an important factor for the memory utilization and speed of the computation. Another factor that mainly affects the performance of the computation is the method that is utilized for the solution of system of equations. Different solution methods, their advantages, and disadvantages will be discussed in detail. Besides, parallel implementations of these methods and parallel solution environments proposed as a remedy for increasing the computational efficiency will also be presented.

#### 1.2.1 Matrices and Matrix Storage Schemes

Matrices can be classified according to the occurrence of their non-zero terms. Frequently encountered matrix types are dense, band, and sparse matrices. Dense matrices has few number of non-zero terms or even not at all. On the contrary, "a sparse matrix is a matrix populated primarily with zeros" [7]. As a special form of sparse matrix, band matrix is the one whose non-zero entries are confined to a diagonal band, comprising the main diagonal and zero or more diagonals on either side.

Depending on the matrix type, matrix storage schemes, namely how the matrices are stored in computer memory, differ. The conventional way of storing a matrix is utilizing a two-dimensional array. This storage may be reasonable when the matrix is dense. However, if the matrix is sparse, such storage is consumptive as the majority of the elements of the matrix are zero and need not to be stored explicitly. For sparse matrices, the common practice is to store only the non-zero entries and to keep track of their locations in the matrix through an indexing scheme. There are a variety of specialized indexing schemes utilized to store sparse matrices. These specialized schemes not only reduce memory consumption but also yield computational savings [8]. Since the locations of the non-zero elements in the matrix are known explicitly, unnecessary computations involving zeros can be avoided. However, the indexing based storage schemes increase the number of non-contiguous memory accesses and this may increase the application execution time [9]. Like these storage schemes, by using symmetry of the matrix or any pattern of the non-zero terms, further minimization of the memory required for storage can be achieved.

In literature, there are different types of sparse matrix storage schemes. Frequently used ones are Coordinate Storage (CS), Compressed Row Storage (CRS), Compressed Column Storage (CCS), Blocked Compressed Row Storage (BCRS), Compressed Diagonal Storage (CDS), Jagged Diagonal Scheme (JDS) and Skyline Storage (SS).

$$A = \begin{pmatrix} a_{11} & a_{12} & 0 & 0 \\ a_{21} & a_{22} & 0 & 0 \\ 0 & 0 & a_{33} & a_{34} \\ 0 & 0 & a_{43} & a_{44} \end{pmatrix}$$

(1.2)

| Coordinate Storage (CS)                                                                                                         | Compressed Row Storage (CRS)                                                                                                                                                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $ Value = \left( \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                            | $Value = \left(\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                              |  |

| $RowIndeces = \left(\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                         | $ColumnIndeces = \left(\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                      |  |

| $ColumnIndeces = \left(\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                      | $RowStartingIndeces = \left(\begin{array}{ccc} 0 & 2 & 4 & 6 \end{array}\right)$                                                                                                                |  |

| Compressed Column Storage (CCS)                                                                                                 | Blocked CRS (BCRS)                                                                                                                                                                              |  |

| $ Value = \left( \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                            | $Value = \left(\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                              |  |

| $RowIndeces = \left(\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                         | $ColumnIndeces = \left(\begin{array}{cc} 0 & 2 \end{array}\right)$                                                                                                                              |  |

| $ColumnIndeces = \left(\begin{array}{ccc} 0 & 2 & 4 & 6 \end{array}\right)$                                                     | $RowIndeces = \left(\begin{array}{cc} 0 & 2 \end{array}\right)$                                                                                                                                 |  |

| Compressed Diagonal Storage (CDS)                                                                                               | Jagged Diagonal Storage (JDS)                                                                                                                                                                   |  |

| $Value = \begin{pmatrix} 0 & a_{12} & 0 & a_{34} \\ a_{11} & a_{22} & a_{33} & a_{44} \\ a_{21} & 0 & a_{43} & 0 \end{pmatrix}$ | $Value = \begin{pmatrix} a_{11} & a_{12} \\ a_{21} & a_{22} \\ a_{33} & a_{34} \\ a_{43} & a_{44} \end{pmatrix} ColumnIndeces = \begin{pmatrix} 0 & 1 \\ 0 & 1 \\ 2 & 3 \\ 2 & 3 \end{pmatrix}$ |  |

| Skyline Storage (SS)                                                                                                            |                                                                                                                                                                                                 |  |

| $ UpperValues = \left( \begin{array}{cccc} a_{11} & a_{22} & a_{12} & a_{33} & a_{44} & a_{34} \end{array} \right) $            | $UpperStartIndeces = \left(\begin{array}{ccc} 0 & 1 & 3 & 4 \end{array}\right)$                                                                                                                 |  |

| $ LowerValues = \left(\begin{array}{cccc} a_{11}^* & a_{22}^* & a_{21} & a_{33}^* & a_{44}^* & a_{43} \end{array}\right) $      | $LowerStartIndeces = \left(\begin{array}{ccc} 0 & 1 & 3 & 4 \end{array}\right)$                                                                                                                 |  |

Table 1.1: Matrix Storage Schemes

In all of the above sparse matrix storage schemes, with the exception of the CDS scheme which is also known as packed banded matrix storage [10], the indexing is handled by additional data structures like arrays or matrices that stores indices of values. These different data structures typically necessitate non-contiguous multiple memory system accesses which hinders performance. In order to access  $a_{ij}$ , first the place of the value in value list should be calculated by accessing and using index lists. Therefore, these multiple indirect accesses are difficult for the compiler to optimize for fast memory accesses and resulting in poor performance [11]. If it is possible to implement such a specialized algorithm that can utilize CDS, no additional accesses are required. In contrast, two index list accesses are required to obtain  $a_{ij}$  in CS. Although implementation of this scheme is easier than CRS or CCS, it requires more memory space. Also, skyline storage is generally advantageous because after an initial access to index list, no accesses is required through that active column or row.

#### 1.2.2 Solution Methods for System of Linear Equations

The system of linear equations arising from a linear solution of a structural model with n degree of freedoms (DOF) is represented by Equation 1.1 as

$$[K] \, . \, \{u\} = \{F\}$$

In case of multiple loading conditions, there are multiple right hand sides, and the solution is performed for each right hand side. Therefore, for each right hand side, corresponding displacements are obtained.

The stiffness matrices resulted from the linear finite element method are symmetric and positive definite. Besides, the stiffness matrices are generally sparse. In literature, there are mainly two kinds of methods for the solution of linear system of equations:

• Direct Methods: These methods give the exact solution of a linear system of equations by performing known number of operations. There are mainly two different approaches in direct methods: first is finding the inverse of stiffness matrix K and just multiplying it with F vector, second is the transforming the coefficient matrix into triangular or diagonal form in order to eliminate the coupling between equations. First method requires a lot of operations so it is seldom used. The most commonly used transformation based direct methods are Gauss elimination and LU decomposition in general,  $LL^T$  decomposition for symmetric, positive-definite coefficient matrices and  $LDL^T$  decomposition for symmetric coefficient matrices.

• Iterative Methods: These methods are similar to trial and error. They start with an initial guess and try to converge to the result by refining the solution at each iteration step. Due to their iterative behaviour, preconditioning techniques are utilized to reduce the number of iterations and to guarantee the convergence of solution. Mostly used examples are Jacobi Method, Gauss-Seidel Method and Conjugate Gradient Method.

For parallel solution, iterative methods are scalable and require less memory compared to direct methods, allowing the solution of very large problems with limited computational resources. However, the convergence of iterative methods depend on the preconditioner used for a problem, and the runtime of iterative methods is unpredictable due to their iterative nature. Additionally, iterative methods can be inefficient for analyzing structures for multiple load cases since the entire solution start from scratch for each right hand side vector.

The direct methods, on the other hand, factorize stiffness matrix for only once, then, the system of equations can be solved efficiently for multiple right hand side vectors without the need of any additional factorization. The sparsity of a system is used to minimize the arithmetic operation and data storage required for the solution. These methods have high numerical precision and guarantee the solution within a predictable amount of time if computational resources are adequate. Direct methods are often the method of choice because finding and computing a good preconditioner for an iterative method can be computationally more expensive than using a direct method [12]. Because of these advantages, direct methods are preferred in most commercial structural analysis software.

#### **1.2.3** Direct Solution Methods

#### 1.2.3.1 Background

Direct methods are based on the factorization of the stiffness matrix. They can be classified according to the way of the factorization is performed, for example in LU decomposition, the stiffness matrix is factorized as

$$A = LU = \begin{bmatrix} 1 & 0 & \cdots & 0 \\ L_{2,1} & \ddots & 0 & \vdots \\ \vdots & \ddots & \ddots & 0 \\ L_{n,1} & \cdots & L_{n,n-1} & 1 \end{bmatrix} \begin{bmatrix} U_{1,1} & U_{1,2} & \cdots & U_{1,n} \\ 0 & \ddots & \ddots & \vdots \\ \vdots & 0 & \ddots & U_{n-1,n} \\ 0 & \cdots & 0 & U_{n,n} \end{bmatrix}$$

(1.3)

where U is upper triangular coefficient matrix obtained at the end of forward elimination, and L is lower triangular matrix formed by multipliers that is used during forward elimination. For a symmetric stiffness matrix A, this decomposition becomes

$$A = LL^{T} = \begin{bmatrix} L_{1,1} & 0 & \cdots & 0 \\ L_{2,1} & \ddots & 0 & \vdots \\ \vdots & \ddots & \ddots & 0 \\ L_{n,1} & \cdots & L_{n,n-1} & L_{n,n} \end{bmatrix} \begin{bmatrix} L_{1,1} & L_{1,2} & \cdots & L_{1,n} \\ 0 & \ddots & \ddots & \vdots \\ \vdots & 0 & \ddots & L_{n-1,n} \\ 0 & \cdots & 0 & L_{n,n} \end{bmatrix}$$

(1.4)

which is known as Cholesky's decomposition. Following formulas apply for the entries of L;

$$L_{i,j} = \frac{1}{L_{j,j}} (A_{i,j} - \sum_{k=1}^{j-1} L_{i,k} L_{j,k}), \text{ for } i < j$$

(1.5)

and

$$L_{i,i} = \sqrt{A_{i,i} - \sum_{k=1}^{i-1} L_{i,k}^2}$$

(1.6)

where indices for entries of L, i = 1...n, and j = 1...n.

Here, computation of square root hinders the performance of the procedure. To avoid taking square roots, following alternative can be utilized;

$$A = LDL^{T} = \begin{bmatrix} 1 & 0 & \cdots & 0 \\ L_{2,1} & \ddots & 0 & \vdots \\ \vdots & \ddots & \ddots & 0 \\ L_{n,1} & \cdots & L_{n,n-1} & 1 \end{bmatrix} \begin{bmatrix} D_{1,1} & 0 & \cdots & 0 \\ 0 & \ddots & 0 & \vdots \\ \vdots & 0 & \ddots & 0 \\ 0 & \cdots & 0 & D_{n,n} \end{bmatrix} \begin{bmatrix} 1 & L_{1,2} & \cdots & L_{1,n} \\ 0 & \ddots & \vdots \\ \vdots & 0 & \ddots & L_{n-1,n} \\ 0 & \cdots & 0 & 1 \\ (1.7) \end{bmatrix}$$

where D is a diagonal matrix. So, formulations for the entries of D and L are;

$$L_{i,j} = \frac{1}{D_j} (A_{i,j} - \sum_{k=1}^{j-1} L_{i,k} L_{j,k} D_k), \text{ for } i < j$$

(1.8)

and

$$D_i = A_{i,i} - \sum_{k=1}^{i-1} L_{i,k}^2 D_k$$

(1.9)

where indices for entries of L, i = 1...n, and j = 1...n.

For all decomposition methods mentioned above, forward elimination followed by backward substitution completes the solution process for each given right hand side vector.

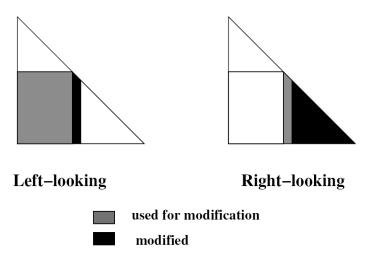

Figure 1.1: Memory access patterns for variants of Cholesky Decomposition

According to the way a matrix is factorized, direct solution methods can be examined into two groups as left-looking and right-looking (Figure 1.1). Both of these computations can be typically expressed in terms of two primitives. First, cmod(j,k) to add into column j a multiple of column k and second cdiv(j): divide column j by a scalar.

• Left-looking (or fan-in) algorithms; where updates are performed on each column in turn by all the previous columns that contribute to it, then the pivot is chosen in that column and the multipliers calculated. In other words, the general structure of the left-looking approach is as follows, with the  $k^{th}$  term iterating over columns to the left of column j in the matrix.

# Algorithm 1.1 Left-Looking Algorithmfor j = 1 to n docdiv(j)for each k that modifies j do

$\operatorname{cmod}(j, k)$

Right-looking (or fan-out) algorithm; where, after the calculation of pivot and multipliers, that column is immediately used to update all future columns that it modifies. Namely, the general structure of the right-looking approach is as follows, with the j term iterating over column to the right of column k.

| Algorithm 1.2 Right-Looking Algorithm        |  |  |

|----------------------------------------------|--|--|

| for $k = l$ to n do                          |  |  |

| $\operatorname{cdiv}(k)$                     |  |  |

| for each j modified by k do                  |  |  |

| $\operatorname{cmod}(\mathrm{j},\mathrm{k})$ |  |  |

In both cases, j iterates over destination columns and k iterates over source columns. Note also that the cmod() operation is performed a number of times per column while the cdiv() operation is performed only once. Therefore, the cmod() operation dominates the computation time.

The tests over the efficiency of both of the algorithms reveal that left-looking algorithm is more efficient because it enables the usage of contiguous data in memory. However, this difference in performance is negligible when the improvement achieved by the use of blocked algorithms considered [13].

During factorization step, various linear algebra routines like matrix-vector or matrixmatrix operations are executed numerous times [2, 13, 14]. To handle such common operations, BLAS (Basic Linear Algebra Subprograms) are developed and distributed in public domain. BLAS are subdivided into three levels, each of which offers increased scope for exploiting performance. This subdivision corresponds to three different types of basic linear algebra operations:

- Level 1 BLAS : for vector operations, such as  $y \leftarrow \alpha x + y$ ,

- Level 2 BLAS : for matrix-vector operations, such as  $y \leftarrow \alpha Ax + \beta y$ ,

• Level 3 BLAS : for matrix-matrix operations, such as  $C \leftarrow \alpha AB + \beta C$ .

Here, A, B, and C are matrices, x and y are vectors, and  $\alpha$  and  $\beta$  are scalars [10].

The main obstacle to obtaining high performance is the bottleneck in getting data from the main memory to the functional units. Many machines have multiple caches usually organized hierarchically from fastest-smallest to slowest-largest. Therefore, to obtain high performance relative to the peak of the machine, it is necessary to reuse data in the cache as much as possible to amortize the cost of getting it to the cache from main memory. In this context, performance of the routines in BLAS increases with the increase in its level because more contiguous data will be transferred to cache and used repetitively [11]. Therefore, the most suitable and widely used kernels are Level 3 BLAS for  $O(n^3)$  operations involving matrices of order n [1,10,15,16]. Likewise, instead of factorizing a single column, factorizing a blocked column is more efficient. For example, Level 2.5 BLAS is designed as the multiplication of a set of vectors by a matrix where the vectors cannot be stored in two-dimensional arrays. In other words, source data can be held in cache and applied to the target columns or blocks of columns of the target data, thus getting a high degree of reuse of data and a performance similar to the Level 3 BLAS [17].

Currently, various solvers, not only utilize methods discussed here but also by slightly modifying these methods, try to enhance computational efficiency on different computational environments like parallel solution environments.

#### 1.2.3.2 Direct Solvers for Dense Matrices

With the great achievement of BLAS to become a *de facto* standard for linear algebra computations, an upper level library, LAPACK, or Linear Algebra PACKage, is built over BLAS routines [11]. This library is a collection of routines for linear system solution, linear least squares problems, and eigenproblems. The associated matrix factorizations (LU, Cholesky, QR, SVD, etc..) are also provided. Dense and banded matrices are handled. High performance is attained by using algorithms that perform most of their work in calls to the BLAS, with an emphasis on matrix-matrix multiplication [18].

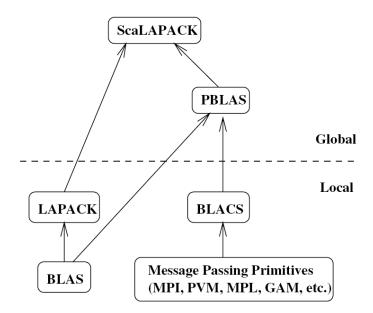

Because of their high performance, dense matrix kernels also have a widespread usage in parallel linear algebra. Besides, native parallel dense solver packages such as ScaLAPACK are also provided in public domain. To have a parallel dense solver library, communication libraries are required in addition to the kernels. BLACS, or Basic Linear Algebra Communication Subroutines provides point-to-point or collective communication subroutines.

ScaLAPACK is a library of high performance linear algebra routines for PC clusters (refer Section 1.2.5). It is based on LAPACK and PBLAS (a set of parallel version of BLAS) which uses BLACS for communication and calls the BLAS. Like LAPACK, the ScaLAPACK routines are based on block partitioned algorithms in order to minimize the frequency of data movement between different levels of the memory hierarchy. In the ScaLAPACK routines, all inter-processor communication occurs within the PBLAS and the BLACS. As it can be seen from Figure 1.2, libraries below the dashed line are serial, in other words, sequential libraries that does not require any communication among computers.

Figure 1.2: ScaLAPACK Software Hierarchy [1]

The goals of ScaLAPACK project are *efficiency*, so that the computationally intensive routines execute as fast as possible; *scalability* as the problem size and number of processors grow; *reliability*, including the return of error bounds; *portability* across machines; *flexibility* so that users may construct new routines from well-designed components; and *ease of use* [1].

Scalability demands that a program be reasonably effective (refer to Appendix A) over a wide range of numbers of processors. The scalability of parallel algorithms over a range of architectures and numbers of processors requires that the granularity of computation be adjustable. To accomplish this, block partitioned algorithms are

provided with adjustable block sizes [19].

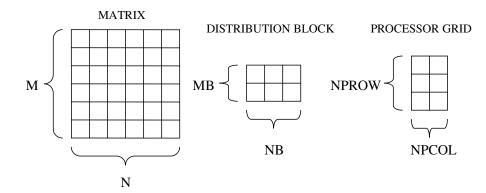

The performance of the ScaLAPACK drivers, are dependent to the performance of each computer in the cluster, computational workload assigned to each computer, data distribution type and block size. The ScaLAPACK software assumes that the user's input data has been distributed on a two-dimensional grid of processors according to the block cyclic data distribution (4.4.1.1.1). For a given number of processors, the parameters of this family of data distributions are the shape of the processor grid and the size of the block used to partition and distribute the matrix entries over the processor grid. These parameters affect the number of messages exchanged during the operation, the aggregated volume of data communicated, and the computational load balance [1].

#### 1.2.3.2.1 Cholesky Factorization in LAPACK

Cholesky factorization factors an  $N \times N$ , symmetric, positive-definite matrix A into the product of a lower triangular matrix L and its transpose, i.e.,  $A = LL^T$  (or  $A = U^T U$ , where U is upper triangular). It is assumed that the lower triangular portion of A is stored in the lower triangle of a two-dimensional array and that the computed elements of L overwrite the given elements of A. At the  $k^{th}$  step, the  $n \times n$  matrices A(k), L(k), and  $L^T(k)$  are partitioned, and the system is written as

$$\begin{bmatrix} A_{11} & A_{21}^T \\ A_{21} & A_{22} \end{bmatrix} = \begin{bmatrix} L_{11} & 0 \\ L_{21} & L_{22} \end{bmatrix} \begin{bmatrix} L_{11}^T & L_{21}^T \\ 0 & L_{22}^T \end{bmatrix} = \begin{bmatrix} L_{11}L_{11}^T & L_{11}L_{21}^T \\ L_{21}L_{11}^T & L_{21}L_{21}^T + L_{22}L_{22}^T \end{bmatrix}$$

(1.10)

where the block  $A_{11}$  is  $nb \times nb$ ,  $A_{21}$  is  $(n - nb) \times nb$ , and  $A_{22}$  is  $(n - nb) \times (n - nb)$ .  $L_{11}$  and  $L_{22}$  are lower triangular.

The block-partitioned form of Cholesky factorization may be inferred inductively as follows. If it is assumed that  $L_{11}$ , the lower triangular Cholesky factor of  $A_{11}$ , is known, the block equations can be rearranged as;

$$L_{21} \leftarrow A_{21} (L_{11}^T)^{-1} \tag{1.11}$$

and

$$\tilde{A}_{22} \leftarrow A_{22} - L_{21}L_{21}^T = L_{22}L_{22}^T \tag{1.12}$$

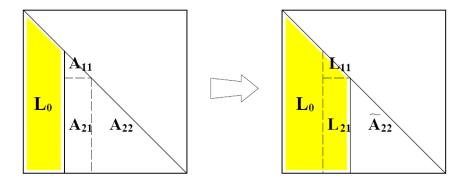

A snapshot of the block Cholesky factorization algorithm in Figure 1.3 shows how the column panel  $L^{(k)}$  ( $L_{11}$  and  $L_{21}$ ) is computed and how the trailing submatrix  $A_{22}$  is updated. The factorization can be done by recursively applying the steps outlined above to the  $(n - nb) \times (n - nb)$  matrix  $\tilde{A_{22}}$ .

Figure 1.3: A snapshot of block Cholesky factorization[2]

In the right-looking version of the LAPACK routine, the computation of the above steps involves the following operations:

1. **DPOTF2**: Compute the Cholesky factorization of the diagonal block  $A_{11}$ .

$$A_{11} \to L_{11} L_{11}^T \tag{1.13}$$

2. **DTRSM**: Compute the column panel  $L_{21}$ ,

$$L_{21} \leftarrow A_{21} (L_{11}^T)^{-1} \tag{1.14}$$

3. **DSYRK**: Update the rest of the matrix,

$$\tilde{A_{22}} \leftarrow A_{22} - L_{21}L_{21}^T = L_{22}L_{22}^T \tag{1.15}$$

#### 1.2.3.2.2 Cholesky Factorization in ScaLAPACK

The parallel implementation of the Cholesky factorization in ScaLAPACK proceeds as follows:

- 1. **PDPOTF2**: The processor  $P_i$ , which has the  $nb \times nb$  diagonal block  $A_{11}$ , performs the Cholesky factorization of  $A_{11}$ .

- $P_i$  performs  $A_{11} \rightarrow L_{11}L_{11}^T$ , and sets a flag if  $A_{11}$  is not positive definite.

- $P_i$  broadcasts the flag to all other processors so that the computation can be stopped if  $A_{11}$  is not positive definite.

- 2. **PDTRSM**:  $L_{11}$  is broadcast columnwise by  $P_i$  down all rows in the current column of processors, which computes the column of blocks of  $L_{21}$ .

3. **PDSYRK**: the column of blocks  $L_{21}$  is broadcast rowwise across all columns of processors and then transposed. Now, processors have their own portions of  $L_{21}$  and  $L_{21}^T$ . They update their local portions of the matrix  $A_{22}$ .

#### 1.2.3.3 Direct Solvers for Sparse Matrices

The resulting system of equations produced by the finite element method are generally sparse and in literature there is plenty of research on direct solution of sparse matrices.

One of the fundamental concepts in sparse matrix factorization is the elimination tree. The elimination tree is defined for any sparse matrix whose sparsity pattern is symmetric. For a sparse matrix of order n, the elimination tree is a tree on n nodes such that node j is the father (or parent) of node i if entry(i, j), j > i is the first entry below the diagonal in column i of the lower triangular factor. Similarly, node i is called as leaf (or descendant) of node j. Each node is connected with an edge.

For example, Sparse Cholesky factorization by columns can be represented by an elimination tree. This can either be a left-looking or a right-looking algorithm. Either way, the dependency between columns which will be updated and columns will be used for update, is determined by the elimination tree. If each node of the tree is associated with a column, a column can only be modified by columns corresponding to nodes that are descendants of the corresponding node in the elimination tree.

Even though they have different solution procedures and approaches in global, most of the popular sparse equation solvers are using dense matrix kernels for the core of computation. This is because of avoiding indirect addressing and trying to manipulate blocked algorithms for high performance purposes [11, 15, 16, 20].

One approach to using higher level BLAS in sparse direct solvers is a generalization of a sparse column factorization. Higher level BLAS can be used if columns with a common sparsity pattern are considered together as a single block or supernode and algorithms are termed column-supernode, supernode-column, and supernode-supernode depending on whether target, source, or both are supernodes. This approach is named as supernodal approach.

Sparse direct methods solve systems of linear equations by factorizing (described in Section 1.2.3) the coefficient matrix A. An ordering method which is interchanging the rows and/or the columns of sparse matrix and can be utilized with an elimination tree in order to minimize both the storage requirement and amount of computations performed. Sparse direct solvers usually have numerous distinct phases [12] that are summarized below:

- 1. An ordering phase that determines a factorization order which reduces both storage requirements and the number of floating-point operations required.

- 2. An analysis phase (which is sometimes referred to as the symbolic factorization step [15]) that the matrix structure is examined in order to determine the amount of storage for factorization and solution phases. Furthermore, elimination tree which governs the calculations during the factorization and subsequent solution phase is created. The tree is also used to schedule the parallel tasks, since the nodes of the tree can be viewed as representing computations and the edges representing transfer of data.

- 3. A numerical factorization phase that uses the elimination tree to factorize the matrix.

- 4. A triangular solution phase that performs forward elimination followed by back substitution using the computed factors at previous stages.

According to Dongarra et al. [11], three levels parallelism can be achieved in direct sparse solvers;

- System Level Parallelism; can be exploited by dividing the problem into subproblems that can be solved independently. Then the contributions of each problem form an interconnecting system problem which is quite smaller than the original problem.

- Matrix Level Parallelism; can be achieved by using the sparsity pattern of the coefficient matrix. Usually elimination trees are used for determining the independent computations.

- Sub-matrix Level Parallelism; can be achieved by performing series of dense matrix operations over sub-matrices. PBLAS and ScaLAPACK (refer to Section 1.2.3.2) can be used for this purpose.

In literature, there are numerous research on parallel direct solvers for sparse systems because of their robustness and guaranteed success over different types of sparse matrices resulting from different types of problems. Although they have slightly different strategies and performances, all of the modern sparse solvers are trying to take the advantage of dependency among the sparse data to be processed and utilize blocked dense solvers in lower levels of computation, allowing the exploitation of higher-level BLAS. Some state-of-art parallel sparse direct solvers will be discussed next.

SuperLU DIST, as the name implies, the distributed (parallel) version of SuperLU algorithm which uses supernodal approach for factorization. SuperLU DIST, utilizes a directed acyclic graph (elimination tree) to reduce the memory requirement and a static task scheduling according to the elimination tree. Right-looking formulation (described in 1.2.3) is used to carry out the elimination updates. Immediately after factorization of a block of columns (namely, supernode) corresponding to a node in the tree, data are sent to update blocks corresponding to ancestors in the tree [15,21,22].

MUMPS utilizes a multifrontal approach where the Gaussian eliminations are carried out on dense frontal matrices corresponding to children nodes in the elimination tree. The resulting Schur complements (condensed matrices) are thereupon sent for assembly to the parent nodes. Thus, the elimination structure utilized by MUMPS is called as assembly tree. MUMPS exploits parallelism arising from the sparsity in the matrix and parallelism available for dense matrices. Additionally, large computational tasks are divided into smaller subtasks to enhance parallelism. MUMPS uses a distributed dynamic scheduling technique that allows numerical pivoting and the migration of computational tasks to lightly loaded processors. Asynchronous communication is used to overlap communication with computation. By default, MUMPS automatically chooses the ordering algorithm depending on the packages installed, the size of the matrix, and the number of processors available [15,20].

These two solvers, MUMPS and SuperLU Dist are compared by various studies [15, 22]. According to the results of these studies, the block sizes occurring during factorization within SuperLU Dist were smaller than those utilized within MUMPS, giving less efficient use of the Level 3 BLAS kernels and hence generally produced slower factorization and solution speeds. On the other hand, it was also observed that efficiency of MUMPS dropped because of the memory problems and increasing communication overhead when the number of processors increased.

In the study conducted by Guermouche et al. [23] problems of multifrontal methods were discussed. They compared the effect of five different reordering algorithms, AMD [24], AMF [25], PORD [26], METIS [3], and SCOTCH [27], on the shape of the corresponding assembly trees, hence, their effects on the memory usage. The METIS [3] and SCOTCH [27] libraries produced wide, well balanced trees where the others produced very deep unbalanced trees with a large number of nodes. In terms of memory usage, deep unbalanced trees were found to be better than the wide ones. They concluded that, however, for parallel cases, the computational scheduling had to be considered since it also had a significant effect on the memory requirement. In conclusion, there are two main problems in multifrontal methods; they may require large memory space for incore storage which is not always possible. Secondly, their parallel efficiency depends on how the elimination trees are constructed.

TAUCS is another state-of-art parallel direct solver which is based on multifrontal supernodal sparse Cholesky factorization. The multifrontal supernodal method factors the matrix using recursion on the assembly tree. Each node in the tree is associated with a set of columns of the Cholesky factor L (unknowns in the linear system). The method works by factorizing the columns associated with all the columns associated with proper descendants of a parent node, then updating the coefficients of the unknowns associated with this node, and factorizing the columns of it. The updates and the factorization are performed using calls to the dense Level 3 BLAS kernels. TAUCS is currently used in Mathematica [14].

#### 1.2.4 Substructuring

Popular parallel direct sparse solvers like MUMPS and SuperLU are not explicitly performing a parallelization on system level [15, 22]. Their main concern is solving a linear system of equations as fast as possible. However, in finite element analysis, preprocessing and post-processing stages may take considerable amount of time especially with the enhanced speed of sparse solvers. Pre-processing stage involves the formation of element stiffness matrices and assembly of the structural stiffness matrix and load vectors. Similarly, after the solution of the system, results are used in post-processing stage in which element forces and stresses are computed. Within this framework, substructuring can be used to extend the parallelism to cover pre-processing and post-processing computations of a direct solution of finite element analysis problem.

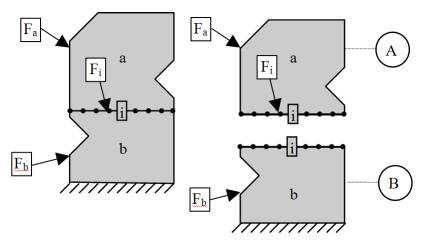

Another advantage of substructuring is that it can reduce the number of equations to manageable size by dividing a structure into non-overlapping substructures. The element stiffness matrices of each element that lies on each substructure is assembled to generate the substructure equations. By treating each substructure as a super-element with many internal and external (interface) nodes, and using static condensation (refer to Section 2.3.2), the equations of substructure are reduced to a form involving only the interface nodes of that particular substructure. The reduced substructure equations can then be assembled to obtain the overall system equations involving only the interface unknowns of the various substructures. The number of these system equations is much less compared to the total number of unknowns. The solution of the system equations gives values of the interface unknowns of each substructure. The known interface nodal values can then be used as prescribed interface conditions for each substructure to solve for the respective internal nodal unknowns.

In substructure based parallel solution methods (explained in Section 1.2.4.3), the performance of the solution is very sensitive to the way the structure is partitioned into substructures. The optimum substructuring [6] for a particular structure should;

- guarantee that the parallel solution time is less than the serial solution time

- balance the workloads for each processor

- minimize the communication among the processors

#### 1.2.4.1 Partitioning

All the requirements mentioned in Section 1.2.4, for an optimum substructuring to analyze a structure, increase the complexity of the substructuring problem. Hence, several partitioning approaches are developed. These methods can be examined in two groups; static partitioning and dynamic partitioning.

Static partitioning methods are preferred when the workload and communication requirements are known before the actual computation initiates. Kurç [6] classified these methods in four groups as geometric, topological, graph based, and hybrid methods. Geometric based methods divide the domain by using the geometric properties of each object, i.e. nodal coordinates, elements etc. Recursive Coordinate Bisection Method [28], Unbalanced Recursive Bisection Method [29], and Recursive Inertial Bisection [30] can be given as examples for this group. Second group is topological based methods in which the connectivity information among the objects are used for partitioning. Greedy Algorithm [31], Bandwidth Reduction Approach [32], and Octree Partitioning [33] are examples to this group. Third group is graph based algorithms. In such methods, graph models of a computation are prepared and all the partitioning computations are performed on these models. Examples for this group are Recursive Spectral Bisection Method [34] and Multilevel Approaches [35].

Dynamic partitioning methods can be used in cases that arise where it is either impossible to calculate the computational loads initially or the computational requirement varies during solution in an unpredictable way. One way to handle this problem is using the new information about the computational loads to repartition the mesh (Scratch-Remap Algorithms [36,37]). However, it should be guaranteed that the new partition is similar to the previous one, otherwise, huge amounts of data should be transferred among processors. The other option is transferring nodes among the processors in order to balance the load by shifting the interfaces (Diffusion Algorithms [38]). In this case, interface shifting might cause considerable increase in the interface size which will increase the communication volume. Therefore, having a transfer algorithm that will balance the workload while keeping the edge-cut as small as possible is very important for such methods [6].

#### 1.2.4.2 Workload Balancing

Workload imbalance is one of the most important phenomenon that reduces the efficiency of any parallel solution algorithm. When direct solution methods are utilized, the number of operations required to solve a linear system of equations can be predicted before the solution initiates. Hence, in literature there are various methods that attempts to balance the computational loads of processors that participated in solution.

Yang and Hsieh [39] proposed an iterative partition optimization method for direct substructuring. After finding the initial partitions, the number of arithmetic operations required for condensation is computed using the symbolic factorization. The weights of the elements within a substructure are adjusted according to the operation counts found for each substructure. Later the partitions are modified by using the partitioning packages JOSTLE [40] and METIS [3]. While METIS [3] restarts the partitioning from the scratch, JOSTLE [40] has the feature to adjust the partitions from the previous iterations. Iteratively refining the partitions using JOSTLE [40] generally provides balanced partitions with less iteration. Refining the partitions by moving small number of elements between the partitions shows similarities to the dynamic partitioning that tries to minimize the number of objects moved between partitions.

Kurç and Will [41] proposed a workload balancing scheme for the condensation of the substructures. METIS [3] partitioning library is utilized for the initial partitioning of the nodal graph representation of a structure. Later the node weights of partitions are adjusted according to the estimated operation counts. The PARMETIS [42] library is used for repartitioning according to the adjusted node weights. The diffusion and scratch-remap repartitioning algorithms are investigated. It was concluded that scratchremap produced computationally more balanced substructures. Moreover, the number of interface equations was smaller with scratch-remap algorithm compared to diffusion algorithm. They also stated that time spent during workload balancing iterations was insignificant compared to the improvements obtained in the condensation times. Test results indicated that workload balancing iterations reduce the total solution timings considerably.

#### 1.2.4.3 Substructure based Solution Methods

Substructuring offers several advantages such as enabling the parallelization of every step of the solution, from formation of element stiffness matrices to the computation of element forces and stresses and minimizing the communication by requiring data transfer only during the solution of interface equations. These features make them very suitable for PC Clusters that have relatively low communication speed with respect to their computation power. Besides, with the use of direct solvers, they may enhance the solution of systems that have multiple loading conditions.

Duff and Scott [43] applied substructuring methods to multi-fronts scheme. In such a case, instead of creating elimination trees, the underlying domain was partitioned into subdomains and frontal decompositions were performed on each domain separately. In conclusion, they stated that domain partitioning could reduce operation counts, factorization and solution times. Besides, they observed that costs of communication and interface problem solution did not dominate the overall solution time and they obtained reasonable speed-ups.

Farhat et al. [44] implemented substructuring for parallel finite element solution. Their method initiated by partitioning the structure into subdomains. For each subdomain, the stiffness matrix and force vectors were formed by first numbering the internal degrees of freedom and then the interface degrees of freedom. The internal equations were transferred to the interfaces by static condensation. For the solution of interface problem, the row-wise  $LDL^T$  decomposition was utilized. They observed that efficiency of the method is dropping with the increase in the number of processors. They, however, stated that with the increase in problem size the efficiency drop could be compensated.

Bjørstad et al. [45] implemented a direct solution algorithm, based on processing substructures in parallel. Proposed algorithm was to divide substructures into smaller substructures in a multilevel fashion. At any given level in this procedure, the unknowns were divided into two disjoint sets, the internal variables and the external (interface) variables. Before the algorithm proceeds to the next level, all internal variables were eliminated by static condensation. At the next level the retained variables from the previous level were again split into two sets and this process repeated until one reached the highest level where all remaining variables in the problem would be in the internal set. An elimination tree was constructed before the computation and according to this tree, pool of tasks where information about all the tasks including execution schedule and time estimates were formed. With this approach they ensured a symmetric and well load balanced substructures.

In another study, Baugh and Sharma [46] implemented the domain decomposition method to solve linear equations on a network of workstations. They compared five different algorithms based on direct, iterative, and hybrid methods. In the direct approach, the partitions were first condensed with a direct static condensation method and a direct solution was performed at the interface. In the iterative approach, they solved the system globally by using two different versions of the conjugate gradient method. The hybrid approach used direct condensation and parallel and sequential versions of conjugate gradient method for the interface problem. The test results showed that the iterative solution methods were outperformed by the direct solution methods for the solution of a rectangular membrane problem on a workstation environment that was connected with an ordinary LAN.

Fulton and Su [47] implemented the substructuring method on a shared memory parallel computer. They used active column storage scheme to store the substructure level stiffness matrix. During the condensation, the internal equations were first numbered and then the interface equations. The interface stiffness matrix was kept in the shared memory and the contribution of each substructure was assembled to the interface stiffness matrix according to the correct location determined during the renumbering phase. In order to balance the various computational loads for the condensation phase of each substructure, more processors were assigned to the substructures which were estimated to require more computation. The proposed approach performed much better than the parallel global solution algorithm.

The other paper by Synn and Fulton [48] searched the answers for the following issues: direct versus iterative solution, the optimum number of processors for the parallel matrix decomposition, workload balancing, and which solution type to be utilized for a particular problem. They recommended the direct solution methods even though iterative methods were more scalable. The load balancing during condensation step was provided by assigning more processors to the subdomains estimated to have larger number of equations and bandwidths. Moreover, they derived operation count equations to estimate the optimum number of processors and to choose whether to use the global solution instead of substructure based solution.

An object-oriented database structure was proposed by Hsieh et al. [49] that could be used in parallel finite element codes for structural engineering applications. They preferred substructuring approach with direct solvers in their code which utilized the parallel matrix library developed by Modak et al. [50]. In this library, the linear solution algorithm was based on active column matrices that utilized Cholesky decomposition method. Within the view of test cases, small speed-ups were obtained for the factorization phase during the interface solution. Moreover, the forward and back substitution times remained constant as the number of processors increased.

Escaig et al. [51] presented a multilevel domain decomposition method with a direct solver for the interface problem. They first partitioned the structure in such a way that the number of subdomains was larger than the number of processors. During the parallel solution, the subdomains were condensed by the first available processor. This way it was possible to balance the workload among the processors. However, as the number of subdomains increased, the size of the interface problem also increased. They tested their algorithm both in shared and distributed memory architectures. Although they obtained reasonable results for shared memory architectures, the performance dropped as the number of processors increased for distributed architectures.

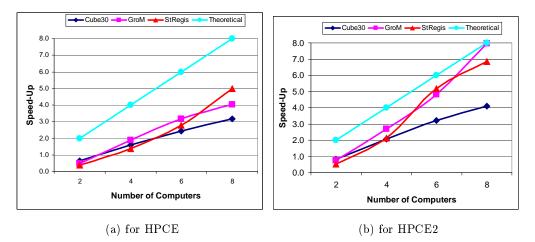

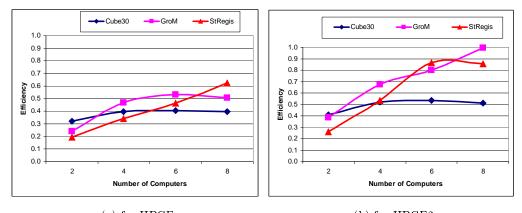

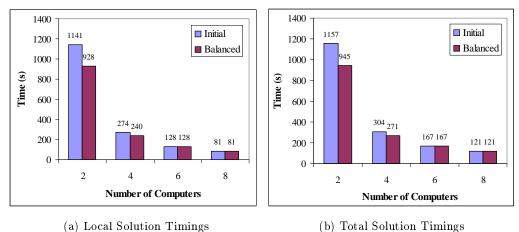

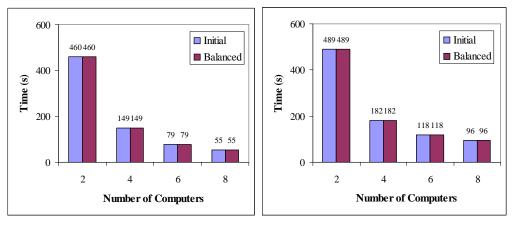

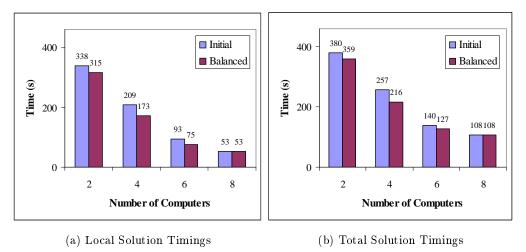

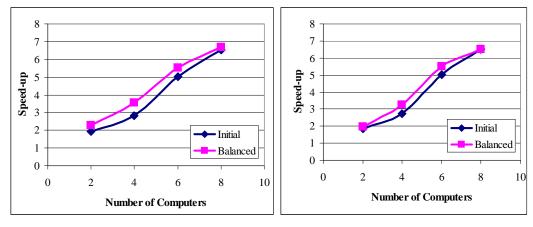

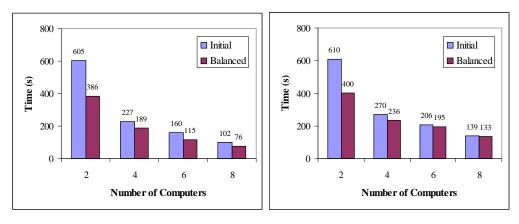

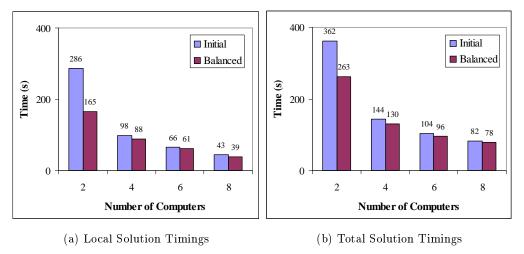

An analytical study performed by Nikishkov et al. [52] examined the parallel performance of the domain decomposition method with LDU based condensation and solution algorithms. They first calculated the number of operations and the communication volumes and estimated the solution times of each algorithm for a square domain problem. Then, they compared the time estimations with the actual values. The predicted values mostly agreed with the actual ones (<5%) and good parallel efficiency 95% with 6 processors, 85% with 8 processors, was obtained.