# PERFORMANCE OF PARALLEL DECODABLE TURBO AND REPEAT ACCUMULATE CODES IMPLEMENTED ON AN FPGA PLATFORM

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

ENES ERDÍN

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2009

Approval of the thesis:

# PERFORMANCE OF PARALLEL DECODABLE TURBO AND REPEAT ACCUMULATE CODES IMPLEMENTED ON AN FPGA PLATFORM

submitted by ENES ERDIN in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan ÖZGEN<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>                                     |  |

|---------------------------------------------------------------------------------------------------------------------------|--|

| Prof. Dr. İsmet ERKMEN<br>Head of Department, <b>Electrical and Electronics Engineering</b>                               |  |

| Assoc. Prof. Dr. Ali Özgür Yılmaz<br>Supervisor, <b>Electrical and Electronics Engineering</b><br><b>Department, METU</b> |  |

| Examining Committee Members                                                                                               |  |

| Examining Committee Members:                                                                                              |  |

| Prof. Dr. Yalçın TANIK<br>Electrical and Electronics Engineering Dept., METU                                              |  |

| Assoc. Prof. Dr. Ali Özgür YILMAZ<br>Electrical and Electronics Engineering Dept., METU                                   |  |

| Asst. Prof. Dr. Behzat A. ŞAHİN<br>Electrical and Electronics Engineering Dept., METU                                     |  |

| Asst. Prof. Dr. Çağatay CANDAN<br>Electrical and Electronics Engineering Dept., METU                                      |  |

| Güzin KURNAZ, Ph.D.<br>Digital Design Engineer, TÜBİTAK-SAGE                                                              |  |

| Date:                                                                                                                     |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: ENES ERDİN

Signature :

# ABSTRACT

# PERFORMANCE OF PARALLEL DECODABLE TURBO AND REPEAT ACCUMULATE CODES IMPLEMENTED ON AN FPGA PLATFORM

Erdin, Enes M.S., Department of Electrical and Electronics Engineering Supervisor : Assoc. Prof. Dr. Ali Özgür Yılmaz

September 2009, 75 pages

In this thesis, we discuss the implementation of a low latency decoding algorithm for turbo codes and repeat accumulate codes and compare the implementation results in terms of maximum available clock speed, resource consumption, error correction performance, and the data (information bit) rate. In order to decrease the latency a parallelized decoder structure is introduced for these mentioned codes and the results are obtained by implementing the decoders on a field programmable gate array. The memory collision problem is avoided by using collision-free interleavers. Through a proposed quantization scheme and normalization approximations, computational issues are handled for overcoming the overflow and underflow issues in a fixed point arithmetic. Also, the effect of different implementation styles are observed.

Keywords: Repeat-Accumulate Codes, Turbo Codes, Parallel Decoder, FPGA, Xilinx

# ÖZ

### PARALELLEŞTİRİLMİŞ TURBO VE TEKRARLA-BİRİKTİR KODLARININ FPGA PLATFORMU ÜZERİNDE GERÇEKLENMESİ VE BAŞARIMI

Erdin, Enes Yüksek Lisans, Elektrik-Elektronik Mühendisliği Bölümü Tez Yöneticisi : Doç. Dr. Ali Özgür YILMAZ

Eylül 2009, 75 sayfa

Bu tezde turbo kodlar ve tekrarla-biriktir kodları için düşük gecikmeli bir kod çözme algoritmasının donanımsal tasarımı ve tasarım sonuçlarının saat hızı, kaynak tüketimi, hata düzeltme yeteneği ve veri hızı açısından incelmesi gerçekleştirilmiştir. Çözücüdeki gecikmeyi azaltmak için paralelleştirilmiş çözücü mimarisi önerilmiş ve bahsi geçen kodlar için sonuçlar, alan programlanabilir kapılar dizisinde (FPGA) incelenmiştir. Hafiza çakışma problemi, çakışmasız karıştırıcılar kullanılarak önlenmiştir. Ayrıca önerilen nicemleme ve düzgeleme yaklaşımlarıyla sabit noktalı hesaplamalarda oluşabilecek alttaşma ve üsttaşma sorunları da çözülmüştür.

Anahtar Kelimeler: Tekrarla biriktir kodlar, Turbo kodlar, Paralleştirilmiş Çözücü, FPGA, Xilinx

To My Family, To My Wife

# ACKNOWLEDGEMENTS

I am most thankful to my supervisor Assoc. Prof. Dr. Ali Özgür Yılmaz for sharing his invaluable ideas and experiences on the subject of my thesis. I learnt too much from his innovative ideas. I feel myself privileged to have had him as a mentor.

I would like to extend my thanks to all lecturers at the Department of Electrical and Electronics Engineering, who greatly helped me to store the basic knowledge onto which I have built my thesis.

I want to thank to Çağlar Kılcıoğlu who was a good friend in the laboratory. He had done great job in writing our paper.

I would like to thank to Onur Dizdar for his patience in debugging the testbed environment which took many hours of him.

I am very grateful to TÜBİTAK-SAGE for providing tools and other facilities throughout the production of my thesis.

I would like to forward my appreciation to all my friends and colleagues who contributed to my thesis with their continuous encouragement.

I would like to express my deep gratitude to my family, who has always provided me with constant support and help.

Special thanks to my wife for all her help and showing great patience during my thesis.

# **TABLE OF CONTENTS**

| ABSTR  | ACT     |                                                   |                                          | iv   |  |  |

|--------|---------|---------------------------------------------------|------------------------------------------|------|--|--|

| ÖZ     |         |                                                   |                                          | v    |  |  |

| DEDIC  | ATON .  |                                                   |                                          | vi   |  |  |

| ACKNO  | OWLEDO  | GEMENTS                                           | \$                                       | vii  |  |  |

| TABLE  | OF CON  | ITENTS .                                          |                                          | viii |  |  |

| LIST O | F TABLE | ES                                                |                                          | xi   |  |  |

|        |         |                                                   |                                          |      |  |  |

| LIST O | F FIGUR | RES                                               |                                          | xii  |  |  |

| CHAPT  | ERS     |                                                   |                                          |      |  |  |

| 1      | INTRO   | DUCTION                                           | ۸                                        | 1    |  |  |

| 2      | TURB    | O CONCE                                           | РТ                                       | 3    |  |  |

|        | 2.1     | TURBO                                             | CODES                                    | 5    |  |  |

|        |         | 2.1.1                                             | Turbo Code Encoder Structure             | 5    |  |  |

|        |         | 2.1.2                                             | Convolutional Encoding                   | 6    |  |  |

|        |         | 2.1.3                                             | Interleaving                             | 8    |  |  |

|        |         | 2.1.4                                             | Turbo Code Decoder Structure             | 8    |  |  |

|        | 2.2     | TURBO-                                            | LIKE CODES                               | 10   |  |  |

|        |         | 2.2.1                                             | Low Density Parity Check Codes           | 10   |  |  |

|        |         | 2.2.2                                             | Repeat Accumulate Codes                  | 11   |  |  |

|        |         | 2.2.3                                             | Repeat Accumulate Code Encoder Structure | 11   |  |  |

|        |         | 2.2.4                                             | Repeat Accumulate Code Decoder Structure | 13   |  |  |

| 3      | TESTB   | ED SETU                                           | Р                                        | 16   |  |  |

|        | 3.1     | ML-402                                            | FPGA Evaluation Board                    | 16   |  |  |

|        | 3.2     | Software Used For Debugging and Implementation 20 |                                          |      |  |  |

|       | 3.2.1                | Xilinx ISE and XST                               | 20 |

|-------|----------------------|--------------------------------------------------|----|

|       | 3.2.2                | Implementation steps of an ISE project           | 21 |

|       |                      | 3.2.2.1 Synthesis                                | 21 |

|       |                      | 3.2.2.2 Translate Process                        | 21 |

|       |                      | 3.2.2.3 Mapping Process                          | 22 |

|       |                      | 3.2.2.4 Place and Route Process                  | 22 |

|       | 3.2.3                | BitGen                                           | 23 |

|       | 3.2.4                | ChipScope Analyzer                               | 23 |

|       | 3.2.5                | MATLAB                                           | 23 |

|       | 3.2.6                | MODELSIM                                         | 24 |

| 3.3   | Overall S            | System Setup                                     | 26 |

|       | 3.3.1                | System                                           | 26 |

|       | 3.3.2                | LFSR Noise Generator                             | 27 |

|       | 3.3.3                | Error Counter                                    | 33 |

|       | 3.3.4                | UART Module                                      | 33 |

| IMPLE | MENTAT               | ION ISSUES                                       | 36 |

| 4.1   | Channel              | Model                                            | 36 |

| 4.2   | BCJR De              | ecoder                                           | 37 |

| 4.3   | FPGA In              | nplementation of BCJR Decoder                    | 41 |

|       | 4.3.1                | Center to Top Algorithm                          | 42 |

|       | 4.3.2                | Observation Quantization                         | 42 |

|       | 4.3.3                | Addition and Subtraction Operations              | 46 |

|       | 4.3.4                | Node $(\alpha, \beta)$ Metric Normalization      | 48 |

|       | 4.3.5                | <i>max</i> <sup>*</sup> Approximation            | 49 |

| 4.4   | Memory               | Collision Free Interleavers                      | 50 |

| 4.5   | Encoder/             | Decoder Design of Parallel Decodable Turbo Codes | 53 |

|       | 4.5.1                | Encoder Design                                   | 53 |

|       | 4.5.2                | Decoder Design                                   | 54 |

| 4.6   | Encoder/<br>cumulate | Decoder Design of Parallel Decodable Repeat Ac-  | 56 |

4

|       |       | 4.6.1     | Encoder De                           | sign                   | 56 |

|-------|-------|-----------|--------------------------------------|------------------------|----|

|       |       | 4.6.2     | Decoder De                           | sign                   | 56 |

| 5     | RESUL | TS FOR T  | THE PERFORMANCE OF PARALLEL DECODERS |                        |    |

|       | 5.1   | Implemen  | ntation Resul                        | ts                     | 58 |

|       | 5.2   | Simulatio | on Results .                         |                        | 60 |

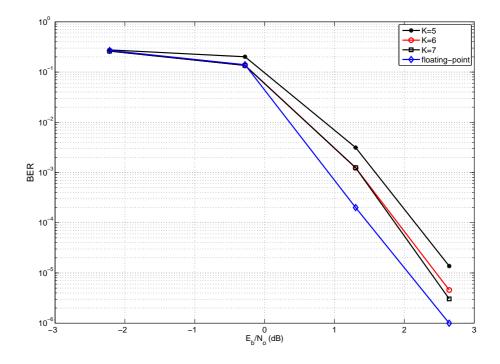

|       |       | 5.2.1     | Bit Size (K)                         | Selection              | 60 |

|       |       | 5.2.2     | NormMax                              | Selection              | 61 |

|       |       | 5.2.3     | Interleaver                          | Size                   | 64 |

|       |       | 5.2.4     | Memory Co                            | omplexity              | 67 |

|       |       |           | 5.2.4.1                              | PDTC memory structure  | 67 |

|       |       |           | 5.2.4.2                              | PDRAC memory structure | 68 |

|       |       | 5.2.5     | Transmissio                          | on Bit Rate            | 68 |

| 6     | CONCL | LUSIONS   |                                      |                        | 71 |

| REFER | ENCES |           |                                      |                        | 74 |

# LIST OF TABLES

# TABLES

| Table 2.1 | Rate, Threshold and Shannon threshold comparison for RA codes          |    |

|-----------|------------------------------------------------------------------------|----|

| [12]      |                                                                        | 14 |

| Table 3.1 | Some LFSR generator polynomials with varying size of shift registers.  | 29 |

| Table 3.2 | The registers and their meaning in the design of the UART transmitter. | 34 |

| Table 3.3 | The registers and their meaning in the design of the UART transmitter. | 35 |

| Table 4.1 | Xilinx ISE synthesis report for parallel turbo encoder                 | 54 |

| Table 4.2 | Xilinx ISE synthesis report for parallel turbo encoder                 | 56 |

| Table 5.1 | Implementation results for PDTC decoder using log-MAP decoders         | 59 |

| Table 5.2 | Implementation results for PDTC decoder using max-log-MAP de-          |    |

| coder     | rs                                                                     | 59 |

| Table 5.3 | Implementation results for PDRAC decoder using log-MAP decoders        | 60 |

| Table 5.4 | Another approach to PDTC decoder implementation : Implementa-          |    |

| tion r    | results for PDTC decoder using log-MAP decoders [2]                    | 60 |

| Table 5.5 | Another approach to PDTC decoder implementation : Implementa-          |    |

| tion r    | results for PDTC decoder using max-log-MAP decoders [2]                | 60 |

| Table 5.6 | Performance comparison of the proposed decoder structures              | 67 |

| Table 5.7 | Comparison of the proposed decoder structures                          | 69 |

# **LIST OF FIGURES**

# FIGURES

| Figure 2.1                                                              | Encoder Structure of a Turbo Code                                                                                       | 5  |  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----|--|

| Figure 2.2                                                              | re 2.2 Parallelized Turbo Code Encoder Structure                                                                        |    |  |

| Figure 2.3                                                              | A Rate 1/2 Convolutional Encoder                                                                                        | 6  |  |

| Figure 2.4 The FSM representation of the convolutional encoder shown in |                                                                                                                         |    |  |

| Figure                                                                  | e 2.3 each bit arrival( <i>I</i> ) contributes to a state transition and reveals                                        |    |  |

| two ou                                                                  | utput bits (0) which are shown in $I/OO$ format [9]                                                                     | 7  |  |

| Figure 2.5                                                              | Trellis description of a convolutional encoder. The initial and the                                                     |    |  |

| final s                                                                 | tates are the all-zero state [9]                                                                                        | 7  |  |

| Figure 2.6                                                              | Turbo Decoder                                                                                                           | 9  |  |

| Figure 2.7                                                              | Parallelized Architecture for turbo code decoder                                                                        | 10 |  |

| Figure 2.8                                                              | Repeat Accumulate code encoder                                                                                          | 11 |  |

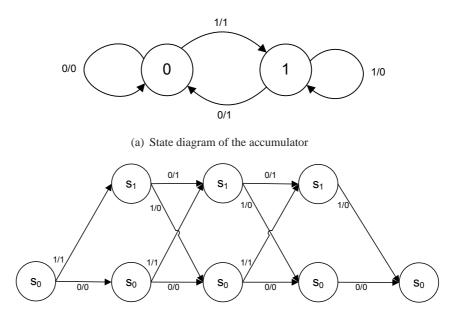

| Figure 2.9                                                              | State transition and trellis diagram of the accumulator                                                                 | 12 |  |

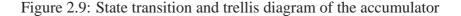

| Figure 2.10                                                             | Parallelized Repeat Accumulate Encoder                                                                                  | 13 |  |

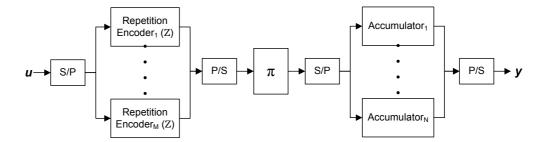

| Figure 2.11                                                             | Iterative RA Code Decoder with APP algorithm                                                                            | 14 |  |

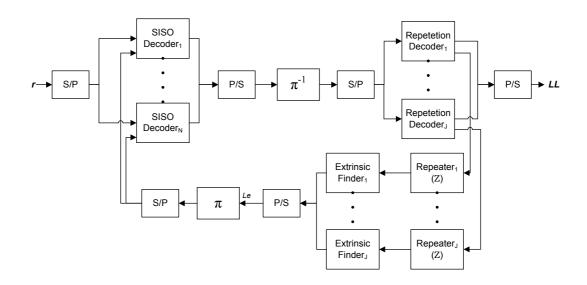

| Figure 2.12                                                             | 2 Parallelized Repeat Accumulate Decoder                                                                                | 15 |  |

| Figure 3.1                                                              | The structure of a CLB in a Xilinx FPGA                                                                                 | 17 |  |

| Figure 3.2                                                              | The effect of dividing logic with flip-flops, pipelining                                                                | 18 |  |

| Figure 3.3                                                              | ML402 board used in the study                                                                                           | 19 |  |

| Figure 3.4                                                              | A generalized system model for testing the decoders                                                                     | 26 |  |

| Figure 3.5                                                              | An LFSR with seed 0101100011001101                                                                                      | 28 |  |

| Figure 3.6                                                              | The 16 <sup>th</sup> ,14 <sup>th</sup> ,13 <sup>th</sup> ,10 <sup>th</sup> bit are added and the result is forwarded to |    |  |

| the be                                                                  | ginning of the register                                                                                                 | 28 |  |

| Figure 3.7 With a clock trig the found result is registered as the first bit of the            |

|------------------------------------------------------------------------------------------------|

| register, the content of the register is shifted once towards right                            |

| Figure 3.8 Normally distributed noise generation by LFSR                                       |

| Figure 3.9 The hystogram of a pseudo-random Gaussian noise generator ob-                       |

| tained by collection of 10000 samples                                                          |

| Figure 3.10 A histogram of a noise sequence generated by MATLAB's randn                        |

| function                                                                                       |

| Figure 3.11 The bit alignment in a UART transmission                                           |

| Figure 4.1 A general block diagram of a communication system                                   |

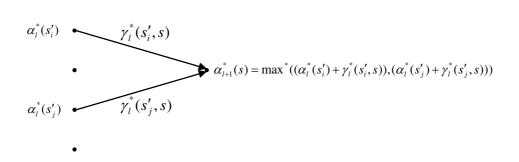

| Figure 4.2 Forward recursion in calculation of $\alpha_{l+1}^*(s)$                             |

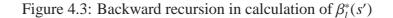

| Figure 4.3 Backward recursion in calculation of $\beta_l^*(s')$                                |

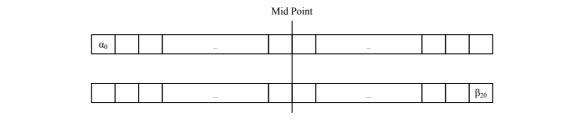

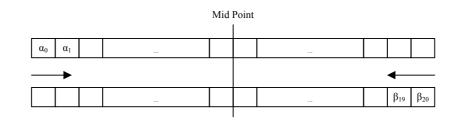

| Figure 4.4 $\alpha$ and $\beta$ values are initialized initially at time 0                     |

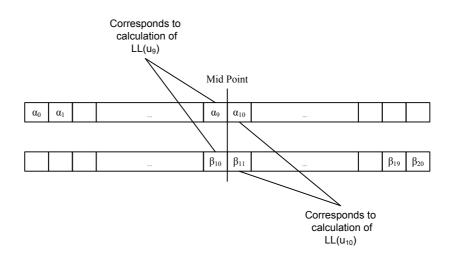

| Figure 4.5 $\alpha$ and $\beta$ values are computed independently and in a recursive manner 43 |

| Figure 4.6 $\alpha$ and $\beta$ values first meet at time 10 and at this time all information  |

| for computing the first LL values are ready                                                    |

| Figure 4.7 An illustration of how a memory collision may happen in an en-                      |

| coding process                                                                                 |

| Figure 4.8 RCS-random interleaver is a good approach for memory collision                      |

| freee interleaver design including the good properties of S-random inter-                      |

| leavers [9]                                                                                    |

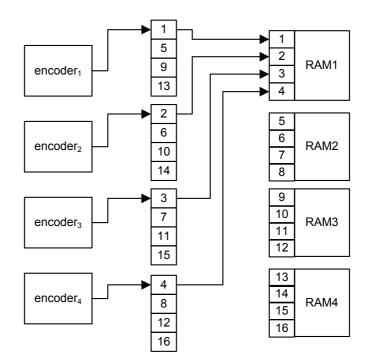

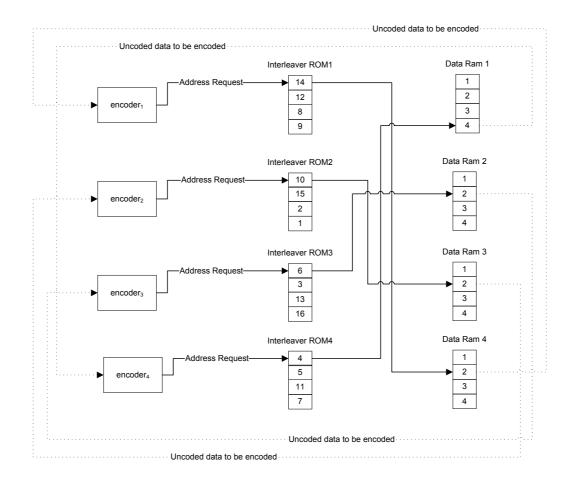

| Figure 4.9 The interleaver operation taking place in the FPGA. Each address                    |

| request is decoded, the requested RAM and the corresponding location is                        |

| found and the requested data is forwarded to the demanding encoder 53                          |

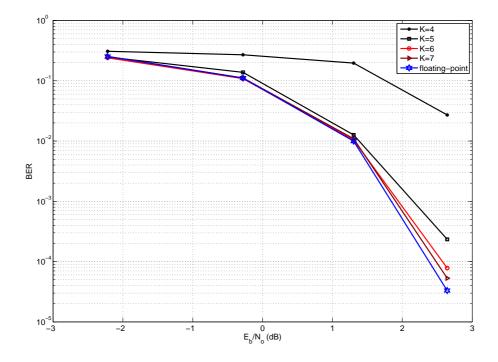

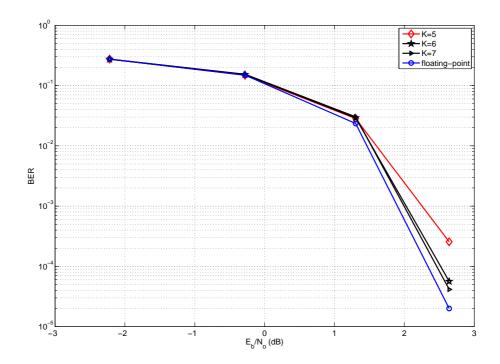

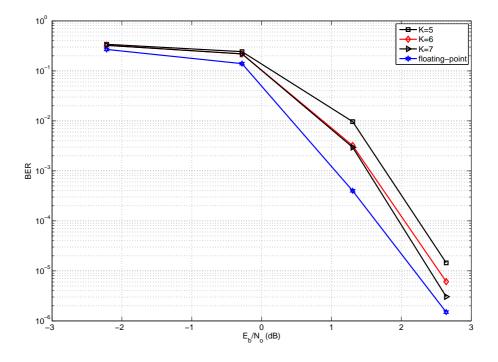

| Figure 5.1 SNR vs BER for log-MAP based turbo decoder. 4 iterations for                        |

| 2000 frames of 160 bits through 4 parallel MAP decoders 61                                     |

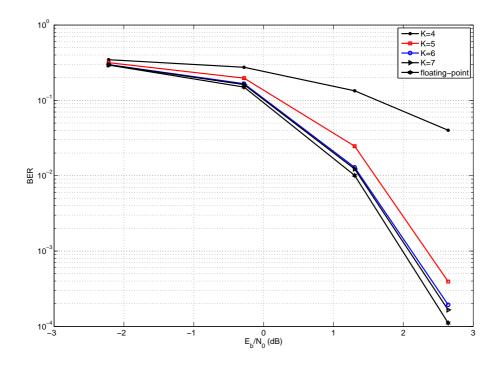

| Figure 5.2 SNR vs BER for max-log-MAP based turbo decoder. 4 iterations                        |

| for 2000 frames of 160 bits through 4 parallel MAP decoders                                    |

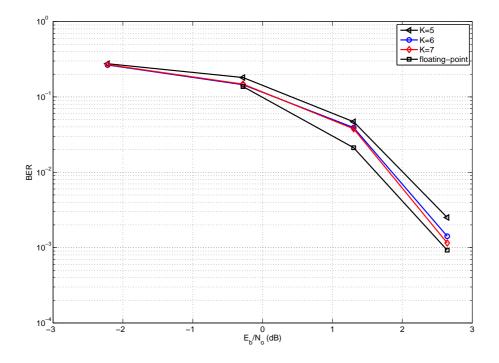

| Figure 5.3 SNR vs BER for PDRAC decoder. 8 iterations for 2000 frames of                       |

| 160 bits through 4 parallel MAP decoders                                                       |

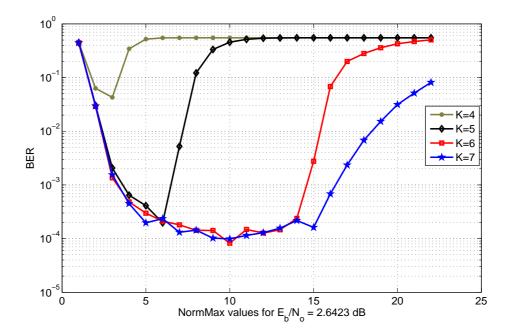

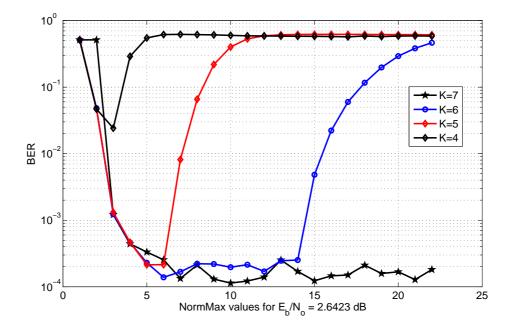

| Figure 5.4 NormMax values for log-MAP turbo code decoder for different       |    |

|------------------------------------------------------------------------------|----|

| bit representations. The average of 6000 packets of 160 data bits with 4     |    |

| parallel decoders.                                                           | 63 |

| Figure 5.5 NormMax values for max-log-MAP turbo code decoder for differ-     |    |

| ent bit representations. The average of 6000 packets of 160 data bits with   |    |

| 4 parallel decoders                                                          | 63 |

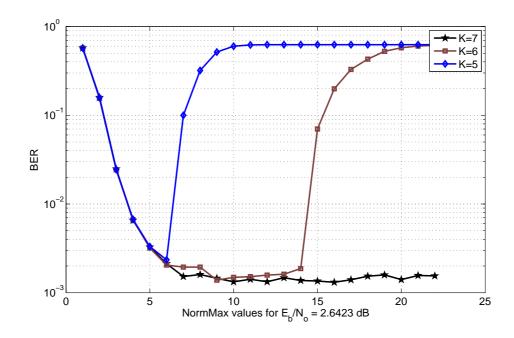

| Figure 5.6 NormMax values for repeat accumulate codes for different bit rep- |    |

| resentations. The average of 6000 packets of 160 data bits with 4 parallel   |    |

| decoders.                                                                    | 64 |

| Figure 5.7 SNR vs BER for RA with 4 parallel sub-decoders decoding 1344      |    |

| bits in total with 8 iterations.                                             | 65 |

| Figure 5.8 SNR vs BER for turbo decoder with 4 parallel max-log-MAP de-      |    |

| coders decoding 1344 bits in total with 4 iterations                         | 65 |

| Figure 5.9 SNR vs BER for turbo decoder with 4 parallel log-MAP decoders     |    |

| decoding 1344 bits in total with 4 iterations.                               | 66 |

| decoding 1544 bits in total with 4 iterations                                | 00 |

# **CHAPTER 1**

### **INTRODUCTION**

In wireless communication systems channel coding is one of the most important tools. By the help of strong channel codes the quality in communication can be highly improved. By recent developments and improvements in communication systems technology, reliable and high speed data transfer became an important issue. From satellite communications to wireless local area networks(WLAN), large bandwidth and high speed transfers with a minimum error probability are desired.

Since Shannon determined the maximum achievable rates for AWGN channels, many studies in channel coding have been conducted. One of the most significant studies conducted in this area is the study of Gallager introducing low-density parity check (LDPC) codes in 1963. However, LDPC codes were not popular due to their iterative docoders were impractical at those times. The most important study which ushered a new era in coding theory was introduced by Berrou et al. with the name turbo codes [4]. Right after the introduction of the turbo structure, this idea is applied to other coding schemes and this yielded to invention of many classes of codes, broadly called turbo-like codes. The family of Repeat-Accumulate codes is a well-known type of turbo-like codes [5].

Although turbo and repeat accumulate codes are efficient in terms of bit error ratio (BER) vs. signal to noise ratio (SNR) performance, their decoders introduce large decoding delays due to their iterative decoding scheme. As the number of iterations are increased, a better error performance is usually obtained but the time of decoding increases in proportion to the iteration number. In order to decrease such huge latencies various ideas have been implemented like building many decoders operating in

parallel which is a widely used technique in literature. This approach significantly decreases the decoding delay with almost no loss in terms of BER [9]. For further decrease in decoding latency, certain algorithms such as center to top algorithm are also utilized inside the marginal a-posteriori (MAP) decoders [13].

Parallelization is a powerful tool for decreasing the decoding latency. While constructing a decoder structure operating in parallel memory collision problems can occur. Decoders operating in parallel attempt accessing information residing in the same memory segment. Such problems can be avoided with the implementation of suitable collision free interleavers as studied in the thesis.

In this thesis, our aim is observing the performance of parallelized encoder and decoder structures for turbo and repeat accumulate codes implemented on an FPGA platform and investigating the parameters which affect their operation. The performances of the decoders will be evaluated in terms of BER performance, FPGA resource usage, maximum achievable FPGA clock speed, and data throughput.

The outline of the thesis can be summarized as follows. In Chapter 2, a general description on turbo and repeat accumulate codes is given. We explain the basic encoder and decoder structures for these codes and give a brief description for building decoders and encoders operating in parallel. In Chapter 3, the environment in which the implementations are carried on is described. In Chapter 4, we explain the implementation steps for obtaining a MAP decoder that is later used for constructing parallelized decoders. In Chapter 5, we demonstrate the SNR vs. BER performances of the proposed decoder architecture and discuss the implementation results. Also, the maximum throughput of the decoders are calculated in this chapter. Finally in Chapter 6, we conclude the thesis and provide suggestions for future work.

# **CHAPTER 2**

### **TURBO CONCEPT**

The noisy-channel coding theorem, stated by Claude Shannon in 1948 [16], opened a new era in communications. The theorem basically states that, one can transmit information reliably at information rates (R) smaller than a specific rate referred to as the channel capacity (C). The theorem implies that information transmission with arbitrarily small rate is possible with the conditon R < C. The theorem was the starting point of the Information Theory. As the years passed, many studies for obtaining the minimum available error rate over a noisy channel are conducted as attempts for achieving the Shannon Limit.

In order to enjoy a reliable communcation for wireless systems *Forward error correction (FEC)* schemes are used. FEC codes are designed to improve the decisions that the receiver makes by giving it enough information to correct some of the errors that the channel introduced into the signal. The technique is adding redundancy to the information by channel coding.

Channel coding can be thought as a process in which redundant bits are added to a series of bits which are to be transmitted to some receivers. The aim in this redundancy operation is to mitigate the effect of the noise on the transmitted signal. Since these bits are processed by some rule, the receiver side is expected to correct the erroneous bits as much as possible by the help of these redundant bits. There are many different coding techniques for different kind of situations. Bursts of errors, thermal noise or fading channel effects are some examples for these situations [19]. Channel codes can be broadly divided into two categories: Block Codes : Repetition codes, BCH codes, Reed Solomon codes are the most well-known codes in this category. These codes operate under fixed-size bit blocks. The messages of k bits are mapped to codewords of length n bits. The code rate, R, for an (n, k) block code is then given by

$$R = \frac{k}{n}.$$

(2.1)

For k bits of information there exist n - k bits of redundancy.

• **Convolutional Codes** : They can operate under varying size of blocks. Their encoders and decoders are usually less complex compared to that of block codes. This type of codes constitute the basis of this thesis.

After the genesis of Information theory, a number of capacity achieving codes have been invented. The oldest of these codes as first introduced by Gallager in his doctoral thesis in 1963 [8]. The class announced by Gallager was the low density parity check (LDPC) codes, but these codes did not gain popularity up until the invention of turbo codes. Berrou et al. introduced turbo codes [4] in 1993. Turbo codes attracted the attention of the researchers with its good error performance. After these developments a return to LDPC codes occured and people restarted studying them. The class of repeat-accumulate codes introduced in [5] is the result of these efforts.

Turbo codes enjoyed a grand fame with its good error performance and reasonable complexity. After a few years of its invention almost everyone in the area of coding theory agreed that it is a pioneering achievement in the area. As a result, it is accepted as among the coding techniques for next generation wireless communication systems such as Wideband CDMA (WCDMA) and 3<sup>rd</sup> Generation Partnership Project (3GPP) for IMT-2000.

Another important class of codes are repeat-accumulate (RA) codes. RA codes which is a special type of LDPC codes, is first introduced by Divsalar et al. in [5]. RA codes are known for their low complexity decoder and good error performance.

In this chapter brief information about turbo codes and repeat accumulate codes will be given. The parallelization idea for the encoders and the decoders of these codes also will be explained. The parallel decoder and encoder structure under investigation will be presented.

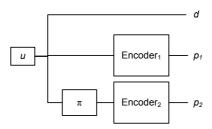

Figure 2.1: Encoder Structure of a Turbo Code

#### 2.1 TURBO CODES

#### 2.1.1 Turbo Code Encoder Structure

In general the encoder structure of a turbo code is parallel concatenation of two encoders. Figure 2.1 depicts the structure of a turbo code encoder. The information bits, a sequence of bits u, are passed through encoders and bypassed. d is the bypassed version of u which is also called as the systematic part.  $p_1$  is the parity bit sequence which is obtained by passing u through an encoder, a convolutional encoder in our case, and called *parity bits* throughout this thesis. The block  $\pi$  represents the interleaver block by which the turbo codes gains its power.  $p_2$  represents the parity bits obtained by encoding of "interleaved" data bits which is called the *interleaved parity bits*. The codes Berrou et al. used was convolutional codes and their scheme was called parallel concetenated convolutional codes (PCCC).

For mitigating the encoding decoding latency parallelization of encoders and decoders are suggested in the literature. The parallelized form of the encoder structure is not too much different from the usual form. The parallelized form of turbo encoders can be seen in Figure 2.2. At this point the most crucial subject is the design of a collision-free interleaver block which will be handled in the preceding sections. For ease of demonstration u,  $p_1$ ,  $p_2$  and  $\pi$  can be thought as matrices of size  $[n \ge N]$ , where n is the codeword length passed through a single encoder.

Figure 2.2: Parallelized Turbo Code Encoder Structure

#### 2.1.2 Convolutional Encoding

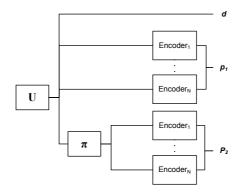

In convolutional encoding the output bit streams are generated with a state transition matrix and an input bit stream. Their operation principle can be thought as a finite state machine in which *n* bits of input corresponds to *k* bits of output. k/n results in the rate, *R*, of the encoder. Algorithmically there are two main parts of a convolutioanal encoder, a shift register and binary adder blocks. The number of locations in the shift register is indicated by  $m_i$  and the constraint length of the encoder is defined as  $max(m_i + 1)$  [19]. Another important parameter in convolutional codes is *minimum free distance*,  $d_{free}$ , defined as the minimum Hamming distance between any two output sequences. Figure 2.3 depicts a rate 1/2 convolutional encoder with

Figure 2.3: A Rate 1/2 Convolutional Encoder

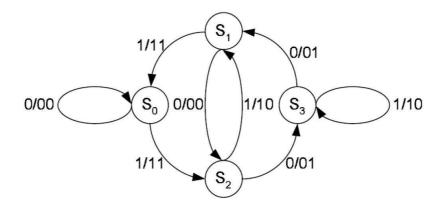

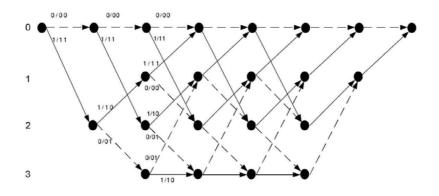

$m_1 = 2$ , with one information bit *u* and two coded output bits  $c_1$  and  $c_2$ . Since the shift register is composed of 2 storing elements, this encoder has  $2^2 = 4$  states. Its constraint length is 3 and minimum distance is 5. We already stated that the convolutional encoders can be thought as finite state machines (FSM) Figure 2.4 explains

how they can be treated as state machines. Figure 2.5 shows the trellis diagram of

Figure 2.4: The FSM representation of the convolutional encoder shown in Figure 2.3 each bit arrival(I) contributes to a state transition and reveals two output bits (O) which are shown in I/OO format [9]

the encoder and shows how the transitions may occur over time. The encoder used as an example in Figures 2.3, 2.4 and 2.5 will be the default encoder in the encoder of parallel decodable turbo codes (PDTC).

Figure 2.5: Trellis description of a convolutional encoder. The initial and the final states are the all-zero state [9]

After the encoding of a frame is finished, the final state of the encoder can be adjusted to be in a known state for getting a better performance in decoding, as shown in Figure 2.5. In general both the initial and the final states of the encoder is adjusted to be the all-zero state where all of the shift registers are zero. If the final state is also wanted to be controlled then *termination bits* must be added to the frame. The length of the termination bits must be  $m_i$  at least.

Many convolutional encoders do not employ feedback, and thus can be thought as finite impulse response (FIR) filters. Recursive convolutional encoders have a feedback component which makes the encoder behave as a infinite impulse response (IIR) filter. Our example is a recursive convolutional encoder with feedback.

#### 2.1.3 Interleaving

Interleaving means changing the place of a bit in the sequence to a newer place such that the initial and the final location of the bits are related to each other with some rule. In wireless channels, transmission suffers from fading problems, which results in bursts of errors. A well defined interleaver decreases the probabability of error by distributing the erroneous consecutive bits far from each other. So at the output of the interleaver the errors seem to be independent of each other. Besides, interleaving enhances performances of turbo codes by reducing the number of low weight codewords [6].

The *S*-*random* interleaver will be the interleaver type to be used in the designs. The steps for producing an *S*-*random* interleaver can be given as follows [1]:

- 1. All the mappings occur randomly with equal chance of selection

- 2. The randomly selected order is accepted only if it is in a distance greater than *S* for all of the *S* previously selected orders. Otherwise, it is not accepted and a new random order is generated, until this condition is satisfied.

The parameter *S* is predetermined and usually satisfies  $S \leq \sqrt{K/2}$ , where *K* is the interleaver size [6]. *S*-random interleavers have good spreading characteristics compared to other interleavers and provide good BER performance when used with convolutional codes.

### 2.1.4 Turbo Code Decoder Structure

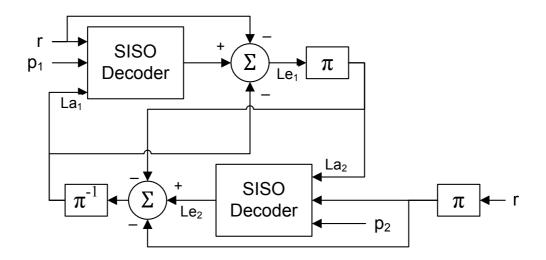

In the original turbo code study the scientists used a modified version of the Bahl et al. (known as BCJR [14]) algorithm [4]. The iterative turbo decoder can be seen

Figure 2.6: Turbo Decoder

recursive systematic convolutional (RSC) codes. r represents the channel observation corresponding to the systematic data,  $p_1$  corresponding the parity bit produced by the use of systematic part and  $p_2$  to the parity bit produced by the use of the interleaved version of the systematic data. The soft in soft out (SISO) decoders can be any decoder. Soft output Viterbi algorithm (SOVA) decoders and the BCJR-MAP decoders are two commonly used decoders among many. In our study a MAP decoder implemented by the BCJR algorithm will be used.

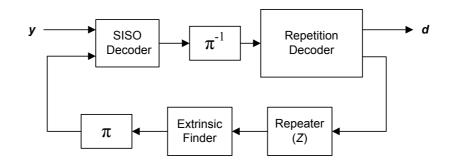

Decoding latency is a big issue in iterative decoding of turbo codes. In order to decrease the latency, a parallelization of decoders may be proposed likewise in the encoder part [9]. The parallelized decoder architecture for a turbo code is given in Figure 2.7. The number N of parallel processing SISO decoders decrease the decoding latency approximately N-folds. Although there is a small performance loss as N increases as observed in [9], the significant latency enhancement justifies parallelization.

Figure 2.7: Parallelized Architecture for turbo code decoder

#### 2.2 TURBO-LIKE CODES

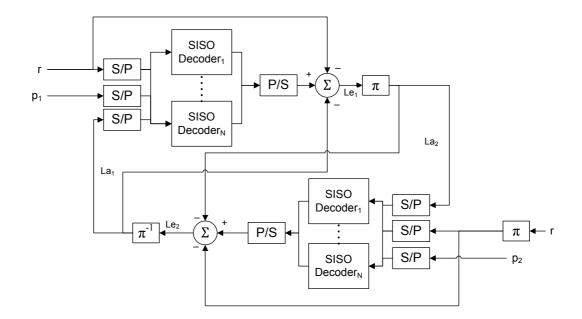

In this section parallelization of the repeat accumulate codes are discussed. Repeat accumulate (RA) codes are considered to be a sub-class of low density parity check (LDPC) codes. Although there are studies on the parallelization of turbo codes, the same can not be told for repeat accumulate codes.

#### 2.2.1 Low Density Parity Check Codes

Low density parity check (LDPC) codes introduced by Gallager [8] are the first known channel coding family that performs close to the Shannon limit. When Gallager introduced this type of coding in 1960's, researchers did not give importance to these codes because of its large decoding complexity. After the invention of turbo codes a return to Gallager's study occured. Nowadays, many studies on analysis of LDPC codes of different variants are taking place.

#### 2.2.2 Repeat Accumulate Codes

Repeat Accumulate codes are first introduced by Divsalar et al. in 1998 [5]. After the introduction of turbo coding principle Divsalar used this concept and invented the RA codes. An RA code can be decoded iteratively and its iterative decoding performance is considerably good despite its low complexity, whereas its coding is simple and the decoder structure is suboptimal [12]. Additionally, RA codes achieve the ultimate Shannon limit -1.592 dB as the code rate goes to zero on the AWGN channel.

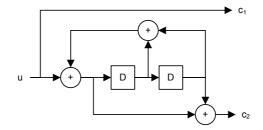

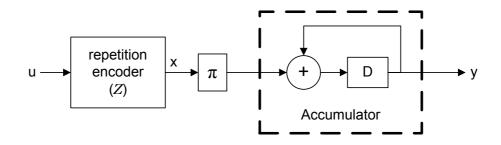

#### 2.2.3 Repeat Accumulate Code Encoder Structure

The RA encoder consists of concatenation of a Z-times repeating repetition encoder and an accumulator. If the information bits are transmitted, this type is called systematic RA code. Sometimes the repetition part works in an irregular way, that is, it repeats each bit  $Z_i$  times where  $Z_i$  is a variable parameter for each uncoded bit at time *i*, on operation. Irregular repeat accumulate (IRA) codes are formed in this way. IRA codes are actually better codes which excite the curiosity of the coding theorists.

The basic encoder structure of a non-systematic RA code can be seen in Figure 2.8. The information bits are repeated Z times and forwarded to an accumulator. Before the accumulator there exists an interleaver which is one of the most important part in the code since the existence of the interleaver brings the power of the RA codes, as in turbo codes.

Figure 2.8: Repeat Accumulate code encoder

The accumulator is the part which makes the RA codes simpler compared to other

coding schemes like LDPC or Turbo codes. The accumulator, as it can be seen in Figure 2.8, performs a modulo-2 adding operation. It sums up the current bit with the previous bit and produces what is called a parity bit. From one perspective it can be thought as a 2-state convolutional encoder with transfer function 1/(1 + D) whose state transition diagram is given in Figure 2.9(a) and trellis diagram in Figure 2.9(b). From another perspective it can be seen as a block code with inputs  $[x_0, \ldots, x_{n-1}]$  and

(b) Trellis diagram of the accumulator

outputs  $[y_1, \ldots, y_{n-1}]$  whose equations can be given as

$$y_0 = x_0$$

$$y_1 = x_0 + x_1$$

$$y_2 = x_0 + x_1 + x_2$$

:

$$y_{n-1} = x_0 + x_1 + x_2 + \dots + x_{n-1}$$

The performance derivations of RA codes are done by using its block code behavior but its opearating principle is easy to understand with its convolutional form.

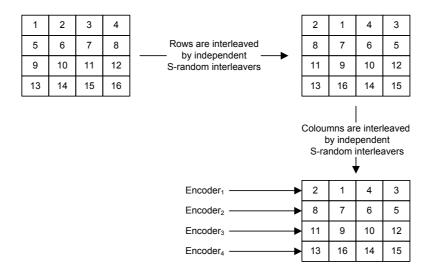

One way for enabling parallelization at the receiver is by the parallelization of the encoders. A parallelization scheme for the encoders can be seen in Figure 2.10. A

number M of repeaters are processing in parallel and forwarding the results to an interleaver. An accumulator cluster consisting of N parallel processing accumulators encodes the repeated bits.

Figure 2.10: Parallelized Repeat Accumulate Encoder

#### 2.2.4 Repeat Accumulate Code Decoder Structure

RA codes can be decoded using variable techniques [15]. Majority-logic (MLG) and bit-flipping (BF) decoding are two examples for hard decision decoding. A posteriori probability (APP) decoding and iterative decoding based on belief propagation (IDBP) which is also known as sum-product algorithm (SPA) are soft decision decoding techniques. Weighted BF decoding is a compromise between hard decision and soft decision decoding. Techniques including hard decision decoding are out of our scope since soft decision decoding algorithms usually provide better performance. The SPA algorithm is the most widely used decoding technique for decoding of RA codes. In the SPA decoding, Tanner graphs [18], introduced by Tanner, are used by the information passing algorithm, generally known as belief propagation. In this study we will focus on using APP decoding by using a BCJR-MAP decoder.

Theorem 3.2 stated in [12] says that if Z goes to infinity then the SNR threshold value,  $\gamma_Z$ , which is the lowest bit SNR value for error free transmission, approaches *log2*, that is, RA codes achieve the Shannon limit for the AWGN channel. Table 2.1 shows a comparison between Z, the achievable SNR threshold value for error-free communication and the corresponding Shannon limit for the related rate. Decoding latency is again an issue for the iterative decoding of RA codes. In order to decrease the effect of this inherent latency, a parallelized architecture for the decoder is pro-

Figure 2.11: Iterative RA Code Decoder with APP algorithm

Table 2.1: Rate, Threshold and Shannon threshold comparison for RA codes [12]

|   | Ζ        | R   | $\gamma_Z$ (dB) | Shannon (dB) |

|---|----------|-----|-----------------|--------------|

| - | 3        | 1/3 | 0.792           | -0.495       |

|   | 4        | 1/4 | -0.052          | -0.764       |

|   | 5        | 1/5 | -0.480          | -0.963       |

|   | 6        | 1/6 | -0.734          | -1.071       |

|   | ÷        | :   | :               | :            |

|   | $\infty$ | 0   | -1.592          | -1.592       |

posed. The decoder block can be seen in Figure 2.12. N SISO decoders operating in parallel first decode the incoming data sequence since this part was encoded by the accumulator in the transmitter. The likelihoods generated by SISO decoders are passed through a deinterlaver and decoding continues with the M number of repetition decoders. If there are termination bits in the received sequence, which improves the error performance of the code N must be the same as that of in the encoder part (as it can be remembered there were N number of parallel encoders in the PDRAC encoder). On the other hand, M has no need to be the same as M in the encoder part, because only the repeated bits are related to each other. As M increases the decoding latency decreases significantly however, this time memory operations must be handled carefully. For the subsequent iterations decoded bits taken from the repetition decoders are passed through repeaters and then an extrinsic finder calculates the a priori probabilities for the next iteration of the SISO decoders.

Figure 2.12: Parallelized Repeat Accumulate Decoder

# **CHAPTER 3**

# **TESTBED SETUP**

In this thesis the motivation was basically the hardware realization and comparison of parallelized turbo and repeat accumulate decoders. Initially the study was a continuation of a previous thesis [1]. In this previous study an integrated testbed environment was implemented. However, because of some unresolvable and unexpected problems occured later on the testbed, the designs are carried on a stand-alone operating environment. The characteristics of a real environment is simulated on the FPGA platform.

# 3.1 ML-402 FPGA Evaluation Board

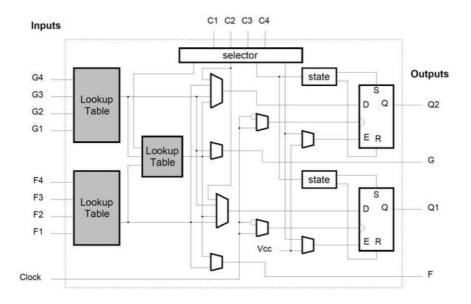

FPGAs are *reconfigurable logic devices* composed of smaller logic blocks. The building blocks of the FPGA are called *Configurable Logic Blocks* (CLB). A CLB (denominated as *Slice* in Xilinx<sup>1</sup>), shown in Figure 3.1, is the smallest building block of a Xilinx FPGA and for all of Xilinx FPGAs the CLB structure is the same <sup>2</sup>. A slice is composed of two four-input LUTs, six various size multiplexers, and two flip-flops (FFs). Although the logic operations are done with gates in the schematic designs, these gates are embedded into the LUTs in the hardware. When the inputs of the LUTs are excited, the output yields a result which is adjusted to yield the same result as the logic circuits would yield in the schematic design.

All of the logic blocks are connected to each other with programmable switches.

<sup>&</sup>lt;sup>1</sup> To get more information about the famous FPGA manufacturer visit www.xilinx.com

<sup>&</sup>lt;sup>2</sup> This structure will change after the not yet manufactured Virtex6 and Spartan6 products

Figure 3.1: The structure of a CLB in a Xilinx FPGA

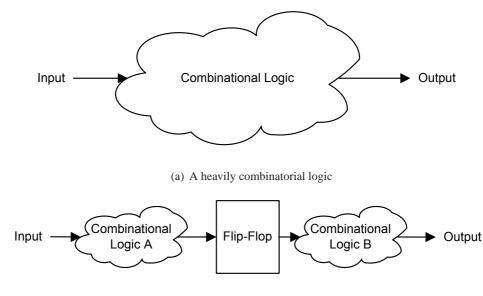

If there is a relation between slices then these switches will be ON, else OFF. The results of the LUTs can be multiplexed to the slice flip-flops in the case of a need for storing the result. One other important role that flip-flops introduce to the design is pipelining. Pipelining is the most powerful tool for obtaining a fast operating module. Since FPGA is formed by transistors each transistor has a certain delay in response to excitements. If large combinatorial logical blocks are used then these delays can reach tremendeous levels. If these large logic cells are analyzed well and partitioned into smaller blocks by placing flip-flops in between, these partitions will enhance the operation speed of the design. Figure 3.2(a) and Figure 3.2(b) shows this situation. If the large logical block is divided into smaller blocks A and B, with the necessity that the block A does not need the result coming from block B instantaneously, delays will decrease and maximum available clock speed will increase. In this case the output of the design is postponed by one clock period.

Another important block that is available in FPGAs is the block RAM, shortly BRAM. A BRAM in a Xilinx FPGA consists of 18x1024 bits<sup>3</sup>. By cascading these RAMs in parallel or in serial one can obtain RAMs of different sizes. The advantage

<sup>&</sup>lt;sup>3</sup> This size of BRAMs are the same for all Xilinx FPGAs

(b) A heavily combinatorial logic divided into smaller pieces with FFs

Figure 3.2: The effect of dividing logic with flip-flops, pipelining

of RAMs is that they are cheaper compared to slices and for storing purposes they provide a larger area. However, their operating speed is slower than that of slices.

Some FPGAs also include embedded microprocessors, for example, some Xilinx FPGAs include PowerPC cores. By the help of well picked peripherals it is easy to convert a microprocessor into a fully operating microcontroller. Besides, Xilinx MicroBlaze and Picoblaze are available as soft processor blocks, for the FPGAs which do not include PowerPC. As explained before, since FPGAs are very flexible devices in terms of logical operations, a processor composed of slices can be easily embedded into an FPGA. The advantage of such a solution is that, FPGAs without hard processors are cost effective. The disadvantage of it is, a soft core processor consumes some of the resources of the FPGA so available number of logic blocks decreases.

FPGAs also include additional blocks such as clock management blocks which can be used for multiplying/dividing clocks and/or mitigating the clock skews, dedicated multi-gigabit input/output ports, input/output (I/O) buffers those are compatible with many electrical standards such as LVTTL, LVDS, LVPECL etc., dedicated fast binary multipliers and so on.

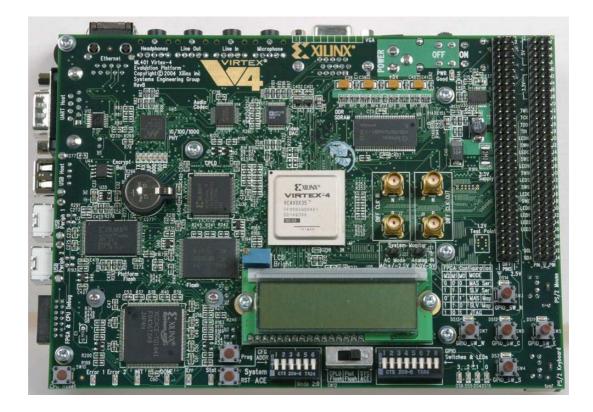

The board we used in designing the encoders and decoders was ML-402 Virtex4

Evaluation Board, shown in Figure 3.3. This board carries a Xilinx Virtex4 SX35 FPGA on it which can be thought to be an average capacity FPGA compared to others in the industry. Besides containing an FPGA, the ML-402 board contains other chips which can be used extensively for many different applications.

Figure 3.3: ML402 board used in the study

**DDR SDRAM :** The board includes an external 64 MB of DDR SDRAM using two Infineon HYB25D256160BT-7 chips. Each chip has 16 bits wide data port and two of them form a 32 bit data bus capable of running up to 266 MHz [11]. In the presence of a microprocessor these RAMs can be used for external data storage in stand-alone operations. Besides, these RAMs can be used as the processor memory which includes instructions in the presence of a soft microprocessor core.

**ZBT Synchronous SRAM :** The board contains a 256K x 36 bit synchronous ZBT RAM. The ZBT RAM provides a high speed low-latency external memory to the FPGA. This RAM can also be used for temporary external storage.

10/100/1000 Tri-Speed Ethernet PHY : The board contains a Marvell Alaska

PHY device operating at 10/100/1000 Mbps. By the use of a small porocessor and an ethernet controller the board can be reached through ethernet connection. One application can be incorporating the device into a local area network and reaching to it over ethernet connection.

**Differential Clock Input And Output With SMA Connectors :** High precision clock signals can be fed to FPGA by the use of  $50 \Omega$  SMA connectors. This functionality allows the FPGA to be fed by function generators. For example a demodulator output can be connected to the board, hence, further decoding process can be applied.

**RS-232 Port with Direct FPGA connection :** The ML-402 board contains an DB-9 serial port allowing the FPGA communicate with another device using serial data. An interface chip changing the voltage-levels are also included. The RS-232 serial port is one of the most widely used communication protocol and is known for its low-weight receiver/transmitter structure. In the thesis RS232 is commonly used for simulation purposes. The FPGA communicated with a PC through this port and the PC interpreted the results coming from the FPGA.

**Compact Flash and System ACE:** The board contains a Xilinx System ACE Compact Flash (CF) configuration controller. Through the JTAG port both the hardware and the software data can be downloaded to the CF. Maximum eight configuration images on a single CF card can be supported by SystemACE controller. By the help of switches available on the board, the address of each configuration can be selected and then System ACE controller loads the FPGA with that configuration. Besides being used as a configuration storage, a CF can also be used as a FAT filesystem storage device, i.e. harddrive.

#### 3.2 Software Used For Debugging and Implementation

#### 3.2.1 Xilinx ISE and XST

Xilinx ISE (Integrated Synthesis Environment) is the Integrated Development Environment (IDE) designed by Xilinx as a graphical user interface (GUI) for synthesizers. Xilinx synthesis tools (XST) is one of the synthesizers developed by Xilinx for complete synthesis and implementation of an FPGA project. The free version of ISE which is called the Webpack Edition supports a limited number of Xilinx FPGAs which are generally small in size. The unlimited version supports all of the FPGAs fabricated by Xilinx.

#### **3.2.2** Implementation steps of an ISE project

The implementation steps of a Xilinx project is divided into steps. Each step has certain inputs and outputs.

#### 3.2.2.1 Synthesis

By synthesis, "logic synthesis" is meant and it is an important step before implementation. Since FPGA design is a hardware process unlike compilers, these tools are named as synthesizers. The Synthesis operation basically converts a hardware description language (HDL) into register transfer level (RTL) composed of logic blocks like gates related to the design architecture. Another job done in the synthesis level is the optimization of the design. Optimization is done in a way that the synthesis tool either wipes out unused signals and entity ports, or it reduces the number of gates if two or more gates do exactly the same job. In XST, optimization of the design can be limited by special built-in constraints. For example, a general issue about this topic is that a two signal exactly created by the same logic will be optimized by XST by deleting one of these signals. However, these two signals will survive by setting the "remove equal logic" constraint accordingly.

#### 3.2.2.2 Translate Process

Translate process is the first step in the implementation process. The translate process produces a Xilinx native generic database (NGD) file which includes all of the netlists and design constraint information for implementation. A netlist is the combination of the blocks such as counters, adders, multipliers, comparators so on and connections between them. This process combines these pieces of information in a way that the logic is mapped into the target FPGA.

#### 3.2.2.3 Mapping Process

This step follows the translate process. The mapping process takes the previously created NGD file, runs a design rule check (DRC) over this file and maps the logic into the FPGA-specific hardware blocks. If one or more of the constraints is not applied properly, an error will pop up at this step and report that the constraint is not applicable. For example, if a buffer compatible with low-voltage differential signaling (usually called as LVDS buffer) is instantiated in an FPGA project its differential ports must be tied accordingly since these ports are connected to deterministic pin locations. However, if mistakenly the pin locations for that LVDS buffer is tied into irrelevant pin locations the synthesis process will not issue any error since the LVDS buffer instantiation is done in a correct way. Additionally, the translate process will not issue an error too since synthesis is fine and the "declaration syntax" of the pin locations are also correct. In the mapping process the software will check whether the LVDS receiver input pins are suitably placed or not. Since the LVDS pins are dedicated for each LVDS buffer, the mapping process will issue an error because of the failure in the constraints of the location of the LVDS pins and the implementation process will stop. The result of a successful map process will be written in a Xilinx native circuit description (NCD) file.

### 3.2.2.4 Place and Route Process

The place and route (shortly called as PAR) process is executed after the mapping process finishes and takes a mapped NCD file and places and routes the design. This process can be thought as an auto-router like in a printed-circuit board design software. Since the blocks and the constraints are known from the previous mapping process, it tries to connect all blocks in accordance with the netlist and the constraints. This process places all of these FPGA blocks in such a way that all limitations are satisfied, all I/O pins are connected, and the design will not go into an erroneus state with the specified clock speed. The output of this process is an NCD file suitable for

the operation of BitGen software.

### 3.2.3 BitGen

BitGen is a programming file generator for Xilinx FPGAs. After the implementation process finishes this software takes the NCD file and produces a .bit file which is suitable for programming an FPGA. If the programming finishes successfully, the FPGA will act in the way it is wanted by the HDL code.

### 3.2.4 ChipScope Analyzer

ChipScope is an advanced real-time debugging and verification tool designed by Xilinx. The ChipScope tool embeds special low-level soft core blocks into the design or into the netlist of the FPGA in order to track the signal changes. After PAR finishes, these blocks are ready to send data to the PC via a special port called the JTAG port. These cores, can be adjusted by software to be triggered in real time at certain conditions. When the set conditions are met, the states of the selected signals are examined and stored for a period of time. When the desired number of samples are taken these values are sent to the PC and the states of the signals are observed by the help of a GUI.

BRAMs of the FPGA are used for storing the signals. A maximum of 255 signals can be observed for a maximum of 16384 samples. Of course these are the achievable maxima allowed by the software. If the FPGA is not a large one, large Chipscope blocks are impossible to embed because of resource limitations.

#### **3.2.5 MATLAB**

MATLAB is used in various phases of the study. Since it provides a high level programming environment, a code can be changed and tried in minutes by the help of this software. It also provides a visual interface into the variables so that, by the help of the naked eye most of the problems can be seen and solutions can be produced. MATLAB is used firstly for the implementation of the encoders and the decoders. By

verifying that the results of the encoders and decoders are as desired, the discretized (fixed-point rather than floating-point) versions of them are written and simulated. After this step, the FPGA implementation and simulation is carried on in an easier way. It must be noted that any HDL is low level compared to any of the programming or scripting languages like C, C++, MATLAB since HDL deals with RTL. For example, an algorithm designed in a programming language in a few hours can be fully simulated on a HDL platform over weeks. The benefit of MATLAB can easily be seen. Another situation MATLAB was used is the generation of look-up tables. The approximations performed to decrease the complexity of the designs are also simulated in MATLAB, so that, the designs continued in a more confident way. After programming the FPGA with the implemented decoders, MATLAB is also used for to observe how the decoders operate on the FPGA. A controller module written in the FPGA was listening the commands transmitted from MATLAB through RS232 and was returning information such as the bit error rate, the frame error rate, the SNR, and the number of decoded packets. Such received information were processed in MATLAB, and illustrative results and plots were obtained.

# 3.2.6 MODELSIM

Modelsim is an advanced simulation and debugging tool for ASIC and FPGA projects provided by Mentor Graphics which is one of the leaders in the electronic design automation (EDA) industry. ModelSim recently started supporting many hardware description languages (HDL) including VHDL, Verilog HDL, SystemC, SystemVerilog. ModelSim has 3 major distributions, ModelSim SE, ModelSim PE, and ModelSim LE. Special distributions are also distributed for FPGA vendors. ModelSim provides ModelSim XE (Xilinx edition) for Xilinx. ModelSim XE is distributed with 2 licenses, one is a free but limited license and a full license which must be purchased from Xilinx. The full version is 100 times faster than the free version and the free version also additionally slows down if the HDL code is more than 1000 lines. In order to use ModelSim with ISE and a Xilinx FPGA a compiled form of the Xilinx FPGA blocks (these blocks are FPGA specific blocks that only the FPGA vendor may distribute the simulation models) must be available. Basically, ModelSim compiles a HDL code into a form that is suitable for the operation of ModelSim. In order to use the HDL code in consistence with the FPGA specific block, the compiled version of the Xilinx blocks must be added to the library of the ModelSim.

ModelSim is a very helpful software for debugging a project with its well-designed GUI. The best approach for debugging a code is simulating the design module by module. Writing successful testbenches are important at this step. The integration of modules to each other will be less painful after successful tests.

Simulations can be divided into two main parts. One is functional simulation and the other is timing simulation.

A functional simulation simulates the behavior of the code. The timing in the simulation will be perfect compared to the real world behavior. As the name implies, this simulation simulates the functionality of the HDL code. No optimizations or simplifications occur, you see what you write. This kind of simulation is the fastest since no gate delays, IOB delays, clock skews, and setup-hold violations are observed.

A timing simulation (or equivalently "Post place and route simulation") can be done after the PAR process finishes. This simulation style is the most reliable one. If the post-PAR simulation is successfully applied, it is highly predictable that the design will operate after it is loaded into the FPGA. The timing simulation is slower compared to the functional one. In this simulation all of the components and routings used in the FPGA are replaced by its simulation models, so the skew and latency of a signal can be easily observed. The setup and hold times of the flip-flops, gate delays, and IOB delays are tracked and erroneus situations are reported by the simulator. In this simulation it is highly predictable that the designer will not be able to see all of the codes written. That is simply because all of the design is created after optimization steps. So the designer must be aware that if the functional simulation results are not alike the post-PAR one, the code must be rechecked. A synchronous design is the most reliable design because most probably it will operate without timing failure.

ModelSim can also be used via a console. It supports TCL (Tool command language) scripts so the software can be used without the need of a graphical interface and the simulations speed up.

#### 3.3 Overall System Setup

In this section the setup that is used to implement and simulate the decoder performance will be explained. The important step in this part is the realization of a channel on the FPGA. Additionally how the FPGA get into contact with the outer world will be dealt.

#### 3.3.1 System

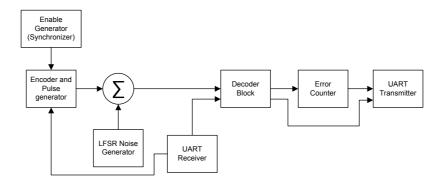

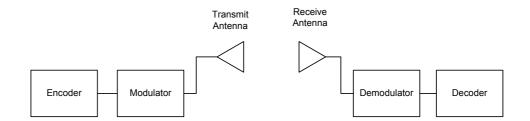

A general system model can be seen in Figure 3.4. The decoder block consists of a decoder and some auxiliary modules for proper operation which will be described in the upcoming sections.

Figure 3.4: A generalized system model for testing the decoders

The "Enable Generator (Synchronizer)" block perodically produces an enable signal which triggers the encoder block. Because of the chain structure of the design and the periodic behavior of this module, it can also be called the synchronizer. After the encoder block receives an enable signal, it starts to produce the encoded version of a known sequence. When the encoded sequence is ready, this module also produces a ready signal to indicate that the sequence is ready for decoding. The encoded data is scaled by a parameter received from the outer world via UART. This parameter is  $\sqrt{E_s}$  which is the amplitude of the encoded data. Hence, the energy of each bit in the sequence is  $E_s$ . After the encoded data is produced and multiplied by  $\sqrt{E_s}$ , a pseudorandom noise is added to the sequence. The pseudo-random noise is generated by the LFSR noise generator module. Afterwards, the noisy sequence is forwarded to the decoder block. The information produced by the decoder block, which will also be discussed in the upcoming sections, is transmitted to the outer world through UART port.

### 3.3.2 LFSR Noise Generator

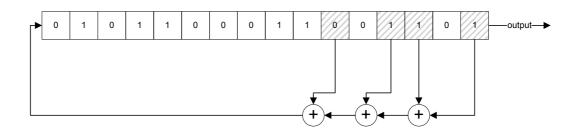

While testing the implemented decoders, varying inputs must be fed into the decoder along with many different noise realizations for a proper test operation. In order to generate a realistic environment in our study, random data generation algorithms are used in the FPGA. In the random number generation procedure an initial state called the *seed* is assumed, and the numbers are generated by the use of this seed. Since the state of the generator can be known in any time because of its seed-based structure the numbers generated are actually pseudo-random in nature. Then we have the chance to test the design for so many different inputs. By obtaining a gaussian like distribution we also have the opportunity of creating an AWGN channel in the FPGA. Among various random number generator algorithms a *linear feedback shift register* (LFSR) based one is chosen here because of its simple structure and wide usage. An LFSR is called linear becaues it is composed of binary linear operations, basically xor (exclusive or). Besides, it has a feedback structure in which a generated bit value is fedback to the shift register again. The feedback operation is done under a special characteristic equation. As the size of the shift register varies, the characteristic equation changes. Table 3.3.2 shows some characteristic feedback polynomials and corresponding register widths [3].

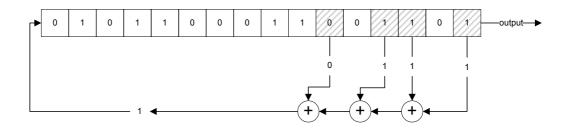

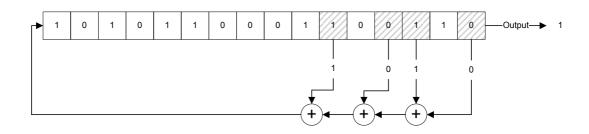

Figures 3.5, 3.6, and 3.7 shows the operation cycles of an LFSR composed of a 16 bit shift register. The shaded bit locations are called as taps which also demonstrates the locations those are described in the characteristic polynomial, namely 16th, 14th, 13th, and 10th locations. The initial state of the LFSR is called the seed of the LFSR and it can be any sequence of bits. As the name implies, the shift-register operates with the existance of a trigger signal, generally a clock. When the clock triggers the register, the *xor*-ed value is fed into the initial bit location and all of the bits are shifted. The last bit is the result coming from the shift register. When a seed is

Figure 3.5: An LFSR with seed 0101100011001101

Figure 3.6: The  $16^{th}$ ,  $14^{th}$ ,  $13^{th}$ ,  $10^{th}$  bit are added and the result is forwarded to the beginning of the register

Figure 3.7: With a clock trig the found result is registered as the first bit of the register, the content of the register is shifted once towards right

| Bits (n) | Feedback polynomial                     | Period $2^n - 1$ |

|----------|-----------------------------------------|------------------|

| 10       | $x^{10} + x^7 + 1$                      | 1024             |

| 11       | $x^{11} + x^9 + 1$                      | 2047             |

| 12       | $x^{12} + x^{11} + x^{10} + x^4 + 1$    | 4095             |

| 13       | $x^{13} + x^{12} + x^{11} + x^8 + 1$    | 8191             |

| 14       | $x^{14} + x^{13} + x^{12} + x^2 + 1$    | 16383            |

| 15       | $x^{15} + x^{14} + 1$                   | 32767            |

| 16       | $x^{16} + x^{14} + x^{13} + x^{11} + 1$ | 65535            |

| 17       | $x^{17} + x^{14} + 1$                   | 131071           |

| 18       | $x^{18} + x^{11} + 1$                   | 262143           |

| 19       | $x^{19} + x^{18} + x^{17} + x^{14} + 1$ | 524287           |

Table 3.1: Some LFSR generator polynomials with varying size of shift registers.

suitable to obtain all  $2^n - 1$  numbers then this seed is called as the maximal.

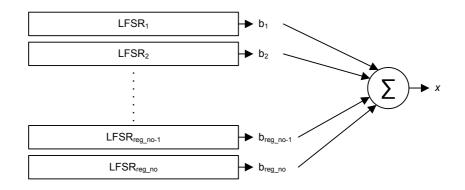

If many LFSRs are implemented with different seeds<sup>4</sup>, then the output of each LFSR will be independent of each other. If the outputs of these LFSRs are summed up as shown in Figure 3.8 then by the Central Limit Theorem a pseudo-random noise generator whose probability distribution is close to that of the Gaussian distrubiton will be obtained.

Figure 3.8: Normally distributed noise generation by LFSR

The mean and the variance of the random noise generator can be evaluated through some equations. Let x be a random variable that is obtained by the summation of the

<sup>&</sup>lt;sup>4</sup> Special care should be taken when assigning seeds to the LFSRs. A bad choice of seeds may lead to incorrect results due to auto-correlation etc.

output bits of  $reg_no$  number of LFSRs. The mean of x is

$$E(x) = E\left(\sum_{reg_{-no}} b_i\right)$$

(3.1)

Since summation is a linear operation and each  $b_i$  is independent of each other the expectation function can go into the summation and (3.1) yields

$$E(x) = \sum_{reg-no} E(b_i).$$

(3.2)

The probability of  $b_i$  to be either 0 or 1 is equal, 1/2 so (3.2) can be calculated as

$$E(x) = \sum_{reg_{-no}} \frac{1}{2},$$

(3.3)

$$E(x) = \frac{reg_{-}no}{2}.$$

(3.4)

The variance of x is found by the well known variance equation that

$$Var(x) = E(x^{2}) - E^{2}(x),$$

=  $E\left(\left(\sum_{reg_{-no}} b_{i}\right)^{2}\right) - \frac{(reg_{-no})^{2}}{4}.$  (3.5)

Here comes a square of a summation and this equation must also be put into a linear form for ease of calculation. If the squared term is written in an open form it will be seen that there will be  $reg_no$  number of  $b_i^2$ 's and other terms will be in the form of  $b_ib_j$ . The variance of x can be rewritten in the following form:

$$Var(x) = E\left(\sum_{reg_{-no}} b_i^2 + \sum_{i,i\neq j}^{reg_{-no}} \sum_{j=1}^{reg_{-no}} b_i b_j\right) - \frac{(reg_{-no})^2}{4}$$

(3.6)

$$= \sum_{reg_{-no}} E(b_i^2) + \sum_{i,i\neq j}^{reg_{-no}} \sum_{j=1}^{reg_{-no}} E(b_i)E(b_j) - \frac{(reg_{-no})^2}{4}$$

(3.7)

$$= \frac{reg_{-no}}{2} + (reg_{-no} - 1)reg_{-no}\frac{1}{4} - \frac{(reg_{-no})^2}{4}$$

(3.8)

$$=\frac{reg_{-no}}{2} + \frac{reg_{-no}^{2}}{4} - \frac{reg_{-no}}{4} - \frac{(reg_{-no})^{2}}{4}$$

(3.9)

$$=\frac{reg_no}{4}.$$

(3.10)

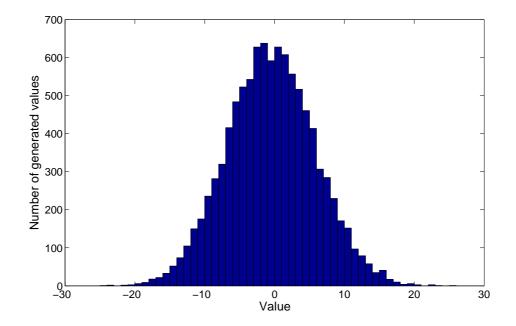

In the design of the pseudo-random gaussian noise generator 40 LFSRs ( $reg_no =$  40) of 16 bit locations with different seeds are generated <sup>5</sup>. At each rising edge of a

<sup>&</sup>lt;sup>5</sup> 16 bit LFSR corresponds to 65536 cycles in period. For long tests, this period seems to be too small for noise generation. However, if the length and the period of the generated transmitted data frames do not coincide with the period of the LFSRs, this would not significantly affect the results here due to the use of highly randomized turbo codes.

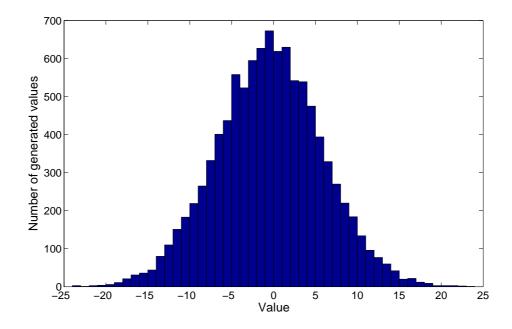

clock the usual LFSR operation is carried on. The outputs of the LFSRs are summed up and the sum is taken as a normally distributed random variable. Since the produced numbers are fairly uncorrelated from each other, summing up consecutive results of the generator results in a Gaussian distribution. Figure 3.9 shows the histogram of the outputs of such a generator obtained by MATLAB simulation. On the other hand, Figure 3.10 shows the histogram of a normal distribution obtained by MATLAB's randn function which has the same variance of that illustrated in Figure 3.9.

Figure 3.9: The hystogram of a pseudo-random Gaussian noise generator obtained by collection of 10000 samples

The LFSR random noise generator VHDL code is as

```

process(clk4X)

begin

if rising_edge(clk4X) then

if rising_edge(clk4X) then

if rst = '1' then

for i in 1 to reg_no loop

seed(i) <= file_sonucu(i*16 downto (i-1)*16+1);

end loop;

else

for jj in 1 to reg_no loop

seed(jj) <= seed(jj)(14 downto 0) & (seed(jj)(10) xor

seed(jj)(12) xor seed(jj)(13) xor seed(jj)(15));

end loop;</pre>

```

Figure 3.10: A histogram of a noise sequence generated by MATLAB's randn function

end if; end if; end process;

*file\_sonucu* is an array of strings composed of 1's and 0's previously generated by MATLAB and written into a text file. When the synthesis happens, the tool reads that file and initializes all of the LFSRs with the desired seeds.  $reg_no$  is the number of LFSRs taking place in the noise generator. It is 40 in our studies but it can be adjusted with the necessity that *file\_sonucu* must also be renewed. Since there are 40 registers the summation results a normal distribution with mean 20, hence in order to make the mean of that random variable 0 a 20 is always subtracted from the summation result. The variance of the sequence generated by this code is 10. The process operates with a clock 4 times faster than the usual operating clock (clk4x represents this notation). The reason for this is that 4 consecutive random numbers are added up to obtain a noise with a larger variance, that is, 4 times of a single sequence, so the variance of the new distribution is 40. Since the LFSR clock is 4 times faster than the usual clock, the generated random numbers are collected in a first in first out buffer (FIFO) and an adder module at the normal clock side reads 4 of them and sums up the numbers.

### 3.3.3 Error Counter

The error counter module counts the number of errors occured in a packet. As mentioned in Section 3.3.1 a known packet of data is encoded and transmitted. This uncoded data sequence is also known by this module. Whenever the decoder block starts to produce the bit estimates this module starts to check bit by bit whether the estimation is correct or not and keeps the number of incorrect estimations. Besides calculating the wrong bit decoding, it also counts how many packets are decoded incorrectly. These numbers are fed to the UART transmitter module for reporting to the PC.

# 3.3.4 UART Module

UART is the acronym for Universal Asynchronous Receiver Transmitter. In our design a full duplex UART is used in conjunction with RS232. A UART takes parallel data and transmits it bit by bit in a sequential fashion. The receiver side understands a new data coming and translates the bit by bit received sequence into a parallel form. The conversion between serial to parallel or vice versa in the transmitter and receivers is accomplished by the use of shift registers.

The protocol is called asynchronous because the transmitter does not send any clock signal to the receiver side. The transmission process starts whenever the transmitter sends a start bit. After the transmission of the start bit the data is transmitted from the least significant bit to the most significant. Optionally a parity bit for error check can also be included after the transmission of the data. A stop bit finishes the transmission of a byte. Figure 3.11 represents the alignment of these bits.

| Start | Data | Data | Data | Data | Data | Data | Data | Data | Stop Bit |

|-------|------|------|------|------|------|------|------|------|----------|

| Bit   | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |          |

Figure 3.11: The bit alignment in a UART transmission

The transmission of data from FPGA to PC and from PC to FPGA is handled by

a protocol. In the PC to FPGA part a register map mode is used. In this mode some numbers are protected. If these special characters are sent, the next character will be the content of that register. That is, if initially byte A is transmitted and then byte B is transmitted the receiver module on the FPGA checks whether byte A is the address of a register. If it is then the content of register addressed by A is changed by B. If a value is wanted to be assigned to a register, this value cannot be the address of the registers, equivalently, B can not be protected numbers. This check is done in the MATLAB module that if B somehow enters to the forbidden zone the MATLAB code does not send this value and issues an error to the user. The register scheme is shown in Table 3.3.4.

Table 3.2: The registers and their meaning in the design of the UART transmitter.

| Register Address | Register Name | Description                                             |