### PERFORMANCE IMPROVEMENT OF VLSI CIRCUITS WITH CLOCK SCHEDULING

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

KEREM KAPUCU

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2009

Approval of the thesis:

# PERFORMANCE IMPROVEMENT OF VLSI CIRCUITS WITH CLOCK SCHEDULING

submitted by **KEREM KAPUCU** in partial fulfillment of the requirements for the degree of **Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University** by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>         |  |

|-----------------------------------------------------------------------------------------------|--|

| Prof. Dr. İsmet Erkmen<br>Head of Department, <b>Electrical and Electronics Engineering</b>   |  |

| Prof. Dr. Murat Aşkar<br>Supervisor, <b>Electrical and Electronics Engineering Department</b> |  |

| <b>Examining Committee Members:</b><br>Prof. Dr. Hasan Güran                                  |  |

| Electrical and Electronics Engineering, METU                                                  |  |

| Prof. Dr. Murat Aşkar<br>Electrical and Electronics Engineering, METU                         |  |

| Assist. Prof. Dr. Haluk Külah<br>Electrical and Electronics Engineering, METU                 |  |

| Assist. Prof. Dr. Şenan Ece Güran Schmidt<br>Electrical and Electronics Engineering, METU     |  |

| Dr. Neslin İsmailoğlu<br>TÜBİTAK UZAY                                                         |  |

Date:

\_

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: KEREM KAPUCU

Signature :

## ABSTRACT

#### PERFORMANCE IMPROVEMENT OF VLSI CIRCUITS WITH CLOCK SCHEDULING

Kapucu, Kerem M.S., Department of Electrical and Electronics Engineering Supervisor : Prof. Dr. Murat Aşkar

December 2009, 87 pages

Clock scheduling is studied to improve the performance of synchronous sequential circuits. The performance improvement covers the optimization of the clock frequency and the peak power consumption, separately. For clock period minimization, cycle stealing method is utilized, in which the redundant cycle time of fast combinational logic is transferred to slower logic by proper clock skew adjustment of registers. The clock scheduling system determines the minimum clock period that a synchronous sequential circuit can operate without hazards. The timing of each register is adjusted for operation with the minimum clock period. The dependence of the propagation delays of combinational gates on load capacitance values are modeled in order to increase the accuracy of the clock period minimization algorithm. Simulation results show up to 45% speed-up for circuits that are scheduled by the system. For peak power minimization, the dependence of the switching currents of circuit elements on the load capacitance values are modeled. A new method, namely the Shaped Pulse Approximation Method (SPA), is proposed for the estimation of switching power dissipation of circuit elements for arbitrary capacitive loads. The switching current waves can accurately be estimated by using the SPA method with less than 10% normalized rms error. The clock scheduling algorithm of Takahashi for the reduction of the peak power consumption of synchronous sequential circuits is implemented using the SPA method. Up to 73% decrease in peak power dissipation is observed in simulation results when proper clock scheduling scheme is applied to test circuits.

Keywords: vlsi, clock scheduling, peak power minimization, clock period minimization, vlsi power estimation

#### SAAT ZAMANLAMASI İLE VLSI TÜMDEVRELERDE BAŞARIMIN İYİLEŞTİRİLMESİ

Kapucu, Kerem Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Prof. Dr. Murat Aşkar

Aralık 2009, 87 sayfa

Bu çalışmada, senkron devrelerin saat hızları ve tepe güç tüketimlerinin, saat zamanlaması kullanılarak iyileştirilmesi amaçlanmıştır. Saat periyodunu küçültmek için, çevrim aşırma yöntemi kullanılmıştır. Bu yöntemde, yazmaçların saat zamanlaması ayarlanarak, devrenin hızlı birleşimsel bölümlerinden arta kalan zaman, daha yavaş birleşimsel bölümlere aktarılmaktadır. Saat zamanlaması sistemi, senkron devrelerin sorunsuzca çalışabileceği en düşük saat periyodunu belirler. Devrenin, en düşük saat periyodu ile çalışması için, her bir yazmacın zamanlaması ayarlanır. Saat periyodu küçültme yönteminin kesinliğini artırmak için, devre elemanlarının yayılma gecikmesinin sığal yük ile değişimi modellenmiştir. Benzetim sonuçlarına göre, saat zamanlaması sistem tarafından yapılan devrelerde %45'e varan hızlanma gözlenmiştir. Tepe güç tüketiminin azaltılması için, devre elemanlarının anahtarlama akımlarının sığal yük ile değişimi modellenmiştir. Devre elemanlarının herhangi bir sığal yük altındaki anahtarlama güç tüketimlerini tahmin etmeye yarayan, Biçimlendirilmiş Atım Kestirimi (BAK) isimli yeni bir yöntem önerilmiştir. BAK yöntemi ile devre elemanlarının anahtarlama akımları %10'un altında normalize rms hata ile saptanabilmektedir. Takahashi'nin senkron devrelerin tepe güç tüketimini düşürmeye yarayan saat zamanlaması yöntemi, BAK yöntemi kullanılarak oluşturulmuştur. Bu yöntem ile saat zamanlaması yapılan

devrelerin, tepe güç tüketimleri, %73'e varan oranlarda düşürülmüştür.

Anahtar Kelimeler: vlsi, saat zamanlaması, tepe güç azaltma, saat devri kisaltma, vlsi güç tahmini

To my family...

### ACKNOWLEDGMENTS

The author wishes to express his deepest appreciation and gratitude for his supervisor Prof. Dr. Murat AŞKAR for his precious guidance, advice, criticism, encouragement and insight throughout the development of this work.

The author would also like to thank his examining committee member Dr. Neslin İsmailoğlu for her valuable suggestions and comments.

The author wishes to thank TÜBİTAK-UZAY for the facilities and environment provided to him throughout the research. The author's colleagues and friends at TÜBİTAK-UZAY are also appreciated for all the support and encouragement he received from them.

The author also wishes to thank TÜBİTAK for their support of his M.Sc. studies with their scholarship.

The author wishes to express his deepest gratitude to Pınar Ün for her invaluable friendship, patience and support that helped him through the hard times during the course of this work.

Last but not least, the author thanks especially to his family for their amazing love, constant support, great patience and extensive encouragement throughout his studies.

# TABLE OF CONTENTS

| ABSTR  | RACT    |          |                                                       | iv   |

|--------|---------|----------|-------------------------------------------------------|------|

| ÖZ     |         |          |                                                       | vi   |

| DEDIC  | ATON .  |          |                                                       | viii |

| ACKN   | OWLED   | GMENTS   |                                                       | ix   |

| TABLE  | OF CO   | NTENTS   |                                                       | x    |

| LIST O | FTABL   | ES       |                                                       | xii  |

| LIST O | F FIGUE | RES      |                                                       | xiii |

| СНАРТ  |         |          |                                                       |      |

| -      |         |          |                                                       |      |

| 1      |         |          | Ν                                                     | 1    |

| 2      | CLOC    | K SCHED  | ULING                                                 | 7    |

|        | 2.1     | General  | Synchronous Framework                                 | 10   |

|        | 2.2     | Systems  | of Difference Constraints                             | 14   |

|        | 2.3     | Minimu   | m Feasible Clock Period                               | 20   |

|        | 2.4     | Minimu   | m Cost Scheduling                                     | 23   |

|        |         | 2.4.1    | Finding the Optimal Amount of Clock Timing Adjustment | 24   |

|        |         | 2.4.2    | Finding Cost Reducible Register Sets                  | 27   |

|        | 2.5     | Clock S  | cheduling System                                      | 39   |

| 3      | PEAK    | POWER I  | MINIMIZATION                                          | 41   |

|        | 3.1     | Estimati | on Of Peak Power Consumption                          | 42   |

|        |         | 3.1.1    | Calculation of Switching Probabilities                | 43   |

|        |         | 3.1.2    | Calculation of Peak Power Consumption                 | 45   |

|        |         | 3.1.3    | Switching Power Estimation                            | 47   |

|        |         | 3.1.4    | Power Estimation Algorithm                            | 53   |

|       | 3.2   | Clock Sc | heduling For Peak Power Consumption Reduction | 56 |

|-------|-------|----------|-----------------------------------------------|----|

| 4     | SIMUL | ATIONS A | AND TESTS                                     | 59 |

|       | 4.1   | Gate Cha | racterization                                 | 60 |

|       |       | 4.1.1    | Gate Propagation Delay Modeling               | 60 |

|       |       | 4.1.2    | Gate Switching Current Modeling               | 61 |

|       | 4.2   | Register | Characterization                              | 63 |

|       |       | 4.2.1    | Register Setup and Hold Time Measurements     | 64 |

|       |       | 4.2.2    | Register Switching Power Measurements         | 68 |

|       | 4.3   | Performa | nce Evaluation of the Algorithms              | 69 |

|       |       | 4.3.1    | Implementation of the Algorithms              | 69 |

|       |       | 4.3.2    | Test Circuits                                 | 69 |

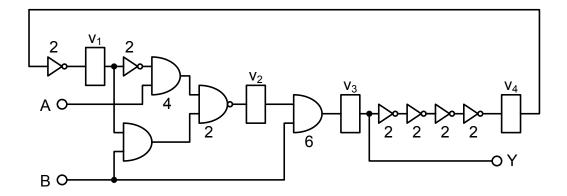

|       |       | 4.3.3    | Clock Period Minimization                     | 71 |

|       |       | 4.3.4    | Peak Power Minimization                       | 71 |

| 5     | CONCI | LUSION . |                                               | 76 |

| REFER | ENCES |          |                                               | 79 |

| А     | HDL G | ENERAT   | DR                                            | 84 |

| В     | RAND  | OM INPU  | T GENERATOR                                   | 87 |

# LIST OF TABLES

## TABLES

| Table 3.1 The condition probabilities of $n$ input gates to be $a \ldots a$ |                  | 44 |

|-----------------------------------------------------------------------------|------------------|----|

| Table 3.2    The Normalized Rms Estimation Error For Gates                  |                  | 54 |

| Table 4.1 The propagation delays of the 4-input AND gate for 15 difference  | fferent combina- |    |

| tions of switching inputs, as the result of the first phase of delay        | simulation. The  |    |

| propagation delay values for the input signal switching in two direction    | ections are mea- |    |

| sured and the average of the two values are also shown. The in              | puts that do not |    |

| switch are fixed to logic "1" for AND gate. The unit of the value           | s is picoseconds |    |

| and the measurements are done with 1 ps precision                           |                  | 61 |

| Table 4.2    The characteristics of benchmark circuits.                     |                  | 70 |

| Table 4.3    The speed-up of test circuits.                                 |                  | 72 |

| Table 4.4    The simulation durations of the test circuits.                 |                  | 74 |

| Table 4.5         The peak power minimization of test circuits.             |                  | 75 |

# **LIST OF FIGURES**

## FIGURES

| Figure 2.1 The example circuit for illustrating the clock period minimization by cycle  |    |

|-----------------------------------------------------------------------------------------|----|

| stealing method. The circuit consists of three stages of registers and combinational    |    |

| parts in between.                                                                       | 8  |

| Figure 2.2 Input and output signal waveforms of the registers of the circuit in Fig 2.1 |    |

| for fully synchronous operation. All the registers are clocked by the same clock        |    |

| with a period of 12 units.                                                              | 8  |

| Figure 2.3 Input and output signal waveforms of the registers of the circuit in Fig 2.1 |    |

| for semi synchronous operation. With the application of 4 units of delay to the         |    |

| clock signal of register $v$ , the minimum clock period of the circuit is decreased     |    |

| from 12 units to 8 units. Circuit speed improvement with cycle stealing is illustrated. | 9  |

| Figure 2.4 Two registers with data path taken as a part of a synchronous circuit        | 10 |

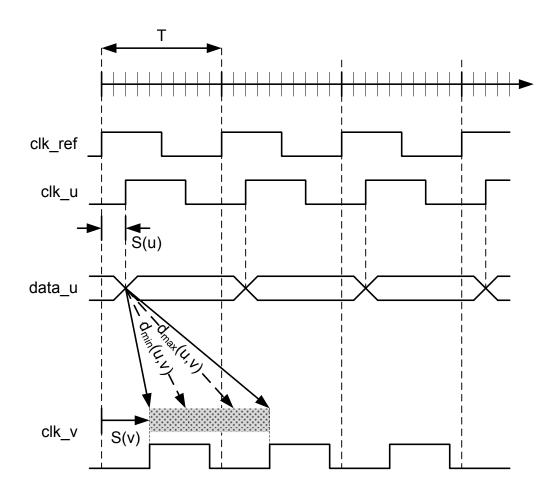

| Figure 2.5 Timing diagram for setup and hold time constraints                           | 11 |

| Figure 2.6 Example circuit [58]                                                         | 13 |

| Figure 2.7 Constraint graph of the example circuit                                      | 14 |

| Figure 2.8 Minimum feasible clock period algorithm.                                     | 21 |

| Figure 2.9 Negative cycle detection algorithm: Bellman-Ford Algorithm with modi-        |    |

| fied walk-to-the-root strategy.                                                         | 22 |

| Figure 2.10 Minimum cost scheduling algorithm.                                          | 25 |

| Figure 2.11 Algorithm that finds an initial feasible clock schedule                     | 26 |

| Figure 2.12 TryDec algorithm                                                            | 27 |

| Figure 2.13 TryInc algorithm                                                            | 28 |

| Figure 2.14 Algorithm that finds cost reducible by decrease sets                        | 29 |

| Figure 2.15 Algorithm that computes the transitive closure of a graph.                  | 30 |

| Figure 2.16 Algorithm that finds cost reducible by increase sets                               | 34 |

|------------------------------------------------------------------------------------------------|----|

| Figure 2.17 Clock scheduling system.                                                           | 38 |

| Figure 2.18 Algorithm that determines the clock schedule ranges of all registers               | 39 |

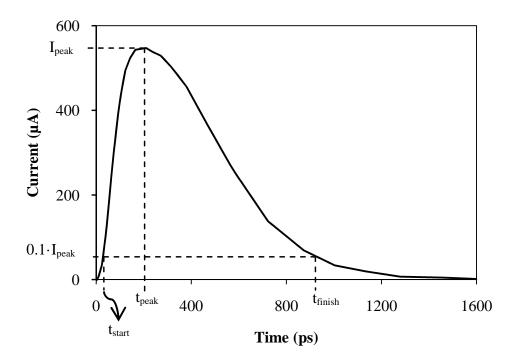

| Figure 3.1 Switching current wave of a 2-input AND gate for output transition from             |    |

| low to high. The parameters for characterizing the current waveform are also shown.            | 48 |

| Figure 3.2 The switching current waves of a 2-input AND gate for output switching              |    |

| from low to high. The waves are plotted for various capacitive loads ranging from              |    |

| 1 fF to 100 fF                                                                                 | 49 |

| Figure 3.3 The variation of the peak value of the switching current of 2-input AND             |    |

| gate with respect to load capacitance. The curve can be fitted with a logarithmic              |    |

| function but a 6th order polynomial gives a better fitting with less error                     | 51 |

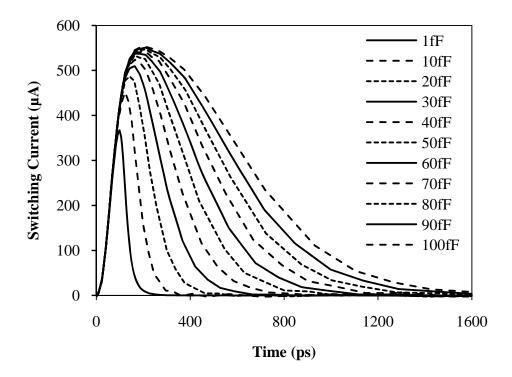

| Figure 3.4 The variation of the switching current pulse width of the 2-input AND gate          |    |

| with respect to load capacitance. The pulse width is measured from $t_{start}$ to $t_{stop}$ . | 51 |

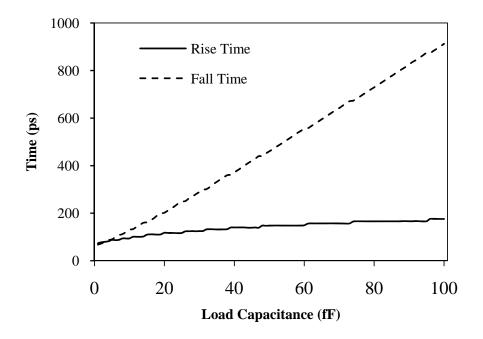

| Figure 3.5 The variation of rise and fall times of the switching power wave of 2-input         |    |

| AND gate with respect to load capacitance. Rise time curve can be fitted with a                |    |

| 3rd order polynomial function. Fall time curve can be fitted with a linear function.           | 52 |

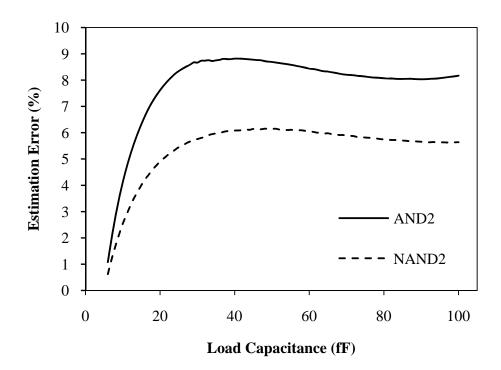

| Figure 3.6 Estimation error for 2-input AND and 2-input NAND gates. The switch-                |    |

| ing current wave for 5 fF capacitance is used as the unit wave, and the switching              |    |

| current waves for capacitive loads in 6 fF - 100 fF range are estimated using the              |    |

| method. The estimated waves are compared with simulation results and the esti-                 |    |

| mation error is calculated using (3.21).                                                       | 53 |

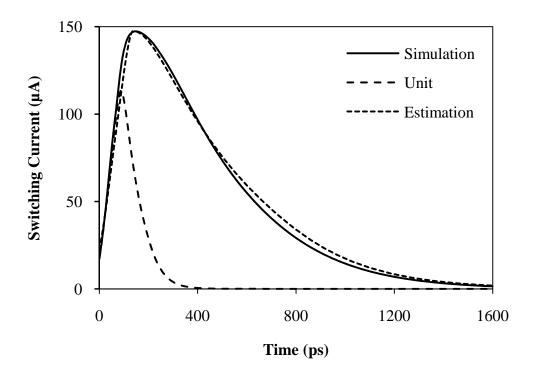

| Figure 3.7 The switching current wave of 2-input NAND gate for 5 fF and 100 fF load            |    |

| capacitances shown with the estimated current wave for 100 fF load using the data              |    |

| for 5 fF load. The normalized rms error is 5.7%                                                | 54 |

| Figure 3.8 The algorithm to estimate the register originated power consumptions of             |    |

| the registers of a circuit.                                                                    | 56 |

| Figure 3.9 First stage of the two stage algorithm that minimizes the peak power con-           |    |

| sumption of a circuit with clock scheduling.                                                   | 57 |

| Figure 3.10 Second stage of the two stage algorithm that greedily minimizes the peak           |    |

| power consumption of a circuit with clock scheduling.                                          | 57 |

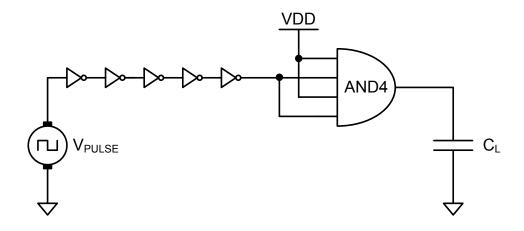

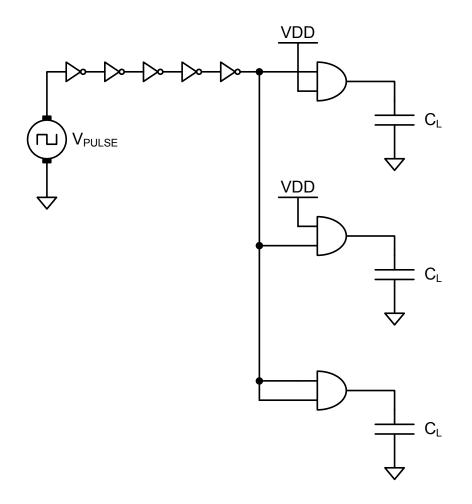

| Figure 4.1 The circuit used in the propagation delay measurement of the 4-input AND       |    |

|-------------------------------------------------------------------------------------------|----|

| gate. The case when the inputs A and C are fixed, and the inputs B and D are              |    |

| switched is shown                                                                         | 62 |

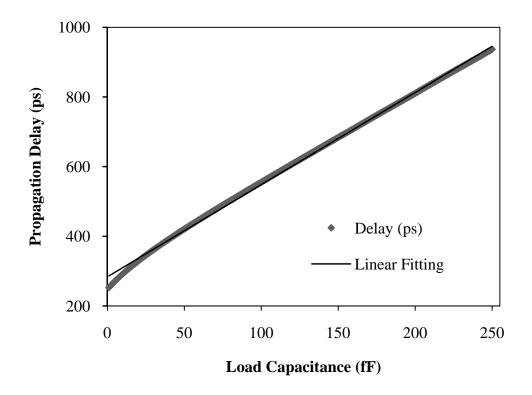

| Figure 4.2 Variation of the propagation delay of the 4-input AND gate with respect to     |    |

| the load capacitance value. The fitted linear curve is also shown                         | 62 |

| Figure 4.3 The circuit used in switching current measurement of the 2-input AND           |    |

| gate. All three switching input combinations that causes switching at the output          |    |

| are simulated at once. The total supply current of the three AND gates are divided        |    |

| by 3 to find the average switching power of the 2-input AND gate                          | 64 |

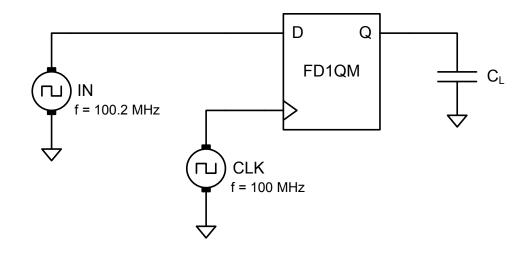

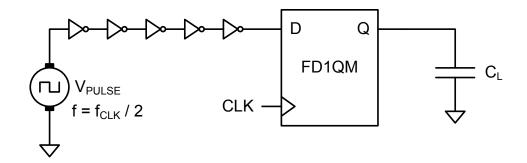

| Figure 4.4 The circuit used in setup time and hold time measurements of the D flip-       |    |

| flop. Clock and input signals with slightly different frequencies are applied to the      |    |

| D flip-flop                                                                               | 65 |

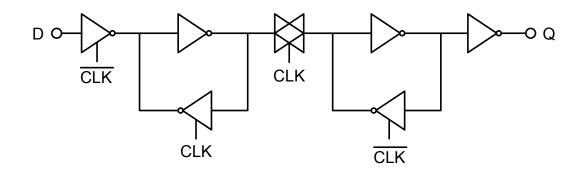

| Figure 4.5 The gate level schematics of the D flip-flop that is used in the test circuits | 65 |

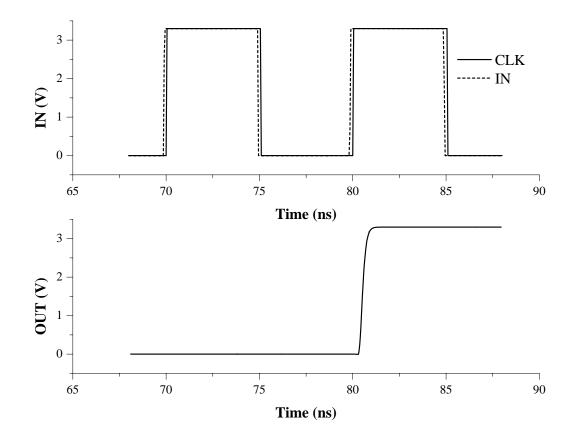

| Figure 4.6 The input, clock and output signals from the simulation output when the        |    |

| setup time is measured.                                                                   | 66 |

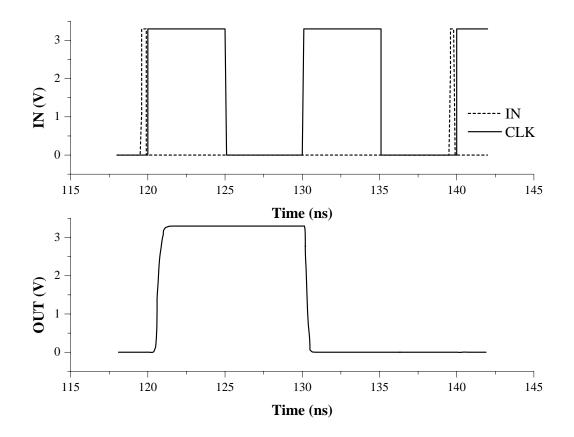

| Figure 4.7 The input, clock and output signals from the simulation output when the        |    |

| hold time is measured                                                                     | 67 |

| Figure 4.8 The circuit used in switching power measurement of the D flip-flop             | 68 |

| Figure A.1 Example circuit [58]                                                           | 84 |

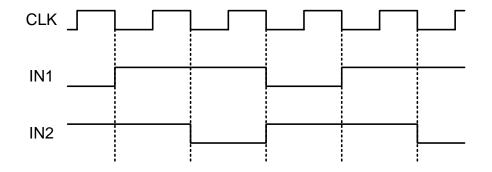

| Figure B.1 Timing diagram showing the clock signal and two example input signals.         |    |

| The input signals change with the falling edges of the clock in order to eliminate        |    |

| metastability issues.                                                                     | 87 |

## **CHAPTER 1**

## **INTRODUCTION**

The digital design is dominated by the synchronous approach, where the systems are composed of finite state machines and synchronously clocked registers. The systematic approach in designing the synchronous sequential circuits and the ease of verification have led to dramatic progress in the architectures of the systems and the productivity of the designers.

Owing to the advances in the semiconductor manufacturing technology, the number of elements in integrated circuits are increasing exponentially, following Moore's Law [1]. The scale, speed and power consumption of VLSI circuits has improved rapidly. However, shrinking the feature sizes in VLSI circuits, has dramatically decreased the interconnect thickness; which, in turn, increases resistance of the interconnects and the ratio of routing delay to propagation delay. This puts a limit to the performance improvements in fully synchronous circuits, where simultaneous switching of all the registers are assumed.

Power consumption and speed are among the major constraints in chip design. Power consumption is identified to be in top three overall challenges in chip design for the last five years [2]. For many consumer electronic applications, low average power dissipation is desirable. Moreover, mobile applications such as portable personal communication systems and entertainment devices usually require tight power dissipation constraints. The weight limitations of portable devices arising from the consumer tendency towards smaller and lighter devices put a limit on battery sizes, too. Thus, peak power consumption is as important as average power consumption. Also, the trend towards system-on-chip modules has increased the importance of low power consumption, because heat dissipation is a major problem at that level of integration.

In sequential VLSI circuits, clock signal is generated at a clock source and distributed to the

registers via a clock distribution network. The mismatches in resistance and capacitance of the interconnects due to process variations result in differences in interconnect delays on the clock distribution network. As a result, the clock signals do not arrive at all of the registers at the same time. With the decrease of feature sizes in VLSI circuits, these differences are not negligible anymore. Clock skew is the difference in the arrival times of clock edges to different registers in a circuit due to the differences in the interconnect delays on the clock distribution network.

In 1965, Cotten described a data race mechanism in which clock skew may cause a synchronous circuit to fail [3]. Synchronous circuit designers have made a constant effort to eliminate clock skew since then. Methods are proposed in order to achieve zero clock skew in clock distribution networks and satisfying results are obtained for skew minimization [4]-[9].

In synchronous circuits, all the registers are clocked simultaneously. When a register is clocked, its output signal starts to propagate through the combinational circuit to the input of the next register. In order to eliminate a hazardous operation, this signal must arrive at the input of the next register before the next clock edge. Hence, the minimum clock period is bounded below by the maximum propagation delay between two consecutive registers in the circuit. Taking clock skews into account, the minimum clock period of the circuit is chosen to be larger than the sum of the maximum signal propagation delay and the maximum clock skew to guarantee the correct function [10]. Thus, clock skew is usually perceived as an undesirable phenomenon deteriorating circuit performance and efforts are made towards its elimination.

Conservative design styles, such as those adopted for FPGAs, explicitly discourage "tampering with the clock" [11]. Another approach views clock skew as a "manageable resource than a liability" and increases circuit performance by careful adjustment of clock skews of registers with intentionally introduced delays [12]. In 1990, Fishburn suggested that clock skew can be approached as a means of circuit performance improvement by carefully adjusting the clock timings of each register [13]. Fishburn showed that, the clock period of a synchronous circuit can be minimized by clock skew optimization while maximizing the safety margins against clock hazards [13]. This is the introduction of the basic idea of semi-synchronous circuits, where each register is clocked periodically but not necessarily simultaneously. The conditions for a synchronous circuit to operate correctly with a clock period are given in terms of clock timings of registers and maximum and minimum propagation delays between registers [13]. The process of adjusting the clock timings of registers of a synchronous circuit for circuit performance improvement is called *clock scheduling* [56].

The clock skew optimization problem is formulated by a linear program [13] and various algorithms are proposed to minimize the clock period of synchronous circuits [14]-[19]. Since the computation time to solve the linear program increases with larger circuits, methods to reduce the size of the linear program are also developed [15], [19].

Exploiting the special form of the timing constraints, graph algorithms are proposed for clock schedule optimization [20]. It is shown that, the clock skew optimization can efficiently be done using directed, weighted graphs to represent setup and hold time constraints [10], [12], [20]-[26]. The minimum feasible clock period is obtained by graph-theoretic approaches with binary search. Bellman-Ford algorithm is used to determine whether a clock period is feasible at each iteration of the binary search [12], [20]-[24]. Since this is a time consuming method, negative cycle detection strategies are utilized in order to fasten the algorithms for large circuits [25]. Graph-theoretic approaches without binary search are also proposed [10], [26]. Clock scheduling algorithms aiming to schedule a circuit with minimum cost to a given infeasible clock schedule are developed [25], [27].

The early works on clock scheduling aimed the minimization of clock period as the optimization goal [13]-[24]. However, clock scheduling has been applied for a number of other quality of circuit improvements, as well. Circuit reliability is improved using clock scheduling [10], [26]-[30]. Clock scheduling is applied to increase the tolerance of synchronous sequential circuits to clock jitter [28] and process variations [32], [33].

Peak current is a primary concern in the design of power distribution networks of VLSI circuits [34]. In order to account for the large current peaks observed in the synchronous digital circuits, the power and ground lines are over-dimensioned [34]. The maximum voltage drop and the probability of failure due to electromigration increases with large peak currents [35], [36]. Demicheli et al. proposed the minimization of peak power supply current by clock scheduling for the first time [34]. It is shown that the current peaks occurring due to the simultaneous switching of the registers and the first stages of combinational circuits can be minimized using clock scheduling without increasing the average power dissipation of the circuit. Also, a clustering method for easy realization of the clock scheduling is given [34].

The power dissipation of synchronous sequential circuits should accurately be estimated for peak power reduction with clock scheduling. Methods are proposed for power estimation of combinational and sequential circuits [37]-[42]. Current waveforms of digital circuits are estimated using probabilistic methods [38], and means of worst-case power estimation are developed [35], [39]. The switching probabilities are estimated by calculating the transition densities [37] and taking the effects of glitching into account [41], [42]. In [34] the power consumption is estimated under the assumption that the switching timings of gates are fixed and independent of the clock scheduling. Genetic Algorithm is used to obtain a feasible clock schedule that reduces the peak power dissipation of a circuit. However, since the switching times of the gates in a circuit depend heavily on the clock schedule, the power estimation and the obtained clock schedule are not accurate. Moreover, as a characteristic property of the Genetic Algorithm, the computation time of this method is very long.

Extending the methods in [34], power supply noise suppression [43], [44] and reduction of leakage power is achieved [45]. In [43], the power consumption is estimated by assuming that the switching times of gates depend on the minimum delay from a register and the switching time of the register. However, the gates may switch due to a switching on a non-minimum delay path from a register, which decreases the accuracy of this method. Again the clock scheduling is obtained by a time consuming Genetic Algorithm based method.

Atsushi et al. proposed a fast and more accurate power estimation algorithm and a peak power reduction algorithm based on that power estimation method [46]. In [46], the power consumption of a circuit is modeled as the sum of register originated power consumptions. The switching probabilities of gates are assumed independent of the inputs and calculated iteratively. Clock scheduling for minimum peak power consumption is done by a fast two-stage algorithm [46].

The clock scheduling algorithms are developed under the assumption that the desired clock skews can be introduced to the clock tree. Methods have been proposed for clock routing [7], clock tree synthesis and physical realization [47]-[51] in order to implement the clock schedules efficiently. The minor increase in the power consumption of the clock tree due to the introduction of the clock skews can be eliminated with special clock synthesis algorithms [56].

The thesis study mainly consists of the application of clock scheduling to synchronous se-

quential circuits in order to improve two performance metrics of the circuits: clock period and peak power consumption. In complete-synchronous framework, all the registers are clocked simultaneously and this results in two problems. The first problem is that the minimum clock period of the circuit is determined by the longest combinational delay between two registers, whereas faster combinational paths wait idle for the next clock edge although their outputs are ready. The second problem arises from the simultaneous switching of all the registers in a circuit. This results in a high peak power for a short duration after the clock edge, whereas for the rest of the time the circuit dissipates relatively small static power. In this work, clock scheduling is utilized as a solution to both problems. The clock period of a synchronous sequential circuit can be minimized by cycle stealing. The redundant time of fast combinational paths are transferred to slower combinational paths by adjusting the skew of the registers. By this way, each combinational path between registers is assigned the time it needs to generate the outputs while increasing the overall speed of the circuit. The peak power of synchronous sequential circuits can be minimized by clock scheduling. The power dissipation wave can be suppressed and broadened without disturbing the proper operation of the circuit by carefully adjusting the switching times of the registers. In the chapters that follow, these issues are presented as follows:

The basics of clock scheduling is given in Chapter 2. The method for determining the minimum feasible clock period of a synchronous sequential circuit is explained. Clock scheduling algorithms for increasing the clock frequency of the circuit are discussed. The algorithms for scheduling a circuit with minimum cost to an infeasible clock schedule are also presented.

Chapter 3 covers the algorithm for estimating the peak power consumption of a synchronous sequential circuit. The newly proposed Shaped Pulse Approximation method for estimating the switching current waveform of circuit elements is explained. This chapter also covers how the clock scheduling is utilized to reduce the peak power consumption of a synchronous sequential circuit.

In Chapter 4 the simulations and tests made for the evaluation of the algorithms are discussed. The the delay and switching power characterization of gates and registers are explained in detail. The simulation results showing the performance improvement of the benchmark circuits are presented.

In Chapter 5 the thesis work is summarized, conclusions are drawn and suggestions are made

for future improvements of the proposed power estimation method.

### **CHAPTER 2**

### **CLOCK SCHEDULING**

Synchronous digital circuits can be examined in two frameworks [13, 46]: complete synchronous framework (c-frame) and general synchronous framework (g-frame). In c-frame, all registers are assumed to be simultaneously clocked; whereas, in g-frame registers are not necessarily clocked simultaneously, provided that the periodicity of the clock signals are still preserved. The circuits in which registers are clocked with more than one clock timing are called *semi-synchronous circuits* [27]. G-frame offers a degree of freedom to the circuit designer, which can be used to improve circuit performance metrics such as clock frequency, peak power consumption, and etc. by adjusting the clock arrival times of registers. The procedure of determining the clock arrival timings of registers is called *clock scheduling* [56].

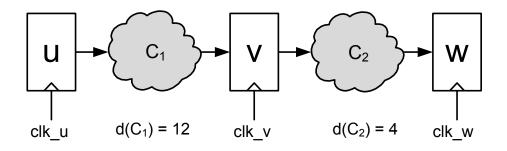

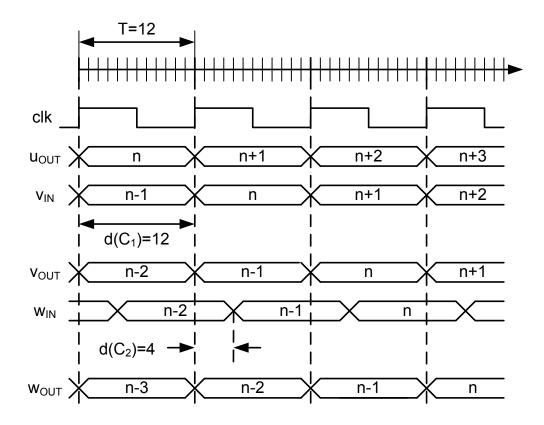

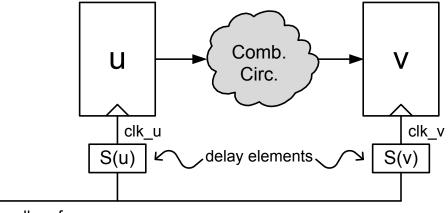

In order to illustrate how the clock period of a synchronous circuit can be minimized by clock scheduling, consider the example circuit in Fig. 2.1. The circuit consists of three stages of registers, u, v and w, with combinational parts in between. Let the propagation delays of combinational parts  $C_1$  and  $C_2$  be 12 units and 4 units, respectively. The minimum clock period for the fully-synchronous clocking scheme is 12 units for this circuit, assuming zero clock skews among the registers. If there are clock skews, the minimum clock period is even required to be larger. However, if a skew of 4 units is applied to the clock line of register v, the circuit can operate with a minimum clock period of 8 units. The time that the output of register v stays idle after propagating to the input of register w is *stolen* and given to register u which has a longer propagation delay. Figures 2.2 and 2.3 show the signal waveforms for the example circuit without and with clock scheduling respectively. This method, proposed by Fishburn, is called *cycle stealing* or *cycle borrowing*.

This chapter starts with the basics of clock scheduling and general synchronous framework.

Figure 2.1: The example circuit for illustrating the clock period minimization by cycle stealing method. The circuit consists of three stages of registers and combinational parts in between.

Figure 2.2: Input and output signal waveforms of the registers of the circuit in Fig 2.1 for fully synchronous operation. All the registers are clocked by the same clock with a period of 12 units.

Figure 2.3: Input and output signal waveforms of the registers of the circuit in Fig 2.1 for semi synchronous operation. With the application of 4 units of delay to the clock signal of register v, the minimum clock period of the circuit is decreased from 12 units to 8 units. Circuit speed improvement with cycle stealing is illustrated.

The constraints for proper operation of a synchronous circuit and the graph representation of these constraints are discussed in the first section. The second section starts with a brief explanation of systems of difference equations, that are used for representing the constraints for a sequential circuit. The solution of such systems to be used in clock scheduling is also explained. Then, the theory behind the algorithm for finding the minimum clock period is discussed in detail. In the third section, the algorithm for finding the minimum clock period of a semi-synchronous circuit and the algorithm for clock scheduling to operate the circuit with the minimum clock period is explained. The fourth section covers the algorithms used for scheduling a circuit with minimum cost to a given infeasible target clock schedule. Finally, in the fifth section the *clock scheduling engine* that combines these algorithms into a complete

clk\_ref

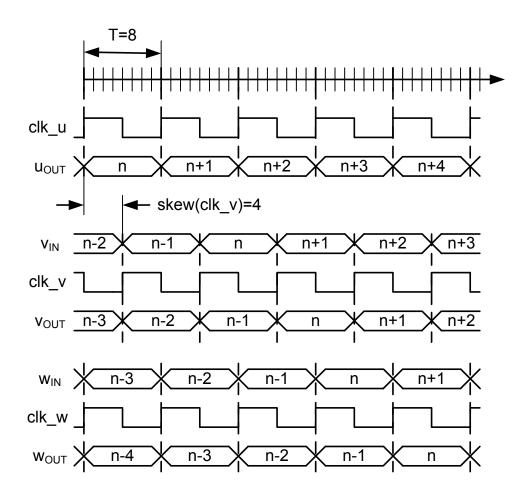

Figure 2.4: Two registers with data path taken as a part of a synchronous circuit

clock scheduling system is discussed.

#### 2.1 General Synchronous Framework

In semi-synchronous circuits the registers are not necessarily simultaneously clocked. The time at which the clock edge arrives at a register v with respect to an arbitrarily chosen, maybe hypothetical, reference register is called the *clock timing* of register v, and denoted by s(v). The clock timings of all registers in a semi-synchronous circuit is called the *clock schedule* of the circuit, S(v). Note that the clock timing of a register is not required to be a unique value; rather, the clock timing can be determined as a range of values. The *clock timing range* of register v denoted by r(v), is defined as the range of clock timings for that register [56] :

$$r(v) = [s_{min}(v), s_{max}(v)].$$

(2.1)

*Clock scheduling* is the procedure of determining the clock timings of registers of a semisynchronous circuit [56].

There are two data race mechanisms that may cause failure in synchronous systems [3] such as the one shown in Figure 2.4. The two registers, u and v, are clocked with different clock timings, S(u) and S(v), respectively, and the delay of the combinational path is d. If s(u) + d < s(v), the output data of register u will be sampled twice by the same clock edge, which is called *double-clocking hazard*. Furthermore, if s(u) + d > s(v) + T, where T is the clock period, data will not be sampled at all, i.e. data will be lost, which is called *zero*-

Figure 2.5: Timing diagram for setup and hold time constraints

*clocking hazard.* In other words, the output of register *u* should arrive at register *v* between s(v) and s(v) + T for proper operation without hazards. (See Figure 2.5)

For proper register operation the data should be stable at the register input during the time interval:

$$s(v) - setup(v) < t < s(v) + hold(v),$$

$$(2.2)$$

where setup(v) is the setup time and hold(v) is the hold time of register v. If the output of register u arrives at register v before s(v), it will be a violation of the *setup-time constraint*, if it arrives later than s(v) + T, it will be a violation of the *hold-time constraint*.

In general, two types of constraints must be satisfied for each register pair with signal propagation in order to eliminate the clocking hazards and assure the correct operation of a semisynchronous circuit [13, 25]. Hold (No Double-Clocking) Constraint:

$$s(v) - s(u) \le d_{min}(u, v), \tag{2.3}$$

Setup (No Zero-Clocking) Constraint:

$$s(u) - s(v) \le T - d_{max}(u, v),$$

(2.4)

where  $d_{min}(u, v)$  is the minimum propagation delay from register u to v, and  $d_{max}(u, v)$  is the maximum propagation delay from register u to v along the combinational path between the two registers. As more precisely defined in [25];

$$d_{min}(u,v) = d'_{min}(u,v) - hold(v) - margin_h(v), \qquad (2.5)$$

where  $d'_{min}(u, v) (\geq 0)$  is the minimum propagation delay from register *u* to register *v*,  $hold(v) (\geq 0)$  is the hold time of register *v*,  $margin_h(v) (\geq 0)$  is the predefined timing margin. Similarly;

$$d_{max}(u,v) = d'_{max}(u,v) + setup(v) + margin_s(v),$$

(2.6)

where  $d'_{max}(u, v) \ge 0$  is the maximum propagation delay from register *u* to register *v*, setup(v) ( $\ge 0$ ) is the setup time of register *v*, margin<sub>s</sub>(v) ( $\ge 0$ ) is the predefined timing margin. The timing margin is useful in practical aspects such as securing the feasibility in realizing the clock-timing, securing the reliability of the circuit and providing more room for optimization of circuit performance.

There may be timing constraints for the inputs and outputs of the circuit arising from the interaction of the circuit with other circuits, modules, etc. In order to handle these types of constraints, hypothetical registers outside the circuit with fixed clock timings are assumed to be connected to the inputs and the outputs of the circuit [34]. In the constraint inequalities, the constant input arrival time replaces s(u) for input constraints, and the constant output required time replaces s(v) for output constraints.

A clock schedule is said to be *feasible* for some clock period T if all the constraints are satisfied by that clock schedule for that clock period [10], i.e. there are no hazards or setup/hold time violations and the circuit operates properly.

In order to find a feasible clock schedule, all the constraints should be satisfied at the same time, which requires solving many equations at once. A *constraint graph* G(V, E) is used to

Figure 2.6: Example circuit [58]

represent these constraints [10], [25], [27], [46], [56]. A vertex  $v \in V$  in the graph corresponds to a register in the circuit. If a group of registers in the circuit are constrained to be clocked simultaneously, they should be represented by a single vertex in the constraint graph [10]. A directed edge  $(u, v) \in E$  in the graph corresponds to either a setup or a hold constraint, named as *setup edge* or *hold edge* respectively. The edge weight  $\omega(u, v)$  is  $d_{min}$  for hold edges and  $T - d_{max}$  for setup edges. Hence, in the constraint graph each directed edge represents the constraint:

$$s(v) - s(u) \le \omega(u, v). \tag{2.7}$$

The constraint graph G for clock period T is denoted by  $G_T$ , similarly the edge weight  $\omega(u, v)$  for clock period T is denoted by  $\omega_T(u, v)$ . The *slack* of an edge is defined as:

$$\Delta_T(u,v) = s(u) + \omega_T(u,v) - s(v).$$

(2.8)

An edge (u, v) is *legal* if  $s(v) - s(u) \le \omega_T(u, v)$ , i.e.,  $\Delta_T(u, v) \ge 0$ ; and it is *illegal* otherwise. An edge with zero slack is called *critical edge*. A clock schedule is feasible for a clock period *T* if there is no illegal edge in the constraint graph [27], i.e. all constraints are satisfied. A feasible clock schedule is not necessarily unique, since each register may have a range of possible clock timings. A set of clock ranges is said to be *consistent* if a feasible clock schedule is obtained for any clock timing, s(v), chosen within the clock timing range, r(v), for each register  $v \in V$  [56].

An example circuit with corresponding constraint graph is given in Fig. 2.6 and Fig. 2.7, respectively. Note that one vertex is assigned for the two inputs since the input timings are assumed to be equal, and another vertex is assigned for the output since the output required

Figure 2.7: Constraint graph of the example circuit

time is assumed to be different than the input timings. Also note that, a single *host* register for representing the inputs and outputs is used if input and output timings are the same.

#### 2.2 Systems of Difference Constraints

The constraints for a sequential circuit to operate without hazards for a given clock schedule are presented in Section 2.1. These constraints are in the form of *difference constraints*. Consider a set of m difference constraints, involving n unknowns, each being a simple linear inequality in the form:

$$x_j - x_i \le b_k, \tag{2.9}$$

where,  $1 \le i, j \le n$  and  $1 \le k \le m$ . This is a system of difference constraints represented as:

$$Ax \le b, \tag{2.10}$$

where *A* is an  $m \times n$  matrix, which contains a single "1" and a single "-1" in each row with all remaining entries being "0"; *b* is an *m*-vector and *x* is an *n*-vector, where  $x_i$ 's are the unknowns. In order to find the minimum feasible clock period of the circuit, the objective is to find any *feasible solution*, *x*, that satisfies  $Ax \le b$  or to determine that no feasible solution exists. As the following lemma suggests a feasible clock schedule is not unique.

**Lemma 2.2.1** Let  $x = (x_1, x_2, ..., x_n)$  be a solution to the system of difference constraints,  $Ax \le b$ , and let d be any constant. Then  $x + d = (x_1 + d, x_2 + d, ..., x_n + d)$  is also a solution to  $Ax \le b$  as well [59].

**Proof.** For each  $x_i$  and  $x_j$ :

$$(x_i + d) - (x_i + d) = x_i - x_i.$$

(2.11)

Thus, if x satisfies  $Ax \le b$ , so does x + d [59].

It is practical to represent the systems of difference constraints with constraint graphs and interpret them graph-theoretically [59]. The system  $Ax \le b$  with *n* unknowns and *m* inequalities can be represented by a constraint graph G(V, E) with *n* vertices and *m* directed edges. Each vertex  $v_i$  in the graph corresponds to an unknown  $x_i$  with  $1 \le i \le n$ , and each directed edge  $(x_i, x_j)$  with weight  $b_k$  in the graph represents one of *m* inequalities in the form  $x_j - x_i \le b_k$ . More formally, given a system  $Ax \le b$  of difference constraints, corresponding constraint graph G(V, E) is a weighted, directed graph with:

$$V = \{v_0, v_1, \dots, v_n\},$$

(2.12)

and

$$E = \{(v_i, v_j) : x_j - x_i \le b_k \text{ is a constraint}\} \bigcup \{(v_0, v_1), (v_0, v_2), \dots, (v_0, v_n)\}.$$

(2.13)

Note that, an additional vertex  $v_0$  is added to guarantee that every other vertex is reachable from  $v_0$ . This vertex is named as *source* or *root*. In the constraint graph, the weight of directed edge  $(v_i, v_j)$  is  $\omega(v_i, v_j) = b_k$  corresponding to the constraint inequality  $x_j - x_i \le b_k$ . The weight of each edge,  $(v_0, v_i)$ , leaving the source vertex is zero, that is:

$$\omega(v_0, v_i) = 0 \ \forall v_i \in V. \tag{2.14}$$

The *weight* of a path is defined as the sum of the weights of all edges in the path. The *distance* of a vertex from the source is defined as the weight of the shortest path among all paths between the source and the vertex [25], [59]. The distance of vertex  $v_i$ , from the source,  $v_0$ , is denoted by  $\delta(v_0, v_i)$  or  $\delta(v_i)$ . A *cycle* is a set of edges, where the source vertex of the first edge and the target vertex of the last edge are the same, with no other mutual vertices among edges. A cycle is called a *critical cycle* if the sum of the weights of the edges in the cycle is zero [61].

**Lemma 2.2.2** (*Triangle Inequality*) Let G(V, E) be a weighted, directed graph with weight function  $w : E \to \Re$  and source vertex s. If G contains no negative-weight cycle, then the following inequality must be satisfied for all edges  $(u, v) \in E$  [59]:

$$\delta(s, v) \le \delta(s, u) + \omega(u, v). \tag{2.15}$$

**Proof.** Let p be a shortest path from source s to vertex v. Then, the weight of p is not more than the weight of any other path from s to v. Specifically, the weight of path p, is not more than the weight of the particular path that consists of the shortest path from source s to vertex u and edge (u, v)[59].

The following theorem states that, utilizing shortest path algorithms on the constraint graph determines the existence of a solution to the constraint system and finds a feasible solution, if exists.

**Theorem 2.2.3** Let G(V, E) be the corresponding constraint graph of a system of difference constraints,  $Ax \le b$ . If G contains no negative-weight cycles, then a feasible solution for the system is given by [59]:

$$x = (\delta(v_0, v_1), \delta(v_0, v_2), \delta(v_0, v_3), \dots, \delta(v_0, v_n)).$$

(2.16)

Moreover, if G contains a negative-weight cycle, then there is no feasible solution for the system [59].

**Proof.** Consider any edge  $(v_i, v_j) \in E$  of the constraint graph G. By the triangle inequality,

$$\delta(v_0, v_j) \le \delta(v_0, v_i) + \omega(v_i, v_j), \tag{2.17}$$

or equivalently,

$$\delta(v_0, v_i) - \delta(v_0, v_i) \le \omega(v_i, v_i). \tag{2.18}$$

Thus, letting  $x_i = \delta(v_0, v_i)$  and  $x_j = \delta(v_0, v_j)$  satisfies the difference constraint that corresponds to edge  $(v_i, v_i)$ :  $x_j - x_i \le \omega(v_i, v_j)$ . Hence, if the constraint graph contains no negative-weight cycles, then (2.16) gives a feasible solution [59].

Suppose that the constraint graph *G* has a negative-weight cycle. Without loss of generality, let the negative-weight cycle be  $C = \langle v_1, v_2, \dots, v_k, v_1 \rangle$ . Note that, source vertex  $v_0$  can not

be on the negative cycle, since it has no entering edges. The edges in cycle C represents the following difference constraints:

$$x_2 - x_1 \le \omega(v_1, v_2),$$

(2.19)

$$x_3 - x_2 \le \omega(v_2, v_3),$$

(2.20)

$$x_4 - x_3 \le \omega(v_3, v_4),$$

(2.21)

$$x_k - x_{k-1} \le \omega(v_{k-1}, v_k),$$

(2.22)

$$x_1 - x_k \le \omega(v_k, v_1). \tag{2.23}$$

Suppose that, there is a solution for x that satisfies each of the k inequalities. Then, this solution must also satisfy the sum of these k inequalities:

÷

$$x_{2} - x_{1} + x_{3} - x_{2} + \dots + x_{k} - x_{k-1} + x_{1} - x_{k} \le \omega(v_{1}, v_{2}) + \omega(v_{2}, v_{3}) + \dots + \omega(v_{k-1}, v_{k}) + \omega(v_{k}, v_{1}),$$

(2.24)

which reduces to:

$$0 \le \omega(C), \tag{2.25}$$

because on the left-hand side of the inequality each unknown is added once and subtracted once. On the right-hand side of the inequality, the weights of all the edges in the cycle C are summed up to be the weight of the cycle C. But since C is a negative-weight cycle,

$$\omega(C) < 0, \tag{2.26}$$

resulting in a contradiction:

$$0 \le \omega(C) < 0. \tag{2.27}$$

Thus, there is no feasible solution for a constraint system, if there is a negative-weight cycle in the corresponding constraint graph.  $\Box$

As shown by Theorem 2.2.3, shortest path algorithms such as Bellman-Ford Algorithm can be used to solve systems of difference constraints. Note that Dijkstra's Algorithm is useless due to the existence of negative-weight edges in the constraint graph. The added source vertex  $v_0$  guarantees that, any negative-weight cycle in the constraint graph is reachable from source vertex  $v_0$ , since there are out-edges from  $v_0$  to all the other vertices in the constraint graph. Bellman-Ford Algorithm converges, i.e., the distances of all vertices are finite, if there is no negative-weight cycle in the constraint graph. If Bellman-Ford Algorithm returns TRUE, the distance of each vertex to the source gives a feasible solution to the system of difference constraints. If Bellman-Ford Algorithm returns FALSE, it means a feasible solution to the system of difference constraints does not exist. The constraint graph G(V, E) for a system of *m* difference constraints with *n* unknowns, has n + 1 vertices and n + m edges. Hence, Bellman-Ford Algorithm solves the system in  $O((n + 1)(n + m)) = O(n^2 + nm)$  time [59].

**Lemma 2.2.4** A clock period T is feasible, if constraint graph  $G_T$  for that clock period contains no negative cycle [61].

**Proof.** Follows directly from Theorem 2.2.3.

**Lemma 2.2.5** If a clock period T is not feasible, then the clock period  $T' \leq T$  is not feasible [61].

**Proof.** If clock period *T* is not feasible, then there is a negative-weight cycle in the constraint graph  $G_T$ . Let *C* be the negative-weight cycle, consisting of hold-edges  $C_h$  and setup-edges  $C_s$ , then:

$$\omega(C) = \sum_{e_h \in C_h} d_{min}(u, v) + \sum_{e_s \in C_s} T - d_{max}(u, v) \le 0, \qquad (2.28)$$

where  $e_h = (u, v)$  is a hold edge and  $e_s = (u, v)$  is a setup edge of the negative-weight cycle.

For  $T' \leq T$ :

$$\sum_{e_s \in C_s} T' - d_{max}(u, v) \leq \sum_{e_s \in C_s} T - d_{max}(u, v), \qquad (2.29)$$

Hence;

$$\sum_{e_h \in C_h} d_{min}(u, v) + \sum_{e_s \in C_s} T' - d_{max}(u, v) \le \sum_{e_h \in C_h} d_{min}(u, v) + \sum_{e_s \in C_s} T - d_{max}(u, v) \le 0.$$

(2.30)

Thus, C will be a negative-weight cycle for clock period T', thus T' is not feasible.  $\Box$

**Lemma 2.2.6** If a clock period T is feasible, then the clock period  $T' \ge T$  is also feasible [61].

**Proof.** Assume that T' is not feasible. Then, by Lemma 2.2.5,  $T \le T'$  is not feasible, which is a contradiction. Hence, T' is feasible [60].

**Lemma 2.2.7** (Upper Bound on Clock Period) An upper bound,  $U_T$ , on the clock period is given by [25], [60]:

$$T \leq U_T = \max_{(u,v)\in E_S} \left\{ d_{max}(u,v) \right\} < \infty.$$

(2.31)

**Proof.** From the setup edge constraint given in 2.4, for zero clock skew condition, i.e., all registers are scheduled at 0:

$$T \leq d_{max}(u, v), \tag{2.32}$$

which is a feasible clock period for even the zero clock skew case and an upper bound for the minimum feasible clock period [25], [60].  $\Box$

**Lemma 2.2.8** (Lower Bound on Clock Period) A lower bound,  $L_T$ , on the clock period is given by [25], [60]:

$$T \geq L_T = \max\left\{\max_{(u,u)\in E_s} \{d_{max}(u,u)\}, \max_{(u,v)\in E} \{d_{max}(u,v) - d_{min}(u,v)\}\right\} \geq 0,$$

(2.33)

where  $d_{max}(u, u) = 0$  if there is no signal path from a register to the same register, and  $E_S$  is the set of all setup edges.

**Proof.** The propagation delay from a register to the same register is obviously a lower bound on the clock period [25], [60].

For the second term, consider the setup and hold edge constraints given in (2.3) and (2.4) respectively, which are satisfied for each register pair with signal propagation:

$$s(v) - s(u) \le d_{min}(u, v),$$

(2.34)

$$s(u) - s(v) \le T - d_{max}(u, v).$$

(2.35)

Summing both sides of the inequalities gives:

$$0 \le T - d_{max}(u, v) + d_{min}(u, v), \tag{2.36}$$

Hence;

$$d_{max}(u,v) - d_{min}(u,v) \le T,$$

(2.37)

for all (u, v), for a feasible clock period T, which also holds for minimum feasible clock period  $T_{min}$ :

$$d_{max}(u,v) - d_{min}(u,v) \le T_{min},\tag{2.38}$$

for all edges (u, v). Hence, a lower bound for minimum feasible clock period:

$$\max_{(u,v)\in E} \left\{ d_{max}(u,v) - d_{min}(u,v) \right\} \le T_{min}.$$

(2.39)

Consequently, the lower bound is the maximum of the two terms.

**Theorem 2.2.9** A finite solution to the clock period minimization problem exists [60].

**Proof.** Following directly from Lemmas' 2.2.7 and 2.2.8, the minimum feasible clock period is bounded by:

$$0 \le L_T \le T \le U_T < \infty. \tag{2.40}$$

$\square$

For the sake of completeness, the following lemmas from [61] are given without proof.

**Lemma 2.2.10** The constraint graph contains at least one critical cycle when the clock period is the minimum feasible clock period [61].

**Lemma 2.2.11** For the constraint graph with a feasible clock schedule; each directed edge in the critical cycle is a critical edge [61].

### 2.3 Minimum Feasible Clock Period

Theorem 2.2.9 states that the minimum clock period of a given sequential circuit is finite and bounded. Moreover, Theorem 2.2.3 states that shortest path algorithms such as Bellman-Ford Algorithm can determine if a clock period is feasible or not. Thus a binary search can be made to find the minimum feasible clock period [12], [25], [60]. The algorithm for finding the minimum feasible clock period similar to those in [12], [12], [60], is given in Figure 2.8. A binary search is made for the minimum feasible clock period in the interval bounded by the upper and lower bounds given in Lemmas 2.2.7, and 2.2.8, where at each step the interval is halved until the minimum feasible clock period is determined with an error less than  $\epsilon$ . The upper and lower bounds are checked before the binary search is initiated. If the lower bound is feasible, then it is returned as the minimum feasible clock period. If the upper bound is not feasible, the algorithm returns *infinity*, meaning that there is no feasible clock period.

# **Procedure MinClock**(G(V, E)) **Input:** constraint graph G(V, E)**Output:** minimum feasible clock period *T*

```

1: L_{self} := \max_{(u,u) \in E} d_{max}(u, u)

2: L_{diff} := \max_{(u,v) \in E} \{ d_{max}(u,u) - d_{min}(u,v) \}

3: L := \max\{L_{self}, L_{diff}\}

4: T := \max_{(u,v) \in E} d_{max}(u, v)

5: if IsNoNegCycle(G, L) = "Yes" then

return L

6:

7: end if

8: if IsNoNegCycle(G, T) = "No" then

return ∞

9:

10: end if

11: while T - L \ge \epsilon do

M := (T + L)/2

12:

if IsNoNegCycle(G, T) = "Yes" then

13:

14:

T := M

15:

else

L := M

16:

end if

17:

18: end while

19: return T

```

Figure 2.8: Minimum feasible clock period algorithm.

At each step of the binary search, the feasibility of the clock period is checked using Bellman-Ford Algorithm. If there is a negative-weight cycle in the graph, Bellman-Ford Algorithm does not converge and the update procedure is repeated as many times as the number of vertices. Hence, a negative-weight cycle detection method is needed to determine the existence of a negative-weight cycle in the graph at early stages.

There are a number of negative-weight cycle detection strategies [57], one of which is the "walk-to-the-root" method. In "walk-to-the-root" method, a negative-weight cycle is detected by following parent pointers from a vertex. If source *s* is not reachable from a vertex, that means there is a negative-weight cycle in the graph. In [57], the checking is made before the labeling operation with respect to edge (u, v). If *v* is reached on the way from *u* to *s*, negative cycle is detected since the labeling with respect to (u, v) will create a negative cycle. In [25], a slightly modified walk-to-the-root method is proposed, where the checking is made after all the labeling operations to the neighbors of *u* are finished. If these labeling operations create a cycle, the path from *u* contains *u*. Also, labeling from *u* to *r* creates a negative cycle; which is

**Procedure IsNoNegCycle**(G(V, E), T) **Input:** constraint graph G(V, E), clock period T**Output:** Yes or No

1: Construct  $G_T$ , add source vertex *s*, add edges { (s, u) :  $\forall u \in V$ ,  $\omega(s, u) = 0$  } // Init. 2:  $Q_1 \leftarrow \emptyset, Q_2 \leftarrow \emptyset$  // Init. 3: for all  $v \in V$  do  $\delta(v) := \infty$  // Initially all distances set to infinity 4: 5: end for 6:  $\delta(s) = 0$ , push s to  $Q_1$  // Init. 7: while  $Q_1$  is not empty do // Update Procedure (steps 7-21)  $u \leftarrow pop(Q_1)$ 8: 9: for all v adjacent to u in G do if  $\delta(v) \ge \delta(u) + \omega_T(u, v)$  then // Labeling operation (steps 10-16) 10:  $\delta(v) := \delta(u) + \omega_T(u, v)$ 11: set parent pointer from v to u 12: 13: if v is not in  $Q_2$  then push v to  $Q_2$ 14: 15: end if end if 16: end for 17: 18: if reach *u* by following parent pointer from *u* then *//* Negative-weight cycle exists! return "No" 19: 20: end if 21: end while 22: if  $Q_2$  is empty then // No negative-weight cycle 23: return "Yes" 24: end if 25:  $Q_1 \leftarrow Q_2, Q_2 \leftarrow \emptyset$ 26: goto step 7

Figure 2.9: Negative cycle detection algorithm: Bellman-Ford Algorithm with modified walk-to-the-root strategy.

also checked by the algorithm. Note that in [25], a *root* vertex r, is selected among the vertices instead of adding to the constraint graph a *source* node s, with only out-edges. Hence, the labeling from u to r needs to be checked as a part of walk-to-the-root method.

In this work, a slightly modified version of the approach in [25] is used. A source node s, with only out edges is added to the constraint graph in the beginning and the negative-weight cycle checking is made at a vertex after all labeling operations are made from that vertex. By this way, the checking of labeling from u to s is eliminated since the source vertex does not have any entering edges. The overhead of "walk-to-the-root" method for constraint graphs is less than 1% for graphs with no negative-weight cycles [25].

The accuracy of the algorithm depends on the determination of propagation delays of the elements in the circuit. Neglecting the dependence of the propagation delay on the load capacitance value or using coarsely tabulated values may cause errors in minimum clock period calculation. In this work, the variation of the propagation delay of each gate type with respect to the load capacitance value is modelled as discussed in Subsection 4.1.1. The propagation delay of each gate according to the actual capacitive load of the gate in the circuit is estimated by using the model and the constraint graph is constructed accordingly.

Let *n* be the number of vertices, *m* be the number of edges and *k* be the number of distinct edges in a shortest trail. The time complexity of the initialization (steps 1-6) is O(n); the time complexity of the labeling operation (steps 10-16) is O(1); the time complexity of walk-to-the-root (steps 18-20) is O(k). Update procedure (steps 7-21) is repeated at most *k* times and in each update, labeling is made at most *m* times and walk-to-the-root is done at most *n* times [25]. Hence, the time complexity of the negative-weight cycle detection algorithm is:

$$O(n) + k \cdot (m \cdot O(1) + n \cdot O(k)) = O(km + kn^{2}).$$

(2.41)

The time complexity of the negative-weight cycle detection algorithm in this work is the same as that in [25], which is better than that in [57] with a minor difference.

The time complexity of finding upper and lower bounds for the binary search algorithm are O(m). Hence, the time complexity of the minimum-feasible clock period algorithm is:

$$O(\gamma(km+kn^2)), \tag{2.42}$$

where  $\gamma$  is the number of repetitions [25]. Experimentally, k < 100 and  $\gamma < 20$  are found for most circuits.

#### 2.4 Minimum Cost Scheduling

The *cost* of a clock schedule is defined as the sum of differences between the clock schedule S and a target clock schedule O for all registers of a circuit [25], [27]. Minimum cost scheduling algorithm finds a feasible clock schedule S of a circuit for a given clock period T, with minimum cost from a given target clock schedule O. Obviously, if the target clock schedule is feasible, this is an easy task. Hence, throughout the discussion in this section, the target clock schedule is assumed to be infeasible.

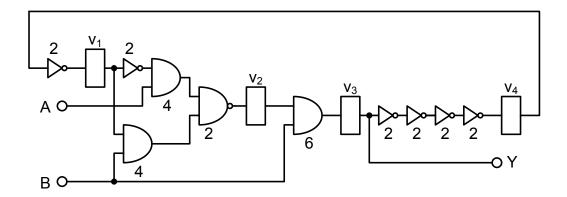

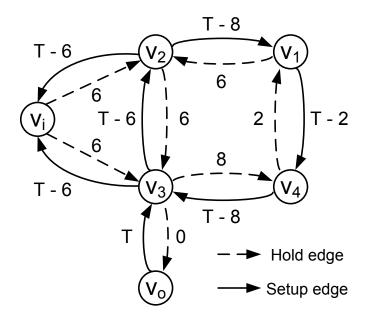

Figure 2.10 shows the minimum cost scheduling algorithm. Firstly, an initial feasible clock schedule is found by using the Bellman-Ford algorithm as shown in Fig. 2.11. This algorithm simply chooses a *root* vertex and calculates the distance of every node with respect to the *root*. The distance of a register to the root  $\delta(r, v)$ , is assigned as the initial clock timing of each register, i.e.,  $s(v) = \delta(v)$ . Then, the clock timing s(v) of each register v is replaced with s(v) - o(v), regarding the target clock timing of each register as zero. The initial clock schedule is iteratively improved, by using TryDec and TryInc given in Figs. 2.12 and 2.13, respectively. The iterations continue until no further improvement can be made on the initial clock schedule. After all the iterations are finished, the clock timing s(v) of each register v is replaced by s(v) + o(v).

FindCRD algorithm [27], finds a set of registers such that the overall cost can be reduced by decreasing the clock timing of each register in the set by the same amount. The optimal amount of decrease is calculated by TryDec. Similarly, FindCRI algorithm, finds a set of registers such that the overall cost can be reduced by increasing the clock timing of each register in the set by the same amount. The optimal amount of increase is calculated by TryInc.

#### 2.4.1 Finding the Optimal Amount of Clock Timing Adjustment

Let G(V, E) be a constraint graph of a circuit with a feasible clock schedule S and let  $R \subseteq V$  be a set of registers of the circuit. Consider another clock schedule for the same circuit S' such that:

$$s'(v) = \begin{cases} s(v) - \alpha, & \text{if } v \in R \\ s(v), & \text{otherwise.} \end{cases}$$

(2.43)

If vertices *u* and *v* are both in *R* or are both in  $V \setminus R$ , the edge (u, v) is legal. The condition for the edge (u, v) to be legal in *S'* when  $u \in R$  and  $v \notin R$  is:

$$s(v) - (s(u) - \alpha) \le \omega(u, v). \tag{2.44}$$

Hence;

$$\alpha \le s(u) - s(v) + \omega(u, v) = \Delta(u, v). \tag{2.45}$$

**Procedure MinCost**( $G_T(V, E_T), O$ ) **Input:** Constraint graph  $G_T(V, E_T)$ , target clock timing of all registers,  $O = \{ o(v) : \forall v \in V \}$ **Output:** Clock schedule  $S = \{ s(v) : \forall v \in V \}$

```

1: FindInitialSchedule(G_T(V, E_T)) // Get an initial feasible clock-schedule

2: if s(v) = o(v) forall v \in V then

return S

3:

4: end if

5: for all v \in V do

s(v) := s(v) - o(v)

6:

7: end for

8: do

9:

do

S := \operatorname{TryDec}(G_T, S)

10:

while S is modified

11:

12:

do

S := \mathbf{TryInc}(G_T, S)

13:

while S is modified

14:

15: while S is modified

16: for all v \in V do

17:

s(v) := s(v) + o(v)

18: end for

19: return S

```

Similarly the condition for the edge (u, v) to be legal in S' when  $u \notin R$  and  $v \in R$  is:

$$(s(v) - \alpha) - s(u) \le \omega(u, v). \tag{2.46}$$

Hence;

$$-\Delta(u, v) = s(u) - s(v) + \omega(u, v) \le \alpha.$$

(2.47)

Thus, S' is feasible if and only if [25]:

$$L_R \le \alpha \le U_R,\tag{2.48}$$

where,

$$L_{R} = \max_{u \notin R, v \in R} \{ -\Delta(u, v) \},$$

(2.49)

$$U_R = \max_{u \in R, v \notin R} \{\Delta(u, v)\}.$$

(2.50)

In order to minimize the cost of clock schedule S', clock timings of registers in R should be changed by such an amount that, at the end the number of registers with positive clock timing

# **Procedure FindInitialSchedule**(G(V, E)) **Input:** Constraint graph G(V, E)**Output:** Clock schedule $S = \{ s(v) : \forall v \in V \}$

- 1: Select a *root* node, *r*

- 2: Calculate the distance  $\delta(r, v)$  of every node  $v \in V$  to the root *r* using Bellman-Ford Algorithm

- 3: for all  $v \in V$  do

- 4:  $s(v) = \delta(r, v)$

- 5: **end for**

- 6: **return** *S*

Figure 2.11: Algorithm that finds an initial feasible clock schedule.

is equal to the number of registers in with negative clock timing. If such a clock schedule is infeasible, then the difference between the number of registers with positive clock timing and the number of registers with negative clock timing should be minimized [27].

As defined in [27]; let  $\beta$  be zero, if the number of registers in *R* is even and  $\lfloor \frac{n+1}{2} \rfloor$ -th largest clock timing in *R* is non-negative in *S* and  $\lceil \frac{n+1}{2} \rceil$ -th largest clock-timing in *R* is non-positive in *S*. Otherwise, let  $\beta$  be the  $\lfloor \frac{n+1}{2} \rfloor$ -th largest clock timing of registers in *R* in *S*. The following lemma states the optimum amount of clock timing adjustment that minimizes the cost of the clock scheduling,  $\alpha$ , in terms of  $\beta$ .

**Lemma 2.4.1** The optimal  $\alpha$ , that minimizes the cost of S' is [27]:

$$\alpha_{opt} = \begin{cases} \beta, & L_R \le \beta \le U_R \\ L_R, & \beta \le L_R \\ U_R, & U_R \le \beta \end{cases}$$

(2.51)

Obviously, if  $\alpha_{opt}$  is zero, the cost of the clock scheduling can not be changed by the set of registers. For the set of registers to reduce the cost,  $\alpha_{opt}$  must be positive or negative.  $\alpha_{opt}$  is negative if and only if both  $L_R$  and  $\beta$  are negative, that is, there is no critical *in-edge* to *R* in *S*, and the number of registers in *R* with negative clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S*. Similarly,  $\alpha_{opt}$  is positive if and only if both  $B_R$  and  $\beta$  are positive, that is, there is no critical *out-edge* from *R* in *S*, and the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S*. Similarly,  $\alpha_{opt}$  is positive if and only if both  $B_R$  and  $\beta$  are positive, that is, there is no critical *out-edge* from *R* in *S*, and the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with positive clock timing in *S* is larger than the number of registers in *R* with

**Procedure TryDec**( $G_T(V, E_T), S$ ) **Input:** Constraint graph  $G_T(V, E_T)$ , and current clock schedule  $S = \{s(v) : \forall v \in V\}$ **Output: TRUE** or **FALSE**

1:  $R \leftarrow \emptyset$ 2:  $\beta := 0, \alpha_{opt} := 0$ 3: R :=**FindCRD**( $G_T(V, E_T)$ ) 4: if *R* is empty then return FALSE 5: 6: **end if** 7:  $U_R := \min_{u \in R, v \notin R} (\Delta(u, v))$ 8:  $L_R := \max_{u \notin R, v \in R} (-\Delta(u, v))$ 9: if number of vertices in *R* is odd then  $\beta := \left| \frac{n+1}{2} \right|$ -th largest clock-timing in *R* 10: 11: else if  $\left|\frac{n+1}{2}\right|$ -th largest clock-timing in R is non-negative and  $\left[\frac{n+1}{2}\right]$ -th largest clock-timing in *R* is non-positive **then**  $\beta := 0$ 12: 13: end if 14: if  $L_R \leq \beta \leq U_R$  then  $\alpha_{opt} := \beta$ 15: 16: else if  $\beta < L_R$  then  $\alpha_{opt} := L_R$ 17: 18: else if  $U_R < \beta$  then 19:  $\alpha_{opt} := U_R$ 20: end if 21: for all  $v \in R$  do 22:  $s(v) := s(v) - \alpha_{opt}$ 23: end for 24: return TRUE

Figure 2.12: TryDec algorithm

negative clock timing in S. The methods of finding such sets of registers will be discussed in the next subsection.

#### 2.4.2 Finding Cost Reducible Register Sets

A set of registers R is called *cost reducible by decrease* (CRD), if the cost of the clock schedule can be reduced by decreasing the clock timing of each register in R by the same amount without violating the setup and hold time constraints [25]. Similarly, a set of registers R is called *cost reducible by increase* (CRI), if the cost of the clock schedule can be reduced by increasing the clock timing of each register in R by the same amount without violating the **Procedure TryInc**( $G_T(V, E_T), S$ ) **Input:** Constraint graph  $G_T(V, E_T)$ , and current clock schedule  $S = \{s(v) : \forall v \in V\}$ **Output: TRUE** or **FALSE**

1:  $R \leftarrow \emptyset$ 2:  $\beta := 0, \alpha_{opt} := 0$ 3: R :=**FindCRI**( $G_T(V, E_T)$ ) 4: **if** *R* is empty **then** return FALSE 5: 6: **end if** 7:  $U_R := \min_{u \in R, v \notin R} (\Delta(u, v))$ 8:  $L_R := \max_{u \notin R, v \in R} (-\Delta(u, v))$ 9: if number of vertices in *R* is odd then  $\beta := \left| \frac{n+1}{2} \right|$ -th largest clock-timing in *R* 10: 11: else if  $\left|\frac{n+1}{2}\right|$ -th largest clock-timing in *R* is non-negative and  $\left[\frac{n+1}{2}\right]$ -th largest clock-timing in *R* is non-positive **then**  $\beta := 0$ 12: 13: end if 14: if  $L_R \leq \beta \leq U_R$  then  $\alpha_{opt} := \beta$ 15: 16: else if  $\beta < L_R$  then  $\alpha_{opt} := L_R$ 17: 18: else if  $U_R < \beta$  then 19:  $\alpha_{opt} := U_R$ 20: end if 21: for all  $v \in R$  do  $s(v) := s(v) - \alpha_{opt}$ 22: 23: end for 24: return TRUE

Figure 2.13: TryInc algorithm

setup and hold time constraints.

In order for a set of registers to be a cost reducible set, the optimum amount of adjustment,  $\alpha_{opt}$ , of the registers must be non-zero. If  $\alpha_{opt}$  is negative, the set is a CRI set; if  $\alpha_{opt}$  is positive, the set is a CRD set.

As Lemma 2.4.1 suggests, given a constraint graph G(V, E) with a clock schedule S; a set of registers R, is a CRD set if there is no critical out-edge from R in S and the number of registers in R with positive clock timing in S is larger than the number of registers in R with negative clock timing in S [25]. Considering the critical graph  $G_C(V, E_C)$ , consisting of only the critical edges of G(V, E), and labeling the registers with s(v) > 0 as "+" and the registers with  $s(v) \le 0$

**Procedure FindCRD**( $G_T(V, E_T), S$ )

**Input:** Constraint graph  $G_T(V, E_T)$ , and current clock schedule  $S = \{s(v) : \forall v \in V\}$ **Output:** Set *R* of cost reducible by decrease vertices or empty set if no such vertex exist

- 1:  $R \leftarrow \emptyset$

- 2:  $R' \leftarrow \emptyset$

- 3: Construct critical graph  $G_C(V, E_C)$  that consists of only critical edges

- 4: Construct  $G'_{H}(V, E'_{H})$ , the transitive graph of  $G_{C}(V, E_{C})$  using Warshall's Algorithm

- 5: for all  $v \in V$  do

- 6: **if** s(v) > 0 **then**

- 7: Label:  $v \leftarrow "+"$

- 8: **else if**  $s(v) \le 0$  then

- 9: Label:  $v \leftarrow$  "-"

- 10: end if

- 11: **end for**

- 12: Construct  $G_H(V, E_H)$  from  $G'_H(V, E'_H)$  by deleting all edges in  $E_H$  except edges going from "+" to "-" vertices

- 13: Obtain a maximum matching of  $G_H(V, E_H)$  by using Hopcroft-Karp Algorithm, and reverse the matched edges to obtain  $G_H^*(V, E_H)$

- 14: if all "+" vertices matched then

- 15: **return**  $R = \emptyset$

- 16: end if

- 17: Select an unmatched "+" vertex,  $v_S$

- 18:  $R' = \{v \in V : v \text{ is reachable from } v_s \text{ in } G_H^*\}$

- 19:  $R = R' \bigcup \{ \text{vertex } v \text{ reachable from } R' \text{ in } G_C \}$

- 20: return R

Figure 2.14: Algorithm that finds cost reducible by decrease sets

as "-"; the definition can be re-stated as follows: Given a critical graph  $G_C(V, E_C)$ , a set of registers *R*, is a CRD set if there is no critical out-edge from *R* and the number of "+" registers in *R* is larger than the number of "-" registers in *R* [25].

The algorithm to find a CRD set is given in Figure 2.14. The algorithm takes a constraint graph  $G_T(V, E_T)$  for a clock period T and the current clock schedule S of the circuit as input. The output of the algorithm is the set R of cost reducible by decrease vertices. If the algorithm returns an empty set, that means there is no set of CRD registers. The register set R, returned by the algorithm has more "+" registers than "–" registers and there are no edges (u, v) in  $G_C$  with  $u \in R$  and  $v \notin R$ . The algorithm starts by constructing the critical graph  $G_C(V, E_C)$  consisting of only critical edges. Then, the transitive graph  $G'_H(V, E'_H)$  is constructed using Warshall's Algorithm for transitive closure [59]. The vertices with timing greater than zero (s(v) > 0) are labeled as "+" and the vertices with timing less than or equal to zero  $(s(v) \le 0)$

#### Warshall's Algorithm for transitive closure

**Input:** Directed graph G(V, E)

**Output:** Transitive closure matrix T, such that T[u, v] = 1 if there is a path from u to v; T[u, v] = 0 if there is no path from u to v

1: for all  $u \in V$  do 2: for all  $v \in V$  do 3: if u = v or  $(u, v) \in E$  then  $T[u, v] \leftarrow 1$ 4: 5: else  $T[u, v] \leftarrow 0$ 6: 7: end if end for 8: 9: end for 10: for all  $w \in V$  do for all  $u \in V$  do 11: for all  $v \in V$  do 12:  $T[u, v] \leftarrow T[u, v] \lor (T[u, w] \land T[w, v])$ 13: 14: end for end for 15: 16: end for 17: **return** *T*

Figure 2.15: Algorithm that computes the transitive closure of a graph.

are labeled as "–". After that, the graph  $G_H(V, E_H)$  is constructed from  $G'_H(V, E'_H)$ , consisting of only "+" to "–" edges. A maximum matching of  $G_H(V, E_H)$  is obtained using Hopcroft-Karp Algorithm [62], [63], [64] and the matched edges are reversed to obtain  $G^*_H(V, E_H)$ . At this point, if all the "+" are matched, the algorithm returns an empty set, because no CRD set of vertices exist. Else, an unmatched "+" vertex,  $v_S$ , is selected and the set R' is constructed with all the vertices reachable from  $v_S$  in  $G^*_H(V, E_H)$ . Finally, the set R is constructed by adding to R' a vertex reachable from R' in  $G_C(V, E_C)$ .

The following theoretical discussion stated in [27] provides a theoretical basis for the Find-CRD algorithm and shows the correctness of the FindCRD algorithm.

**Theorem 2.4.2** *There is no set of CRD vertices in the graph, if all "+" vertices are matched in step 14 of FindCRD algorithm [27].*