# A CURRENT SOURCE CONVERTER BASED STATCOM FOR REACTIVE POWER COMPENSATION AT LOW VOLTAGE

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

NAZAN BİÇER

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

MAY 2010

# Approval of the thesis:

## A CURRENT SOURCE CONVERTER BASED STATCOM FOR REACTIVE POWER COMPENSATION AT LOW VOLTAGE

submitted by NAZAN BİÇER in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>            |  |

|--------------------------------------------------------------------------------------------------|--|

| Prof. Dr. İsmet Erkmen<br>Head of Department, <b>Electrical and Electronics Engineering</b>      |  |

| Prof. Dr. Muammer Ermiş<br>Supervisor, <b>Electrical and Electronics Engineering Dept., METU</b> |  |

| Dr. H.Faruk Bilgin<br>Co-Supervisor, <b>TUBITAK</b>                                              |  |

| Examining Committee Members:                                                                     |  |

| Assist. Prof. Dr. Ahmet M. Hava<br>Electrical and Electronics Engineering Dept., METU            |  |

| Prof. Dr. Muammer Ermiş<br>Electrical and Electronics Engineering Dept., METU                    |  |

| Dr. Erbil NALÇACI<br>Electrical and Electronics Engineer                                         |  |

| Prof. Dr. H. Bülent Ertan<br>Electrical and Electronics Engineering Dept., METU                  |  |

| Prof. Dr. Işık Çadırcı<br>Electrical and Electronics Engineering Dept., Hacettepe Üniversitesi   |  |

|                                                                                                  |  |

Date:

-----

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Nazan BİÇER

Signature :

# ABSTRACT

## A CURRENT SOURCE CONVERTER BASED STATCOM FOR REACTIVE POWER COMPENSATION AT LOW VOLTAGE

Biçer, Nazan M.Sc., Department of Electrical and Electronics Engineering Supervisor : Prof. Dr. Muammer Ermiş Co-Supervisor : Dr. H.Faruk Bilgin

May 2010, 105 pages

This research work is devoted to the analysis, design and development of the Current-Source Converter (CSC) based distribution-type Static Synchronous Compensator (D-STATCOM) for low-voltage applications in reactive-power control in order to achieve i) faster transient response in reactive-power control, ii) lower current harmonic distortion, iii) lower power losses and iv) minimum storage elements in comparison with conventional solutions. The developed CSC-D-STATCOM includes a low-pass input filter and a three phase forced-commutated CSC which is composed of six insulated gate bipolar transistors (IGBT) with built-in series diodes. The analysis and the control of the CSC-D-STATCOM are carried out in dq-synchronous reference frame in order to obtain the reference current waveform which is to be generated by switching the IGBTs at 3kHz with the use of space vector modulation.

**Keywords:** Reactive Power Compensation, Current Source Converter, STATCOM, pulse-width modulation

# DÜŞÜK GERİLİMDE REAKTİF GÜÇ KOMPANZASYONU İÇİN AKIM KAYNAKLI ÇEVİRGECE DAYALI STATKOM

Biçer, Nazan Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Prof. Dr. Muammer Ermiş Ortak Tez Yöneticisi : Dr. H.Faruk Bilgin

Mayıs 2010, 105 sayfa

Bu çalışma, düşük gerilim seviyesinde yapılan reaktif güç kontrolü uygulamalarında geleneksel çözümlere oranla i) daha hızlı geçici tepki elde edilmesi ii) akım harmonikleri bozulumunun azaltılması iii) güç kayıplarının düşürülmesi ve iv) depolama elemanlarının küçültülmesinin başarılabilmesi için Akım Kaynaklı Çevirgece (AKÇ) dayalı dağıtım tipi Statik Senkron Kompanzatörünün (D-STATKOM) analizi, tasarımı ve geliştirilmesine hasredilmektedir.

Geliştirilen AKÇ-D-STATKOM, düşük geçirgen giriş filtresi ve altı adet seri diyotlu IGBT'den müteşekkil üç fazlı cebri anahtarlamalı AKÇ' den oluşmaktadır. Uzay vektörü darbe genliği kiplenimi metodu kullanılarak IGBT' lerin 3kHz frekansında anahtarlanmasıyla üretilecek olan referans akım dalga şeklinin elde edilebilmesi için AKÇ-D-STATCOM' un analizi ve kontrolü dq-senkron referans düzleminde gerçekleştirilmiştir.

Anahtar Kelimeler: Reaktif Güç Kompanzasyonu, Akım Kaynaklı Çevirgeç,

STATKOM, Uzay vektörü darbe genliği kiplenimi.

To My Family

# ACKNOWLEDGEMENTS

I would like to express my deepest gratitude and sincerest respects to my supervisor Prof. Dr. Muammer Ermiş and to my co-supervisor, Dr. H.Faruk Bilgin for their guidance, advice, criticism, encouragements and insight throughout this research.

I would like to acknowledge my colleagues Tevhid Atalık and İlker Yılmaz for their crucial contributions to the DSP programming.

I would also like to acknowledge that, this study is fully supported by the Public Research Grant Committee (KAMAG) of TÜBİTAK within the scope of the National Power Quality Project (105G129).

The assistance of the valuable staff in Power Electronics Group of TÜBİTAK-UZAY is gratefully acknowledged.

# TABLE OF CONTENTS

| ABSTRACTiv                                                         |

|--------------------------------------------------------------------|

| ÖZv                                                                |

| ACKNOWLEDGMENTSvii                                                 |

| TABLE OF CONTENTSviii                                              |

| LIST OF TABLESx                                                    |

| LIST OF FIGURESxi                                                  |

| CHAPTERS                                                           |

| 1. INTRODUCTION                                                    |

| 1.1 Reactive Power Compensation1                                   |

| 1.2 Compensation Systems                                           |

| 1.3 STATCOM (Static Synchronous Compensator)                       |

| 1.4 Literature Survey on Current Source Converter                  |

| 1.5 Scope of the Thesis                                            |

| 2. SYSTEM DESCRIPTION                                              |

| 2.1 Introduction                                                   |

| 2.2 Basic Circuit Configuration and Operating Principles           |

| 2.2.1 Modeling of CSC STATCOM in dq Synchronous Reference Frame 21 |

| 2.2.1.1 Active Damping Method                                      |

| 2.3 Modulation Techniques                                          |

| 2.4 Commutation Types                                              |

| 2.4.1 Forced Commutation                                           |

| 2.4.2 Load Commutation                                             |

| 2.5   | Summary                                                   |     |

|-------|-----------------------------------------------------------|-----|

| 3. DE | ESIGN OF CSC STATCOM                                      | 43  |

| 3.1   | Introduction                                              | 43  |

| 3.2   | Design Specifications of CSC STATCOM                      | 44  |

| 3.3   | Selection of Modulation Technique                         | 44  |

| 3.4   | Design of DC Link Reactor                                 | 49  |

| 3.5   | Input Filter Design                                       |     |

| 3.6   | Selection of Power Semiconductors                         | 60  |

| 3.7   | Design of Power Stage                                     | 64  |

| 3.8   | Design of Control System                                  | 70  |

| 3.9   | Summary                                                   | 71  |

| 4. EX | XPERIMENTAL RESULTS                                       | 73  |

| 4.1   | Introduction                                              | 73  |

| 4.2   | Experimental Results                                      | 77  |

| 4.2   | 2.1 Current and Voltage Waveforms of Power Semiconductors | 77  |

| 4.2   | 2.2 AC Side Voltage and Current Waveforms                 | 81  |

| 4.2   | 2.3 Power Losses                                          | 87  |

| 4.2   | 2.4 DC Side Voltage and Current Waveforms                 | 88  |

| 4.2   | 2.5 Reactive Power Compensation Performance               | 90  |

| 5. CC | DNCLUSION                                                 | 95  |

| REFER | ENCES                                                     | 97  |

| APPEN | IDICES                                                    |     |

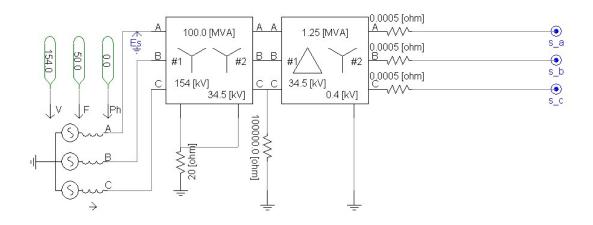

| A     | PSCAD/EMTDC MODEL FOR VSC BASED STATCOM                   | 100 |

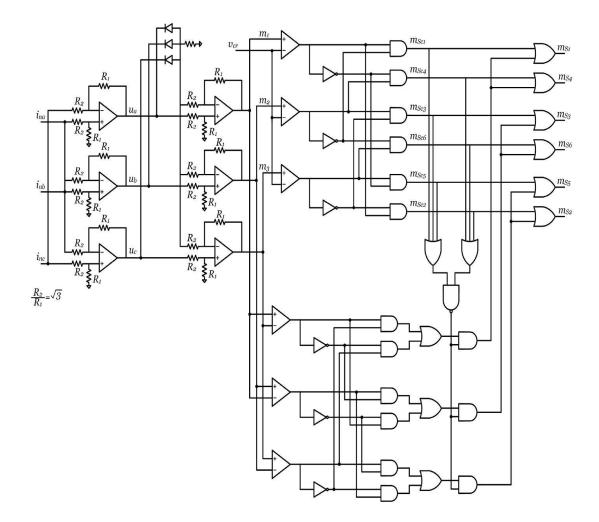

| В     | PWM PATTERN GENERATORS                                    | 103 |

| С     | INTERNAL STRUCTURE OF APTGF300U120DG                      |     |

# LIST OF TABLES

# TABLES

| Table 3.1 Technical Specifications of CSC STATCOM                         |          |

|---------------------------------------------------------------------------|----------|

| Table 3.2 Modulation Technique vs. Switching Frequency                    |          |

| Table 3.3 IEEE 519 harmonic current limits                                |          |

| Table 3.4 Reactive Power Generation of STATCOM                            |          |

| Table 3.5 Reactive Power Generation Limits of STATCOM                     |          |

| Table 3.6 Absolute maximum Ratings of APTGF300U120DG                      |          |

| Table 3.7 Commutation Path Parasitic Inductances                          |          |

| Table 4.1 List of Measurement Devices                                     | 73       |

| Table 4.2 CSC STATCOM Component List                                      | 74       |

| Table 4.3 List of Control System Cards                                    |          |

| Table 4.4 Lower order Harmonics of Converter Current $I_R$ and Filtered C | onverter |

| Current for 17kVAr Capacitive Reactive Power Generation of STATCOM and    | nd Limit |

| Values Recommended by IEEE Std. 519-1992                                  |          |

| Table 4.5 Lower order Harmonics of Converter Current $I_R$ and Filtered C | onverter |

| Current for 17kVAr Inductive Reactive Power Generation of STATCOM ar      | nd Limit |

| Values Recommended by IEEE Std. 519-1992                                  |          |

# LIST OF FIGURES

# FIGURES

| Figure 1.1 Instantaneous Power (Inductive Load)1                               |

|--------------------------------------------------------------------------------|

| Figure 1.2 Phasor Diagrams for Different VAR Compensation Approach             |

| Figure 1.3 Reactive Power Generation by Mechanically Switched Capacitors       |

| Figure 1.4 Synchronous Condenser                                               |

| Figure 1.5 Thristor Switched Capacitor                                         |

| Figure 1.6 TCR with TSC7                                                       |

| Figure 1.7 Voltage Source Converter (VSC) Based STATCOM9                       |

| Figure 1.8 Current Source Converter (VSC) Based STATCOM10                      |

| Figure 2.1 CSC STATCOM15                                                       |

| Figure 2.2 Reactive Current Components of Load and CSC STATCOM15               |

| Figure 2.3 Basic Circuit Configuration                                         |

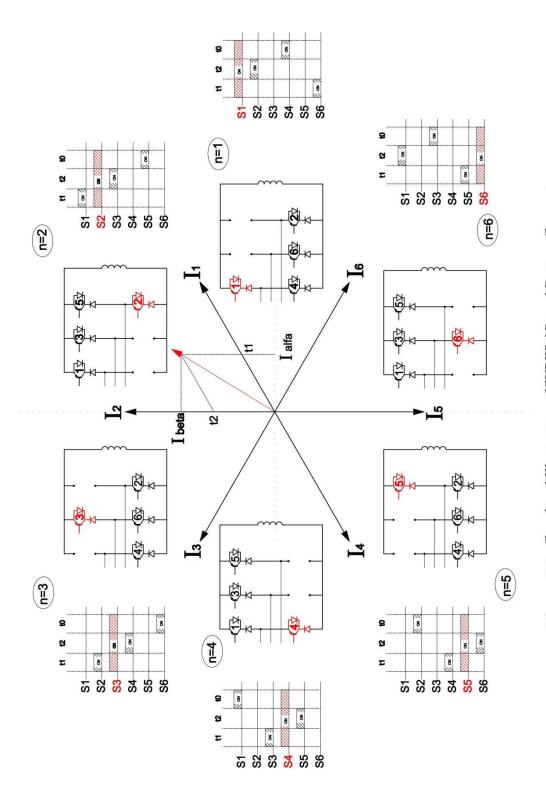

| Figure 2.4 Switch Positions                                                    |

| Figure 2.5 Phase Currents                                                      |

| Figure 2.6 Vector Representation of Capacitive and Inductive Currents          |

| Figure 2.7 Circuit diagram of CSC based STATCOM to be used for modeling 21     |

| Figure 2.8 Phasor diagrams used in deriving transformation matrices            |

| Figure 2.9 Equivalent circuit of CSC based STATCOM in dq-synchronous frame     |

| for transient state                                                            |

| Figure 2.10 Equivalent circuit of CSC based STATCOM in dq-synchronous frame    |

| for steady state                                                               |

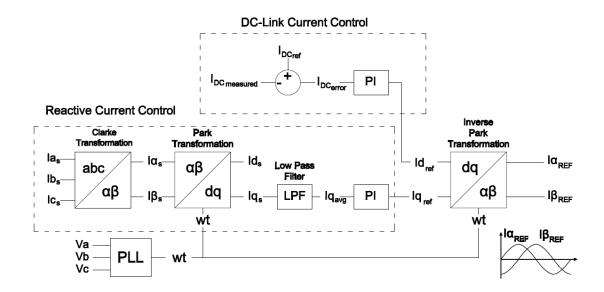

| Figure 2.11 Active Current Control                                             |

| Figure 2.12 Reactive Current Control                                           |

| Figure 2.13 Reference Current Generation                                       |

| Figure 2.14 Frequency Response of LC filter with & without Damping Resistor 32 |

| Figure 2.15 Connection of Damping Resistor                                     |

| Figure 2.16 Active Damping Method                                                  |

|------------------------------------------------------------------------------------|

| Figure 2.17 Active Damping Reference Current Calculation                           |

| Figure 2.18 Commutation path                                                       |

| Figure 2.19 Commutation Paths                                                      |

| Figure 2.20 Forced Commutation                                                     |

| Figure 2.21 Load Commutation                                                       |

| Figure 3.1 Harmonic Spectrum of CSC Current Capacitive Mode                        |

| Figure 3.2 Harmonic Spectrum of Filtered CSC Current Capacitive Mode               |

| Figure 3.3 Harmonic Spectrum of CSC Current Inductive Mode                         |

| Figure 3.4 Harmonic Spectrum of filtered CSC Current Inductive Mode 49             |

| Figure 3.5 DC-Link Voltage and Current                                             |

| Figure 3.6 DC Current Peak to Peak Ripple                                          |

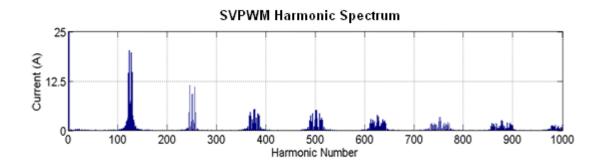

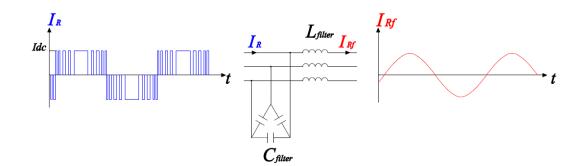

| Figure 3.7 (SVPWM) Generated AC Current ( <i>I<sub>R</sub></i> ) Harmonic Spectrum |

| Figure 3.8 Low Pass Filter                                                         |

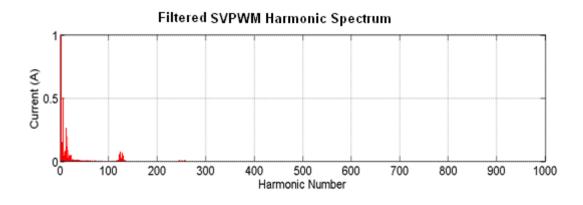

| Figure 3.9 (SVPWM) Filtered AC Current ( <i>I<sub>Rf</sub></i> ) Harmonic Spectrum |

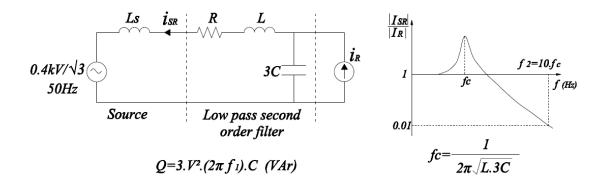

| Figure 3.10 Single line diagram of the input filter                                |

| Figure 3.11 Converter Voltage Variation a) Capacitive Mode b) Inductive Mode 55    |

| Figure 3.12 Harmonic Spectrum of Generated CSC Currents and Filtered CSC           |

| Currents                                                                           |

| Figure 3.13 Frequency Response of Designed Input Filter                            |

| Figure 3.14 IGBT with series diode (a) Reverse blocking (b) Forward blocking 60    |

| Figure 3.15 Operating Frequency vs. Collector Current of APTGF300U120DG 62         |

| Figure 3.16 CSC STATCOM Circuit Electrical Connections                             |

| Figure 3.17 Commutation Path between S1 and S365                                   |

| Figure 3.18 Power Stage of CSC STATCOM                                             |

| Figure 3.19 Switching Test Setup                                                   |

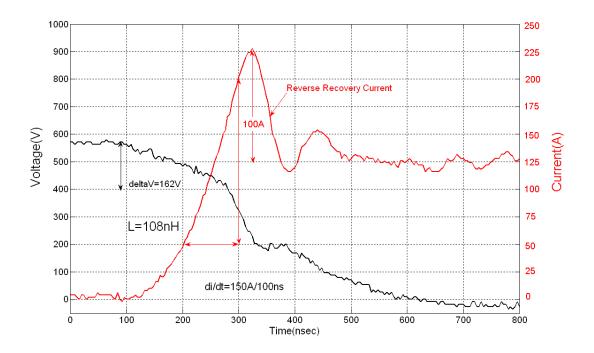

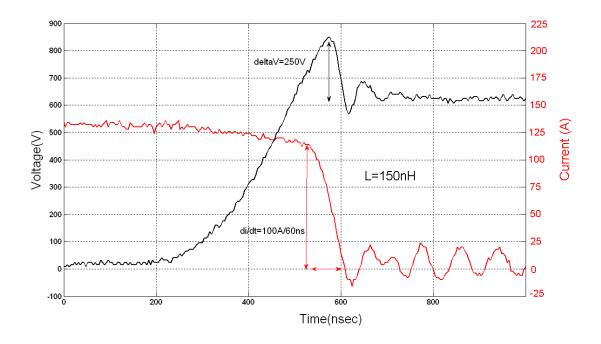

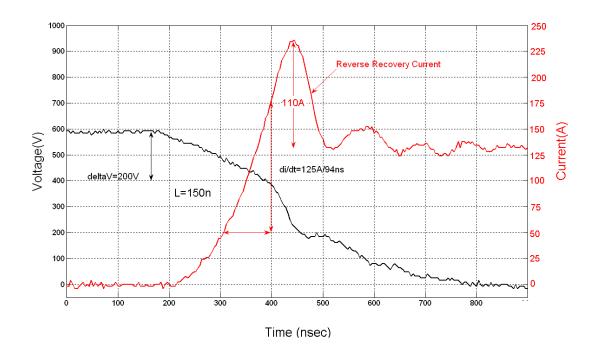

| Figure 3.20 S1 Turn-off Voltage & Current (V <sub>RS</sub> Top Commutation Path)68 |

| Figure 3.21 S1 Turn-on Voltage & Current (V <sub>RS</sub> Top Commutation Path)68  |

| Figure 3.22 S1 Turn-off Voltage & Current (V <sub>RT</sub> Top Commutation Path)69 |

| Figure 3.23 S1 Turn-on Voltage & Current (V <sub>RT</sub> Top Commutation Path)69  |

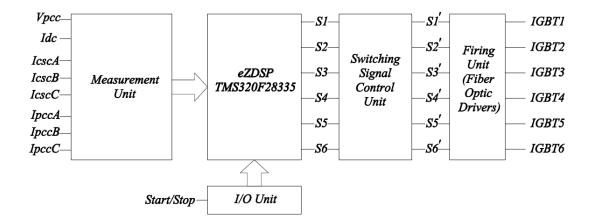

| Figure 3.24 Control System Sub Units                                                     |

|------------------------------------------------------------------------------------------|

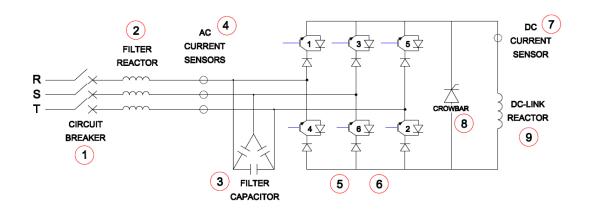

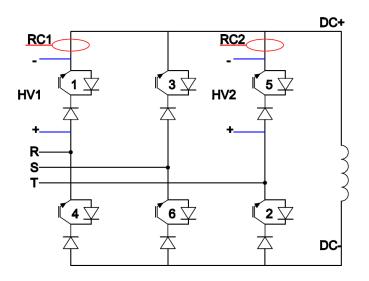

| Figure 4.1 CSC STATCOM Circuit74                                                         |

| Figure 4.2 CSC STATCOM Front and Back view75                                             |

| Figure 4.3 Electronic Control System Front and Back View76                               |

| Figure 4.4 Power Semiconductor Current & Voltage Measurement Set-up77                    |

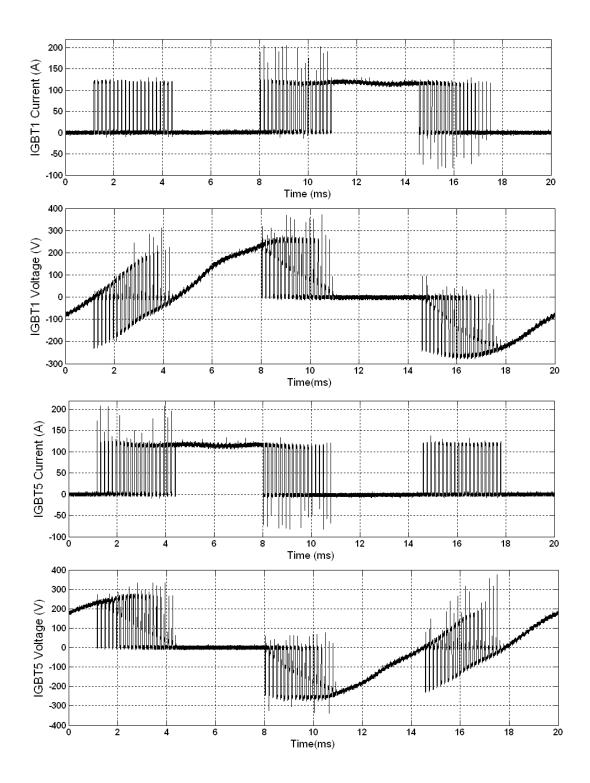

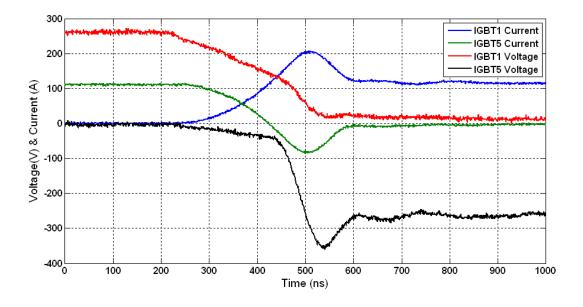

| Figure 4.5 Voltage and Current Waveforms of IGBT1 and IGBT5 for 17kVAr                   |

| Capacitive Reactive Power Generation of STATCOM                                          |

| (sampling rate=5 MS/s)78                                                                 |

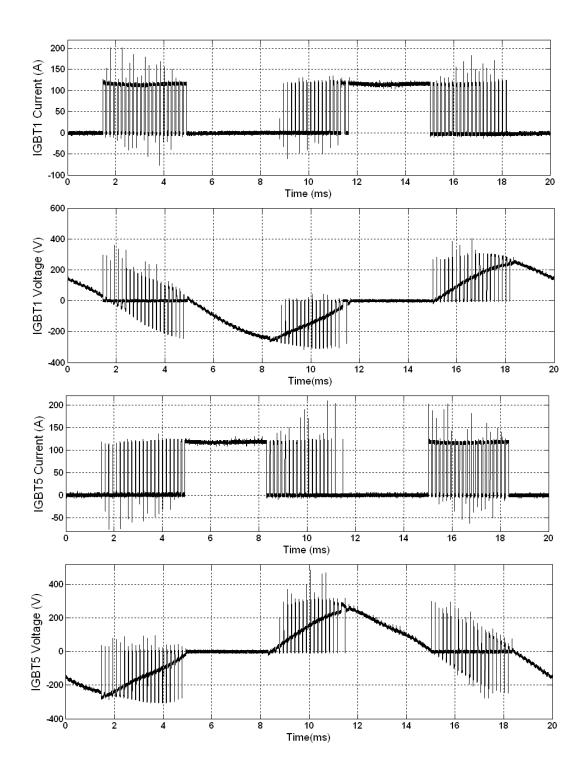

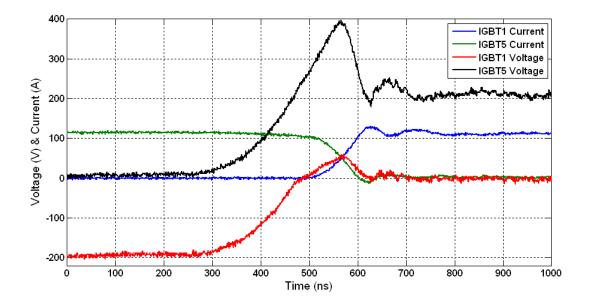

| Figure 4.6 Voltage and Current Waveforms of IGBT1 and IGBT5 for 17kVAr                   |

| Inductive Reactive Power Generation of STATCOM                                           |

| (sampling rate=5 MS/s)79                                                                 |

| Figure 4.7 Voltage and Current Waveforms of IGBT1 and IGBT5 during Load                  |

| Commutation (sampling rate=25GS/s)                                                       |

| Figure 4.8 Voltage and Current Waveforms of IGBT1 and IGBT5 during Forced                |

| Commutation (sampling rate=25GS/s)                                                       |

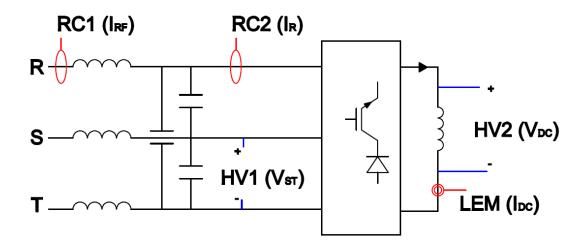

| Figure 4.9 Current & Voltage Measurement Set-up                                          |

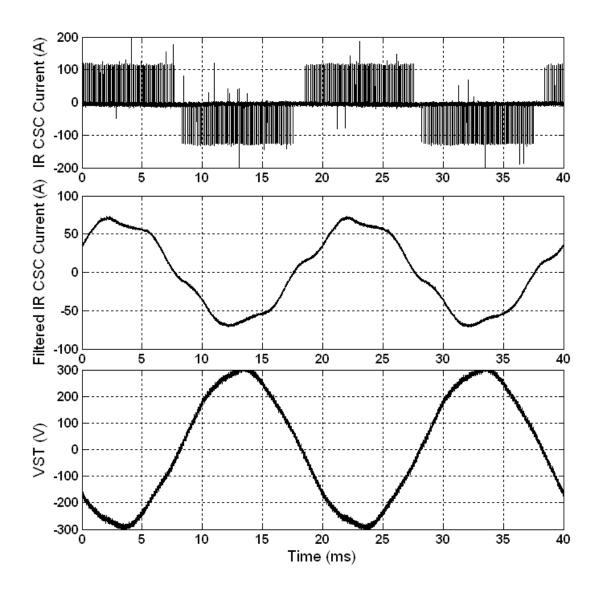

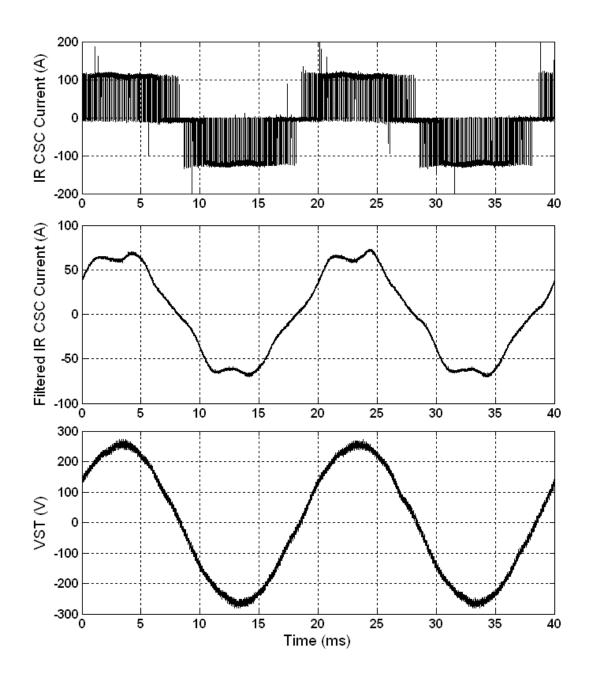

| Figure 4.10 Voltage and Current Waveforms of Converter Current $I_R$ , Filtered          |

| Converter Current and Phase-to-phase Voltage $V_{ST}$ for 17kVAr Capacitive Reactive     |

| Power Generation of STATCOM (sampling rate=2.5MS/s)                                      |

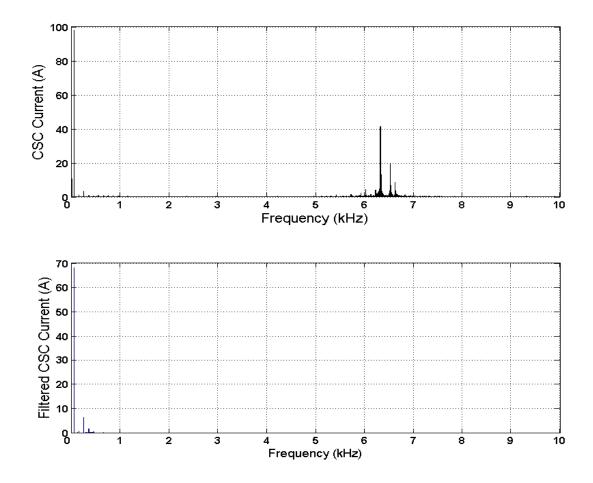

| Figure 4.11 Harmonic Spectrum of Converter Current $I_R$ and Filtered Converter          |

| Current for 17kVAr Capacitive Reactive Power Generation of STATCOM                       |

| Figure 4.12 Voltage and Current Waveforms of Converter Current $I_R$ , Filtered          |

| Converter Current and Phase-to-phase Voltage $V_{ST}$ for 17kVAr Inductive Reactive      |

| Power Generation of STATCOM (sampling rate=2.5MS/s)                                      |

| Figure 4.13 Harmonic Spectrum of Converter Current $I_{\text{R}}$ and Filtered Converter |

| Current for 17kVAr Inductive Reactive Power Generation of STATCOM85                      |

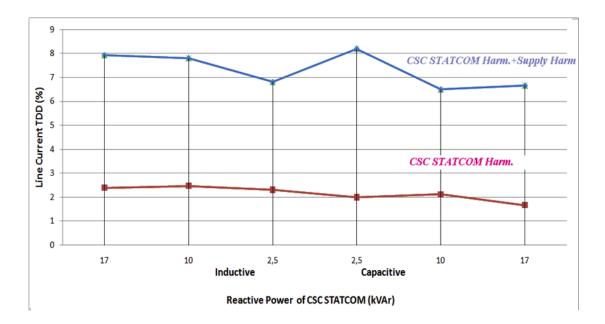

| Figure 4.14 Variations in TDD of CSC based STATCOM line current                          |

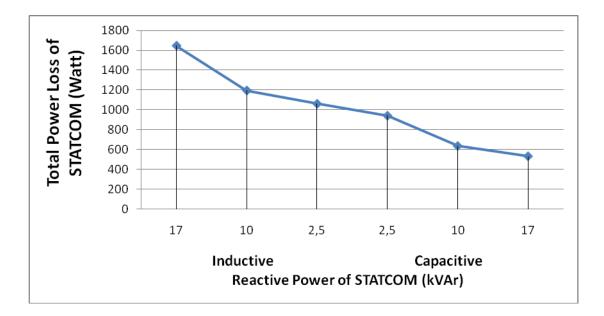

| Figure 4.15 Total STATCOM losses against reactive power                                  |

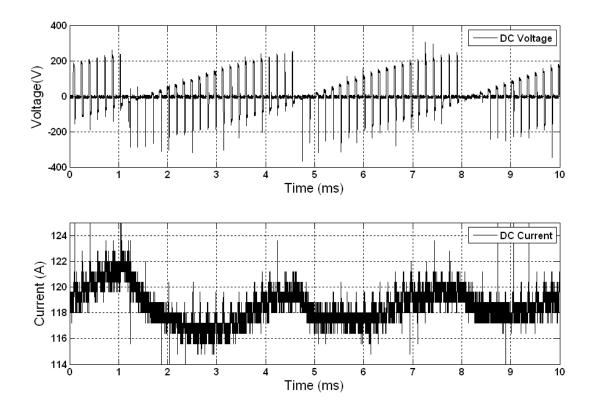

| Figure 4.16 DC link waveforms of CSC for 17 kVAr Capacitive Reactive Power               |

| Generation of STATCOM (sampling rate=2.5MS/s)                                            |

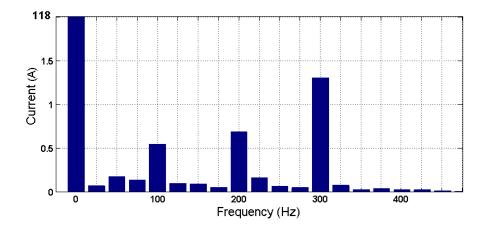

| Figure 4.17 Harmonic Spectrum of DC Link Current for 17 kVAr Capacitive                                            |

|--------------------------------------------------------------------------------------------------------------------|

| Reactive Power Generation of STATCOM                                                                               |

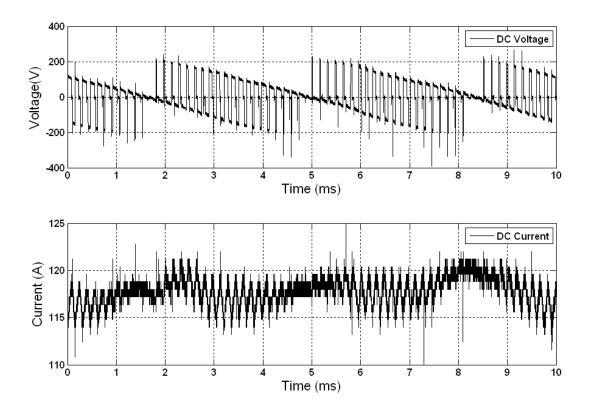

| Figure 4.18 DC link waveforms of CSC for 17 kVAr Inductive Reactive Power                                          |

| Generation of STATCOM (sampling rate=2.5MS/s)                                                                      |

| Figure 4.19 Harmonic Spectrum of DC Link Current for 17 kVAr Inductive Reactive                                    |

| Power Generation of STATCOM                                                                                        |

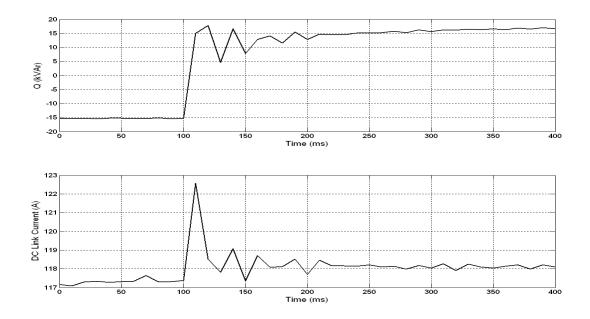

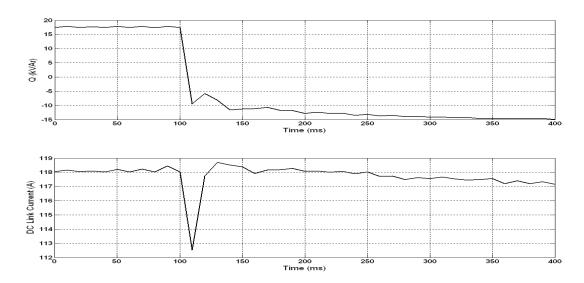

| Figure 4.20 Transient response of reactive power control loop and dc-link current to                               |

| a step input changing from maximum inductive reactive power to maximum                                             |

| capacitive reactive power (q is averaged at every 20 ms) (sampling rate= 100 KS/s                                  |

| and averaged at every 1000 sample)                                                                                 |

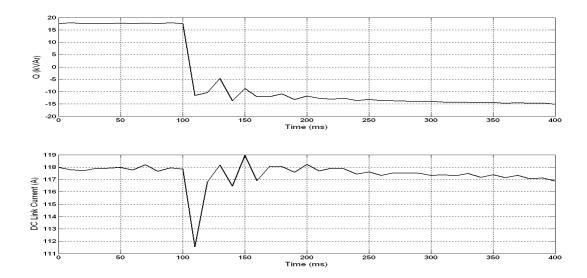

| Figure 4.21 Transient response of reactive power control loop and dc-link current to                               |

| a step input changing from maximum capacitive reactive power to maximum                                            |

| inductive reactive power (q is averaged at every 20 ms) (sampling rate= 100 KS/s                                   |

| and averaged at every 1000 sample)                                                                                 |

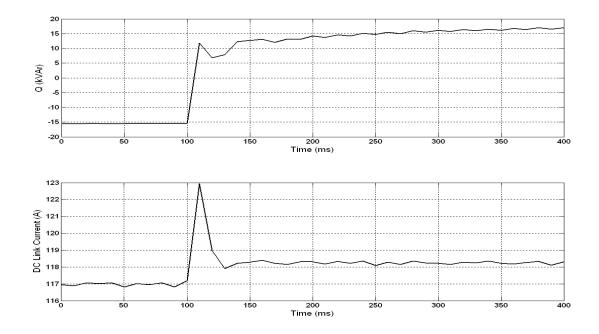

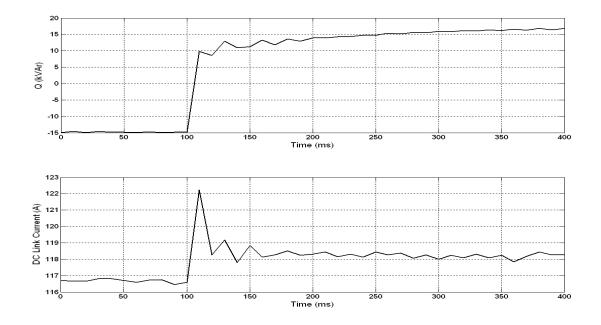

| Figure 4.22 Transient response of reactive power control loop and dc-link current to                               |

| a step input changing from maximum inductive reactive power to maximum                                             |

| capacitive reactive power (q is averaged at every 10 ms) (sampling rate= 100 KS/s                                  |

| and averaged at every 1000 sample)                                                                                 |

| Figure 4.23 Transient response of reactive power control loop and dc-link current to                               |

| a step input changing from maximum capacitive reactive power to maximum                                            |

| inductive reactive power (q is averaged at every 10 ms) (sampling rate= 100 KS/s                                   |

| and averaged at every 1000 sample)                                                                                 |

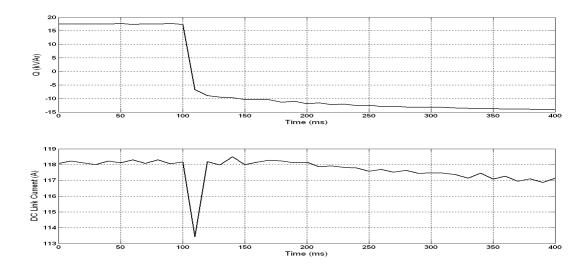

| Figure 4.24 Transient response of reactive power control loop and dc-link current to                               |

| a step input changing from maximum inductive reactive power to maximum                                             |

| capacitive reactive power (q is averaged at every 5 ms) (sampling rate= 100 KS/s and                               |

| averaged at every 1000 sample)                                                                                     |

| Figure 4.25 Transient response of reactive power control loop and dc-link current to                               |

| a step input changing from maximum capacitive reactive power to maximum                                            |

|                                                                                                                    |

| inductive reactive power (q is averaged at every 5 ms) (sampling rate= 100 KS/s and averaged at every 1000 sample) |

# **CHAPTER 1**

# **INTRODUCTION**

#### 1.1 Reactive Power Compensation

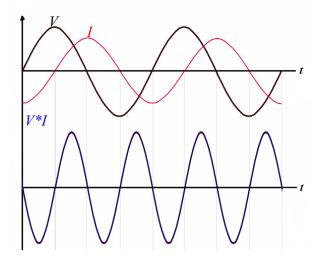

The reactive power is defined as the ac component of the instantaneous power, with a frequency equal to 100 Hz in a 50-Hz system. As illustrated in Figure 1.1 the reactive power generated by the ac power source is stored in a capacitor or a reactor during a quarter of a cycle, and in the next quarter cycle is sent back to the power source. In other words, the reactive power oscillates between the ac source and the capacitor or reactor, and also between them, at a frequency equals to two times the rated value (50 Hz), [1]. In order to carry this oscillating power by transmission systems rated value of the installed devices should be higher, this increases the cost of transmission systems and power losses, and also the power system stability is affected by reactive power.

Figure 1.1 Instantaneous Power (Inductive Load)

In order to avoid this problem, the reactive power should be compansated using voltampere-reactive (VAR) generators. VAR generators can be connected in parallel or in series.

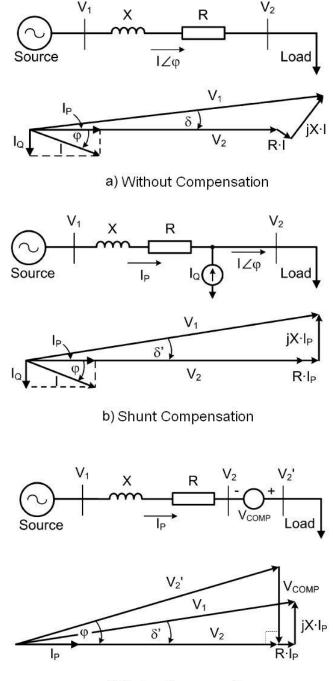

#### • Shunt Compensation:

Figure 1.2 (b) shows the principles and theoretical effects of shunt reactive power compensation in a basic ac system with an inductive load.  $V_I$  is the source voltage and  $V_2$  is the load voltage.  $I_P$  represents active component of the line current and  $I_Q$  reactive component of the load.  $I_Q$  increases the magnitude of the total line current  $I \angle \varphi$  which is supplied by the source. If reactive power is compansated near the load by injecting the reactive current  $-I_Q$ , the magnitude of the line current can be reduced to its active component. Hence, the power losses can be reduced and the voltage regulation can be improved at the load terminals. This can be done by one of three ways; 1) using capacitor for inductive load and reactor for capacitive load, 2) using a voltage source, 3) using a current source. The illustrated example shows a current source type compensator. The main advantage of using a voltage or current source VAR generators (instead of inductors or capacitors) is the reactive power generated is independent of the voltage at the point of connection.

#### • Series Compensation:

As can be seen Figure 1.2 (c) in series compensation  $V_{COMP}$  has been added between the line and the load to change the angle of  $V_2$  in order to make the angle between line current  $I_P$  and  $V_2$  zero. Like shunt compensation, series compensation may also be implemented with current- or voltage-source devices. Typical series compensation systems use capacitors to decrease the equivalent reactance of a power line at rated frequency in order to increase angular stability of the power line, improve voltage stability and optimize power sharing between parallel circuits.

c) Series Compensation

Figure 1.2 Phasor Diagrams for Different VAR Compensation Approach

#### **1.2** Compensation Systems

Compensation systems are classified depending on the way of connection to the power line (shunt or series) and depending on the technology used in their implementation. Mechanically switched capacitors and synchronous machines were the only reactive power compensators before the invention of power electronic devices. With the developments in power semiconductor technology, different static VAR generators have been developed. A brief explanation of various compensation ststems is as follows.

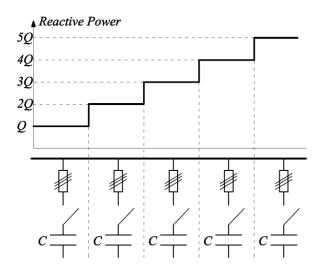

#### • Mechanically Switched Capacitors:

Shunt capacitors were first employed for reactive power compensation in the first decades of the 20th century. Depending on the total VAR requirement capacitors are switched in or switched out by using mechanical switches such as contactors or circuit breakers. Reactive power generated by mechanically switched capacitors is illustrated in Figure 1.3.

Figure 1.3 Reactive Power Generation by Mechanically Switched Capacitors

Since the reactive power is generated in discrete steps, load may be instantaneously over-compensated or under-compensated. Also the response of the system is very slow due to delay in mechanical switches and discharge time of the capacitors. Moreover, high in-rush current during switch in and frequent maintenance of the mechanical switchgear are other concerns of this system. This type of compensation is commonly used in low voltage applications because of its low cost and simple installation. On the other hand, a satisfactory compensation for slowly changing inductive loads can be achieved by using sufficient number of capacitors.

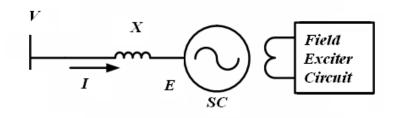

#### • Synchronous Condensers:

Synchronous machines can be used as reactive VAR generators by adjusting its field current in order to generate or absorb reactive power. The continuous control of reactive power is achieved by using automatic exciter circuit. Synchronous condensers connected to transmission systems are used commonly for 50 years in order to improve stability of the power system and keep voltages within limits under varying load conditions and contingency situations. Disadvantages of these systems are 1) slow response for rapidly changing loads, 2) significant amount of starting and protective equipment, 3) contribution to the short circuit current, 4) high maintenance and 5) much higher losses as compared with the other compensation systems.

Figure 1.4 Synchronous Condenser

#### • Thyristor Switched Capacitor (TSC):

As shown in Figure 1.5 capacitors are connected to system with back-to-back connected thyristor pairs. The use of thyristor as a switching element presents a transient free switching-in of capacitors without inrush current. It also eliminates the requirement for the discharge of capacitors. This is supplied by switching-on and switching-off thyristors at the instances when dv/dt rating on capacitor is zero. L may be connected not only limiting the fault current but also designing a tuned harmonic filter.

Figure 1.5 Thristor Switched Capacitor

The disadvantages of TSC are stepwise control of reactive power demand of the load, like mechanically switched capacitor and selection of the peak voltage rating of the thyristor with two times the peak value of supply voltage.

#### **Thyristor Controlled Reactor (TCR):**

Stepless, smooth control of reactive power can be achieved by means of firing angle ( $\alpha$ ). However, TCR injects current harmonics as the firing angle is changed and these harmonic currents should be filtered by using appropriated harmonic filters with TCR. Therefore, TCR systems are generally implemented with harmonic filters which provide capacitive reactive power. The net reactive power of complete system is then equal to the difference between the capacitive reactive power of the harmonic filter and the inductive reactive power of TCR. These harmonic filters can be arranged as thyristor switched filters in order to adjust the reactive power control range of the system adaptively without excessive losses in TCR (see Figure 1.6). The adjustment of  $\alpha$  can be made instantaneously; which provides compensation of reactive power demand of rapidly changing loads. The disadvantages of TCR are mainly the generation of low order harmonic currents, hence large harmonic filters, large system footprint and higher reactor losses.

Figure 1.6 TCR with TSC

#### **1.3 STATCOM (Static Synchronous Compensator)**

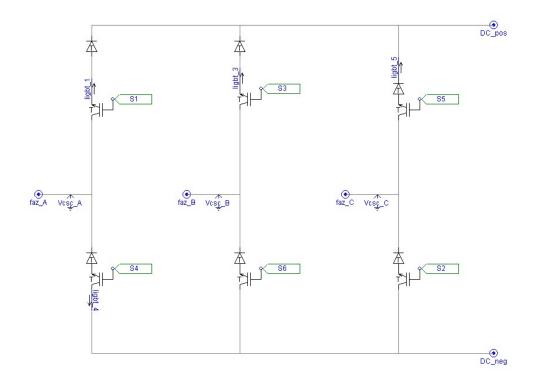

With developments in semiconductor technology, the switching power converters where self commutated power semiconductors are switched at high voltage, high current and high frequency have become widely applicable in high power applications. This presents the use of switching converters which generate controlled inductive or capacitive currents independent of the ac system voltage with minimum energy storage elements such as capacitors or reactors. The shunt connected of these switching power converters are termed as STATCOM.

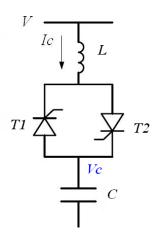

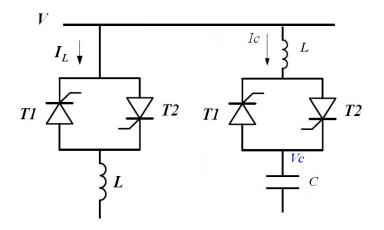

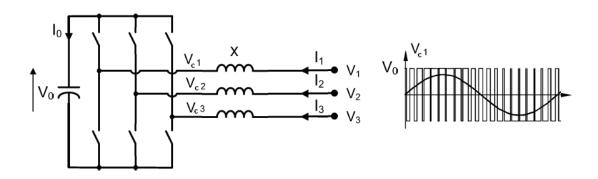

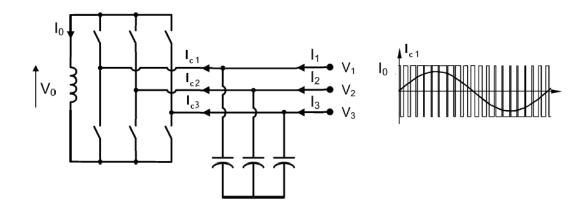

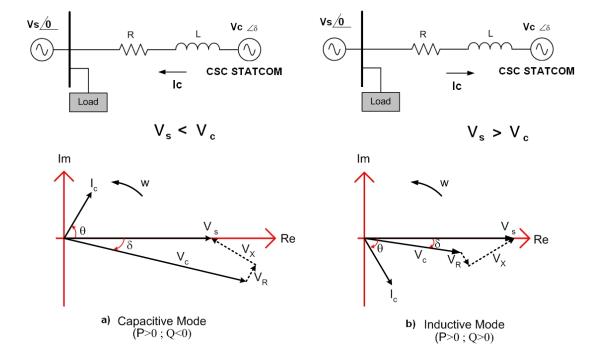

The switching power converters may be either voltage source type (VSC) (see Figure 1.7) or a current source type (CSC) (see Figure 1.8). In VSC based STATCOM, the converter produces a set of controllable three-phase output voltage ( $V_1$ ,  $V_2$  and  $V_3$ ) at supply frequency from a dc-voltage provided by dc-link capacitor. Each output voltage is in phase with and coupled to the corresponding phase of ac system via coupling reactor (including reactance of the coupling transformer) so that required reactive current can be injected into the power system. On the other hand, CSC produces a set of controllable three-phase output current ( $I_1$ ,  $I_2$  and  $I_3$ ) at supply frequency from a dc-current provided by the dc-link reactor. The switching frequency harmonics of these output currents are filtered by the input filter and then injected directly into the power system.

Commercially available STATCOM systems are mainly based on voltage source converter and there has been excessive research on VSC based STATCOM because of the following reasons.

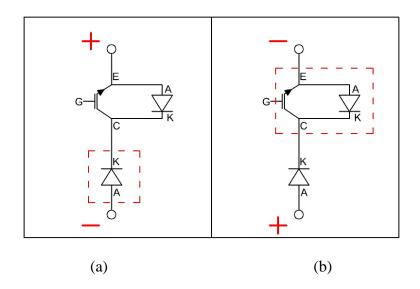

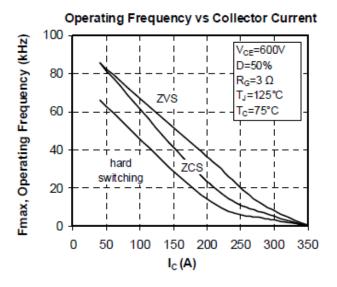

i) The semiconductors used in current source converters should have bidirectional voltage blocking capability, but available high power semiconductors with gate turn-off capability (GTOs, IGBTs) cannot block reverse voltage. Reverse voltage blocking diodes should be used in series with semiconductor switches which is increasing conduction losses.

ii) Current source converter dc-link reactor losses are higher compared to voltage source converter dc-link capacitor losses.

iii) VSC requires series reactors connected to ac side of the converter in order to filter voltage harmonics and this may be naturally provided by the leakage inductance of the coupling transformer. CSC requires capacitors on ac terminals in order to filter current harmonics.

Inspite of these facts, CSC based STATCOM is still promising attractive features such as, a) it does not need precharching of dc-link and it does not require inrush current limiting equipment, b) better ac current waveforms can be obtained by current source converter at relatively lower switching frequency, c) it does not inject harmonics in 'idle' state.

Figure 1.7 Voltage Source Converter (VSC) Based STATCOM

Figure 1.8 Current Source Converter (VSC) Based STATCOM

#### 1.4 Literature Survey on Current Source Converter

As compared with VSC STATCOM, there are limited researches on CSC STATCOM [2-6]. These are summarized as follows.

The research work in [2] presents the method of reactive current control by using phase angle control. The proposed method is applied to a laboratory set-up of 117V, 1.1kVA CSC STATCOM, where off-line PWM method with a switching frequency of 660Hz is used. The resultant system does not minimize the energy storage elements (e.g., inductance of the dc-link reactor and the filter reactor is 27mH and 6.6mH, respectively). Moreover, the transient response of the system is not considered.

The operating principles of CSC STATCOM with an alternative reactive power control is presented by [3], where the modulation index is controlled together with the phase angle. Dc-link current is regulated at a constant value by phase angle control and the reactive power is controlled by varying modulation index. CSC is modulated by space vector PWM with a switching frequency of 1620Hz. However,

the results are also lack of practical considerations, such as transient response, harmonic distortion levels, minimization of energy storage elements.

The analysis and modeling of CSC STATCOM in dq-synchronous reference frame is presented in [4]. The simultaneous control of phase angle and modulation index is compared with only phase angle control. A multivariable full state feedback control is employed for reactive power control in order to achieve fast and non-oscillatory response. It is shown that the proposed control results in satisfactory transient response.

The first industrial application of CSC STATCOM at 1kV,  $\pm 500kVA$  level is presented in [7]. In this application, selective harmonic elimination method (SHEM) is used as modulation method in order to minimize lower order harmonics and switching losses. Reactive power is controlled by varying the dc-link current via phase-shift-angle. The design methods are set out for an application of CSC STATCOM to a medium voltage application. The proposed methods are verified by the results obtained from the field tests. However, the transient response is inherently slow due to the use of off-line modulation technique and the system losses can not be decreased further by the elimination of damping resistors in the input filter.

#### **1.5** Scope of the Thesis

Within the scope of this thesis, the anaylsis, design and implementation of a CSC based STATCOM for low-voltage applications are studied in order to obtain i) fast transient response in reactive power control, ii) low current harmonic distortion, iii) low power losses, iv) minimum storage elements. For this purpose, the simplest three phase current source converter topology is used with an optimized input filter and dc-link reactor. The analysis and the control of CSC STATCOM are carried out in dq-synchronous reference frame and the CSC is modulated by the space vector PWM in

order to generate the reference current waveform. Active damping method is also employed in the control system in order to damp the characteristic of the input filter around its resonance frequency. The proposed control and design methods are verified on a laboratory prototype.

The organization of this thesis is given as follows.

In chapter 2, system description and operation principles of CSC STATCOM is described. Current control method and reference current generation by using dq theory is explained with current control block illustrations. Active damping method and passive damping method is compared and the theory of active damping technique is explained. Different on-line PWM methods are evaluated and finally current commutation types are described.

In chapter 3, design principles of CSC STATCOM are presented. Specifications of designed laboratory prototype is given first and secondly selection of modulation technique is explained. Design of dc-link reactor and input filter is described in detail. Selection of power semiconductors and design of power stage is explained and finally control system design is presented.

In chapter 4 theoretical and experimental results are presented.

In chapter 5, contributions of the thesis are summarized and concluding remarks, and recommended future works are proposed.

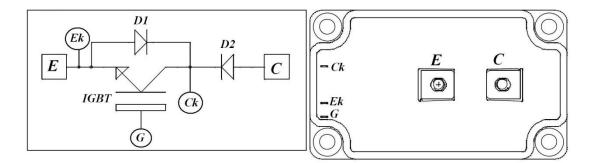

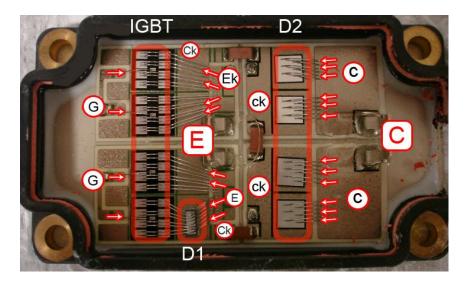

The simulation model of the CSC STATCOM is given in appendix A. In appendix B, the block diagrams for the generation of switching signal are given for dead band sinusoidal pulse-width modulation and space vector modulation, respectively. The internal structure of the insulated gate bipolar transistor which is used in this research is presented in appendix C.

# **CHAPTER 2**

# SYSTEM DESCRIPTION

#### 2.1 Introduction

The problems on electrical power quality have been seriously considered by the utility authority and the consumers in Turkey, since 2000. Therefore, the Energy Regulatory Authority of Turkey imposed strict limits on the harmonic currents and the reactive power demand for the consumers in order to improve the power quality and reliability of the Turkish Electricity System. As the limits get tighter, new power quality conditioners which present fast, accurate and complete solution for the power quality problems have been introduced. Static synchronous compensator (STATCOM) which has been known and mainly applied to medium voltage for nearly 20 years become a strong candidate for low-voltage distribution systems as the cost of system parts in STATCOM decreases.

In addition to reactive power compensation, a distribution type static synchronous compensator (D-STATCOM) may have the capability of filtering load harmonics and balancing unbalanced loads. These features are only achieved by the application of an on-line generated pulse-width modulation (PWM) to the switching power converter of STATCOM. The switching power converters are basically classified as voltage-source converter and current-source converter. In spite of the extensive research and application of voltage-source converter based STATCOM, the current-source converter based STATCOM has not been well exploited in industry, yet.

The three phase current source converter based static synchronous compensator (CSC STATCOM) is composed of a current-source type converter and can be applied as a D-STATCOM in the distribution systems by employing appropriate PWM technique and control methods.

In this chapter, system description and operating principles of CSC STATCOM will be covered. Current control of CSC STATCOM will be analyzed in detail. Active damping method and PWM modulation technique will be described theoretically. Finally commutation types will be presented.

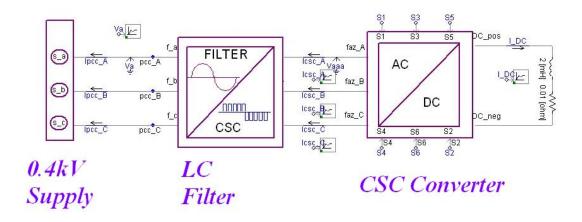

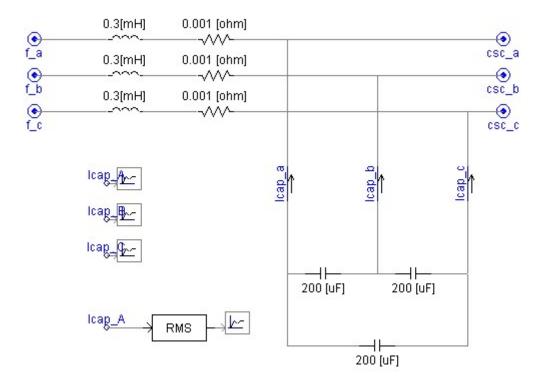

#### 2.2 Basic Circuit Configuration and Operating Principles

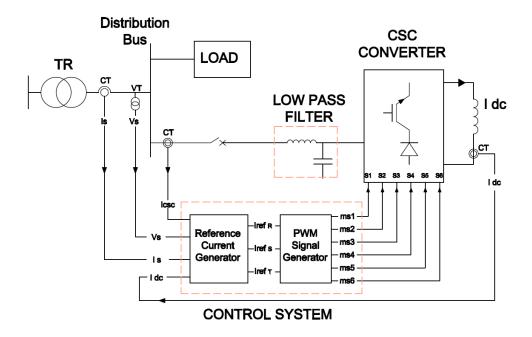

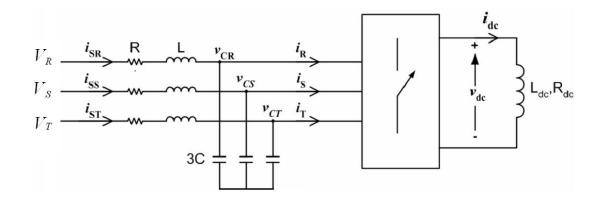

CSC STATCOM is composed of a forced-commutated current source converter (CSC), a low pass filter, a dc-link reactor and a control system. It generates three phase sinusoidal currents at fundamental frequency with controlled amplitude and phase angle. It is connected to distribution bus as shown in Figure 2.1. CSC STATCOM is able to compensate loads which have rapidly changing reactive power demand.

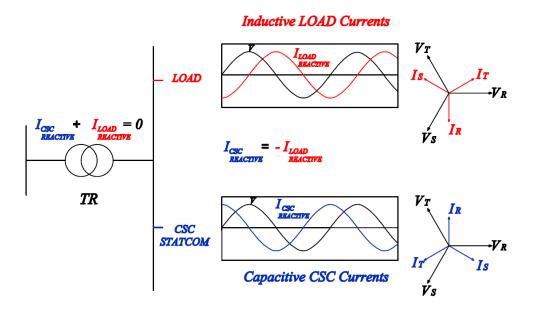

Undesired reactive components of load currents can be eliminated by generating the current waveforms which have the same amplitude but anti-phase, as shown in Figure 2.2. CSC generates three phase reference currents from dc-link current by switching semiconductors. While dc-link current is kept constant, the amplitude and phase of three phase currents can be adjusted by controlling switching signals.

Figure 2.1 CSC STATCOM

Figure 2.2 Reactive Current Components of Load and CSC STATCOM

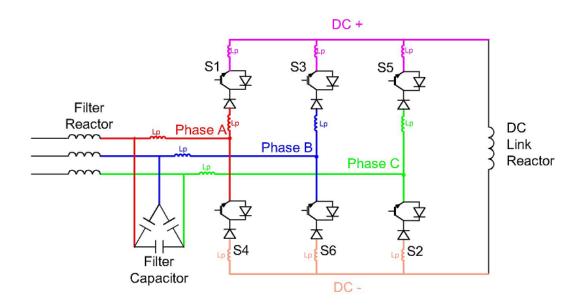

Figure 2.3 Basic Circuit Configuration

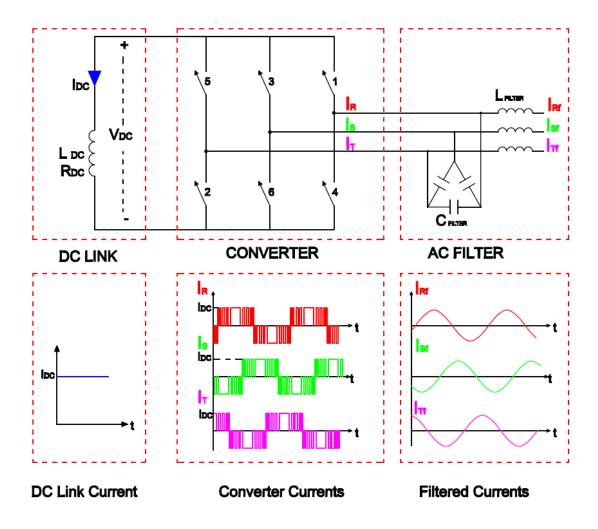

Basic circuit configuration of current source converter is shown in Figure 2.3. It is different than voltage-source converter (VSC), such as

- The voltage on each semiconductor switch may be either positive or negative and the current through each semiconductor switch flows only in one direction. This requires fully controllable semiconductor switches, each of which has a unidirectional current carrying and bipolar voltage blocking capability.

- In order to obtain a dc-current source, a reactor has been used in dc-link as the energy storage element. The power loss of the dc-link reactor is represented by its internal resistance  $R_{dc}$ .

- Due to the presence of the reactor in the dc-link, the flow of dc-link current must be continuous such that one switch from the upper half and one switch from the lower half of the converter must be conducting at any time.

- The currents generated by the converter are constructed from the dc-link current by switching the power semiconductors with an appropriate modulation technique, as shown in Figure 2.3. They have harmonic current components and should be filtered by a low pass filter to obtain nearly sinusoidal three phase currents at supply frequency.

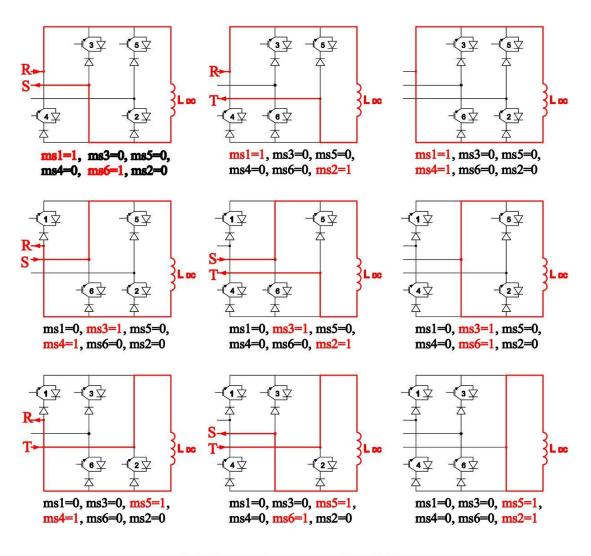

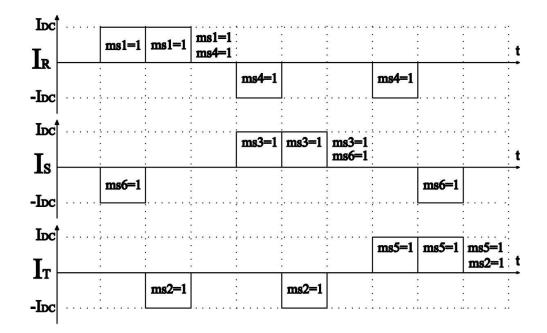

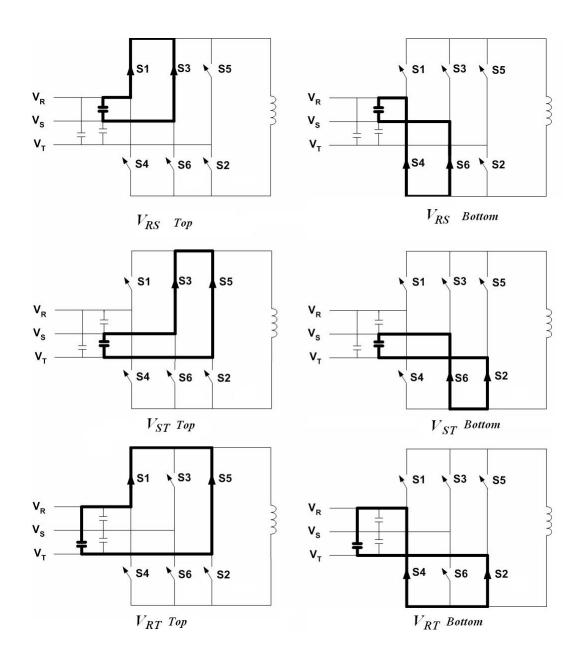

Control system calculates the reactive components of the load currents by the use of voltage signals at the point of common coupling. Then, it generates the required reference current waveforms ( $i_{Rref}$ ,  $i_{Sref}$ ,  $i_{Tref}$ ) as can be seen in Figure 2.1. PWM signal generator generates switching signals ( $m_{s1}$ ,  $m_{s2}$ ,  $m_{s3}$ ,  $m_{s4}$ ,  $m_{s5}$  and  $m_{s6}$ ) for the corresponding power semiconductors according to the reference current waveforms. The switching signal is equal to 1 if the corresponding power semiconductor is to be turned on. Otherwise, it is equal to 0. All possible conducting semiconductors and converter line current directions according to the switching signals are shown in Figure 2.4 and Figure 2.5, respectively.

Rule for current source converter switching :

ms1 + ms3 + ms5 = 1, ms4 + ms6 + ms2 = 1

Figure 2.4 Switch Positions

Figure 2.5 Phase Currents

The relation between the switching signals and the converter line currents are illustrated in Figure 2.5 and given in (2.1).

$$I_{R}(t) = (m_{s1} - m_{s4})Idc = M.I_{dc.}\sin(\omega t + \theta) + \sum_{h=2}^{\infty} I_{h}\sin(\omega_{h}t - \lambda_{h})$$

$$I_{S}(t) = (m_{s3} - m_{s6})Idc = M.I_{dc}.\sin(\omega t + \theta - 2\pi/3) + \sum_{h=2}^{\infty} I_{h}\sin(\omega_{h}t - \varsigma_{h}) \qquad (2.1)$$

$$I_{T}(t) = (m_{s5} - m_{s2})Idc = M.I_{dc}.\sin(\omega t + \theta - 4\pi/3) + \sum_{h=2}^{\infty} I_{h}\sin(\omega_{h}t - \psi_{h})$$

For the converter line currents, the use of an appropriate modulation technique ideally provides a component at the fundamental frequency (e.g., the supply frequency or the frequency of the reference current waveform) and the harmonic components at the carrier frequency and its multiples, as in (2.1). These harmonic components of converter line currents are filtered out and only the fundamental component is used to compensate the reactive load currents.

By the applied modulation method, the modulation index (*M*) is defined as the ratio of the amplitude of the fundamental component in the converter line current ( $I_{CSC}$ ) to the dc-link current ( $I_{dc}$ ).

$$M = \frac{I_{CSC}}{I_{DC}}$$

(2.2)

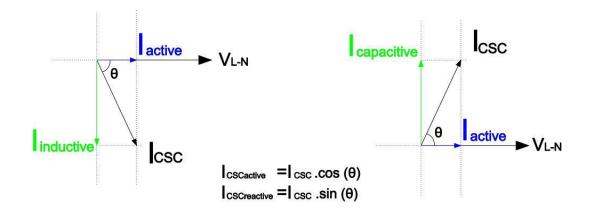

As shown in Figure 2.6, the fundamental component of the converter line current can be decomposed into active and reactive components. Active component is in phase with the corresponding line voltage and the reactive component is in quadrature axis, lagging or leading the corresponding line voltage. Active and reactive components of generated phase currents can be controlled independently. This will be explained in detail by using equivalent circuit of CSC STATCOM in dq-synchronous reference frame.

Figure 2.6 Vector Representation of Capacitive and Inductive Currents

#### 2.2.1 Modeling of CSC STATCOM in dq Synchronous Reference Frame

CSC based STATCOM will be modeled in dq-synchronous frame for balanced AC supply. Modelling in dq-synchronous frame supply less number of control variables which are dc at supply frequency. Obtaining dc control variables instead of ac variables provides better filtering of harmonic components and simplicity in controlling the system.

For modeling, the equivalent circuit shown in Figure 2.7 will be used. In this circuit, three phase delta connected filter capacitor bank is connected in wye and equivalent capacitance of each capactior is taken as 3C. Following assumptions will be considered in the modeling:

i)all the power semiconductor switches are lossless

ii)three phase balanced AC supply having harmonic-free line voltages, as defined in Figure 2.7.

$$V_{\rm R} = V\cos(\omega t)$$

$$V_{\rm S} = V\cos(\omega t - 2\pi/3)$$

$$V_{\rm T} = V\cos(\omega t - 4\pi/3)$$

(2.3)

Figure 2.7 Circuit diagram of CSC based STATCOM to be used for modeling

AC side differential equations are given in (2.4) for phase *R*. Same equations can be easily written for the other phases, *S* and *T*.

$$V_{R} = Ri_{SR} + L\frac{di_{SR}}{dt} + V_{CR}$$

$$i_{SR} = 3C\frac{dv_{CR}}{dt} + i_{R}$$

(2.4)

Dc side differential equation of CSC based STATCOM is as follows

$$\mathbf{V}_{\rm dc} = L_{dc} \, \frac{di_{dc}}{dt} + R_{dc} i_{dc} \tag{2.5}$$

AC side and dc side quantities are coupled with switching functions as in (2.6).

$$V_{dc} = (m_{s1} - m_{s4})V_{CR} + (m_{s3} - m_{s6})V_{CS} + (m_{s5} - m_{s2})V_{CT}$$

$$I_R = (m_{s1} - m_{s4})i_{dc}$$

$$I_S = (m_{s3} - m_{s6})i_{dc}$$

$$I_T = (m_{s5} - m_{s2})i_{dc}$$

(2.6)

Using (2.4), (2.5) and (2.6) these switching functions can be expressed in terms of their Fourier components as in (2.7).

$$m_{s1} - m_{s4} = M \sin(\omega t + \theta) + b_h \sin(\omega_h t - \lambda)$$

$$m_{s3} - m_{s6} = M \sin(\omega t + \theta - 2\pi/3) + b_h \sin(\omega_h t - \xi)$$

$$m_{s5} - m_{s2} = M \sin(\omega t + \theta - 4\pi/3) + b_h \sin(\omega_h t - \psi)$$

(2.7)

Switching functions do not linearly dependent on the control variables modulation index, M and phase angle,  $\theta$  since they contain harmonic components, which do not depend on modulation index and phase angle explicitly.

In order to linearize the switching functions harmonic components should be neglected. This does not cause any problem in analyzing the system performance since harmonics do not contribute to active and reactive power flow. Then, switching functions can be approximated as in (2.8).

$$m_{s1} - m_{s4} \cong M \sin(\omega t + \theta)$$

$$m_{s3} - m_{s6} \cong M \sin(\omega t + \theta - 2\pi/3)$$

$$m_{s5} - m_{s2} \cong M \sin(\omega t + \theta - 4\pi/3)$$

(2.8)

Before applying transformation from *abc*-rotating frame to 0dq -synchronous frame, (2.4) and (2.6) must be rearranged and put into appropriate matrix form as in (2.9) (2.10) and (2.11) where p=d/dt

$$\begin{bmatrix} V_R \\ V_S \\ V_T \\ i_R \\ i_S \\ i_T \end{bmatrix} = \begin{bmatrix} Lp + R & 0 & 0 & 1 & 0 & 0 \\ 0 & Lp + R & 0 & 0 & 1 & 0 \\ 0 & 0 & Lp + R & 0 & 0 & 1 \\ 1 & 0 & 0 & -3Cp & 0 & 0 \\ 0 & 1 & 0 & 0 & -3Cp & 0 \\ 0 & 0 & 1 & 0 & 0 & -3Cp \end{bmatrix} \begin{bmatrix} i_{SR} \\ i_{SS} \\ i_{ST} \\ v_{CR} \\ v_{CS} \\ v_{CT} \end{bmatrix}$$

(2.9)

$$\mathbf{v}_{dc} = \begin{bmatrix} M \sin(\omega t + \theta) & M \sin(\omega t + \theta - 120^{\circ}) & M \sin(\omega t + \theta - 240^{\circ}) \end{bmatrix} \begin{bmatrix} v_{CR} \\ v_{CS} \\ v_{CT} \end{bmatrix}$$

(2.10)

$$\begin{bmatrix} \mathbf{i}_{\mathrm{R}} \\ \mathbf{i}_{\mathrm{S}} \\ \mathbf{i}_{\mathrm{T}} \end{bmatrix} = \begin{bmatrix} M \sin(\omega t + \theta) \\ M \sin(\omega t + \theta - 120^{0}) \\ M \sin(\omega t + \theta - 240^{0}) \end{bmatrix} \begin{bmatrix} \mathbf{i}_{dc} \end{bmatrix}$$

(2.11)

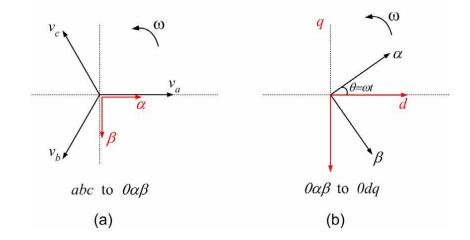

Transformation takes place first from abc-rotating frame to  $\partial \alpha \beta$ -rotating frame, then to  $\partial dq$ -synchronous frame. These are done by proper transformation matrices. These transformation matrices are derived referring to Figure 2.8 as in (2.12) - (2.15).

$$\begin{bmatrix} a \\ b \\ c \end{bmatrix} = C_1 \begin{bmatrix} 0 \\ \alpha \\ \beta \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1/\sqrt{2} & 1 & 0 \\ 1/\sqrt{2} & -1/2 & \sqrt{3}/2 \\ 1/\sqrt{2} & -1/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} 0 \\ \alpha \\ \beta \end{bmatrix}$$

(2.12)

$$\begin{bmatrix} 0\\ \alpha\\ \beta \end{bmatrix} = C_2 \begin{bmatrix} 0\\ d\\ q \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0\\ 0 & \cos \omega t & -\sin \omega t\\ 0 & \sin \omega t & \cos \omega t \end{bmatrix} \begin{bmatrix} 0\\ d\\ q \end{bmatrix}$$

(2.13)

$$C_{1} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1/\sqrt{2} & 1 & 0\\ 1/\sqrt{2} & -1/2 & \sqrt{3}/2\\ 1/\sqrt{2} & -1/2 & -\sqrt{3}/2 \end{bmatrix}$$

(2.14)

$$C_{2} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \cos \omega t & -\sin \omega t \\ 0 & \sin \omega t & \cos \omega t \end{bmatrix}$$

(2.15)

Figure 2.8 Phasor diagrams used in deriving transformation matrices

Since transformation matrices are "orthogonal matrices", such that they satisfy (2.16) and (2.17).

$$C_1^T C_1 = 1 (2.16)$$

$$C_2^T C_2 = 1$$

(2.17)

The transformation matrices are applied to both sides of (2.9) as in (2.18). These transformation matrices are also applied to right-hand side of (2.10) and lefthand side of (2.11) as in (2.18) and (2.19) respectively.

$$C_{1}C_{2}\begin{bmatrix}v_{0}\\v_{d}\\v_{q}\\i_{0}\\i_{d}\\i_{q}\end{bmatrix} = \begin{bmatrix}Lp+R & 0 & 0 & 1 & 0 & 0\\0 & Lp+R & 0 & 0 & 1 & 0\\0 & 0 & Lp+R & 0 & 0 & 1\\1 & 0 & 0 & -3Cp & 0 & 0\\0 & 1 & 0 & 0 & -3Cp & 0\\0 & 0 & 1 & 0 & 0 & -3Cp\end{bmatrix} C_{1}C_{2}\begin{bmatrix}i_{s0}\\i_{sd}\\i_{sq}\\v_{c0}\\v_{cd}\\v_{cq}\end{bmatrix}$$

(2.18)

$$\mathbf{v}_{dc} = \begin{bmatrix} M\sin(\omega t + \theta) & M\sin(\omega t + \theta - 120^{\circ}) & M\sin(\omega t + \theta - 240^{\circ}) \end{bmatrix} C_1 C_2 \begin{bmatrix} v_{C0} \\ v_{Cd} \\ v_{Cq} \end{bmatrix}$$

(2.19)

$$C_{1}C_{2}\begin{bmatrix}i_{0}\\i_{d}\\i_{q}\end{bmatrix} = \begin{bmatrix}M\sin(\omega t + \theta)\\M\sin(\omega t + \theta - 120^{0})\\M\sin(\omega t + \theta - 240^{0})\end{bmatrix}\begin{bmatrix}i_{dc}\end{bmatrix}$$

(2.20)

Equations in (2.18) and (2.20) can be arranged as in (2.21) and (2.22) respectively.

$$\begin{bmatrix} v_{0} \\ v_{d} \\ v_{q} \\ i_{0} \\ i_{d} \\ i_{q} \end{bmatrix} = C_{2}^{-1}C_{1}^{-1} \begin{bmatrix} Lp + R & 0 & 0 & 1 & 0 & 0 \\ 0 & Lp + R & 0 & 0 & 1 & 0 \\ 0 & 0 & Lp + R & 0 & 0 & 1 \\ 1 & 0 & 0 & -3Cp & 0 & 0 \\ 0 & 1 & 0 & 0 & -3Cp & 0 \\ 0 & 0 & 1 & 0 & 0 & -3Cp \end{bmatrix} C_{1}C_{2} \begin{bmatrix} i_{s0} \\ i_{sd} \\ v_{c0} \\ v_{c0} \\ v_{cd} \\ v_{cq} \end{bmatrix}$$

(2.21)

$$\begin{bmatrix} \mathbf{i}_{0} \\ \mathbf{i}_{d} \\ \mathbf{i}_{q} \end{bmatrix} = C_{2}^{-1} C_{1}^{-1} \begin{bmatrix} M \sin(\omega t + \theta) \\ M \sin(\omega t + \theta - 120^{0}) \\ M \sin(\omega t + \theta - 240^{0}) \end{bmatrix} \begin{bmatrix} \mathbf{i}_{dc} \\ \mathbf{i}_{dc} \end{bmatrix}$$

(2.22)

\_

In applying transformation matrices, the effect of operator "p" should be noted as given in (2.23). After applying transformation matrices to (2.19), (2.21) and (2.22), expressions in Odq-synchronous frame are obtained and given in (2.24), (2.25) and (2.26).

$$(L_p + R)\cos\omega t = -\omega L\sin\omega t + \cos\omega t (L_p + R)$$

(2.23)

$$\begin{bmatrix} v_{0} \\ v_{d} \\ i_{q} \\ i_{q} \\ i_{q} \end{bmatrix} = \begin{bmatrix} Lp + R & 0 & 0 & 1 & 0 & 0 \\ 0 & Lp + R & -\omega L & 0 & 1 & 0 \\ 0 & \omega L & Lp + R & 0 & 0 & 1 \\ 1 & 0 & 0 & -3Cp & 0 & 0 \\ 0 & 1 & 0 & 0 & -3Cp & 3\omega C \\ 0 & 0 & 1 & 0 & -3\omega C & -3Cp \end{bmatrix} \begin{bmatrix} i_{S0} \\ i_{Sd} \\ v_{C0} \\ v_{C0} \\ v_{Cq} \end{bmatrix}$$

(2.24)

$$\begin{bmatrix} i_0 \\ i_d \\ i_q \end{bmatrix} = \begin{bmatrix} 0 \\ \sqrt{\frac{3}{2}}M\sin\theta \\ -\sqrt{\frac{3}{2}}M\cos\theta \end{bmatrix} \begin{bmatrix} i_{dc} \end{bmatrix}$$

(2.25)

$$\mathbf{v}_{dc} = \begin{bmatrix} 0 & \sqrt{\frac{3}{2}}M\sin\theta & -\sqrt{\frac{3}{2}}M\cos\theta \end{bmatrix} \begin{bmatrix} v_{C0} \\ v_{Cd} \\ v_{Cq} \end{bmatrix}$$

(2.26)

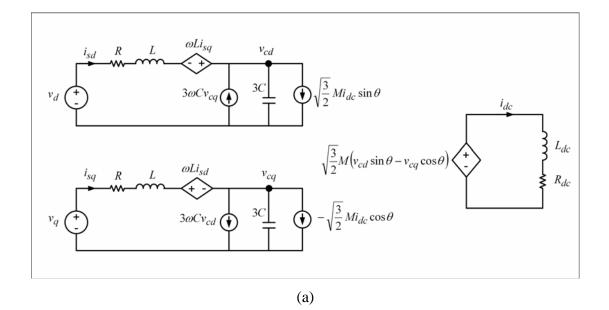

From the representation of CSC STATCOM in (2.24), (2.25) and (2.26) equivalent circuit in dq-synchronous frame can be found as given in Figure 2.9. Advantage of the equivalent circuit in Figure 2.9 is that all quantities at supply frequency become dc quantity in steady-state as shown in Figure 2.10. Based on the transformation matrices and equivalent circuits, active and reactive power can be defined as in (2.27) and (2.28).

$$P = V_d I_{sd} + V_q I_{sq}$$

$$Q = -V_d I_{sq} + V_q I_{sd}$$

$$(2.27)$$

Figure 2.9 Equivalent circuit of CSC based STATCOM in dq-synchronous frame for transient state

Figure 2.10 Equivalent circuit of CSC based STATCOM in dq-synchronous frame for steady state

In the presented steady state dq model which is given in Figure 2.10, since the supply voltage is balanced  $V_q$  component is zero and active power drawn by CSC STATCOM can be calculated by the formula (2.29). Since  $V_d$  is constant active power is controlled by changing  $I_{sd}$ .  $I_{sd}$  is controlled by controlling active component of converter current  $i_d$ .

$$P = V_d I_{sd} + V_q I_{sq} = V_d I_{sd}$$

(2.29)

In the steady state model of dc-link only internal resistance of the dc-link reactor is taken into account and active power of dc-link can be calculated by (2.30).

$$P_{dc} = \sqrt{\frac{3}{2}} M I_{dc} \sin \theta . v_{Cd} - \sqrt{\frac{3}{2}} M I_{dc} \cos \theta . v_{Cq} = I_{dc}^2 R_{dc}$$

$$i_d = \sqrt{\frac{3}{2}} M I_{dc} \sin \theta \qquad i_q = \sqrt{\frac{3}{2}} M I_{dc} \cos \theta$$

$$P_{dc} = i_d v_{Cd} - i_q v_{Cq} = I_{dc}^2 R_{dc}$$

(2.30)

As can be seen in (2.30)  $P_{dc}$  should be kept constant in order to have constant dc-link current  $I_{dc}$ . Since  $P_{dc}$  is constant  $i_d$  will be affected from changes in  $i_q$  during reactive power control. By controlling  $i_d$  dc-link current is tried to be kept constant. Control of dc-link current is achieved by using control blocks given in Figure 2.11.

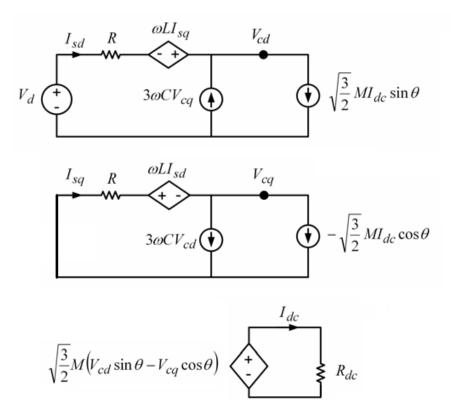

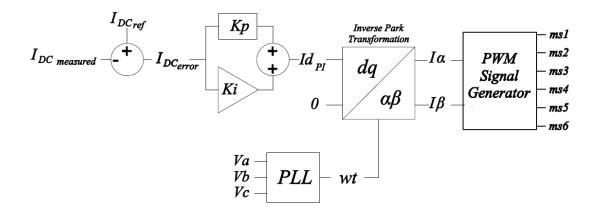

Figure 2.11 Active Current Control

$I_{DCref}$  is the set value for dc current.  $I_{DCmeasured}$  is the measured dc-link current value. The difference between reference dc current and measured dc current is kept zero by close loop PI type controller. PI controller gives ( $Id_{PI}$ ) current as output and it is transformed by inverse park transformation block. PWM signal generator calculates  $m_{s1}$ ,  $m_{s2}$ ,  $m_{s3}$ ,  $m_{s4}$ ,  $m_{s5}$  and  $m_{s6}$  switching signals which generates active current component. If  $Iq_{PI}$  component is taken as zero CSC STATCOM does not generate reactive current. By using this control method dc-link current is kept at a constant  $I_{DCref}$  value. Dc-link current value limits the peak value of generated CSC current. If modulation index takes its maximum value M=1 dc-link current is equal to peak value of CSC current (2.2).

As can be seen in Figure 2.10  $V_q$  component is zero in steady state conditions and reactive power can be calculated by using (2.31). Since the supply voltage  $V_d$  is constant reactive power can be controlled by controlling  $I_{sq}$ .  $I_{sq}$  is controlled by controlling reactive component of converter current  $i_q$ .

$$Q = -V_d I_{sq} + V_q I_{sd} = -V_d I_{sq}$$

(2.31)

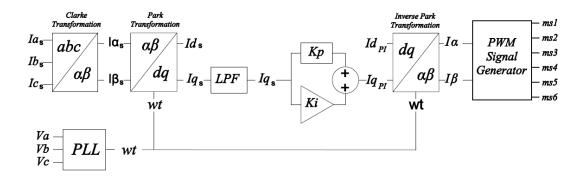

Figure 2.12 Reactive Current Control

In Figure 2.12 three phase supply currents at point of common coupling ( $Ia_s$ ,  $Ib_s$  and  $Ic_s$ ) are transformed by Clarke and Park transformations and  $Iq_s$  is obtained. Fundamental component of reactive supply current is filtered by a low pass filter. Fundamental component of  $Iq_s$  is kept zero by using close loop PI type controller. PI controller gives  $Iq_{PI}$  current as output.  $Iq_{PI}$  and is transformed by inverse park transformation block. PWM signal generator calculates  $m_{s1}$ ,  $m_{s2}$ ,  $m_{s3}$ ,  $m_{s4}$ ,  $m_{s5}$  and  $m_{s6}$  switching signals which generates reactive current component.

The total block diagram of the proposed control system based on dq-synchronous reference frame is given in Figure 2.13. Since the equivalent circuit of CSC STATCOM in dq-synchronous reference frame presents decoupled control variables  $(i_d, i_q)$ , the dc-link current can be controlled by active power transfer from ac-side to dc-side or vice versa via  $i_d$ . On the other hand, the reactive current of CSC STATCOM can be indepedently controlled via  $i_q$ .

Therefore, the control system is composed of two parts: dc-link current control and the reactive curent control. The conventional proportional-integral (PI) controller is used both for the dc-link control and the reactive current control.

Figure 2.13 Reference Current Generation

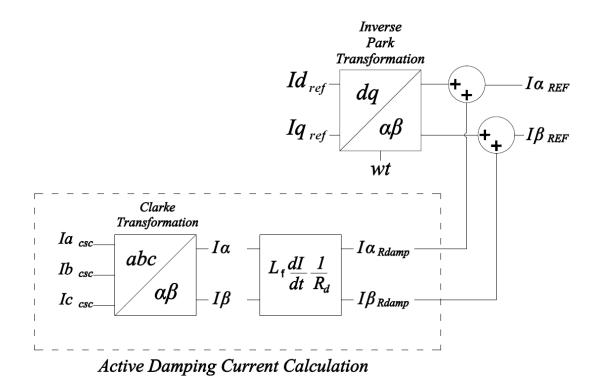

Direct axis component of reference current  $(Id_{ref})$  gives active component information of reference current and quadrature axis component  $(Iq_{ref})$  gives reactive component information of reference current.  $Id_{ref}$  and  $Iq_{ref}$  components are converted to  $I_{\alpha REF}$  and  $I_{\beta REF}$  by using inverse park transformation block.

### 2.2.1.1 Active Damping Method

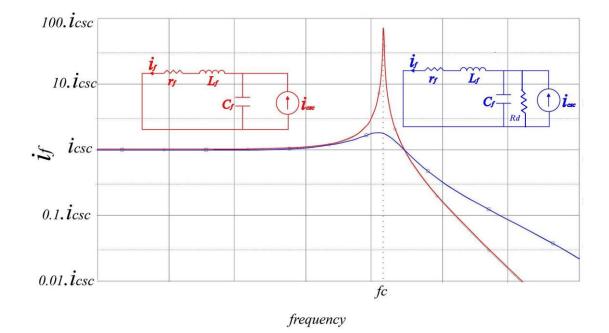

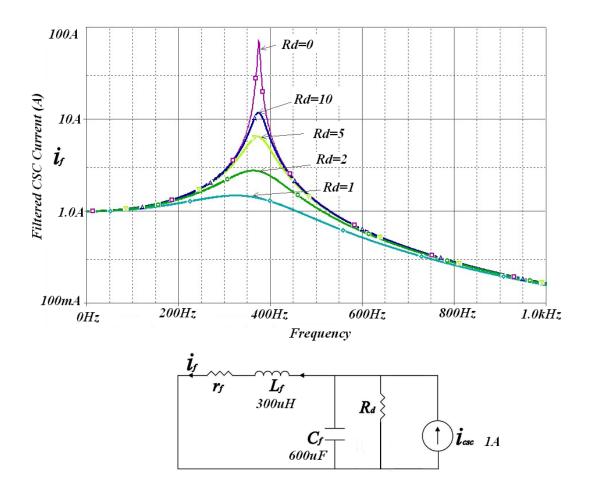

In Figure 2.14, a typical frequency response of a LC filter is given. The red line shows the lightly damped frequency response, where the power loss in the filter is negligibly small (i.e., the internal resistance of the filter reactor,  $r_f$  is small). The blue line shows under damped frequency response where a considerable power loss in the filter exists due to the presence of  $R_d$ .

Figure 2.14 Frequency Response of LC filter with & without Damping Resistor

Lightly damped LC filters used in current source converter applications may cause oscillations even if a small harmonic component of the converter line current exists at a frequency around the corner frequency ( $f_c$ ). In order to damp these oscillations quality factor Q of the designed filter should be low. Introducing a damping resistor increases the power loss in the filter and minimizes quality factor Q of the filter (2.32)  $\omega$  is defined to be the angular frequency of the system.

$$Q = \omega \times \frac{\text{Energy Stored}}{\text{Power Loss}}$$

(2.32)

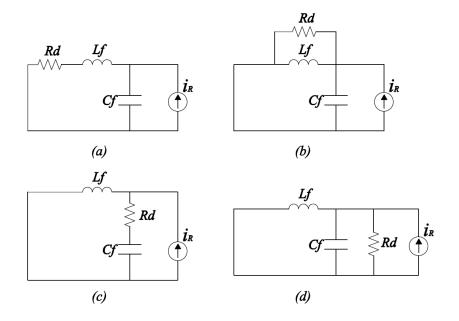

As can be seen in Figure 2.15, damping resistor can be connected in series with filter reactor, parallel to filter reactor [6], in series with filter capacitor or parallel to filter capacitor. But in high power applications, this resistor causes undesired power losses.

Figure 2.15 Connection of Damping Resistor

Active damping method proposes that a virtual damping resistor can be implemented by the flexible current generating capability of CSC, where on-line PWM methods are employed [10-14].

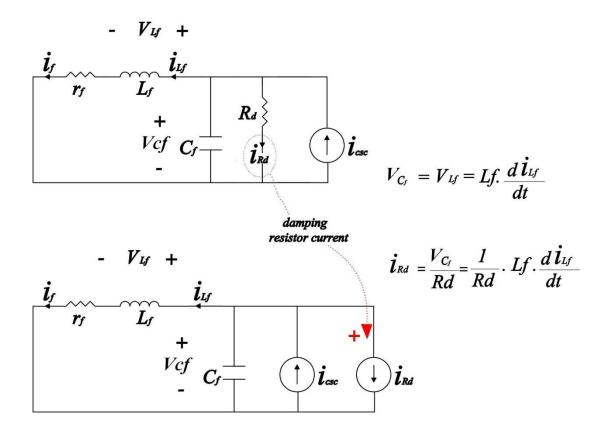

As can be seen in Figure 2.16, voltage across the damping resistor is equal to voltage across the filter capacitor  $V_c$ . Since the damping resistor is not effective at the fundamental frequency, i.e., the supply frequency, the supply voltage can be considered to be short circuit in the equivalent circuit in Figure 2.16. Moreover, if filter resistance  $(r_f)$  is ignored, then the voltage across  $R_d$  is also equal to the voltage across the filter inductance  $V_l$ .  $V_l$  can be calculated by measuring the line current of the filter reactor.

Figure 2.16 Active Damping Method

By taking the derivative of measured STATCOM line current and multiplying it by the inductance of the filter reactor and then dividing it to the resistance of the virtual damping resistor, the damping current can be obtained (see Figure 2.16).

Since the reference current waveform to be generated by the CSC is obtained in  $\alpha$ - $\beta$  rotating frame, the currents of the virtual damping resistor are also obtained in  $\alpha$ - $\beta$  rotating frame. For this purpose, the three-phase STATCOM line current quantities transformed into  $\alpha$ - $\beta$  rotating frame by Clarke transformation.

The current waveform of the virtual damping resistor can then be added to reference currents which are calculated from dc-link current and reactive current control,  $I_{dref}$  and  $I_{qref}$ , respectively as illustrated in Figure 2.17.

Figure 2.17 Active Damping Reference Current Calculation

Selection of the virtual damping resistance requires a good compromise. A small damping resistance is preferred for decreasing Q of the filter, thus minimizing the oscillations around corner frequency. On the other hand, unnecessarily small damping resistance makes the active damping loop gain too high such that the contribution of the damping current to the reference current becomes too high and the dc-link current and the reactive current control is lost. Selection of damping resistor will be explained in chapter 3 in filter design part.

### 2.3 Modulation Techniques

In voltage source and current source converter applications switching pattern of semiconductor switches are generated by different modulation methods [15-17]. Developments in semiconductor production technologies and the evolution and variation of these modulation techniques are dependent to each other. The frequency limit of the semiconductor switches is the most important parameter which determines the modulation type.

Developed modulation techniques are implementable to high frequency current source converter applications [18-24]. High frequency modulation methods provide the advantage of generating sinusoidal currents with negligible lower order harmonics. Since the lower order harmonics are negligible a smaller low pass input filter can be designed by selecting a higher corner frequency in order to filter harmonics around switching frequency.

Also by applying high frequency modulation techniques dc-link current ripples will be minimized. As long as the modulation frequency is increased a smaller dc-link reactor with a lower time constant will be sufficient in order to generate constant dc current on dc-link of the converter. But as a drawback increase in switching frequency increases switching losses. Modulation techniques have different nature depending on how they have been generated. They are categorized as off-line techniques and on-line techniques. In offline techniques switching signals are calculated by optimization techniques as constant patterns in order to eliminate lower order harmonics but, the tradeoff is slow dynamic response and imprecise control of the ac line current. Selective Harmonic Elimination Method (SHEM) is an off-line modulation technique [25]. Online modulation techniques can be classified in analog modulation techniques and digital modulation techniques. Analog modulation techniques are based on the comparison of a reference signal with a carrier signal; they are also named as carrier based modulation methods. Sinusoidal pulse width modulation (SPWM), dead band SPWM (DSPWM) [23], modified dead band SPWM (MDSPWM) are some examples to carrier based PWM techniques which will be analyzed in the scope of the thesis. Digital modulation techniques are based on the space vector technique. There are several space vector PWM (SVPWM) methods which propose different switching patterns are available in literature [26, 24]. And also in this thesis SVPWM method is analyzed and compared with DSPWM and MDSPWM methods. In appendix B generation methods for DSPWM and MDSPWM methods are illustrated. On-line pattern generation methods are more preferable in high frequency applications with respect to off-line methods, because on-line methods provide faster dynamic response, continuous and precise control of the ac current. Also active damping method is applicable only with on-line modulation techniques.

Comparison results between modulating signals with active damping method will be presented in chapter 3.

### 2.4 Commutation Types

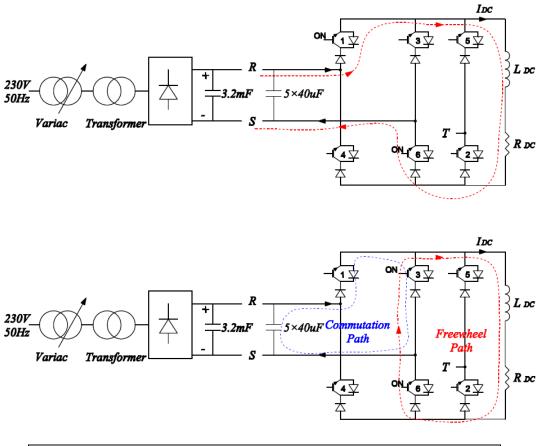

In the forced-commutated CSC in Figure 2.3, only two power semiconductors, one in the upper half and one in the lower half of the bridge are in conduction at any time so

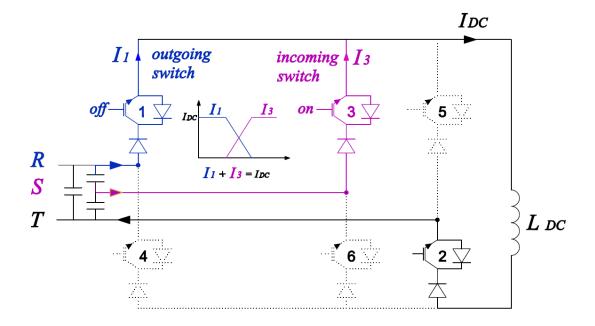

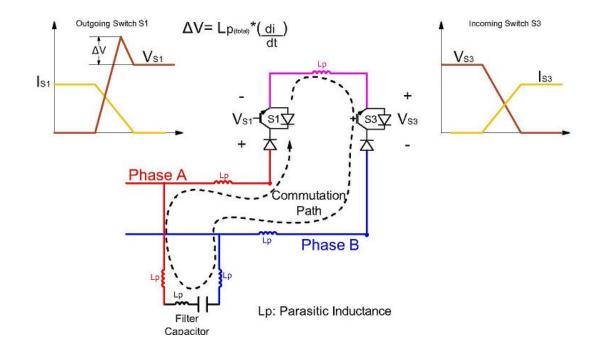

that the continuous flow of dc-link current can be guaranteed. However, during commutation which can be defined as the transfer of dc-link current among the power semiconductors and takes less than a microsecond for IGBTs, the dc-link current is transferred from one semiconductor to another in the same half of the bridge while one of the semiconductors in the other half is in conduction as shown in Figure 2.18. All possible commutation paths of the current between incoming and outgoing switches are as given in Figure 2.19.

There are two types of commutation; forced commutation and load commutation.

Figure 2.18 Commutation path

Figure 2.19 Commutation Paths

### 2.4.1 Forced Commutation

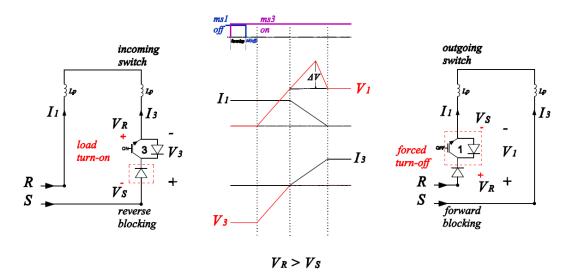

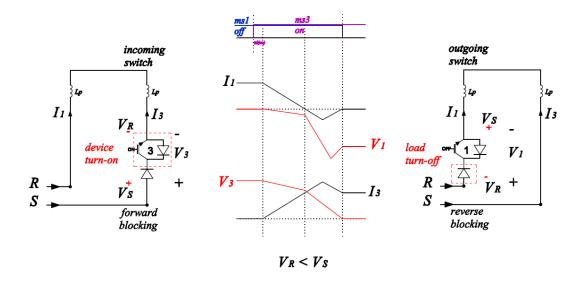

If the voltage across the incoming switch  $(S_3)$  is negative just before the commutation (i.e.,  $V_{RS} > 0$  and series diode of  $S_3$  is reverse-biased and blocking this negative voltage as shown in Figure 2.21), the voltage across the outgoing switch  $(S_1)$  will be positive (i.e., IGBT of  $S_1$  will block as shown in Figure 2.21). When the incoming switch receives ON signal, its current does not increase until the voltage across it decreases to zero (i.e., the series diode of the incoming switch is forward-biased). As the outgoing switch receives OFF signal, its voltage starts to increase to line-to-line voltage (i.e.,  $V_{RS}$  in Figure 2.20). This simultaneously decreases the voltage across the incoming switch. When the voltage across the outgoing switch is equal to line-toline voltage, the voltage across the incoming switch is equal to line-toline through the outgoing switch starts to transfer to incoming switch. This transfer continues until the incoming switch full takes over the dc-link current.

**Figure 2.20 Forced Commutation**

The mechanism which starts with the generation of ON signal for the incoming switch and ends with the complete transfer of dc-link current from the outgoing switch to incoming switch is called as *forced commutation*.

The turn-off of the outgoing switch is called as *forced turn-off* and the turn-on of the out-going switch is called as *load turn-on*.

Forced commutation requires that the incoming switch should receive ON signal before the outgoing switch receives OFF signal because the incoming switch should be ready to take over the current before the transfer of dc-link current is initiated. This is illustrated in Figure 2.20 as an overlap in the switching signals,  $m_{s1}$  and  $m_{s3}$ .

#### 2.4.2 Load Commutation

As shown in Figure 2.21, if  $V_R < V_S$  incoming switch voltage polarity is positive when it is not conducting. And the forward voltage is blocked by  $S_3$  IGBT. When  $S_3$ receives on signal the voltage on  $S_3$  starts to decrease after a delay time and current through  $S_3$  starts to increase. This type of turn on is called as *device turn-on*. Since current on  $S_1$  is decaying, voltage  $V_1$  starts to decrease to  $V_{RS}$  value.

When the voltage on  $S_3$  is equal to zero, voltage on  $S_1$  decreases to negative  $V_{RS}$  voltage and this reverse voltage is blocked by  $S_1$  diode. This type of turn-off mechanism is called as *load turn-off*.  $S_1$  switch is turned off by applying reverse voltage on diode without any turn-off signal applied to gate.

Reverse recovery current of diode can be minimized by choosing a better diode characteristics or reducing rate of change of current (di/dt). Since the total current  $I_1+I_3$  should be equal to  $I_{dc}$ , during reverse recovery process  $I_3$  current exceeds  $I_{dc}$  value. Semiconductor current carrying capacity should meet this excessive current.

Figure 2.21 Load Commutation

Commutation mechanism, voltage and current characteristics of semiconductor switches during commutation should be understood carefully in order to design current source converter power stage and determine semiconductor device parameters. Selection of semiconductor devices and design of power stage will be explained in detail in chapter 3.

### 2.5 Summary

In this chapter, system description and operating principles of three phase CSC based STATCOM have been presented. DQ model of CSC STATCOM is derived and dqcontrol method is explained in detail. The relation between direct axis component of CSC STATCOM current and active power control, and quadrature axis component of converter current and reactive power control is described. Active damping method is introduced and modulation methods for current source converters are discussed. Finally current commutation types are explained and the voltage and current behaviors during commutation are illustrated with figures.

## **CHAPTER 3**

# **DESIGN OF CSC STATCOM**

### 3.1 Introduction

In chapter 2, theoretical background and operating principles of current source converter (CSC) based STATCOM is introduced. Modulation technique, active and reactive power control technique and active damping method have been explained in detail. These techniques and theoretical methods are modeled by using PSCAD/EMTDC simulation tool [27]. These simulations have shown that the CSC STATCOM provides fast and satisfactory reactive power compensation.

In this chapter design principles of CSC STATCOM will be presented for the implementation of the prototype at low voltage. The design work has been carried out by using simulation tools: PSCAD/EMTDC, MATLAB and ORCAD [27-29].

First, the technical specifications of the prototype are specified. Then, the candidate modulation techniques for the generation of switching signals are benchmarked. The considerations in the design input filter and selection of dc-link reactor are presented. Afterward, the determination of the ratings for power semiconductors is stated. The most challenging design work on the design of power stage is set out in view of the chosen power semiconductors. Finally, the principles in tuning the parameters of the control system are described.

## 3.2 Design Specifications of CSC STATCOM

Within the scope of this research, the prototype of CSC STATCOM will be designed and implemented at low voltage in order to achieve i) fast transient response in reactive power compensation, ii) low current harmonic distortion, iii) low power losses, iv) minimum storage elements. The technical specifications of the laboratory prototype are given in Table 3.1.

| Converter Reactive Power | $\pm$ 70 kVAr         |

|--------------------------|-----------------------|

| System Voltage           | $400V \pm \%10, 50Hz$ |

| Cooling System           | Air forced cooling    |

| I_TDD                    | ≤ 5 %                 |

Table 3.1 Technical Specifications of CSC STATCOM

#### **3.3** Selection of Modulation Technique

As mentioned in part 2.3 on-line modulation techniques are compared in this Section. Dead-band sinusoidal pulse width modulation (DSPWM), modified dead-band sinusoidal pulse width modulation (MDSPWM) and space vector pulse width modulation SVPWM techniques are the most common on-line modulation techniques in current source converter applications. The comparison criteria are based on switching frequency, total harmonic distortion and the magnitude of the low-order harmonics.

### Switching frequency:

The switching losses directly depend on the switching frequency. Therefore, low switching frequency is preferred. The comparison of the modulation techniques is given in Table 3.2. DSPWM has the highest switching frequency for the same carrier frequency.

### Table 3.2 Modulation Technique vs. Switching Frequency

| Modulation Technique | Switch.Freq.      |

|----------------------|-------------------|

| DSPWM                | $\frac{2}{3}fc$   |

| MDSPWM               | $\frac{1}{2}fc$   |

| SVPWM                | $\frac{1}{2}fcyc$ |

$f_c$  is carrier frequency and  $f_{cyc}$  is the sampling frequency

### Total Harmonic Distortion:

The THD of current is defined as in (3.1) where the I<sub>h</sub> is the rms value of the current harmonic components and I<sub>1</sub> is the rms value of the fundamental current component.

$$THD_{I} = \frac{\sqrt{\sum_{h=2}^{h_{max}} I_{h}^{2}}}{I_{1}}$$

(3.1)

The THD<sub>I</sub> defining the distortion level can exhibit quite high (misleadingly, unacceptable) values for nonlinear loads operating under light load conditions. However, since the magnitude of harmonic components is low, this high THD<sub>I</sub> value is not critical and the influence of the harmonic current on the PCC voltage distortion is insignificant. In order to avoid such misinterpretation, IEEE 519 defines the term Total Demand Distortion (TDD), which is given in (3.2) where  $I_h$  is the rms value of current harmonic hth component and  $I_L$  is the rated rms value of the load current at fundamental frequency.

$$TDD = \frac{\sqrt{\sum_{h=2}^{h_{max}} I_h^2}}{I_L}$$

(3.2)

This definition accounts for the loading effect of nonlinear loads. Therefore, the harmonic current limits proposed by IEEE 519 are expressed in terms of TDD rather than THD and are given in Table 3.3 for the customers.

| $I_{SC}/I_{L1}$ | h<11 | 11≤h<17 | 17≤h<23 | 23≤h<35 | 35≤h | TDD (%) |

|-----------------|------|---------|---------|---------|------|---------|

| <20             | 4.0  | 2.0     | 1.5     | 0.6     | 0.3  | 5.0     |

| 20-50           | 7.0  | 3.5     | 2.5     | 1.0     | 0.5  | 8.0     |

| 50-100          | 10.0 | 4.5     | 4.0     | 1.5     | 0.7  | 12.0    |

| 100-1000        | 12.0 | 5.5     | 5.0     | 2.0     | 1.0  | 15.0    |

| >1000           | 15.0 | 7.0     | 6.0     | 2.5     | 1.4  | 20.0    |

Table 3.3 IEEE 519 harmonic current limits

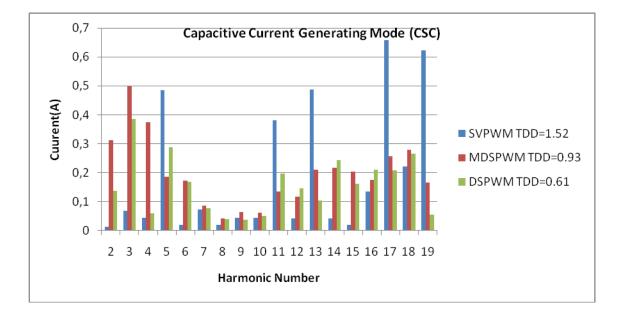

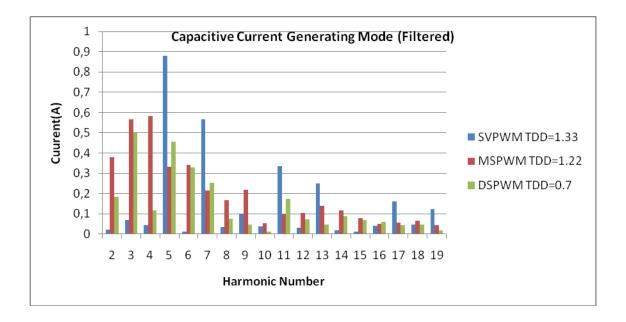

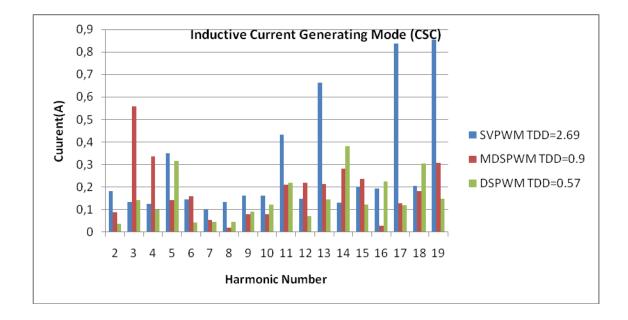

To determine optimum modulation technique for CSC STATCOM, PSCAD simulation results are compared for TDD values calculated at two diffrent operating modes; capacitive mode and inductive mode. Carrier frequencies are specified as 6250 Hz and  $I_L$  is 70 Arms. In all cases fundamental current component generated by CSC STATCOM is 70Arms and harmonic currents are plotted starting from 2<sup>nd</sup> harmonics in order to see graphical values. And the TDD value is calculated by the formula given in (3.3).

$$TDD = \frac{\sqrt{\sum_{h=2}^{19} I_h}}{I_L}$$

(3.3)

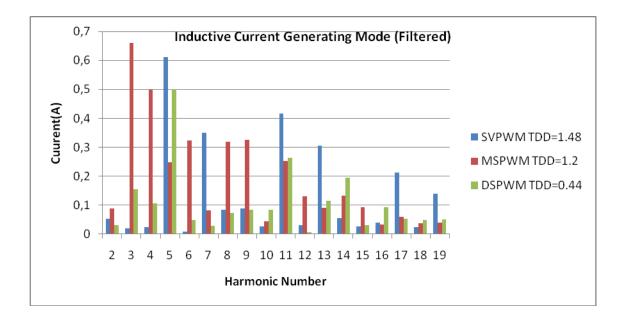

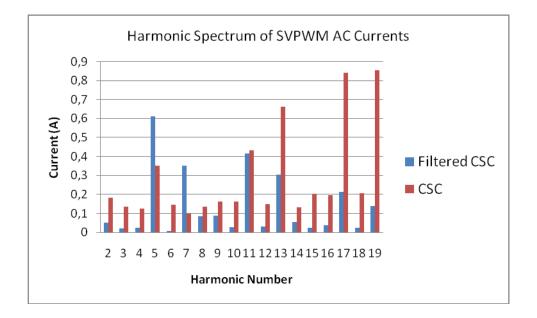

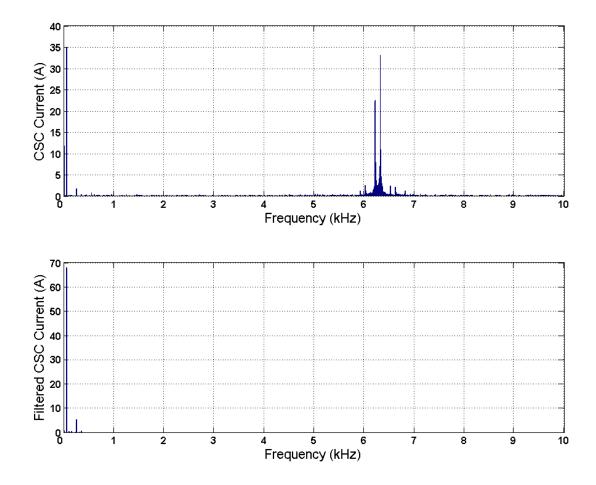

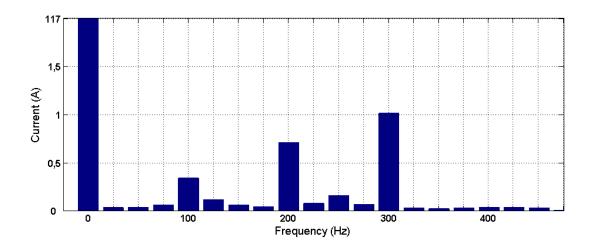

According to the simulation results given in Figure 3.2-3.4, TDD performances of SVPWM and MDSPWM are nearly the same and DSPWM method gives better results, but DSPWM method has higer swithing frequency. DSPWM and MDSPWM are analog on-line modulation techniques and SVPWM is digital modulation technique. Since implementation of SVPWM is more convenient in digital applications it is selected as the modulation technique of CSC STATCOM.

Figure 3.1 Harmonic Spectrum of CSC Current Capacitive Mode

Figure 3.2 Harmonic Spectrum of Filtered CSC Current Capacitive Mode

Figure 3.3 Harmonic Spectrum of CSC Current Inductive Mode

Figure 3.4 Harmonic Spectrum of filtered CSC Current Inductive Mode

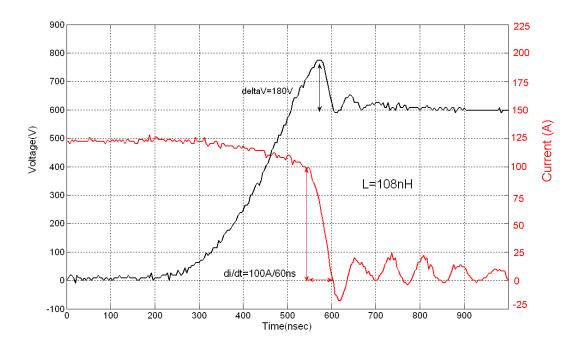

### 3.4 Design of DC Link Reactor

In order to select optimized dc-link reactor value for current source converter, two parameters should be considered; peak-to-peak ripples in dc-link current and the reactor losses.

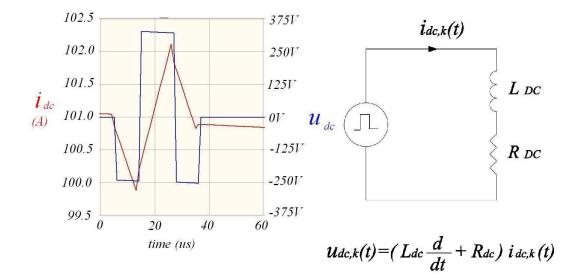

In Figure 3.5 the variation of dc-link voltage and dc-link current is given. DC-link voltage  $V_{dc}(t)$  is composed of mean voltage  $v_{dc}$  and ac component  $v_{ac}(t)$  which is composed of segments of line-to-line input voltage waveform of CSC and zero voltage segments corresponding to freewheeling operation. Since the voltage pulses are very narrow in high frequency SVPWM modulated current source converters, each pulse can be approximated to step functions as given in (3.8) where n is the number of step functions in one complete cycle and  $u_{dc,k}(t)$  is given in Figure 3.5.  $i_{dc,k}(t)$  can be found as given in (3.5).

$$V_{dc}(t) = \sum_{k=1}^{n} u_{dc,k}(t)$$

(3.4)

$$i_{dc,k}(t) = I_{dc0,k} + \frac{u_{dc,k}(t)}{R_{dc}} (1 - e^{-t/\tau_{dc}})$$

(3.5)

Figure 3.5 DC-Link Voltage and Current

Since time constant of dc-link reactor will be very high (milliseconds) as compared to voltage pulse width (microseconds), (3.5) can be approximated as given in (3.6)

$$i_{dc,k}(t) \cong I_{dc0,k} + \frac{u_{dc,k}(t)}{L_{dc}}t$$

(3.6)

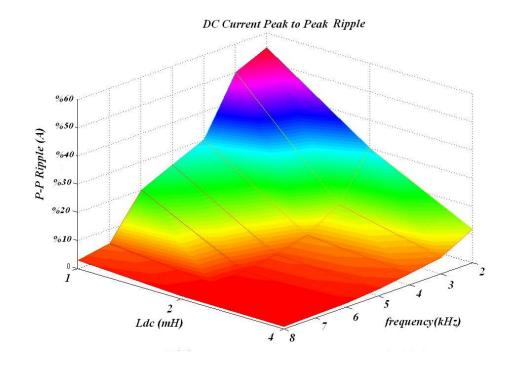

As can be understood from Figure 3.5 and dc-link current formula (3.6), changes in dc-link current is directly related with voltage pulse width and amplitude and inversely related with dc-link inductance value. Increase in modulation frequency decreases voltage pulse width. As can be observed from Figure 3.6 if the switching

frequency is increased, peak-to-peak ripples in dc current can be decreased for the same dc-link reactor. On the other hand, this increases the switching loss. If the inductance value is increased when the modulation frequency is kept constant, again the ripples in dc-link current can be minimized. In order to increase DC-link reactor value, the number of turns in the reactor increases, which causes higher copper losses.

Figure 3.6 DC Current Peak to Peak Ripple