### REAL TIME 3D SURFACE FEATURE EXTRACTION ON FPGA

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SICENES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

### ZAFER HAŞİM TELLİOĞLU

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

JUNE 2010

Approval of the thesis:

### **REAL TIME 3D SURFACE FEATURE EXTRACTION ON FPGA**

submitted by ZAFER HAŞİM TELLİOĞLU in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>          |    |

|------------------------------------------------------------------------------------------------|----|

| Prof. Dr. İsmet Erkmen<br>Head of Department, <b>Electrical and Electronics Engineering</b>    |    |

| Assist. Prof. Dr. İlkay Ulusoy<br>Supervisor, Electrical and Electronics Engineering Dept., ME | TU |

|                                                                                                |    |

| Examining Committee Members:                                                                   |    |

| Prof. Dr. Gözde Bozdağı Akar<br>Electrical and Electronics Engineering Dept., METU             |    |

| Assist. Prof. Dr. İlkay Ulusoy<br>Electrical and Electronics Engineering Dept., METU           |    |

| Assoc. Prof. Dr. Tolga Çiloğlu<br>Electrical and Electronics Engineering Dept., METU           |    |

| Assist. Prof. Dr. Cüneyt Bazlamaçcı<br>Electrical and Electronics Engineering Dept., METU      |    |

| M.Sc. Erdem Akagündüz<br>Image Processing Dep., ASELSAN Inc.                                   |    |

|                                                                                                |    |

Date: 14.06.2010

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name: Zafer Haşim TELLİOĞLU

Signature:

## ABSTRACT

#### **REAL TIME 3D SURFACE FEATURE EXTRACTION ON FPGA**

TELLİOĞLU, Zafer Haşim

M.Sc. Department of Electrical and Electronics Engineering Supervisor: Assist. Prof. İlkay ULUSOY

June 2010, 108 pages

Three dimensional (3D) surface feature extractions based on mean (H) and Gaussian (K) curvature analysis of range maps, also known as depth maps, is an important tool for machine vision applications such as object detection, registration and recognition. Mean and Gaussian curvature calculation algorithms have already been implemented and examined as software. In this thesis, hardware based digital curvature processors are designed. Two types of real time surface feature extraction and classification hardware are developed which perform mean and Gaussian curvature analysis at different scale levels. The techniques use different gradient approximations. A fast square root algorithm using both LUT (look up table) and linear fitting technique is developed to calculate H and K values of the surface described by the 3D Range Map formed by fixed point numbers. The proposed methods are simulated in MatLab software and implemented on different FPGAs using VHDL hardware language. Calculation times, outputs and power analysis of these techniques are compared to CPU based 64 bit float data type calculations.

**Keywords**: FPGA, Scale Space, Gaussian curvature, Mean curvature, HK segmentation, hardware gradient approximation, feature, fast square root calculation

### FPGA KULLANARAK 3B YÜZEYLERİN ÖZNİTELİKLERİNİN GERÇEK ZAMANLI OLARAK ÇIKARTILMASI

TELLİOĞLU, Zafer Haşim Yüksek Lisans, Elektrik Elektronik Mühendisliği Bölümü Tez Yöneticisi: Yrd. Doç. İlkay ULUSOY

Haziran 2010, 108 sayfa

Uzaklık haritaları ile ifade edilen üç boyutlu (3B) yüzeylerin, ortalama (H) ve Gaussian (K) eğrilik analizleri kullanılarak özniteliklerinin çıkartılması, nesne algılamadan tanımaya kadar olan birçok bilgisayar görüntü işleme algoritması için önemli bir teknik olarak görülmektedir. Ortalama ve Gaussian eğrilik analizleri bilgisayarlar üzerinde yazılım tabanlı olarak geliştirilmiş ve uygulanmıştır. Bu çalışmada, FPGA üzerinde gerçek zamanlı çalışan sayısal eğrilik işlemcisi tasarlanmıştır. Hız bakımından yazılım tabanlı uygulamalara alternatif olarak, çoklu ölçekler üzerinde H ve K analizlerine göre yüzey sınıflandırması yapabilen, iki adet farklı sayısal eğrilik işlemcisi geliştirilmiştir. Bu iki işlemci farklı türev hesaplama yaklaşımları kullanmaktadır. İşlemciler içerisinde, analizler için gerekli olan gerçek zamanlı karekök hesaplama devresi tasarlanmıştır. Bu devre, giriş sayılarının olasılıklarını göz önünde tutarak, hatanın en az olması için gerekli bölgelerde RAM kullanan yada doğrusal tahmin yapan bir yapıdır. Analiz edilen yüzeyler sabit noktalı sayı temsilleri ile ifade edilmektedir. İşlemciler MatLab üzerinde tasarlanmış ve test edilmiş, VHDL donanım dili ile iki farklı FPGA üzerinde çalıştırılmıştır. Donanım, simülasyon ve yazılım sonuçları birbirleri ile kıyaslanmıştır. Ayrıca hız sonuçları ve güç tüketimleri de verilmiştir.

Anahtar Kelimeler: Ortalama eğrilik, Gaussian eğrilik, FPGA, hızlı karekök

To My Family

## ACKNOWLEDGEMENTS

I would like to express my thanks to my supervisor Assist. Prof. İlkay Ulusoy for her guidance throughout the development of this thesis. I gratefully thank Erdem Akagündüz for his efforts and motivation during the thesis. His suggestions in several stages of the work provided important improvements in the thesis. I appreciate Burak Şekerlisoy for his assistance in hardware implementation. Also I would like to thank Sibel Şekerlisoy for her contribution in reviewing the thesis. Lastly, I would like to give my sincere thanks to my mother for her love and support all through my life.

# **TABLE OF CONTENTS**

| ABSTR          | ACT            |                                                                   | IV   |

|----------------|----------------|-------------------------------------------------------------------|------|

| ÖZ             | •••••          |                                                                   | V    |

| ACKNO          | OWLEI          | DGEMENTS                                                          | VII  |

| TABLE          | COF CO         | ONTENTS                                                           | VIII |

| LIST O         | F TAB          | LES                                                               | XI   |

| LIST O         | F FIGU         | URES                                                              | XII  |

| СНАРТ          |                |                                                                   |      |

|                |                | CTION                                                             | 1    |

| 1.1            |                | ation                                                             |      |

| 1.1            |                | ground and Literature                                             |      |

| 1.2            |                | s Objective and Outline                                           |      |

|                |                | ARIES                                                             |      |

| 2 I KEI<br>2.1 |                |                                                                   |      |

| 2.1            | e              | e Map                                                             |      |

|                | 2.1.1<br>2.1.2 | Range Map Generation<br>Range Map Precision & Data Formats        |      |

|                | 2.1.2          | Quantization Effect on Range Map                                  |      |

|                | 2.1.4          | Valid and Invalid Points of Range Maps                            | 7    |

|                | 2.1.5          | 3D Range Map                                                      |      |

| 2.2            | Scale          | Space                                                             |      |

| 2.3            | HK Se          | egmentation                                                       |      |

|                | 2.3.1          | Curves, Tangent and Normal Vectors                                |      |

|                | 2.3.2          | Curvature                                                         |      |

|                | 2.3.3<br>2.3.4 | Surface Representation<br>Surface Tangent Plane and Normal Vector |      |

|                | 2.3.5          | Surface Curvature                                                 |      |

|                | 2.3.6          | Principle Curvatures                                              |      |

|                | 2.3.7          | Mean and Gaussian Curvature Based Surface Classification          |      |

|                | 2.3.8          | Derivation of K and H                                             | 24   |

| 2.4            | Real 7         | Гіme Concept                                                      |      |

|                | 2.4.1          | Hardware & Software Partitioning                                  |      |

|                | 2.4.2          | Real Time Criteria in HK Analysis                                 |      |

| c -            | 2.4.3          | Real Time Hardware Platforms                                      |      |

| 2.5            |                | A Basics                                                          |      |

|                | 2.5.1          | Used FPGAs                                                        |      |

| 2.6            | Syster         | n on Chip (SoC) Design                                            |      |

| 3 | DIGI | TAL PH                      | ROCESSING & HARDWARE IMPLEMENTATION                                                     | 36 |  |  |

|---|------|-----------------------------|-----------------------------------------------------------------------------------------|----|--|--|

|   | 3.1  | Mean                        | and Gaussian Curvature Computation in Discrete Domain                                   | 36 |  |  |

|   |      | 3.1.1<br>3.1.2              | Estimation Techniques<br>Noise on Surfaces and Definition of Classification Type Ranges |    |  |  |

|   |      | 3.1.3<br>3.1.4              | Filtering Range Data<br>Thresholds                                                      |    |  |  |

|   | 3.2  | Hardw                       | vare Based Digital Curvature Processor Proposal                                         | 42 |  |  |

|   |      | 3.2.1<br>3.2.2              | Real Time Requirements<br>Control of Parameters                                         |    |  |  |

|   |      | 3.2.2                       | Range Map Data Format and Quantization                                                  |    |  |  |

|   |      | 3.2.4                       | Real Time Stream Signal Input and Parallelism                                           |    |  |  |

|   |      | 3.2.5                       | Pipeline Scale Space Analysis                                                           |    |  |  |

|   |      | 3.2.6                       | Gradient Outputs                                                                        | 51 |  |  |

|   | 3.3  | Non-C                       | ausality Problem in Range Map Processing                                                | 52 |  |  |

|   | 3.4  | Digital                     | Curvature Processor Type 1                                                              | 54 |  |  |

|   |      | 3.4.1                       | Derivative Approximations in Hardware                                                   |    |  |  |

|   |      | 3.4.2<br>3.4.3              | Hardware Scale Space Technique<br>HK Calculation                                        |    |  |  |

|   | 3.5  |                             | I Curvature Processor Type 2                                                            |    |  |  |

|   | 3.5  | -                           |                                                                                         |    |  |  |

|   |      | 3.5.1<br>3.5.2              | Gradient Approximations in Hardware<br>Hardware Scale Space Technique                   |    |  |  |

|   |      | 3.5.3                       | HK Calculation                                                                          |    |  |  |

|   | 3.6  | Surface Type Classification |                                                                                         |    |  |  |

|   | 3.7  | 1                           |                                                                                         |    |  |  |

|   | 3.8  | Thresh                      | nolds                                                                                   | 74 |  |  |

| 4 | EMB  | EDDED                       | O COMPUTER & SOFTWARES                                                                  | 76 |  |  |

|   | 4.1  | Comp                        | uter Architecture                                                                       | 76 |  |  |

|   | 4.2  | Softwa                      | ıre                                                                                     | 78 |  |  |

|   |      | 4.2.1                       | Connected Component and Center of Mass Algorithm                                        |    |  |  |

| 5 | RESU | JLTS &                      | COMPARISONS                                                                             | 82 |  |  |

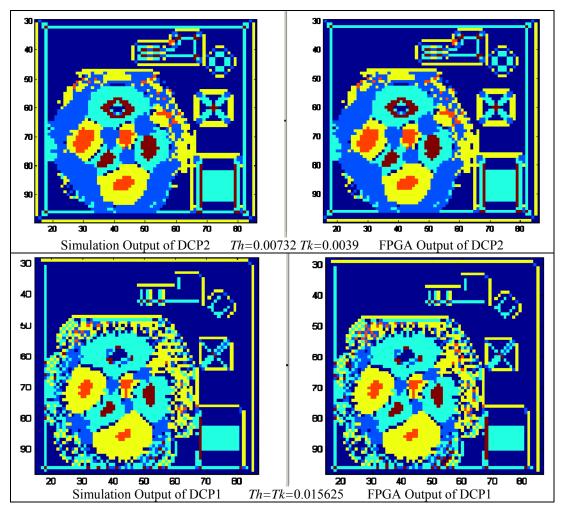

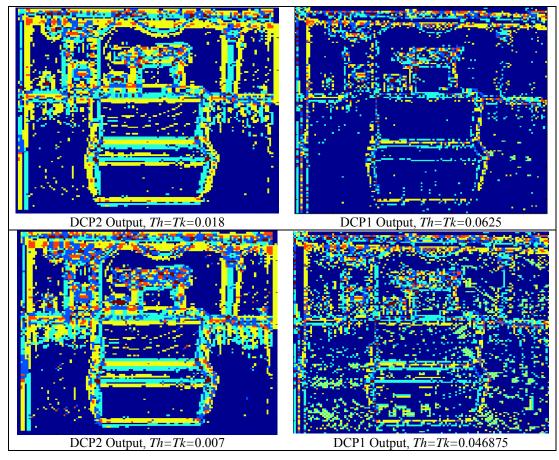

|   | 5.1  | Outpu                       | t Validation and Comparisons                                                            | 82 |  |  |

|   |      | 5.1.1                       | Notation of Classification                                                              |    |  |  |

|   |      | 5.1.2                       | Simulation and Hardware Outputs                                                         |    |  |  |

|   |      | 5.1.3                       | Comparison of DCP Outputs                                                               |    |  |  |

|   |      | 5.1.4<br>5.1.5              | Fix Point Quantization Effect<br>Comparison of Software and Hardware Implementations    |    |  |  |

|   |      | 5.1.6                       | Rounding Operator Effect in DCP2.                                                       |    |  |  |

|   |      | 5.1.7                       | Rotation and Translation Invariance                                                     | 92 |  |  |

|   |      | 5.1.8                       | Scale Space Level Outputs                                                               |    |  |  |

|   | 5.2  |                             | are Output                                                                              |    |  |  |

|   | 5.3  |                             | Measurements and Comparisons                                                            |    |  |  |

|   |      | 5.3.1                       | Software Performance                                                                    | 96 |  |  |

|       | 5.3.2 | Hardware Performance                          | 97    |

|-------|-------|-----------------------------------------------|-------|

|       | 5.3.3 | Hardware and Software Speed Comparison        |       |

| 5.4   | Embe  | edded CPU Connected Component Algorithm Speed |       |

| 5.5   | Powe  | r Analysis                                    |       |

| 6 CON | CLUSI | ON AND FUTURE WORKS                           | 101   |

| REFER | RENCE | S                                             | 103   |

| APPEN | DIX A | MEAN AND GAUSSIAN CURVATURE IN MATL           | AB107 |

# **LIST OF TABLES**

## TABLES

| Table 1 – Gaussian classification of surfaces.                             | 23 |

|----------------------------------------------------------------------------|----|

| Table 2 – Available classifications in HK segmentation.                    | 25 |

| Table 3 – Sign representation in 2's complement form                       | 60 |

| Table 4 – DCP Classification outputs                                       | 67 |

| Table 5 – Effect of coefficient quantization                               | 72 |

| Table 6 – Selected node points for approximation in hardware               | 72 |

| Table 7 – Colored representation of surface classification.                | 83 |

| Table 8 – Time measurements of software implementations in MatLab          | 97 |

| Table 9 – Possible maximum speeds of designed curvature processors.        | 98 |

| Table 10 – Speed measurements of the processor realized on ml403 and ml505 |    |

| boards                                                                     | 98 |

# **LIST OF FIGURES**

## **FIGURES**

| <b>Figure 1</b> - Intensity image and range map of a real scene [13] are shown in (a)        |     |

|----------------------------------------------------------------------------------------------|-----|

| and (b), respectively.                                                                       | 5   |

| Figure 2 - A peak is shown in the range map. The precision is enough in (a), but             | ıt  |

| in (b) 1bit fraction length causes artificial edges and corners. The real values are         | 9   |

| shown in (c) and (d).                                                                        | 7   |

| Figure 3 - Graphical visualization of a 3-D (2.5D) range map. The map has 4 2-               | -D  |

| layers                                                                                       | 8   |

| Figure 4 – Shifting in range data, in (b), causes damaging surface representation            | n.  |

| In a good range data, in (a), mean error in each rows or columns should be zero.             | .10 |

| <b>Figure 5</b> – Bilinear transformation example of an erroneous range map                  | 11  |

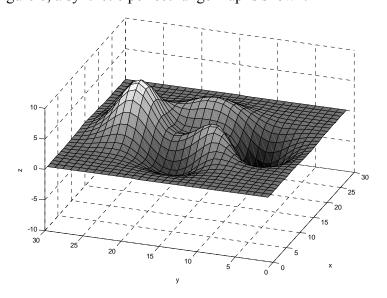

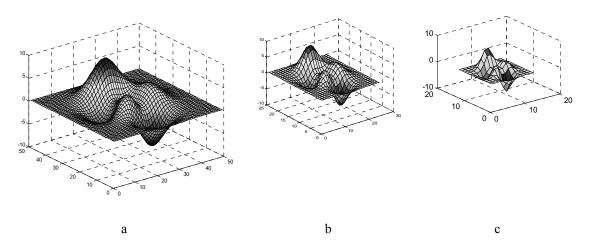

| Figure 6 – A synthetic equally sampled range map                                             | 11  |

| Figure 7 – Scale space representations of a synthetic range map. 0 <sup>th</sup> scale space | ,   |

| the source data, is in (a). $1^{st}$ scale is in (b) and $2^{nd}$ is in (c)                  | 12  |

| Figure 8 – A Curve and its tangent normal vectors.                                           | 14  |

| Figure 9 – Tangent vector, Normal Vector and tangent plane of a surface [22]                 | 17  |

| Figure 10 – Tangent vectors, tangent plane and normal vector of a parametric                 |     |

| surface [22]                                                                                 | 17  |

| <b>Figure 11</b> – Tangent vector of $\rho(t)$ and its angle with $r_u$ [23]                 | 20  |

| Figure 12 - Different curves on surface and principle curvature geodesics                    | 21  |

| <b>Figure 13</b> – Changing of Curvature with $\theta$ [23]                                  | 22  |

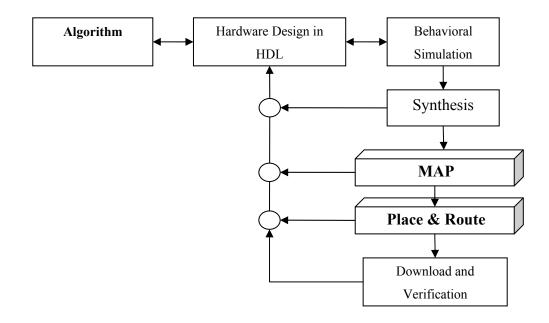

| <b>Figure 14</b> – FPGA design flow.                                                         | 32  |

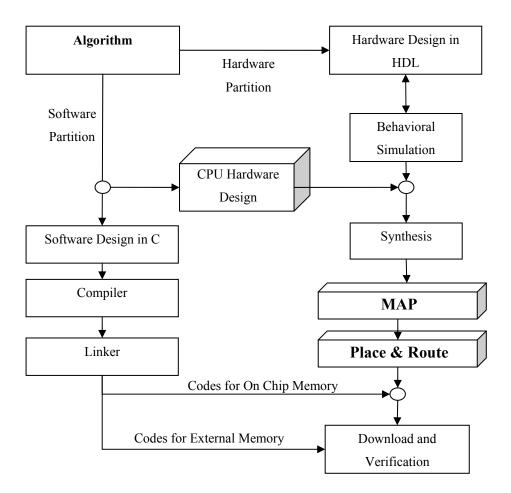

| Figure 15 – Hardware software partitioning and System on Chip design flow in                 | L   |

| FPGAs                                                                                        |     |

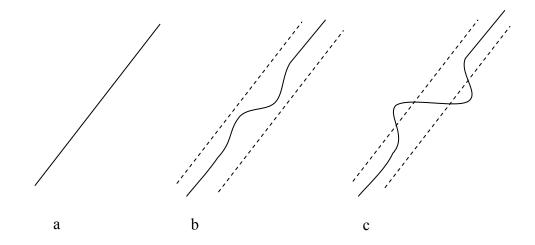

| Figure 16 – Bending thresholds in 2-D.                                                       | 38  |

| <b>Figure 17</b> – A closer look to a planar surface makes irregularities more visible.      | 39  |

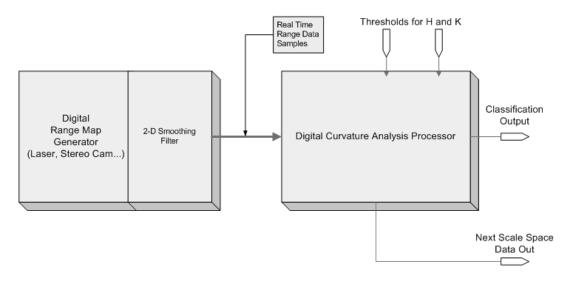

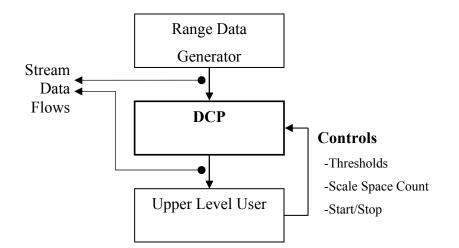

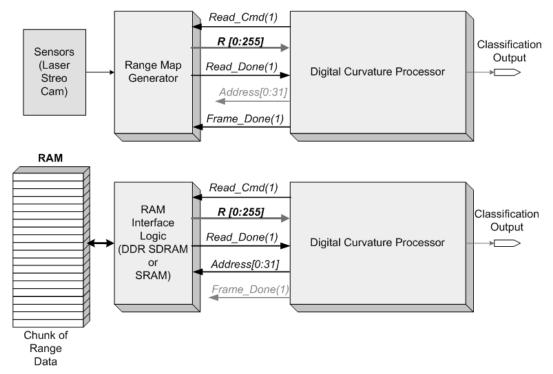

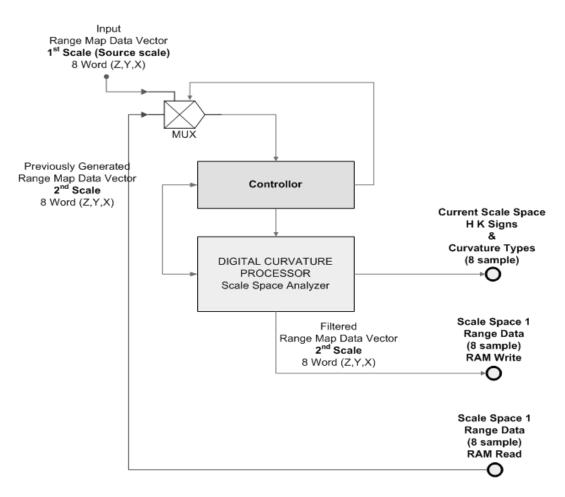

| <b>Figure 18</b> – DCP and Range Map Generator connectivity                                  | 40  |

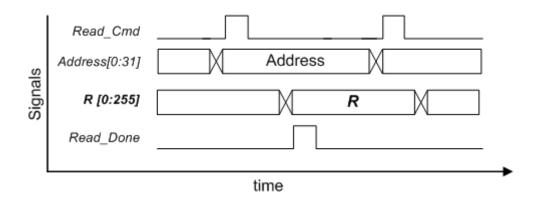

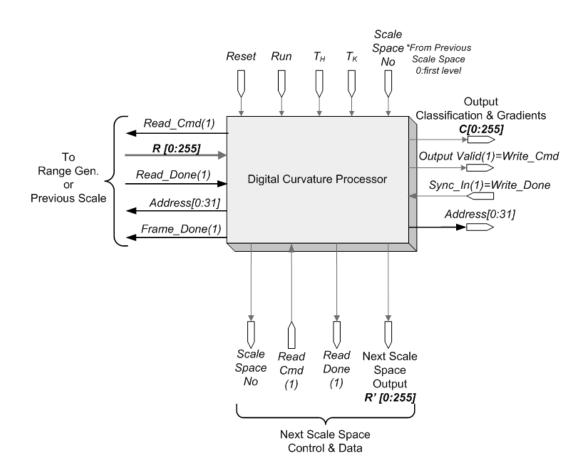

| Figure 19 – Configuration of DCP by upper level user.                                        | 43  |

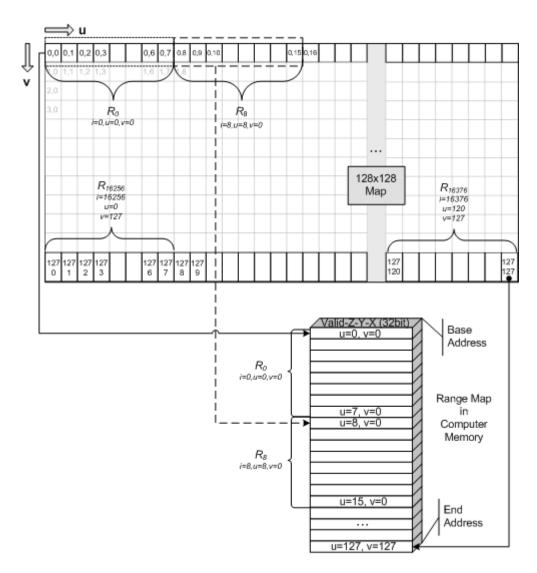

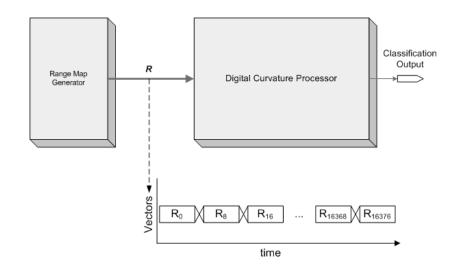

| <b>Figure 20</b> – 128x128 range map organization in a RAM                     | 46     |

|--------------------------------------------------------------------------------|--------|

| Figure 21 – Vector flow between Range map generator and DCP                    | 46     |

| <b>Figure 22</b> – DCP application with range map generator (top) or a RAM (bo | ottom) |

|                                                                                | 47     |

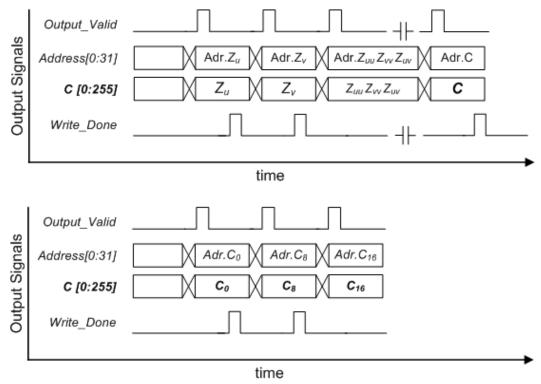

| Figure 23 – Timing diagram of interface signals                                | 47     |

| Figure 24 – Control signals for synchronization between DCP logics             | 48     |

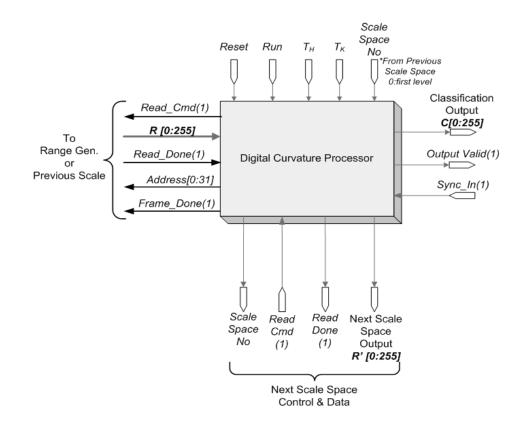

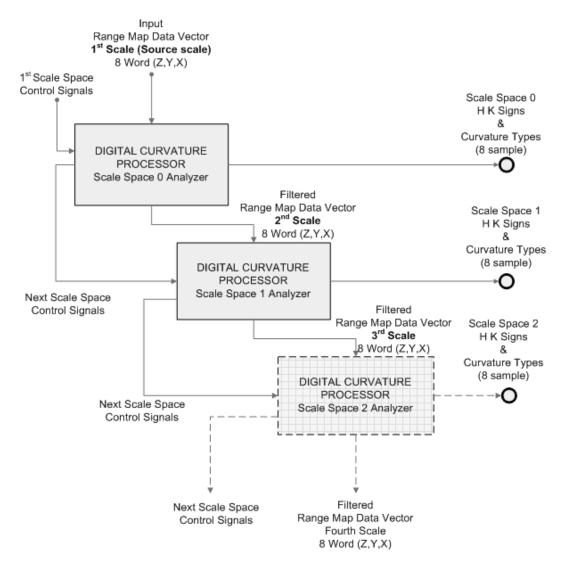

| Figure 25 – Pipeline usage of DCP for scale space analysis                     | 49     |

| Figure 26 – Single DCP usage for scale space analysis                          | 50     |

| Figure 27 – Gradient output and address decoder supported DCP and IO si        | gnals  |

|                                                                                | 51     |

| Figure 28 – Output signal flows of two different DCP, gradients available      | n top  |

| design.                                                                        | 52     |

| Figure 29 – Scale space kernel.                                                | 53     |

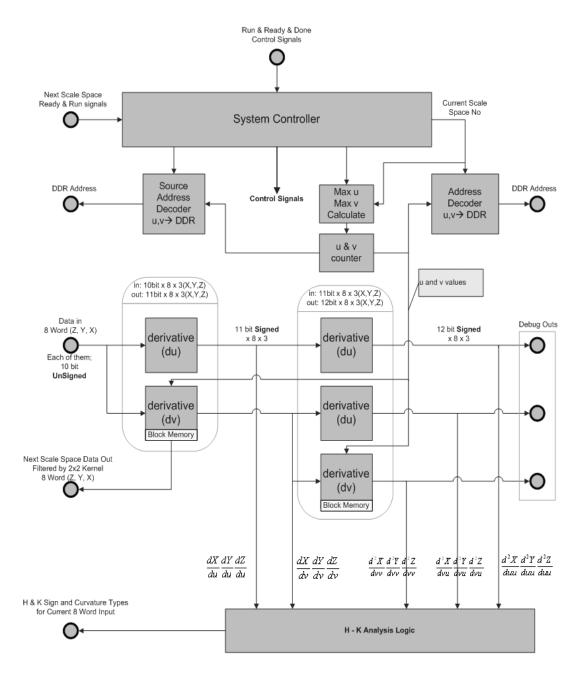

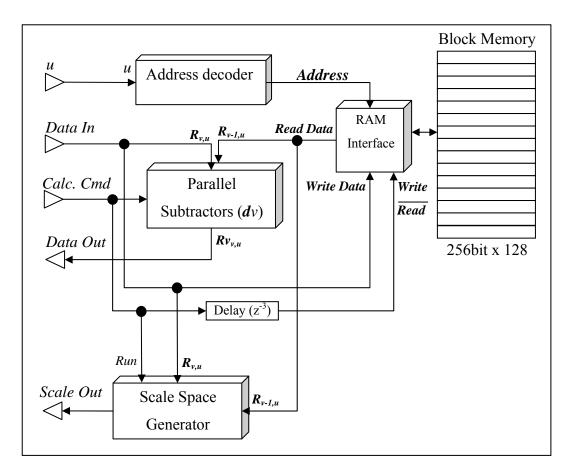

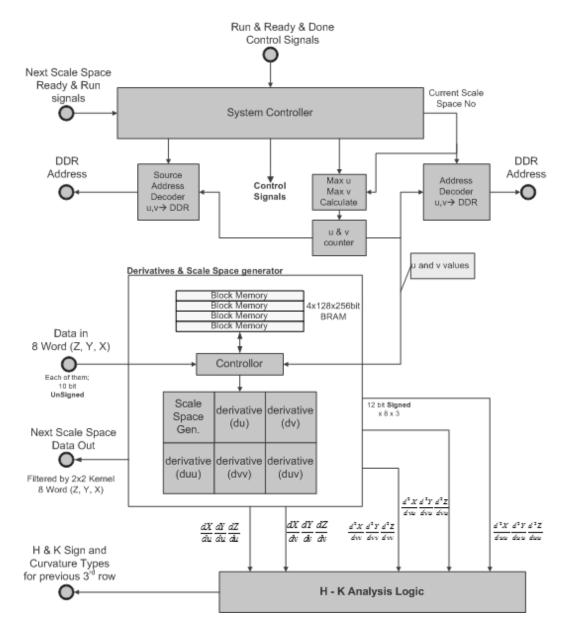

| <b>Figure 30</b> – Logic architecture of DCP type 1                            | 54     |

| Figure 31 – Input vectors used for derivatives                                 | 55     |

| <b>Figure 32</b> – Dv derivative and scale space block logic diagram           | 57     |

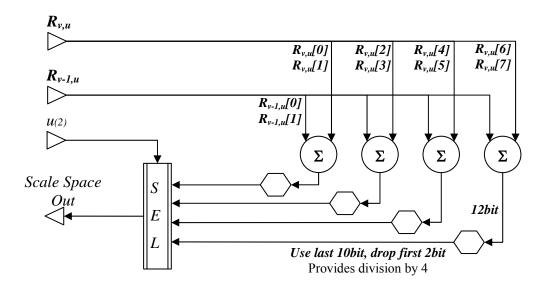

| Figure 33 – Scale Space generation logic                                       | 58     |

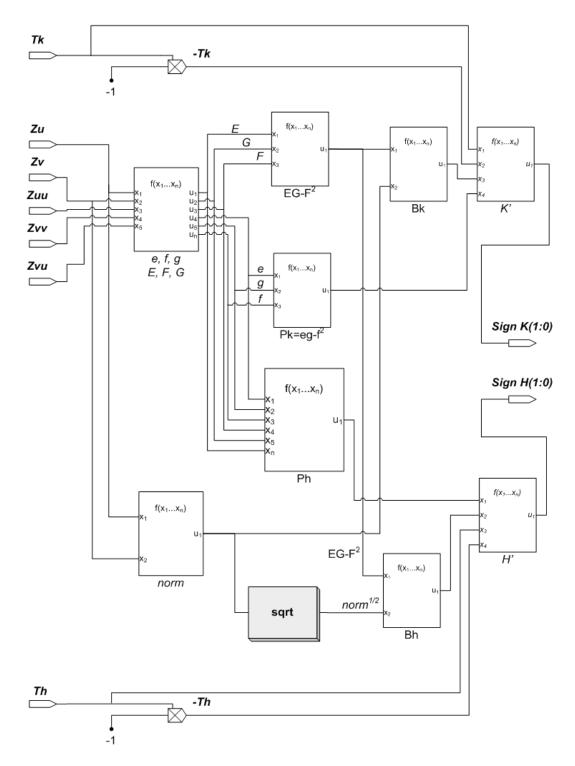

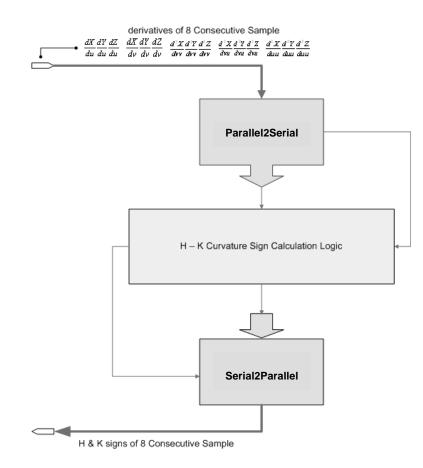

| Figure 34 – H and K sign extraction logic architecture.                        | 62     |

| Figure 35 – One instance usage example of HK Logic.                            | 63     |

| Figure 36 - Logic architecture of DCP type 2                                   | 64     |

| Figure 37 – Required samples to calculate derivatives in DCP2                  | 65     |

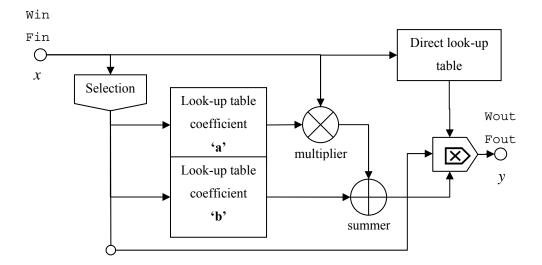

| Figure 38 – Purposed square root logic                                         | 69     |

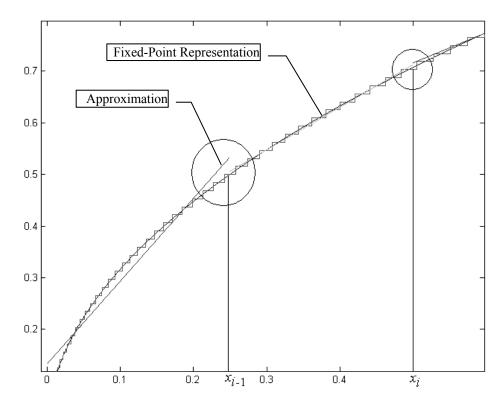

| Figure 39 – Square root line and its discontinuous approximation               | 70     |

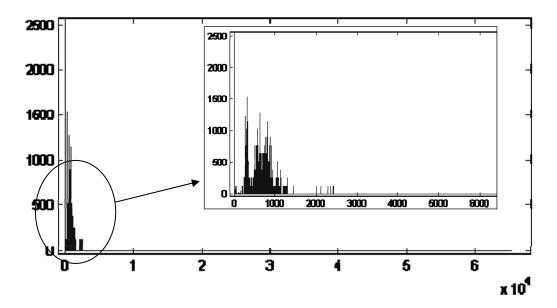

| <b>Figure 40</b> – Input distribution of square root function, Wl=22, Fl=6     | 71     |

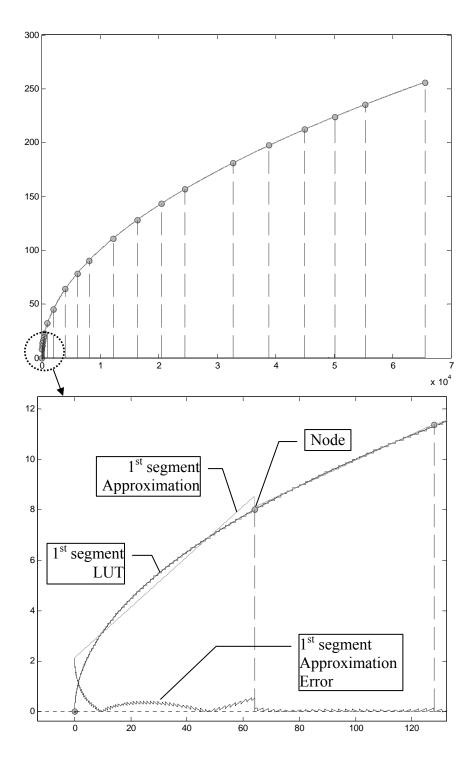

| <b>Figure 41</b> – Overall approximation and error in the first interval       | 73     |

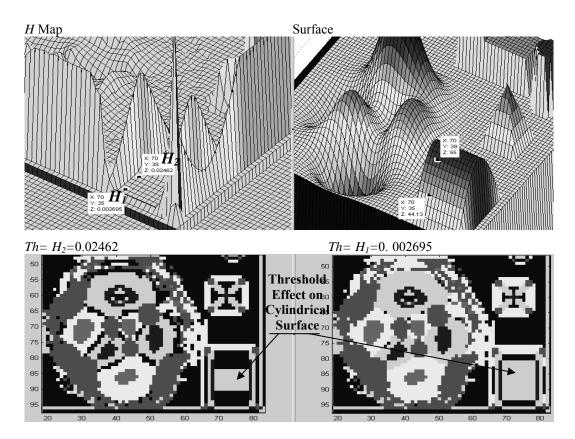

| Figure 42 – H and K values and threshold effect                                | 74     |

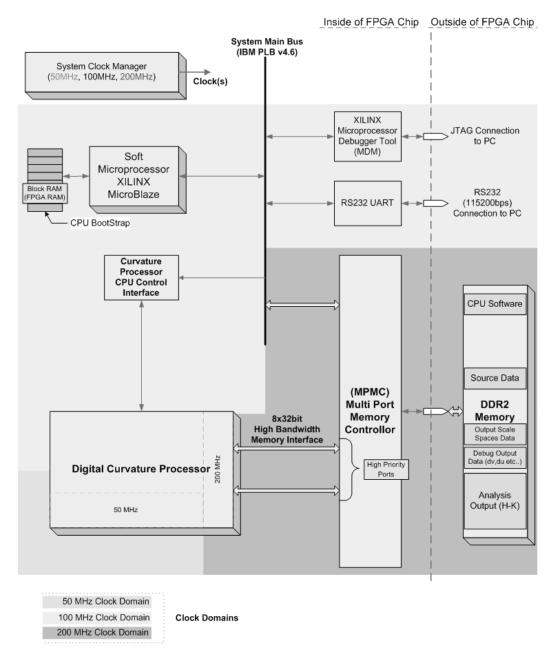

| Figure 43 – Top level FPGA design                                              | 77     |

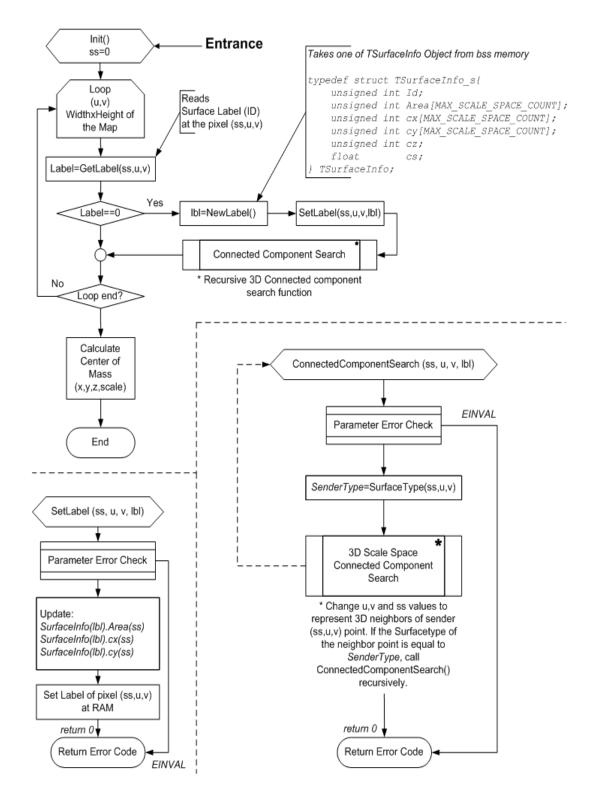

| Figure 44 – Connected component label assignment                               | 79     |

| Figure 45 – Connected component algorithm output                               | 79     |

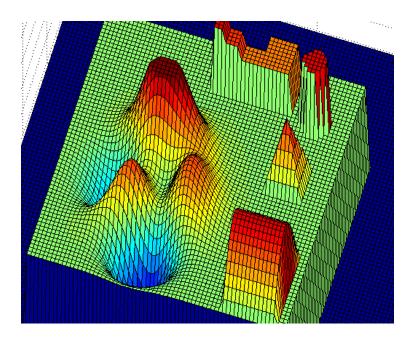

| Figure 46 – Artificial surfaces                                                | 84     |

| Figure 47 – Simulation and real hardware outputs of the artificial data        |        |

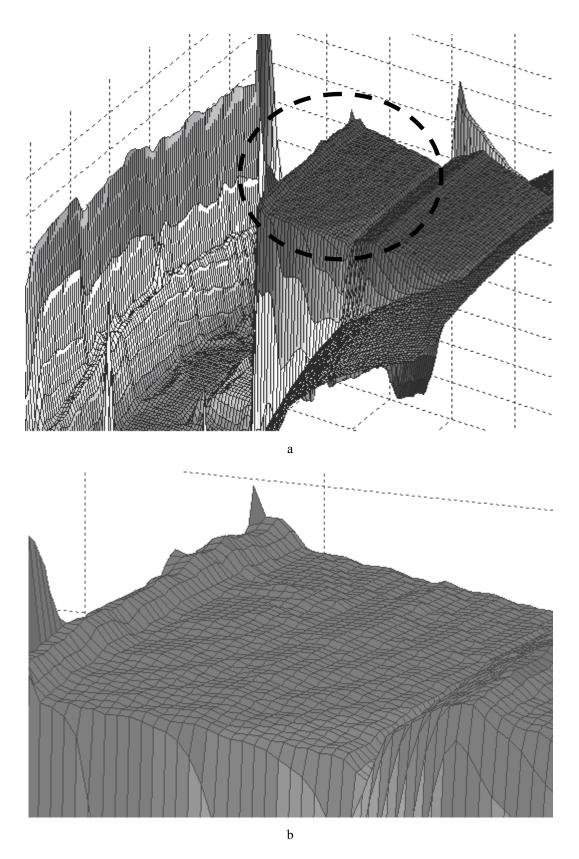

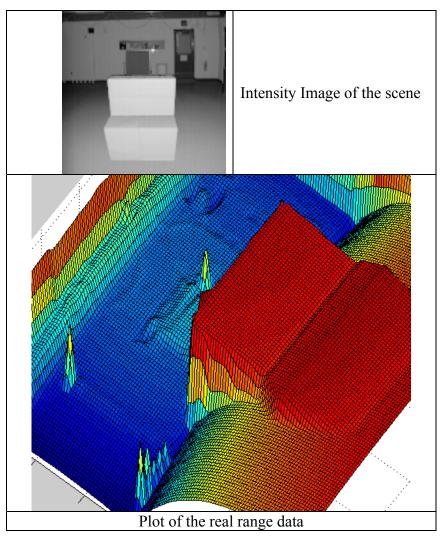

| Figure 48 – Range data of a scene and its 3D plot [13]                         | 85     |

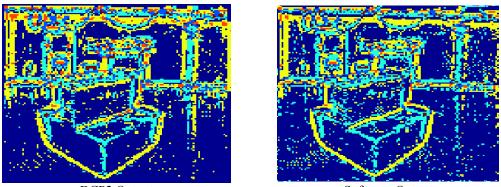

| Figure 49 – Hardware outputs of the range data in Figure 48                         | 86 |

|-------------------------------------------------------------------------------------|----|

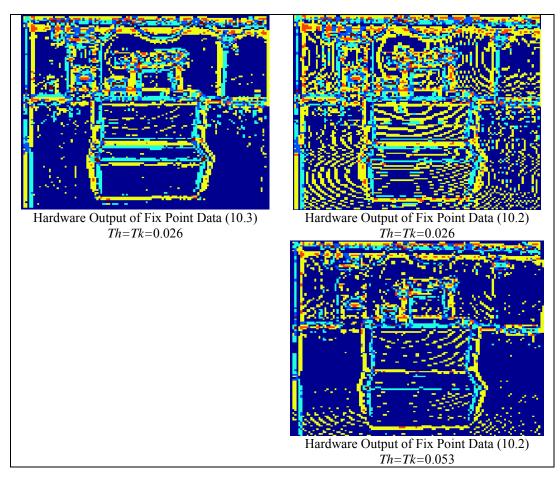

| Figure 50 – Software outputs of float64 and quantized fix-point range data          | 87 |

| Figure 51 – Quantization effect                                                     | 88 |

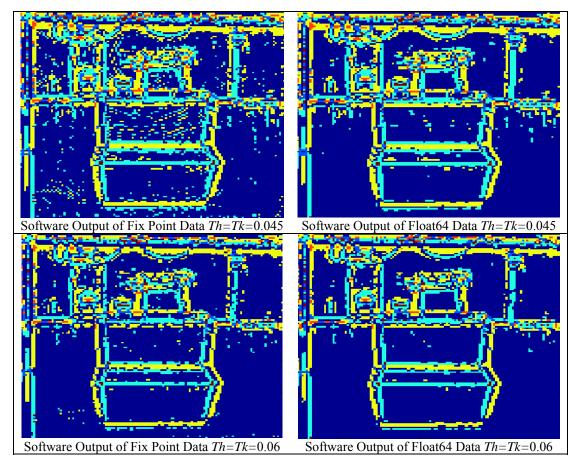

| Figure 52 – Software and hardware outputs                                           | 89 |

| Figure 53 – Outputs without rounding operation in DCP2                              | 91 |

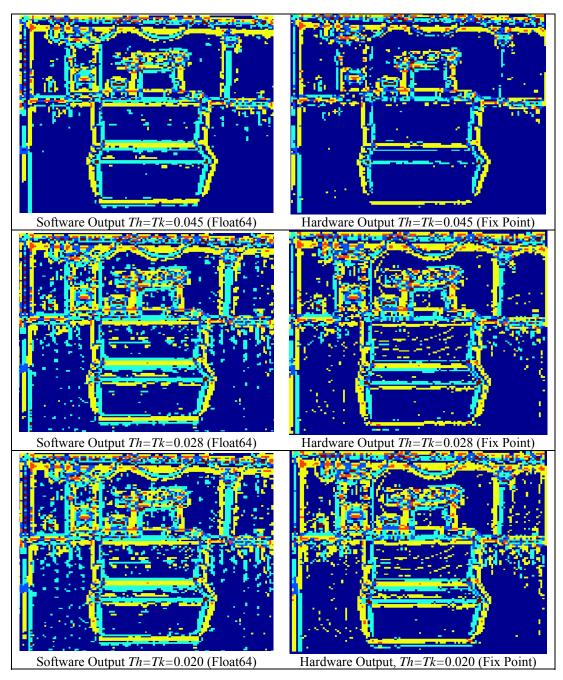

| Figure 54 - Intensity image of the rotated object [12]                              | 92 |

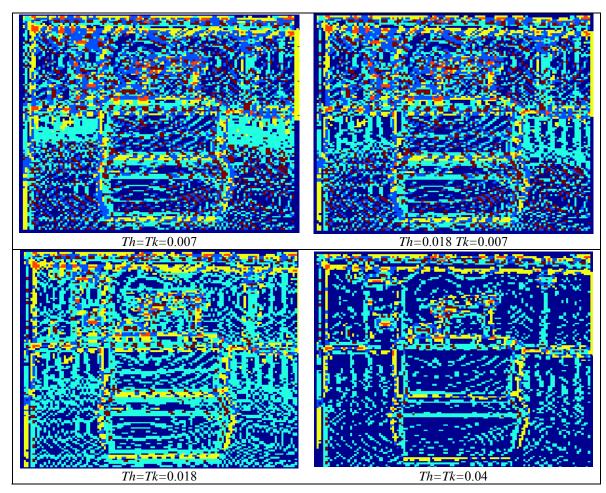

| Figure 55 – Outputs of the rotated object                                           | 92 |

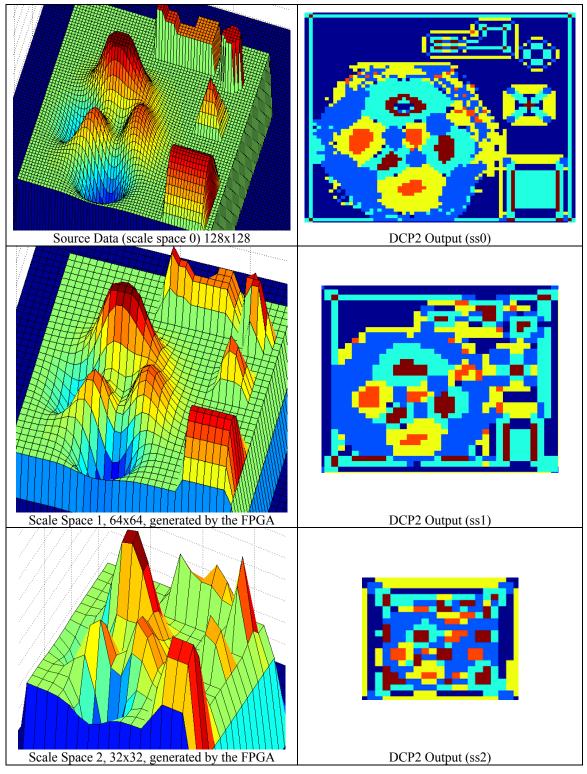

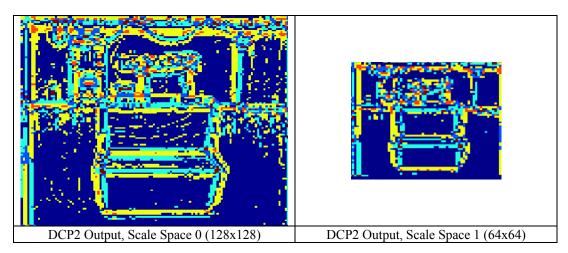

| Figure $56$ – Scale space levels and their analysis outputs for the artificial data | 93 |

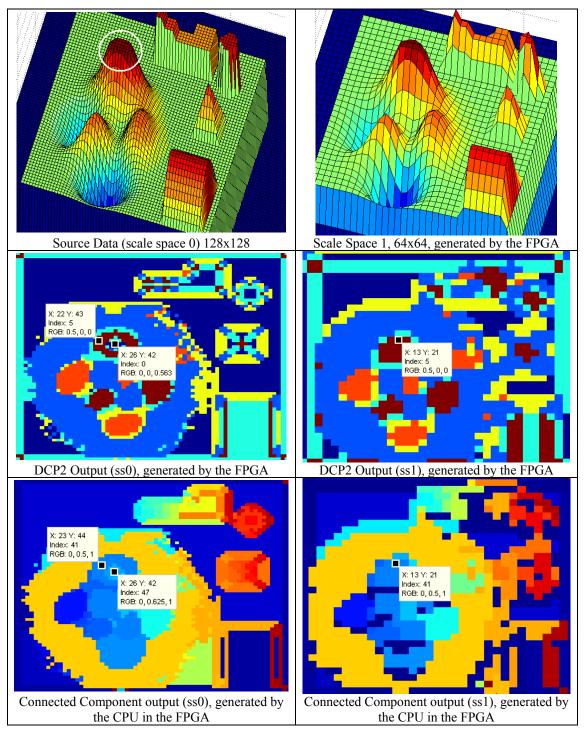

| Figure 57 – Scale space levels analysis outputs for the real data                   | 94 |

| Figure 58 – Connected component algorithm outputs.                                  | 95 |

## **CHAPTER 1**

# **INTRODUCTION**

### **1.1 Motivation**

Processing image texture and range maps to extract features has been very popular approach for the past years. Usually, the extracted features are used by different applications, such as object recognition. Feature extraction enables faster processing for computers to evaluate desired algorithms. Without feature extraction, to have a valid output, for example face recognition, it is required to make the same calculations in the whole image again and again. Therefore extracting the key points, which are meaningful properties for the algorithm, is a more preferred technique. In range map processing, one of the commonly used feature type is surface classification. Different approaches are proposed for classification of surfaces until now. Edge and corner detection algorithms have been very popular in recent years. Texture based surface analysis is performed in [1]. In [2], Photometric stereo with frequency domain analysis has been proposed to extract surface texture information especially considering surface-rotation invariance. These algorithms are texture based and also applicable to range data. Behind these algorithms, curvature based approaches are started to be used widely. Curvature analysis does not only provide edge and corner information, but also classifies any discrete point (or pixel) in the real range data into a variety of categories. This categorization makes curvature analysis more powerful in digital image and video processing. However, complexity and computational load is very high in curvature based surface classification algorithms.

Although feature extraction provides less computational cost for higher level algorithms, processing the range data or an image to extract features requires many computations. If both feature extraction and feature processing are implemented in software, the speed of whole algorithm can be worse than direct analyzing. Therefore software and hardware partitioning is used for system design. High computational task can be integrated into hardware while complex algorithms are implemented in software. Curvature extraction from range map using hardware will provide higher performance for surface classification based higher level algorithms.

### **1.2 Background and Literature**

There are two different types of curvature analysis methods widely used in literature. First one is Mean, abbreviated as H, and Gaussian, abbreviated as K, curvature classification. This method is known as HK segmentation [3] and proposed by Besl in 1986. In this method, principle curvatures are used to calculate H and K values in each point in image or range data. According to signs of these values one of 8 possible classifications is assigned to the point. The second method is shape index, S, and curvature magnitude, curvedness, C, based classification method, which is proposed by Koenderink [4]. Again, principle curvatures determine S and C values. Both techniques are examined and compared previously [5, 6]. In [5], Cantzler and Fisher conclude that SC segmentation method is slightly better to noise than HK segmentation is. However, when multiple scale spaces are used, HK segmentation is more successful [6].

Another important analysis tool in digital image and video processing world is scale space construction and running the desired algorithm in each scale level. This is a very useful approach to convert scale dependent algorithms to scale invariant. Many algorithms, like SIFT [7], use scale space technique. Scale space is also used in curvature analysis previously in [8, 6]. Classification types applied to all points in the surface may make it hard to extract actual surface type. In most cases, analyzing next scale space makes large areas, i.e. relevant features, more visible. This study has been performed in [6]. HK based surface classification is researched and implemented in software by different authors for different purposes. Processing of laser points, range map generated by laser range device, is performed in [9]. Object recognition purposed classification is researched in [10,11]. An interesting study is performed in medical science in [12], aiming finding of airway lesions. None of these works are time critical applications.

### **1.3 Thesis Objective and Outline**

Throughout this thesis, the main purpose is to develop a new hardware based real time digital curvature processor which is capable of classifying surface curvature by using HK segmentation technique in multiple scale space levels. Comparison of hardware based classification with the software ones is also aimed. The input of digital curvature processor, DCP, is real time serial 3D range map vectors. The algorithms use fixed point data format. We aim to use parallel processing and hardware acceleration. Two different design techniques are developed for DCPs. Both techniques are simulated in MatLab and implemented in two different XILINX FPGAs. The outputs of the two design approaches are compared with each other and both outputs are compared with the outputs of software based available techniques. Speed performance of the software and the developed hardware implementations are also compared.

The outline of the thesis is as follows; Chapter 2 includes a brief introduction to range maps, mathematical description of curves, surfaces, curvature, H and K. Also FPGA based design strategies and SoC design approach are explained in this chapter. In Chapter 3, digital curvature processing in hardware is developed. Derivative approximations, HK classifications and fast square root logic, considering input distribution and nonlinearity of square root line, are developed in this chapter. Chapter 4 includes embedded computer design and software. Detailed results and comparisons are given in Chapter 5. Chapter 6 is the conclusion part and presents possible future works.

# **CHAPTER 2**

## PRELIMINARIES

## 2.1 Range Map

2-D images can not express real surfaces very well, because they are intensity based and this limits expression of surface geometry. To overcome the problem, range maps are developed. Range maps include positions of all points with respect to a reference point. It can be thought as a real position image. A variety of range maps is available. A range map may include x, y and z values of points in the scene, or it might just contain z values. If only z values are available, range map is considered as a range image or z-buffering.

Range maps are also known as depth maps, depth images, range buffers and depth buffers.

#### 2.1.1 Range Map Generation

Range map generation requires special techniques and devices. Different techniques are available in literature. Laser scanners are one of the mostly used types of devices. Stereo camera based approaches are also very common.

Human vision takes depth information by exploiting stereo vision approach, we have two eyes and this provides depth and approximate range information of the scene. Based on this idea, range maps are calculated by using stereo camera.

Laser scanner scans the scene using a laser beam and measures the distance. Laser distance measurement is very sensitive and may produce noisy maps. Therefore a post processing, smoothing filter, is required.

Range image construction has been researched in many universities. University of South Florida Computer Vision and Pattern Recognition Group generated real range images using laser scanners and structured light method [13]. Ohio State University Signal Analysis and Machine Perception Laboratory group have many laser based range images. They also keep some other universities' range image data base [14]. Stanford University Computer Science department has real and synthetic range images [15]. Synthetic data is useful for testing the algorithms. Also, Stuttgart University synthetic range image database is very useful [16].

Besides software, range map construction has been implemented in hardware. Harlan Hile and Colin Zheng have generated range map by using stereo video processing in FPGAs [17]. Their data 512x480 pixels and representation is 5bit. Another work is performed by Ahmad Darabiha, Jonathan Rose and James MacLean [18]. This work produces 256x360 maps with 8bit resolution in FPGAs. The speed is 30 frames sec.

### 2.1.2 Range Map Precision & Data Formats

A range map is shown in Figure 1 below. The representation format of data is important especially for higher level algorithms. Data format defines precision of distance measurements, x, y and z. A high precision defines surface more accurately. On the other hand, high precision range map data requires more space since more bits used.

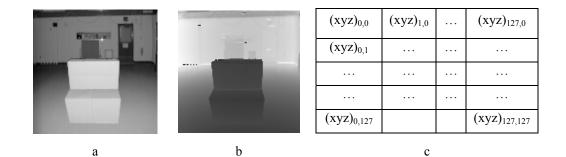

**Figure 1** - Intensity image and range map of a real scene [13] are shown in (a) and (b), respectively. In (c) the map values are represented in matrix format. In each cell, x, y and z values are stored with desired representation format. The image and map are  $128 \times 128$  pixel size.

In software based applications, 32bit floating point representation is usually used. Today's computer architectures are mostly 32bit and hard floating point unit is available in many processors. Using 32bit range map data is preferred in both representation precision and computer architecture aspects. Others formats may also be used.

In hardware processing, floating point approach is not so preferred. Fixed point numbers are more useful, because multiplication, summation and subtraction operations are easier. However, more bits can be required to provide enough precision in fixed point data representation. Therefore, while range map is being generated, resolution of measurements should already be determined. According to the resolution, fixed point word and fraction lengths should also be selected accordingly.

#### 2.1.3 Quantization Effect on Range Map

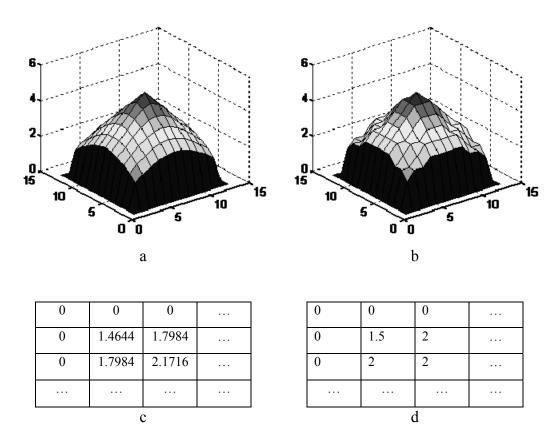

If fixed point fraction length is not enough to represent a scene, an excessive quantization error occurs. The quantization error in the range map may cause artificial edges, peaks or corners on the surface. An example is shown in Figure 2 below. In the figure, the range map includes a peak. Using enough precision, the peak is shown in (a). However, using the 1bit fraction length precision, the peak has some distortions as shown in (b). The real values are shown in (c) and (d). Obviously, 1bit precision is not enough for this range map.

Quantization of a surface data directly affects the quality of curvature analysis. As shown in Figure 2 (b), the corners of the peak are distorted. Curvature analysis of the corners on this data can not give actual description of the surface, the peak in the map. Most of the time, higher level algorithms put a smoothing filter to deal with surface roughness. If the roughness is due to quantization, the filtering can not solve the problem unless precision is increased at least in filtering stage. Therefore a valid range map must have enough precision to represent surface and scene in desired resolution.

**Figure 2** - A peak is shown in the range map. The precision is enough in (a), but in (b) 1bit fraction length causes artificial edges and corners. The real values are shown in (c) and (d).

### 2.1.4 Valid and Invalid Points of Range Maps

Range generating algorithms may not distinguish all points in the scene. In this case, the range map algorithm must sign these points. Usually another data in the range map is provided with x, y and z. The data is called by valid flags. This flag map explains which points in the range map are valid and invalid. Unfortunately, this technique increases the size of the map, even though 1bit is used for the flag. For a 128x128 map, extra 2K bytes are required. The problem is important especially for small embedded computers since they may not have enough memory. Another disadvantage of invalid points in curvature analysis may appear in surface classification. An invalid point causes misclassification of its neighbor points, even they are valid.

### 2.1.5 3D Range Map

As already mentioned, a range map does not only include depth, z, information. x and y values are also important to represent surface accurately. In differential geometry, a surface is represented by:

$$z = f(x, y)$$

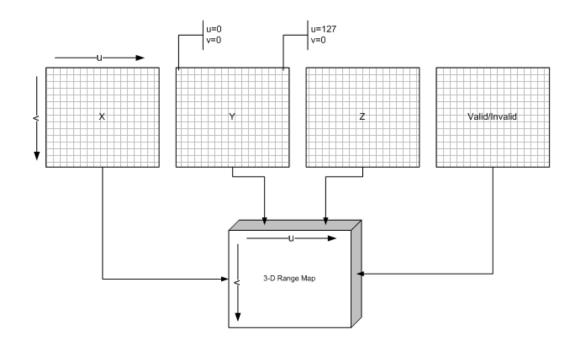

Figure 3 - Graphical visualization of a 3-D (2.5D) range map. The map has 4 2-D layers.

Therefore z is a function of x and y. Indeed, what a perfect range map is the function *f*. Another parameter of range map is its pixels. Conventionally u and v are used for range map pixel notation. In 2-D representation, i.e. matrix form, u refers to columns and v refers to rows of the range map. A complete range map contains 4 2-D maps. The fourth is valid/invalid map. In some resources, these types of range maps are called by 2.5D maps. Indeed, the map does not have all point information in 3D, it has only x, y and z values of a point of view. In this work, we prefer to use "3D map" term. A graphical representation is shown in Figure 3. Using new u and v variables, we may define the surface equation as;

$$x = X(u, v)$$

$$y = Y(u, v)$$

$$z = Z(u, v) = f(x, y) = f(X_{(u,v)}, Y_{(u,v)})$$

By these definitions, we can extract curvature structure of the range map. For a suitable range map, x and y values are monotone increasing with u and v values, respectively. A perfect range map has a relation between x and u, y and v values.

$$X(u, v) = u * \Delta_X$$

$$Y(u, v) = v * \Delta_Y$$

$\Delta_x$  and  $\Delta_y$  values are desired horizontal and vertical resolutions of the range map. The precision of data type used in range map must cover these values. Most of the time, range maps, unfortunately, can not hold these relations exactly. Especially in hardware, providing a perfect range map is very difficult. Therefore we express the relations with using an error term;

$$X(u,v) = (u * \Delta_X) \pm \varepsilon_X$$

$$Y(u,v) = (v * \Delta_Y) \pm \varepsilon_Y$$

In this case, the fix point resolution must be enough to express  $\varepsilon_x$  and  $\varepsilon_y$ . These error terms depend on range map generation hardware, and they should be in a defined range. We may define the error ranges in worst case,

$$0 < \varepsilon_{\chi} < \Delta_{\chi}$$

$$0 < \varepsilon_{\chi} < \Delta_{\chi}$$

Of course the range can be narrower, or zero, and range map generation algorithms should keep the errors in the ranges. If the errors excess defined ranges in a pixel, it is a definitely invalid point for upper level algorithm, curvature analysis in this case.

Also we may define instantaneous sampling errors as,

$$\begin{split} & \Delta_{X(u,v)} = X_{(u,v)} - X_{(u-1,v)} \\ & \Delta_{Y(u,v)} = Y_{(u,v)} - Y_{(u,v-1)} \\ & e_{x(u,v)} = \Delta_X - [X_{(u,v)} - X_{(u-1,v)}] \leq \varepsilon_{X(u,v)} \\ & e_{Y(u,v)} = \Delta_Y - [Y_{(u,v)} - Y_{(u,v-1)}] \leq \varepsilon_{Y(u,v)} \end{split}$$

According to these definitions we may calculate mean sampling error in a single row;

$$\overline{e_{X(v)}} = \frac{1}{N} \sum_{u=1:N} [\Delta_X - (X_{(u,v)} - X_{(u-1,v)})] \cong 0 \quad v = [0..N-1]$$

(Eq. 2.1)

N: width of the map

Here we define that the mean error for a single row must be zero. If this equation is not satisfied for a row, then we conclude that the row is shifted and the map is not valid. However, inverse of the assumption does not imply that the map is valid. Also, if the mean errors are equal for all rows, the assumption fails again because in that case the map has a phase shift and it does not affect the analysis. The assumption is also applicable to columns of range map.

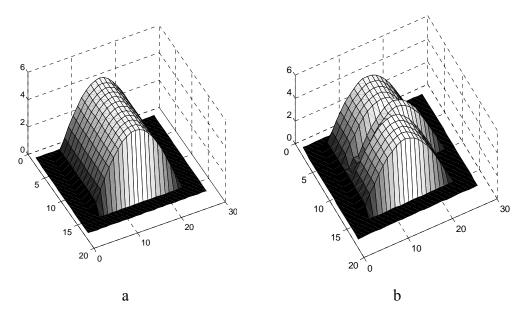

**Figure 4** – Shifting in range data, in (b), causes damaging surface representation. In a good range data, in (a), mean error in each rows or columns should be zero.

A synthetic example is given in Figure 4. A cylindrical surface is shown in (a). One of the rows is shifted in x-direction and mean error for that row is greater than zero in (b). If all rows were shifted in the same amount, the cylindrical surface would be still valid.

An erroneous range map may be transformed into a zero erroneous map, i.e.  $\varepsilon_x = \varepsilon_y = 0$ . Basically, this is an interpolation process, bilinear or bicubic. In Figure 5, a noisy map and its zero error transform are shown. At top, some measurement errors in X and Y effect the Z values. The transform hinders measurement error in Z. Desired sampling distances are  $\Delta_x = \Delta_y = 1$ .

| 1                   | 2.2 | 3.1 |

|---------------------|-----|-----|

| 0.8                 | 2.1 | 3.2 |

| 1                   | 1.8 | 2.9 |

| X Map (Measurement) |     |     |

2

2

2

3

3

3

|                     | 1.3 | 1.1 | 0.8 |

|---------------------|-----|-----|-----|

|                     | 2.2 | 1.8 | 2.1 |

|                     | 3.1 | 3   | 3.2 |

| Y Map (Measurement) |     |     |     |

| 0.8                 | 0.91 | 0.79 |  |

|---------------------|------|------|--|

| 0.88                | 1.1  | 0.94 |  |

| 0.8                 | 0.89 | 0.79 |  |

| Z Map (Measurement) |      |      |  |

|   |   |   | . – |  |

|---|---|---|-----|--|

| 1 | 1 | 1 |     |  |

| 2 | 2 | 2 |     |  |

3

3

|       |       | 0.823 |

|-------|-------|-------|

| 0.895 | 1.058 | 0.958 |

| 0.811 | 0.878 |       |

Z Map (bilinear)

X Map (Expected)

1

1

1

Figure 5 – Bilinear transformation example of an erroneous range map

Y Map (Expected)

3

In Figure 6, a synthetic perfect range map is shown.

Figure 6 – A synthetic equally sampled range map.

## 2.2 Scale Space

Scale space provides scale invariant analysis for image processing. The concept has been analyzed by Tony Lindeberg [19]. Scale space is widely used in feature extraction, as well. In the same scene, there can be different size of features or a feature may contain many small features. Scale space technique is very helpful when the small features hide large features.

In curvature analysis, surface classification suffers from too detailed outputs. In a real range map data, surfaces are usually very rough, therefore outputs contain many different features, i.e. different classifications, on the same surface. Also, we may want to see only large surfaces and we may discard the small areas. Scale spaces of range maps provide these benefits in curvature analysis.

Scale space technique in curvature analysis is already used by many authors [6, 8].

In this work, we generate scale spaces by using Gaussian pyramids method, width and height of the map reduced by half in each scale using a 2-D Gaussian kernel. A scale space example of synthetic data is given in Figure 7. As going to next scale, details of surfaces disappear and only peaks stay visible.

**Figure 7** – Scale space representations of a synthetic range map.  $0^{th}$  scale space, the source data, is in (a).  $1^{st}$  scale is in (b) and  $2^{nd}$  is in (c).

## 2.3 HK Segmentation

Mean and Gaussian curvature based range map segmentation is basically a differential geometry operation. In this chapter, a mathematical description of HK analysis will be provided. The content can be found in an elementary differential geometry book.

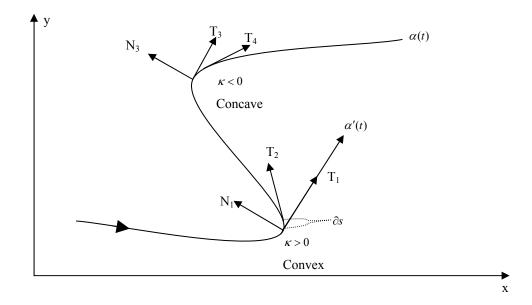

### 2.3.1 Curves, Tangent and Normal Vectors

A differentiable curve in 3-D,  $\alpha$ , is expressed by

$$I = [a,b] \ a,b \in R$$

$$\alpha : I \to R^{3}$$

$$\alpha(t) = (x(t), y(t), z(t)) \ t \in I$$

The function above is called by plane curve in 3-D. If third component, z, is always zero, the curve is in 2-D and its representation;

$$I = [a,b] \ a,b \in R$$

$$\alpha : I \to R^{2}$$

$$\alpha(t) = (x(t), y(t)) \ t \in I$$

Differentiable condition implies *x*, *y* and *z* functions to be differentiable. Therefore derivative of vector function  $\alpha$ ;

$$\alpha'(t) = (x'(t), y'(t))$$

The tangent vector is also given by the formula above. Tangent vector contains direction of the curve at t instant. The unit tangent vector or direction vector, T, is calculated by;

$$T(t) = \frac{\alpha'(t)}{|\alpha'(t)|}$$

Figure 8 – A Curve and its tangent normal vectors.

Derivative of unit tangent vector is orthogonal to itself and it gives direction of normal vector. Unit normal vector, *N*, is expressed by;

$$T(t) \bullet T(t) = 1$$

$$\frac{\partial (T(t) \bullet T(t))}{\partial t} = 0$$

$$T'(t) \bullet T(t) + T(t) \bullet T'(t) = 0$$

$$2 \cdot T(t) \bullet T'(t) = 0 \Rightarrow T(t) \perp T'(t)$$

$$N(t) = \frac{T'(t)}{|T'(t)|}$$

(Eq. 2.2)

The unit tangent and unit normal vectors are shown in Figure 8 for different *t* instants. The orthonormal vectors *N* and *T* construct a basis set for 2-D space.

### 2.3.2 Curvature

Curvature,  $\kappa$ , is a measurement of how much the curve is bended. Intuitively, it is a quantity of direction change while moving along the curve. For a straight line, direction, unit tangent vector, does not change while moving on the line. Therefore, a normal vector has zero length and the curvature is also zero. Referring to Figure 8, the infinite small length of the curve, arch length, is represented by  $\partial s$ . We already define direction change by taking derivative of tangent vector. According to the definition, curvature;

$$\kappa = \left| \frac{\partial T}{\partial s} \right| = \left| \frac{\partial T}{\partial t} \cdot \frac{\partial t}{\partial s} \right|$$

The unit arch length is derivative of the vector function;

$$\left|\partial s\right| = \left|\alpha'(t)\right| \cdot \left|\partial t\right|$$

The curvature;

$$\frac{\partial T}{\partial t} \cdot \frac{\partial t}{\partial s} = \frac{\frac{\partial T}{\partial t}}{\frac{\partial s}{\partial t}} = \frac{1}{|\alpha'(t)|} \frac{\partial T}{\partial t} = \kappa N$$

Any regular parameterized curve can be re-parameterized by arch length [20]. Therefore arch length, *s*, is a parameterization parameter. The curvature for arch-length parameterized curves can be expressed by;

$$\kappa(s) = \frac{T'(s)}{N(s)}$$

Therefore, if T is the twisting counterclockwise, curvature is greater than zero,  $\kappa > 0$  and the curve is convex. If T is twisting clockwise, curvature is negative and curve is concave [21]. In Figure 8, near t=1 point, the curve is convex and around t=3, it is concave.

#### **2.3.3 Surface Representation**

We may write a surface, *S*, in terms of its three components *x*, *y* and *z*;

$$S \subset R^{3}$$

$$S = \{x, y, z\} \quad z = Z(x, y)$$

The range map, R, is a parametric representation of the components x, y, z.

$$x = X(u, v)$$

$$y = Y(u, v)$$

Considering our range map definitions;

$$X(u,v) = u * \Delta_X$$

$$Y(u,v) = v * \Delta_Y$$

There is a unique linear mapping between X and u values. Therefore we may use the following notation to represent surface S,

$$U \subset I^2 \quad I : \text{integer numbers}$$

$$r: U \to S$$

$$r(U) = S$$

$$r(u,v) = (X_{(u,v)}, Y_{(u,v)}, Z(X_{(u,v)}, Y_{(u,v)})) \quad u, v \in U$$

$$r(u,v) = (u * \Delta_X, v * \Delta_Y, Z_{(u,v)}) \quad u, v \in U$$

In differential geometry, a defined one-to-one mapping between x and u components represented by;

$$z = f(x, y) = Z(u, v) = Z(x, y)$$

$$r(u, v) = (u, v, Z_{(u,v)})$$

(Eq. 2.3)

This convention is known as graph surface representation and the surface is called Monge patch. The range map provides representation of surfaces with two variables, u and v, according to the assumptions. There exists a similarity between our range map and graph surface. In 3D range map, x and y values are depends on u and v values.

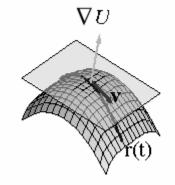

### **2.3.4** Surface Tangent Plane and Normal Vector

As in the curves, the surfaces also have normal vector for a given point. Directional derivatives, gradient, gives the normal vector of the surface at any point. For the surface U, unit normal vector [22], N, is;

$$\nabla U = \left(\frac{\partial U(x, y, x)}{\partial x}, \frac{\partial U(x, y, x)}{\partial y}, \frac{\partial U(x, y, x)}{\partial z}\right)$$

$$N = \frac{\nabla U}{\left|\nabla U\right|}$$

(Eq. 2.4)

The gradient, i.e. unit normal vector, is orthogonal to tangent vector of all level curves of the surface at any point on the surface. On a continuous surface in 3-D, there are infinitely many curves passing through a point on the surface. These curves are known as *geodesic* in differential geometry. In Figure 9 below, one of the curves, r(t) = (x(t), y(t), z(t)), gradient vector,  $\nabla U$ , and the tangent vector of the curve,  $\mathbf{v}$ , is shown.

Figure 9 – Tangent vector, Normal Vector and tangent plane of a surface [22]

The tangent vector of any curves on the surface is orthogonal to normal vector of the surface;

$$\nabla U \bullet v = 0$$

A plane can be expressed by its normal and a point on it. The normal vector is known and taking a point on the surface, we may express tangent plane of the surface at that point. Tangent plane of the surface U is also shown in Figure 9.

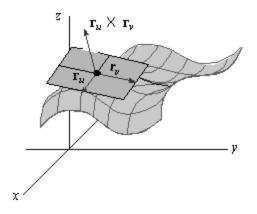

For parametric surfaces, another possible normal vector calculation is cross product of tangent vectors along principle directions of parameterizations. A parameterized surface r(u,v) has tangent vectors along u and v directions.

Figure 10 – Tangent vectors, tangent plane and normal vector of a parametric surface [22]

A parameterized surface r is given by

$$r(u,v) = (x(u,v), y(u,v), z(u,v))$$

(Eq. 2.5)

The tangent vectors along u and v directions;

$$r_{u} = \left(\frac{\partial x}{\partial u}, \frac{\partial y}{\partial u}, \frac{\partial z}{\partial u}\right)$$

$$r_{v} = \left(\frac{\partial x}{\partial v}, \frac{\partial y}{\partial v}, \frac{\partial z}{\partial v}\right)$$

The unit surface normal vector can be expressed by;

$$N = \frac{r_u \times r_v}{|r_u \times r_v|}$$

(Eq. 2.6)

$r_u$  and  $r_u$  vectors construct a basis set for tangent plane of the surface. The normal vector, tangent plane and basis vectors are shown in Figure 10. The tangent vectors are orthogonal to both each other and normal vector.

#### 2.3.5 Surface Curvature

Curvature is already defined in previous sections as direction change while moving on a curve within unit step. To achieve curvature of surface at a point, we should consider lines on the surface, i.e. geodesics. There are many different approaches in literature to define curvature of a surface. Shape operator, i.e. Weingarten Map, is commonly used in many resources. Here, mathematical approach is preferred and all content is based on works of Kevin Shirley and Jeff Knisley in [23]. More details can be found in this source.

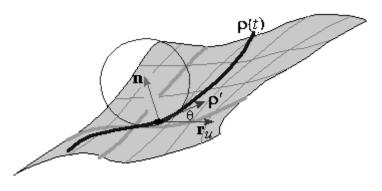

The curvature of a curve is calculated using unit arch length function of the curve. Remember  $\frac{\partial s}{\partial t}$  is a parameter for curvature. Assume r(u,v) is a surface and  $\rho(t)$  is a geodesic on it. The arch length [23]

$$\left|\frac{\partial s}{\partial t}\right| = \left(\left\langle \rho', \rho'\right\rangle\right)^{1/2}$$

$$\rho' = r_u \cdot \frac{\partial u}{\partial t} + r_v \cdot \frac{\partial v}{\partial t}$$

$$\rho' \bullet \rho' = r_u \bullet r_u \left(\frac{\partial u}{\partial t}\right)^2 + 2 \cdot r_u \bullet r_v \cdot \frac{\partial u}{\partial t} \bullet \frac{\partial v}{\partial t} + r_v \bullet r_v \cdot \left(\frac{\partial v}{\partial t}\right)^2$$

Defining coefficients;

$$g_{11} = r_u \bullet r_u \quad g_{12} = r_u \bullet r_v \quad g_{22} = r_v \bullet r_v$$

Arch length;

$$\left(\frac{\partial s}{\partial t}\right)^2 = g_{11} \left(\frac{\partial u}{\partial t}\right)^2 + 2g_{12} \left(\frac{\partial u}{\partial t}\right) \left(\frac{\partial v}{\partial t}\right) + g_{22} \left(\frac{\partial v}{\partial t}\right)^2$$

Remember that  $\rho'(t)$  is tangent vector of the curve and its normalized version gives direction vector T. Considering  $\rho'' = \kappa N$ ; *normal curvature*  $\kappa_n$  in the direction of **n** given by

$$\kappa_n = \boldsymbol{\rho}^{\prime\prime} \cdot \mathbf{n}$$

(Eq. 2.7)

$$\mathbf{n} = \mathbf{r}_u \times \mathbf{r}_v$$

**ρ**'';

$$\rho'' = \frac{\partial r_u}{\partial t} \frac{\partial u}{\partial t} + r_u \frac{\partial^2 u}{\partial t^2} + \frac{\partial r_v}{\partial t} \frac{\partial v}{\partial t} + r_v \frac{\partial^2 v}{\partial t^2}$$

$$\rho'' = \left(\frac{\partial r_u}{\partial u} \frac{\partial u}{\partial t} + \frac{\partial r_u}{\partial v} \frac{\partial v}{\partial t}\right) \frac{\partial u}{\partial t} + r_u \frac{\partial^2 u}{\partial t^2} + \left(\frac{\partial r_v}{\partial u} \frac{\partial u}{\partial t} + \frac{\partial r_v}{\partial v} \frac{\partial v}{\partial t}\right) \frac{\partial v}{\partial t} + r_v \frac{\partial^2 v}{\partial t^2}$$

$$\rho'' = r_{uu} \left(\frac{\partial u}{\partial t}\right)^2 + r_{uv} \frac{\partial v}{\partial t} \frac{\partial u}{\partial t} + r_u \frac{\partial^2 u}{\partial t^2} + r_{vu} \frac{\partial u}{\partial t} \frac{\partial v}{\partial t} + r_v \frac{\partial^2 v}{\partial t^2}$$

$$\rho'' = r_{uu} \left(\frac{\partial u}{\partial t}\right)^2 + 2r_{uv} \frac{\partial v}{\partial t} \frac{\partial u}{\partial t} + r_u \frac{\partial^2 u}{\partial t^2} + r_v \left(\frac{\partial v}{\partial t}\right)^2 + r_v \frac{\partial^2 v}{\partial t^2}$$

Curvature along normal direction;

$$\kappa_{n} = \rho'' \bullet n = \frac{\partial r_{u}}{\partial u} \bullet n \frac{\partial u}{\partial t} \frac{\partial u}{\partial t} + r_{u} \bullet n \frac{\partial^{2} u}{\partial t^{2}} + \frac{\partial r_{v}}{\partial v} \bullet n \frac{\partial v}{\partial t} \frac{\partial v}{\partial t} + r_{v} \bullet n \frac{\partial^{2} v}{\partial t^{2}}$$

$$\kappa_{n} = r_{uu} \bullet n \left(\frac{\partial u}{\partial t}\right)^{2} + 2r_{uv} \bullet n \frac{\partial v}{\partial t} \frac{\partial u}{\partial t} + r_{u} \bullet n \frac{\partial^{2} u}{\partial t^{2}} + r_{vv} \bullet n \left(\frac{\partial v}{\partial t}\right)^{2} + r_{v} \bullet n \frac{\partial^{2} v}{\partial t^{2}}$$

$\mathbf{r}_u$  and  $\mathbf{r}_v$  are orthogonal to  $\mathbf{n}$ ;

$$\kappa_{n} = \rho'' \bullet n = r_{uu} \bullet n \left(\frac{\partial u}{\partial t}\right)^{2} + r_{vv} \bullet n \left(\frac{\partial v}{\partial t}\right)^{2} + r_{v} \bullet n \frac{\partial^{2} v}{\partial t^{2}}$$

$$\kappa_{n} = r_{uu} \bullet n \left(\frac{\partial u}{\partial t}\right)^{2} + 2r_{uv} \bullet n \frac{\partial v}{\partial t} \frac{\partial u}{\partial t} + r_{vv} \bullet n \left(\frac{\partial v}{\partial t}\right)^{2}$$

Referring to Figure 11;  $du/dt = \cos(\theta) |\mathbf{r}_u|^{-1}$  and  $dv/dt = \sin(\theta) |\mathbf{r}_v|^{-1}$ . Here,  $\theta$  is the angle between  $\mathbf{r}_u$  and tangent vector,  $\boldsymbol{\rho}'$ .

$$\rho' = \cos(\theta) \frac{r_u}{|r_u|} + \sin(\theta) \frac{r_v}{|r_v|}$$

**Figure 11** – Tangent vector of  $\rho(t)$  and its angle with  $r_u$  [23]

After substituting, the curvature along surface normal;

$$\kappa_n(\theta) = \frac{r_{uu} \bullet n}{|r_u|^2} \cos^2(\theta) + \frac{r_{uv} \bullet n}{|r_u||r_v|} \sin(2\theta) + \frac{r_{vv} \bullet n}{|r_v|^2} \sin^2(\theta)$$

(Eq. 2.8)

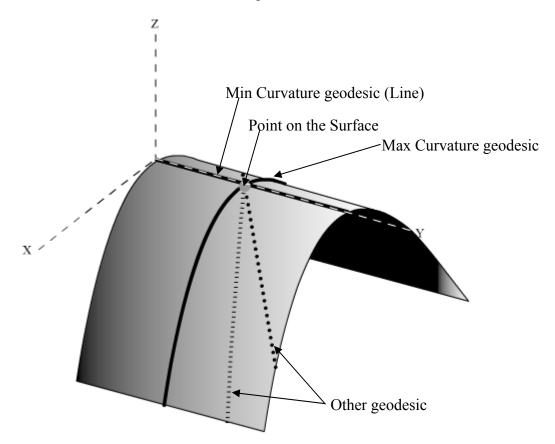

Obviously, curvature of a surface depends on the angle  $\theta$ . This angle is between tangent vector of a geodesic and  $\hat{\mathbf{u}}$  direction. In other words, angle of the curve to  $\hat{\mathbf{u}}$  direction. For a continuous surface, there are infinitely many curves, geodesics, and the curvature changes continuously while  $\theta$  is changing.

Meaning of changing  $\theta$  is selecting another curve on the surface. Actually different curves cause different  $\theta$  but thinking as changing the angle causes different curve selection is also meaningful approach to understand relationships

between the angle and the curvature. As we select different curve, i.e. different angle, we will have different curvature. In Figure 12 below, different selections of curves on the surface and their normal planes are shown. As mentioned, all of the curves have different curvature at the point on the surface.

Figure 12 - Different curves on surface and principle curvature geodesics.

### 2.3.6 Principle Curvatures

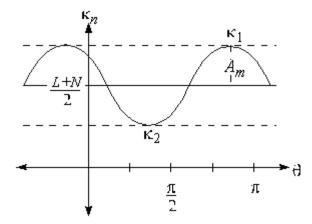

Selecting different geodesic causes different curvatures. The angle is changing between  $[0 \sim \pi]$ . Observe that, curvature is periodic with  $[0 \sim \pi]$ . Let revise the formula [23];

$$\kappa_{n}(\theta) = \frac{r_{uu} \bullet n}{|r_{u}|^{2}} \cos^{2}(\theta) + \frac{r_{uv} \bullet n}{|r_{u}||r_{v}|} \sin(2\theta) + \frac{r_{vv} \bullet n}{|r_{v}|^{2}} \sin^{2}(\theta)$$

$$L = \frac{r_{uu} \bullet n}{|r_{u}|^{2}} \qquad M = \frac{r_{uv} \bullet n}{|r_{u}||r_{v}|} \qquad N = \frac{r_{vv} \bullet n}{|r_{v}|^{2}}$$

$$\kappa_{n}(\theta) = \frac{L - N}{2} \cos(2\theta) + M \sin(2\theta) + \frac{L + N}{2}$$

$$A_{m} = \sqrt{\left(\frac{L - N}{2}\right)^{2} + M^{2}}$$

$$\overline{\kappa}_{n} = \frac{L + N}{2}$$

The curvature function is a sinusoidal wave with a phase shift. Its dc (mean) and ac components are  $\overline{\kappa}_n$  and  $A_m$ , respectively.

If we plot the curvature values in the range;

**Figure 13** – Changing of Curvature with  $\theta$  [23]

The peak values of the wave;

$$\kappa_{peak} = \overline{\kappa}_n \pm A_m$$

$$\kappa_1 = \overline{\kappa}_n + A_m \qquad \kappa_2 = \overline{\kappa}_n - A_n$$

Two peaks of the wave,  $\kappa_1$  and  $\kappa_2$ , are known as *principle curvature* of the surface and, they are considered as an intrinsic property of surfaces in differential geometry. Indeed, if we consider Figure 12 again, it is shown that the one of the curve has maximum curvature, it is along x direction, and one of them is just a straight line, i.e. 0 curvature, it is along y direction. These two values provide an important clue about shape of the surfaces.

#### 2.3.7 Mean and Gaussian Curvature Based Surface Classification

Johann Carl Friedrich Gauss (1777-1855) has proposed Gaussian curvature, K, to have information about a point on the surface just existence of knowledge  $\kappa_1$  and  $\kappa_2$ . The Gaussian curvature;

$$K = \kappa_1 \cdot \kappa_2 \tag{Eq. 2.9}$$

Gauss classified the points on the surface as flat, elliptical and hyperbolic. If principle curvatures are zero, K=0, no change occurs near the point and obviously the plane shaped surface exists at the point. If both have the same sign, positive or negative, then K>0 and point is spherical. If K<0, i.e. different signed principle curvatures, the point is hyperbolic. The classifications are summarized in Table 1.

| Plane      | K~=0                                                       |  |

|------------|------------------------------------------------------------|--|

| Elliptical | K>0<br>Both principle<br>curvatures have the<br>same sign. |  |

| Hyperbolic | K<0<br>Principle curvatures<br>have opposite signs.        |  |

Table 1 – Gaussian classification of surfaces.

Behind Gauss Classification, mean of the principle curvatures, H, provides some information about point on the patch. If mean curvature is positive, the

tangent vector turns clockwise and concave shape occurs at that point. Otherwise convex curvature is present.

$$H = \frac{\kappa_1 + \kappa_2}{2} \tag{Eq. 2.10}$$

Using both H and K in surface classification is proposed by P.J. Besl [3]. This approach is better way for classification and it is widely used. For example, usage of only Gaussian curvature can not provide recognition of cylindrical surface as in Figure 12, because one of the curvatures, also K, is zero. Mean curvature together with Gaussian curvature provide more types for classification. The available types and their visualizations are shown in Table 2.

#### 2.3.8 Derivation of K and H

For a surface, defined by r(u, v), Gaussian curvature, *K*, value [23];

$$r(u, v) = (x_{(u,v)}, y_{(u,v)}, Z_{(u,v)})$$

$$\kappa_n(\theta) = \frac{r_{uu} \bullet n}{|r_u|^2} \cos^2(\theta) + \frac{r_{uv} \bullet n}{|r_u| |r_v|} \sin(2\theta) + \frac{r_{vv} \bullet n}{|r_v|^2} \sin^2(\theta)$$

$$L = \frac{r_{uu} \bullet n}{|r_u|^2} \quad M = \frac{r_{uv} \bullet n}{|r_u| |r_v|} \quad N = \frac{r_{vv} \bullet n}{|r_v|^2}$$

$$\kappa_n(\theta) = \frac{L - N}{2} \cos(2\theta) + M \sin(2\theta) + \frac{L + N}{2}$$

$$A_m = \sqrt{\left(\frac{L - N}{2}\right)^2 + M^2}$$

$$\overline{\kappa}_n = \frac{L + N}{2}$$

$$\kappa_1 = \overline{\kappa}_n + A_m \quad \kappa_2 = \overline{\kappa}_n - A_m$$

$$K = \kappa_1 \cdot \kappa_2$$

$$K = \left(\frac{L + N}{2}\right)^2 - \left(\frac{L + N}{2}\right)^2 - M^2$$

| Sign of <b>H</b> | Sign of <b>K</b> | Local (around the point)<br>Surface Shape | Visualization [24] |

|------------------|------------------|-------------------------------------------|--------------------|

| 0                | 0                | Plane                                     |                    |

| +                | 0                | Concave Cylindrical<br>(Valley)           |                    |

| -                | 0                | Convex Cylindrical<br>(Ridge)             |                    |

| +                | +                | Concave Elliptical<br>(Pit)               |                    |

| -                | +                | Convex Elliptical<br>(Peak)               |                    |

| 0                | -                | <b>Hyperbolic</b><br>(Minimal Surface)    |                    |

| -                | -                | <b>Hyperbolic</b><br>(Saddle Ridge)       |                    |

| +                | -                | <b>Hyperbolic</b><br>(Saddle Valley)      |                    |

Table 2 – Available classifications in HK segmentation.

$$K = LN - M$$

$$K = \frac{r_{uu} \bullet n}{|r_u|^2} \cdot \frac{r_{vv} \bullet n}{|r_v|^2} - \left(\frac{r_{uv} \bullet n}{|r_u||r_v|}\right)^2$$

$$K = \frac{(r_{uu} \bullet n)(r_{vv} \bullet n) - (r_{uv} \bullet n)^2}{|r_u|^2 |r_v|^2 - (r_u \bullet r_v)^2}$$

Unit Normal vector, *n*;

$$U(u, v, z) = z - Z(u, v)$$

$$\nabla U = (-Z_u, -Z_v, 1)$$

$$n = \frac{(-Z_u, -Z_v, 1)}{|(-Z_u, -Z_v, 1)|} = \frac{(-Z_u, -Z_v, 1)}{\sqrt{(Z_u^2 + Z_v^2 + 1)}}$$

The formulas above are extracted for any parametric surface. In our 3D range map definition, surface points are represented by;

$$r(u, v) = (X_{(u,v)}, Y_{(u,v)}, Z(X_{(u,v)}, Y_{(u,v)}))$$

$$x(u, v) = u \cdot \Delta x$$

$$y(u, v) = v \cdot \Delta y$$

$$r(u, v) = (u \cdot \Delta x, v \cdot \Delta y, Z_{(u,v)})$$

Note that, surfaces depth value, z, is actually a function of x and y. The parameterization by u and v defines the x, y and indirectly z values. For defined range map;

$$r_{u} = \frac{\partial r(u, v)}{\partial u} = \left(\frac{\partial X(u, v)}{\partial u}, \frac{\partial Y(u, v)}{\partial u}, \frac{\partial Z(x, y)}{\partial u}\right)$$

$$r_{v} = \frac{\partial r(u, v)}{\partial v} = \left(\frac{\partial X(u, v)}{\partial v}, \frac{\partial Y(u, v)}{\partial v}, \frac{\partial Z(x, y)}{\partial v}\right)$$

$$\frac{\partial X(u, v)}{\partial u} = \Delta x \quad \frac{\partial X(u, v)}{\partial v} = \Delta y$$

$$Z_{u} = \frac{\partial Z(x, y)}{\partial u} = \left(\frac{\partial Z(x, y)}{\partial x} \cdot \frac{\partial x}{\partial u}\right) + \left(\frac{\partial Z(x, y)}{\partial y} \cdot \frac{\partial y}{\partial u}\right) = Z_{x}\Delta x$$

$$Z_{v} = \frac{\partial Z(x, y)}{\partial v} = \left(\frac{\partial Z(x, y)}{\partial x} \cdot \frac{\partial x}{\partial v}\right) + \left(\frac{\partial Z(x, y)}{\partial y} \cdot \frac{\partial y}{\partial v}\right) = Z_{y}\Delta y$$

$$r_{u} = (\Delta x, 0, Z_{x}\Delta x) \qquad r_{v} = (0, \Delta y, Z_{y}\Delta y)$$

Second derivatives;

$$r_{uu} = \frac{\partial r_u}{\partial x} \cdot \frac{\partial x}{\partial u} + \frac{\partial r_u}{\partial y} \cdot \frac{\partial y}{\partial u} = (0, 0, Z_{xx} \Delta x^2) \quad r_{vv} = (0, 0, Z_{yy} \Delta y^2) \quad r_{uv} = (0, 0, Z_{xy} \Delta y \Delta x)$$

Unit normal vector,  $\boldsymbol{n}$ , in our parameterization is  $\mathbf{r}_{u} \times \mathbf{r}_{v}$ ;

$$r_{u} = (\Delta x, 0, Z_{x}\Delta x) \qquad r_{v} = (0, \Delta y, Z_{y}\Delta y)$$

$$r_{u} \times r_{v} = \begin{bmatrix} \hat{x} & \hat{y} & \hat{z} & \hat{x} & \hat{y} \\ \Delta x & 0 & Z_{x}\Delta x & \Delta x & 0 \\ 0 & \Delta y & Z_{y}\Delta y & 0 & \Delta y \end{bmatrix} = (-Z_{x}\Delta x\Delta y, -Z_{y}\Delta x\Delta y, \Delta x\Delta y)$$

$$n = \frac{r_{u} \times r_{v}}{|r_{u} \times r_{v}|} = \frac{(-Z_{x}\Delta x\Delta y, -Z_{y}\Delta x\Delta y, \Delta x\Delta y)}{\sqrt{Z_{x}^{2}\Delta x^{2}\Delta y^{2} + Z_{y}^{2}\Delta x^{2}\Delta y^{2} + \Delta x^{2}\Delta y^{2}}} = \frac{\Delta x\Delta y \cdot (-Z_{x}, -Z_{y}, 1)}{|\Delta x\Delta y|\sqrt{Z_{x}^{2} + Z_{y}^{2} + 1}}$$

$$= S \frac{(-Z_{x}, -Z_{y}, 1)}{\sqrt{Z_{x}^{2} + Z_{y}^{2} + 1}} , S = sign(\Delta x\Delta y) = \pm 1$$

Then *K*;

$$K = \frac{(r_{uu} \bullet n)(r_{vv} \bullet n) - (r_{uv} \bullet n)^{2}}{|r_{u}|^{2} |r_{v}|^{2} - (r_{u} \bullet r_{v})^{2}}$$

$$r_{uu} \bullet n = (0,0, Z_{xx} \Delta x^{2}) \bullet \left(S \frac{(-Z_{x}, -Z_{y}, 1)}{\sqrt{Z_{x}^{2} + Z_{y}^{2} + 1}}\right) = S \frac{Z_{xx} \Delta x^{2}}{\sqrt{Z_{x}^{2} + Z_{y}^{2} + 1}}$$

$$r_{vv} \bullet n = S \frac{Z_{yy} \Delta y^{2}}{\sqrt{Z_{x}^{2} + Z_{y}^{2} + 1}} \qquad r_{vu} \bullet n = S \frac{Z_{xy} \Delta x \Delta y}{\sqrt{Z_{x}^{2} + Z_{y}^{2} + 1}}$$

$$(r_{uu} \bullet n)(r_{vv} \bullet n) - (r_{uv} \bullet n)^{2} = S^{2} \frac{Z_{xx} \Delta x^{2} \cdot Z_{yy} \Delta y^{2} - Z_{xy}^{2} \Delta x^{2} \Delta y^{2}}{|Z_{x}^{2} + Z_{y}^{2} + 1|}$$

$$S^{2} = 1$$

$$(r_{uu} \bullet n)(r_{vv} \bullet n) - (r_{uv} \bullet n)^{2} = \Delta x^{2} \Delta y^{2} \frac{Z_{xx} Z_{yy} - Z_{xy}^{2}}{|Z_{x}^{2} + Z_{y}^{2} + 1|}$$

$$\begin{aligned} \left| r_{u} \right|^{2} &= (\Delta x^{2} + Z_{x}^{2} \Delta x^{2}) \qquad \left| r_{v} \right|^{2} = (\Delta y^{2} + Z_{y}^{2} \Delta y^{2}) \\ &(r_{u} \bullet r_{v})^{2} = Z_{x}^{2} \Delta x^{2} Z_{y}^{2} \Delta y^{2} \\ \left| r_{u} \right|^{2} \left| r_{v} \right|^{2} - (r_{u} \bullet r_{v})^{2} &= (\Delta x^{2} + Z_{x}^{2} \Delta x^{2})(\Delta y^{2} + Z_{y}^{2} \Delta y^{2}) - Z_{x}^{2} \Delta x^{2} Z_{y}^{2} \Delta y^{2} \\ &= \Delta x^{2} \Delta y^{2} (Z_{x}^{2} + Z_{y}^{2} + 1) \end{aligned}$$

$$\begin{aligned} K &= \frac{(r_{uu} \bullet n)(r_{vv} \bullet n) - (r_{uv} \bullet n)^{2}}{\left| r_{u} \right|^{2} \left| r_{v} \right|^{2} - (r_{u} \bullet r_{v})^{2}} = \frac{\Delta x^{2} \Delta y^{2} \frac{Z_{xx} Z_{yy} - Z_{xy}^{2}}{\left| Z_{x}^{2} + Z_{y}^{2} + 1 \right|} \\ \Delta x^{2} \Delta y^{2} (Z_{x}^{2} + Z_{y}^{2} + 1) \end{aligned}$$

$$\begin{aligned} K &= \frac{Z_{xx} Z_{yy} - Z_{xy}^{2}}{(Z_{x}^{2} + Z_{y}^{2} + 1)^{2}} \end{aligned}$$

Similarly *H*;

$$H = \frac{(1 + Z_x^{2})Z_{yy} - 2Z_xZ_yZ_{xy} + (1 + Z_y^{2})Z_{xx}}{2 \cdot (Z_x^{2} + Z_y^{2} + 1)^{3/2}}$$

These two formulas can be revisited by defining common variables;

$$norm = (Z_x^2 + Z_y^2 + 1)$$

$$E = 1 + Z_x^2 \qquad e = Z_{xx}$$

$$F = Z_x Z_y \qquad f = Z_{xy}$$

$$G = 1 + Z_y^2 \qquad g = Z_{yy}$$

$$K = \frac{e \cdot g - f^2}{norm \cdot (E \cdot G - F^2)}$$

$$H = \frac{2 \cdot f \cdot F - e \cdot G - g \cdot E}{2 \cdot (E \cdot G - F^2) \sqrt{norm}} \qquad (Eq. 2.11)$$

These notations will be very useful for implementation process.

# 2.4 Real Time Concept

Digital signal processing has been very popular for past years. The DSP algorithms are designed by mathematical tools in computers and usually implemented using software in computers again. Most of the case, output validity

is already known and it is the first verification test for both design and implementation time. This approach is meaningful because beginning of the project, the output accuracy is the most wanted requirement. If the implementation provides somehow necessary speed in software or in hardware, the design seems to meet all criteria. Indeed, algorithm designers usually do not consider implementation platform while designing. However, most of the time, especially in software implementations, the platform is very important, because computer architectures may differ from platforms to platforms. Speeds of RAMs, CPU frequency, main bus architecture, cache size etc... are very significant quantities for speed requirements. Also, in multi threaded environments, operating system and other running processes affect performance of algorithms. Therefore, before starting to implement an algorithm, it is very essential to know the speed requirements. If a real time running prerequisite exists, the algorithm implementation is changed according to the target requirements, both output validity and speed.

Basically, there is no exact definition of real time concept. The condition is given by the target algorithm. For example, a person tracker system in a garden may process at the rate of 1 frame/sec. On the other hand, for a vehicle tracker, this is very slow rate, since the vehicles move much faster than people. Therefore real time criteria and the expected outputs of system should be decided together at the beginning of the project.

The next step of real time design, after the requirements are decided, is algorithm development according to target platform. During design time, if the speed requirement is discarded and only providing a valid output is considered, it is very hard to achieve real time processing at the end of system realization. In this case, changing the target platform according to developed algorithm is usually used. Unfortunately, this approach does not work always. Finding very fast processors or hardware may be impossible or it can be very expensive. Therefore the best way of a system design is deciding both output and timing criteria altogether and then starting to development considering both criteria together.

#### 2.4.1 Hardware & Software Partitioning

According to requirements, hardware/software partitioning should be determined. Software and hardware partitioning is a very meaningful approach for complex system design. Cost of developing all algorithms in software can be too much, or it can be impossible. One processor makes one computation at a time. The increasing of clock frequency may not enough to deal with timing requirement. Increasing processor count also increases both money and power costs. Also, parallel programming in software is not an easy approach. On the other hand, using only hardware to realize an algorithm would be a very heuristic try. Digital design is much harder than software and it is not useful way for algorithm developing. The algorithm should be already confirmed and it must be developed according to hardware facts. An untested algorithm can not be successful in hardware. Another hardware design struggle is required design time. Hardware designs take much more time than software designs.

The first key point of partitioning is parallelism. Trying to implement a sequential algorithm in hardware, even using pipelined architecture, may not be useful when considering design time and output accuracy. For these types of algorithms CPUs are more useful. Before starting hardware design, the parallel running stages should be constructed and these stages should be designed according to hardware facts. Another key point is recursive callings. A pure recursive algorithm should not be implemented in hardware. The recursive algorithms are fit to software; they are not so suitable for hardware design. If the hardware stages of the algorithm contain a recursive case, the stages should be revised and the algorithm should be changed. Thirdly, control of algorithms and systems should be kept in software code is easy, so using state machines in hardware for algorithm control is not a good approach.

The partitioning approach has been researched and many algorithms have been implemented in this way by many researchers. An example of fixed point coprocessor for floating point conversion has been performed in [25], and the researches continue in this science.

#### 2.4.2 Real Time Criteria in HK Analysis

In feature extraction, time requirements depend on what purpose the features are used for. For an elementary object recognition, 100 msec processing time for a single frame is sufficient. Humans can not recognize object in 100 msec, therefore it is enough to have a valid output in curvature analysis for object recognition in this aspect. Of course, for different purposes, 100 msec. may not be adequate. In this thesis, we use 100msec/frame limit for real time curvature analysis. According to timing condition and speed measurements of software based curvature feature extraction, it is very useful to develop a hardware curvature processor. As already mentioned, real range maps are generated in hardware [17, 18]. The next step is processing the maps in hardware and providing features to software to decrease the processing load.

#### 2.4.3 Real Time Hardware Platforms

Hardware design can be implemented in many platforms, such as ASICs, CPLDs, FPGAs etc... Today, the most preferred hardware design realization platform for testing purpose is reconfigurable FPGAs. Reconfigurable FPGAs are not one time programmable lgogic devices and their logics are designed by higher level hardware description languages, HDL. Also the designs can be converted to other platforms, supporting HDL. ASICs are application specific and they are not a programmable device. They are a custom logic device, but faster than FPGAs. Also ASIC design requires much more time than FPGA design. Therefore we prefer to use reconfigurable FPGAs to realize the hardware algorithms. The used HDL is VHDL.

### 2.5 FPGA Basics

Field programmable gate arrays, FPGAs, consist of configurable logic blocks (CLB), clock managers (PLL, DCM), on chip memory (BRAM), hard multipliers, summers and a matrix formed interconnection grids. Also modern FPGAs have hard Ethernet MAC, PCI-E and hard processors etc... CLBs are configured according to desired application and logic elements of the design are constructed. These logics are connected via programmable interconnection lines. Therefore a high flexibility is achieved on a single device. Also FPGAs have dedicated memories and FIFO elements. Merely all logic designs require small memories or FIFOs. These elements are connected to designed logics (CLB) again via interconnection lines. Also, for signal processing application, FPGAs have hard DSP chips, providing fast multiply and accumulate logics. Moreover, the next generation FPGAs have hard processors. The processors and logic circuits in a single chip open System on Chip, SOC, era in electronics science. With these advantages, FPGAs are starting to be a very powerful hardware implementation platform.

Figure 14 – FPGA design flow.

A typical FPGA design flow is shown in Figure 14. The algorithm is developed by mathematical tools, simulated in higher level software, MatLab for example. The algorithms should be in, of course, hardware sense. Then the HDL is prepared. Using schematic, Verilog or VHDL is possible. The next step is behavioral simulation. In this step, the outputs of behavioral simulation of the HDL code should be match with outputs of the algorithm. Otherwise the revising is required. When the behavioral simulation is finished, hardware realization can be started. The first stage is synthesis. In this stage, the HDL code is converted into logic components, gates flip-flops etc... Sometimes HDL may contain nonsynthesizable codes or synthezing may not be possible for the codes. In this case HDL is revised again. If synthesis is finished successfully, the logic design can be transferred to the target FPGA. For this purpose, a mapping is started; elements of the logic circuit are mapped to target FPGA's elements. Unfortunately, if the design has too much elements for target FPGA, mapping fails. The design must be revised to have lower logic elements or the FPGA must be changed with a higher density chip. The last realization step is place and route. Here, the mapped logic elements are placed according to the required frequency of design and then they are routed, connected. The CLBs are static in the chip, therefore putting which logic circuits into which CLB to achieve desired frequency as the result of connections requires a brilliant algorithm and it takes time. Sometimes, designed circuits can not reach the required clock frequency and place and routing fail for target FPGA. Again, the failed connection has to be revised and the timing problem must be solved. After hardware realization is completed, the chip is programmed and output verification is made. The outputs may not match with behavioral simulation. Usually it is due to clock latency of used hard logic elements in FPGAs. Using internal signal browsers in the chip, the problem can be solved.

Obviously, any problem in any stage causes restart of the whole design flow, again. This time consuming process is one of the biggest disadvantage of the hardware implementation.

#### 2.5.1 Used FPGAs