## AN FPGA BASED HIGH PERFORMANCE OPTICAL FLOW HARDWARE DESIGN FOR AUTONOMOUS MOBILE ROBOTIC PLATFORMS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

GÖKHAN KORAY GÜLTEKİN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2010

#### Approval of the thesis:

## AN FPGA BASED HIGH PERFORMANCE OPTICAL FLOW HARDWARE DESIGN FOR AUTONOMOUS MOBILE ROBOTIC PLATFORMS

submitted by GÖKHAN KORAY GÜLTEKİN in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>              |  |

|----------------------------------------------------------------------------------------------------|--|

| Prof. Dr. İsmet Erkmen<br>Head of Department, <b>Electrical and Electronics Engineering</b>        |  |

| Asst. Prof. Dr. Afşar Saranlı<br>Supervisor, Electrical and Electronics Engineering Dept.,<br>METU |  |

|                                                                                                    |  |

| Examining Committee Members:                                                                       |  |

| Prof. Dr. M. Kemal Leblebicioğlu<br>Electrical and Electronics Engineering Dept., METU             |  |

| Asst. Prof. Dr. Afṣar Saranlı<br>Electrical and Electronics Engineering Dept., METU                |  |

| Prof. Dr. Gözde Bozdağı Akar<br>Electrical and Electronics Engineering Dept., METU                 |  |

| Assoc. Prof. Dr. A. Aydın Alatan<br>Electrical and Electronics Engineering Dept., METU             |  |

| Asst. Prof. Dr. Melik Dölen<br>Mechanical Engineering Dept., METU                                  |  |

| Date:                                                                                              |  |

| I hereby declare that all<br>and presented in accord<br>also declare that, as requ<br>and referenced all mater | lance with acaden<br>uired by these rule | nic rules and ethical of s and conduct, I have | conduct. I fully cited                |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------|---------------------------------------|

|                                                                                                                |                                          | ure 1100 011 <b>9</b> 111111 00                | · · · · · · · · · · · · · · · · · · · |

|                                                                                                                |                                          |                                                |                                       |

|                                                                                                                | Name, Last Name:                         | GÖKHAN KORAY GÜ                                | LTEKİN                                |

|                                                                                                                | Signature :                              |                                                |                                       |

|                                                                                                                |                                          |                                                |                                       |

|                                                                                                                |                                          |                                                |                                       |

|                                                                                                                |                                          |                                                |                                       |

#### ABSTRACT

### AN FPGA BASED HIGH PERFORMANCE OPTICAL FLOW HARDWARE DESIGN FOR AUTONOMOUS MOBILE ROBOTIC PLATFORMS

Gültekin, Gökhan Koray

M.S., Department of Electrical and Electronics Engineering

Supervisor : Asst. Prof. Dr. Afşar Saranlı

September 2010, 91 pages

Optical flow is used in a number of computer vision applications. However, its use in mobile robotic applications is limited because of the high computational complexity involved and the limited availability of computational resources on such platforms. The lack of a hardware that is capable of computing optical flow vector field in real time is a factor that prevents the mobile robotics community to efficiently utilize some successful techniques presented in computer vision literature. In this thesis work, we design and implement a high performance FPGA hardware with a small footprint and low power consumption that is capable of providing over-realtime optical flow data and is hence suitable for this application domain. A well known differential optical flow algorithm presented by Horn & Schunck is selected for this implementation. The complete hardware design of the proposed system is described in details. We also discuss the design alternatives and the selected approaches together with a discussion of the selection procedure. We present the performance analysis of the proposed hardware in terms of computation speed, power consumption and accuracy. The designed hardware is tested with some of the available test sequences that are frequently used

iv

for performance evaluations of the optical flow techniques in literature. The proposed hardware is capable of computing optical flow vector field on 256x256 pixels images in 3.89ms which corresponds to a processing speed of 257 fps. The results obtained from FPGA implementation are compared with a floating-point implementation of the same algorithm realized on a PC hardware. The obtained results show that the hardware implementation achieved a superior performance in terms of speed, power consumption and compactness while there is minimal loss of accuracy due to the fixed point implementation.

Keywords: FPGA, embedded vision for mobile robotics, optical flow, real time image processing, Horn and Schunck algorithm

#### OTONOM GEZGİN ROBOTİK PLATFORMLARI İÇİN FPGA TABANLI YÜKSEK PERFORMANSLI BİR OPTİK AKIŞ DONANIM TASARIMI

Gültekin, Gökhan Koray Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Yrd. Doç. Dr. Afşar Saranlı

#### Eylül 2010, 91 sayfa

Optik akış, birçok bilgisayar ile görme uygulamalarında kullanılmaktadır. Ancak, yüksek işlem karmaşıklığı ve kısıtlı işlem kaynakları sebebiyle gezgin robot uygulamalarında kullanımı limitli olmaktadır. Gerçek zamanda optik akış hesaplayan donanımların eksikliği, bilgisayar ile görme literatüründe sunulan birçok başarılı çalışmanın gezgin robot araştırmalarında kullanılmasını kısıtlayan bir etmendir. Bu tez çalışmasında, gezgin robot uygulamaları için, gerçek zaman üstü optik akış verisi sağlayabilen küçük boyutlarda ve düşük güç tüketen yüksek performanslı bir FPGA donanım tasarımı yapılmaktadır. Horn ve Schunck tarafından sunulan tanınmış bir diferansiyel optik akış algoritmasının uygulaması yapılmıştır. Önerilen donanım tasarımının tamamı detaylı bir şekilde açıklanmıştır. Ayrıca, tasarım alternatifleri ve seçilen yöntemler gerekçekçeleriyle birlikte tartışılmıştır. Önerilen donanımın performans analizleri; işlem hızı, güç tüketimi ve doğruluk bakımından sunulmuştur. Tasarlanan donanım, literatürde optik akış yöntemlerinin performans değerlendirmesinde sıklıkla kullanılan mevcut bazı test dizileri ile sınanmıştır. Önerilen donanım, 256x256 pikselden oluşan görüntüler üzerinde optik akış hesabını saniyede 257 kare işlemeye

karşılık gelen 3.89ms sürede hesap edebilmektedir. FPGA uygulamasından elde edilen sonuçlar, aynı algoritmanın PC donanımı üzerinde kayan nokta uygulamasından elde edilen sonuçlarla karşılaştırılmıştır. Elde edilen sonuçlar donanım uygulamasının, sabit nokta gösterim uygulamasından kaynaklanan doğruluktaki makul bir azalmaya karşılık, hız, güç tüketimi ve az yer kaplama bakımından üstün bir performans gösterdiğini ortaya koymuştur.

Anahtar Kelimeler: FPGA, gezgin robotik için gömülü bilgisayar görme, optik akış, gerçek zamanlı görüntü işleme, Horn ve Schunck algoritması

to my loving mother, dear father and brother

#### ACKNOWLEDGMENTS

I would like to express my deep appreciation and sincere gratitude to my supervisor Dr. Afşar Saranlı for his leading guidance, encouragement, and continuous support from beginning to the end of my M.S. study. His suggestions during our research meetings played a tremendous role in helping me to broaden my view and knowledge. He showed me different ways to approach a research problem and the need to be persistent to accomplish any goal. He let me take part in the SensoRHex project which was a great opportunity for me to extend my academic and technical skills. He also made the Rolab (Laboratory of Robotics and Autonomous Systems) a wonderful workplace by providing us many new equipments we need.

I wish to express my deep sense of gratitude to Dr. Uluç Saranlı for his guidance and being a source of inspiration for me in the conduct of my thesis work and our research project. I also would like to thank Dr. Kemal Leblebicioğlu for conducting the ULİSAR project in the Rolab which added much to my experience. I should also extend my sincere thanks to Dr. Hamit Erdem. I learnt a lot from him, which I am sure will be useful in different stages of my life. I thank to Engin Çiftçi from Karel and Hakan Aydın from Linera for their help on pointing out the problems occurred during the FPGA design.

I literally consider myself a lucky person to work with the amazing group of people in Rolab. I am very thankful to Mert Ankaralı, Emre Ege, Orkun Öğücü, Ferit Üzer, Emre Akgül, Ege Saygıner and all other members for sharing me their time and knowledge. Further thanks should also go to the all members of BDRL (Bilkent Dexterous Robotics and Locomotion), especially Ömür Arslan and Tolga Özaslan.

I would like to thank the Scientific and Technological Research Council of Turkey (TÜBİTAK) for awarding me their prestigious master of science studies scholarship.

I apologize from the people who I should also have included their names here for their contributions but may forgot because of the rush I am in. I send my thanks to all

#### individually.

Finally, yet the most importantly, nothing is adequate to express my heartfelt feelings to my beloved family forever. None of this would have been even possible without the love and patience of them. I owe a great many thanks to my loving mother(Elif Gültekin), my dear father(Mahmut Gültekin) and my sweetie brother(Korcan Emre Gültekin) for their undying love, unconditional support, encouragement and their trust in me.

#### TABLE OF CONTENTS

| ABSTI  | RACT    |          |              |                                         | iv   |

|--------|---------|----------|--------------|-----------------------------------------|------|

| ÖZ     |         |          |              |                                         | vi   |

| DEDIC  | CATION  |          |              |                                         | viii |

| ACKN   | OWLED   | GMENT    | S            |                                         | ix   |

| TABLE  | E OF CO | ONTENT   | 'S           |                                         | xi   |

| LIST ( | OF TAB  | LES      |              |                                         | xiv  |

| LIST ( | F FIGU  | JRES     |              |                                         | xvi  |

| LIST ( | F ABB   | REVIAT   | IONS         |                                         | xxi  |

| CHAP'  | TERS    |          |              |                                         |      |

| 1      | INTRO   | ODUCTI   | ON           |                                         | 1    |

|        | 1.1     | Motiva   | tion         |                                         | 1    |

|        | 1.2     | Literati | ure Survey   |                                         | 3    |

|        | 1.3     | Contrib  | outions      |                                         | 6    |

|        | 1.4     | Outline  | of the The   | esis                                    | 7    |

| 2      | BACK    | GROUN    | D ON OPT     | TICAL FLOW COMPUTATION                  | 9    |

|        | 2.1     | Optical  | Flow         |                                         | 9    |

|        | 2.2     | Differer | ntial Optica | l Flow Computation Methods              | 9    |

|        |         | 2.2.1    | Horn-Sch     | unck Optical Flow Computation Algorithm | 10   |

|        |         |          | 2.2.1.1      | Pre-Assumptions                         | 10   |

|        |         |          | 2.2.1.2      | Optical Flow Constraint Equation        | 11   |

|        |         |          | 2.2.1.3      | Horn & Schunck Smoothness Constraint .  | 12   |

|        |         |          | 2.2.1.4      | The Numerical Solution                  | 14   |

| 3 | FPGA | HARDW    | ARE PLATFORM FOR VISION                                             | 17 |

|---|------|----------|---------------------------------------------------------------------|----|

|   | 3.1  | Require  | ments of the FPGA Hardware Platform                                 | 17 |

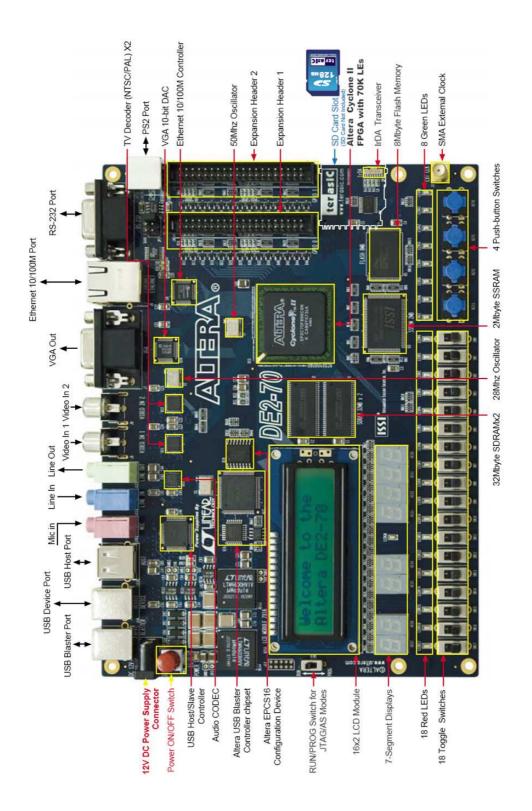

|   | 3.2  | FPGA I   | Development Platform Specifications                                 | 19 |

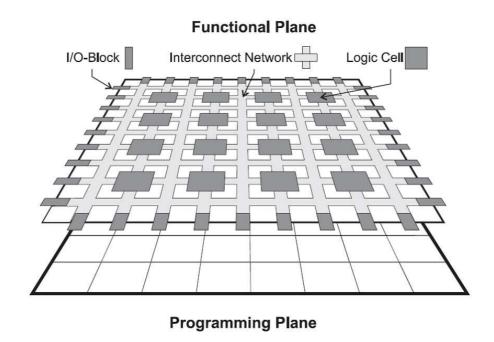

|   | 3.3  | FPGA A   | Architecture                                                        | 23 |

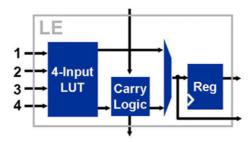

|   |      | 3.3.1    | Logic Elements                                                      | 25 |

|   |      | 3.3.2    | Embedded Memory Blocks                                              | 26 |

|   |      | 3.3.3    | Embedded Multipliers                                                | 26 |

|   | 3.4  | FPGA I   | Development Environment and Design Flow                             | 27 |

|   |      | 3.4.1    | Quartus II                                                          | 27 |

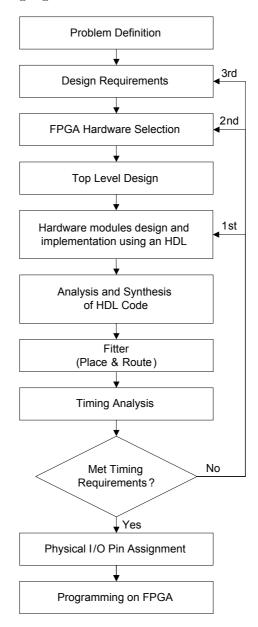

|   | 3.5  | FPGA I   | Design Flow                                                         | 27 |

| 4 | PROP | OSED FF  | PGA HARDWARE DESIGN FOR OPTICAL FLOW .                              | 30 |

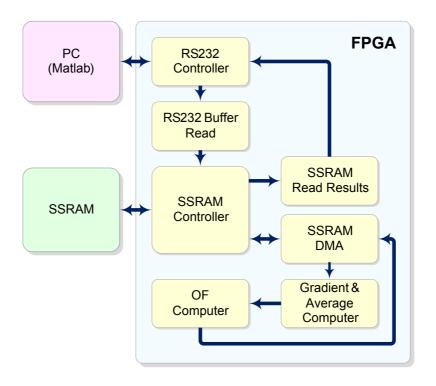

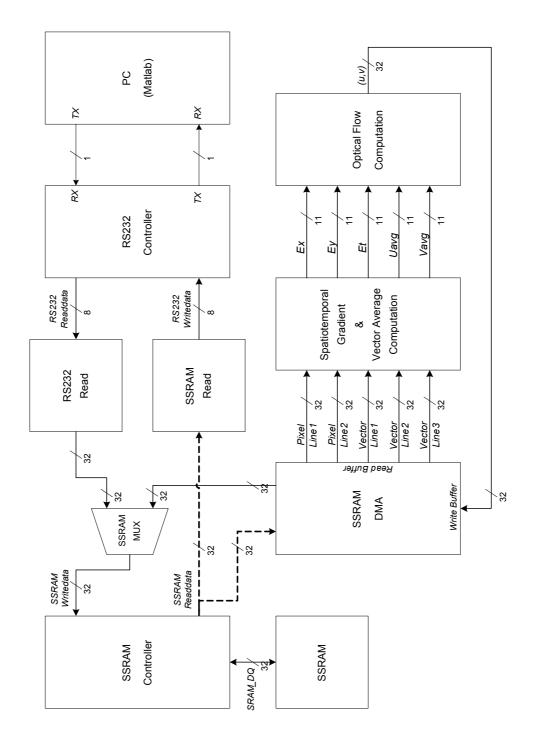

|   | 4.1  | High Le  | vel Block Diagram                                                   | 30 |

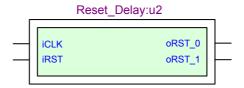

|   | 4.2  | Reset C  | ircuitry                                                            | 33 |

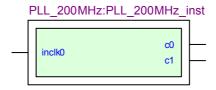

|   | 4.3  | Clocking | g Circuitry                                                         | 34 |

|   | 4.4  | Memory   |                                                                     | 36 |

|   |      | 4.4.1    | SSRAM Memory Controller                                             | 37 |

|   |      | 4.4.2    | Direct Memory Access Module                                         | 38 |

|   |      |          | 4.4.2.1 FIFO Buffers                                                | 44 |

|   | 4.5  |          | mporal Gradient and Optical Flow Vectors Local Avenueur Description | 45 |

|   | 4.6  | Optical  | Flow Computation                                                    | 50 |

|   | 4.7  | PC Com   | nmunication                                                         | 52 |

|   |      | 4.7.1    | UART Controller                                                     | 53 |

|   |      | 4.7.2    | RS232 to SSRAM Data Transfer Module                                 | 53 |

|   |      | 4.7.3    | SSRAM to RS232 Data Transfer Module                                 | 56 |

| 5 |      |          | ESIGN PERFORMANCE ANALYSIS AND TEST RE-                             | 58 |

|   | 5.1  | Tests W  | ith Standard Image Sequences                                        | 58 |

|   |      | 5.1.1    | Description of Standard Data Set                                    | 58 |

|   |      | 5.1.2    | Performance Measure                                                 | 59 |

|   |      | 5 1 3    | Results                                                             | 60 |

|       |       |          | 5.1.3.1     | Rubik's Cube Sequence     | 60 |

|-------|-------|----------|-------------|---------------------------|----|

|       |       |          | 5.1.3.2     | Hamburg Taxi Sequence     | 67 |

|       |       |          | 5.1.3.3     | Translating Tree Sequence | 70 |

|       | 5.2   | Perform  | ance Analys | sis of Designed Hardware  | 73 |

|       |       | 5.2.1    | Resource    | Usage                     | 73 |

|       |       | 5.2.2    | Power Con   | nsumption                 | 77 |

|       |       | 5.2.3    | Computat    | ion Time                  | 81 |

|       | 5.3   | Comme    | nts on Anal | ysis & Results            | 82 |

| 6     | CONC  | LUSION   |             |                           | 85 |

|       | 6.1   | Future ' | Work        |                           | 87 |

| DEFEE | FNCES | 1        |             |                           | 80 |

### LIST OF TABLES

#### TABLES

| Table 3.1 Cyclone II FPGA family features[2]. The development board we use     |    |

|--------------------------------------------------------------------------------|----|

| includes EP2C70 device which has the highest resources available in the        |    |

| Cyclone II family                                                              | 23 |

|                                                                                |    |

| Table 4.1 Operating clock frequencies of modules. 200MHz is used for the       |    |

| modules that access SSRAM memory to reduce memory bottleneck. $50\mathrm{MHz}$ |    |

| is used for the rest                                                           | 35 |

| Table 4.2 Properties of memories available on DE2-70 board. SSRAM is pre-      |    |

| ferred because of its higher bandwidth although its capacity is lower than     |    |

| the SDRAM memory                                                               | 36 |

| Table 4.3 Maximum data rates of some communication protocols                   | 52 |

|                                                                                |    |

| Table 5.1 Total error rates of Rubik's cube sequence                           | 65 |

| Table 5.2 Partial error rates of Rubik's cube sequence caused by the approxi-  |    |

| mation in computation of local averages of optical flow vectors                | 65 |

| Table 5.3 Error rates of Rubik's cube sequence versus number of fraction bits  |    |

| used to represent the optical flow vector values                               | 65 |

| Table 5.4 Maximum operating frequency of a signed division operation versus    |    |

| the word length of its operands                                                | 67 |

| Table 5.5 Error rates of Hamburg Taxi sequence caused by the fixed point       |    |

| implementation                                                                 | 68 |

| Table 5.6 Error rates of Translating Tree sequence                             | 71 |

| Table 5.7 Resource usage of the overall design and available resources on the  |    |

| FPGA device                                                                    | 73 |

| Table 5.8 Resource usage of individual design modules | 75 |

|-------------------------------------------------------|----|

| Table 5.9 Total power dissipation                     | 77 |

| Table 5.10 Current drawn from supply pins             | 78 |

| Table 5.11 Power consumption of individual modules    | 79 |

#### LIST OF FIGURES

#### FIGURES

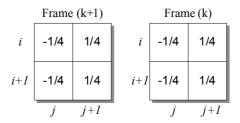

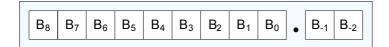

| Figure 2.1 | Numerical computation of $E_x$ using first order difference of 8 pixels.                                                                                                                                                                       | 15 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

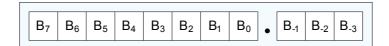

| Figure 2.2 | Numerical computation of $E_y$ using first order difference of 8 pixels.                                                                                                                                                                       | 15 |

| Figure 2.3 | Numerical computation of $E_t$ using first order difference of 8 pixels.                                                                                                                                                                       | 16 |

| Figure 2.4 | Weight matrix for estimating local averages of optical flow vectors .                                                                                                                                                                          | 16 |

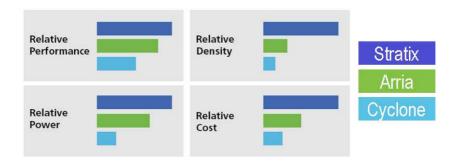

|            | The FPGA product portfolio of Altera with a comparison of their ole resources, performances, power consumptions and costs                                                                                                                      | 20 |

| Figure 3.2 | Altera DE2-70 FPGA development board[1]                                                                                                                                                                                                        | 21 |

| plane i    | General hardware architecture of FPGA devices[21]. Functional is used to implement logic functions defined by user by logic cells and g channels. Programming plane stores the LUT values in SRAMs for uration of functional plane at start up | 24 |

| used to    | Components of a logic element block[2]. Each logic element can be o implement combinational, sequential logic functions and arithmetic ions                                                                                                    | 25 |

| Figure 3.5 | FPGA Design Flow Diagram                                                                                                                                                                                                                       | 28 |

| Figure 4.1 | Block diagram of the designed system                                                                                                                                                                                                           | 31 |

| Figure 4.2 | Data flow diagram of the designed system                                                                                                                                                                                                       | 32 |

|            | Reset signal generator module. Two reset signals are generated with<br>nt release times. They are used to synchronize the start up of modules                                                                                                  |    |

| design     | ed                                                                                                                                                                                                                                             | 34 |

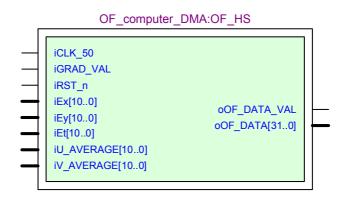

| Figure 4.6 Direct Memory Access (DMA) module terminals. DMA is used to handle memory read/write operations required for the operation of optical flow computations. It helps increasing the bus utilization and reduces the memory bottleneck                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | rigure 4.4 Phase Locked Loop (PLL) module generates the required clock signals for the operation of designed modules. There are two clocks generated which are 200MHz and 50MHz from the input clock of 50MHz | 35 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

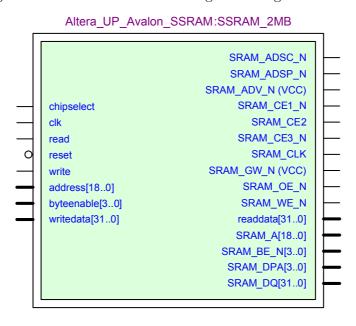

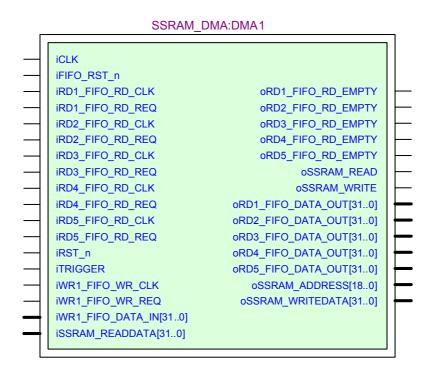

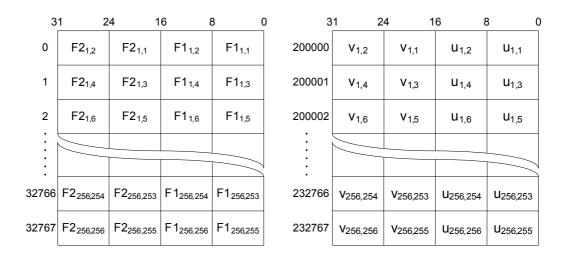

| handle memory read/write operations required for the operation of optical flow computations. It helps increasing the bus utilization and reduces the memory bottleneck.  39  Figure 4.7 Layout of stored data in SSRAM for two frames of 256x256 pixels. Image frames are stored starting from the first address location and optical flow vectors are stored beginning from the 200,000th address location of SSRAM.  40  Figure 4.8 Layout of pixel FIFO buffers. Each location of FIFO buffers is 32 bits in width and stores 2 consecutive pixels from frame 1, and 2 consecutive pixels from frame 2.  Figure 4.9 Layout of optical flow vectors in FIFO buffers. There is a phase difference of 1 line of vectors between three FIFO buffers.  42  Figure 4.10 DMA module FSM states  43  Figure 4.12 Spatiotemporal gradient computation module terminals. This module computes both spatiotemporal gradient values and the local averages of optical flow vectors.  45  Figure 4.13 Spatiotemporal gradients data representation in 11 bits fixed point format. 2 bits fraction is enough for representing the gradient results without any accuracy lost.  46  Figure 4.14 The weight matrix used for estimating local averages of optical flow vectors on FPGA. The weights given in Fig. 2.4 are modified to simplify the division operation and increase the accuracy.  47  Figure 4.15 Optical flow vector local average data representation in 11 bits fixed point format. 3 bits fraction is enough for representing the vector local | Figure 4.5 SSRAM memory controller module terminals                                                                                                                                                           | 37 |

| Image frames are stored starting from the first address location and optical flow vectors are stored beginning from the 200,000th address location of SSRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | handle memory read/write operations required for the operation of optical flow computations. It helps increasing the bus utilization and reduces the                                                          | 39 |

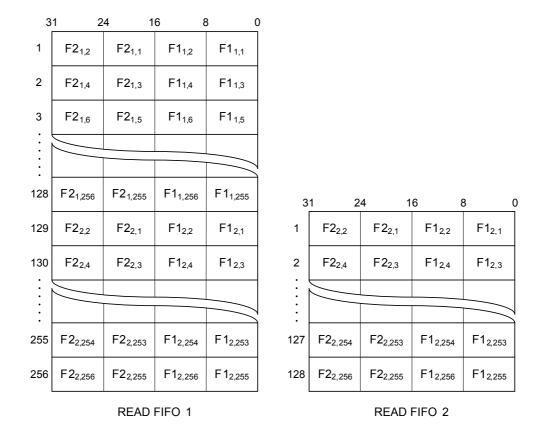

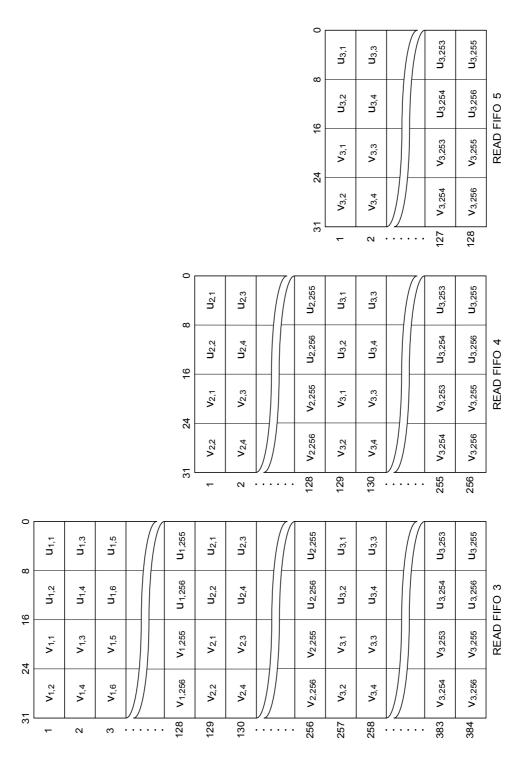

| Figure 4.8 Layout of pixel FIFO buffers. Each location of FIFO buffers is 32 bits in width and stores 2 consecutive pixels from frame 1, and 2 consecutive pixels from frame 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Image frames are stored starting from the first address location and optical flow vectors are stored beginning from the 200,000th address location of                                                         | 40 |

| difference of 1 line of vectors between three FIFO buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 4.8 Layout of pixel FIFO buffers. Each location of FIFO buffers is 32 bits in width and stores 2 consecutive pixels from frame 1, and 2 consecutive                                                    | 41 |

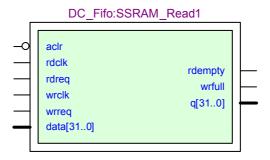

| Figure 4.11 Dual clock FIFO buffer module terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                               | 42 |

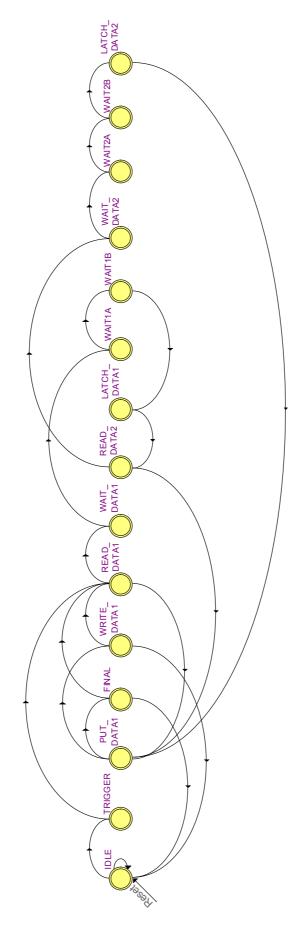

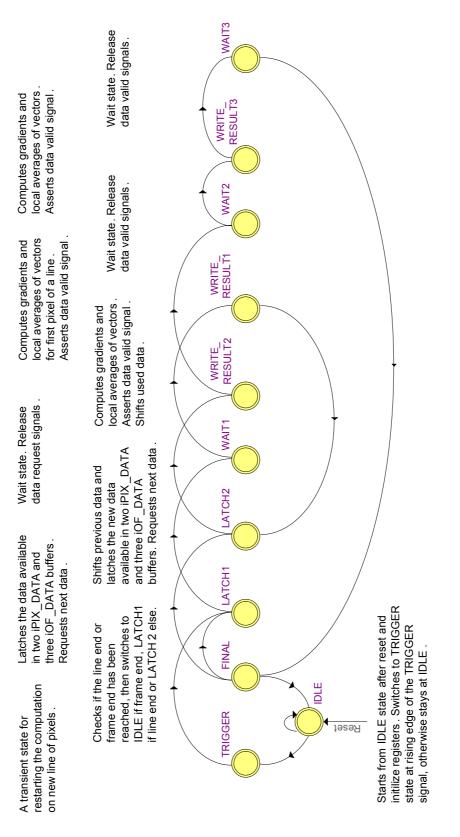

| Figure 4.12 Spatiotemporal gradient computation module terminals. This module computes both spatiotemporal gradient values and the local averages of optical flow vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 4.10 DMA module FSM states                                                                                                                                                                             | 43 |

| ule computes both spatiotemporal gradient values and the local averages of optical flow vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 4.11 Dual clock FIFO buffer module terminals                                                                                                                                                           | 44 |

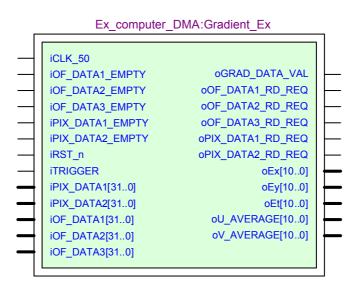

| format. 2 bits fraction is enough for representing the gradient results without any accuracy lost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ule computes both spatiotemporal gradient values and the local averages of                                                                                                                                    | 45 |

| vectors on FPGA. The weights given in Fig. 2.4 are modified to simplify the division operation and increase the accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | format. 2 bits fraction is enough for representing the gradient results with-                                                                                                                                 | 46 |

| point format. 3 bits fraction is enough for representing the vector local                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vectors on FPGA. The weights given in Fig. 2.4 are modified to simplify                                                                                                                                       | 46 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                               | 47 |

| Figure 4.16 Spatiotemporal gradient computation module FSM states                                                                                        | 49 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

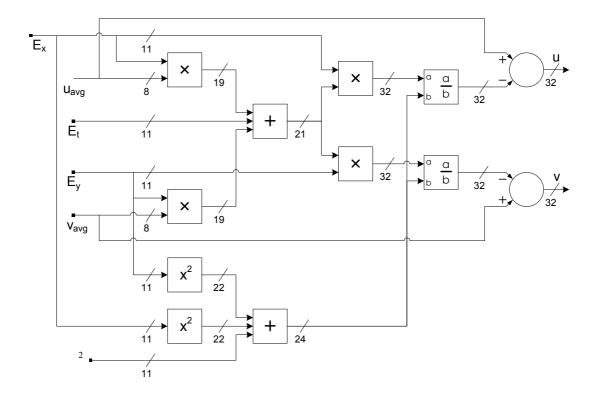

| Figure 4.17 Optical flow computation module                                                                                                              | 50 |

| Figure 4.18 Optical flow computation module data flow diagram $\dots \dots$                                                                              | 51 |

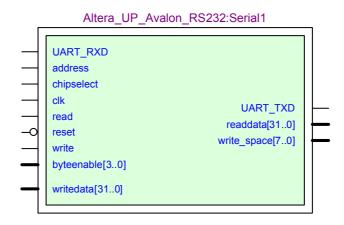

| Figure 4.19 RS232 controller module terminals                                                                                                            | 53 |

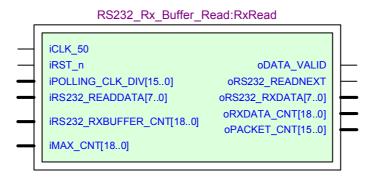

| Figure 4.20 RS232 to SSRAM data transfer module terminals. This module acts as an interface for transferring image frames read from RS232 controller and |    |

| written to SSRAM memory                                                                                                                                  | 54 |

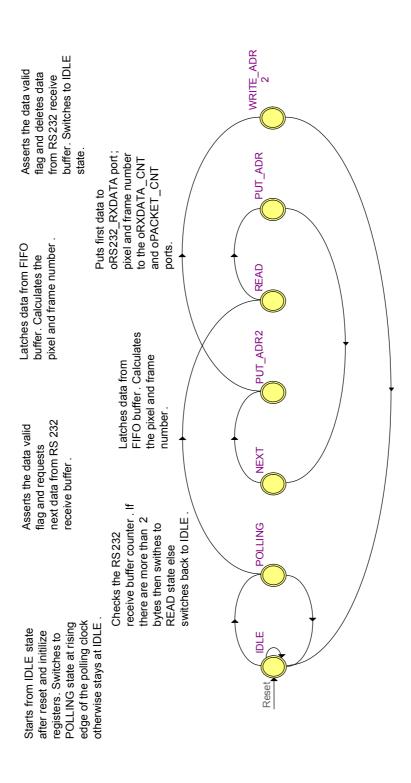

| Figure 4.21 RS232 to SSRAM data transfer module FSM states                                                                                               | 55 |

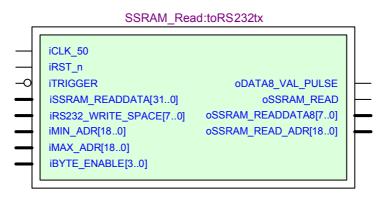

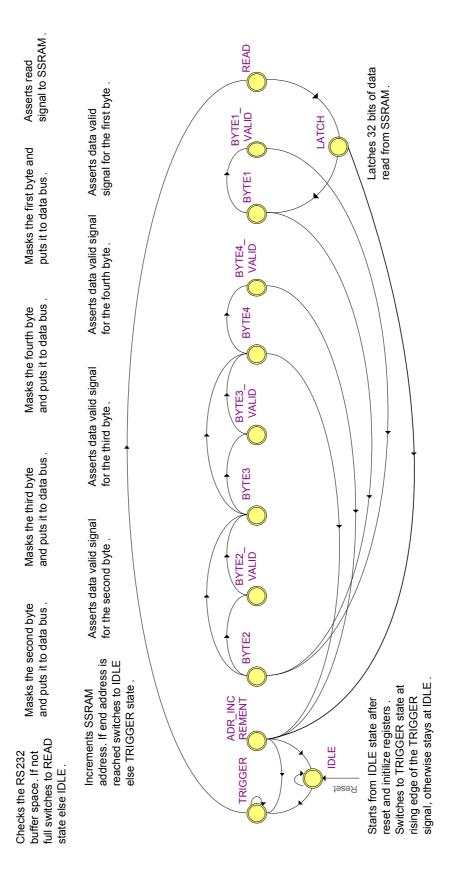

| Figure 4.22 SSRAM to RS232 data transfer module                                                                                                          | 56 |

| Figure 4.23 SSRAM to RS232 data transfer module FSM states                                                                                               | 57 |

| Figure 5.1 Output of the $E_x$ gradient computation on FPGA hardware. The                                                                                |    |

| pixel values are inverted to get better visualization. White represents the                                                                              |    |

| lowest value and black represents the highest value                                                                                                      | 61 |

| Figure 5.2 Output of the $E_y$ gradient computation on FPGA hardware. The                                                                                |    |

| pixel values are inverted to get better visualization. White represents the                                                                              |    |

| lowest value and black represents the highest value                                                                                                      | 61 |

| Figure 5.3 Output of the $E_t$ gradient computation on FPGA hardware. The                                                                                |    |

| pixel values are inverted to get better visualization. White represents the                                                                              |    |

| lowest value and black represents the highest value                                                                                                      | 62 |

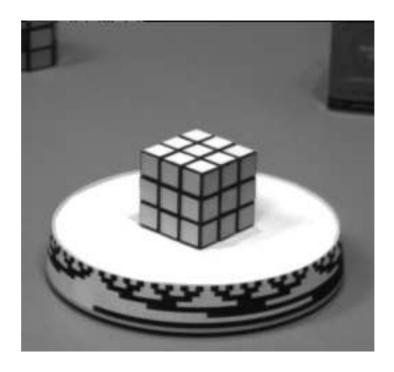

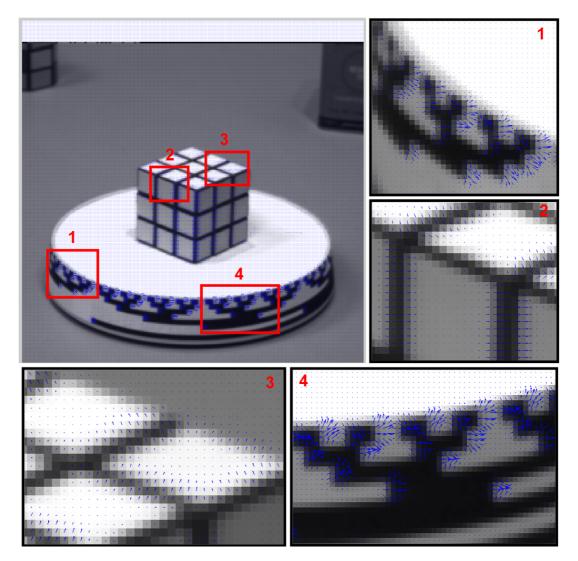

| Figure 5.4 1st frame of Rubik's cube sequence. The turntable rotates counter-<br>clockwise with the Rubik's cube on top of it                            | 62 |

| Figure 5.5 Optical flow vectors computed on FPGA hardware for Rubik's cube                                                                               |    |

| sequence                                                                                                                                                 | 63 |

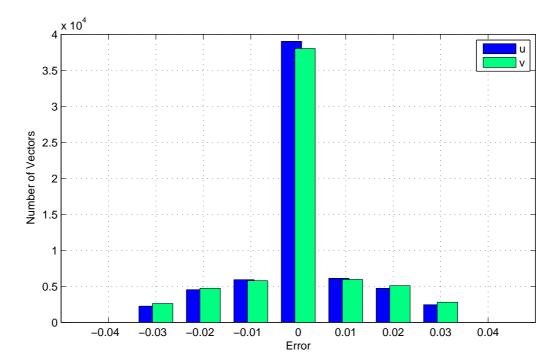

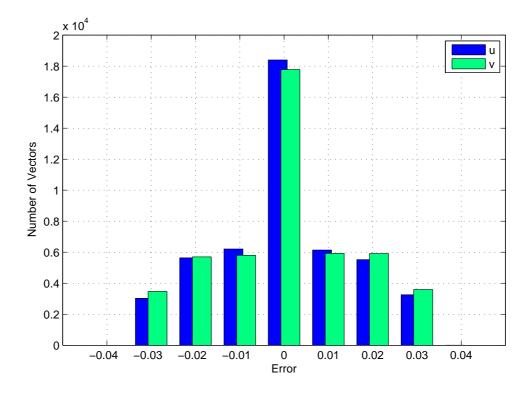

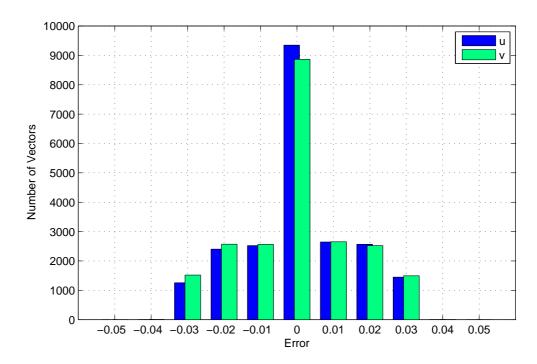

| Figure 5.6 Error histogram of optical flow vectors for Rubik's cube sequence.                                                                            |    |

| Error values indicate the center points of $\pm 0.005$ error intervals                                                                                   | 64 |

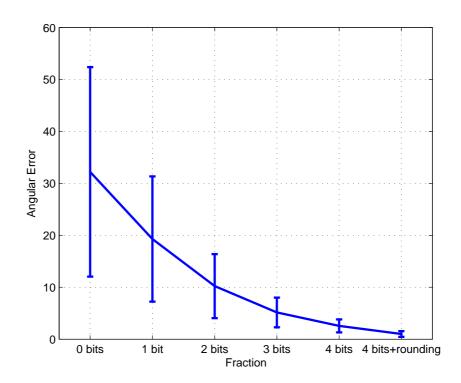

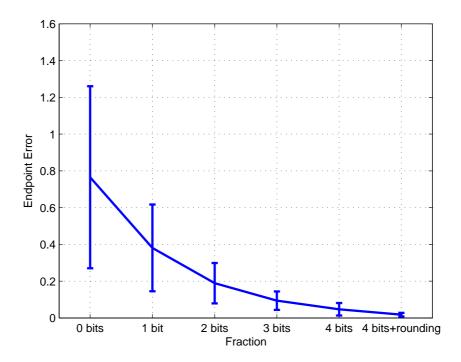

| Figure 5.7 Angular error rate versus number of fraction bits used to represent                                                                           |    |

| the optical flow vector values                                                                                                                           | 66 |

| Figure 5.8 Endpoint error rate versus number of fraction bits used to represent                                                                          |    |

| the optical flow vector values                                                                                                                           | 66 |

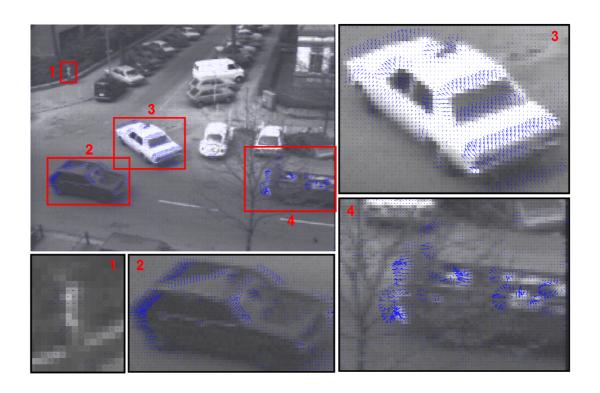

| The car on the left and the van on the right are driving in their way, the taxi in the middle is turning the corner and the pedestrian is walking on                                                                                                                                                                   |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| the pavement                                                                                                                                                                                                                                                                                                           | 68 |

| Figure 5.10 OF vectors computed on FPGA hardware for Hamburg Taxi sequence.                                                                                                                                                                                                                                            | 69 |

| Figure 5.11 Error histogram of optical flow vectors for Hamburg Taxi sequence. Error values indicate the center points of $\pm 0.005$ error intervals                                                                                                                                                                  | 69 |

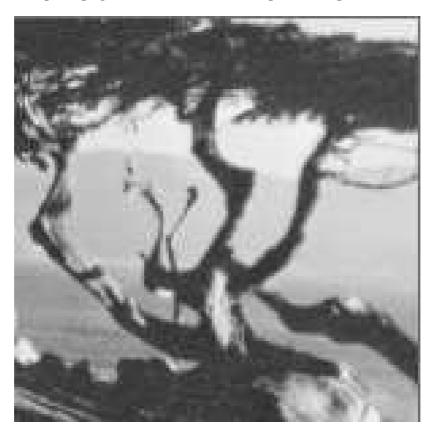

| Figure 5.128th frame of synthetic Translating Tree sequence. The camera is moving from right to left while looking at a constant scene including a tree in the front side. The motion field has a velocity ranging from 1.73 and 2.26 pixels/frame                                                                     | 70 |

| Figure 5.13 Error histogram of optical flow vectors for Translating Tree sequence.                                                                                                                                                                                                                                     |    |

| Error values indicate the center points of $\pm 0.005$ error intervals                                                                                                                                                                                                                                                 | 71 |

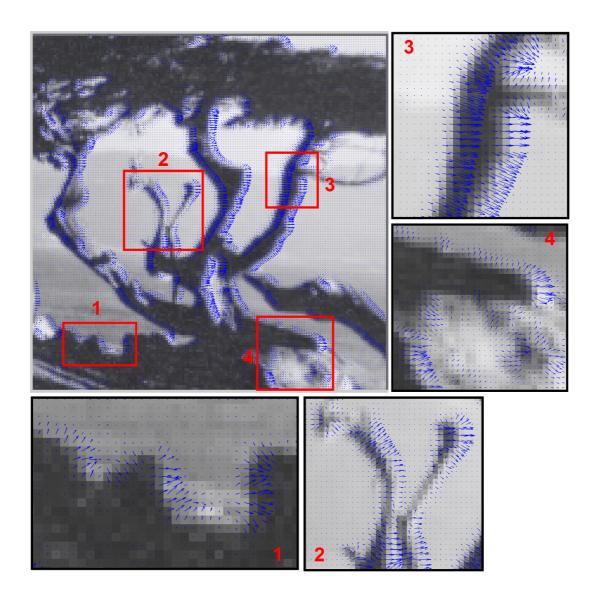

| Figure 5.14 Optical flow vectors computed on FPGA hardware for Translating  Tree sequence. Four regions are zoomed in to provide a closer view of the optical flow field computed on FPGA                                                                                                                              | 72 |

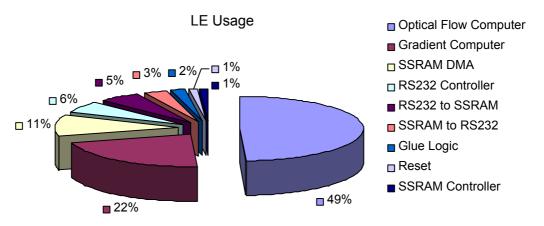

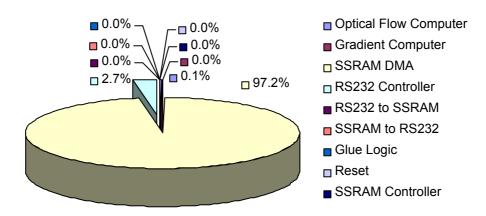

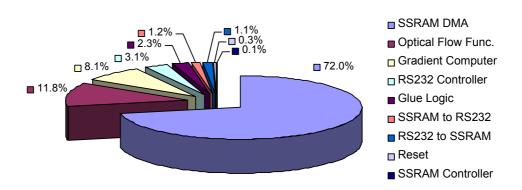

| Figure 5.15 LE usage percentage of modules                                                                                                                                                                                                                                                                             | 74 |

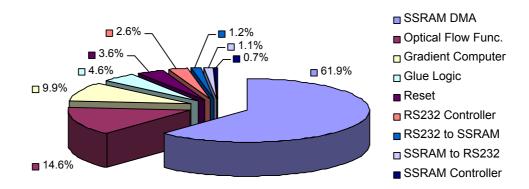

| Figure 5.16 Memory usage percentage of modules                                                                                                                                                                                                                                                                         | 75 |

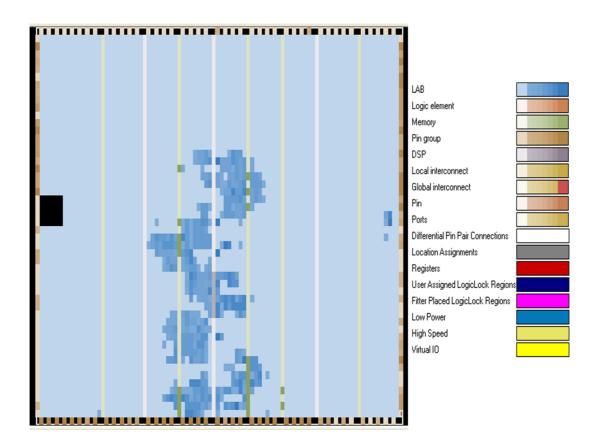

| Figure 5.17 Floorplan of the designed hardware fitted on a EP2C70 device. The schematic shows the layout of the resources on the chip that are used to implement the design. The color legend is given next to the figure. The darker color of a particular resource indicates the higher usage ratio of that resource | 76 |

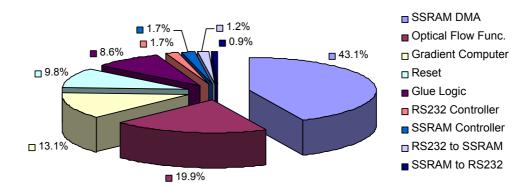

| Figure 5.18 Pie chart represents the total power consumption partitioned among the design modules according to their percentages. More than half of the total power is consumed by the DMA module because of its high operating                                                                                        |    |

| frequency and high resource usage. It is followed by the OF function and                                                                                                                                                                                                                                               | 80 |

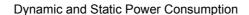

| Figure 5.19 Pie chart represents the dynamic and static power consumption par-   |    |

|----------------------------------------------------------------------------------|----|

| titioned among the design modules according to their percentages. Nearly         |    |

| 3/4 of this power type is consumed by the DMA module because of its              |    |

| high operating frequency and high resource usage. It is followed by the OF       |    |

| function and the Gradient computation modules                                    | 80 |

| Figure 5.20 Pie chart represents the total routing power consumption partitioned |    |

| among the design modules according to their percentages. Nearly half of the      |    |

| routing power is consumed by the DMA module because of its high memory           |    |

| usage. It is followed by the OF function and the Gradient computation            |    |

| modules                                                                          | 81 |

#### LIST OF ABBREVIATIONS

**AAE** Average Angular Error

**AE** Angular Error

**AEE** Average Endpoint Error

**ASIC** Application Specific Integrated Circuit

DMA Direct Memory AccessDSP Digital Signal Processor

**EE** Endpoint Error

**EEPROM** Electrically Erasable Programmable Read Only Memory

**FIFO** First In First Out

FIP Fixed PointFLP Floating Point

**FPGA** Field Programmable Gate Array

fps Frames per secondFSM Finite State MachineGPU Graphical Processing Unit

HDL Hardware Description Language

IC Integrated CircuitIP Intellectual PropertyJTAG Joint Test Action Group

LAB Logic Array Block

LE Logic Element

LUT Look Up Table

OF Optical Flow

PC Personal Computer

PLL Phase Locked Loop

**PROM** Programmable Read Only Memory

RTL Register Transfer Level

SDRAM Synchronous Dynamic Random Access Memory

STD Standard Deviation

**SRAM** Static Random Access Memory

SSRAM Synchronous Static Random Access Memory

TS Test Sequence

**UART** Universal Asynchronous Receiver Transmitter

**USB** Universal Serial Bus

VHDL Very High Speed Integrated Circuit Hardware Description

Language

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

Optical flow computation is one of the computer vision algorithms that have a high computational complexity. Although it has many application areas such as collision detection, motion segmentation, tracking, background subtraction, visual odometry, video compression and many more, these applications generally suffer from insufficient computational power. There is a huge amount of data to be processed in image sequences and optical flow computations involves complex, time consuming operations. Unlike the applications where offline computation is possible, robotic applications generally require the computation of optical flow in real time. Moreover, in most of the applications, optical flow is computed as a pre-processing step and then it is fed to other high level vision algorithms as input which requires even extra computational power for those tasks.

The architecture of microprocessors is poorly suited to the structure of image processing algorithms. The demanded computational power generally exceeds the power supplied by todays conventional general purpose desktop computers and digital signal processors[14]. In addition, because of their high clock rates, they consume a huge amount of electrical power which also causes a high heat dissipation. To cool down the hardware, they have extra cooling equipments that increase their sizes and weights. Unfortunately, in aerial and mobile robotic platforms, available amount of power, space and weight is limited. Also, high clock rates of processors prevent them to be used in some areas such as space robotics where they are more susceptible to radiation[25]. So, these high end processors are usually not feasible to operate on

these robotic platforms. It is observed that, many available optical flow computation methods in literature can not be utilized on mobile robots for real-time applications because of these weaknesses of computational hardware.

There have been many studies made in literature on developing new methods for accurate and efficient computation of optical flow. The available methods are also compared in terms of their accuracy, density and computational complexity in some studies[10, 11]. Although there are very accurate methods proposed, they still require a high computational power.

While new methods on optical flow computation continue to appear, recently there has been a noticeable interest on application specific alternative computation platforms[25]. Application specific integrated circuits(ASIC) are designed to maintain the needs of that specific application in terms of computational power, space and power consumption. They can be designed to process chunks of data at once in parallelized and pipelined structures whereas, general purpose sequential processors require multiple processor cycles. This property of ASICs make them much more efficient than conventional processors. However, ASIC design and manufacturing is a long and difficult process. Once an ASIC is manufactured it is impossible to make any changes on it any more. So ASIC design and manufacturing is a costly process and it is only advantageous in mass production. Although their numerous advantages mentioned above, ASICs can not be utilized in academic studies.

For the solution to the static structure of ASICs, field programmable gate arrays (FPGAs) are developed. Having similar performance with ASICs in terms of computational power, size and power dissipation, they can also be programmed in field. This property makes FPGAs a flexible platform which enables to make modifications to the design in a matter of hours. These advantages of FPGAs attract academic interests to them nowadays. Although FPGAs are in use since 1980s they are newly used in academic studies. There are even some recent publications made on the suitability of FPGAs in vision systems which claim that FPGAs have an important potential to be utilized in vision research[25].

At robotics laboratory of Electrical and Electronics Engineering Department in METU, we came up with the need to do some computer vision operations on our highly mobile legged robot platform SensoRhex for higher level tasks. However, we faced with the shortage of computational power on our robot and searched for a feasible solution. Being motivated by our needs and encouraged by a few successful applications and suggestions presented in literature, we designed a custom hardware solution for computing optical flow which is subject to this thesis work.

We would like to clearly state here that the scope of this thesis work is related with the high performance and efficient hardware design to compute an optical flow computation algorithm that is already available in computer vision literature. We focus our efforts not on the performance of the algorithm itself but on developing the hardware that fulfills the aforementioned objectives for robotics platforms.

#### 1.2 Literature Survey

Studies in optical flow calculation dates back to 80's and up to now, there are many methods proposed for optical flow computation. These methods can be mainly grouped as gradient based, correlation based, energy based and phase based methods [11].

Gradient-based methods depend on the evaluation of spatio-temporal derivatives. The earliest two gradient based methods are presented by Horn & Schunck [23] and Lucas & Kanade [24]. Horn and Schunck presents a method assuming that the optical flow field is smooth which introduces a global smoothness term to constrain the estimated velocity field. Lucas & Kanade's method depends on an assumption that a point's neighboring pixels move with it, meaning that the flow is constant locally. This introduces additional equations to determine optical flow vectors by utilizing a least squares estimate. Since gradient based methods are rather popular, there are many other gradient based methods presented later in [28], [12] and [31]. The Horn & Schunck's method have relatively less computational complexity over many other methods and provide high density optical flow vectors with a reasonable error rate. This method is also suitable for high performance FPGA hardware implementations. The computations can be done using fixed point representations with small word lengths. They can be implemented using parallel and pipelined structures which yields a high throughput.

The matching based approaches depends on the determination of correspondences between consecutive frames. These correspondences can be found by correlating small patches in the images at different times to find the best fit. The first matching based method is presented by Anandan which is based on an SSD based matching technique [4]. A region including 5x5 pixels is searched around 3 pixels displacement for a suitable match.

Energy based (also called frequency based) methods utilizes the output energy of velocity tuned filters. Heeger's method [22] can be considered for one of the methods in this group. In this method, 3D Gabor filters are used to sample the power spectrum. Then a least squares estimate is utilized to minimize the difference between the predicted and the measured motion energies.

Phase based methods are similar to the energy based techniques. The method is first presented by Fleet & Jepson given in [20]. They use the outputs of velocity-tuned filters. However, they utilize the phase information instead of the amplitude component utilized in energy based methods. Their method yields a dense flow field with high accuracy in expense of high computational cost.

The authors of the presented optical flow techniques, implement and test their methods on general purpose computers. The first reason is to achieve comparable performance evaluation of the methods with each other. Although the clock rates vary from PC to PC, this measure roughly gives a benchmark. The other reason is probably the ease of implementation on a general purpose computer. Although the presented computational performances of their methods implemented on a PC are a disappointment for many realtime application, the chosen test platforms are general purpose computers for the reasons we mentioned.

On the other hand, the performance evaluation of methods on sequential general purpose computers gives no clear idea about their performances on parallelized and pipelined architectures such as implementations on ASICs, FPGAs or GPUs. It is known that in many computer vision algorithms, parallelized and pipelined implementations on FPGAs can produce better performances than in general purpose computers[25]. To be able to enhance the computation performance of optical flow methods, some FPGA implementations are presented in literature in [5, 7, 8, 9, 29, 34].

FPGA implementation of Horn & Schunck method is first peresented in [7] with a performance of processing 19 fps of 50x50 pixels images. To decrease the calculation time, they run the algorithm for 3 iterations which yields enough precision for many applications. Another implementation of the same authors uses the Camus correlation method [15] yielding an output of 25 fps at 100x100 pixels images[8]. They also implement a method presented in [32]. None of their publications gives quantitative measures on the accuracy or make comparisons with other studies. Later, they presented new studies on utilizing their implementations on real time applications such as lane departure detection[6]. Another hardware implementation of Horn & Schunck method is presented in [26]. They claimed processing 256x256 pixels images at 60 fps. However, there is no information, discussion or comparison on the power consumption, error rates and accuracy of the implemented system. A recent work is presented in [17] which uses census transformation. They achieve a processing time of 22ms on images with 640x480 resolution..

Lucas & Kanade's method is implemented in hardware by Diaz et al. two times in 2004 [19] and in 2008 [18]. In [19], they claim to achieve a performance of processing 320x240 pixels images at 24 fps operating in real-time. Their implementation yield 100% density because of the absence of error thresholding. However, the resultant flow field has a high average angular error rate of 18° where software implementation can yield only 4.3° on the same image sequence. In [18], they present an improved version of their previous work which is capable of processing 800x600 images at 170 fps. They also present a detailed accuracy analysis. They achieve an angular error rate of 18.3° with 92% density and 3.5° with 36% density.

There are also alternative computation platforms other than FPGAs that can be used for high performance optical flow computation. GPUs (Graphical Processing Units) are one of these platforms. There are a few studies in literature that reports the performance of optical flow computation on GPUs. A study on optical flow computation using GPU is given in [33]. They implement a tensor based method and achieve a 2.8 times speed-up compared to a Pentium4 2.8 GHz PC implementation. However, there is no discussion on accuracy of the computed flow field. The only GPU implementation of Horn & Schunck's method is presented in [27]. They use multiresolution method with 2 levels. The computation of 316x252 images takes 443ms in multi-scale and 3ms

in single-scale. In [16], there is a comparison between an FPGA and a GPU implementation of optical flow computation. They use a tensor based optical flow method and claim a processing 320x240 images at 538 frames per second. They discuss the advantages and drawbacks of GPUs over FPGAs. The most important drawback of FPGAs is the complexity of design process. They claim that FPGAs require a 12x more development time. However, GPUs consume much more power than FPGAs and requires a host PC for operation where FPGAs can be placed on stand-alone platforms. Therefore, the high power consumption and high space occupation properties of GPUs make them unfeasible to be utilized on mobile robotic platforms. A more detailed version of this study in [16] can be found in the thesis work given in [13].

As far as we know, there is no work presenting the accuracy, power consumption and logic resource usage of Horn & Schunck's method implemented on FPGA. Mentioned studies on this method concentrates on the computation speed. However, it is known that, it is disadvantages to implement floating point operations on FPGAs[25]. The workaround is often to use fixed point operations which decreases the accuracy of the computations. Along with the speed, accuracy is also a key parameter to determine the feasible application areas of the presented method.

#### 1.3 Contributions

The lack of a hardware that is capable of processing optical flow in real time is a factor that prevents the robotics research to utilize many studies presented in computer vision literature. Having the ability to implement available computer vision techniques in robotic platforms has a high potential to achieve great improvements in robotics research.

Unfortunately, it is not possible to obtain the required hardware off the shelf. Although there are some hardware mpeg coding chips that compute optical flow for video compression applications, they do not allow hardware reconfiguration to adapt to new situations. There is no such configurable commercial product for the time being as far as we know. In the literature, we came across a few universities that claim to design their own hardware but none of them provide the source HDL code for their design. Even if they provided the source code, it is still not easy to implement the

code unless having the same or similar FPGA hardware. At the end of this thesis work, we obtain a high performance hardware with low power consumption that is capable of providing over-realtime optical flow data to be used on our current robotic platform SensoRHex and other robotic platforms to be used further on.

As far as we know, none of the presented hardware implementations of Horn & Schunck optical flow in literature, report the accuracy, power consumption and resource usage of their hardware. There is an absence of this kind of knowledge in the literature. This thesis work also provides us the mentioned information. We think that the achievements of this thesis work will be appreciated by the related research society and so have a high potential for publication of these results.

#### 1.4 Outline of the Thesis

In this chapter, we stated our motivation for this thesis work and a literature survey on the related publications. The contributions of this thesis work is presented. We finish this chapter after giving an outline of the thesis. The reminder of this thesis is organized as follows.

Chapter 2 presents a brief summary on the background of optical flow computation. We explain the mathematical derivation of the optical flow algorithm used and its numerical computation on digital hardware.

Chapter 3 explains the hardware requirements to implement a computer vision algorithm on an FPGA. We also introduce the properties of the FPGA platform used to implement the designed hardware and a short description of the FPGA structure. Then we complete this chapter with explaining the development tools utilized and the top down design methodology used to design the proposed hardware on FPGA.

Chapter 4 describes the complete hardware design of the proposed system in details. We also discuss the design alternatives and the selected approaches with providing the reasons.

Chapter 5 presents the performance analysis of the proposed design by stating the performance measures. The designed system is tested with some of the available

test sequences that are frequently used for performance evaluations of the optical flow techniques in literature. The results obtained from FPGA implementation are compared with the PC implementation of the same algorithm.

Finally, we conclude this thesis study in Chapter 6, by presenting our comments on the results and discussing the future plans and the possible improvements and modifications that can be done on the proposed design. We also summarize some important points learned from this research.

#### CHAPTER 2

## BACKGROUND ON OPTICAL FLOW COMPUTATION

#### 2.1 Optical Flow

Optical flow is defined as the distribution of apparent velocities of brightness patterns in an image[23]. This motion can be induced due to the relative movement of the objects in the scene or the observer(camera) itself. To determine the motion flow of a scene, it is needed an image sequence including at least two image frames taken from a camera consecutively of that scene. However, an image of a scene is just a 2D representation of a 3D world. Since the optical flow calculation is based on the 2D images, the computed optical flow field is a projection of 3D motion field of the scene. There are a number of methods presented in literature to compute the optical flow vector field on 2D images. Within this chapter, we give a brief summary on the background of optical flow computation and the Horn & Schunck's method [23] which is implemented on hardware.

#### 2.2 Differential Optical Flow Computation Methods

There are various methods for computation of optical flow as mentioned in Section 1.2. Differential methods are rather popular among those methods. They depend on the use of spatio-temporal intensity gradients. They have relatively less computational complexity over other methods and provide high density optical flow vectors with a reasonable error rate. These methods are also suitable for high performance FPGA

hardware implementations. The computations can be done using fixed point representations with small word lengths. They can be implemented using parallel and pipelined structures which yields a high throughput. In this thesis work, we use a well known differential method for hardware implementation which is proposed by Horn & Schunck[23]. We follow the suggestions of Horn & Schunck's original paper on numerical computation of the algorithm.

#### 2.2.1 Horn-Schunck Optical Flow Computation Algorithm

#### 2.2.1.1 Pre-Assumptions

The differential optical flow methods have some pre-assumptions. The first main assumption is the so called "brightness constancy" which comes from the nature of the problem itself. This assumption states that the apparent brightness of the moving objects in the scene are approximately constant under motion for at least a short duration over time. If this assumption is violated, the correspondence of a pixel in the first image can not be matched correctly in the second image, since it does not have the same brightness as before anymore.

The second assumption requires the motion flow not to be large between consecutive frames. This means the changes should be gradual over time. The nature of the problem requires the brightness patterns in the first image to be found inside the second image also. However, the maximum displacement allowed, changes from algorithm to algorithm. Differential methods generally require the motion vectors to have very small velocities. For cases when the motion vectors have large velocities, multiresolution method can be used which computes flow vectors at different scales.

Generally the optical flow algorithms including the one we will utilize takes the input images to be processed to have pixel values represented with grayscale levels. Generally, the brightness data has enough information about the scene to be able to calculate the optical flow field. So the input image data is assumed to be represented by pixel brightness values.

#### 2.2.1.2 Optical Flow Constraint Equation

Starting from the brightness constancy assumption, the constancy of image brightness pattern over time can be formulated as,

$$\frac{dE}{dt} = 0\tag{2.1}$$

Here E(x, y, t) denotes the image brightness at pixel location (x, y) at time t. If we consider a patch of brightness pattern that moves  $\delta x$  horizontally and  $\delta y$  vertically along a time period  $\delta t$ , the following equation holds for brightness constancy. Using chain rule, equation (2.1) can be rewritten as,

$$E(x, y, t) = E(x + \delta x, y + \delta y, t + \delta t)$$

(2.2)

The Taylor series expansion about the point (x, y, t) is expressed in equation (2.3).

$$E(x, y, t) = E(x, y, t) + \delta x \frac{\partial E}{\partial x} + \delta y \frac{\partial E}{\partial y} + \delta t \frac{\partial E}{\partial t} + HOT$$

(2.3)

For a sufficiently small  $\delta t$ , higher order terms can be neglected. Rearranging the equation accordingly yields,

$$\frac{\partial E}{\partial x} \frac{dx}{dt} + \frac{\partial E}{\partial y} \frac{dy}{dt} + \frac{\partial E}{\partial t} = 0$$

(2.4)

If we denote optical flow vectors as,

$$u = \frac{dx}{dt} \qquad v = \frac{dy}{dt} \tag{2.5}$$

and partial derivatives of E as,

$$E_x = \frac{\partial E}{\partial x}$$

$E_y = \frac{\partial E}{\partial y}$   $E_t = \frac{\partial E}{\partial t}$  (2.6)

then equation (2.4) can be rewritten as,

$$E_x u + E_y v + E_t = 0 (2.7)$$

Here we get the so called optical flow constraint equation,

$$(E_x, E_y)(u, v) = -E_t \tag{2.8}$$