## FABRICATION OF SILICON NANOWIRES BY ELECTROLESS ETCHING AND INVESTIGATION OF THEIR PHOTOVOLTAIC APPLICATIONS

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY BARIŞ ÖZDEMİR

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN METALLURGICAL AND MATERIALS ENGINEERING DEPARTMENT

JULY 2011

Approval of the thesis:

#### FABRICATION OF SILICON NANOWIRES BY ELECTROLESS ETCHING AND INVESTIGATION OF THEIR PHOTOVOLTAIC APPLICATIONS

submitted by **BARIŞ ÖZDEMİR** in partial fulfillment of the requirements for the degree of **Master of Science in Metallurgical and Materials Engineering Department, Middle East Technical University** by,

Prof. Dr. Canan Özgen \_\_\_\_\_ Dean, Graduate School of **Natural and Applied Sciences**

Prof. Dr. Tayfur Öztürk Head of Department, **Metallurgical and Materials Engineering**

Assist. Prof. Dr. Hüsnü Emrah Ünalan Supervisor, **Metallurgical and Materials Eng. Dept., METU\_\_\_\_\_**

Prof. Dr. Rașit Turan Co-Supervisor, **Physics Dept., METU**

#### **Examining Committee Members:**

Prof. Dr. Çiğdem Erçelebi Department of Physics, METU

Assist. Prof. Dr. Hüsnü Emrah Ünalan Department of Metallurgical and Materials Engineering, METU

Prof. Dr. Raşit Turan Department of Physics, METU

Prof. Dr. Tayfur Öztürk Department of Metallurgical and Materials Engineering, METU

Assist. Prof. Dr. Eren Kalay Department of Metallurgical and Materials Engineering, METU

Date: 20.07.2011

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Barış ÖZDEMİR

Signature :

#### ABSTRACT

## FABRICATION OF SILICON NANOWIRES BY ELECTROLESS ETCHING AND INVESTIGATION OF THEIR PHOTOVOLTAIC APPLICATIONS

ÖZDEMİR, Barış

M.Sc., Department of Metallurgical and Materials Engineering

Supervisor: Assist. Prof. Dr. Hüsnü Emrah ÜNALAN

Co-Supervisor: Prof. Dr. Rașit TURAN

July 2011, 107 pages

Silicon is the most important semiconducting material for optoelectronics owing to its suitable and tunable physical properties. Even though there are several alternatives, silicon based solar cells are still the most widely produced and commercially feasible system. Extensive efforts have been spent in order to increase the efficiency and decrease the cost of these systems. The studies that do not focus on replacement of the semiconducting material, mostly concentrate on the developments that could be brought by nanotechnological approaches. In this aspect, utilization of silicon nanowires has been predicted to improve the efficiency of the silicon based solar cell technology. Moreover, besides solar cells, silicon nanowires have been investigated for many other electronic systems such as thermoelectrics, light emitting diodes, biological/chemical sensors, photodetectors and lithium ion batteries. Therefore, production of silicon nanowires through a cost-effective and well controlled method could make important contributions to many fields.

In this thesis, electroless etching method, which is a novel and solution based method enabling vertically aligned silicon nanowire array fabrication over large areas, is investigated. A detailed parametric study resulting in a full control over the resultant nanowire morphology is provided. The parameters affecting the structure have been determined as etching time, solution temperature, solution concentration, pressure and starting wafer characteristics. The results show that electroless etching method could replace the conventional silicon nanowire fabrication methods. It was shown that specific nanowire lengths for any application, can be obtained simply by adjusting the parameters of electroless etching system.

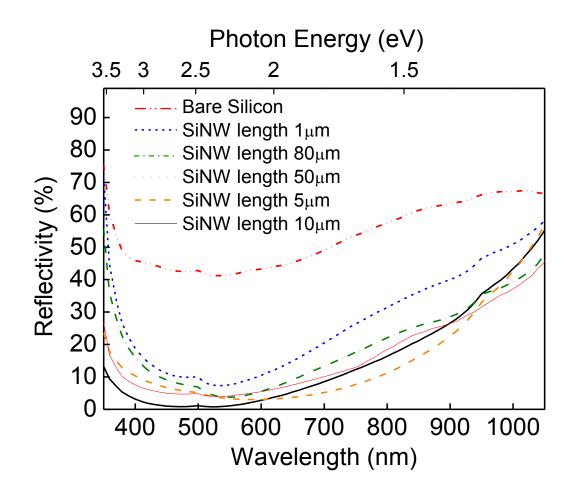

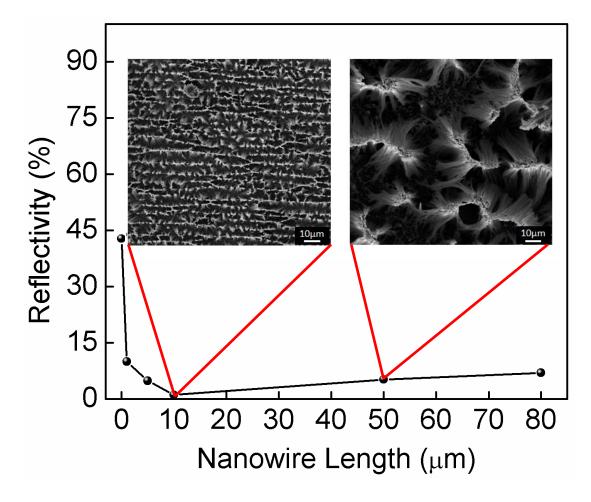

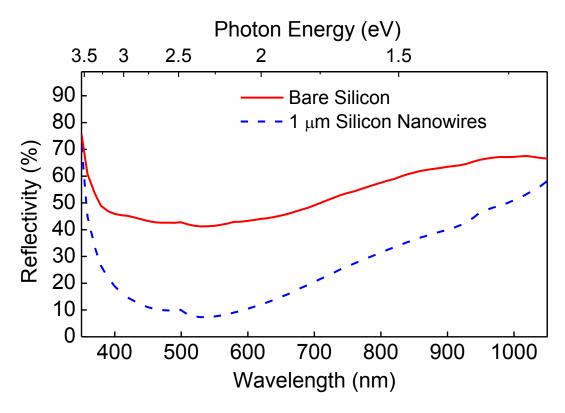

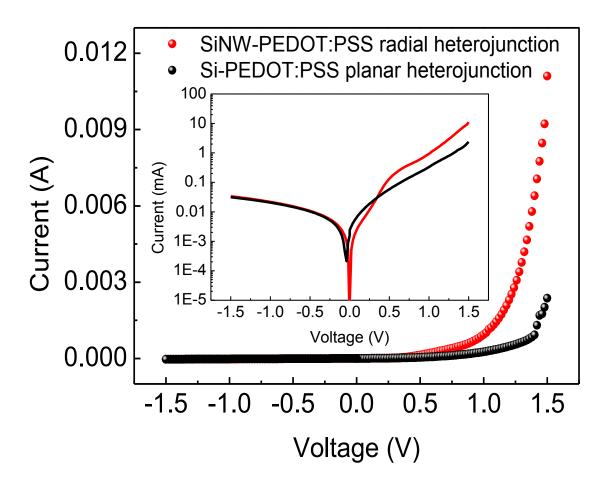

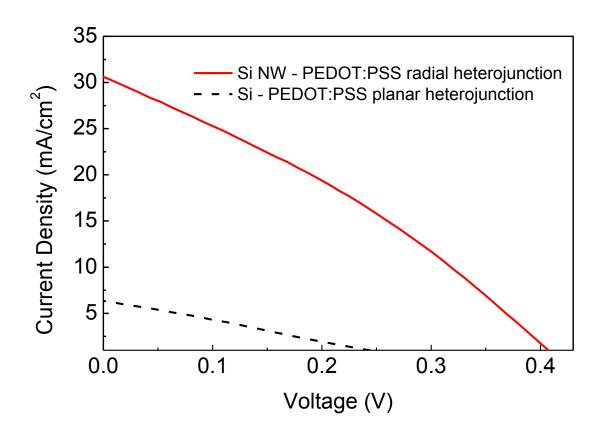

One of the most crucial features of vertically aligned silicon nanowire arrays is their remarkable antireflective properties. The optical reflectivity measurements showed that 42% reflectivity of pristine polished silicon wafer decreases down to 1% following fabrication of silicon nanowire arrays on their surface. This unique characteristic reveals that these nanowires could be used as antireflective surfaces in solar cells. Moreover, it was determined that p-n heterojunctions that are formed by silicon nanowires, namely radial heterojunctions, would yield higher efficiencies compared to planar heterojunctions because of the dramatic increase in the charge carrier collection efficiency and orthogonal photon absorption. On this subject, ntype silicon nanowire arrays were fabricated by electroless etching followed by drop Poly(3,4-ethylenedioxythiophene)poly(styrenesulfonate) (PEDOT:PSS) casting organic layer on these nanowires as the complementary layer, forming the radial heterojunction. The energy conversion efficiency of silicon nanowire / PEDOT: PSS device was found as 5.30%, while planar silicon / PEDOT: PSS control device displayed only 0.62% efficiency. Developments and optimizations in both the electroless etching method and solar cell models could lead to important developments in photovoltaic industry.

Keywords: silicon nanowires, radial heterojunction solar cells, PEDOT:PSS

# ÖZ

## SİLİSYUM NANOTELLERİN ELEKTROKİMYASAL DAĞLAMA İLE ÜRETİMİ VE GÜNEŞ PİLİ UYGULAMALARININ ARAŞTIRILMASI

ÖZDEMİR, Barış

Yüksek Lisans, Metalurji ve Malzeme Mühendisliği Bölümü Tez Yöneticisi: Yrd. Doç. Dr. Hüsnü Emrah ÜNALAN Ortak Tez Yöneticisi: Prof. Dr. Raşit TURAN

#### Temmuz 2011, 107 sayfa

Silisyum, oldukça uygun ve kolaylıkla değiştirilebilir fiziksel özellikleri sayesinde optoelektronik alanı için en önemli konumda olan yarıiletken malzemedir. Alternatif malzemeler geliştirilmiş olmasına rağmen, silisyum bazlı güneş pilleri halen en yaygın olarak kullanılan ve ticari anlamda en uygulanabilir sistemlerdir. Güneş pillerinin verimliliğinin artırılması ve maliyetinin düşürülmesi üzerine oldukça yoğun çalışmalar yapılmaktadır. Bu sistemlerin temel yarıiletken malzemesini değiştirmeyi amaçlamayan çalışmalar genellikle nanoteknolojik yaklaşımlardan yararlanmayı amaçlamışlardır. Bu bağlamda, silisyum nanotellerin güneş pillerinin verimliliğini artırabileceği öngörülmüştür. Ayrıca, güneş pillerine ek olarak, silisyum nanotellerin termoelektrik sistemler, ışık yayan diyotlar, biyolojik/kimyasal sensörler, fotodedektörler ve lityum iyon pilleri gibi birçok elektronik sistemde de kullanımları araştırılmaktadır. Bu gelişmeler, silisyum nanotellerin ucuz ve kontrollü bir şekilde üretilebildiği durumlarda bir çok alanda önemli gelişmeler sağlanabileceği sonucuna işaret etmektedir.

Bu tez çalışmasında, dik olarak hizalanmış nanotellerin geniş alanlarda üretilebilmesine olanak sağlayan, oldukça yeni ve çözelti bazlı bir yöntem olan elektrokimyasal dağlama yöntemi araştırılmıştır. Ortaya çıkacak nanotel morfolojisinin kontrol edilebilirliğini gösteren detaylı bir parametrik calışma yapılmıştır. Bu parametreler zaman, çözelti sıcaklığı, çözelti konsantrasyonu, basınç ve başlıngıç siliyum altlığın özellikleri olarak belirlenmiştir. Elde edilen sonuçlar elektrokimyasal dağlama yönteminin önceki çalışmalarda faydalanılan klasik yöntemler yerine tercih edilebileceğini göstermiştir. Her uygulama için gerekli olan belirli nanotel boylarının elektrokimyasal dağlama yönteminin parametrelerinin ayarlanmasıyla elde edilebileceği ortaya konulmuştur.

Dik olarak hizalanmış nanotellerin en önemli özelliklerinden biri mükemmel optik yansıtmazlık özellikleridir. Başlangıç silisyum altlığı %42 optik yansımaya sahipken, üzerinde nanotel oluşturulduktan sonra bu değer %1'e düşmüştür. Bu özellik silisyum nanotellerin yansıtmaz yüzeyler olarak güneş pillerinde kullanılabileceğini göstermiştir. Ayrıca, silisyum nanoteller ile oluşturulan, radyal farklı tip p-n eklemlerinin düzlemsel farklı tip p-n eklemlerine göre çok daha yüksek verimliliğe sahip oldukları belirlenmiştir. Bu konuda, n-tipi silisyum nanoteller üzerine p-tipi PEDOT:PSS damlatılarak kaplanması ile radyal farklı tip eklemler oluşturulmuştur. Bu radyal eklemli aygıtların enerji dönüşüm verimlilikleri %5.30 olarak elde edilirken, aynı koşullarda üretilen düzlemsel kontrol cihazı sadece %0.62 verimliliğe sahiptir. Hem elektrokimyasal dağlama yönteminde hem de güneş pili modellerinde yapılacak iyileştirmeler ve gelişmeler güneş pili endüstrisinde önemli gelişmeler sağlayabilecektir.

Anahtar Kelimeler: silisyum nanoteller, radyal değişik tür eklemli güneş pilleri, PEDOT:PSS

To My Family...

## ACKNOWLEDGEMENTS

This thesis is an interdisciplinary work between departments of Physics and Metallurgical and Materials Engineering in METU, and financed by GÜNAM and METU-DAP. Also, I would like to acknowledge TÜBİTAK for their financial support in the last year of this graduate study.

I would like to thank my advisor Assist. Prof. Dr. Emrah Ünalan for his support and guidence throughout the whole time I have worked on this project and Prof. Dr. Raşit Turan for giving me the opportunity to occupy all the facilities in the Physics Dept. and his support for my studies. I also would like to thank Hülya Yalçın, Serkan Yılmaz, Güher Kotan and Assist. Prof. Dr. Eren Kalay for spending infinite hours of SEM/TEM sessions, Dr Yan Zhang for field emission measurements and I acknowledge all the great facilities in Metallurgical and Materials Engineering Dept.

I owe my deepest gratitude to my lab-mates and dearest friends Şahin Coşkun, Ayşegül Afal, Elif Selen Ateş, Burcu Aksoy and Şeyda Küçükyıldız for their infinite support, patience and kindness. I will never forget the awesome time we have had together and I feel very lucky to get to know such great people. I feel the need to single out Mustafa Kulakcı, This thesis would be a very different thing had I not been sent to the basement of Physics Department and introduced to him two years ago. His diligence, determination, discipline and knowledge have been an inspiration for me. I would not have been able to accomplish this task without his invaluable contributions. I also appreciate the great moral support from Başak Aysin, Barış Çeltikçi, Halil İbrahim Yavuz, Evren Tan, Berk Seçen, Mehmet Can Akgün, Olgu Demircioğlu, Onur Can Sert, Egemen Çam, Furkan Baltaşı and all my friends in my department who have helped and supported me all along.

And finally, I would like to thank my parents, sister, grandmother and Damla...I can not describe my feelings with any words, your love is the most valuable thing I have... Thank you for everything, thank you for always being there for me.

# TABLE OF CONTENTS

| ABSTRACT          | iv   |

|-------------------|------|

| ÖZ                | vi   |

| ACKNOWLEDGEMENTS  | ix   |

| TABLE OF CONTENTS | X    |

| LIST OF TABLES    | xiii |

| LIST OF FIGURES   | xiv  |

# CHAPTERS

| 1. | INTRODUCTION                                                             | . 1 |

|----|--------------------------------------------------------------------------|-----|

| 2. | SILICON NANOWIRE FABRICATION BY ELECTROLESS ETCHING.                     | 6   |

|    | 2.1.1. Features of Nanowires                                             | 6   |

|    | 2.1.2 Conventional Silicon Nanowire Synthesis Methods                    | 12  |

|    | 2.1.2.1. Vapor Deposition                                                | 13  |

|    | 2.1.2.2. Vapor-Liquid-Solid (VLS) Method                                 | 14  |

|    | 2.1.2.3. Template Assisted Growth                                        | 15  |

|    | 2.1.3. Electroless Etching Method                                        | 18  |

|    | 2.1.3.1. History and Development of Electroless Etching Method           | 18  |

|    | 2.1.3.2. Electroless Etching Mechanism and Reactions                     | 19  |

|    | 2.1.3.3. Comparison of Electroless Etching with the Conventional Methods | 22  |

| 2  | 2.2. Experimental Details                                                | 23  |

| 2  | 2.3. Nanowire Characterization Methods                                   | 27  |

|    | 2.3.1. Scanning Electron Microscopy (SEM)                                | 27  |

|    | 2.3.2. Transmission Electron Microscopy (TEM)                            | 27  |

| 2.3.3. Optical Reflectivity Measurements                                   | . 27 |

|----------------------------------------------------------------------------|------|

| 2.3.4. Field Emission Measurements                                         | . 28 |

| 2.4. Results                                                               | . 29 |

| 2.4.1. Determination of the Electroless Etching Parameters                 | . 29 |

| 2.4.1.1. Solution Concentration                                            | . 29 |

| 2.4.1.2. Time                                                              | . 30 |

| 2.4.1.3. Temperature                                                       | . 34 |

| 2.4.1.4. Pressure                                                          | . 36 |

| 2.4.1.5. Silicon Wafer Characteristics                                     | . 37 |

| 2.4.1.5.1. Doping Type, Crystallographic Orientation and Resistivity       | . 37 |

| 2.4.1.5.2. Crystallinity                                                   | . 39 |

| 2.4.1.5.3 Polishing                                                        | . 40 |

| 2.4.1.6. Mixing, Microwave Heating and Pre-Coating                         | . 43 |

| 2.4.2. TEM Analysis of Silicon Nanowires Fabricated by Electroless Etching | ; 45 |

| 2.4.3. Optical Reflectivity of Silicon Nanowires Fabricated by Electroless |      |

| Etching                                                                    | . 47 |

| 2.4.4. Field Emission Characteristics of Silicon Nanowires                 | . 52 |

|                                                                            |      |

| 3. SILICON NANOWIRE / PEDOT:PSS HETEROJUNCTION SOLAR                       |      |

| CELLS                                                                      | . 56 |

| 3.1. Introduction                                                          | . 56 |

| 3.1.1. Historical Survey                                                   | . 56 |

| 3.1.2. The Current Status of Solar Cell Technology                         | . 57 |

| 3.1.3. Solar Cell Characteristics                                          | . 59 |

| 3.1.3.1. Solar Spectrum                                                    | . 60 |

| 3.1.3.2. Solar Cell Parameters                                             | . 61 |

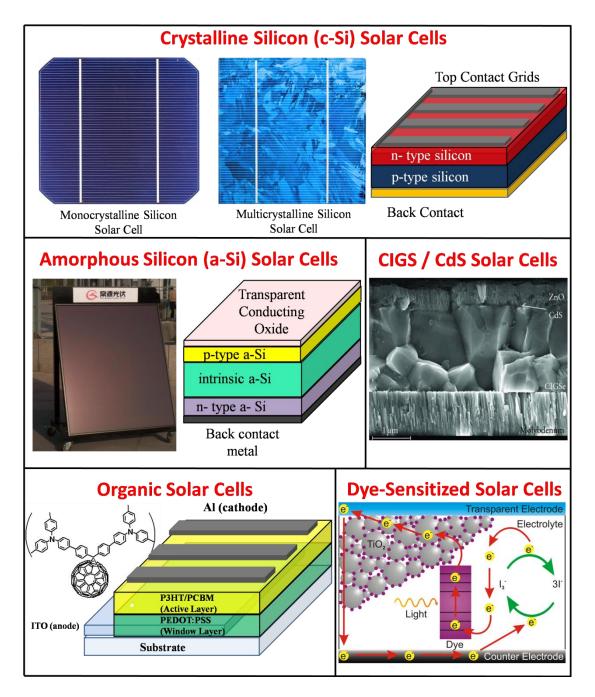

| 3.1.4. Different Solar Cell Models                                         | . 65 |

| 3.1.4.1. Single-crystalline and Multicrystalline Silicon Solar Cells       | . 65 |

| 3.1.4.2. Thin Film Solar Cells                                             | . 65 |

| 3.1.4.3. Novel Solar Cell Designs                                          | . 66 |

| 3.1.4.4. Heterojunction Solar Cells                                        | 68   |

|                                                                            | . 00 |

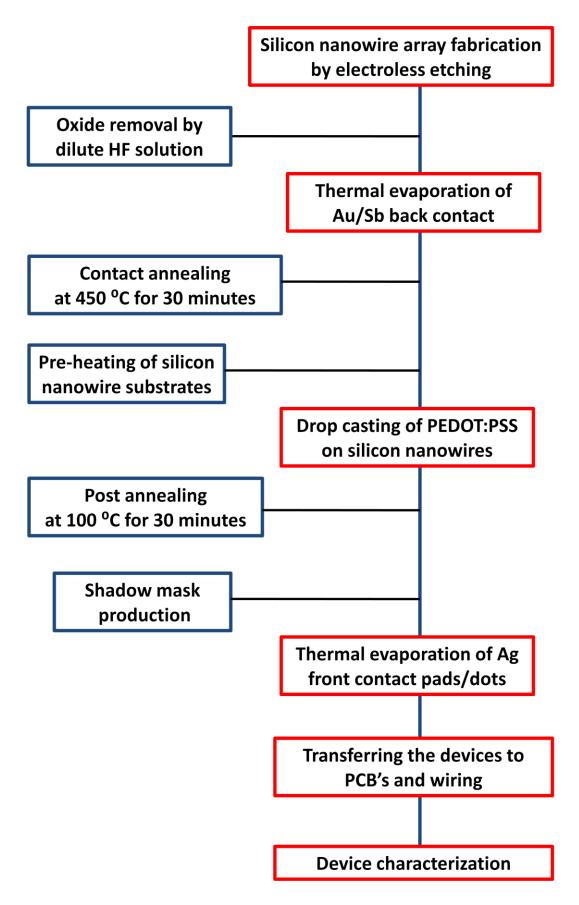

| 3.2. Experimental Details                                                  |      |

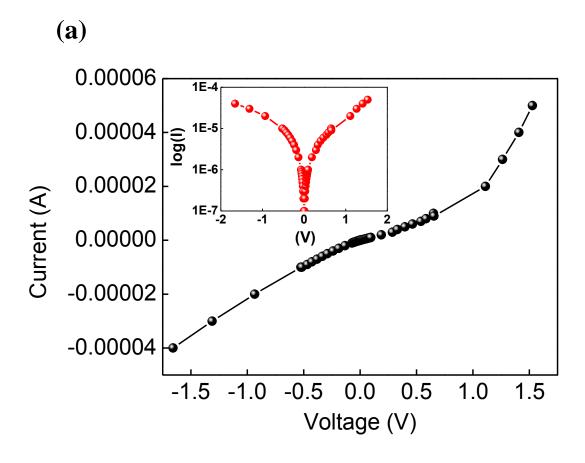

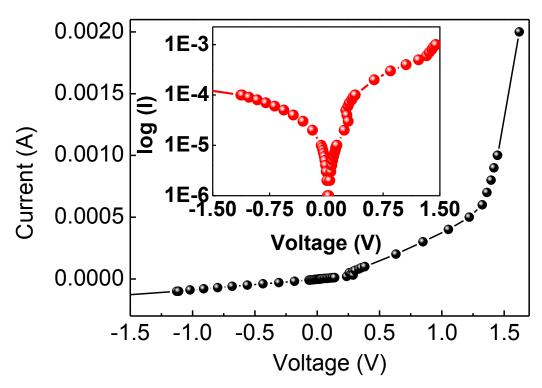

| 3.3.1. Scanning Electron Microscopy (SEM)                  | 77 |

|------------------------------------------------------------|----|

| 3.3.2. Current-Voltage (I-V) Measurements                  | 77 |

| 3.3.3. External Quantum Efficiency Measurements            | 77 |

| 3.4. Results                                               | 78 |

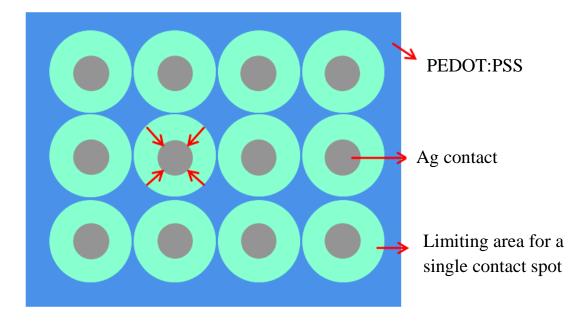

| 3.4.1. Silicon Nanowire/PEDOT:PSS Heterojunction Formation | 78 |

| 4. CONCLUSIONS AND FUTURE RECOMMENDATIONS                  | 97 |

| 4.1. Conclusions                                           | 97 |

| 4.2. Future Recommendations                                | 98 |

| REFERENCES                                                 | 00 |

# LIST OF TABLES

| Table 3.1. Annealing temperature, coating procedure and the resulting n | resistivities of |

|-------------------------------------------------------------------------|------------------|

| silicon nanowire / PEDOT:PSS devices.                                   |                  |

| Table 3.2. Solar cell characteristics of silicon nanowire/PEDOT:PSS so  | olar cells with  |

| different silicon nanowire lengths                                      |                  |

## **LIST OF FIGURES**

| Figure 2.1. Representative schemes of nanostructured materials, which are grouped |

|-----------------------------------------------------------------------------------|

| according to their dimensionality7                                                |

|                                                                                   |

| Figure 2.2. Applications of silicon nanowires other than solar cells              |

| Figure 2.3. Silicon nanowire fabrication methods                                  |

|                                                                                   |

| Figure 2.4. Schematic of a typical CVD reactor                                    |

|                                                                                   |

| Figure 2.5. Representative sketch showing the stages of VLS growth mechanisms of  |

| silicon nanowires                                                                 |

|                                                                                   |

| Figure 2.6. Schematic representation of silicon nanowire production using bottom  |

| imprint method16                                                                  |

|                                                                                   |

| Figure 2.7. SEM image of DRIE etched silicon nanowires                            |

| Figure 2.8. The representative scheme showing nanowire formation mechanism        |

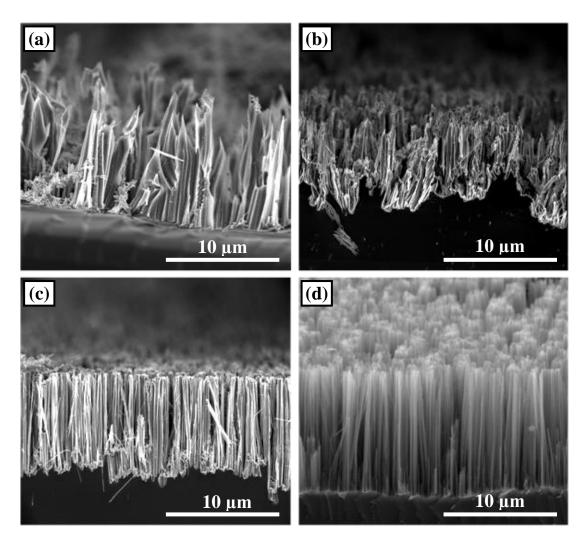

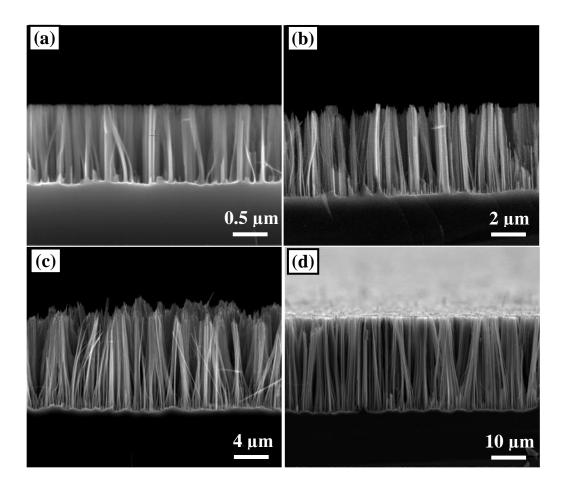

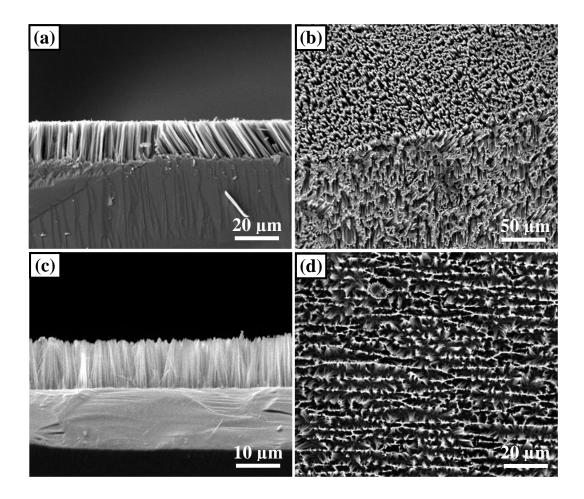

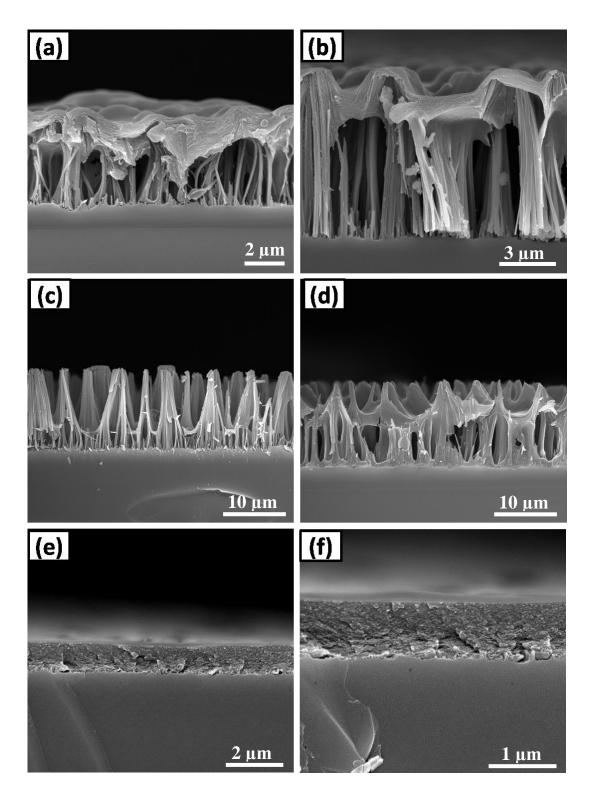

Figure 2.14. Cross-sectional SEM images of the vertically standing silicon nanowire arrays obtained by electroless etching at  $40^{\circ}$ C in a solution containing 4.6 M HF / 0.02 M AgNO<sub>3</sub> for (a) 8 minutes, (b) 40 minutes, (c) 120 minutes and (d) 360 minutes.

Figure 2.27. Nanowire length dependent reflectivity values (measured at 500 nm) Inset shows the relative top-view SEM images of corresponding silicon nanowires.49

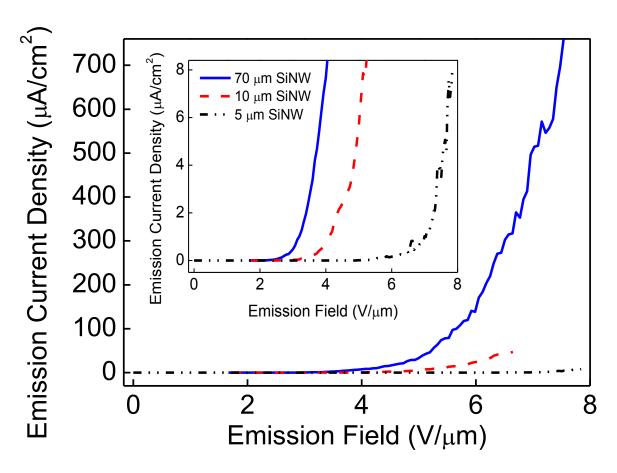

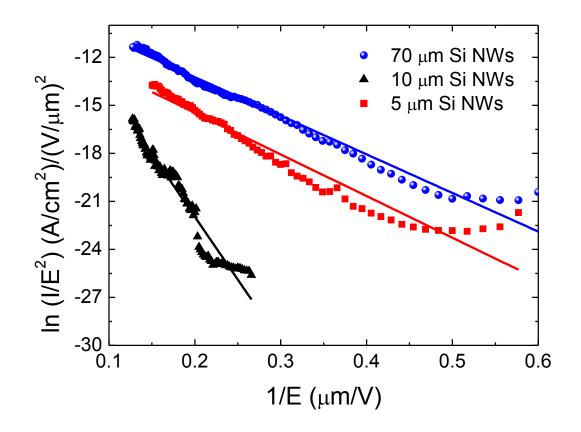

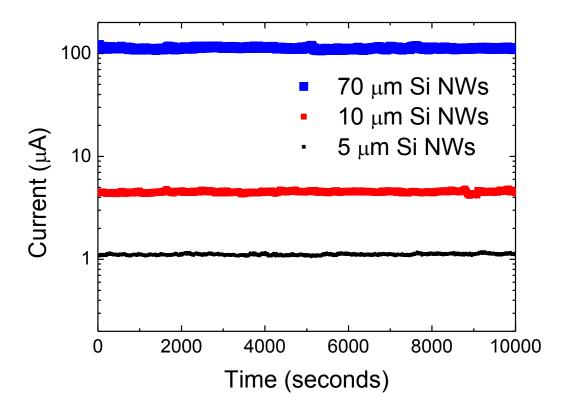

| Figure 2.30. Fowler-Nordheim fit of the emission field dependent current density54                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.31. Emission current stability of silicon nanowires                                                                                              |

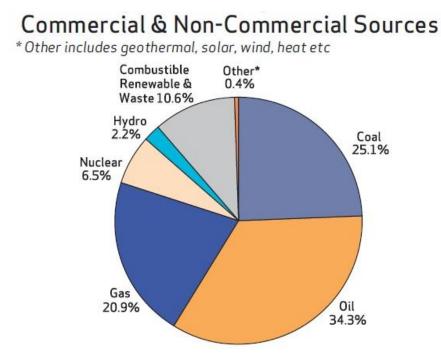

| Figure 3.1. The pie chart revealing the role of each energy resource by their energy percentages over the total energy supplied                           |

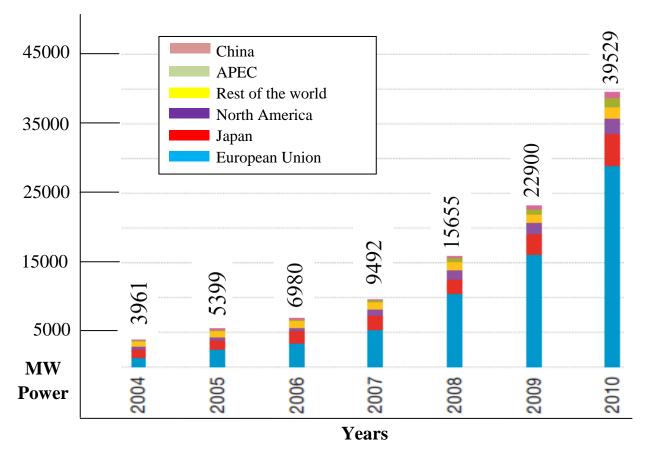

| Figure 3.2. Historical development of global cumulative PV power installed per region                                                                     |

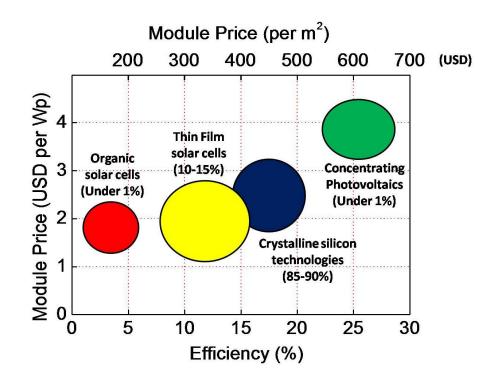

| Figure 3.3. Performance and cost comparison of commercially available photovoltaic technologies                                                           |

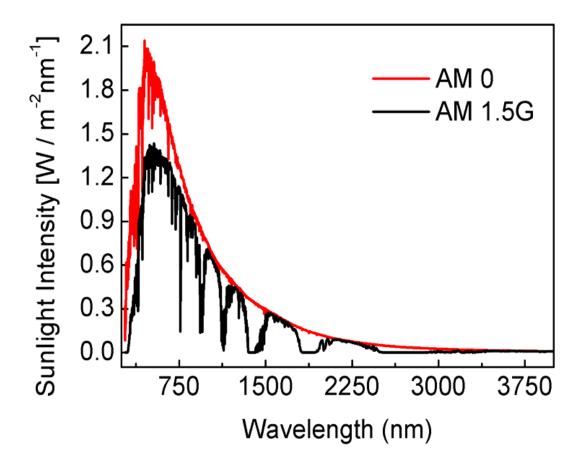

| Figure 3.4. AM 0 and AM 1.5G solar spectrum60                                                                                                             |

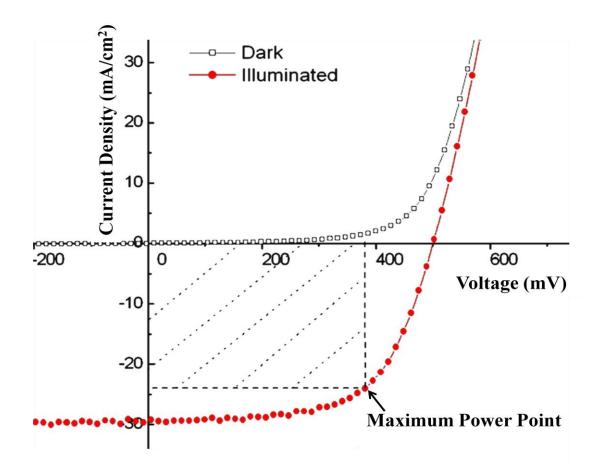

| Figure 3.5. Typical current-voltage curve of a diode in dark and illuminated condition. Shaded area represents the maximum power generated by the diode63 |

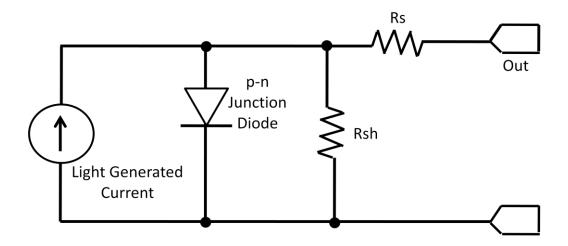

| Figure 3.6. Equivalent circuit model of a solar cell                                                                                                      |

| Figure 3.7. Structures of various types of solar cells                                                                                                    |

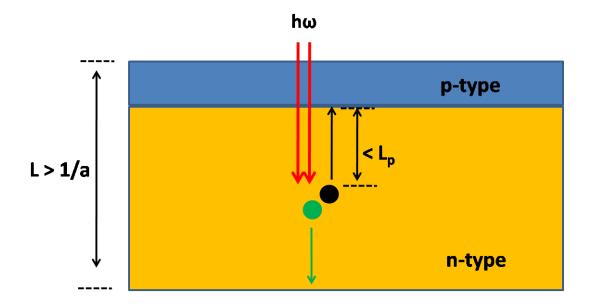

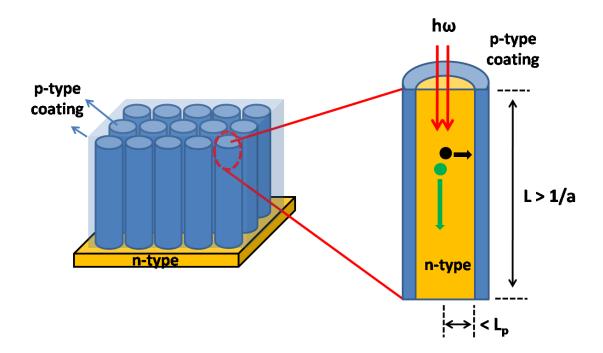

| Figure 3.8. Schematic of a planar heterojunction solar cell                                                                                               |

| Figure 3.9. Schematic showing the structure and carrier diffusion distance and directions of radial heterojunction solar cells70                          |

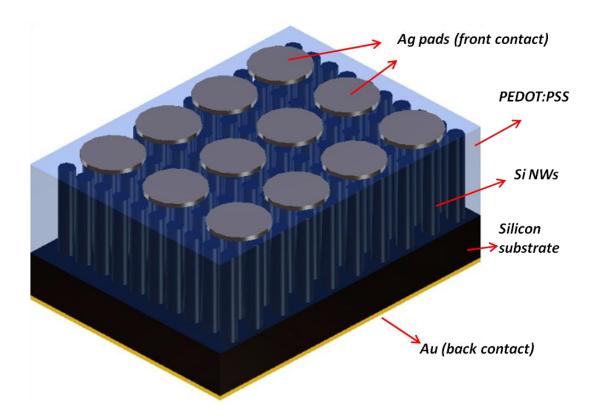

| Figure 3.10. Schematic of silicon nanowire/PEDOT:PSS hybrid heterojunction solar cells                                                                    |

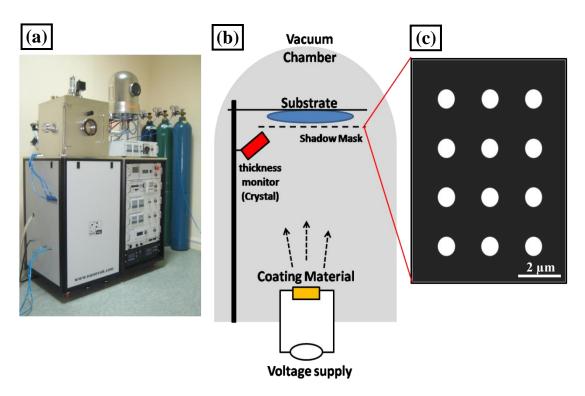

| Figure 3.11 (a) Thermal evaporator used for metallization (b) The representative                                                                          |

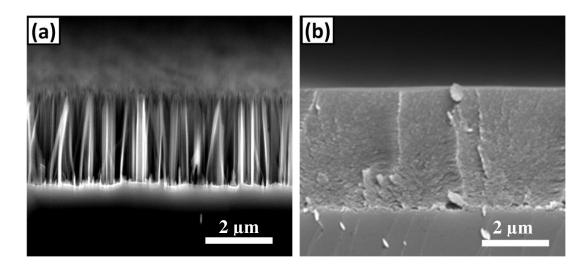

Figure 3.14. Cross-sectional SEM images of first set of silicon nanowire-PEDOT:PSS heterojunctions in (a) – (d) and optimized samples in (e) and (f). ...... 80

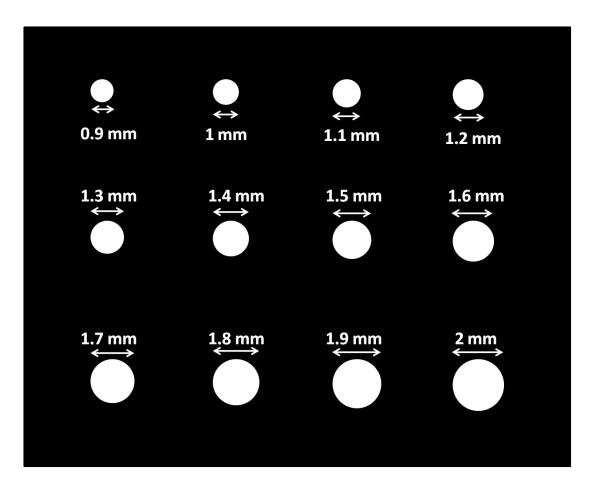

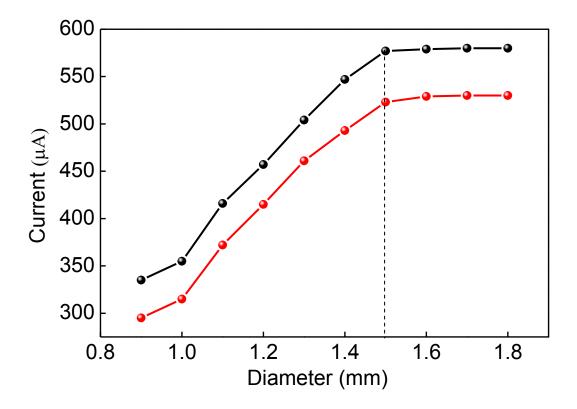

Figure 3.21. The current change versus the diameter of the illuminated region.......90

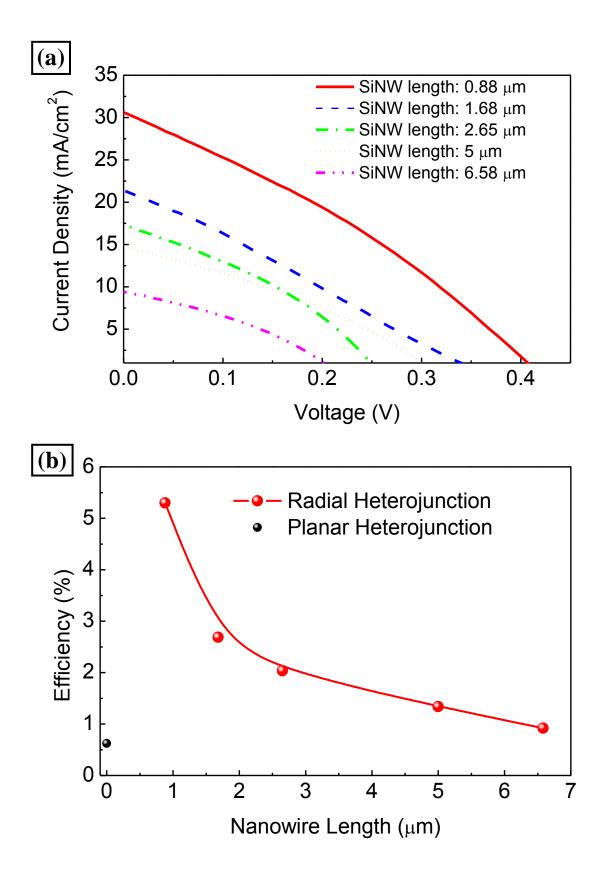

| Figur   | e 3.23. | Current   | density-volta | ge grapl  | n of | radial | and | planar | heterojunction | solar |

|---------|---------|-----------|---------------|-----------|------|--------|-----|--------|----------------|-------|

| cells o | obtaine | d under A | AM 1.5G sim   | ulated li | ght. | •••••  |     |        |                | 91    |

| Figure  | 3.24. | Silicon   | nanowire   | length  | dependent | (a) | current-voltage | characteristics |

|---------|-------|-----------|------------|---------|-----------|-----|-----------------|-----------------|

| and (b) | photo | voltaic o | conversion | efficie | ncy       |     |                 |                 |

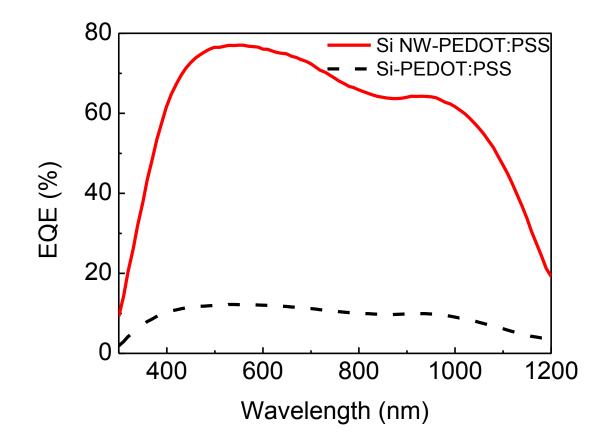

Figure 3.25. EQE measurements of radial and planar heterojunction solar cells. ..... 96

## **CHAPTER 1**

## **INTRODUCTION**

There are three major global problems that coincide with each other; the rapid increase in the world's energy demand, insufficient petroleum based energy sources and emission of the harmful fossil fuel products that causes major pollution and health problems. These facts have directed researchers to develop systems that serve to the energy demand utilizing renewable energy sources. Among these alternatives, solar cell technology stands as the most practical and feasible one, as it is based on the direct conversion of the solar energy into electricity without the need of any moving or complex parts.

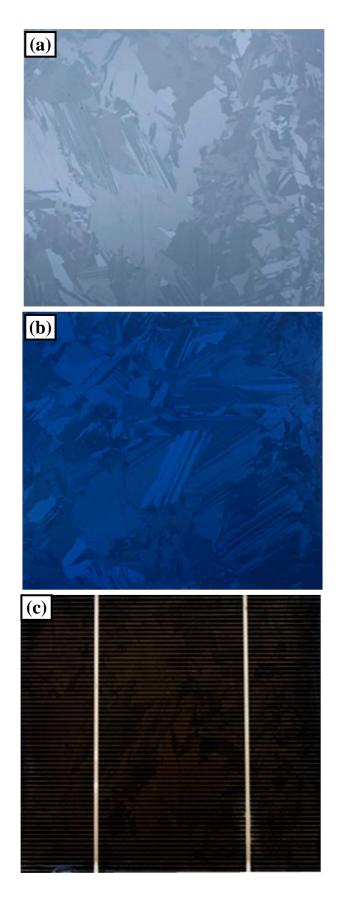

Following the discovery of the photovoltaic effect, many different types of solar cells have been produced and they are grouped according to their material types. Silicon, the most well-known semiconductor with a narrow band gap and tunable physical and electrical properties, has been the most feasible and commercially available material. Although silicon based solar cell systems outperform other systems with relatively high energy conversion efficiencies, these wafer based technologies require large amounts of investments. The equipments for high temperature doping processes are still expensive and these systems require high energy and labor inputs. Also, excessive amounts of materials are spent in a regular crystalline silicon based solar cell production procedure and post treatments. In order to increase the costeffectiveness of such systems, scientists focused on either new semiconducting materials, thereby completely new systems or the use of nanostructures and the strategy of quantum confinement leading to developments in the silicon based photovoltaic technology. Solar cells are classified into three categories, depending on their time of discovery and the type of materials they utilize. The first generation solar cells are crystalline silicon based conventional solar cells that has been studied over many years. The second generation systems have been gaining market share since 2008 and are based on thin film materials. This group of solar cells aims to use alternative material deposition techniques that avoid high temperature processing, decrease the production costs and minimize material use. They also enable use of flexible substrates. However, defective structures restrict them from performing as efficient as first generation solar cells. The most recent studies, namely third generation solar cells, are supposed to become high efficiency-low cost systems, but they have not been commercialized yet. Nanocrystalline silicon solar cells, dye sensitized solar cells, organic solar cells, multi-junction tandem solar cells and photoelectrochemical cells belong to this category. They aim to enhance poor electrical performance of second generation technologies, while maintaining very low production costs.

Nanotechnology is based on the reduction of the size of the materials down to nanoscale or changing the atomic structure of a material in nanoscale to increase its performance, both of which would then bring completely new characteristics. A material with at least one dimension below 100 nm is accepted as a nanomaterial (or nanostructured material). Nanomaterials can be fabricated through two approaches. First one is the bottom-up approach, where one uses atoms to assemble nanomaterial of interest. In the second method, called top down, bulk materials are refined down to nanomaterials using chemical or physical means. Application of nanomaterials in optoelectronics has been investigated in many studies. Especially over the last decade, silicon nanowires have drawn attention as they introduce unique optical and electrical properties to the systems they are utilized. It was also observed that their characteristics change depending on their morphologies, whether they are synthesized in horizontal networks, vertically standing arrays, stacked arrays with extremely high aspect ratios. Considering the fact that different applications would require different nanowire geometries, it is essential to produce them as accurately and precisely as possible.

Most of the researchers have preferred to employ vapor-liquid-solid (VLS) method for the synthesis of silicon nanowires. This is because VLS facilitates a full control

over the resultant nanowire structure. Other bottom-up techniques like physical vapor deposition and laser ablation were also used for the silicon nanowire synthesis. Although most of these methods have shown reliable results in terms of yielding desired nanowire structure, they all contain two important drawbacks, which are not only valid for silicon nanowire based fields, but also major concerns for many nanoscience related studies. The first one is high equipment costs and the second one is the area limitation. The basis for applying nanotechnological methods would be to improve the cost effectiveness of the electronic devices. Therefore, using such expensive set-ups for fabrication of nanomaterials would be in contrary to the starting motivation of this concept; unless an extremely large improvement in the performance of the electronic systems with nanowires is attained. The second issue, area limitation is another factor that would prevent commercial scale applications. Nanowires can only be fabricated on the substrates that are large enough to fit inside the chamber of the growth apparatus. Consequently, only a lab-scale study can be carried out using these methods and any large-scale production falls out of consideration. Therefore, new methods should be designed and developed, such that the resultant structure must be comparable in terms of the material quality, precision, reliability and reproducibility and at the same time the method should not involve costly set-ups and allow the synthesis of nanowires over large areas, if an application such as solar cells is sought.

In comparison with all the other conventional techniques, electroless etching stands as a solution based alternative that fits the profile of being a cost-effective approach. It was first introduced as a two step etching technique [1]. The first step involved coating of the silicon wafer by homogeneous silver (Ag), gold (Au),iron (Fe), platinum (Pt), copper (Cu) or nickel (Ni) films. Then, the second step was to immerse the wafer into hydrofluoric acid/hydrogen peroxide (HF/H<sub>2</sub>O<sub>2</sub>) solution, facilitating galvanic reactions between the metal and HF, inducing formation of pores leaving columnar, wire-like structures at the surface. This method was converted into single step etching mechanism by Peng et. al. [2], as the wafer was directly placed into hydrofluoric acid/silver nitrate (HF/AgNO<sub>3</sub>) solution facilitating vertically aligned silicon nanowire fabrication. This simple method has drawn attention and several research groups have been working on exploration of the mechanism behind this procedure. In this thesis, in the first part (Chapter 2) electroless etching method was studied and a detailed parametric study leading to the fabrication of silicon nanowires with desired length and distribution was conducted. There has been an important gap in the literature on the reliability of this method in terms of yielding a well controlled structure that is comparable to the nanowires produced by conventional methods. This detailed parametric study provided herein also filled this gap in the literature by revealing the effects of all process parameters on the nanowire length.

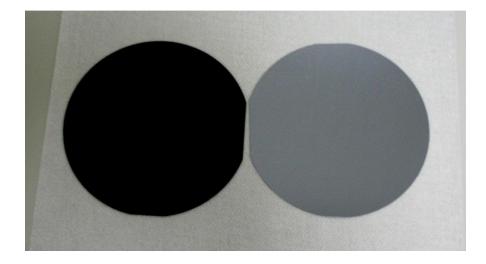

One of the most important features of vertically aligned silicon nanowire arrays fabricated by electroless etching is their remarkable antireflectivity. As the black and dull appearance of the surface containing silicon nanowires suggests, the optical reflectivity of the silicon substrate dramatically decrease following the etching process. This is due to the facts that both the optical path travelled by the incoming photons and the number of scattering events are increased, substantially. In this aspect, optical reflectivity measurements were carried out and it was found that the samples had as low as 1% reflectivity. These results point out that the silicon nanowires would not only function as the active layer of the photovoltaic device, but also act as the antireflective surface, eliminating the need of antireflective coating. Considering the fact that almost 30% of the efficiency losses are caused by reflective losses, silicon nanowire arrays would have an important contribution to solar cell systems, if an efficient model making use of these nanowires could be designed.

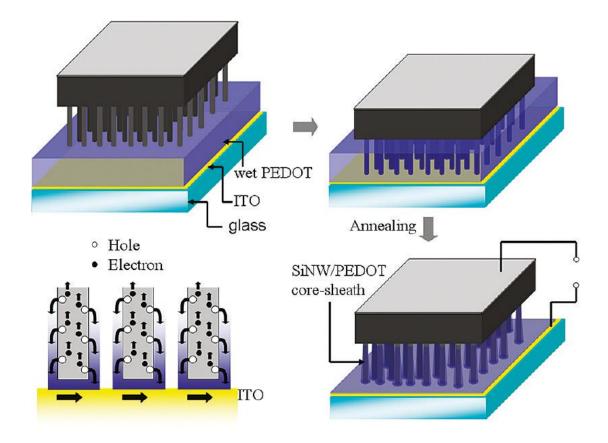

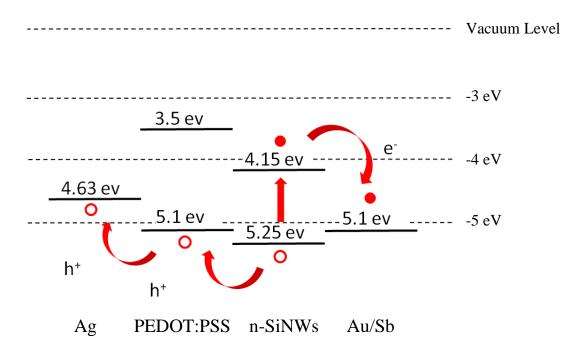

There are several different ways that silicon nanowires could be utilized in solar cell technology. Both homojunction and heterojunction (hybrid) solar cells could be fabricated based on nanowires. The main goal in this thesis was to get around vacuum systems and high temperature doping processes, another cost effective system. Therefore, production and characterization of silicon nanowire based radial heterojunction solar cells was investigated in the second part of this thesis (Chapter 3). It was predicted that the efficiency of planar hybrid heterojunctions, created by deposition of a complementary semiconducting thin film on a semiconducting substrate, could be increased by implementing the radial heterojunction concept that utilize nanowire arrays as one side of the junction. In this thesis, a radial

heterojunction was formed by coating p-type poly (3,4 ethylenedioxythiophene) poly (styrenesulfonate), (PEDOT:PSS), semiconducting polymer as the complementary film on n-type vertically aligned silicon nanowire arrays. This creates a three dimensional junction and a fully light absorbing active layer. The diffusion distances of the generated charge carriers were minimized. Radial heterojunctions provide much more efficient photon absorption, charge transfer and collection compared to planar heterojunctions. In order to investigate this, a control sample with planar silicon / PEDOT:PSS heterojunction was fabricated under the same conditions. Both types of devices were fully characterized and the mechanisms leading to the obtained differences were discussed. It was found that both planar and radial devices can harvest light in 300-1200 nm interval of the spectrum with radial heterojunctions. In addition, the effect of nanowire efficiencies compared to planar heterojunctions.

## **CHAPTER 2**

# SILICON NANOWIRE FABRICATION BY ELECTROLESS ETCHING

## **2.1. Introduction**

#### 2.1.1. Features of Nanowires

Nanotechnology involves working at the atomic and molecular levels in the length scale of 1 - 100 nm, in order to understand and create materials, devices and systems with fundamentally new properties and functions because of their small structure. Bulk materials consist of grains, the size of which ranges from several microns to millimeters and in each grain, they contain billions of atoms. On the other hand, nanostructured materials have much smaller grains, each consisting of only several hundreds of atoms. As a consequence of this dramatic decrease, the volume fraction of the grain boundaries and interfaces increase significantly. Considering the fact that the chemical potential at the surface of a material is much higher compared to the bulk region due to unfilled bonds of the constituent atoms, nanostructured materials gain enhanced mechanical, optical, magnetic, electrical properties, compared to their bulk counterparts. Using a variety of synthesis methods, it is possible to produce nanostructured materials in different geometries, as shown in Figure 2.1.

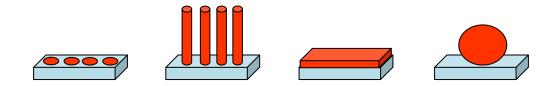

0-D Quantum dots 1-D Nanowires 2-D Thin Films 3-D Nanoparticles

**Figure 2.1.** Representative schemes of nanostructured materials, which are grouped according to their dimensionality.

Nanowires, compared to other low dimensional systems, have two quantum confined directions, while still leaving one unconfined direction for electrical conduction. This allows nanowires to be used in applications where electrical conduction, rather than tunneling transport, is required. The enhanced optical and electrical properties of nanomaterials originate from the quantum confinement effect. Quantum confinement is the trapping of charge carriers in a space small enough that their quantum (wavelike) behavior dominates over their classical (particle-like) behavior. In quantum mechanical terms, for quantum confinement to occur the dimension of the confining device or particle must be comparable to, or smaller than, the de Broglie wavelength of the carriers, the carrier inelastic mean free path and electron-hole Bohr radius of the material it's made from. Because of their unique density of electronic states, nanowires in the limit with sufficiently small diameters are expected to exhibit significantly different optical, electrical and magnetic properties from their bulk counterparts. The increased surface area to volume ratio, very high density of electronic states and joint density of states near the energies of their van Hove singularities, enhanced exciton binding energy, diameter-dependent bandgap, and increased surface scattering for electrons and phonons are just some of the ways in which nanowires differ from their bulk counterparts [3].

Nanowires are expected to become important functional components as integrated circuits continue to shrink in size. In addition to enabling small circuit dimensions, nanowires are known to exhibit low capacitance which helps to reduce power consumption and enhance signal speeds in future integrated circuits. Based on the

unique electrical properties, one of the most important research fields of nanoelectronics is the nanowire based field effect transistors. Various designs of nanowire based transistors have been demonstrated in the last few years and IBM introduced silicon nanowire transistors with 2.6 nm features in 2009. Nanowires have also been proposed for applications associated with extraordinarily high piezoresistive nanomaterials [4] and superconducting nanowires [5]. Furthermore, they have been used as electron field emission sources [6] of flat panel displays since their small diameter and large curvature at the tip, reduce the threshold voltage for the electron emission [7] and display remarkable field emission characteristics.

Fabrication of chemical and biological sensors with nanowires as the active component is also an attractive application area. Nanowire sensors will potentially be smaller, more sensitive, demand less power and react faster than their macroscopic counterparts. Arrays of nanowire sensors could, in principle, achieve nanometer scale spatial resolution and therefore provide accurate real-time information. This information not only includes the concentration of a specific analyte, but also its spatial distribution. They could also provide the corresponding information on other analytes within the same submicron volume. The increased sensitivity and faster response time of nanowires is a result of their large surface-to-volume ratio and the small cross-section available for conduction channels. In the bulk, on the other hand, the abundance of charges can effectively shield external fields, and the abundance of material can afford many alternative conduction channels. Therefore, a stronger chemical stimulus and longer response time is necessary to observe changes in the physical properties of a sensor with bulk active elements in comparison to a sensor fabricated with a nanowire [3].

Another novel characteristic of nanowires is their interesting magnetic properties. It has been demonstrated that arrays of single domain magnetic nanowires, arranged in a close-packed ordered array, can be prepared with controlled diameter and length, aligned along a common direction and that the magnetic properties (coercivity, remanence and dipolar magnetic interwire interaction) can be controlled to achieve a variety of magnetic applications [8]. One of the most interesting applications is for

magnetic data storage, where the large nanowire aspect ratio (length/diameter) is advantageous. At the onset of the superparamagnetic limit, the magnetization direction in the magnetic grains can be reversed by the thermal energy, resulting in loss of recorded data in the magnetic recording medium. In nanowires, the anisotropy is very large and yet the wire diameters are small, so that the magneto-static switching energy can easily be above the thermal energy while the spatial resolution is large.

Nanowire based solar cells have also become one of the hot topics. With remarkable electrical and optical contributions, these systems are heavily investigated by many researchers. One of those new approaches is hybrid solar cells, where organic and inorganic materials are used in conjunction. Both the large surface area and high conductivity along the length of nanowires are favorable for their use in inorganicorganic hybrid solar cells [9] which is promising both in manufacturability and cost. In a hybrid solar cell, the incident light could form bound electron-hole pairs (excitons) in both the inorganic nanocrystal and in the surrounding organic medium. These excitons diffuse to the inorganic-organic interface and disassociate to form an electron and a hole. Since conjugated polymers usually have poor electron mobilities, the inorganic phase is chosen to have a higher electron affinity than the organic phase so that the organic phase carries the holes and the semiconductor carries the electrons. The separated electrons and holes drift to the external electrodes through the inorganic and organic materials, respectively. Silicon nanowires have a direct band gap unlike their bulk counterparts [10]. They exhibit high effective masses of electrons and holes. This is quite advantageous as it allows for extended carrier lifetime and binding energies [11]. The energy gap changes with the size of the nanowires, hence they have tunable, or wavelength selective, optical and electrical properties. For instance, the optical absorption trend could be tuned for maximum optical absorption over the spectrum of the incoming solar irradiation. In addition to this concept, silicon nanowire solar cells with coaxial and radial heterojunctions are offering unique advantages over thin film solar cells. Vertically aligned arrays of silicon nanowires enable orthogonal photon absorption and carrier collection. This allows enhanced optical absorption due to light trapping and improved carrier collection, where the carrier collection distances become comparable to minority

carrier diffusion lengths [12,13]. These properties point out that nanowire based solar cell technologies have great potential for development and could lead to breakthroughs in the field as the intensive research continues.

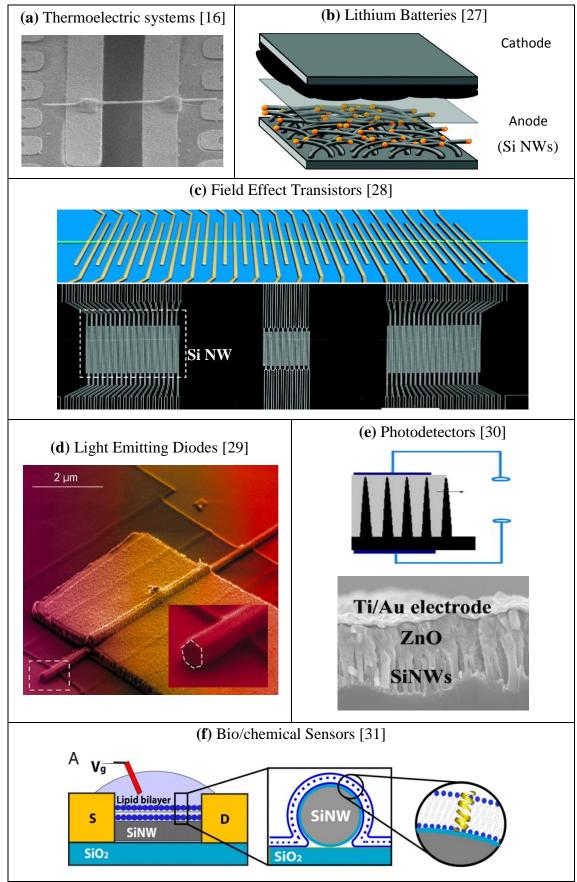

Owing to their unique properties, silicon nanowires (Si NWs) have been used in many research fields, especially in microelectronics and photonics [14,15]. In addition, silicon nanowires have been fabricated for the applications shown in Figure 2.2. List of applications include, but not limited to thermoelectric systems [16,17], lithium batteries [18,19], field effect transistors [20,21], photodetectors [22], light emitting diodes [23] and bio/chemical sensors [24]. Furthermore, it was discovered that they exhibit remarkable improvements for many different solar cell types [25,26]. In this thesis, vertically aligned silicon nanowire fabrication and their use in heterojunction solar cells are investigated.

Figure 2.2. Applications of silicon nanowires other than solar cells.

#### 2.1.2 Conventional Silicon Nanowire Synthesis Methods

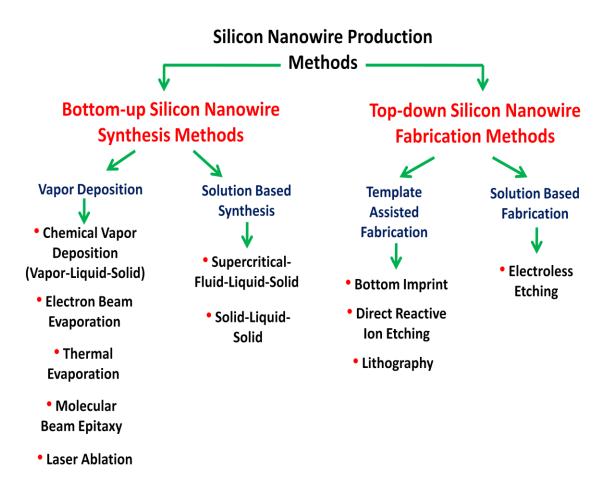

Following the realization of silicon nanowires, a large number of fabrication methods have been reported. These methods are grouped according to their main mechanism such as bottom-up and top-down methods as explained before. Among these, commonly used silicon nanowire production methods are listed in Figure 2.2. The most widely used silicon nanowire fabrication method is Vapor-Liquid-Solid (VLS) method [32,33]. Also there are other bottom-up alternatives such as chemical vapor deposition [34], thermal evaporation [35], molecular beam epitaxy [36], supercritical fluid-liquid-solid [37] and laser ablation [38] that have been frequently reported. As opposed to those, silicon nanowires can also be produced by top-down approaches. Several top-down methods have been reported, namely lithographical methods [39] and direct reactive ion etching (DRIE) [40]. In this section, the most commonly encountered silicon nanowire fabrication methods are introduced.

Figure 2.3. Silicon nanowire fabrication methods.

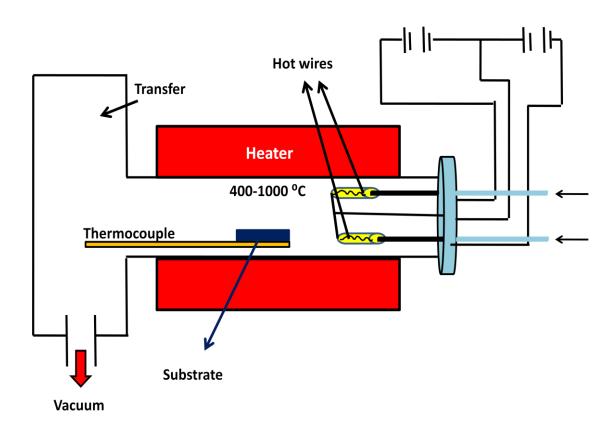

#### 2.1.2.1. Vapor Deposition

Growth of nanowires through vapor deposition includes physical vapor deposition (PVD), thermal evaporation and chemical vapor deposition (CVD). These methods usually require a vacuum system and a reactor through which the precursor gas flows. In the PVD technique, the precursor is heated for sublimation, which then meets with the cold substrate and condenses [41]. Similarly, in CVD method, the precursor vapor is passed through a reactor. A schematic of a typical reactor is given in Figure 2.4. In this method, upon decomposition of the precursor gas, nanowires nucleate on a cold substrate, the size of which is determined by the particle residence time, temperature, precursor composition and pressure. In most of these studies, nanowires are guided through a template in order to control the shape of the resultant structure.

Figure 2.4. Schematic of a typical CVD reactor.

#### 2.1.2.2. Vapor-Liquid-Solid (VLS) Method

Following Wagner and Eliss' first proposal of vapour-liquid-solid (VLS) mechanism of anisotropic crystal growth to produce semiconductor nanowires in 1964 [33], a wide range of other studies utilizing this technique have been reported. This technique allows a great control over the resultant structure and the most recent publications reporting successful synthesis of silicon nanowires utilize this method.

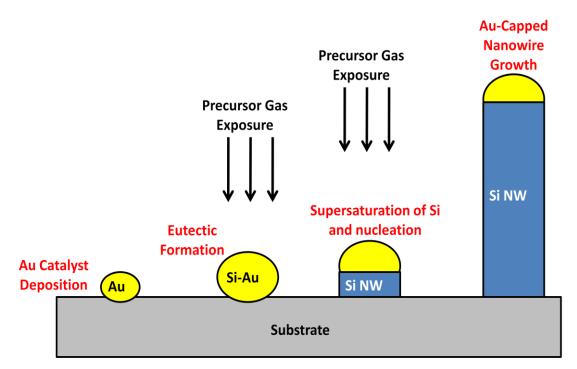

The growth mechanism in this method, schematically shown in Figure 2.5., can be divided into two stages; i) the nucleation and growth of Au-Si eutectic alloy droplets and *ii*) the growth of silicon nanowires. Au is generally used as the catalyst and silane gas (SiCl<sub>4</sub>) is used as the Si source, because this system facilitates wire growth at low temperatures, in the range of 550 – 900 °C [32]. Following silane exposure, an Au-Si liquid alloy is formed. Upon supersaturation of the liquid alloy, a nucleation event generates a solid precipitate of the source material. This seed serves as a preferred site for further deposition of material at the interface of the liquid droplet, promoting the elongation of the seed into a nanowire or a whisker, suppressing further nucleation events on the same catalyst. Since the liquid droplet catalyzes the incorporation of material from the gas source to the growing crystal, the deposit grows anisotropically as a whisker whose diameter is dictated by the diameter of the liquid alloy droplet. The nanowires thus obtained are of high purity, except for the end containing the solidified catalyst as an alloy particle [42]. The presence of gold on the tip of the nanowires limits their utilization in complementary metal oxide semiconductor (CMOS) devices.

**Figure 2.5.** Representative sketch showing the stages of VLS growth mechanisms of silicon nanowires.

#### 2.1.2.3. Template Assisted Growth

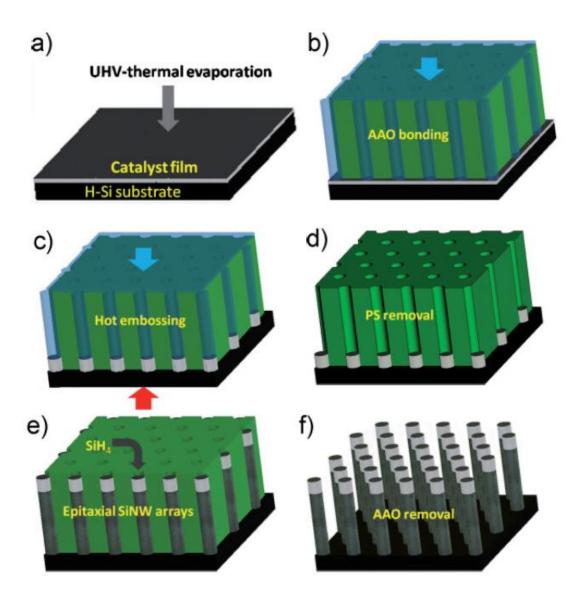

In template-assisted synthesis of nanowires, the chemical stability and mechanical properties of the template, as well as the diameter, uniformity and density of the pores are important characteristics to consider. Templates frequently used for nanowire synthesis include anodic alumina (Al<sub>2</sub>O<sub>3</sub>). Porous anodic alumina (AAO) templates are produced by anodizing pure aluminum (Al) films in various acids [43]. The concept of template assisted synthesis of nanowires is important since templates could also be adapted to the other methods. Template assisted growth yields a well controlled resultant structure and depending on the method it is assisting, highly crystalline silicon nanowires with very low density of defects could be produced.

Figure 2.6. Schematic representation of silicon nanowire production using bottom imprint method [44].

A commonly used example for template assisted growth of silicon nanowires would be bottom imprint technique, shown in Figure 2.6 [44]. In this method, a hydrogenterminated single crystal silicon substrate is covered by a homogeneous metal film, which is a catalytic agent to grow silicon nanowires. A pore-through AAO membrane filled with polystyrene (PS) is prepared and bonded to the substrate. PS occupies the pores by spin-coating on the as-anodized sample. The metal film is deformed and extruded into the end of the pores and the surrounding alumina wall is connected with the silicon substrate. To grow silicon nanowires, the imprinted sample is dipped into chloroform to remove the PS. Therefore, silicon can be grown epitaxially inside the template by applying the CVD process. The AAO template can easily be removed by selective chemical etching and the resulting epitaxially grown nanowires have the same diameters as the imprints.

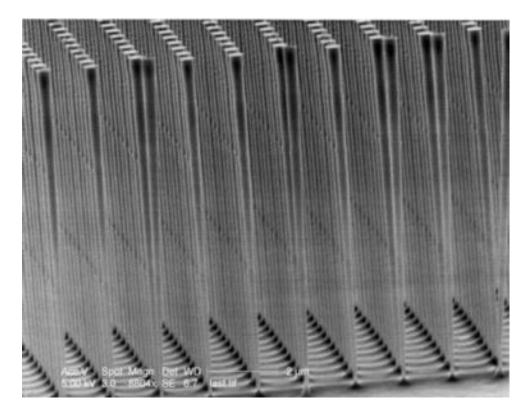

#### 2.1.2.4. Direct Reactive Ion Etching (DRIE) Method

A typical direct reactive ion etching procedure involves several stages. A nanoimprint process is conducted first. Nanoimprinting process includes pressing a mold into a thin thermoplastic polymer film on a substrate to create vias and trenches using electron beam lithography and etching a few hundred nm into the silica layer is carried out. During the imprinting, both the mold and a polymer such as poly(methyl methacrylate) (PMMA) are first heated to a temperature higher than the glass transition temperature of the polymer. Then the mold is compressed against the sample and held there until the temperature dropped below the polymer's glass transition temperature. Isotropic plasma etching of the silicon by sulfur hexafluoride/dioxide (SF<sub>6</sub>/O<sub>2</sub>) is then followed by plasma deposition of octafluorocyclobutane (C<sub>4</sub>F<sub>8</sub>) to passivate the sidewalls and suppress lateral etching of the silicon during the isotropic step. Aspect ratios as high as 60:1 are reported for nanowires with 50 nm diameters using reduced cycle times and gas flow [45]. A representative SEM image is provided in Figure 2.7, showing well-aligned low-diameter silicon nanowire arrays produced by DRIE.

Figure 2.7. SEM image of DRIE etched silicon nanowires [40].

## 2.1.3. Electroless Etching Method

## 2.1.3.1. History and Development of Electroless Etching Method

This solution based etching method, called as "metal assisted chemical etching", was first introduced by Dimova Malinovska et. al. in 1997 [46]. The idea was to obtain porous silicon by etching an aluminum covered silicon substrate in a solution containing HF, nitric acid (HNO<sub>3</sub>) and deionized water. The conclusion they came up with was the dramatic increase in the rate of pore formation due to the Al film. Following this study, Li and Bohn worked on this method in 2000 using various noble metals like gold (Au) and palladium (Pd) instead of Al and examined how these metals reacted with HF, hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) and ethanol (EtOH) solution [1]. They obtained rather sharper and straight pores within the silicon substrate. Developments in this metal assisted chemical etching method and porous silicon characteristics directed many other research groups into this cost effective method. The idea behind this mechanism is the exposure of silicon substrate which was partly covered by a noble metal to HF and an oxidizing agent, resulting in a rapid etching of the parts of the silicon substrate that are not coated with metal. This causes the nobel metal to sink through the initially created pores and form a porous or preferentially a columnar structure.

In 2002, Peng et. al. who widely investigated the metal assisted chemical etching method, came up with a one step process. As the name suggests there is no precoating mechanism involved in this method. The silicon substrate was placed in  $HF/AgNO_3$  solution and Ag coating and silicon etching simultaneously took place yielding a nanowire-like structure. In their study, they investigated the function of various oxidizing agents and different nitrates facilitating the galvanic reactions. In conclusion, they were able to form nanowire-nanobelt structure in a single step process, with the best results observed for the solution containing  $AgNO_3$  and HF. They called this single step process as electroless etching method in their latter studies [2].

Following these studies, several other attempts understanding the mechanism and gaining control over the resultant structure were carried out [47-55]. Although this important solution based method has been widely investigated, the exact mechanism leading to selective etching has not been cleared out yet.

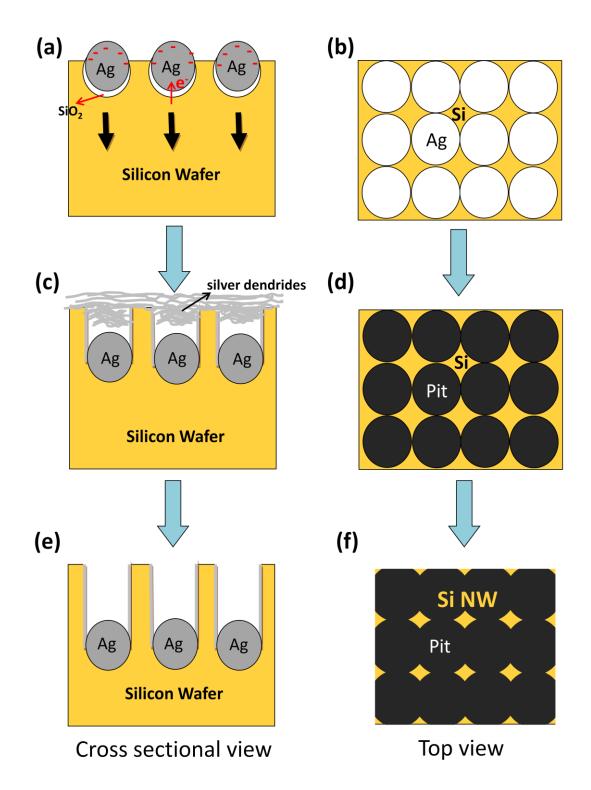

## 2.1.3.2. Electroless Etching Mechanism and Reactions

Silicon nanowire arrays form on silicon substrates by successive reduction-oxidation reactions, which take place along certain energetically favorable crystallographic orientations. Large amounts of silver dendrides immediately cover the etched silicon wafer as a result of intense galvanic displacement reactions. Thus, the surface morphology can not be readily accessible throughout the etching duration. Nevertheless, there are two different models to explain the formation of silicon nanowires with unique shape. The first one is based on a self-assembled localized microscopic electrochemical cell model [48]. At the initial stage, silicon etching and silver deposition occur simultaneously on the silicon wafer surface. The deposited silver atoms coming into contact with silicon nucleate and grow forming nanoclusters, which are distributed throughout the surface of the silicon wafer. These

silver nanoclusters and the silicon surrounding these silver nuclei can, respectively, act as local cathodes and anodes in the electrochemical redox reactions:

$$Ag^+ + e^- \to Ag_{(s)} \tag{2.1}$$

$$\mathrm{Si} + 6\mathrm{F}^{-} \rightarrow \mathrm{SiF_{6}}^{2-} + 4\mathrm{e}^{-} \tag{2.2}$$

These nanometer-sized, free standing excessive numbers of electrolytic cells could be spontaneously assembled on the surface of the substrate. As silver is deposited, the surrounding silicon acting as the anode is etched away as a result of the reaction with fluorine ions (F<sup>-</sup>), meanwhile silver particles acting as the cathode are dispersed in the silicon nanowire array. Therefore, selective etching of the silicon wafer takes place and the silver ion and reducing agent in the solution react directly at catalytic sites on the surface without involving the substrate in the charge transfer process.

In the second model, suggested by Peng et. al., Si/AgNO<sub>3</sub>/HF system is composed of a corrosion-type redox couple: the cathodic reduction of Ag<sup>+</sup> ions and its counterpart, the anodic oxidation and dissolution of silicon, taking place underneath the Ag deposits. Right after immersion of the substrate into the solution, Ag<sup>+</sup> ions near the surface of the substrate come into contact and capture electrons from valence band of silicon to become Ag(s) nuclei or aggregate. Due to the available extra energy around the defects, heterogeneous nucleation of Ag(s) by this electron exchange mechanism is more favourable. Due to having a high electronegativity to adhere, Ag nuclei strongly attracts electrons from silicon and become negatively charged. As a result of this phenomenon, silver nuclei serve to catalyze the subsequent reduction of Ag<sup>+</sup> ions, and causes silicon oxidation. The other Ag<sup>+</sup> ions coming close to the silicon surface preferentially get electrons from the silver nuclei, and are deposited around them. Consequently, growth of the silver nuclei into larger clusters occurs as the reaction goes on. Simultaneously, excess local oxidation occurs, and silicon dioxide (SiO<sub>2</sub>) is produced underneath these silver nanoparticles. As SiO<sub>2</sub> is formed, it reacts with HF already present in the solution and pits would immediately form

**Figure 2.8.** The representative scheme showing nanowire formation mechanism during various stages of the electroless etching from cross-sectional and top views. (a), (b) represent the initial stages where Ag ions come into contact with silicon and catalyze redox reactions. (c), (d) show the vertical etching of silicon leaving nanowire structure, (e) represents the final stage where silver dendrides are removed by nitric acid.

beneath the Ag nanoparticles. As a result of having a higher electronegativity, the Ag particles trapped in these pits do not move horizontally [55]. The representative figures indicating various stages of electroless etching mechanism can be found at Figure 2.8. With longer immersion times in the HF/AgNO<sub>3</sub> solution, the Ag particles that do not enter the pits would grow into branched Ag dendrites, as shown in Figure 2.8 (c). The galvanic reactions suggested by the second model are as follows [55]:

$$Ag^+ + e^- \rightarrow Ag(s)$$

(2.3)

$$\mathrm{Si}(\mathrm{s}) + \mathrm{H}_{2}\mathrm{O} \rightarrow \mathrm{SiO}_{2} + 4\mathrm{H}^{+} + 4\mathrm{e}^{-}$$

(2.4)

$$SiO_2 + 6HF \rightarrow H_2SiF_6 + 2H_2O \tag{2.5}$$

#### 2.1.3.3. Comparison of Electroless Etching with the Conventional Methods

Bottom-up methods usually require complex equipment, involves high temperatures, high vacuum and hazardous silicon precursors all of which drastically increase the cost of the processes. Moreover, silicon nanowire production over large areas is not possible due to limitations in the growth setups used. DRIE, on the other hand, is an equipment and cost intensive method, where large area and homogeneous production of silicon nanowires is non-trivial. However, electroless etching method stands out in all of these important concerns. It is a rather new silicon nanowire fabrication method that provides a low temperature, cost effective and solution based alternative that enables production of vertically aligned silicon nanowire arrays over large areas. In addition, silicon nanowires formed by electroless etching method have exactly the same properties with the starting substrate (i.e. doping type and density), while those synthesized with bottom-up approaches may need to be tuned for the desired characteristics. Considering these important advantages, electroless etching method is expected to become the leading technique to produce one dimensional arrays of silicon nanowires with further developments. In the following part of this thesis, fabrication of silicon nanowires using the electroless etching method over large areas is reported. A detailed parametric study on the electroless etching process parameters such as time, temperature and the nature of the substrate were performed. Also an analysis on the reflection characteristics of the as-produced nanowires indicating the necessary conditions for the nanowire fabrication so that they can be used as efficient absorbers in heterojunction solar cells is provided. As a consequence of geometrical dependence of physical and electrical properties of silicon nanowire based devices, it is very important to fabricate silicon nanowires in a well controlled manner. The nanowires that are produced via electroless etching method may be up to several tens of microns in length and the nanowire length variation throughout the whole surface is almost negligible. It was also found that, both polycrystalline (pc-Si), as well as monocrystalline (mc-Si) silicon substrates yield aligned silicon nanowires.

#### **2.2. Experimental Details**

Electroless etching (EE) process begins with the cleaning of silicon substrates. 400 microns thick, one side polished substrates were used. In order to observe the effect of the properties of the starting substrates, silicon wafers having different doping types (n-type, p-type), resistivities (0.1-1 $\Omega$ .cm, 1-10  $\Omega$ .cm), crystal structure (monocrystalline, multicrystalline) and crystallographic orientations (100, 111) were selected as the starting substrates. Also a study on unpolished wafers was carried out. Some of these unpolished wafers were chemically cleaned and directly went under electroless etching, while some of them were saw-damage etched using potassium hydroxide (KOH) solutions prior to electroless etching. All the chemicals used in this study were purchased from Sigma Aldrich and used without further purification.

In order to obtain a homogeneous nanowire structure at the end of the galvanic etching reactions, the substrates must be completely free of impurities. Any contaminated region of the substrate may result in a disrupted structure or no nanowire formation at all. In this chemical cleaning stage, silicon substrates were consecutively sonicated in acetone (99.8%), isopropanol (99.8%) and deionized water baths for 10 minutes each. This step was followed by preparation of piranha solution by mixing sulfuric acid ( $H_2SO_4$ , 95-97%) and hydrogen peroxide ( $H_2O_2$ , 35%) in 3:1 volume ratio and immersion of the samples in this solution, rinsed under

deionized water and dipped into dilute hydrofluoric acid (HF, 38-40%) solution for 2 minutes to remove the native oxide and allow the substrate surface to become hydrophobic.

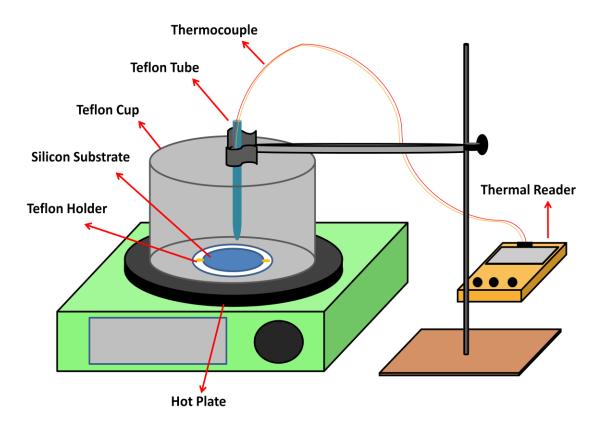

The electroless etching solution was prepared and chemically cleaned silicon substrates were immersed into that solution kept in a Teflon beaker at atmospheric pressure. The representative schematic of the experimental setup is shown in Figure 2.9. EE solution consists of AgNO<sub>3</sub> (99.5%) and HF (38-40%). In order to determine the effect of each parameter on the resultant silicon nanowire structure, cleaned silicon substrates (having various properties mentioned above) were immersed into the solution having different concentrations, for various durations (up to 10 hours), at different temperatures (0-50°C). Moreover, in order to observe the effect of high pressures on the process, the experiment was carried out in an autoclave (Parr Inst. 4744 General Purpose Acid Digestion Vessel) instead of the Teflon beaker open to atmosphere.

Prior to the immersion of the substrates into etching solution, the samples were fixed on a teflon disc by kapton tape in order to isolate the unpolished side of the wafer. This was found to be necessary since the unpolished rough surface were not facilitating vertical alignment each time, leading to confusion during SEM analysis. Although the EE mechanism is known as intrinsically anisotropic and the silicon nanowire growth direction is <100>, multicrystalline silicon substrates or substrates without smooth surfaces may result in nanowire alignments in various directions.

Figure 2.9. The experimental setup facilitating silicon nanowire fabrication by electroless etching method.

The desired silicon nanowire structures containing Ag dendrides are shown in Figure 2.10 (a) and (b). At the end of the etching process, samples were rinsed with deionized water and placed in dilute nitric acid (HNO<sub>3</sub>, 65%) solution for 30 minutes to remove the Ag dendrite layer formed on top of the nanowire arrays. As the final stage of the process, samples were rinsed with deionized water and dried with a nitrogen gun. The relationship of silicon nanowire length and distribution with each EE processing parameter, namely etching time, solution temperature and concentration, wafer orientation, resistivity and doping type was determined. In order to observe this relation, only one parameter was changed at a time while the others were kept constant.

**Figure 2.10.** (a) Cross-sectional and (b)  $45^{\circ}$  tilted SEM images of an electroless etched silicon sample containing 8 µm long silicon nanowire arrays. The SEM examination was carried out before silver dendride removal by nitric acid.

## 2.3. Nanowire Characterization Methods

#### 2.3.1. Scanning Electron Microscopy (SEM)

The resultant lengths and distributions of silicon nanowires were analyzed by FE-SEM (Nova NanoSEM 430) operated at 10 keV voltage. Cross sectional SEM images were obtained from cleaved edges of the silicon substrates. Both cross-sectional and top view SEM images were examined following each parametric change in the experimental procedure. No gold or carbon coating was utilized.

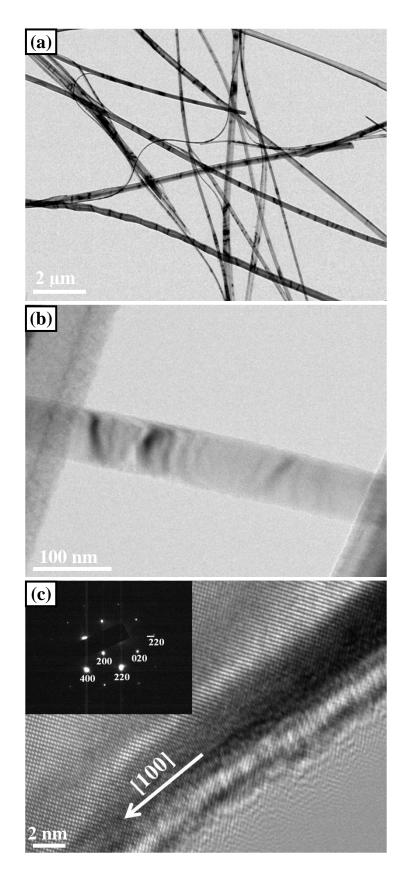

#### 2.3.2. Transmission Electron Microscopy (TEM)

Transmission Electron Microscope (TEM) was used to observe the surface morphology in atomic scale and obtain crystallographic data. The silicon nanowire arrays were scraped off of silicon substrates, dispersed in isopropanol and drop casted on holey carbon coated 400 mesh copper grids. A JEOL 2010 high-resolution transmission electron microscopy (HRTEM) operated at 200 kV was used for characterization.

#### **2.3.3. Optical Reflectivity Measurements**

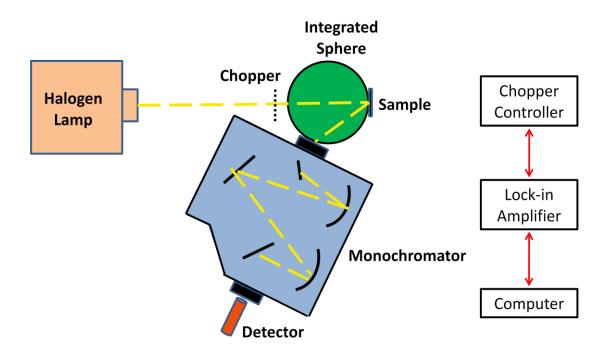

Reflectivity measurements were made through a silicon photodetector calibrated integrated sphere (Newport 70679NS) which also takes into account the diffuse reflectance. The schematic of the reflectivity set-up is given in Figure 2.11. There is a halogen lamp for light generation, chopper, a monocromator to obtain the reflectivity over a spectral bandwith and an integrated sphere with both the sample and the silicon photodetector attached.

Figure 2.11. The optical reflectivity measurement set-up.

## 2.3.4. Field Emission Measurements

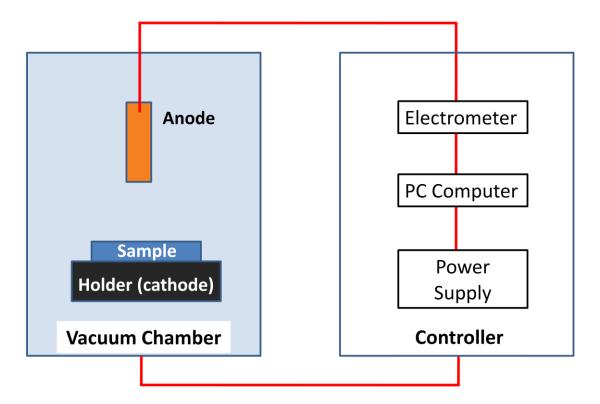

The field emission measurements of the silicon nanowires were carried out in a vacuum chamber at a pressure of  $5 \times 10^{-5}$  Pa. The current density–voltage (J–V) curves were performed using a Keithley 4200 high source measure unit. This study also included stability measurements and current-emission field characterization. The gap between the anode and the cathode was 200 µm. The average area of each sample was 2 cm<sup>2</sup>. The setup used for the field emission measurements is shown in Figure 2.12. Field emission measurements of the silicon nanowire arrays were conducted at the Electrical Engineering Division of University of Cambridge.

Figure 2.12. The field emission measurement set-up.

## 2.4. Results

## 2.4.1. Determination of the Electroless Etching Parameters

#### 2.4.1.1. Solution Concentration

The most critical parameter for the fabrication of silicon nanowires with EE method is the solution concentration due to the nature of this top-down approach. Following the first report on the single step chemical etching [2] (i.e. electroless etching), a solution concentration of 0.02 M AgNO<sub>3</sub> / 4.6 M HF was often reported in the literature. The effect of solution concentration by reducing and increasing the concentrations of AgNO<sub>3</sub> and HF one at a time was investigated in this thesis. However, in all cases a more disrupted structure was obtained as the concentration was changed. The results of several attempts towards the optimization of the solution concentration are shown in the SEM images of the produced structures given in Figure 2.13. It is appearent that the silicon nanostructures in Figure 2.13 (a), (b) and (c) are not well aligned and reveal sharp nanowire morphologies; (d) on the other hand displays vertically well aligned silicon nanowires that are homogeneously distributed over the entire surface. Therefore, the remaining process parameters were all determined using a solution concentration of  $0.02 \text{ M AgNO}_3/4.6 \text{ M HF}$ .

**Figure 2.13.** Cross-sectional SEM images of samples that are electroless etched in solutions having concentrations of (a)  $0.01M \text{ AgNO}_3 / 4.6M \text{ HF}$ , (b)  $0.02M \text{ AgNO}_3 / 7M \text{ HF}$ , (c)  $0.04M \text{ AgNO}_3 / 4.6M \text{ HF}$  and (d)  $0.02M \text{ AgNO}_3 / 4.6M \text{ HF}$ .

## 2.4.1.2. Time

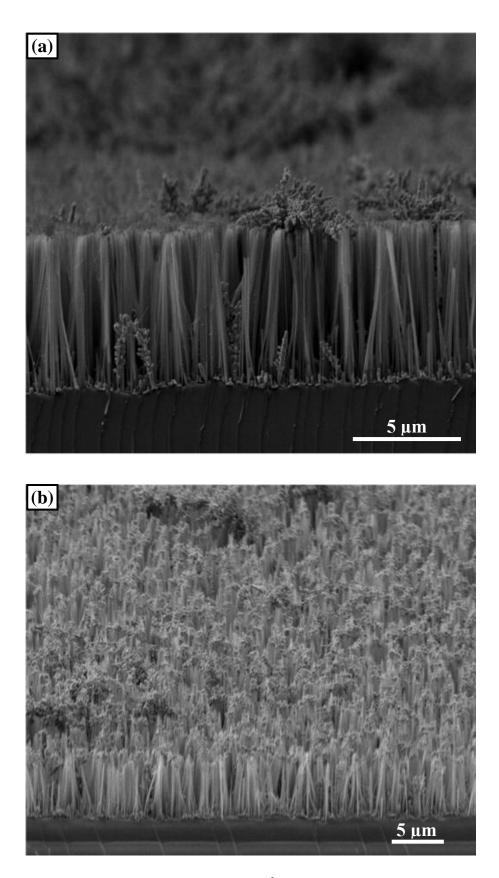

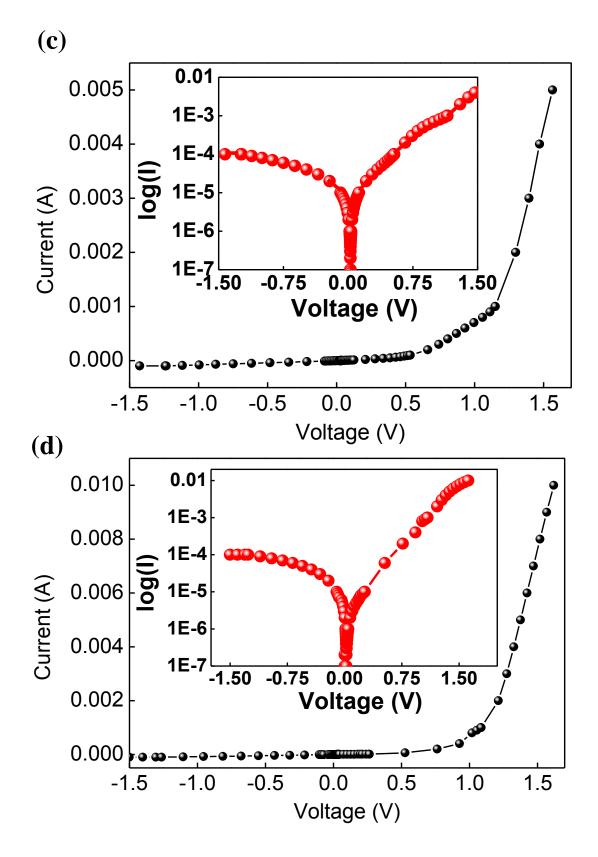

Etching time has a direct influence on the resultant nanowire lengths. Nanowires were fabricated within etching durations of 8, 16, 40, 60, 120, 180, 240, 360, 450 and 600 minutes, while maintaining the solution concentration at 4.6 M HF/ 0.02 M AgNO<sub>3</sub> and temperature at 40°C. Among these samples, SEM images of the silicon nanowires fabricated within 8, 40, 120 and 360 minutes, are shown in Figure 2.14 (a)-(d), respectively. Vertically aligned silicon nanowire arrays can be clearly seen in

all the images. Moreover, the nanowire length as a function of etching time is plotted in Figure 2.15.

**Figure 2.14.** Cross-sectional SEM images of the vertically standing silicon nanowire arrays obtained by electroless etching at  $40^{\circ}$ C in a solution containing 4.6 M HF / 0.02 M AgNO<sub>3</sub> for (a) 8 minutes, (b) 40 minutes, (c) 120 minutes and (d) 360 minutes.

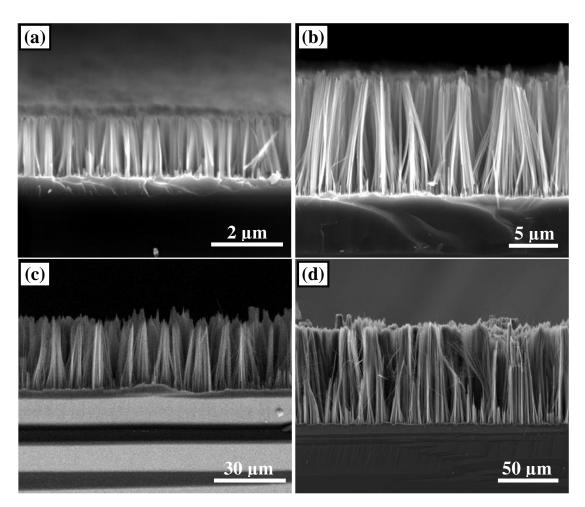

In accordance with the previous work, a linear relationship between etching time and nanowire length was obtained for etching durations up to 4 hours with an etching rate of 0.25  $\mu$ m/min. This clearly indicates the speed of EE process. Further etching, beyond 4 hours, again revealed a linear relationship with a change in the etching rate of the nanowires as shown in Figure 2.15. Etching rate of the nanowires between 4 to 10 hours was determined to be 0.1  $\mu$ m/min. This clearly indicates that the reaction slows down due to the decrease in the reaction kinetics. This decrease in the reaction

Figure 2.15. Variation of nanowire length with etching time

kinetics can be attributed to the inhibition of the sinking mechanism of  $Ag^+$  ions to the bottom of the nanowire arrays, leading to decrease in Ag concentration. Since the reduction-oxidation reactions selectively take place at the interface between the bottom of the nanowires and the top of the bulk substrate, the drop in Ag concentration causes the etching rate to slow down.

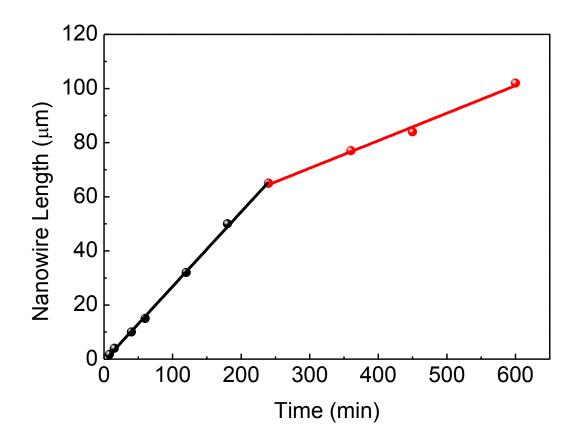

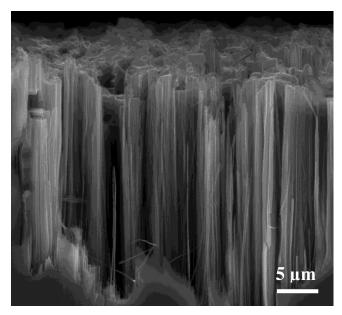

Another aspect in the time dependent nanowire characteristics is the nanowire distribution and alignment. As the nature of the EE method, the nanowires tend to form bundles due to the capillary forces upon pulling them out from the etching solution [56]. As the etching time increases with the nanowire length, these forces become more dominant resulting in a bundled structure rather than vertically aligned individual nanowire arrays, as shown in Figure 2.16 (a). The effects of forming several tens of microns long nanowire bundles on reflectivity are also discussed within the reflectivity measurements.

**Figure 2.16.** (a) Top-view SEM image of agglomerated tips of the approximately 80  $\mu$ m long nanowires. (b) and (c) cross-sectional SEM images of samples with nanowire arrays longer than 100  $\mu$ m. (d) Cross-sectional SEM image of electroless etched thin silicon wafer just before complete conversion into nanowires.

For several applications, relatively long silicon nanowires may be required. Even though the reaction kinetics slow down and the nanowires tend to form bundles, individually standing nanowires could still be obtained. Figure 2.16. (b) and (c) shows SEM images of silicon nanowires longer than 100 microns. Especially for the sample in Figure 2.16 (c), the bundling mechanism is considerably dominant. In addition to etching 400  $\mu$ m thick silicon wafers, previously lapped approximately 110  $\mu$ m thick silicon wafer was etched in order to obtain complete etching of the silicon substrate and nanowires in powder form instead of arrays. Lapping is a procedure, in which the backside of the wafer is brought into contact with an abrasive slurry to remove material from the backside. The slurry is a combination of

lapping oil and silicon carbide or aluminium oxide. The EE experiment was supposed to last until the substrate is completely converted into nanowires; however, in the late stages of EE, Ag dendride film completely covered the reacting interface and stopped the reaction from going further. SEM image in Figure 2.16 (d) pointed out that the sample had 100  $\mu$ m long nanowires standing on top of only 10  $\mu$ m thick substrate. Before the SEM examination, the dendride film was removed by nitric acid treatment and following the SEM analysis, the sample was immersed into a second electroless etching solution and converted completely into 110  $\mu$ m long silicon nanowires.

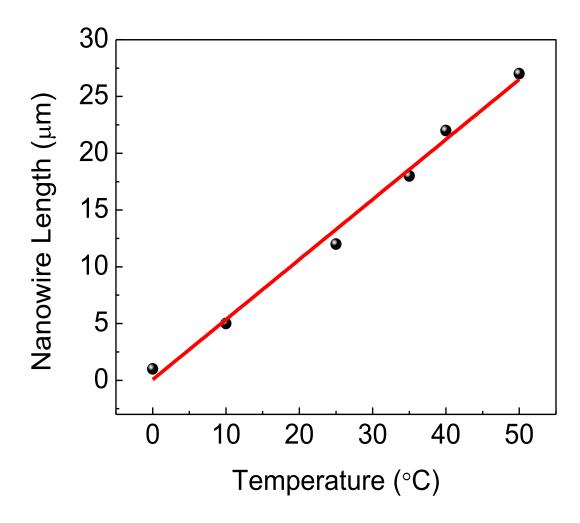

#### 2.4.1.3. Temperature

Temperature of electroless etching solution is another factor that has a direct influence on nanowire length, since it changes the kinetics of the reduction-oxidation reactions. The effect of the temperature was investigated in a range of 0-50 °C and it was found that the length of the silicon nanowires is linearly proportional to the solution temperature. We have avoided temperatures in excess of 50 °C due to safety reasons and to keep the solution concentration stable. Also, taking into account that one of the biggest advantages of this process is the ability to work at low temperatures, low temperatures should be preferred. SEM images of the silicon nanowires fabricated at temperatures of 0, 10, 25 and 50°C are shown in Figure 2.17 (a)-(d) respectively. Nanowire length as a function of temperature is plotted in Figure 2.18 and a linear relationship between temperature and nanowire length is obtained.

Similar to the effect of etching time, conducting the process at high temperatures cause nanowires to agglomerate into each other, meanwhile lower solution temperatures, hence slower reaction kinetics provide well aligned nanowires distributed uniformly throughout the whole wafer surface.

**Figure 2.17.** Cross-sectional SEM images of silicon nanowire arrays obtained by electroless etching method conducted at (a)  $0^{\circ}$ C, (b)  $10^{\circ}$ C, (c)  $25^{\circ}$ C and (d)  $50^{\circ}$ C upon 1 hour etching in a solution containing 4.6 M HF / 0.02 M AgNO<sub>3</sub>.

Figure 2.18. Variation of nanowire length with solution temperature.

## 2.4.1.4. Pressure

Nanowire fabrication by electrochemical etching experiments were conducted in teflon beakers open to atmosphere. However, carrying out this process at a high pressure was predicted to facilitate a homogeneous distribution of nanowire arrays in terms of length and alignment. Also, the electrochemical reactions were estimated to take place more rapidly resulting in longer nanowires in shorter etching durations. In order to observe the effect of pressure, a Teflon lined stainless steel autoclave (Digestion bomb) was utilized. High pressure experiments were carried out within the autoclave using a solution concentration of 0.02 M AgNO<sub>3</sub> / 4.6 M HF. During the reaction, autoclave was kept at 40°C for 40 minutes. However, in the contrary to expectations, nanowire formation could not be obtained at high pressures. Different concentrations, temperatures and durations were applied, but the resultant structures were similar to the one provided in the SEM image given in Figure 2.19. It can be

seen that instead of nanowires, randomly distributed columnar structures were obtained.

Figure 2.19. Micron-sized columnar structures obtained by high pressure experiments.

#### 2.4.1.5. Silicon Wafer Characteristics

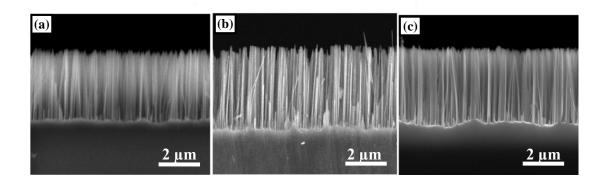

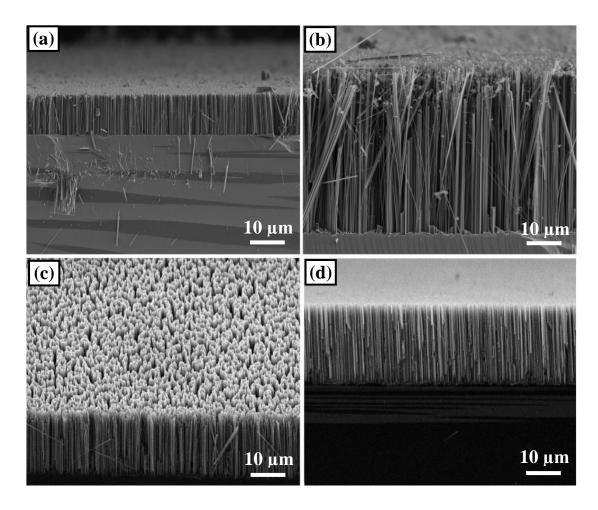

#### 2.4.1.5.1. Doping Type, Crystallographic Orientation and Resistivity

The characteristics of the starting silicon substrate in terms of doping type and density, crystallographic orientation and resistivity were expected to affect the growth rate and the structure of the nanowires during the electroless etching process. This prediction was based on the idea that n-type silicon would have a larger number of electrons available at the surface and also the hole concentrations would be different. In addition, one of the previous studies [55] showed Ag nanoparticle deposition on n-type and p-type silicon substrates. It was reported that Ag distribution becomes higher for n-type silicon substrates, on the other hand Ag particle sizes become relatively larger on the p-type silicon substrates. However, as a result of successive experiments, it was determined that the EE method is almost independent to the doping type and doping level of the starting silicon substrate.

SEM images of electroless etched p-type and n-type silicon wafers are given in Figure 2.20 (a) and (b), respectively.

It was also suggested by the earlier reports that the crystallographic orientation of the monocrystalline silicon wafer changes the alignment of the silicon nanowires that are produced by EE [57]. This is investigated by etching silicon wafers with (100) and (111) crystallographic orientations under the same conditions. SEM images of the electroless etched n-type (100) and n-type (111) substrates are given in Figure 2.20 (a) and (c), respectively. The nanowire alignment was vertical in both cases; therefore, it can be said that the polished monocrystalline silicon wafers are all etched with similar reaction kinetics independent of their doping and resistivities and the nanowire alignment was found to be vertical, independent from the crystallographic orientation of the starting silicon substrates.

**Figure 2.20.** Cross-sectional SEM images of electroless etched (a) n-type (100), (b) p-type (100) and (c) n-type (111) silicon wafers having 1-5 $\Omega$ .cm, 10-20  $\Omega$ .cm and 10-20  $\Omega$ .cm resistivities.

Furthermore, positioning of the silicon substrate in the electroless etching solution, whether the substrate is in a horizontal or vertical position, hung from the lid of the Teflon cup upside down or placed on a holder at a certain angle were investigated. The resultant nanowire structure was the same (vertically aligned) with very minor variations in the reaction kinetics, which were assumed to be resulted due to partially isolated interface (i.e. hanging the sample upside down from the lid of the cup may

lead to a decreased number of silver ions coming into contact with the reacting front).

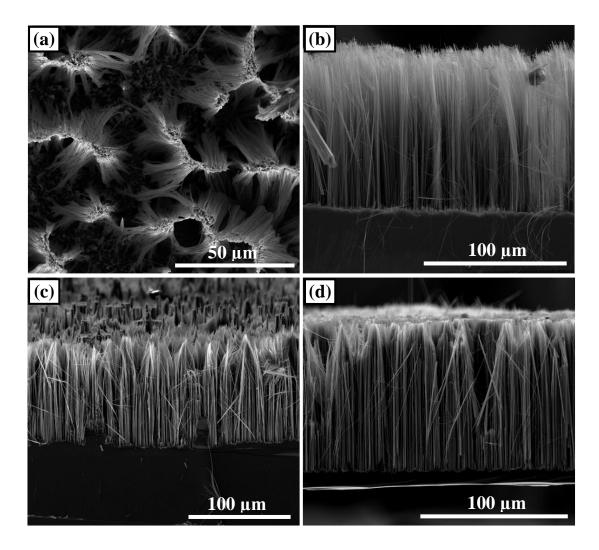

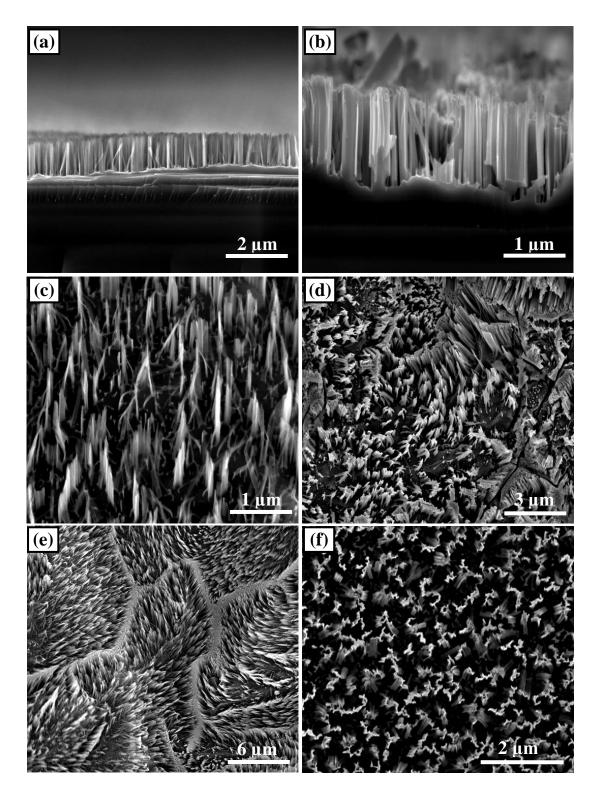

#### 2.4.1.5.2. Crystallinity

All of the reported results related to fabrication of silicon nanowires using EE method belong to etching of monocrystalline silicon substrates up to this section. In this section, the effect of crystallinity of the starting substrate was observed by comparing the morphologies of electroless etched mono and multicrystalline silicon substrates.

As it was mentioned in the previous section, etching of single crystalline substrates with any crystallographic orientation yields vertical alignment. The validity of silicon nanowire fabrication over multicrystalline wafers is also important for optoelectronic applications, since the production costs of the multicrystalline silicon wafers are relatively lower than the single crystalline ones. Furthermore, there was very limited studies that involve etching of multicrystalline silicon wafers in the literature. Crosssectional and top view SEM images of the silicon nanowires fabricated from multicrystalline and monocrystalline silicon wafers are shown in Figures 2.21 (a) -(b) and (c), respectively. Our results demonstrate that silicon nanowire arrays can be fabricated over multicrystalline substrates through this method as well. Figure 2.21 (a) reveals that alignment and length of the nanowires are different in each grain, clearly demonstrating that the etching rate changes with crystallographic orientation associated with the different chemical reactivity of grains. On the other hand, the distribution of the nanowires and their length within each grain was found to be very homogeneous similar to the ones fabricated from monocrystalline silicon. Grain boundaries are also clearly visible in Figure 2.21 (a) and (b).

**Figure 2.21.** (a) Cross-sectional view and (b) top-view of multicrystalline silicon substrate; (c) cross-sectional view and (d) top-view of monocrystalline silicon substrate, electroless etched under the same conditions.

#### 2.4.1.5.3 Polishing