#### DESIGN AND IMPLEMENTATION OF SCHEDULING AND SWITCHING ARCHITECTURES FOR HIGH SPEED NETWORKS

#### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

MUSTAFA SANLI

IN PARTIAL FULLFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ELECTRICAL AND ELECTRONICS ENGINEERING

OCTOBER 2011

Approval of the thesis:

#### DESIGN AND IMPLEMENTATION OF SCHEDULING AND SWITCHING ARCHITECTURES FOR HIGH SPEED NETWORKS

submitted by MUSTAFA SANLI in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen Dean, Graduate School of Natural and Applied Sciences                             |

|---------------------------------------------------------------------------------------------------------|

| Prof. Dr. İsmet Erkmen<br>Head of Department, Electrical and Electronics Engineering                    |

| Prof. Dr. Hasan Cengiz Güran Supervisor, Electrical and Electronics Engineering Dept., METU             |

| Assoc. Prof. Dr. Ece Güran Schmidt<br>Co-Supervisor, Electrical and Electronics Engineering Dept., METU |

| Examining Committee Members:                                                                            |

| Prof. Dr. Semih Bilgen Electrical and Electronics Engineering Dept., METU                               |

| Prof. Dr. Hasan Cengiz Güran<br>Electrical and Electronics Engineering Dept., METU                      |

| Assoc. Prof. Dr. Cüneyt Bazlamaçcı                                                                      |

| Assoc. Prof. Dr. Nail Akar<br>Electrical and Electronics Engineering Dept., Bilkent Univ.               |

| Assist. Prof. Dr. İlkay Ulusoy<br>Electrical and Electronics Engineering Dept., METU                    |

**Date:** October 6, 2011

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

| Name, Last name | : Mustafa Sanlı |

|-----------------|-----------------|

| Signature       | :               |

### ABSTRACT

# DESIGN AND IMPLEMENTATION OF SCHEDULING AND SWITCHING ARCHITECTURES FOR HIGH SPEED NETWORKS

Sanlı, Mustafa

Ph. D., Department of Electrical and Electronics EngineeringSupervisor: Prof. Dr. Hasan Cengiz GüranCo-Supervisor: Assoc. Prof. Dr. Ece Güran Schmidt

October 2011, 122 pages

Quality of Service (QoS) schedulers are one of the most important components for the end-to-end QoS support in the Internet. The focus of this thesis is the hardware design and implementation of the QoS schedulers, that is scalable for high line speeds and large number of traffic flows. FPGA is the selected hardware platform.

Previous work on the hardware design and implementation of QoS schedulers are mostly algorithm specific. In this thesis, a general architecture for the design of the class of Packet Fair Queuing (PFQ) schedulers is proposed. Worst Case Fair Weighted Fair Queuing Plus (WF<sup>2</sup>Q+) scheduler is implemented and tested in hardware to demonstrate the proposed architecture and design enhancements.

The maximum line speed that PFQ algorithms can operate decreases as the number of scheduled flows increases. For this reason, this thesis proposes to aggregate the flows to scale the PFQ architecture to high line speeds. The Window Based Fair Aggregator (WBFA) algorithm that this thesis suggests for flow aggregation provides a tunable trade-off between the efficient use of the available bandwidth and the fairness among the constituent flows. WBFA is also integrated to the hardware PFQ architecture.

The QoS support provided by the proposed PFQ architecture and WBFA is measured by conducting hardware experiments on a custom built high speed network testbed which consists of three data processing cards and a backplane. In these experiments, the input traffic is provided by the hardware traffic generator which is designed in the scope of this thesis.

Keywords: Quality of Service Scheduler, High speed network, Flow aggregation

## ÖΖ

# YÜKSEK HIZLI AĞLAR İÇİN ZAMANLAMA VE ANAHTARLAMA MİMARİLERİNİN TASARIMI VE GERÇEKLENMESİ

Sanlı, Mustafa Doktora, Elektrik Elektronik Mühendisliği Bölümü Tez Yöneticisi: Prof. Dr. Hasan Cengiz Güran Ortak Tez Yöneticisi: Doç. Dr. Ece Güran Schmidt

Ekim 2011, 122 sayfa

Servis kalitesi (QoS) çizelgeleyiciler, internette uçtan uca QoS desteği için en önemli bileşenlerdendir. Bu tezin odaklandığı konu, yüksek hat hızlarına ve çok sayıda trafik akışına ölçeklenebilen QoS çizelgeleyicilerin donanımsal tasarımı ve gerçeklenmesidir. Seçilen donanım platformu FPGA'dir.

QoS çizelgeleyicilerin donanımsal tasarımı ve gerçeklenmesi üzerine yapılan önceki çalışmalar çoğunlukla algoritmaya özeldir. Bu tezde Paket Adil Kuyruklama (PFQ) sınıfındaki çizelgeleyicilerin tasarımı için genel bir mimari önerilmiştir. Bu sınıftaki çizelgeleyicilerden bir tanesi, önerilen mimariyi ve tasarım iyileştirmelerini örnek üzerinde göstermek için donanım üzerinde gerçeklenmiş ve test edilmiştir.

Çizelgelenen akış sayısı arttıkça PFQ algoritmalarının çalışabildiği en yüksek hat hızı azalmaktadır. Bu yüzden, bu tez PFQ mimarisini yüksek hat hızlarına ölçeklendirmek için akışları birleştirmeyi önermektedir. Bu tezde akış birleştirme için önerilen Pencere Tabanlı Adil Birleştirici (WBFA) algoritması, mevcut bant genişliğinin etkin kullanımı ile bileşen akışlar arasındaki adillik arasında ayarlanabilir bir ödünleşim sunmaktadır. WBFA aynı zamanda donanımsal PFQ mimarisine de entegre edilmiştir.

Önerilen PFQ mimarisi ve WBFA tarafından sağlanan QoS desteği üç veri işleme kartı ve bir anakarttan oluşan özel üretilmiş bir yüksek hızlı ağ test ortamında donanımsal deneyler yapılarak ölçülmüştür. Bu deneylerde, giriş trafiği bu tez kapsamında tasarlanan bir donanımsal trafik üretici tarafından oluşturulmuştur.

Anahtar Kelimeler: Servis kalitesi çizelgeleyici, Yüksek hızlı ağ, Akış birleştirme

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my thesis advisor Prof. Dr. Hasan Cengiz Güran and my co-advisor Assoc. Prof. Dr. Ece Güran Schmidt for their invaluable support, guidance, encouragement and friendship throughout the completion of the thesis. I would like to thank Prof. Dr. Semih Bilgen, Assoc. Prof. Dr. Cüneyt Bazlamaçcı, Assoc. Prof. Dr. Nail Akar and Assist. Prof. Dr. İlkay Ulusoy for their precious contributions to my thesis. I must acknowledge Aselsan AŞ for providing me time and facilities for my research. Finally, I would like to thank my family for their continuous support throughout my life.

## **TABLE OF CONTENTS**

| ABSTRACT              | iv   |

|-----------------------|------|

| ÖZ                    | vi   |

| ACKNOWLEDGEMENTS      | viii |

| TABLE OF CONTENTS     | ix   |

| LIST OF TABLES        | xii  |

| LIST OF FIGURES       | xiii |

| LIST OF ABBREVIATIONS | XV   |

## CHAPTERS

| INTRODUCTION                                  |    |

|-----------------------------------------------|----|

| 2 SWITCHES FOR HIGH SPEED NETWORKS            | 8  |

| 2.1 SWITCHES AND ROUTERS                      | 9  |

| 2.2 QUALITY OF SERVICE SCHEDULERS             |    |

| 2.2.1 Packet Fair Queuing Schedulers          | 14 |

| 3 HARDWARE TESTBED                            | 16 |

| 3.1 IDENTIFICATION OF THE DESIGN REQUIREMENTS | 16 |

| 3.1.1 Selection of the Processor              |    |

| 3.1.1.1 General Purpose Processors            | 17 |

| 3.1.1.2 Embedded RISC Processors              | 17 |

| 3.1.1.3 Network Processors                    | 17 |

| 3.1.1.4 ASIC                                  |    |

| 3.1.1.5 FPGA                                                       | 18 |

|--------------------------------------------------------------------|----|

| 3.2 HARDWARE DESIGN OF THE DATA-PROCESSING BOARDS                  | 19 |

| 3.3 HARDWARE DESIGN OF THE BACKPLANE                               | 21 |

| 3.4 LOGIC DESIGN WITH FPGA                                         | 23 |

| 4 FPGEN: A FAST, PROGRAMMABLE TRAFFIC GENERATOR                    | 25 |

| 4.1 SYNTHETIC TRAFFIC GENERATION FOR THE PERFORMANCE               |    |

| EVALUATION OF COMPUTER NETWORKS                                    | 29 |

| 4.1.1 Proprietary Hardware Traffic Generators and Software Traffic |    |

| Generators                                                         | 29 |

| 4.1.2 FPGA-Based Hardware Traffic Generators                       | 30 |

| 4.1.3 Traffic Types Generated by FPGEN                             | 36 |

| 4.2 FPGEN POISSON TRAFFIC GENERATION                               | 37 |

| 4.2.1 Conceptual Design                                            | 37 |

| 4.2.2 Hardware Design                                              | 39 |

| 4.2.3 Experiments and Performance Evaluation                       | 45 |

| 4.3 FPGEN BURSTY TRAFFIC GENERATION                                | 50 |

| 4.3.1 Conceptual and Hardware Design                               | 50 |

| 4.3.2 Experiments and Performance Evaluation                       | 53 |

| 4.4 TRAFFIC GENERATION CAPABILITIES OF FPGEN                       | 54 |

| 4.5 CONCLUSIONS                                                    | 57 |

| 5 HARDWARE DESIGN AND IMPLEMENTATION OF PACKET FAIR                |    |

| QUEUING ALGORITHMS                                                 | 59 |

| 5.1 DESIGN OF A DYNAMICALLY ADAPTABLE PFQ SCHEDULER                | 60 |

| 5.1.1 PFQ Schedulers                                               | 60 |

| 5.1.2 Block Level Design of a PFQ Architecture                     | 61 |

| 5.1.3 Design Challenges and Proposed Solutions                     | 63 |

| 5.1.3.1 Hardware Division                                          | 63 |

| 5.1.3.2 Dynamical Adaptation                                       | 65 |

| 5.1.3.3 Counter Aging                                              | 65 |

| 5.1.3.4 Searching                                          | 66  |

|------------------------------------------------------------|-----|

| 5.2 REVIEW OF THE PREVIOUS WORK ON THE HARDWARE            |     |

| IMPLEMENTATION OF PFQ SCHEDULERS                           | 66  |

| 5.3 IMPLEMENTATION OF WF <sup>2</sup> Q+ ALGORITHM ON FPGA | 69  |

| 5.4 PERFORMANCE MEASUREMENT                                | 72  |

| 5.5 CONCLUSIONS                                            | 75  |

| 6 A WINDOW BASED METHOD FOR PROVIDING QOS GUARANTE         | ES  |

| UNDER FLOW AGGREGATION                                     | 76  |

| 6.1 REVIEW OF THE PREVIOUS WORK ON FLOW AGGREGATION        | 77  |

| 6.2 WINDOW BASED FAIR AGGREGATOR                           | 81  |

| 6.2.1 Preliminaries                                        | 81  |

| 6.2.2 Window Based Fair Aggregator                         | 86  |

| 6.2.3 Calculation of w(t)                                  | 87  |

| 6.2.4 Packet Transmission                                  | 88  |

| 6.3 ANALYSISOF THE WINDOW BASED FAIR AGGREGATOR            | 90  |

| 6.3.1 Calculation of the Delay Bound                       | 93  |

| 6.4 IMPLEMENTATION AND TEST RESULTS                        | 95  |

| 6.5 CONCLUSIONS                                            | 98  |

| 7 SUMMARY AND CONCLUSIONS                                  | 100 |

| REFERENCES                                                 | 105 |

| CURRICULUM VITAE                                           | 120 |

## LIST OF TABLES

#### TABLES

| Table 4-1 The evaluation of the previous work on the software traffic                    |

|------------------------------------------------------------------------------------------|

| generators                                                                               |

| Table 4-2 The evaluation of the previous work on the hardware traffic                    |

| generators                                                                               |

| Table 4-3 The utilization of the FPGA resources for the Poisson traffic generator        |

| design                                                                                   |

| Table 4-4 Experiment loads and data rates    46                                          |

| Table 4-5 Differences between the empirical and computed CDF    48                       |

| Table 4-6 The utilization of the FPGA resources for the bursty traffic generator         |

| design                                                                                   |

| Table 4-7 Test results for bursty traffic generator together with the calculated $p$ and |

| q values and the desired traffic conditions                                              |

| Table 5-1 The basic structure of the look-up table which is used in the division         |

| operation                                                                                |

| Table 5-2 The utilization of the FPGA resources for the $WF^2Q$ + scheduler              |

| Table 5-3 The experiment results of the $WF^2Q$ + scheduler implementation               |

| Table 6-1 The experiment results of the WBFA implementation                              |

## **LIST OF FIGURES**

### FIGURES

| Figure 2-1 Typical interconnected network with several end systems and routers . 10    |

|----------------------------------------------------------------------------------------|

| Figure 2-2 The structure of a generic router 12                                        |

| Figure 3-1 The PCB layers as seen on the HyperLynx software user interface 20          |

| Figure 3-2 The basic building blocks of the data-processing board                      |

| Figure 3-3 The upper view of the data-processing board                                 |

| Figure 3-4 The building blocks of the backplane                                        |

| Figure 3-5 The top level schematic view of the backplane design as seen on the         |

| Mentor Graphics Design Architect                                                       |

| Figure 3-6 The hardware testbed                                                        |

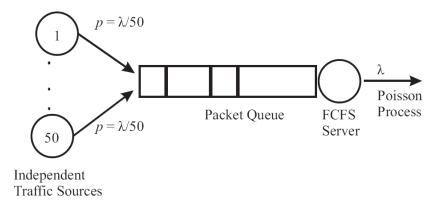

| Figure 4-1 The design idea of the Poisson traffic generator                            |

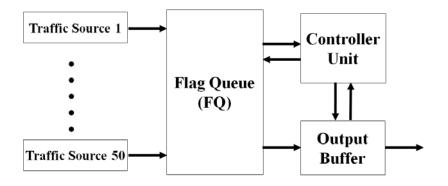

| Figure 4-2 The basic building blocks of the traffic generator design                   |

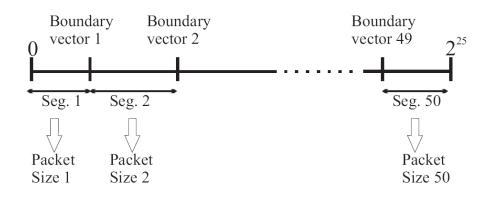

| Figure 4-3 The boundary vectors and the segments                                       |

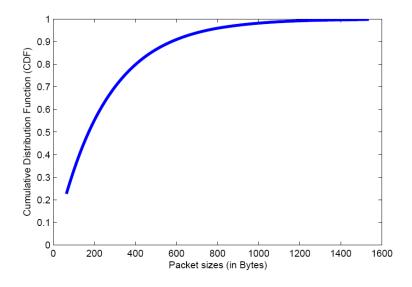

| Figure 4-4 The cumulative distribution of the packet sizes                             |

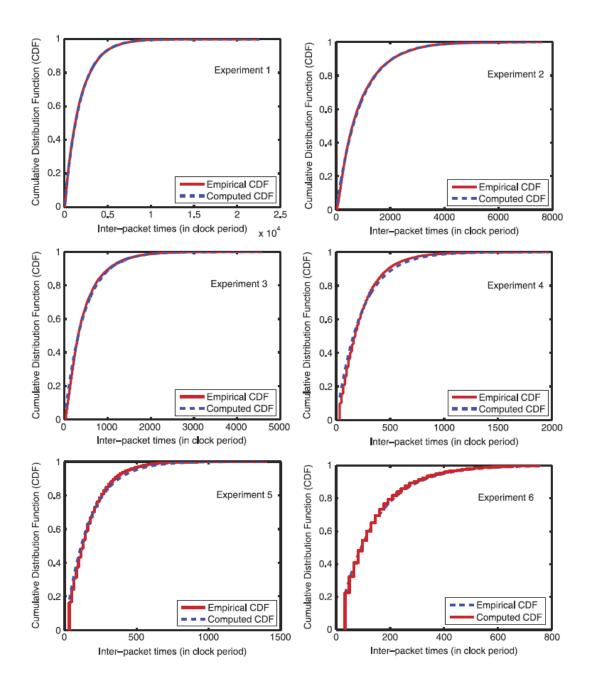

| Figure 4-5 Experiment results for the comparison of generated traffic distribution     |

| and the theoretical expectation                                                        |

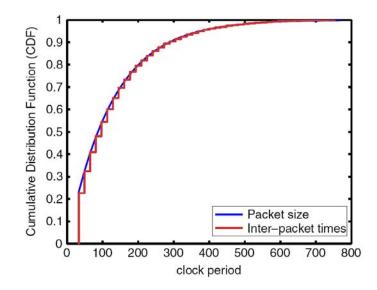

| Figure 4-6 CDFs for packet sizes and inter-packet times at $\rho_6 = 1$                |

| Figure 4-7 The state transition diagram of the bursty traffic generator design and the |

| probabilities corresponding to the state transitions                                   |

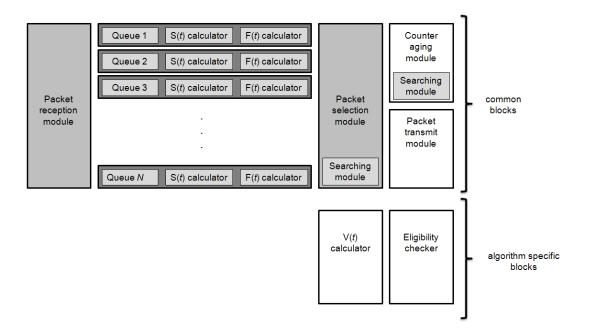

| Figure 5-1 The block level architecture of the PFQ schedulers                          |

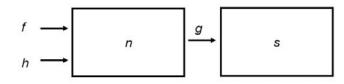

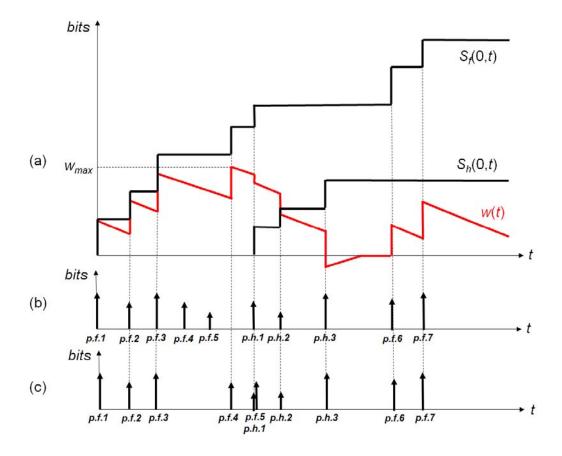

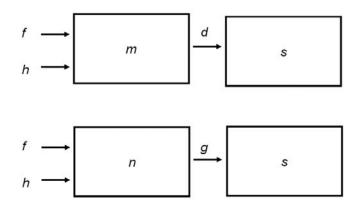

| Figure 6-1 An aggregator <i>n</i> and a scheduler <i>s</i> next to <i>n</i>    | . 83 |

|--------------------------------------------------------------------------------|------|

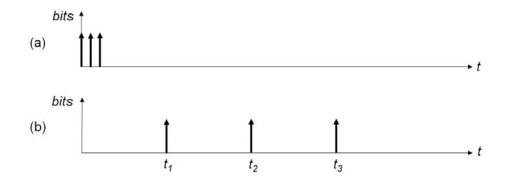

| Figure 6-2 (a) The arrival and (b) the departure times of the packets to       | the  |

| aggregator <i>n</i>                                                            | . 86 |

| Figure 6-3 An example for the operation of WBFA. (a) shows $w(t)$ and the serv | ice  |

| received by flows $f$ and $h$ , (b) shows the arrival times and sizes of       | the  |

| packets and (c) shows the departure times of the packets                       | . 90 |

| Figure 6-4 The aggregators <i>m</i> , <i>n</i> and the scheduler <i>s</i>      | . 91 |

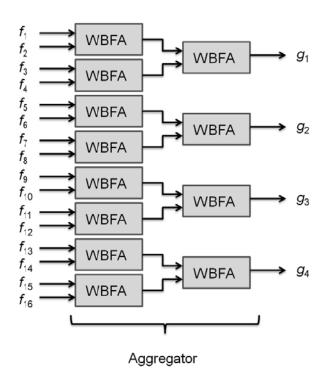

| Figure 6-5 The two level WBFA array structure                                  | . 97 |

## LIST OF ABBREVIATIONS

### ABBREVIATIONS

| ASIC  | : Application Specific Integrated Circuit    |

|-------|----------------------------------------------|

| ATM   | : Asynchronous Transfer Mode                 |

| BSFQ  | : Bin Sort Fair Queuing                      |

| BWRR  | : Budgeted Weighted Round Robin              |

| CAI   | : Work-Conserving Aggregation with Isolation |

| CDF   | : Cummulative Distribution Function          |

| CF    | : Continuous Framing                         |

| CLB   | : Configurable Logic Block                   |

| DDR   | : Double Data Rate                           |

| D-EDD | : Delay Earliest Due Date                    |

| DRAM  | : Dynamic Random Access Memory               |

| FAbS  | : Flow Aggregate based Services              |

| FAN   | : Flow Aware Networking                      |

| FCFS  | : First Come First Served                    |

| FIFO  | : First In First Out                         |

| FPGA  | : Field Programmable Gate Array              |

| FPGEN | : Fast Packet GENerator                      |

| FQ    | : Flag Queue                                 |

| FRR  | : Fair Round Robin                   |

|------|--------------------------------------|

| FSA  | : Flow State Aware Architecture      |

| GFS  | : Gigabit Fair Scheduling            |

| GPS  | : Global Processor Sharing           |

| GR   | : Guaranteed Rate                    |

| HOL  | : Head Of Line                       |

| HRR  | : Hierarchical Round Robin           |

| IP   | : Internet Protocol                  |

| KS   | : Kolmogorov-Simirnov                |

| LFSR | : Linear Feedback Shift Register     |

| LR   | : Latency Rate                       |

| MMBP | : Markov Modulated Bernoulli Process |

| NGN  | : Next Generation Network            |

| PCAP | : Packet CAPture                     |

| PCB  | : Printed Circuit Board              |

| PCI  | : Peripherial Component Interconnect |

| PFQ  | : Packet Fair Queuing                |

| PPS  | : Packets Per Second                 |

| PTG  | : Precise Traffic Generator          |

| QoS  | : Quality of Service                 |

| RAM  | : Random Access Memory               |

| RCSP | : Rate Controlled Static Priority    |

| RED  | : Random Early Detection             |

| RSE  | : RAM-based Searching Engine         |

|      |                                      |

| S&G                | : Stop and Go                                                     |

|--------------------|-------------------------------------------------------------------|

| SCFQ               | : Self Clocked Fair Queuing                                       |

| SFQ                | : Start time Fair Queuing                                         |

| SRAM               | : Static Random Access Memory                                     |

| SRR                | : Stratified Round Robin                                          |

| ТСР                | : Transmission Control Protocol                                   |

| TCRM               | : Traffic Controlled Rate Monotonic priority                      |

| TSFQ               | : Tiered Service Fair Queuing                                     |

| VHDL               | : Very high speed integrated circuit Hardware Decription Language |

| VOIP               | : Voice Over IP                                                   |

| WBFA               | : Window Based Fair Aggregator                                    |

| WF <sup>2</sup> Q  | : Worst Case Fair Weighted Fair Queuing                           |

| WF <sup>2</sup> Q+ | : Worst Case Fair Weighted Fair Queuing Plus                      |

| WFI                | : Worst case Fairness Index                                       |

| WFQ                | : Weighted Fair Queuing                                           |

|                    |                                                                   |

XOR : Exclusive OR

### **CHAPTER 1**

### **INTRODUCTION**

The services in the Next Generation Network (NGN) include real time applications such as IP telephony and video in addition to virtual environments and global or local information centers. These services will be created on demand by the customers and will be carried out with end-to-end Quality of Service (QoS) support such as bandwidth, delay and jitter guarantees [1]. The end-to-end QoS requires the classification of packets into flows on each network node on their path, storing them in per flow queues and employing a scheduler to decide for the service received by these queues. These are all data path operations which have to be executed for each packet hence they are implemented in hardware and their complexity affects the feasibility of the implementation.

The scheduling algorithms which are used in the QoS schedulers of the routers and the switches are one of the most important components determining the Quality of Service (QoS) performance of the Internet. In order to provide QoS support, the scheduling algorithms specify the order of transmission for the the packets that are queued at the output ports. The scheduling algorithms enable different services for different flows and affect the overall QoS closely. A good scheduling algorithm should efficiently utilize the network resources and provide protection between the flows. This protection should prevent some greedy flows from taking the service share of the other flows. The scheduling algorithm should also provide fairness by serving the flows in proportion to the agreed service shares. Another property that should be found in a good scheduling algorithm is flexibility. This property allows the algorithm to support different applications. While possessing these properties, the scheduling algorithm should be simple at the same time. This simplicity provides low algorithmic complexity and also low implementation complexity.

Generalized Processor Sharing (GPS) is an ideal hypothetical scheduling algorithm which can provide perfect protection among the flows [2, 3]. GPS is based on a fluid flow model where traffic flows are infinitely divisible and multiple flows can receive service simultaneously and the service share of each flow is proportional to its weight. GPS can provide network delay bound for leaky bucket constrained traffic [4-6]. However, in packet networks, the packet is the minimum service unit. As a result of this, GPS cannot be realized in packet networks.

With the intent of getting as close as possible to this ideal scheduling, a class of Packet Fair Queuing (PFQ) algorithms is proposed to emulate the behavior of GPS [7-17]. In all PFQ algorithms, there is a global function called virtual time which is used to track the progress of the GPS scheduler. For each head of line (HOL) packet of each flow in the system, a finish time is calculated. This finish time corresponds to the time that this packet would leave the GPS scheduler. Packets are then served in the order of their respective finish times.

All the PFQ algorithms, even the simpler ones have implementation difficulties which put a limit on the maximum number of flows supported for a fixed amount of implementation area. Calculations of the timestamp functions require hardware division. Also the scheduler needs to search the minimum time stamp value among many flows. The logic resources that is necessary to accomplish these tasks increase with the increasing number of flows.

In this thesis, different than the previous works that present designs for specific PFQ algorithms we propose a general framework that can be used to implement any given PFQ algorithm. To this end, we provide a block level architecture which separates

the general components that are common to all PFQ schedulers and the algorithmspecific components. In this architecture, we identify the design challenges and use techniques such as look-up-table based operations and dynamical adaptation of these tables to overcome these difficulties. We use our proposed architecture to implement a popular PFQ algorithm, i.e., Worst Case Fair Weighted Fair Queing Plus (WF<sup>2</sup>Q+) [16] on hardware. The algorithm is implemented on an FPGA (Field Programmable Gate Array) based board and the performance evaluation is performed on a hardware testbed. The main reason for selecting the FPGA as the hardware implementation medium is that the very high number of logic gates and embedded blocks in today's FPGAs enables the design of complex hardware platforms with reduced engineering cost and rapid turnaround time.

The complexity of the scheduling algorithms increases with the quality of the provided service. Furthermore the complexity increases with the number of flows that are scheduled. The schedulers are required to operate at wire speed and the execution of the scheduling algorithm has to be completed in a single packet time. As a consequence, when the number of flows exceeds a certain limit, the scheduling algorithm will be unable to continue its proper operation.

The commonly proposed solution for increasing the number of flows supported by the scheduler is simply employing the latest hardware technology to achieve the fastest implementation. However, the number of flows is always increasing with the new types of applications and the increasing number of devices connected to the Internet. Hence there will always be a limit on the number of flows supported by a given architecture. In addition, the cost of implementing such high-speed, highcapacity router with cutting edge technology is very high. Considering the dynamic network traffic profile with changing loads and flow patterns, it is expected that most of the time the router will be operating with smaller number of flows than it can actually support. This will lead to inefficient use of the investment. Another approach for building packet schedulers that support large number of flows is employing pipeline techniques which require less hardware resources in the expense of increased time to process each packet. In these approaches, the packets arriving at the instances of timestamp calculation and packet selection are discarded. In high data rates, the number of discarded packets can reach to an order of ten thousands [18]. Decreasing the per packet processing time in the pipelined approach requires expensive hardware resources as discussed in [19] which again leads to high cost implementations.

A third approach to support high number of flows is aggregating them to decrease the implementation complexity. The basic problem in flow aggregation is preserving QoS guarantees of the constituent flows in the aggregate. As a result of the greedy behavior of one of these flows, the others may receive decreased delay and fairness performance. This problem is tackled in [20] which proposes a network model that consists of flow aggregators and packet schedulers. In this work, it is proved that if the flow aggregation is performed fairly and the packet schedulers have certain properties, the end-to-end delay guarantees are preserved with respect to the case that no flow aggregation is performed. [20] presents two different approaches for the design of fair aggregators. The first one is "the basic fair aggregator" which limits the service rate for the aggregated flow to the sum of the reserved rates of the input flows. The second approach is "the greedy fair aggregator" which relaxes this limit only if all input flows have an arrival rate greater than their reserved rates. It is possible that the arrival rate of the flows to be aggregated exceed the total reserved rate temporarily. In such case even if there is available capacity to serve these flows, it will not be utilized.

In this thesis, we present Window Based Fair Aggregator (WBFA) and analytically show that it is a fair aggregator as defined in [20]. Hence, the individual delay bounds of the constituent flows aggregated by WBFA are preserved. Our approach allows the constituent flows to use the full capacity of the output channel until the difference in the service received by the flows reaches a limit. As a result of the increase in the utilization, the average end-to-end delays provided by WBFA are expected to be lower than the basic and greedy fair aggregators proposed by [20]. While increasing the utilization, WBFA also preserves the fairness of service to the aggregated flows. WBFA provides a tunable trade-off between the efficient use of the available bandwidth and the fairness among the constituent flows. In addition to these, WBFA has low implementation complexity and can be efficiently implemented on hardware. WBFA is implemented on an FPGA based board and its performance is measured in our hardware testbed.

The hardware testbed is designed in the context of this thesis. The testbed consists of several FPGA based boards and a backplane to connect these boards. The schematic design of the boards, PCB layout design, and manufacturing of the boards are done as a part of this thesis.

A traffic generator "FPGEN (Fast Packet GENerator)" [21] is designed to measure the performance of the schedulers that are implemented on the hardware testbed. FPGEN is a programmable random traffic generator which is entirely implemented on FPGA. FPGEN can generate variable packet size Internet traffic with Poisson and Markovian arrivals at OC-48 rate per interface. We present a model which overcomes the inherent difficulties of generating Poisson traffic on a serial interface due to the required independency between the packet sizes and the inter-packet times. In addition, FPGEN can generate Markov-modulated traffic entirely on hardware.

FPGEN is scalable to high-speeds as it is implemented purely on hardware without using any high level programming or processors. The packet generation times are randomly computed in real-time entirely using the logic resources of the FPGA. The FPGEN board has two OC-48 fiber-optical interfaces and operates at 125MHz. Hence, it is able to support a total traffic generation rate close to 5 Gbps and 250 million packets per second. FPGEN is configurable to generate traffic with different parameters due to the programmability of the FPGA. Our research on FPGEN includes the theoretical design of FPGEN, the hardware design of the FPGA-based traffic generator board and the implementation of FPGEN on FPGA.

The novel contributions of this thesis can be listed as follows.

A traffic generator "FPGEN" which can generate Poisson traffic and Markovmodulated on-off traffic is designed. The traffic generator is scalable to high speeds as a result of the operations being purely carried on hardware [21].

Generating traffic according to given statistics on a serial interface has inherent difficulties due to the required independence between the packet sizes and the interpacket times. We present a model which can overcome these difficulties for Poisson traffic and be implemented on hardware. To the best of our knowledge there is no other published work on a hardware-based packet generator that produces Poisson traffic with exponentially distributed packet sizes.

The previous approaches for generating Markov-modulated traffic include RAM based and processor based techniques. We apply our design approach to generate on-off traffic entirely on hardware.

For FPGEN, we provide hardware design details and performance measurement results that demonstrate the achieved rate and the statistical properties of the generated traffic.

We propose a general hardware architecture for the design of the family of PFQ schedulers. We use this architecture to identify the design challenges. We propose new design improvements and use previously presented approaches to overcome these difficulties.

Using our proposed architecture, we implement the  $WF^2Q+$  algorithm on hardware. We provide hardware design details. We make performance measurements and provide test results. We show that the results are within the theoretical limits.

We propose a novel flow aggregation algorithm "WBFA" and show analytically that WBFA is a fair aggregator. We calculate theoretical delay bounds for WBFA.

We implement WBFA on hardware and make performance measurements. We present the test results and show that the results agree with the theoretical delay bound.

The thesis is organized in seven chapters. In Chapter 2, QoS schedulers are described by introducing the basic concepts used throughout the thesis. Chapter 3 gives the details of the design of the hardware testbed. In Chapter 4, FPGEN traffic generator is explained in detail. Chapter 5 explains the design of the proposed PFQ architecture. Both theoretical design details and implementation results are given in this chapter. In Chapter 6, Window Based Fair Aggregator design is introduced. In this chapter, first it is shown analytically that WBFA is a fair aggregator. Then the hardware implementation of the WBFA is explained. Finally Chapter 7 summarizes the thesis and presents the conclusions.

## **CHAPTER 2**

## **SWITCHES FOR HIGH SPEED NETWORKS**

Everyday, Internet offers new benefits for the welfare of mankind. We have already adopted ourselves to file sharing, voice conversation, video meeting and streaming audio and video applications over the internet. The widespread usage of Voice Over IP (VOIP) and high definition video broadcasting is also on the way. When all of these applications are summed up, we need quite huge network bandwidth and strict quality of service support for the sake of being more tightly connected.

To support the demand for network bandwidth, optical fiber technology has grown very fast and found large application areas especially in backbone networks. Optical fiber technology enables the transmission of multi-gigabit data in one second over a single fiber line. By using many fiber lines in parallel and also adopting optical technologies such as wavelength converters, very high data rates are offered to support the growing bandwidth requirement. Due to the recent developments in optical fiber technology, huge carrying capacities are provided to the computer networks.

The widespread usage of the Internet and computer services has resulted in a rapid increase in the network traffic. In this traffic, an important part of the services require real-time data transmission. Audio and video streaming, video conferencing, internet telephony are a few examples of these kind of multimedia services. These services require large amount of network bandwidth and QoS support such as delay and jitter bounds and throughput guarantees.

In order to provide QoS support for the real-time services and also to utilize the resources such as bandwidth and buffers efficiently, packets should be assigned different priorities when accessing network resources. End to end QoS can be provided by allocating the network resources among flows according to the type of the packet data or the type of service that is purchased by the customer. In order to achieve this, the packets arriving from different flows are kept in separate queues. The QoS scheduler makes a choice among the head of line packets in these queues and selects the packet that is to be transmitted next.

QoS scheduling is a data plane function and is performed on every single packet in a computer network [22-24]. The data plane functions are required to be executed without slowing down the data transmission in a network device. This wire speed operation of a network device demands for extremely short packet processing times. In order to reach high data rates, packet processing applications such as classification, table look-up and header modification should take place in embedded hardware platforms. Packet buffering and buffer management requirements had further increased the importance of efficient implementation of schedulers in hardware.

#### **2.1 SWITCHES AND ROUTERS**

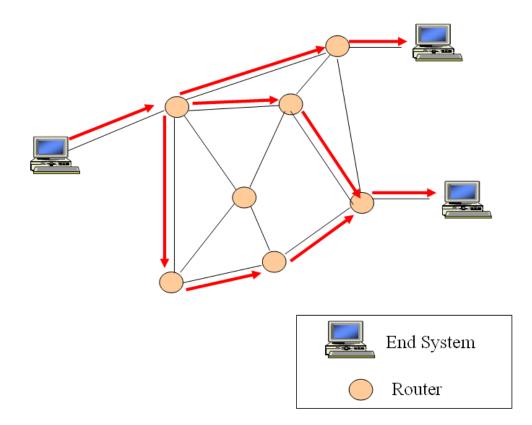

Internet is in fact, network of networks which are composed of millions of computing devices connected with communication links such as copper, radio, fiber, satellite, etc... In these networks, the data is routed among the end systems by the help of routers. The main job of a router is forwarding the packets from source to the recipients. Figure 2-1 shows a typical interconnected network with several end systems and routers.

Figure 2-1 Typical interconnected network with several end systems and routers.

When a packet is received, the router first looks up the packet destination address in the forwarding table to identify the outgoing ports. Then, it manipulates the header according to the needs and sends the packet to the output ports. In the output ports, the packet is queued and finally transmitted onto the outgoing link.

While a router is a layer-3 device, a switch is a layer-2 device that operates on Ethernet frames. The hardware of both devices is similar but the router has additional layer-3 software. Hence, in this thesis, our focus will be on the network switches.

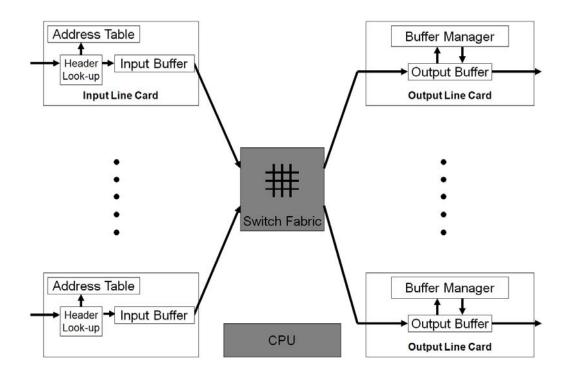

Generic switch architecture is composed of input and output ports which are called line cards, switch fabric and CPU. Figure 2-2 shows the structure of a generic router. Line cards are entry and exit points of data in the router. They connect external network to switch fabric. Many physical layer actions such as signal conversions between different domains, synchronization and frame processing take place in the line cards. Switch fabric connects the input and output ports of the router and performs the task of switching. After switching, the packets are queued at the buffers of the output line cards. The packet that will be delivered to the output line is selected by the QoS scheduler at the output line card. The goal of the QoS scheduler is to provide different service and different priorities for different traffic sources. CPU deals with general management and maintenance of the router such as updating address tables, collecting packet statistics, etc...

One of the most important characteristics of the router architecture is the switch fabric's speedup. Speedup is defined as the ratio of the data rate that can be switched to an output port to line rate. If the speedup is 1, that is the switch fabric speed is the same as that of the network line, all the packets are queued at the input line cards waiting for the switching fabric. Assuming that the router has N input and N output ports, if the speedup is greater than 1 but smaller than N, some of the packets will wait for the switch fabric in the buffers at the input line cards. Ideal performance is achieved when speedup is N. In this case, packets do not need to wait for the switch fabric because the switch fabric is fast enough to serve the packets coming from all the ports as if there were only one input port. The packets are queued only in the buffers at the output line cards of the router. When speedup is N, the QoS scheduler has access to all the packets waiting in the router, hence "speedup=N" is the best case for the QoS support.

Figure 2-2 The structure of a generic router.

#### **2.2 QUALITY OF SERVICE SCHEDULERS**

Quality of service is the ability to have resource guarantees and service differentiation so that the applications which are delay, jitter or loss sensitive can perform satisfactorily. QoS can be provided by giving relative priorities and defining different levels of service to different flows and packets in the network. In order to provide QoS support, the QoS scheduler specifies the order in which the packets queued at the output ports are actually transmitted. The QoS scheduler gives different service to different connections.

In today's switches, increasing QoS requirements have put a significant emphasis on the design of schedulers. Schedulers are generally evaluated using performance metrics such as complexity, delay bound, worst case fairness index (WFI) and required buffer space. The complexity is related with the computational resources required for the execution of the scheduling algorithm. Delay bound is the highest possible delay that a packet can encounter under defined traffic conditions. WFI is a parameter that is used to measure the discrepancy between the scheduling algorithm and GPS. Required buffer space tells the amount of packet data that needs to be buffered in the scheduler.

QoS schedulers have two main classes. These are sorted priority based and frame based schedulers. The sorted priority based scheduler computes a timestamp for each arriving packet with respect to current system state and the system is updated accordingly. The scheduler sorts the packets based on their timestamps. This type of schedulers provides tight end-to-end delay bounds. However, computation of the timestamp for each packet, maintaining priority queues and performing computations at line rate results in high complexity. Weighted Fair Queuing (WFQ) [2, 3], Self Clocked Fair Queuing (SCFQ) [7], Delay Earliest Due Date (D-EDD) [25], Rate Controlled Static Priority (RCSP) [26] and Traffic Controlled Rate Monotonic Priority Scheduling (TCRM) [27] are examples of sorted priority based schedulers.

The frame based scheduler splits time into frames and limits the amount of traffic that can be transmitted during a frame period [10]. There might be an additional delay component to smooth the bursts over the frames. This type of schedulers can provide bandwidth guarantees and have low complexity. Stop and Go (S&G) [28], Hierarchical Round Robin (HRR) [29], Continuous Framing (CF) [30] and Budgeted Weighted Round Robin (BWRR) [31] are examples of frame based schedulers.

To ensure the QoS requirements, the traffic has to be shaped and defined according to special traffic models before entering the network. (r, T),  $(\sigma, \rho)$ , and  $(X_{min}, X_{ave}, I, S_{max})$  are widely used traffic models. In (r, T) model, r is a measure of the average data rate. In an interval of length T, no more than rT bits are transmitted. In  $(\sigma, \rho)$  model,  $\sigma$  indicates the maximum burst size and  $\rho$  indicates the long term bounding rate. In an interval of length *T*, no more than  $(\sigma + \rho T)$  packets are transmitted. In  $(X_{min}, X_{ave}, I, S_{max})$  model,  $X_{min}$  denotes the minimum inter-arrival time between the packets and  $X_{ave}$  denotes the average inter-arrival time between the packets measured over an interval of length *I*.  $S_{max}$  denotes the minimum packet size. In some cases, there may be a need for shaping the traffic at each scheduler. To achieve this, each scheduler has a traffic regulator.

#### 2.2.1 Packet Fair Queuing Schedulers

The ideal scheduling is provided by the hypothetical GPS scheduler. GPS uses a fluid flow model and assumes that the flows are infinitely divisible and multiple flows can receive service at the same time. Despite its ideal scheduling performance, GPS cannot be used in packet switching networks where packet is the smallest service unit. There are different schedulers introduced for use in packet networks. PFQ schedulers try to emulate the behavior of GPS in packet networks.

PFQ schedulers work with  $(\sigma, \rho)$  traffic model. The scheduler first computes the time the packet would complete service when all the connections receive fair service. This value is called "finish number". All the packets are served with this order. The scheduling algorithm is priority based. The finish numbers need to be ordered. The provided end to end delay bound increases with the number of switches on the route.

Weighted Fair Queuing (WFQ) [2, 3] algorithm is known to be the first PFQ algorithm. As long as a flow is leaky bucket constrained, WFQ can provide end-toend delay bound similar to the GPS. It is proven that WFQ does not fall behind the GPS by more than one maximum size packet but it can be ahead of the GPS [15]. The complexity of WFQ is O(V) where V denotes the number of available connections. The complexity comes from computing the timestamp and maintaining the priority queues. The buffer requirement increases in each switch on the route. Due to the high complexity of the algorithm, implementation is very difficult.

Worst Case Fair Weighted Fair Queuing (WF<sup>2</sup>Q) algorithm [15] tries to improve WFQ by using an eligibility test in the selection of the packets. When the scheduler is selecting a packet for transmission, the scheduler considers only the eligible packets which are the set of packets that have started service in the emulated GPS system. WF<sup>2</sup>Q can provide almost the same service as the GPS. The maximum service difference is one maximum packet size [15].

Both WFQ and WF<sup>2</sup>Q have a major drawback of computational complexity. The time complexity of both of the algorithms is O(N) where *N* is the number of flows [23]. WF<sup>2</sup>Q+ [16] is an enhanced version of WF<sup>2</sup>Q and it has less time complexity. WF<sup>2</sup>Q+ computes the virtual time function without emulating the GPS. As a result of this, it can provide worst case fairness properties with utilizing simpler calculations. This leads to increased implementation efficiency on hardware platforms.

Several other scheduling algorithms are also proposed to emulate GPS behavior in different ways. SCFQ [7] and Start Time Fair Queuing (SFQ) [32] try to simplify the emulation of GPS by using efficient virtual time functions. Bin Sort Fair Queuing (BSFQ) [33], Stratified Round Robin (SRR) [34], Fair Round Robin (FRR) [35] and Tiered Service Fair Queuing (TSFQ) [36] uses quantization to simplify the emulation.

## **CHAPTER 3**

### HARDWARE TESTBED

In this thesis, QoS schedulers are designed and implemented in hardware. Also, new architectures are designed and their performance is evaluated on FPGA. In order to use in our hardware implementations and performance measurements, a digital hardware testbed is designed and produced.

#### **3.1 IDENTIFICATION OF THE DESIGN REQUIREMENTS**

The network testbed will contain several data-processing boards and a backplane to organize the communication between the boards. Each one of the data-processing boards should contain a processor for the generation, processing and scheduling of packets, a flash memory to keep non-volatile data, rs-232 interface to connect the board to a PC, DC power converters to produce the different voltage levels required on the board, VME-64 connectors for backplane connection and a PCB designed with special care to prevent signal coupling between the lines at high data rates. Also, fiberoptical transceivers should be used to reach high data rates.

#### 3.1.1 Selection of the Processor

In the implementation of network applications, the choice of the hardware platform affects speed, cost, design time, area requirement, power dissipation and maintenance capabilities. Network applications are implemented on several device families such as general purpose processors, embedded reduced instruction set computer (RISC) processors, network processors, application specific integrated circuits (ASIC), and field programmable gate arrays (FPGA). Each of these families of devices offers specific benefits and drawbacks. A comparison of these families is provided below.

#### **3.1.1.1 General Purpose Processors**

General purpose processors are preferred because they are very well-known, they are rather cheap and they offer very elastic usage. However, these processors are not optimized for the network operations. The implementations on these processors cannot take the advantage of bit-level parallelism and concurrency. Their memory access time is rather long. As a result of this, they cannot succeed at high line speeds.

#### 3.1.1.2 Embedded RISC Processors

They are preferred because of their low power dissipation and small area requirement. Nevertheless, they have the same drawbacks as that of general purpose processors. Also, their operating frequency is lower than general purpose processors [37].

#### 3.1.1.3 Network Processors

Network processors can analyze the packet headers, implement look-up operations, and determine the output port of the packet very rapidly. The high throughput offered by the network processors is a result of their multi-thread operation and their multi-chip architecture. However, the processing of packets which belong to the same connection by different processors destroys the order of the packets. Hence, network processors cannot be used for the implementation of most scheduling algorithms. Also, in order to have proper scheduler architecture, the

execution time of each operation in the processor should be well known by the designer. This makes it necessary to adopt the scheduling algorithm to the processor's command set. Unfortunately, the implementation result varies according to the processor architecture [37, 38].

#### 3.1.1.4 ASIC

ASIC designs achieve the fastest and most successful results for the network applications. However, ASIC design is quite expensive and takes long time. After the design is completed, it is not possible to make modifications on the design [39]. Because of the fact that electronic technology grows very rapidly, ASIC cannot respond to the modification and maintenance needs in the network systems. As a result of these, ASIC designs are rather expensive and do not provide elasticity required for the network applications.

#### 3.1.1.5 FPGA

FPGA designs do not need long design time as ASIC. FPGA technology provides a suitable design environment for the schedulers with many logic cells and high clock speed. The design modifications and improvements can be achieved easily on the FPGA. Also, FPGA design can be the first step to the ASIC design.

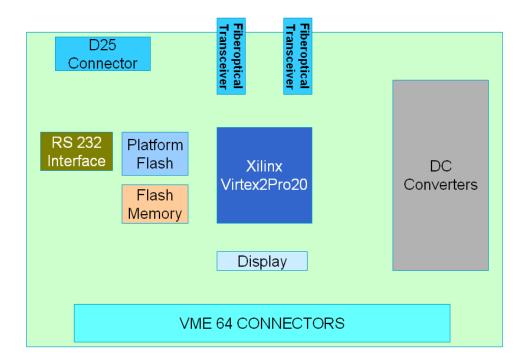

In the light of the given relative strengths and weaknesses of possible processor choices, FPGA is preferred for the scheduler implementations in this thesis. Our trial implementations showed that the FPGA should have more than 10000 cells and should support clock frequencies higher than 100 MHz. Also, the FPGA should have more than 400 user configurable I/O for memory interfaces and backplane connections. Xilinx Virtex2Pro20FF1152 is selected because of its widely tested architecture and rich library support. It has 20000 cells and 652 user I/O. An onboard crystal oscillator provides 125MHz clock signal to the FPGA. Intel 28F640 is selected as the flash memory because of its short access time and our available

experience on the product. The platform flash memory is selected as Xilinx XCF16P. Visual Studio .NET platform is selected to communicate with the board through a graphical user interface.

## 3.2 HARDWARE DESIGN OF THE DATA-PROCESSING BOARDS

The hardware design started with the schematic design of the boards. The connections of the FPGA, other integrated circuits, power conversion and distribution circuitry, and clock circuitry are specified on the Mentor Graphics Design Architect software as huge sheets of logic design.

After schematic design, layout of the printed circuit board (PCB) is designed on the same software. The PCB is designed with special care on the spacing between the lines. There are more than 1000 signal lines connected to the FPGA and to be able to pass the ball grids, signal line width is selected as 5 mils. The PCB has 14 layers and a total thickness of 1.8 mm. Gerber files are simulated with HyperLynx software for signal coupling. The simulations showed that the coupling between any of the lines is no more than 300 mV. Figure 3-1 shows the PCB layers as seen on the HyperLynx software user interface.

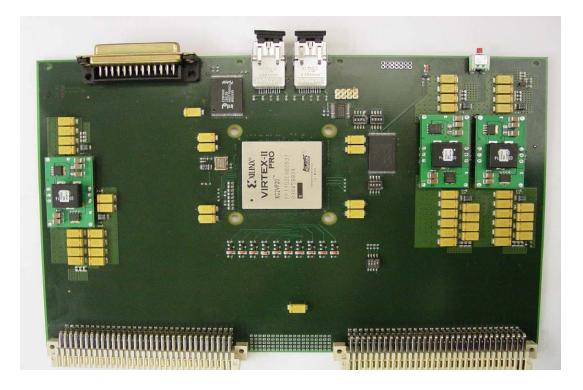

The PCB is produced in ILFA, Germany. The basic building blocks of the dataprocessing board is given in Figure 3-2. Figure 3-3 shows the upper view of the data-processing board.

|    | Layer Name | Usage       | Thickness<br>um, gram | Er            | Diff Z0<br>ohm | Width<br>um | Gap<br>um | Z0<br>Curve |

|----|------------|-------------|-----------------------|---------------|----------------|-------------|-----------|-------------|

| 1  |            | Solder Mask | 18                    | 3.3           |                |             |           | 1           |

| 2  | LVDS1      | Signal      | 18                    | <auto></auto> | 100            | 100         | 103.545   |             |

| 3  |            | Substrate   | 100                   | 4.3           |                |             |           |             |

| 4  | GND1       | Solid Plane | 35                    | <auto></auto> |                |             |           |             |

| 5  |            | Substrate   | 100                   | 4.3           |                |             |           |             |

| 6  | VCC1       | Solid Plane | 35                    | <auto></auto> |                |             |           |             |

| 7  |            | Substrate   | 100                   | 4.3           |                |             |           |             |

| 3  | VCC2       | Solid Plane | 35                    | <auto></auto> |                |             |           |             |

| 9  |            | Substrate   | 100                   | 4.3           |                |             |           |             |

| 10 | VCC3       | Solid Plane | 35                    | <auto></auto> |                |             |           |             |

| 11 |            | Substrate   | 100                   | 4.3           |                |             |           |             |

| 12 | TTL1       | Signal      | 18                    | <auto></auto> | 100            | 100         | 280.014   |             |

| 13 |            | Substrate   | 100                   | 4.3           |                |             |           |             |

| 14 | TTL2       | Signal      | 18                    | <auto></auto> | 100            | 100         | 131.096   |             |

| 15 |            | Substrate   | 100                   | 4.3           |                |             |           |             |

| 16 | LVDS2      | Signal      | 18                    | <auto></auto> | 97             | 150         | 200.697   |             |

| 17 |            | Substrate   | 200                   | 4.3           |                |             |           |             |

| 18 | GND2       | Solid Plane | 18                    | <auto></auto> |                |             |           |             |

| 19 |            | Substrate   | 200                   | 4.3           |                |             |           |             |

| 20 | LVDS3      | Signal      | 18                    | <auto></auto> | 95             | 100         | 124.208   |             |

| 21 |            | Substrate   | 200                   | 4.3           |                |             |           |             |

| 22 | GND3       | Solid Plane | 18                    | <auto></auto> |                |             |           |             |

| 23 |            | Substrate   | 100                   | 4.3           |                |             |           |             |

| 24 | LVDS4      | Signal      | 18                    | <auto></auto> | 105            | 100         | 127.241   |             |

| 25 |            | Solder Mask | 18                    | 3.3           |                |             |           |             |

Figure 3-1 The PCB layers as seen on the HyperLynx software user interface.

Figure 3-2 The basic building blocks of the data-processing board.

Figure 3-3 The upper view of the data-processing board.

#### **3.3 HARDWARE DESIGN OF THE BACKPLANE**

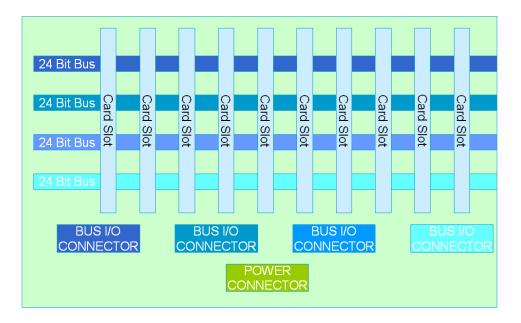

The backplane connects the data-processing boards with four 24-bit busses. Figure 3-4 shows the building blocks of the backplane. The bus lines are connected to D-25 connectors for further extension requirements and testing purposes. Also, the backplane distributes the 5V power to the data-processing boards. Same design steps are followed for the design of the backplane. The top level schematic view of the backplane design as seen on the Mentor Graphics Design Architect software is given in Figure 3-5.

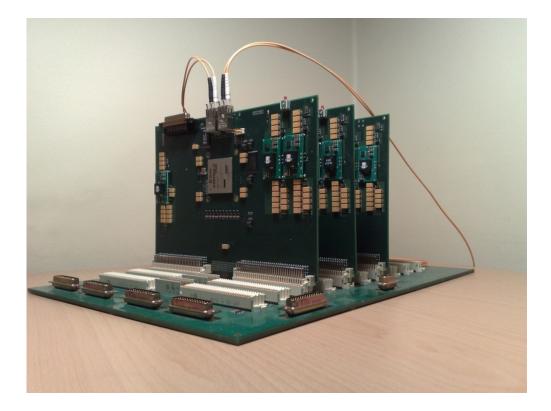

After the production of the data-processing boards and the backplane, each board is tested for design and manufacturing errors. Following the tests, the data processing boards are integrated to the backplane to form the final testbed. Figure 3-6 shows the hardware testbed.

Figure 3-4 The building blocks of the backplane.

Figure 3-5 The top level schematic view of the backplane design as seen on the Mentor Graphics Design Architect.

Figure 3-6 The hardware testbed.

#### **3.4 LOGIC DESIGN WITH FPGA**

FPGA is composed of thousands of configurable logic blocks (CLB). These logic blocks are configured during the implementation of the design according to the required hardware structure. The hardware behavior is first defined with one of the hardware description languages: VHDL or Verilog. Then, the system behavior is tested with one of the simulation tools: Xilinx ISE Simulator or Modelsim. These simulation tools have specific libraries for each family of FPGA devices and could perform realistic results. After the simulation, the design is implemented in hardware. In the implementation phase, the signals are assigned to the selected FPGA pins, time constraints are used to force the place and route process to optimize the length of the routes and placement of the design. After that, a BIT file is generated. This file contains all the information for the implementation of the

design and defines the configuration of the logic blocks and the routing between the logic blocks. The BIT file is loaded onto the hardware using IMPACT software and Xilinx Parallel JTAG Programming Cable. The behavior of the system can be tested by observing the signals on hardware by using the software ChipscopePro. This software uses JTAG pins of the FPGA to monitor the signals and displays the results on PC with a graphical interface.

In this thesis work, VHDL is used for hardware description. Xilinx ISE 9.2 is used as code development environment. ChipscopePro 9 is used for hardware testing.

### **CHAPTER 4**

# FPGEN: A FAST, PROGRAMMABLE TRAFFIC GENERATOR

The increasing bandwidth and the variety of new applications of computer networks continuously motivate both academic and industrial research for the development of new network equipment such as switches and routers as well as new applications and protocols. In this respect, traffic generators are required to test and evaluate the performance of network applications, protocols, equipments or an entire network under predetermined load conditions. The packets can be generated with a traffic pattern according to a stochastic specification or based on a previously collected trace. Network equipment manufacturers use traffic generators to test their equipment in the laboratory environment and to demonstrate their capabilities to their customers. Benchmark tests are performed in evaluation labs to test and certify the equipments from different manufacturers by the help of very capable (and expensive) traffic generators [40-42].

There is a large number of academic studies on the design and evaluation of different switch architectures, fabric and QoS scheduling algorithms and buffer management strategies. Important performance metrics such as packet delay and loss depend on the management and scheduling of the buffers. These metrics are evaluated analytically by modeling the buffers as queuing systems with traffic arrivals such as Poisson, Bernoulli or Markov-modulated processes [43–52]. Hence,

traffic generators which can produce packets according to these certain processes can demonstrate the accuracy of the analytical performance results when the proposed architecture is implemented in hardware.

The traffic generators are required to be scalable to high speeds (in bit and packet rates) and configurable to generate traffic according to the desired shape. While software-based traffic generators [53–60] can produce a wide variety of traffic patterns, they cannot reach high packet and bit rates [61]. Hence, design and implementation of high-speed packet generators that can generate the intended traffic properties on hardware is an important research issue.

The commonly used hardware platform for packet generator design in the previous academic literature is FPGA. Today's FPGAs comprise a very high number of logic gates and embedded blocks in small packages. When compared to full custom designs, FPGA technology enables the design of complex hardware platforms with reduced engineering cost and rapid turnaround time. Furthermore, FPGA-based prototype production is an important step for the verification of the expensive and time-critical ASIC projects [62]. It is possible to convert a hardware design on FPGA to ASIC provided that power source design, packaging and boundary scan testing constraints are taken into consideration [63].

Previous work on hardware packet generators features techniques that limit the scalability and flexibility of the design such as computing the packet generation times and packet sizes using on-board processors [64] and external computers [65], or relying on previously collected packet generation statistics at the expense of a memory access for each packet generation [66, 67]. Some of these previous studies are implemented and tested on hardware [64–67] while some of them are only simulated in software [68, 69]. Furthermore there is no evaluation of the generated traffic according to the desired statistics.

In this chapter, we present the design, implementation and performance evaluation of a hardware-based packet generator FPGEN (Fast Packet GENerator). FPGEN can generate Poisson traffic with exponentially distributed packet sizes and Markov modulated on–off traffic which are widely adopted traffic models. To this end, FPGEN can be used to evaluate the performance of switch fabric architectures, buffer managers and QoS support mechanisms such as schedulers and packet classifiers. The contributions of our research are as follows.

Firstly, our implementation is scalable to high-speeds as it is carried out purely on hardware without using any high level programming or processors. The packet generation times are computed in real-time entirely using the logic resources of the FPGA. FPGEN does not depend on any collected traffic trace and can be configured to generate traffic with different parameters exploiting the programmability of the FPGA. The hardware design of FPGEN can generate one packet per clock period per interface. This rate scales linearly with the number of interfaces and can be achieved for both Poisson and on–off traffic types. The FPGEN board has two interfaces and operates at 125 MHz which enables a maximum packet generation rate of 125 Million packets/second (pps) per interface and 250 Mpps total. FPGEN can fully utilize the two OC-48 fiberoptic interfaces and generate a maximum of 2.5 Gbps traffic per interface and a total of 5 Gbps. We provide the hardware implementation details and experiment results to demonstrate the capabilities of FPGEN. We did not find any previous work on hardware packet generators with such a detailed description of the design to justify the claimed packet and bit rates.

Generating traffic according to given statistics on a serial interface has inherent difficulties due to the required independence between the packet sizes and the interpacket times. The second contribution of this work is presenting a model which can overcome these difficulties for Poisson traffic and be implemented on hardware. To the best of our knowledge there is no other published work on a hardware-based packet generator that produces Poisson traffic with exponentially distributed packet sizes.

Generation of Markov-modulated on–off traffic is studied before in [68, 69, 64]. However, the used techniques in the previous work are RAM-based and processor based. The third contribution of our work is applying our design approach to generate on–off traffic entirely on hardware.

Finally the fourth contribution of our work is the hardware design details, the experimental study carried out on hardware and its results that demonstrate not only the rate achieved by FPGEN but also the statistical properties of the generated traffic. [64–67] provide measurements of packet rate on hardware. However there is no presentation of the hardware design such as its state machine structure which can demonstrate the maximum number of clock periods to generate a packet. We provide the implementation details to justify that our design is capable of generating one packet per clock period per interface and this rate scales linearly with the number of interfaces. In addition, our experimental study shows that the interpacket times and packet sizes for the Poisson traffic and the average burst sizes and the load achieved for Markov-modulated on–off bursty traffic achieve the targeted statistical properties.

The remainder of the chapter is organized as follows. In Section 4.1, we summarize and discuss the previous work in the literature on traffic generators. We introduce the conceptual design followed by the hardware design and implementation of the Poisson traffic generation of FPGEN in Section 4.2. Furthermore, we demonstrate the generated traffic rates and their statistics. We present the design and evaluation of the Markov-modulated on–off traffic generation of FPGEN in Section 4.3. We summarize the features of FPGEN in Section 4.4, after demonstrating them by our experimental studies. Our conclusions are given in Section 4.5.

# 4.1 SYNTHETIC TRAFFIC GENERATION FOR THE PERFORMANCE EVALUATION OF COMPUTER NETWORKS

Performance evaluation studies in computer networking research require synthetic traffic generation. To this end, traffic generators are used to replicate the traffic conditions of the specific network environment that the device or the protocol under test will be deployed on. According to the device, component or protocol to be tested different parameters of the generated traffic are significant. While the packet rate is important to test a packet classifier or a packet scheduler, the load conditions, the inter-packet time and packet size distribution have to be considered to test a new buffer management algorithm. The validity of statistical approaches can only be justified with precise replication of the assumed traffic conditions.

# 4.1.1. Proprietary Hardware Traffic Generators and Software Traffic Generators

Traffic generators can be software or hardware-based. The hardware-based packet generators such as [41, 42] are usually professionally developed and purchased at expensive prices by network device manufacturers. These hardware packet generators can achieve high packet and data rates with different traffic profiles, however due to their cost and proprietary design they do not fit well into the academic networking research.

There are a number of software-based traffic generators which provide flexible configurable environments at low costs. However, the bit and packet rates and the statistical accuracy of the generated traffic depend on the hardware that the software runs on. Botta et al. [61] present a detailed recent study on the performance of software traffic generators. In this study four packet level traffic generators [57–60] ([60] is also described in [54, 55]) are selected according to their popularity.

The results of [61] are summarized in Table 4-1. It is observed that the software traffic generators fail to achieve the imposed packet rate starting from fairly low rates. It is also observed that beyond 500 Mbps with the minimum-sized packets, the throughput capabilities of the investigated generators saturate. Furthermore starting from even lower rates the inter-packet times of the generated traffic are found to deviate from the expected distribution. The reason for this behavior is stated as the lack of dedicated buffers as opposed to hardware implementations and the involvement of the CPU which is an expensive operation.

Table 4-1 The evaluation of the previous work on the software traffic generators[61].

| Name, ref.       | Traffic type(s)                         | Kpps | Mbps |

|------------------|-----------------------------------------|------|------|

| TG, [57]         | Constant, uniform, exponential, on/off  | 70   | 600  |

| MGEN, [58]       | Constant, exponential, on/off           | 70   | 600  |

| RUDE/CRUDE, [59] | Constant                                | 80   | 500  |

| D-ITG, [60]      | Constant, uniform, exponential, Pareto, | 130  | 500  |

|                  | Cuchy, normal, Poisson, gamma, on/off   |      |      |

#### 4.1.2. FPGA-Based Hardware Traffic Generators

FPGA-based hardware traffic generators both exploit the programmability of the FPGA to provide flexible implementation and avoid the problems of the software traffic generators as discussed above. Furthermore generation of traffic at high rates demands for concurrency, bit-level parallelism, high operating frequency and short memory access time which can be provided by the FPGA platform.

Traffic generation with certain statistical behavior requires a random number generator which does not repeat itself for a sufficiently long time, state machine structures for bursty traffic generation and different queues to aggregate traffic or store packets before they are transmitted. It is possible to design hardware random number generators on FPGA with very long periods until they repeat. Furthermore FPGA provides appropriate infrastructure for state machine implementation and ready to use blocks such as FIFO queues.

Generating a packet includes a number of steps such as deciding the packet transmission time, its size, its header and payload content that are independent from each other. Different packet streams can be generated independently both for multiplexing to achieve certain aggregate behavior or for transmitting on different interfaces. While, implementing these steps on a processor results in the sequential and hence slow execution, the structure of the FPGA is very convenient for designing logic circuits which are working in parallel. This enables the designer to use high degrees of concurrency and thus shorten the total execution time. Another favorable feature of the FPGA is that the execution time of each operation on the hardware is well known by the designer. This is very important especially while generating traffic according to a specific distribution in real-time to test a networking device.

Other features that make FPGAs preferred platforms for the design of traffic generators are their affordability, short development time and flexibility thanks to their programmability. After the FPGA design, the generated design files can easily be converted to ASIC designs with small effort [62, 63].

We present a comparative evaluation of FPGA-based hardware traffic generators in the literature with FPGEN in Table 4-2. Related work dates back to 1996 motivated by the then high-speed ATM technology [69]. In this study, the maximum traffic generation rate is computed as 4.5 Gbps by simply multiplying the trigger rate of 12 MHz and 53 bytes per ATM cell. However, no experimental results are reported to demonstrate that the packets are indeed generated at the stated maximum achievable rate with the correct stochastic distribution. In addition, no discussion is provided on the capability of the state machine structure in the designs to generate a new packet in each clock period.

| Table 4-2 The evaluation of the previous work on the hardware traffic generators. |

|-----------------------------------------------------------------------------------|

| Sim: Simulation, HW: Hardware, Mpps: Million packets per second.                  |

| Ref., year             | Traffic type(s), packet                                                                                                                                    | Platform, approach,                                                                                                    | Freq, max bps                                                                  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                        | size(s)                                                                                                                                                    | implementation                                                                                                         |                                                                                |

| [69], 1996             | Markov Modulated<br>Bernoulli Process<br>(MMBP), fixed size<br>(ATM Cell, 53 bytes)                                                                        | Altera MAX Plus II2<br>[37], state machine, sim                                                                        | 12 MHz, 4.5 Gbps                                                               |

| [67], 2002             | Long-range dependent,<br>4 different packet sizes:<br>40, 256, 512, 1500 bytes                                                                             | Altera FLEXIOK250E-<br>1, time-series data<br>stored in RAM is used<br>to represent the<br>transmitted traffic, HW     | 12 MHz, 4.5 Gbps                                                               |

| [68], 2005             | Bernoulli, 2-state<br>Markov modulated,<br>packet sizes are not<br>specified                                                                               | Xilinx Virtex-4 FPGA<br>[38], state machine, sim                                                                       | 20 MHz, BW is not specified                                                    |

| [64], 2006             | Self-similar, Bernouilli,<br>Markov-modulated, 5<br>different packet sizes:<br>40, 512, 600, 700, 1500<br>bytes                                            | Altera<br>EP1SGX40GF1020<br>Stratix GX, on board<br>NiOS processor is<br>programmed to generate<br>packets, HW         | 155.52 MHz, OC-48                                                              |

| [66], 2009             | Any traffic type, any size                                                                                                                                 | Xilinx Virtex II Pro 50<br>FPGA, PCAP file that is<br>loaded into SRAM is<br>replayed, HW                              | Not specified, 1 Gbps<br>per interface, total: 4<br>Gbps                       |

| [65], 2009             | Any traffic type, only<br>packet headers                                                                                                                   | Xilinx Virtex II Pro 50<br>FPGA, controls the<br>timing of packets<br>received from asoftware<br>traffic generator, HW | 33 MHz (PCI freq.),<br>total: 1 Gbps (Limited<br>by PCI bus)                   |

| [21]<br>FPGEN,<br>2010 | Poisson traffic, 2-state<br>Markov modulated, 50<br>different packet sizes<br>(min: 64 bytes, max:<br>1536 bytes) payloads<br>can be created as<br>needed. | Xilinx Virtex II Pro 20<br>FPGA, linear feedback<br>shift register for<br>generating random<br>variables, HW           | 125 MHz, 125 Mpps<br>and 2.5 Gbps per<br>interface, total: 250<br>Mpps, 5 Gbps |

In [67], the interarrival times for the packets are first stored in a 64 megabyte offchip memory in time-series format and then loaded into an FPGA via a PCI interface. The size of the memory determines the time period that the packet generation process repeats. The time-series data has predetermined intervals of 1, 10, 100 and 1000 ms, and an OC-48 rate of 2.36 Gbps is reached for packet sizes that are larger than 512 bytes. The statistical correctness of the generated traffic is demonstrated by comparing the Hurst parameters of the original time-series data and the measured time-series data. The implementation platform does not work standalone and requires a PC to work with. Furthermore the authors do not explain if it is possible to generate the payload of the packets.

The arrivals are generated using probability values that are stored in RAMs in [68]. The correct operation of the packet generator is verified using stimulus written in System C, and cosimulated with the Verilog HDL implementation, using the Synopsys VCS-MX simulator. In the implementation of this design, triggers are generated instead of real packets. Hence, no packet size or maximum achievable data rate information is provided.

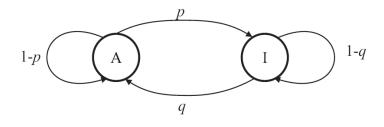

[64] is the most advanced and the fastest stage of a series of traffic generators with the same design approach that are developed by the same authors. In this approach, the traffic generator is coded in C and downloaded to an NiOS processor. The processor runs the Micro C OS II operating system. Whereby it has to be noted that the use of a processor instead of a pure hardware design limits the system performance. Five different packet sizes are supported.