## AN FPGA BASED BLDC MOTOR CONTROL SYSTEM

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

SERDAR UYGUR

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

FEBRUARY 2012

Approval of the thesis:

### AN FPGA BASED BLDC MOTOR CONTROL SYSTEM

submitted by SERDAR UYGUR in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan ÖZGEN<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>          |  |

|------------------------------------------------------------------------------------------------|--|

| Prof. Dr. İsmet ERKMEN<br>Head of Department, <b>Electrical and Electronics Engineering</b>    |  |

| Prof. Dr. Hasan Cengiz Güran<br>Supervisor, Electrical and Electronics Engineering Dept., METU |  |

|                                                                                                |  |

| Examining Committee Members:                                                                   |  |

| Prof. Dr. Muammer ERMİŞ<br>Electrical and Electronics Engineering Dept., METU                  |  |

| Prof. Dr. Hasan Cengiz GÜRAN<br>Electrical and Electronics Engineering Dept., METU             |  |

| Assoc. Prof. Dr. Cüneyt F. BAZLAMAÇCI<br>Electrical and Electronics Engineering Dept., METU    |  |

| Assist. Prof. Dr. İlkay ULUSOY<br>Electrical and Electronics Engineering Dept., METU           |  |

| Ali YILMAZKOÇLAR, M.Sc.<br>TÜBİTAK-SAGE, ETB                                                   |  |

|                                                                                                |  |

Date:

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: SERDAR UYGUR

Signature :

# ABSTRACT

#### AN FPGA BASED BLDC MOTOR CONTROL SYSTEM

Uygur, Serdar M.Sc., Department of Electrical and Electronics Engineering Supervisor : Prof. Dr. Hasan Cengiz Güran

February 2012, 148 pages

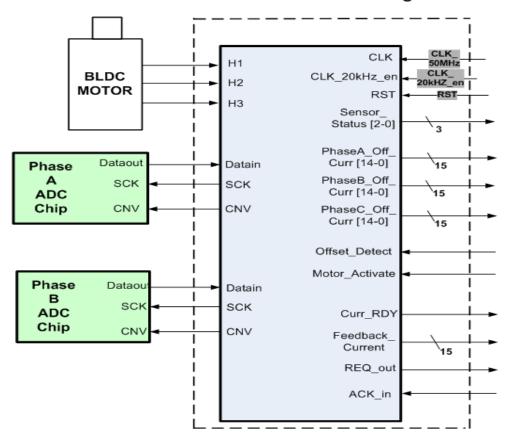

In this thesis, position and current control systems for a brushless DC (Direct Current) motor are designed and integrated into one FPGA (Field Programmable Gate Array) chip. Experimental results are obtained by driving the brushless DC motors of Control Actuation System of a guided missile. Because of their high performance, brushless DC motors are widely used in Control Actuation Systems of guided missiles. In order to control the motor torque, current controller is designed and implemented in the FPGA. Position controller is designed to fulfill the position commands. A soft processor in the FPGA is used to connect and configure the current controller, position sensor interfaces and communication modules such as UART (Universal Asynchronous Receiver Transmitter) and Spacewire. In addition; position controller is implemented to implement control algorithms, power converter circuitry and to perform other tasks such as communication with PC (Personal Computer). In order to monitor the behavior of the controllers in real time and to achieve performance tests, a graphical user interface is provided.

Keywords: Brushless DC Motor, Current Control, Position Control, FPGA, Soft Processor

#### FPGA TABANLI FIRÇASIZ DOĞRU AKIM MOTOR KONTROL SİSTEMİ

Uygur, Serdar Yüksek Lisans, Elektrik Elektronik Mühendisliği Bölümü Tez Yöneticisi : Prof. Dr. Hasan Cengiz GÜRAN

Şubat 2012, 148 sayfa

Bu tezde firçasız doğru akım motoru için pozisyon ve akım kontrol sistemleri tasarlanmış ve alan programlanabilir kapılar dizisinde (FPGA) çalıştırılmıştır. Deneysel sonuçlar güdümlü bir füzenin kanat tahrik sistemindeki fırçasız doğru akım motorları kontrol edilerek elde edilmiştir. Fırçasız doğru akım motorları yüksek performanslarından dolayı güdümlü füzelerin kanat tahrik sistemlerinde yaygın olarak kullanılmaktadır. Motor torkunu kontrol etmek için akım kontrolcü tasarlanmış ve alan programlanabilir kapılar dizisinde (FPGA) çalıştırılmıştır. Sonra pozisyon komutlarını yerine getirmek için pozsiyon kontrolcü tasarlanmıştır. Akım kontrolcü, pozisyon algılayıcı arayüzü ve haberleşme modüllerini (UART, Spacewire) birbirine bağlamak ve modülleri konfigüre etmek için alan programlanabilir kapılar dizisinde yazılımsal işlemci kullanılmıştır. Buna ek olarak pozisyon kontrolcü yazılımsal işlemci üzerinde çalıştırılmıştır. Kontrol algoritmalarını, güç çevirici devresini çalıştırmak ve kullanıcı bilgisayarı ile haberleşmek için alan programlanabilir kapılar dizisi tabanlı bir elektronik kart tasarlanmış ve üretilmiştir. Kontrol algoritmalarının davranışlarını gerçek zamanlı izlemek için ve performans testlerini gerçekleştirebilmek için bir kullanıcı arayüz programı hazırlanmıştır.

Anahtar Kelimeler: Fırçasız Doğru Akım Motoru, Akım Kontrol, Pozisyon Kontrol, FPGA, Yazılımsal İşlemci To My Family, To My Fiance

# ACKNOWLEDGMENTS

I would like to thank my supervisor Prof. Dr. Hasan Cengiz GÜRAN, for his guidance, understanding and patience. Throughout the preparation of this thesis, he provided encouragement, sound advice, and lots of good ideas.

I am very grateful to TÜBİTAK-SAGE for providing tools and other facilities throughout the production of my thesis.

I would like to show my gratitude to colleagues, who supported this work in both technical and moral aspects.

I would like to thank my family and fiance for all their help during my thesis.

# TABLE OF CONTENTS

| ABSTR  | ACT     |                                            | iv  |

|--------|---------|--------------------------------------------|-----|

| ÖZ     |         |                                            | v   |

| ACKNC  | WLEDO   | GMENTS                                     | iii |

| TABLE  | OF CON  | TENTS                                      | ix  |

| LIST O | F TABLE | ES                                         | xi  |

| LIST O | F FIGUR | ES                                         | iii |

| LIST O | F ABBRI | EVIATIONS                                  | XX  |

| СНАРТ  | ERS     |                                            |     |

| 1      | INTRO   | DUCTION AND MOTIVATION                     | 1   |

| 2      | MOTO    | R DRIVER CONTROL SYSTEM DESIGN             | 6   |

|        | 2.1     | Electronic Board Design                    | 6   |

|        |         | 2.1.1 Structure of the FPGA Design         | 17  |

|        | 2.2     | Graphical User Interface Design            | 23  |

|        | 2.3     | Test Setup                                 | 26  |

| 3      | DESIG   | N AND IMPLEMENTATION OF CURRENT CONTROLLER | 30  |

|        | 3.1     | Current Controller Design                  | 31  |

|        |         | 3.1.1 Current Acquisition                  | 39  |

|        |         | 3.1.2 Phase Detection                      | 47  |

|       |       | 3.1.3    | Current Integrator                    |

|-------|-------|----------|---------------------------------------|

|       |       | 3.1.4    | Average Current Calculation           |

|       |       | 3.1.5    | Offset Current Detection              |

|       |       | 3.1.6    | Offset Current Subtraction            |

|       |       | 3.1.7    | Error Current Calculation             |

|       |       | 3.1.8    | PI Controller                         |

|       |       | 3.1.9    | Pulse Width Generator                 |

|       |       | 3.1.10   | Commutation Control                   |

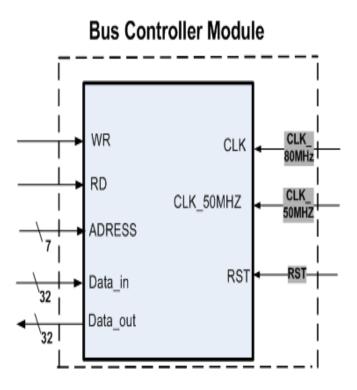

|       | 3.2   | Bus Con  | troller Design                        |

|       | 3.3   | Matlab S | imulations                            |

|       | 3.4   | Experime | ental Results                         |

| 4     | POSIT | ION CON  | TROLLER DESIGN AND IMPLEMENTATION 121 |

|       | 4.1   | PID Con  | troller                               |

|       | 4.2   | I-PD Cor | ntroller                              |

|       | 4.3   | Encoder  | Interface                             |

|       | 4.4   | Matlab S | imulations                            |

|       | 4.5   | Experime | ental Results                         |

| 5     | CONCI | LUSION   |                                       |

| REFER | ENCES |          |                                       |

# LIST OF TABLES

# TABLES

| Table 2.1  | Summary of the FPGA utilization characteristics for the motor control system | 19  |

|------------|------------------------------------------------------------------------------|-----|

| Table 3.1  | Configurable Parameters of the Current Controller Module                     | 34  |

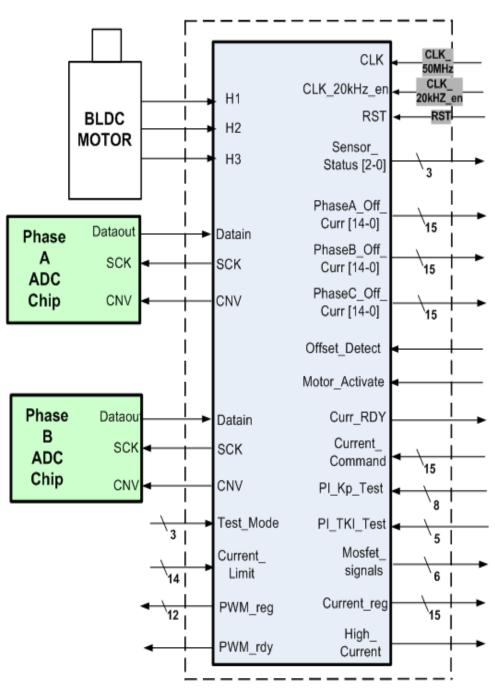

| Table 3.2  | Input, Output ports of the Current Controller Module                         | 36  |

| Table 3.3  | Continuation of the Input, Output ports of the Current Controller Module .   | 37  |

| Table 3.4  | Input, Output ports of the Current Acquisition Module                        | 41  |

| Table 3.5  | Current sensor and ADC sensitivity parameters                                | 44  |

| Table 3.6  | Inputs and Outputs of the Phase Current Detection State Machine              | 47  |

| Table 3.7  | Port Decsriptions of the Phase Detection Module                              | 49  |

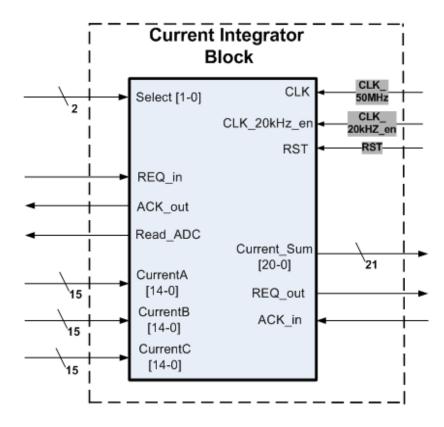

| Table 3.8  | Port Decsriptions of the Current Integrator Module                           | 51  |

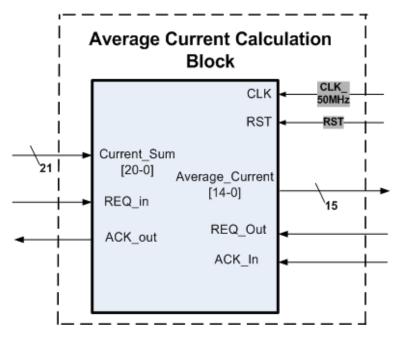

| Table 3.9  | Port Decsriptions of the Average Current Calculation Module                  | 57  |

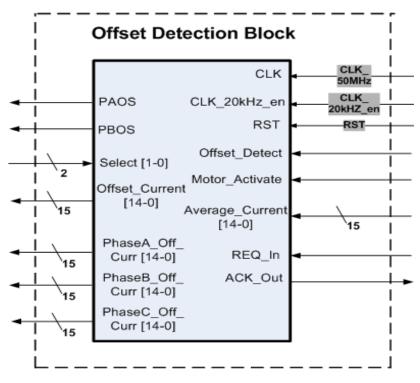

| Table 3.10 | Port Decsriptions of the Offset Detection Module                             | 62  |

| Table 3.11 | Motor Excitation and Sensor Outputs for Clockwise Rotation                   | 87  |

| Table 3.12 | Commutation Table of the Motor                                               | 87  |

| Table 3.13 | Port Decsriptions of the Bus Controller VHDL Module                          | 93  |

| Table 3.14 | Registers of the Bus Controller Module                                       | 94  |

| Table 3.15 | Spacewire Packet Structure                                                   | 102 |

| Table 4.1 | PID System Parameters for $\xi = 1$ . | • | • | • | • | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | • | • | • | 126 |

|-----------|---------------------------------------|---|---|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|---|---|---|-----|

| Table 4.2 | I-PD System Parameters for $\xi = 1$  |   | • |   | • |   |   |   |   |   |       | • |   |   |   | • | • |   | • | • |   | 129 |

# **LIST OF FIGURES**

## FIGURES

| Figure 1.1  | Block Diagram of the Control System                            | 4  |

|-------------|----------------------------------------------------------------|----|

| Figure 2.1  | General Diagram of the Motor Control System                    | 7  |

| Figure 2.2  | Block Diagram of the Electronic Board                          | 8  |

| Figure 2.3  | Data-Strobe Encoding                                           | 11 |

| Figure 2.4  | Structure of the Inverter Circuit                              | 12 |

| Figure 2.5  | Functional Block Diagram of Isolation Chip [14]                | 12 |

| Figure 2.6  | Functional Block Diagram of Motor Driver Circuit               | 13 |

| Figure 2.7  | Current measurement with three shunt resistors                 | 14 |

| Figure 2.8  | Functional Block Diagram of the Current Sensor [16]            | 15 |

| Figure 2.9  | Functional Block Diagram of the Current Sensing Circuit        | 16 |

| Figure 2.10 | Functional Block Diagram of the FPGA Design                    | 18 |

| Figure 2.11 | Functional Block Diagram of the Microblaze Processor Core [17] | 20 |

| Figure 2.12 | 2 Three Stage Pipeline Structure of the Microblaze Core [17]   | 21 |

| Figure 2.13 | Settings Part of the GUI                                       | 23 |

| Figure 2.14 | Current Control Test Parameters Window of the GUI              | 24 |

| Figure 2.15 | Position Control Test Parameters Window of the GUI             | 25 |

| Figure 2.16 Test Control Part of the GUI                                                                            | 26 |

|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.17 Test Results of a Current Control Experiment                                                            | 27 |

| Figure 2.18 Structure of the Test Setup                                                                             | 28 |

| Figure 2.19 An Overview of the SpaceWire Brick Hardware Architecture [18]                                           | 29 |

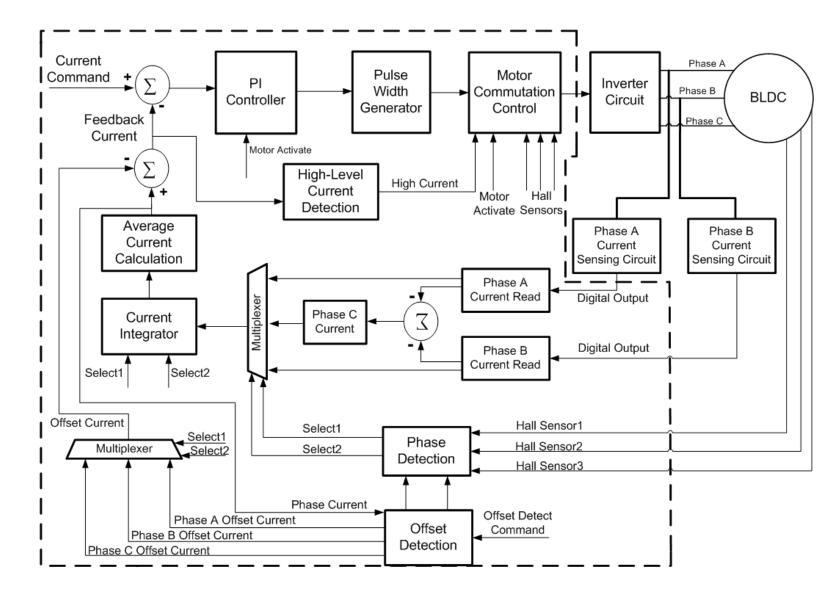

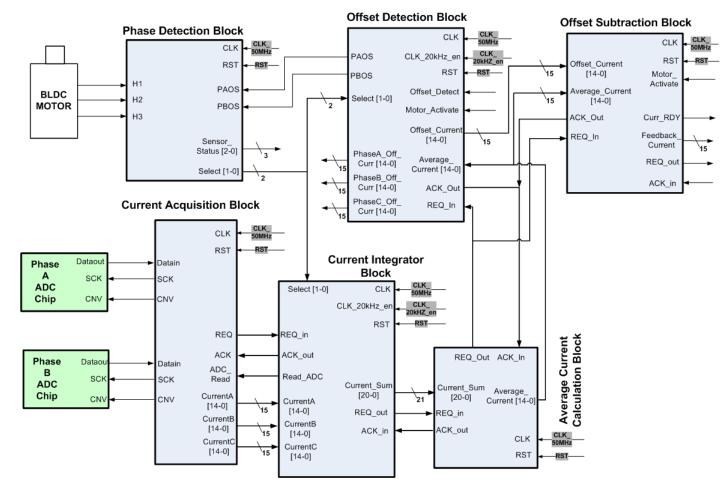

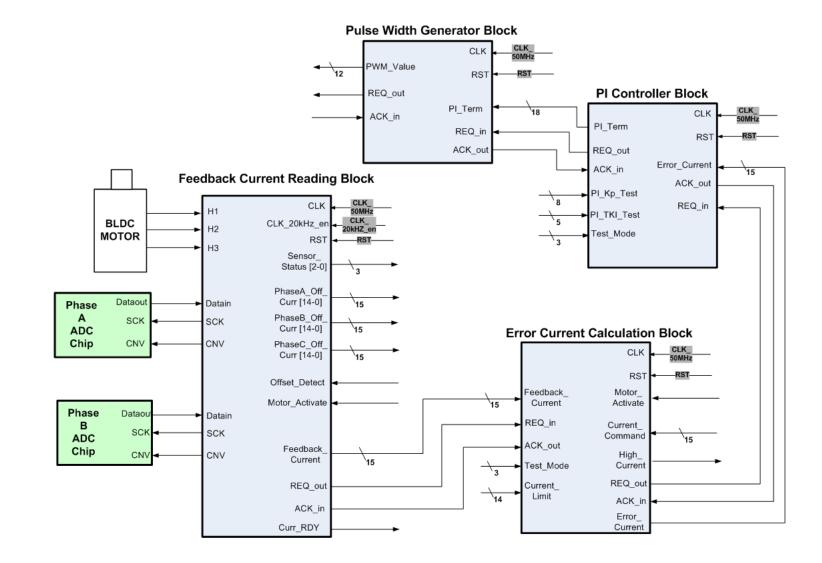

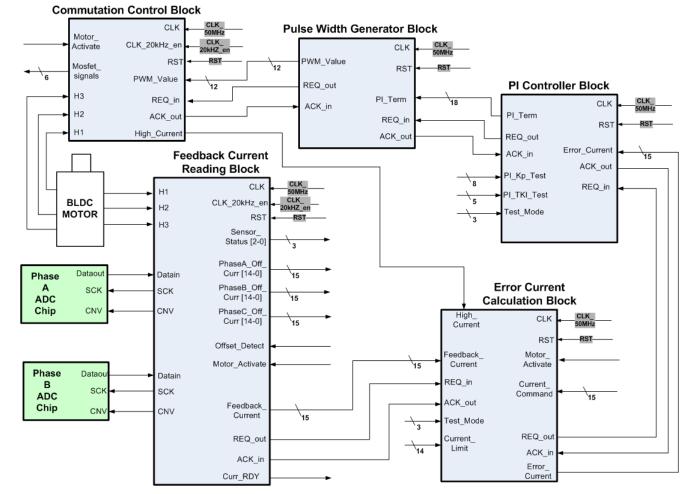

| Figure 3.1 Functional Block Diagram of the Current Controller                                                       | 32 |

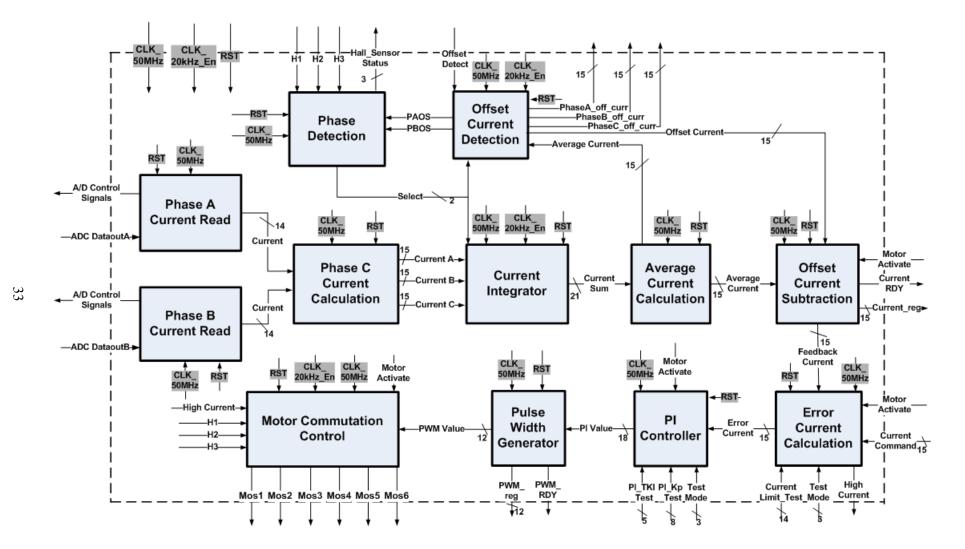

| Figure 3.2 Structure of the Current Controller VHDL Module                                                          | 33 |

| Figure 3.3    Configurable parameters window of the current controller on the EDK plat-      form                   | 35 |

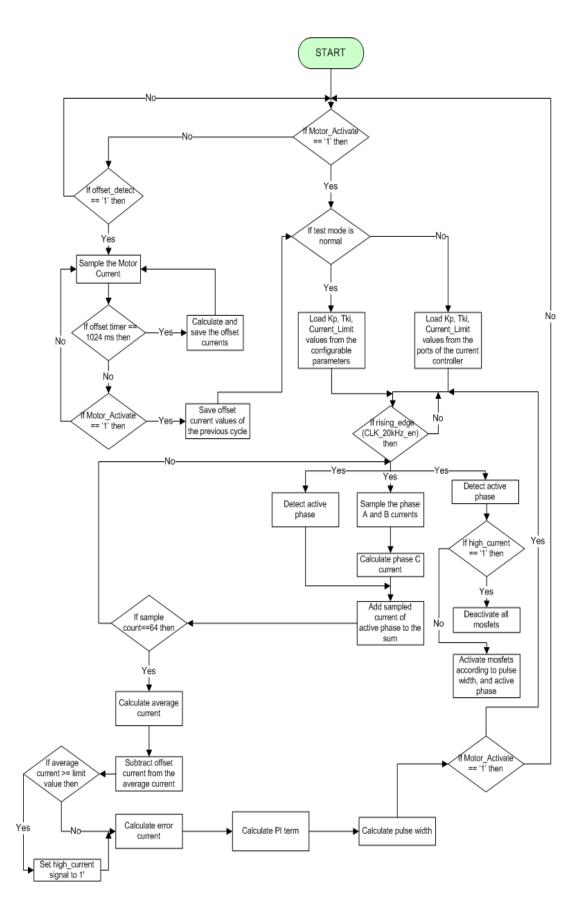

| Figure 3.4 Flowchart of the current controller VHDL module                                                          | 38 |

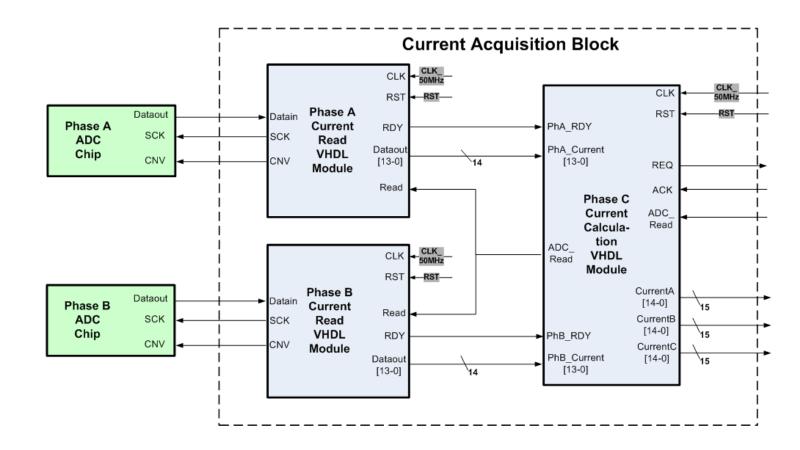

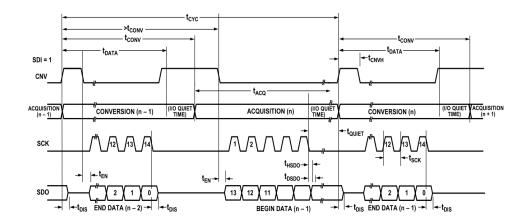

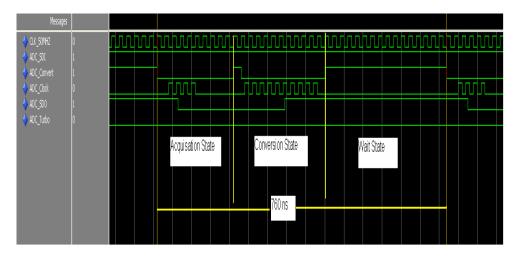

| Figure 3.5 Structure of the current acquisition block                                                               | 40 |

| Figure 3.6 Serial Interface Timing Diagram of AD7944 chip [19]                                                      | 43 |

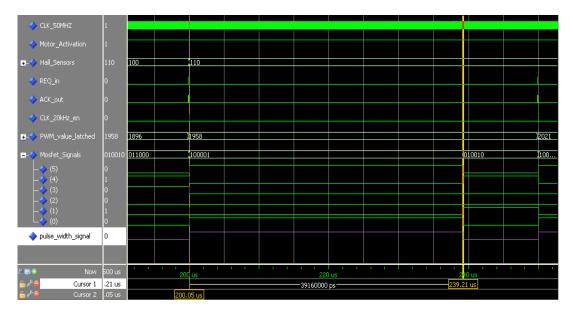

| Figure 3.7 Simulation of ADC Driver Code for One Sampling Cycle                                                     | 43 |

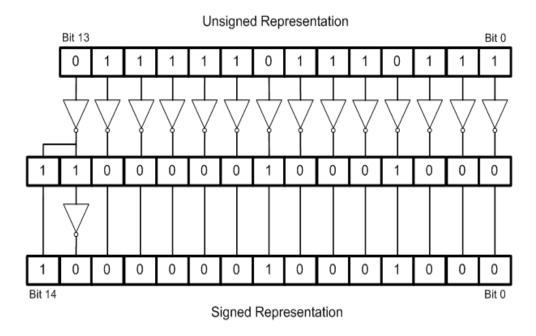

| Figure 3.8 Current Scaling of the Negative-Valued Currents                                                          | 45 |

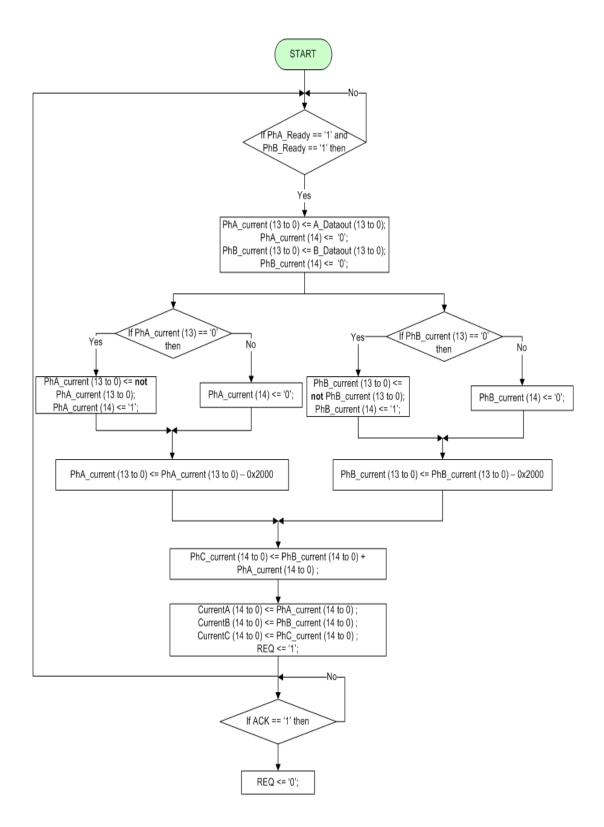

| Figure 3.9 Flowchart of the current acquisition block                                                               | 46 |

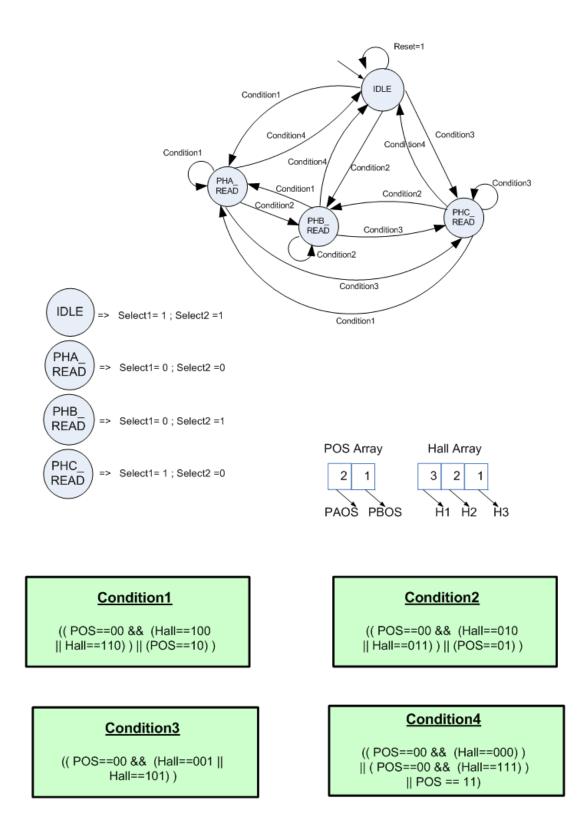

| Figure 3.10 State Machine Diagram of the Phase Detection VHDL Module                                                | 48 |

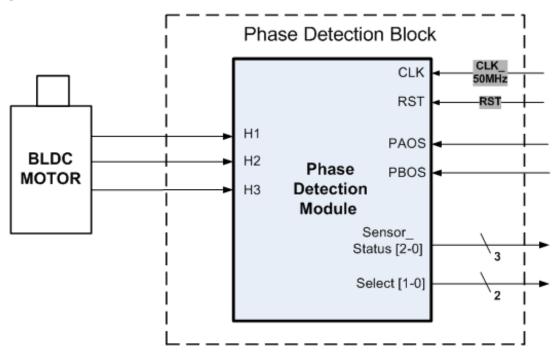

| Figure 3.11 Phase detection VHDL module                                                                             | 49 |

| Figure 3.12 Sampling of the Current Feedback                                                                        | 50 |

| Figure 3.13 Current Integrator VHDL Module                                                                          | 51 |

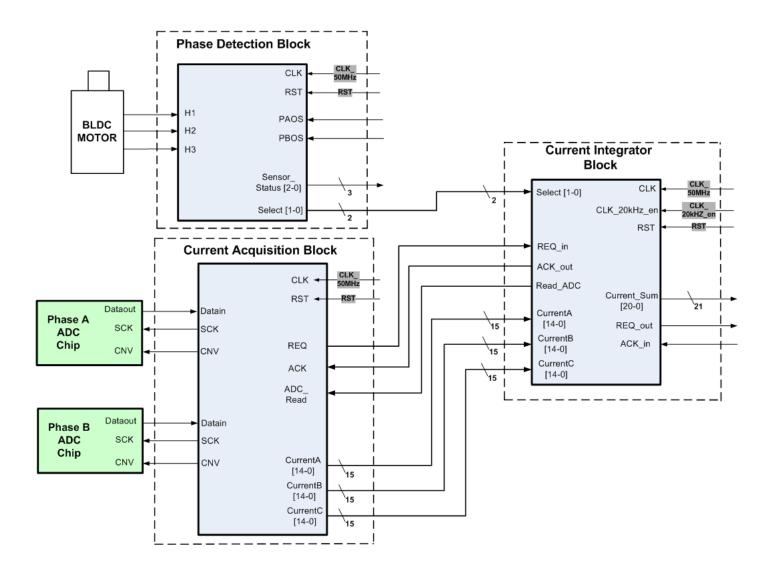

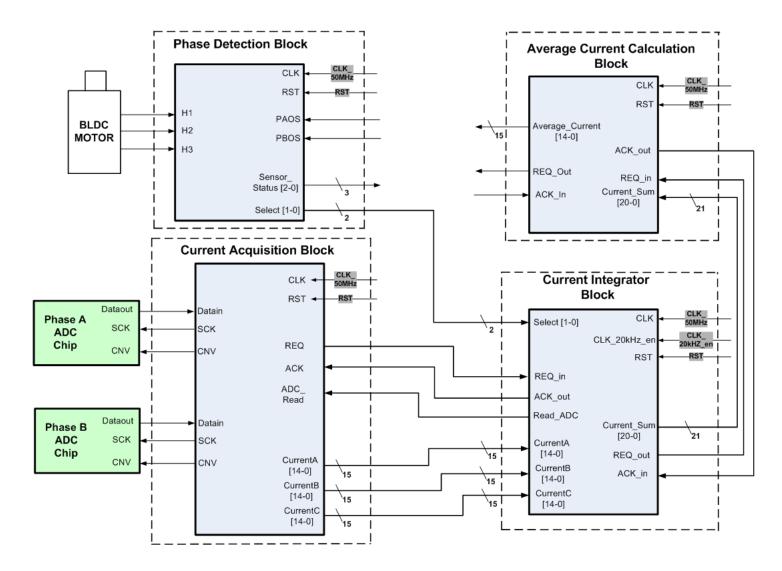

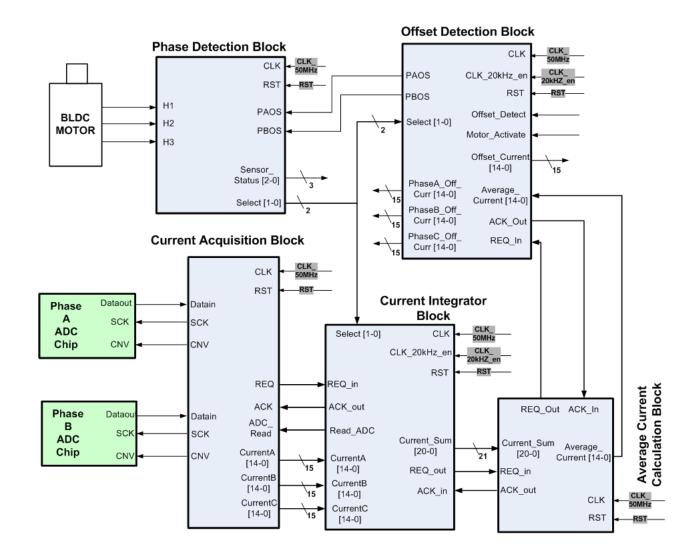

| Figure 3.14 Connection between the current integrator module, current acquisition block and phase detection modules | 53 |

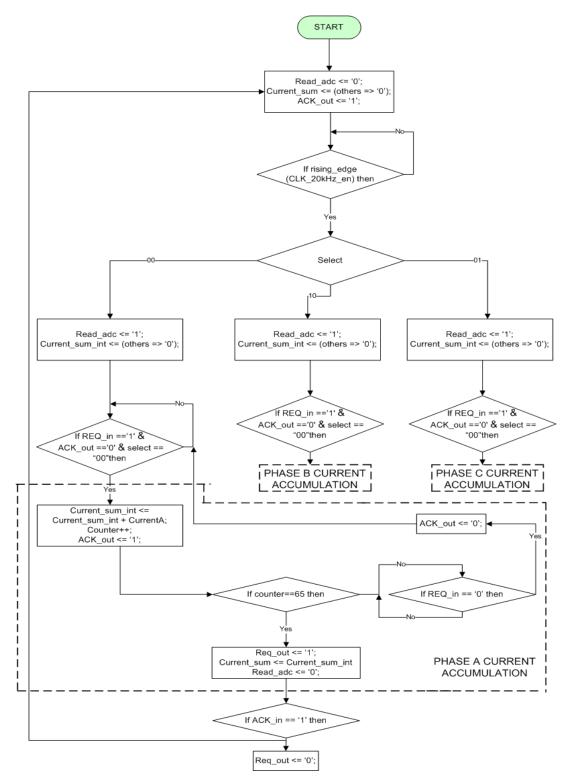

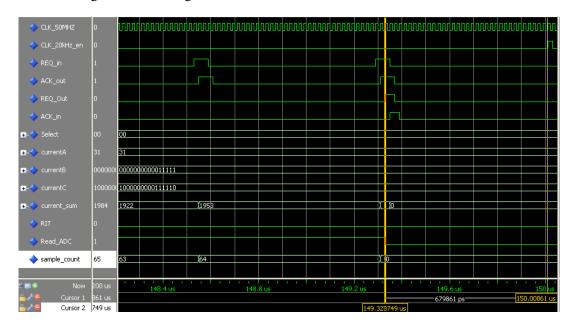

| Figure 3.15 Flowchart of the current integrator block                                                               | 54 |

| Figure 3.16 Simulation of the Current Integrator                                                                    | 55 |

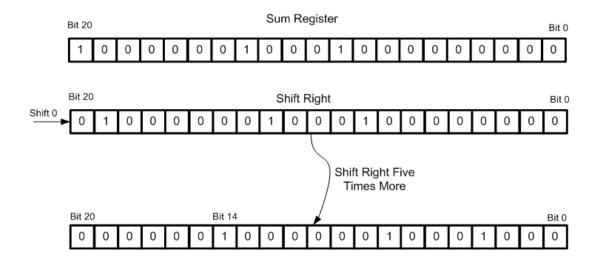

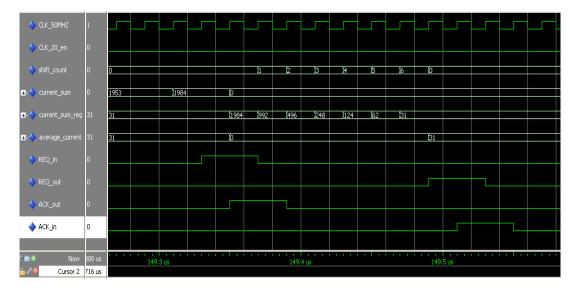

| Figure 3.17 Average current calculation                                                                             | 56 |

|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.18 Average Current Calculation VHDL Module                                                                 | 56 |

| Figure 3.19 Simulation of the Average Current Calculation Module                                                    | 57 |

| Figure 3.20 Connection of the average current calculation module with the other modules                             | 58 |

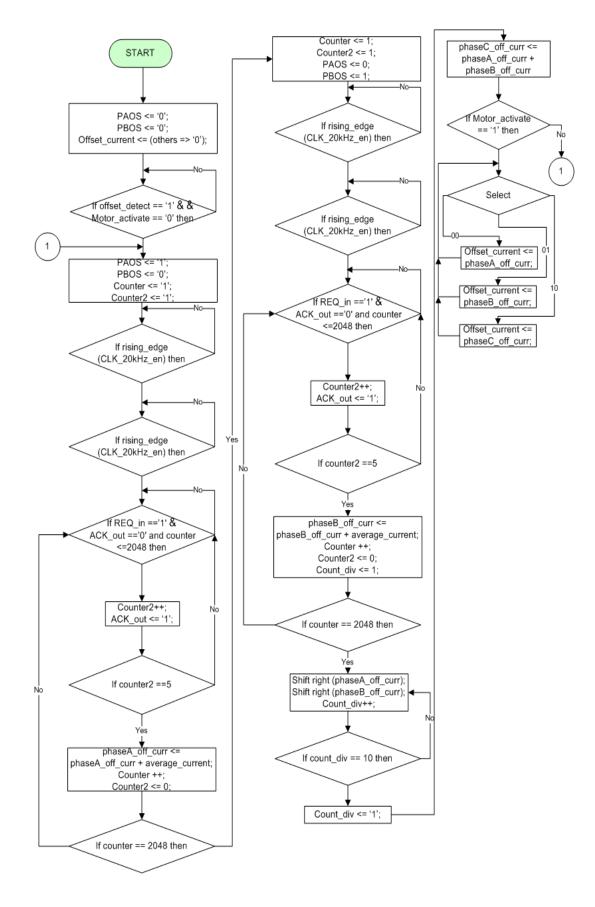

| Figure 3.21 Flowchart of the offset current detection VHDL module                                                   | 60 |

| Figure 3.22 Offset Detection VHDL Module                                                                            | 61 |

| Figure 3.23 Connection of the offset detection block with the other modules                                         | 63 |

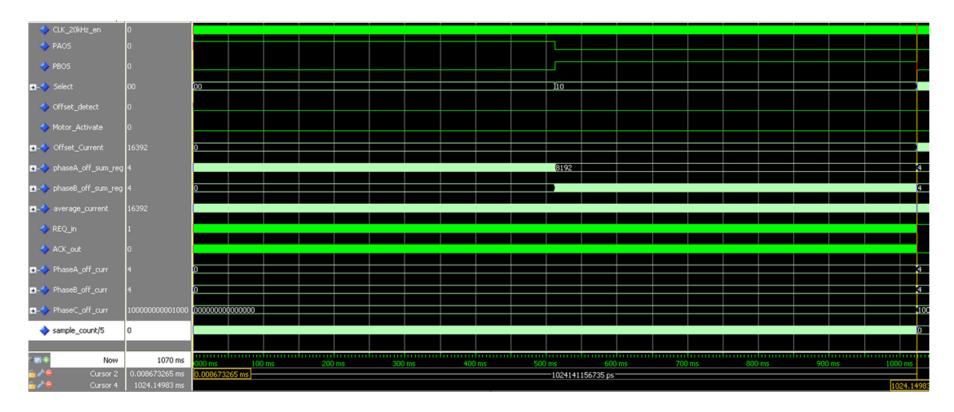

| Figure 3.24 Simulation of the Offset Detection Module                                                               | 64 |

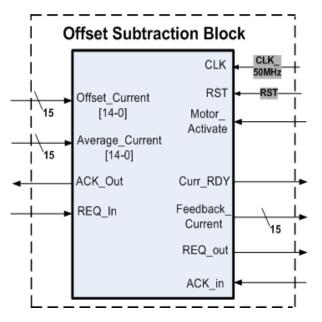

| Figure 3.25 Offset current subtraction VHDL module                                                                  | 65 |

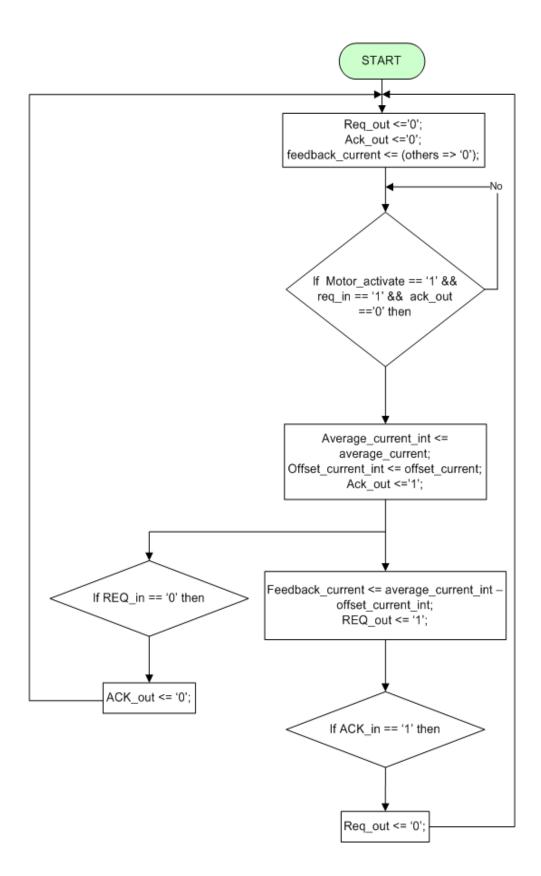

| Figure 3.26 Flowchart of the offset current subtraction VHDL module                                                 | 66 |

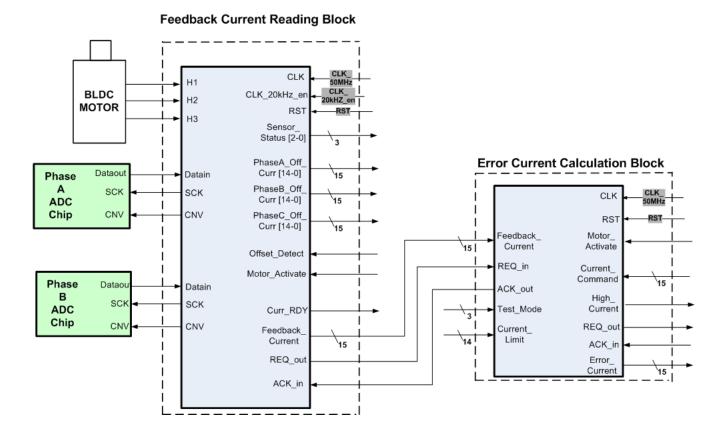

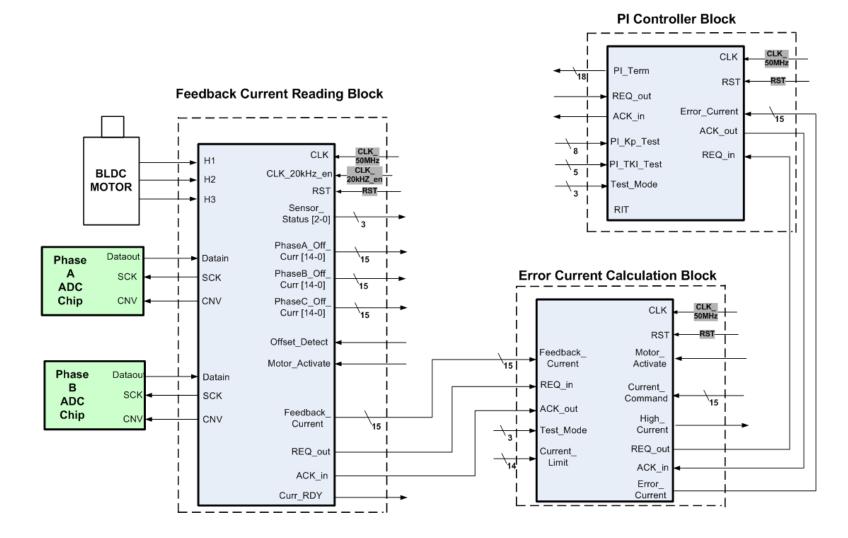

| Figure 3.27 Feedback Current Reading Block                                                                          | 67 |

| Figure 3.28 Top Level View of the Feedback Current Reading Block                                                    | 68 |

| Figure 3.29 Simulation Result Window of the Offset Current Subtraction Module                                       | 69 |

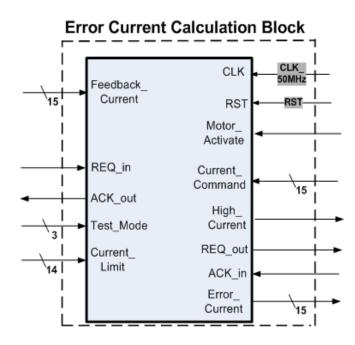

| Figure 3.30 Error Current Calculation VHDL Module                                                                   | 70 |

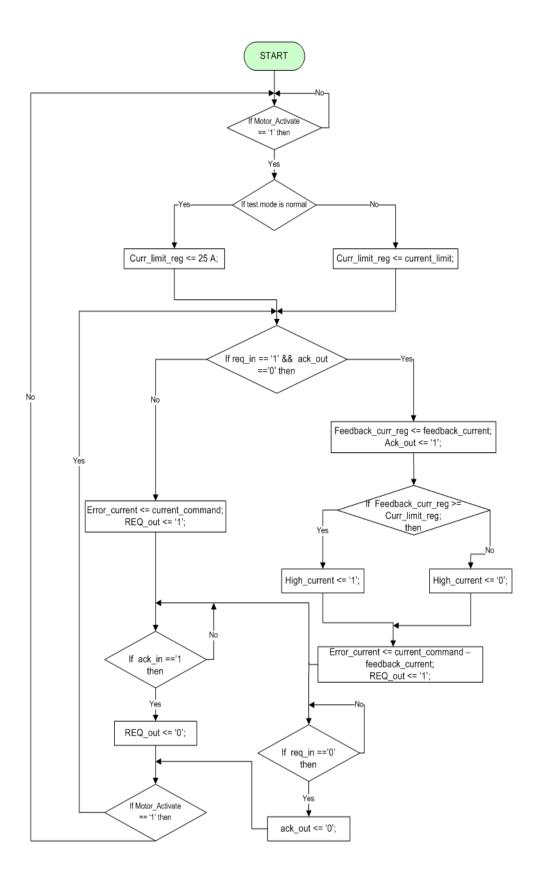

| Figure 3.31 Flowchart of the error current calculation VHDL module                                                  | 71 |

| Figure 3.32 Connection diagram between the error current calculation module and the feedback current reading module | 72 |

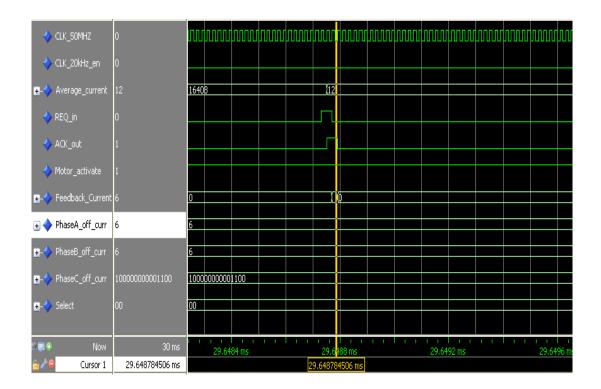

| Figure 3.33 Simulation Result Window of the Error Current Calculation Module                                        | 74 |

| Figure 3.34 PI controller VHDL module                                                                               | 77 |

| Figure 3.35 PI controller state machine                                                                             | 78 |

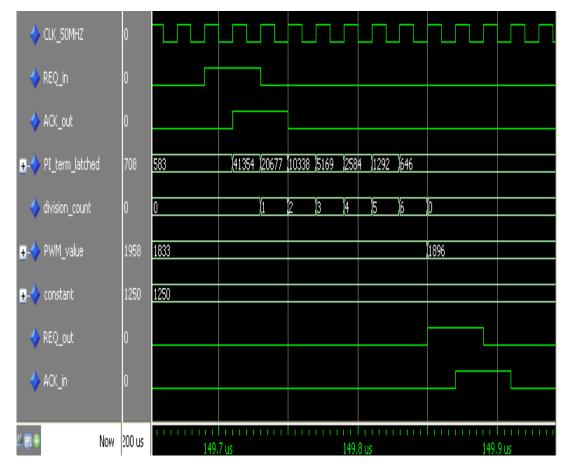

| Figure 3.36 Simulation Result Window of the PI Controller Module                                                    | 80 |

| Figure 3.37 Connection of the PI controller module with the other modules                                           | 81 |

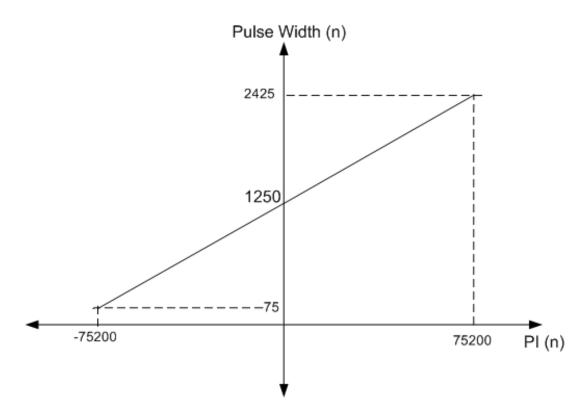

| Figure 3.38 PI versus Pulse Width                                                          | 82  |

|--------------------------------------------------------------------------------------------|-----|

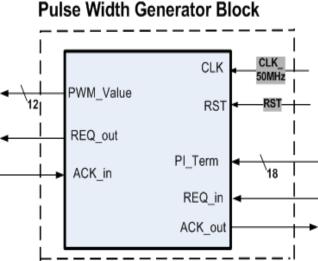

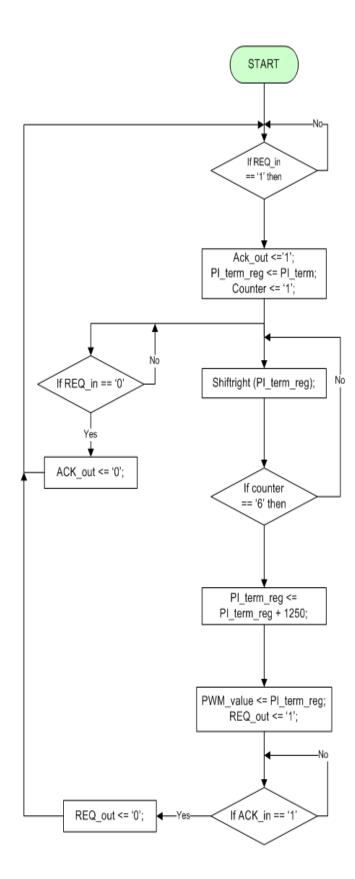

| Figure 3.39 Pulse width generator module                                                   | 83  |

| Figure 3.40 Flowchart of the pulse width generator VHDL module                             | 84  |

| Figure 3.41 Simulation Result Window of the Pulse Width Generator Module                   | 85  |

| Figure 3.42 Connection between the pulse width generator module and the other VHDL modules | 86  |

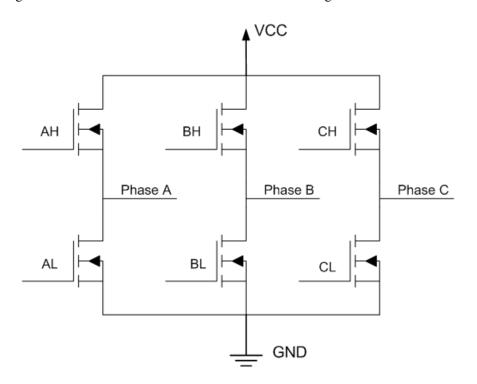

| Figure 3.43 Notation of the Commutation Control's Outputs on the Inverter Circuit          | 88  |

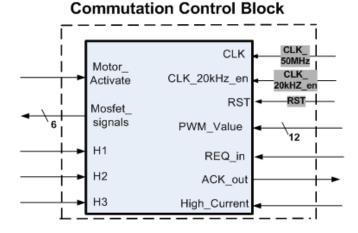

| Figure 3.44 Commutation Control VHDL Module                                                | 89  |

| Figure 3.45 Simulation Result Window of the Commutation Control VHDL Module                | 89  |

| Figure 3.46 Current Controller VHDL Module Structure                                       | 90  |

| Figure 3.47 Top Level View of the Current Controller VHDL Module                           | 91  |

| Figure 3.48 Ports of the Bus Controller VHDL Module                                        | 92  |

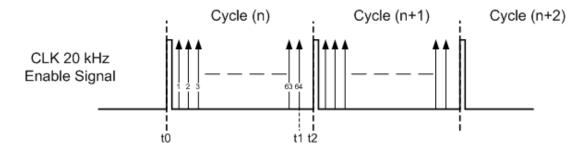

| Figure 3.49 Timing diagram of the 20 kHz clock enable signals                              | 94  |

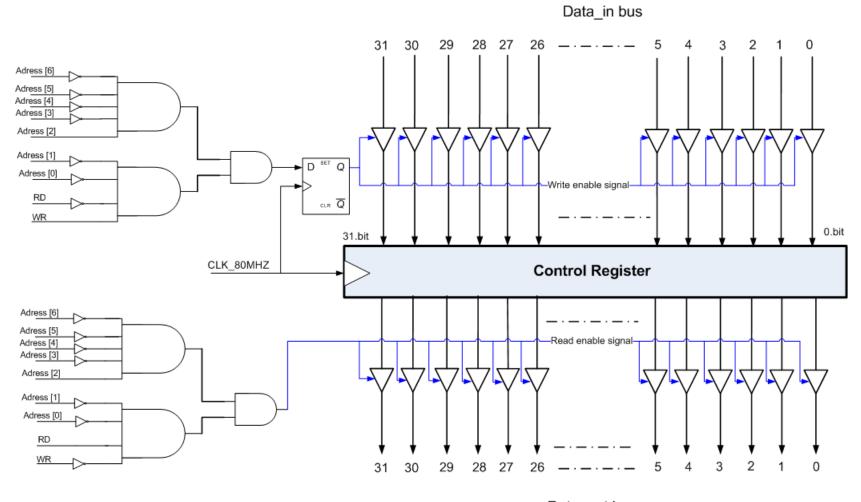

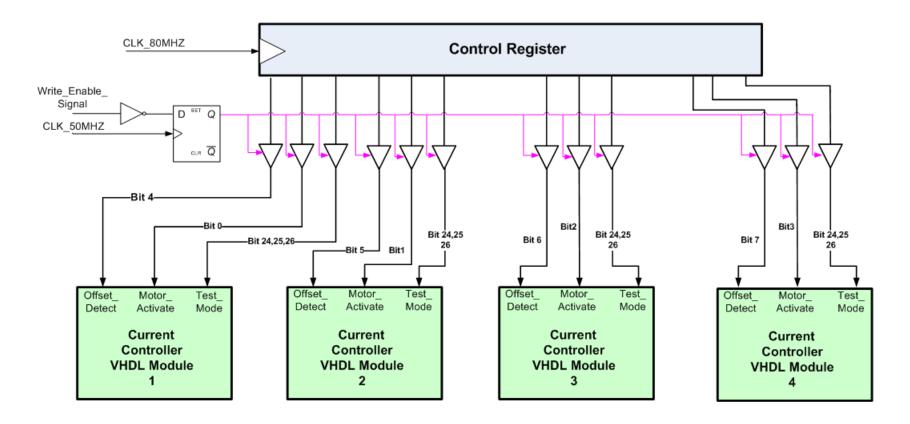

| Figure 3.50 Control Register of the Current Controller Module                              | 95  |

| Figure 3.51 Implementation of the Control Register                                         | 96  |

| Figure 3.52 Mapping of the control register to the current controller modules' ports       | 97  |

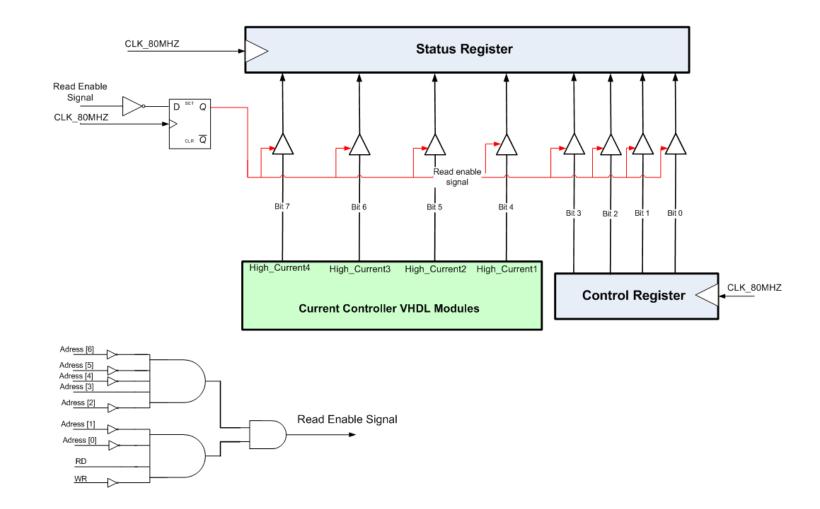

| Figure 3.53 Status Register of the Current Controller Module                               | 98  |

| Figure 3.54 Mapping between the status register and current control modules                | 99  |

| Figure 3.55 Current Command Register of the Current Controller Module                      | 100 |

| Figure 3.56 PI Controller Parameters Register of the Current Controller Module             | 100 |

| Figure 3.57 Structure of the Feedback Data Control Block                                   | 103 |

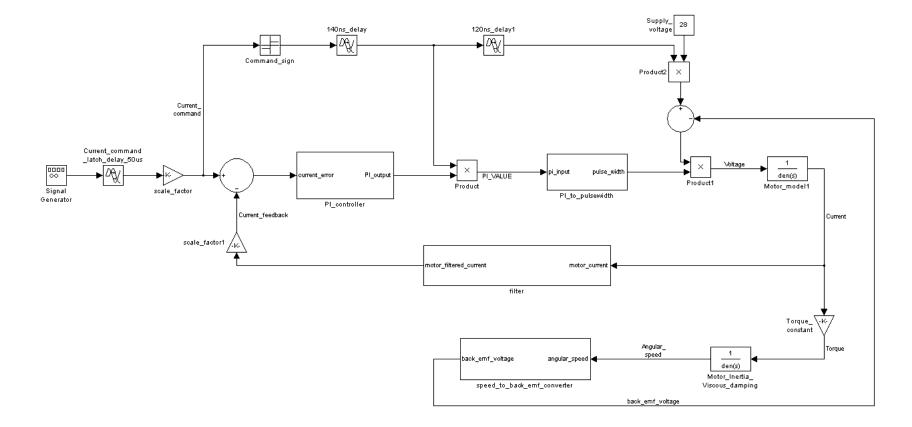

| Figure 3.58 MATLAB Model of the Current Controller                                         | 105 |

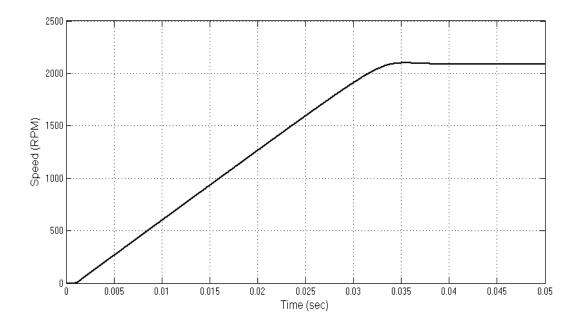

| Figure 3.59 Motor Speed for the 4 A Current Command                                                                  | 107 |

|----------------------------------------------------------------------------------------------------------------------|-----|

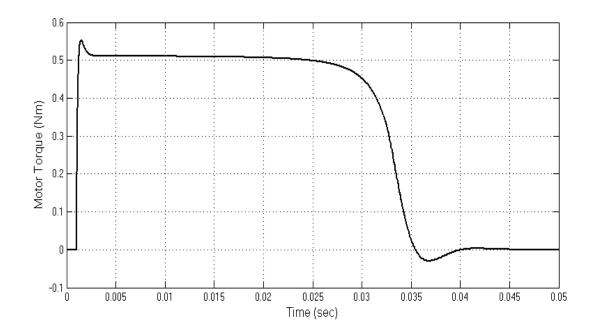

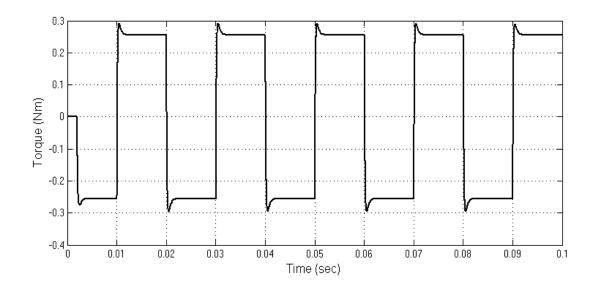

| Figure 3.60 Motor Torque for the 4 A Current Command                                                                 | 107 |

| Figure 3.61 Rectified Current Command and Feedback                                                                   | 108 |

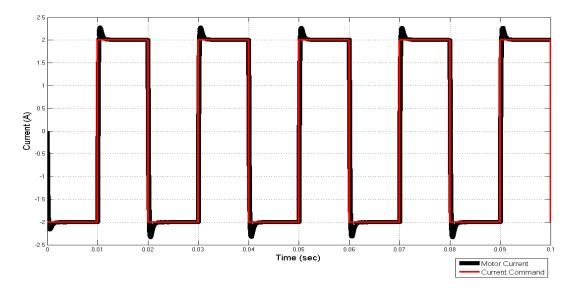

| Figure 3.62 Motor Torque for 4A Peak-to-Peak Square Waveform Current Command .                                       | 109 |

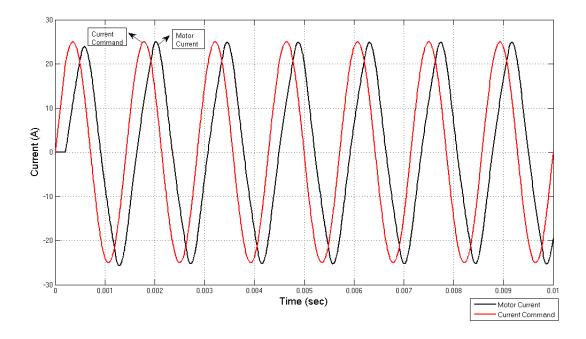

| Figure 3.63 Current Command and Current Feedback Signals for a 700 Hz Sine Current<br>Command of 50 A Magnitude      | 110 |

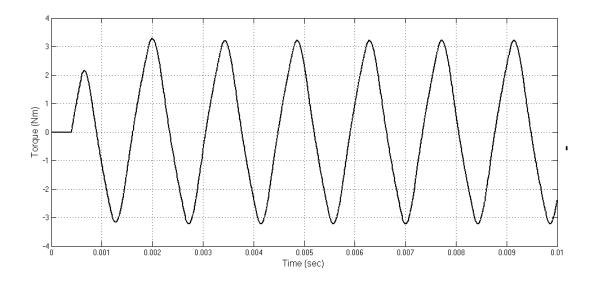

| Figure 3.64 Motor Torque for 700 Sine Current Command of 50 A Magnitude                                              | 110 |

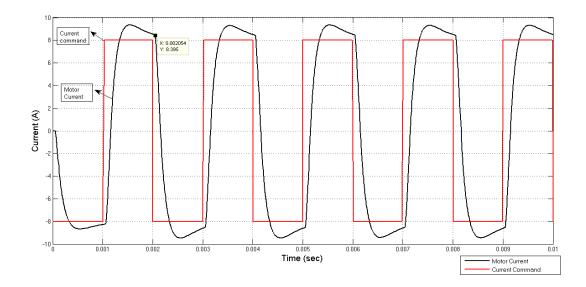

| Figure 3.65 Current Command and Current Feedback Signals for 500 Hz Square Wave<br>Current Command of 16 A Magnitude | 111 |

| Figure 3.66 Current Command and Current Feedback Signals for 500 Hz Square Wave Current Command of 20 A Magnitude    | 111 |

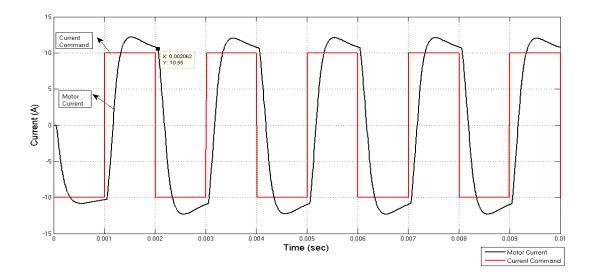

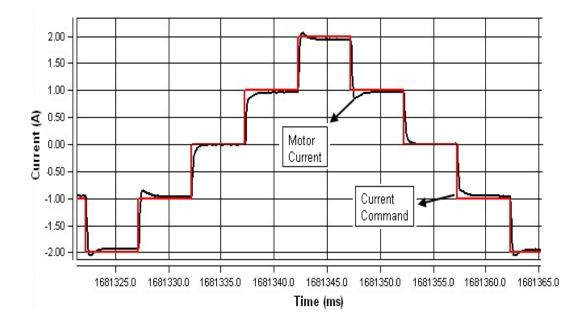

| Figure 3.67 Current Command and Current Feedback Signals for a 50 Hz Square Current Command of 4A Magnitude          | 112 |

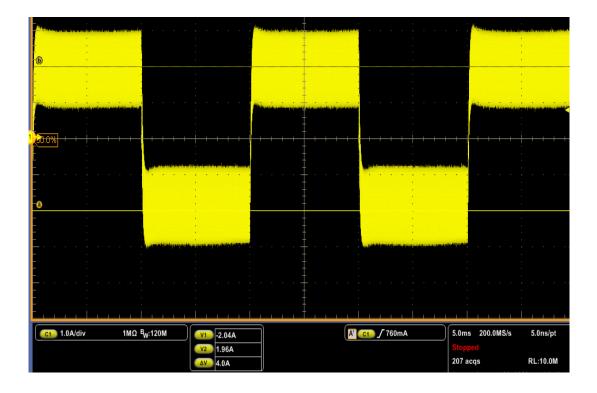

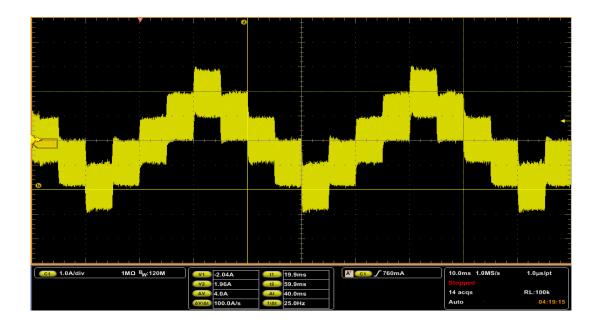

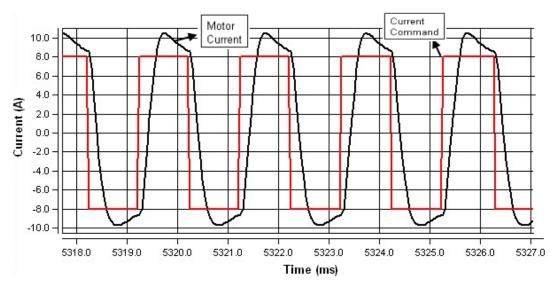

| Figure 3.68 Oscilloscope View of Current Feedback Signal for a 50 Hz Square Current<br>Command of 4A Magnitude       | 113 |

| Figure 3.69 Screen Shot of the 25 Hz Sine Current Command of 4A Magnitude                                            | 114 |

| Figure 3.70 Current Command and Current feedback Signals for a 25 Hz Sine Current<br>Command of 4A Magnitude         | 114 |

| Figure 3.71 Oscilloscope View of Current feedback Signal for a 25 Hz Sine Current<br>Command of 4A Magnitude         | 115 |

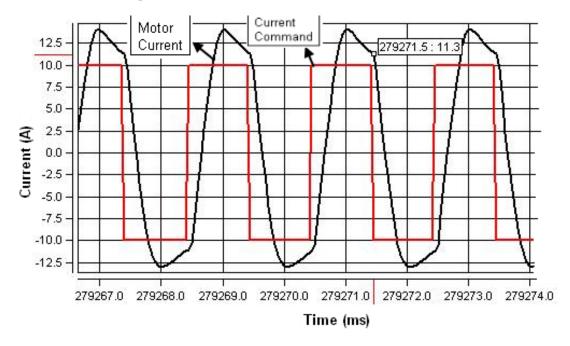

| Figure 3.72 Current Command and Current feedback Signals for a 100 Hz Square Current Command of 4A Magnitude         | 116 |

| Figure 3.73 Overshoot of Current Feedback Signal for a 100 Hz Square Current Com-<br>mand of 4A Magnitude            | 116 |

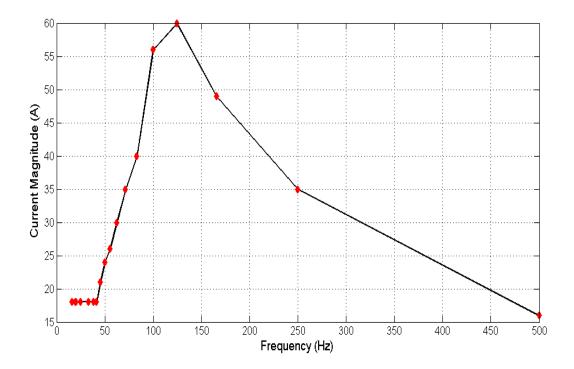

| Figure 3.74 Current Feedback Signal for a 500 Hz Square Current Command of 16A                                    |

|-------------------------------------------------------------------------------------------------------------------|

| Magnitude (Experimental result)                                                                                   |

| Figure 3.75 Current Feedback Signal for a 500 Hz Square Current Command of 20A<br>Magnitude (Experimental result) |

| Figure 3.76 Maximum Current Magnitude versus Frequency of the Square Wave Cur-                                    |

| rent Command                                                                                                      |

|                                                                                                                   |

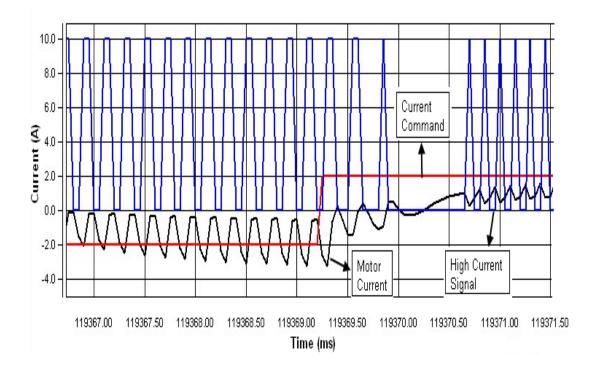

| Figure 3.77 High Current Signal for 1 A Current Limit                                                             |

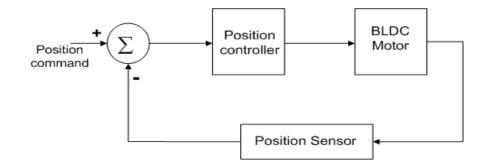

| Figure 4.1 Position Control System                                                                                |

| Figure 4.2 Position control system without the current control loop                                               |

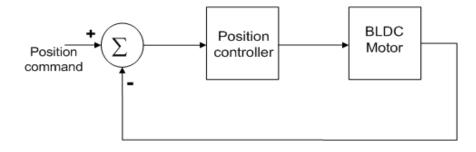

| Figure 4.3 Position control system without the postion transducer                                                 |

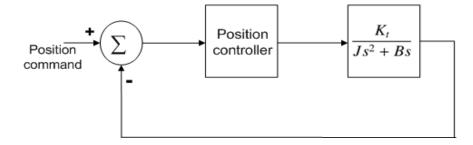

| Figure 4.4 Position control system with the motor model                                                           |

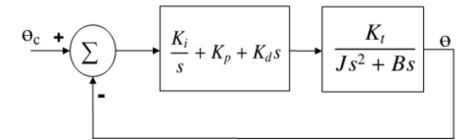

| Figure 4.5 PID Controlled Position Control System                                                                 |

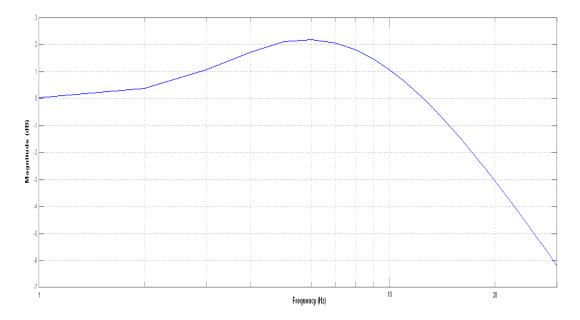

| Figure 4.6 Frequency response of the PID controlled position control system 125                                   |

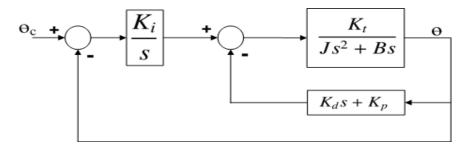

| Figure 4.7 IPD Controlled Position Control System                                                                 |

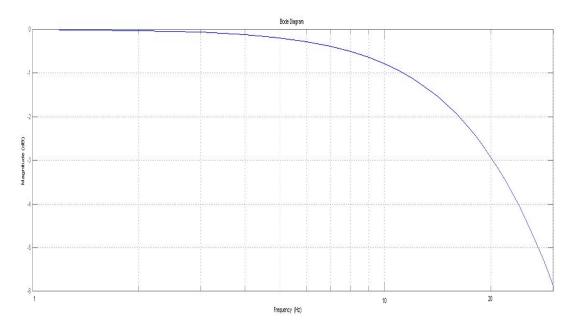

| Figure 4.8 Frequency response of the I-PD controlled position control system 128                                  |

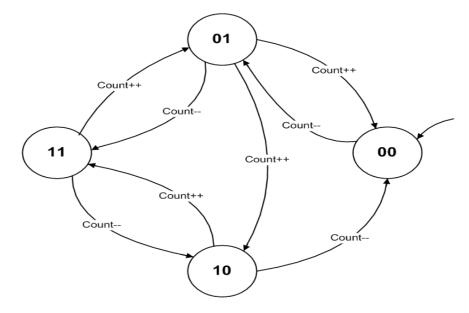

| Figure 4.9 State Machine Diagram of the Encoder Interface Module                                                  |

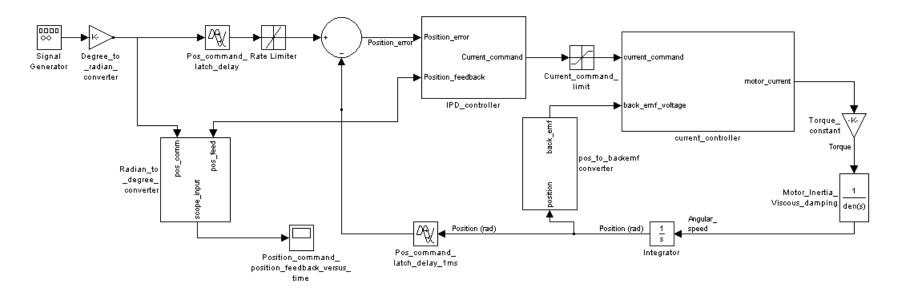

| Figure 4.10 Matlab Model of the I-PD Position Control System                                                      |

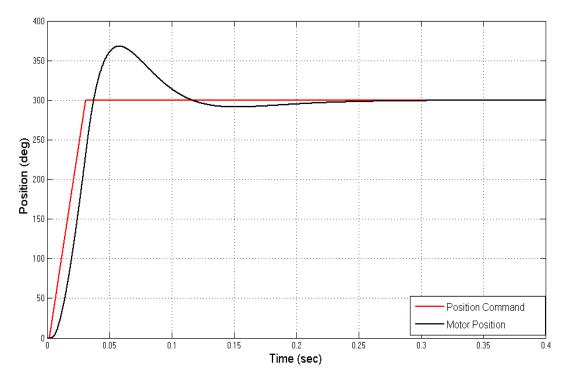

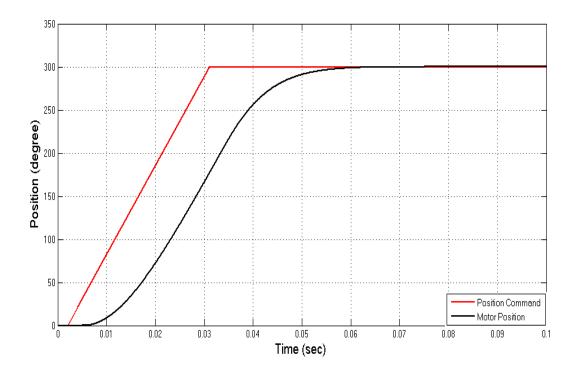

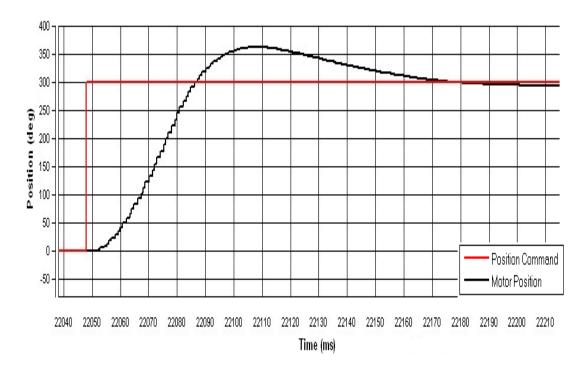

| Figure 4.11 Step response of the PID controlled system for 300 degree command 133                                 |

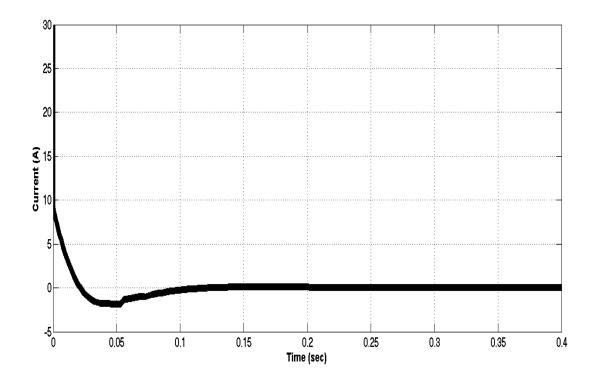

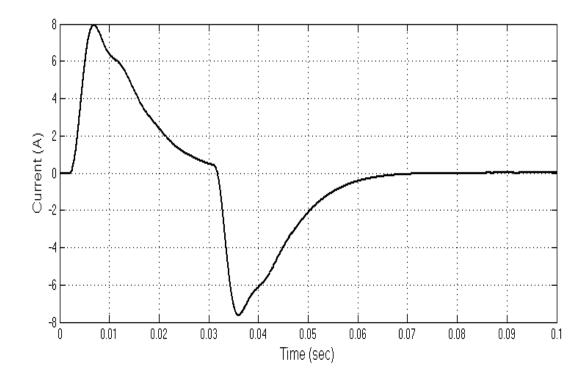

| Figure 4.12 Current command of the PID controlled system for 300 degree step command 134                          |

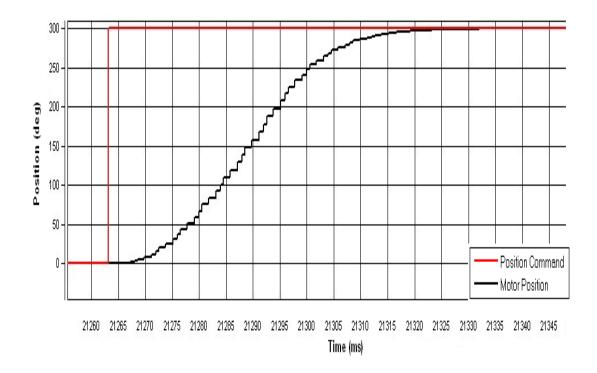

| Figure 4.13 Step response of the I-PD controlled system for 300 degree step command 135                           |

| Figure 4.14 Current command of the I-PD controlled system for 300 degree step command135                          |

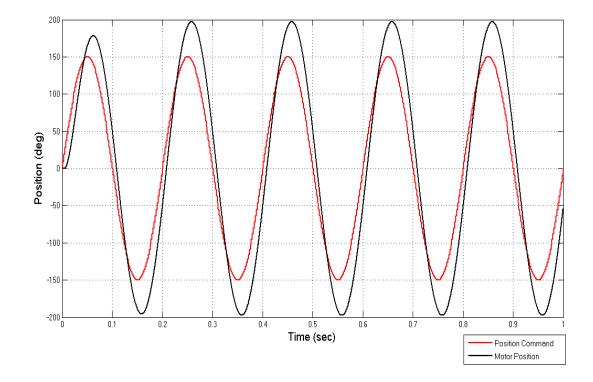

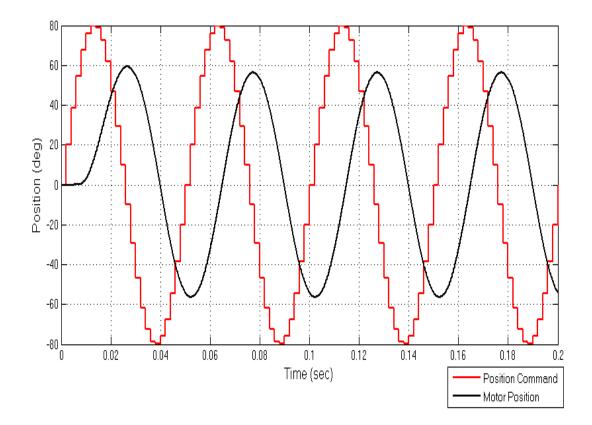

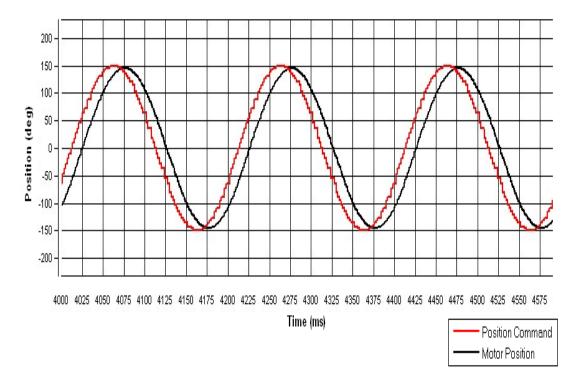

| Figure 4.15 Motor position for PID controlled system and 5 Hz, 300 degree peak to peak sine command               |

|                                                                                                                   |

| Figure 4.16 Motor position for I-PD controlled system and 5 Hz, 300 degree peak to  |     |

|-------------------------------------------------------------------------------------|-----|

| peak sine command                                                                   | 137 |

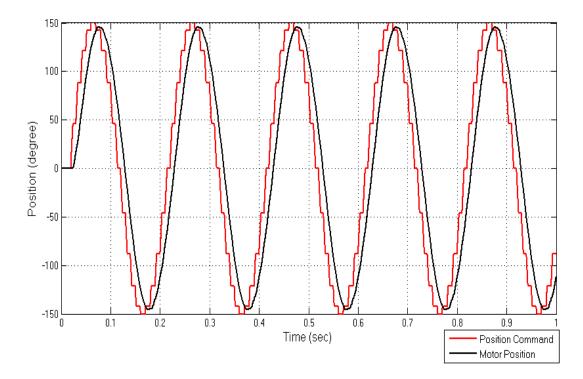

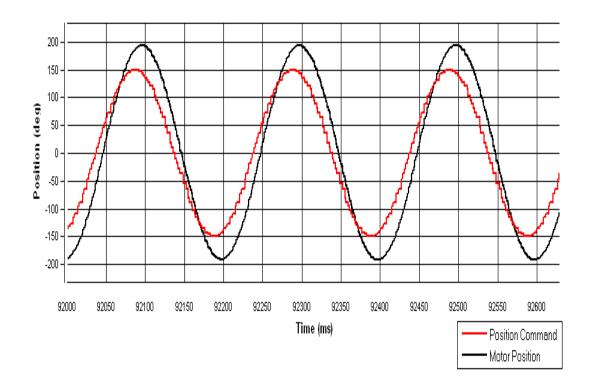

| Figure 4.17 Motor position for 20 Hz sine position command of 160 degree magnitude  | 138 |

| Figure 4.18 Step response of the PID controlled system for 300 degree command (ex-  |     |

| perimental result)                                                                  | 139 |

| Figure 4.19 Step response of the I-PD controlled system for 300 degree command (ex- |     |

| perimental result)                                                                  | 140 |

| Figure 4.20 Motor position for PID controlled system and 5 Hz, 300 degree peak to   |     |

| peak sine command (experimental result)                                             | 141 |

| Figure 4.21 Motor position for I-PD controlled system and 5 Hz, 300 degree peak to  |     |

| peak sine command (experimental result)                                             | 141 |

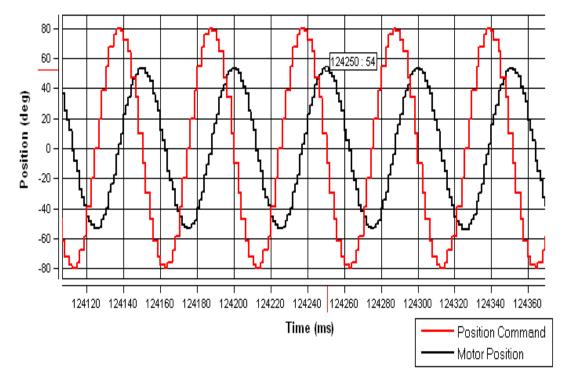

| Figure 4.22 Motor position for 20 Hz sine position command of 160 degree magnitude  |     |

| (experimental result)                                                               | 142 |

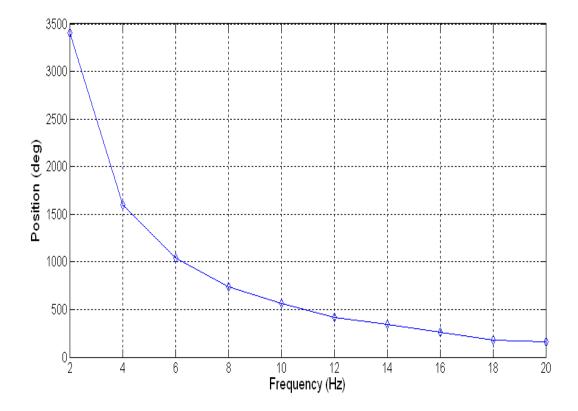

| Figure 4.23 Magnitude of the position command versus frequency of the sine wave     |     |

| position command                                                                    | 143 |

# LIST OF ABBREVIATIONS

- ADC Analog to Digital Converter.

- ALU Arithmetic Logic Unit.

- ASIC Application Specific Integrated Circuit.

- BLDC Brushless Direct Current.

- **BRAM** Block Random Access Memory.

- CPU Central Processing Unit.

- DC Direct Current.

- **DCM** Digital Clock Manager.

- **DSP** Digital Signal Processor.

EEPROM Electronically Erasable Programmable Read-Only Memory.

- EMI Electromagnetic Interference.

- FIFO First In First Out.

- **FPGA** Field Programmable Gate Array.

- I/O Input Output.

JTAG Joint Test Action Group.

- MSPS Mega Sample per Second.

- PC Personal Computer.

- PCB Printed Circuit Board.

- PI Proportional Integral.

- PLB Peripheral Local Bus.

- PQFP Plastic Quad Flat Pack.

- **PROM** Programmable Read-Only Memory.

- **PWM** Pulse Width Modulation.

- RAM Random Access Memory.

- SPI Serial Peripheral Interface.

- SRAM Static Random Access Memory.

- TQFP Thin Quad Flat Pack.

- UART Universal Asynchronous Receiver Transmitter.

- VHDL Very High Speed Integrated Circuit Hardware Description Language.

- **VQFP** Very Small Quad Flat Pack.

- XCL Xilinx Cache Link.

# **CHAPTER 1**

# **INTRODUCTION AND MOTIVATION**

Brushless DC motors are widely used in many areas, such as weapon systems [1], robotics, industrial and commercial applications because of their high efficiency, low EMI (Electromagnetic Interference) and high mechanical reliability. A brushless DC motor operates over a wide range of speed, whereas the speed range of a brushed motor is limited because of its commutation characteristics. Due to absence of brushes, brush induced EMI is eliminated in brushless motors. Compared to the induction machines, they have lower inertia allowing for faster response, because there is no mechanical commutator on the rotor. However, position and speed/torque control of a brushless motor is more complex in terms of algorithms, power electronic circuitry [2] and digital computations [3].

Reducing the electronic board count in the BLDC (Brushless Direct Current) motor control system of a control actuation system of a guided missile constitutes the main reason of this study. The present motor control system includes two electronic boards and four brushless dc motors. Motor control structures on two electronic boards may create difficulties in terms of space, price, design time and flexibility. However; main reasons of the usage of multiple boards in this system are to isolate the digital and power electronic parts due to the possible electromagnetic interference between them and the implementation of the current and position controllers in different platforms. For example; position controller is implemented in a DSP (Digital Signal Processor) chip and the current controller is implemented on the board with the help of the analog integrated circuits. In addition; an FPGA chip is also used for the PWM (Pulse Width Modulation) implementation and some I/O functions. One of the electronic boards in this system includes the FPGA, power electronic circuitry and the analog integrated circuits for the current control and the other board includes the DSP chip and some other motor position sensor interfaces. In order to reduce the board count, a new control scheme must be applied for decreasing the component count on the boards. At the beginning of the study; control schemes in the field of the motor control are surveyed and the most appropriate structure is selected for the new control system.

There are different control schemes in the field of motor control. DSP plus FPGA based structure is the most popular one and widely used in motor control field [4]. In addition; this structure is also used in the control system of the present system. In contrast; utilization of FPGA with DSP chips increases the complexity of the electronic boards, decreases the reliability of the system and complicates the design process. In this control scheme; FPGA chips are not fully utilized and used for simple functions such as PWM implementation, I/O (Input Output) functions, glue logic for the communication interfaces, etc [5]. However; complex current control algorithms, which require high sampling rate and position control algorithms are implemented in digital signal processor chips. As a result; the designer has to make a choice between the high current sampling rate and position control frequency because DSP chips operate in a sequential manner. Another handicap of this control scheme arises for the applications that have N number of motors, which need to be controlled dependently or independently, because of DSP chips' limited capacity in terms of speed (operations per second), the number of CPU (Central Processing Unit), ALU (Arithmetic Logic Unit) cores and the number of PWM channels [6]. To reduce the computational load of DSP chips, to increase the current sampling rate and current update frequency, current control loop is implemented in analog circuitry [1] [7]. In spite of a reduction in the load of DSP, the size of the electronic boards, complexity of electronic design process and likelihood of problem in boards increase dramatically because of implementation of current control loop in analog circuitry. In addition to these disadvantages; configuration of current controller in terms of PI controller and other parameters such as high current limits, etc., becomes harder compared to the digital implementation.

Another popular control scheme for the brushless motor control is based on the application specific microcontrollers [8]. Microcontrollers, which are specified for motor control, have limited capacity in terms of PWM channels, feedback current channels and position feedback input channels. Because of limited sources; a finite number of motors could be controlled in this structure. To decrease the chip size of microcontrollers; chip designers put one or two multiplexed analog to digital converter blocks, used for reading current feedback, into the microcontroller. However; getting feedback current from the multiplexed ADC (Analog to Digital Converter) chips causes attenuation in the sensitivity of the current control loop. Usage

of specified microcontrollers on the motor driver boards decrease the flexibility, configuration ability and adaptability because communication interfaces and sources of them, which are mentioned above, limit the capabilities of the electronic board. Reputation of FPGAs increase significantly in the motor control field because of shorter development cycles, lower costs and higher density [3].

FPGA-based control scheme in the field of motor control in recent years has started to spread [3] [5] [7] [9] [12] [11]. Features of the FPGAs, which are the simplicity, programmability, short design cycle, fast-time to market, low power consumption and high density, enhance the application of FPGAs in the motor control field [9]. FPGA based motor driver boards are less complex and more reliable compared with the DSP plus FPGA based ones and more flexible and adaptable according to the microcontroller based boards. For example; in this thesis, to monitor the motor currents, PWM values, hall sensor data and motor shaft position in real time, Spacewire communication protocol is used and implemented in FPGA. However; there is no available microcontroller or DSP chip, having Spacewire interface, in the market. Apart from these; FPGA based solutions enable more numbers of motor control compared with the DSP or microcontroller based ones because of their high logic density property. In the FPGA based solution, update rates of the current control loop and position/velocity control loop are much higher [5] [10] compared to the DSP based ones and high update rates for the controller loops increase the performance of the motor and sensitivity of the controller. In addition; implementation of current controller in the FPGA removes the density of analog ICs from the board and provides configurability via software. Due to these benefits of the FPGA based control scheme; it seems as the most appropriate solution for our system.

In this thesis; board count of the BLDC motor control system of a control actuation system is reduced to one via implementing the current and position controllers in the FPGA. In addition; some measures are taken on the board for the possible electromagnetic interference problem. When the new motor control system is compared to the present one in terms of the controllers' performance, there is no significant difference between them according to the experimental results. However; current measurement accuracy of the new design is much better because of the current sensing method (hall effect current sensing method). To improve the current measurement accuracy of the present system, size of the PCB (printed circuit board) must be enlarged because hall-effect type current sensing method takes up more space on the PCB compared to the resistive current sensing method. Another advantage of the new system emerges on the power consumption; new design is much better in terms of power consumption because there is a 90 degree phase shift between the pulse width modulation signals of each motor. However; it is not easy to create this phase difference between these modulation signals in the present system due to the implementation of current controller in the analog domain. Although the performance of the current controller of the new system is slightly better, there is no difference between these systems in terms of the position controller's performance, because the speed of the Microblaze soft processor is sufficient for implementing the four independent position controller algorithms and same position sensors are used in both systems.

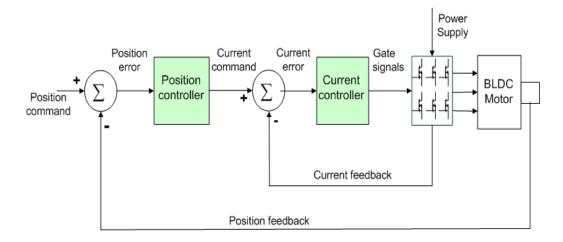

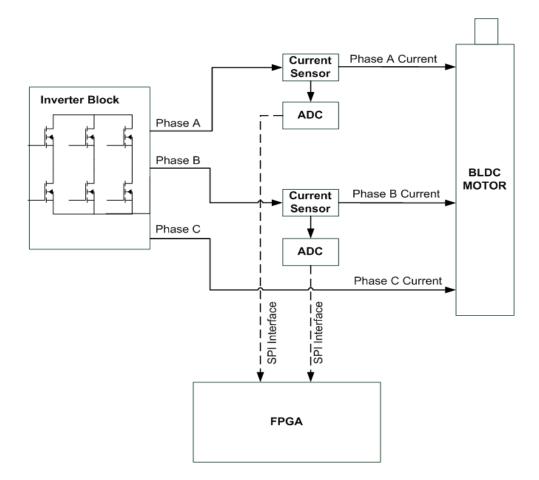

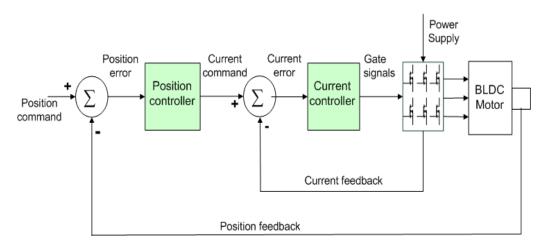

Block diagram of the control system designed and implemented in this thesis is shown in Figure 1.1. Although the current and position controllers are implemented in the same chip, they are coded in different programming languages and implemented in different platforms. Performance of the controllers are tested experimentally and compared with the simulation results.

Figure 1.1: Block Diagram of the Control System

Some important points were taken into account specifically during the design and implementation processes of the FPGA design.

• Sampling count of the phase current in a operation cycle (50 us) is fixed to an even number of 64 to decrease the complexity of the FPGA design. So; calculation time of the pulse width is reduced significantly due to the simplicity of the division operation used in the average current calculation. Operation of the current acquisiton block is explained in Section 3.1.1.

• To shorten the calculation time of the conversion process of the PI (proportional-integral)

controller's output to the pulse width value and to increase the resolution of the PWM signal, a special conversion formula is discovered and limits of the PI controller are tuned according to this formula. Detailed description of the conversion process and the formula are available in Section 3.1.9.

• Microblaze soft processor and current controller VHDL module runs at different clock domains, 80 MHz and 50 MHz respectively. To prevent the possible communication problems due to different clock domains between the processor and controller module, the circuits provided in Section 3.2, are designed and implemented in the FPGA.

• Clock signals of all modules in the FPGA are generated from a single DCM (digital clock manager) which is a ready intellectual property (IP) of Xilinx. Otherwise; routing problems for clock signals occur during the implementation process of the current controller module.

• To reduce the computational load of the processor, packet control of the spacewire protocol is implemented in the current controller module. Control of the spacewire protocol is explained in detail in Section 3.2.

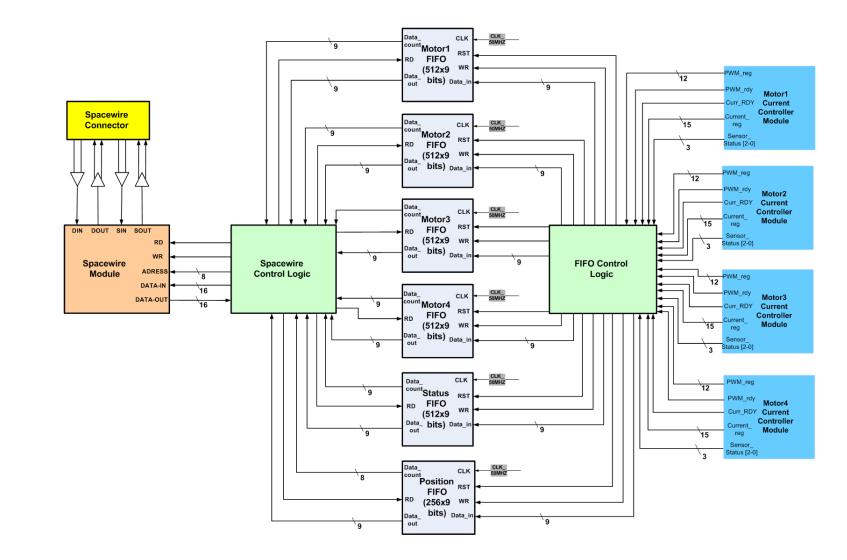

• To monitor the behavior of the current and position controllers in real time graphically, a graphical user interface is designed and implemented in the personal computer. Current and position data are stored in the FIFO (first-in, first-out) type memories in the current controller module during the 5 ms because computer's processing speed is inadequate to handle the continuous incoming data from the spacewire protocol. Implementation of this operation is explained in detail in Section 3.2.

The outline of the thesis can be summarized as follows. In Chapter 2, description of the system including electronic board, graphical user interface and test setup is given. In detail; the architecture of the electronic board in which the implementations are carried on is described. In addition; architecture of the FPGA design is explained in general. In Chapter 3, design process and implementation of the current controller are explained and the results of the experimental tests are provided. In Chapter 4, design and implementation of the position controller are described and results of the experimental tests are presented. Finally in Chapter 5, the conclusion of this study and suggestions for future work are provided.

# **CHAPTER 2**

# MOTOR DRIVER CONTROL SYSTEM DESIGN

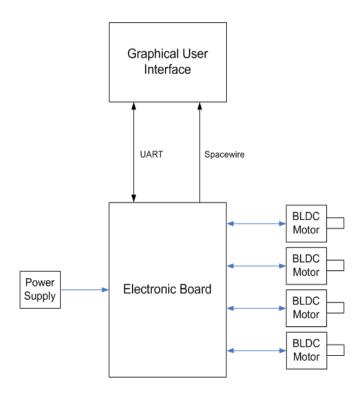

In this thesis; the motivation was basically designing and implementing a flexible, configurable, compact and high-performance brushless DC motor control system. The traditional BLDC motor control systems consist of one digital electronic board, one power electronic board and a graphical user interface [12] [11] [10]. In these systems; digital computations of the control loops are implemented on the board including digital electronic circuitry. However; power electronic circuitry, which consists of inverter blocks, current measurement circuitry, etc., are implemented in the other board. To design a compact controller system; a single board including all the required circuitry is designed and implemented in this study. Implementation of control loops in a single FPGA chip, which results in a reduction in the size of digital circuitry's area, reduced the board count in the system. To increase the flexibility and configurability of the controllers, a soft processor, named Microblaze, is used for configuring and connecting VHDL (Very High Speed Integrated Circuit Hardware Description Language) modules in the FPGA. Soft processor is also used for implementing the position controller. Finally; a graphical user interface is designed for monitoring the behavior of the system in real time. System is designed for controlling four BLDC motors because tests are done with the control actuation system, which includes four motors. However; this structure can be expanded for N numbers of motors. General diagram of the system is shown in Figure 2.1.

#### 2.1 Electronic Board Design

An electronic board was designed and manufactured within the scope of this study. The main tasks of the board can be summarized as controlling four BLDC motors and communicating with a PC. Production and placement process costs of the board were met by TÜBİTAK-

Figure 2.1: General Diagram of the Motor Control System

SAGE. Board consists of mainly two parts, which are digital and power electronic circuitry. Digital electronic circuitry was designed by me and Enes ERDIN (<sup>1</sup>). Power electronic circuitry of the board was designed by Ufuk AYHAN (<sup>2</sup>). Block diagram of the electronic board is shown in Figure 2.2.

<sup>&</sup>lt;sup>1</sup> He received B.S and M.S degrees in electrical and electronics engineering (EEE) from Middle East Technical University (METU), where he is currently working toward the Ph.D degree. He is also working as an expert research engineer in digital electronic design division of TÜBİTAK-SAGE.

<sup>&</sup>lt;sup>2</sup> He received B.S degree in EEE from METU, where he is currently working toward the M.S degree. He is also working as research engineer in analog electronic design division of TÜBİTAK-SAGE.

Figure 2.2: Block Diagram of the Electronic Board

$\infty$

This board carries a Xilinx Spartan3 XC3S4000 FPGA on it which is optimized for high logic density and high I/O designs. FPGA selection criteria are logic density, BRAM (Block Random Access Memory) size, I/O count and cost. Firstly; FPGA families from different companies are analyzed in terms of logic density and price. At the end of the investigation; the options were revealed to two FPGA families, which are Spartan3 and Cyclone3 from Xilinx (<sup>3</sup>) and Altera (<sup>4</sup>) respectively. At the end; a FPGA from the Xilinx Spartan3 family is selected because the cost of the FPGAs from Spartan3 family is much lower compared with the ones from Cyclone3 family and present working experience with Xilinx FPGAs. Package type of the FPGA was selected as ball grid array because it results in much lower chip size compared with the other package types such as PQFP (Plastic Quad Flat Pack), TQFP (Thin Quad Flat Pack), VQFP (Very Small Quad Flat Pack) and etc.

**FLASH :** The board includes one 32MB SPI (Serial Peripheral Interface) Flash chip from Winbond Electronics Corp. Microblaze soft processor's main code, size of which is higher than 64KB, must be put in non-volatile memory. Flash, EEPROM (Electronically Erasable Programmable Read-Only Memory) or Xilinx PROM (Programmable Read-Only Memory) chips are the options for non-volatile memory. Flash chip is decided to be used on the board, because Xilinx Prom chips are writable only via JTAG (Joint Test Action Group) interface, which requires a JTAG master controller. Also; flash chip with SPI interface is preferred because the size of the chip is much lower compared with the ones having parallel interface. At power up; processor loads the bootloader code to the block rams of the FPGA. After that; bootloader code starts to read the main code from the flash chip and write it to SRAM (Static Random Access Memory). At the end of initialization; Microblaze processor starts to work from SRAM chip.

**SRAM :** The board includes one 16MB SRAM chip having 32 bits wide data port from Integrated Silicon Solution, Inc. Because of maximum 64KB internal memory addressable by Microblaze soft processor core, an external memory is required, depending on the application, for the soft processors. This external memory chip is used as processor's instruction and data memory in this study. Access time of the SRAM chip is 8 ns.

**UART :** The board contains two full duplex RS-485/RS-422 transceiver chips from Analog Devices for the electrical signaling of UART protocol. RS-485/RS-422 and RS-232 are the electrical signaling options for the UART protocol. The RS-422 option was selected as the

<sup>&</sup>lt;sup>3</sup> To get more information about the famous FPGA manufacturer visit www.xilinx.com

<sup>&</sup>lt;sup>4</sup> To get more information about the famous FPGA manufacturer visit www.altera.com

electrical interface on the board because of noise resistant and long distance run properties of it. In the system, UART protocol is used for communication between PC and Microblaze soft processor. Because personal computers don't have a RS-422 or RS-485 electrical interface port, RS-422 to the RS-232 external converter module is used for connection with PC.

**CLOCK :** The board contains a 25 MHZ clock oscillator from Fox Electronics. The clock output of the oscillator is connected to the global clock pin of the FPGA. Low-value clock frequency (25 MHZ) is preferred to route on the board for preventing possible signal integrity problems. However; Microblaze soft processor runs at 80 MHZ clock frequency by using *Digital Clock Manager* (DCM), exists in the FPGA. Three major functions of the DCM blocks in the FPGA are Clock-Skew elimination, frequency synthesis and phase shifting [13].

**FPGA Configuration:** FPGA chips in the market can be grouped as Flash and RAM (Random Access Memory) based. Selected FPGA for this board is SRAM-based and much faster than the Flash-based ones. However; configuration data of the SRAM-based FPGA chips are volatile, so they require loading of configuration data from a non-volatile memory at power up. Therefore; 32 MB Xilinx PROM chip is used as the non-volatile memory on the board.

**Encoder Interface:** To get position data of the motor shaft, an incremental type encoder from Dynapar Brand is used in the system. Encoder is mounted on the shaft of the motor and connected to the board via a cable harness. Sensitivity of the encoder is 4096 pulses per revolution, which corresponds to approximately 0.08 degree measurement sensitivity. Two quadruple differential line receiver chips, compatible with RS-422 standard, from Texas Instruments were placed on the board, because encoders have RS-422 differential electrical signaling interface. Output ports of the line receiver chips are connected to the FPGA on the board.

**Spacewire Protocol:** To monitor the behavior of the controllers in real time, Spacewire (<sup>5</sup>) protocol is used in this study. Spacewire controller, designed and implemented in VHDL for previous works in TÜBİTAK-SAGE, is used in the FPGA. Spacewire controller is configured and driven by the bus controller VHDL module, shown in Figure 2.2. To reduce the dependency on the Microblaze soft processor, Spacewire protocol is not connected to it. "Spacewire protocol, based on the IEEE 1355 standard of communications, is a spacecraft communication network" [15]. "The SpaceWire standard was authored by Steve Parkes, University of Dundee with contributions from many individuals within the SpaceWire Working

<sup>&</sup>lt;sup>5</sup> To get more information about the Spacewire protocol visit www.spacewire.esa.int

Group from European Space Agency (ESA), European Space Industry, Academia and NASA" [15]. Spacewire protocol uses *Data-strobe*, *Differential Ended* (DS-DE) encoding technique. DS encoding consists of two signal lines, which are called as data and strobe. The data line is used to carry data, whereas strobe line is used to construct a clock signal in the receiver side. The controller on the driver side changes the state of the strobe line, when the data line is held at the same state. To get clock information from the bus; receiver side passes the data and strobe signals from a XOR gate. Diagram of the DS encoding is shown in Figure 2.3.

Figure 2.3: Data-Strobe Encoding

Spacewire protocol uses *Low voltage differential signaling* (LVDS) electrical standard for signal lines. LVDS Standard uses positive and negative lines for each signal. To comply the standard, we preferred using differential receiver and transmitter buffers, which are available in the FPGA, instead of external ones. We drew the spacewire signal lines on the printed circuit board with 100 ohm empedance value to eliminate the possible jitter and skew problems on the lines. Also; a special connector was put on the board for the Spacewire link.

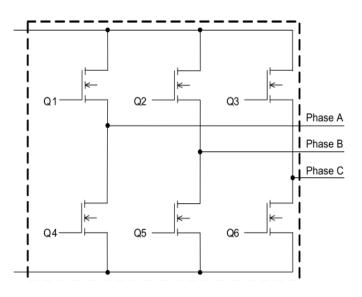

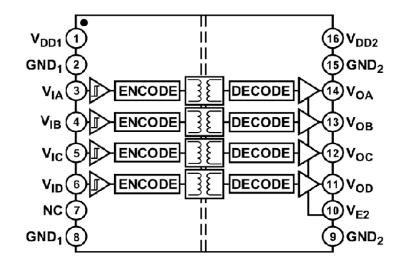

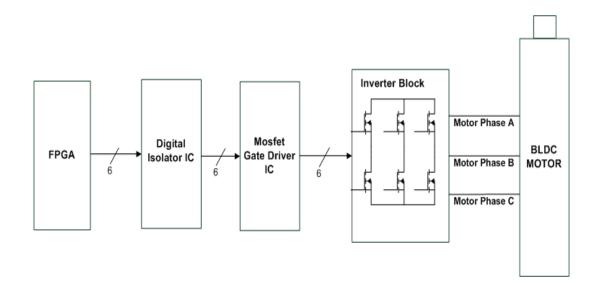

**Motor Driver Circuit:** The board contains four three phase inverter circuits to switch the supply voltage (28 VDC) over the phases of each motor according to the signals coming from the FPGA. Supply voltage was determined according to the operating voltage of the selected motors. Inverter circuit consists of 6 power mosfets from Infineon Technologies. The structure of the inverter circuit, designed and implemented on this board, is shown in Figure 2.4. To control mosfets in the inverter circuit, gate driver chips from International Rectifier are used in the board. Gate driver chips activate the gates of mosfets at 15 VDC according input signals, which are coming from isolatar chips. Isolator chips from Analog Devices are used between the FPGA and gate driver chips to eliminate the negative effects of power ground on the digital ground. Otherwise; flows of high-value return currents on the ground can influence the operation of digital chips negatively. This is one of the reasons, which results in two boards in the traditional motor control systems. Functional block diagram of isolation chip used in the board is shown in Figure 2.5. Functional block diagram of the motor driver circuit, including inverter block, gate driver and isolation chips, for one motor is shown in Figure 2.6.

Figure 2.4: Structure of the Inverter Circuit

Figure 2.5: Functional Block Diagram of Isolation Chip [14]

Figure 2.6: Functional Block Diagram of Motor Driver Circuit

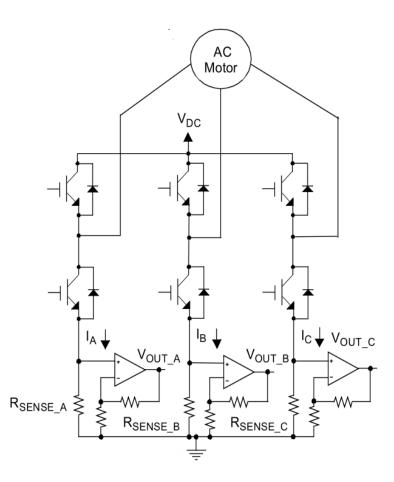

**Current Sensing Block:** The board includes four current sensing circuitry for the implementation of the current controller. Current sensing block consists of two current transducers and two analog to digital converter chips for each motor. During the design process of the board, we compared two current measurement methods, which are closed loop hall effect current sensing and resistive current sensing, in terms of sensitivity, power loss and reliability. Resistive current sensing is commonly used for measuring electrical current on printed circuit boards. To reduce the power loss, a low-value resistor is inserted in series with the supply line. As a result of this situation; measurement sensitivity decreases because voltage drop over resistance is very small for low current levels. In addition; this situation increases demand on the instrumentation amplifier circuit. Also; reliability problem, which is another drawback, arises in this method because the value of a resistor can change significantly via ambient temperature and operating conditions. An example circuit diagram for a resistor is given by  $I^2*R$ . During the measurements of high currents, power loss in the current sense resistor can become significant.

We decided to use closed loop hall effect current sensing method instead of resistive current sensing method because of its drawbacks, which are mentioned above. A magnetic sensor works by measuring the magnetic field surrounding a current carrying conductor. One of the advantages of this method is no additional resistance requirement in the circuit. In this method; current can be sensed at a wide range of common-mode voltages because inputs of

Figure 2.7: Current measurement with three shunt resistors

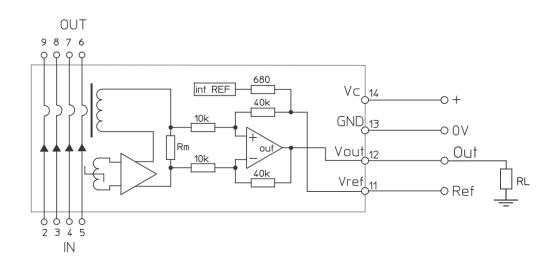

these sensors are completely isolated from the output ports of them. Also; there is no need for an external buffer in the current sensing circuit because output ports of magnetic sensors are low impedance. Finally; we selected a closed loop hall effect current transducer module from LEM company. Functional block diagram of current sensor is shown in Figure 2.8. The measuring range of current sensor is between +50 and -50 amperes above than the estimated maximum motor currents, which are +30 and -30 amperes. Other parameters of the current sensor are analyzed in the current controller chapter. To reduce the board size and cost; we put two current sensors for the A and B phases of each motor. Current of phase C is obtained in the FPGA by the well known three phase motor current equation that

$$IC = -(IA + IB) \tag{2.1}$$

To convert the output of the current sensors into the digital domain; *analog to digital converter chips* (ADC) are used in the board. We put one single channel ADC chip for the A and B phases of the motor instead of using a multiplexed ADC chip with two channels for each

Figure 2.8: Functional Block Diagram of the Current Sensor [16]

motor. Although the usage of one converter chip for each motor reduces the size and cost of the board; usage of multiplexed ADC chip increases the sampling rate of the selected chip due to calculation of phase C current. This situation also can result in possible timing problems in the board and can complicate the FPGA design process. Specifications of the ADC chips were determined according to the *pulse width modulation* (PWM) frequency, current sensing resolution, current sampling rate and the output properties of the current sensor. We determined the PWM frequency as 20 KHZ according to the simulations of the inverter circuit with motor model. When a very small pulse widths like 1 or 2 percentages of the PWM period apply to the motor, short-term currents flow through the motor. To sense these currents; we decided a sampling rate of 64 during one cycle of the current controller, which requires an ADC chip with minimum 1.28 mega sampling rates per second. After that; we determined the resolution of the ADC chip as 14 bits , which means approximately 7mA current sensitivity. Based on these requirements, we selected an ADC chip with 2.5 MSPS throughput and 14 bit resolution from the Analog Devices. Functional block diagram of the current sensing circuit is shown in Figure 2.9.

Hall Effect Position Sensor Interface: To rotate the motor, coils are activated in a predefined sequence depending on the direction, clockwise or counterclockwise. Driver circuit must understand the sequence, which defines the direction of current flow in the coils and magnetic field generated by coils individually. Magnetic field attracts and rejects the permanent magnets of the rotor. Driver circuit rotates the motor by changing the current flow

Figure 2.9: Functional Block Diagram of the Current Sensing Circuit

through the coils and, hence the polarity of the magnetic field in a right manner. To alternate current in a right sequence, position of the shaft must be measured by the circuit and this measurement is done via hall-effect sensors available in the motor. The outputs of the hall effect sensors shows the state of the commutation, which means alternation of the current through the coils. A three-phase BLDC motor has six states of commutation and three sensors are enough to show these states. We also designed a hall effect position sensor interface circuit and placed it on the board for each motor. Interface circuit supplies the hall-effect sensors with 15V and converts the 15V output signals of these sensors to the 3V3 signals for the FPGA interface. Comparator chips are used in this circuit.

### 2.1.1 Structure of the FPGA Design

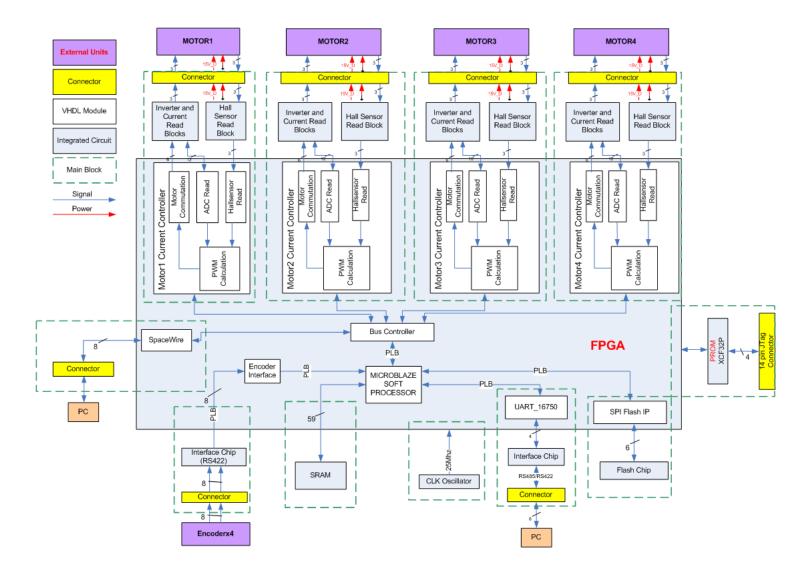

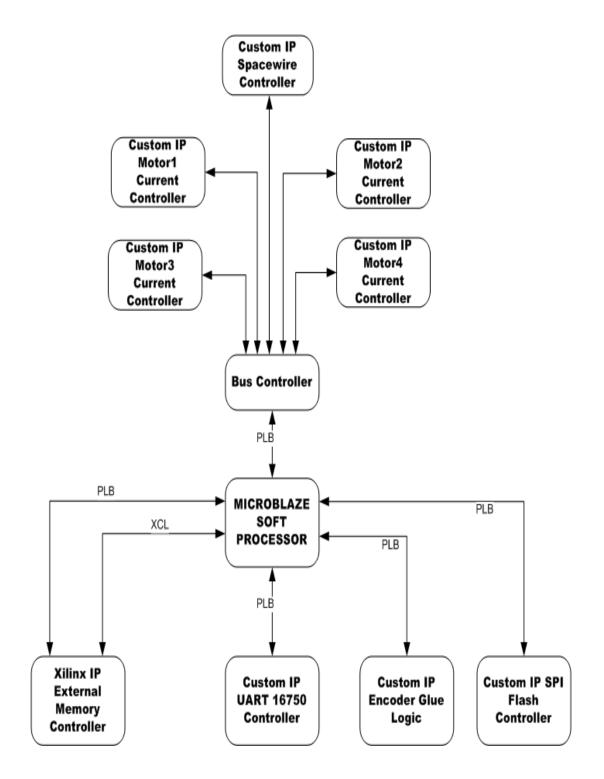

Within the scope of this study; FPGA design is completely done by me. The BLDC motor controller was designed and implemented in the FPGA within the scope of this thesis work. Firstly; position and current controllers are designed and simulated in the Matlab platform. After the verification of designs on the simulation platform; current and position controllers are coded in Very High Speed Integrated Circuit Hardware Description Language (VHDL) and C (programming language), respectively. By this way; position and current controllers can operate in parallel and, hence sampling, update rates of the controllers can become higher compared to the implementations in the processor. Also; implementation of current controller in VHDL increases the flexibility because VHDL modules can be implemented in any FPGA model. This situation removes the chip obsolescence problem, which is an important risk for the continuity of the electronic systems. Microblaze soft processor reduced the integration and testing periods of the VHDL modules. In addition; usage of soft processor in the FPGA provides flexibility and configurability for the system. For example; electronic board designed for this work can be adapted to another board or system via changing the packet structure, coded in C programming language, for the UART protocol. In addition; this system can be converted to an Application Specific Integrated Circuit (ASIC) chip especially for increasing the reliability of the system via netlist files generated automatically by the code synthesizer. In this work; Xilinx ISE (Integrated Synthesis Environment) program was used for debugging and implementation of VHDL modules and Xilinx Platform Studio program was used for the design and implementation of Microblaze soft processor. To simulate VHDL modules; Modelsim, which is an advanced simulation and debugging tool for ASIC and FPGA projects provided by Mentor Graphics, is used in this work. Functional block diagram of the FPGA design is shown in Figure 2.10.

Figure 2.10: Functional Block Diagram of the FPGA Design

FPGA utilization of the motor control system in Figure 2.10 is evaluated and the result is listed in Table 2.1

| IP                   | Number of         | Number of          | Number of    |

|----------------------|-------------------|--------------------|--------------|

|                      | Slices            | LUTs               | BRAMs        |

| Microblaze Soft      | 2128 out of 27648 | 3927 out of 55296  | 40 out of 96 |

| Processor IP         | 8%                | 7%                 | 42%          |

| Four Current         | 6050 out of 27648 | 10721 out of 55296 | 8 out of 96  |

| Controllers +        | 22%               | 20%                | 8%           |

| Bus Controller +     |                   |                    |              |

| Spacewire Controller |                   |                    |              |

| External Memory      | 629 out of 27648  | 897 out of 55296   |              |

| Controller           | 2%                | 1%                 |              |

| UART 16750           | 357 out of 27648  | 605 out of 55296   |              |

| Controller           | 1%                | 1%                 |              |

| Encoder              | 327 out of 27648  | 344 out of 55296   |              |

| Glue Logic           | 1%                | 1%                 |              |

| SPI Flash            | 184 out of 27648  | 256 out of 55296   |              |

| Controller           | 1%                | 1%                 |              |

| Microblaze           | 296 out of 27648  | 509 out of 55296   |              |

| PLB                  | 1%                | 1%                 |              |

|                      | 9996 out of 27648 | 509 out of 55296   | 48 out of 96 |

| Total                | 37%               | 32%                | 50%          |

Table 2.1: Summary of the FPGA utilization characteristics for the motor control system

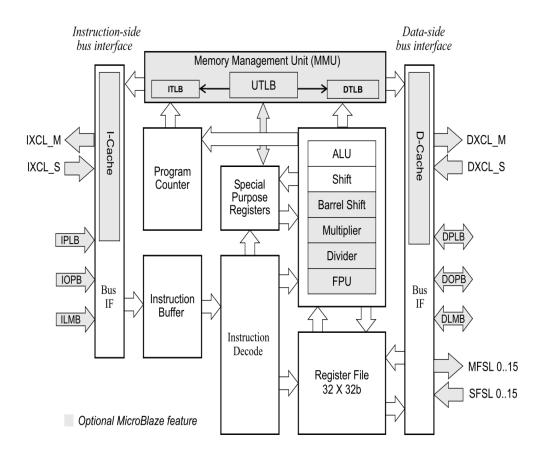

**Microblaze Soft Processor:** The MicroBlaze embedded processor soft core is a *reduced instruction set computer* (RISC) optimized for implementation in Xilinx FPGAs. Microblaze is implemented entirely in the general-purpose memory and the logic fabric of Xilinx FPGAs. Microblaze processor core includes thirty-two 32-bit general purpose registers, 32-bit instruction word, 32-bit address bus and single issue pipeline. Besides these fixed features; processor can be configured for additional functionality such as barrel shifter, hardware multiplier and divider, floating point unit, memory management unit and etc. Microblaze processor core versions are available in the market and version 7.00 is used in this study. Xilinx EDK is the hardware development platform for the Microblaze processor core based systems and Xilinx SDK is the software development platform for the Microblaze core. Functional block diagram of the Microblaze soft processor core is shown in Figure 2.11.

*Pipeline Architecture:* Microblaze core instruction execution is pipelined. Each pipeline stage takes one clock cycle to complete and the completion time of an instruction is equal to the pipeline stages. A few instructions require multiple clock cycles in the execute stage to

Figure 2.11: Functional Block Diagram of the Microblaze Processor Core [17]

complete. This is achieved by stalling the pipeline. When area optimization is enabled, the pipeline is divided into three stages to minimize hardware cost. Three stage pipeline structure is shown in Figure 2.12. However; the pipeline is divided into five stages to maximize the performance when area optimization is disabled.

*Memory Architecture:* Microblaze processor core is implemented with a Harvard Memory architecture; instruction and data accesses are done in separate address spaces [17]. Each address space can handle up to 4 GB of instructions and data memory respectively. Microblaze processor core's instruction and data interfaces are 32 bits wide and use big endian, bit-reversed format. Separate accesses to I/O and memory are not supported in the architecture of the processor. The processor has three interfaces for the memory accesses, which are *Local Memory Bus* (LMB), (Processor Local Bus) (PLB) and *Xilinx Cache Link* (XCL). LMB is a synchronous bus and used for gaining access to block rams available in the FPGA. Xilinx Cache Link is a high performance bus and used for gaining access to cache memories.

|               | cycle 1 | cycle 2 | cycle 3 | cycle4  | cycle5  | cycle6  | cycle7  |

|---------------|---------|---------|---------|---------|---------|---------|---------|

| instruction 1 | Fetch   | Decode  | Execute |         |         |         |         |

| instruction 2 |         | Fetch   | Decode  | Execute | Execute | Execute |         |

| instruction 3 |         |         | Fetch   | Decode  | Stall   | Stall   | Execute |

Figure 2.12: Three Stage Pipeline Structure of the Microblaze Core [17]

Cache memories are used for connection between the core and external memory chip. PLB is a system memory mapped transaction bus with master/slave capability. In this study; we used the local memory bus and Xilinx cache link to access BRAMs and external memory chip, SRAM, respectively. In addition; peripheral local bus (PLB) is used for connection of custom VHDL modules to the processor core.

**External Memory Controller:** To control SRAM chip available in the board; Xilinx generic external memory controller is connected to the Microblaze soft processor core via cache link and peripheral local bus. The Xilinx EDK development platform provides some ready modules for different applications. The generic external memory controller is one of them and it can control SDRAM, SRAM and FLASH chips. However; it is used for the SRAM chip only.

**UART Controller:** A UART controller is decided to be implemented in the FPGA instead of using controller chips on the board because it reduces the cost and the size of the board. Also; it adds configurability and flexibility to the system. After that; we looked for an appropriate VHDL controller and decided to use UART 16750 controller, downloadable from the website of opencores (<sup>6</sup>). The Xilinx EDK platform has a UART 16550 controller, but it can be used after purchasing. UART 16750 controller has some advantages according to the UART 16550 in terms of FIFO size and loopback test modes. The UART 16750 controller is connected to the Microblaze processor core via peripheral local bus.

**SPI Flash Controller:** To control the SPI flash chip; a VHDL controller module was downloaded from the website of opencores and connected to the Microblaze processor core by the peripheral local bus. This module is used as glue logic between the Microblaze processor and flash chip. Controller communicates with the flash chip via *Serial Peripheral Interface* (SPI) according to the commands coming from the Microblaze processor.

<sup>&</sup>lt;sup>6</sup> To get more information about the opencores visit www.opencores.org

**Current Controller:** As mentioned in the previous parts; current controller is coded in VHDL and implemented in the FPGA. The same controller module is used for each motor. To connect current controller of each motor and Spacewire controller with the Microblaze soft processor core; a bus controller is coded in VHDL and connected to the processor. Bus controller module directs the commands and configuration parameters to the related controller and gets information from the controllers according to the request of the processor. Data exchange between the bus controller and processor is done via registers. Spacewire controller is connected to the bus controller instead of connecting to the processor directly. By this way; controller module can be used in a different system as a whole. However; packet controller of the Spacewire protocol must be reimplemented when the spacewire controller is connected to the processor directly. Design and implementation of the controller are explained in detail in Chapter 3.

**Position Controller:** Position controller is coded and implemented in the Microblaze soft processor in the FPGA. Design and implementation of the position controller are explained in detail in Chapter 4.

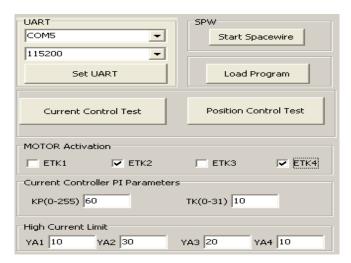

### 2.2 Graphical User Interface Design

To monitor the behavior of the controllers in real time; a graphical user interface (GUI) program is designed and implemented within the scope of thesis work. In addition; GUI is used for configuring the controllers. Program is designed by me and implemented by Kemal Durgut (<sup>7</sup>) in the Borland Developer Studio. GUI program is based on two different test scenarios, which are the position control and current control tests. GUI program is explained in the following parts with the help of snapshots from the program.

**Communication Settings:** Port number of the computer used for the UART communication and the baudrate settings are made by two comboboxes available in the UART part of the GUI. To start spacewire link, "Start Spacewire" button is used. After making the UART settings and starting the spacewire link; other parts of the program are activated. "Load Program" button is used for sending the main code of the processor to it. Settings Part of the GUI is shown in 2.13. This part is available in the upper left of the interface program.

Figure 2.13: Settings Part of the GUI

**Current Controller and Activation Settings:** Before starting to test, the user selects the motors, which will be activated during the test, with the help of checkboxes available in the motor activation part. In addition; parameters of the PI controller available in the current controller are determined by using the text boxes in the "Current Controller PI Parameters" block. Proportional gain (KP) parameter can get the values between 0 and 255. However; Integral gain (KI) parameter can get the values between 0 and 31. After setting the controller

<sup>&</sup>lt;sup>7</sup> He received B.S and M.S degrees in electrical and electronics engineering (EEE) from Hacettepe University. He is also working as an expert research engineer in the software division of TÜBİTAK-SAGE.

parameters, user should enter the high current limit values of each motor to the text boxes available in the "High Current Limit" part of the program. High current limits of each motor can be set independently.

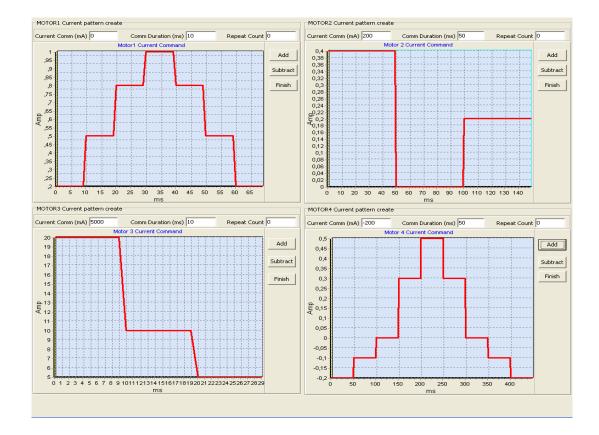

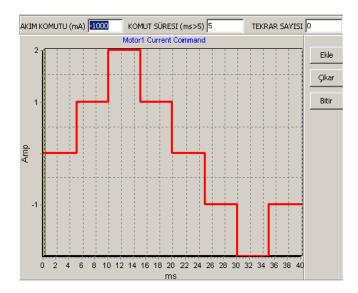

**Current Control Test Patterns:** After setting the current controller's parameters, current patterns, which will be applied to the motor during the test, can be created via the current control test parameters window. This window appears when the "current control test" button is activated. Test patterns can be created independently for each motor. The current control test parameters window of the GUI program is shown in Figure 2.14. User sets the amplitude of the current command in terms of mili-amperes by entering the desired value to the text box called "Current Comm". Duration of the command is determined according to the value in the "Comm Duration" text box. After these steps; command can be shown in the graph by activating the "add" button. If user wants to remove the last command, "subtract" button must be activated. The value of the textbox called as "repeat count" determines how many times the current pattern repeats. The default value of this box is zero, which means infinity repetition.

Figure 2.14: Current Control Test Parameters Window of the GUI

**Position Control Test Patterns:** When the user activates the "position control test" button shown in Figure 2.13, position control test parameters window appears on the screen. User creates position command patterns independently for each motor with the help of this window. A screenshot of this window is shown in Figure 2.15. Two different position command types, square and sine, can be applied to the motors. Peak to peak amplitude of the waveforms can be set in terms of degree with the help of textbox called as "Amplitude". In addition; frequency and duty cycle ratio of the waveforms can be determined in the same way.

| MOTOR1 Position Command |                              |           | MOTOR2 Position Con   | mand                 |                    |

|-------------------------|------------------------------|-----------|-----------------------|----------------------|--------------------|

| Ģ                       | Sine C Square                |           | c                     | Sine 💿 Square        |                    |

|                         | Frequency (Hz) % Duty        | Cycle     | Amplitude (deg)<br>50 | Frequency (Hz)       | % Duty Cycle<br>30 |

| MOTOR3 Position Command |                              |           | MOTOR4 Position Con   | mand                 |                    |

| С                       | 5ine 🖲 Square                |           | ۲                     | Sine 🔿 Square        |                    |

|                         | Frequency (Hz) % Duty 300 70 | Cycle     | Amplitude (deg)<br>80 | Frequency (Hz)<br>90 | % Duty Cycle       |

|                         |                              | Set Paran | neters                |                      |                    |

Figure 2.15: Position Control Test Parameters Window of the GUI

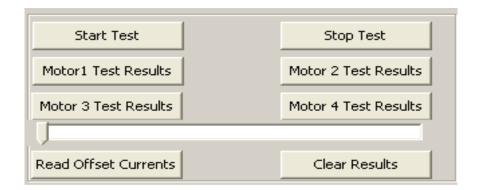

**Start Test:** User can start the test by activating the "Start Test" button, after all settings explained above are made. All commands and setting parameters are sent to the processor with the activation of this button. Processor configures the controllers according to the parameters, which are determined in GUI by the user. At any time of the test, the user can stop by activating the "Stop Test" button. During the test period; user can follow the results of the test by activating the results button of the desired motor. Also; user can see the results of the whole test at the end by sliding the scroll bar. If the user selects save option available at the top of the program, the results of the test will be saved in a text file. By this way; results can be analyzed in a different platform such as MATLAB. Test control part of the GUI is shown in Figure 2.16.

Figure 2.16: Test Control Part of the GUI

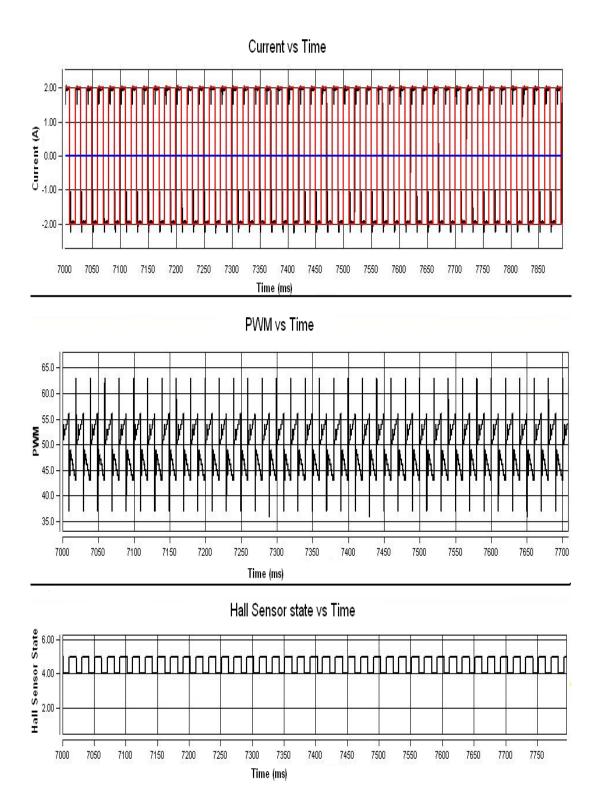

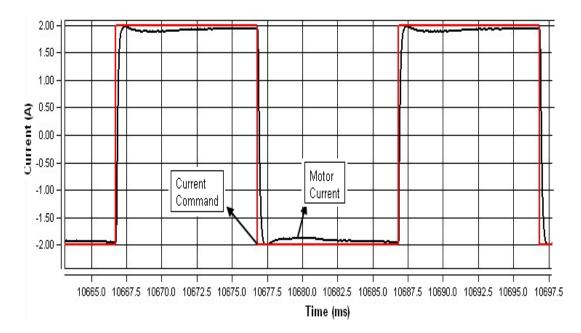

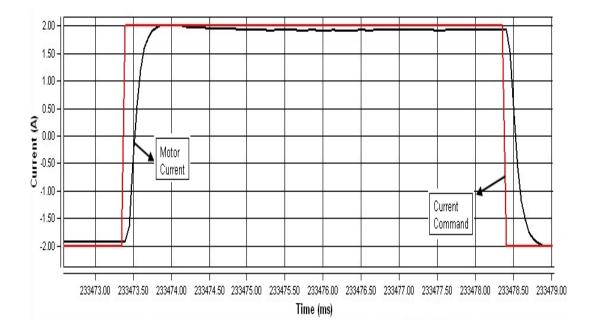

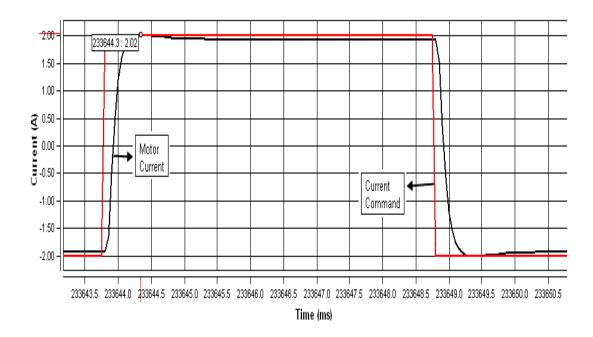

**Results Window:** When the user activates the result button of a motor, results window will appear on the screen. Results window of the current control test differs from the position control test's window in terms of graph's content. Current command versus time (ms) graph is shown for both tests. Feedback current is also drawn on this graph. Second graph of the current control test shows the pulse width modulation magnitude according to the time axis. Final graph of current control test are also shown in the position control test. In addition to these graphs; position of the motor shaft is shown in the position control test. Test results of a current control experiment is shown in Figure 2.17.

# 2.3 Test Setup

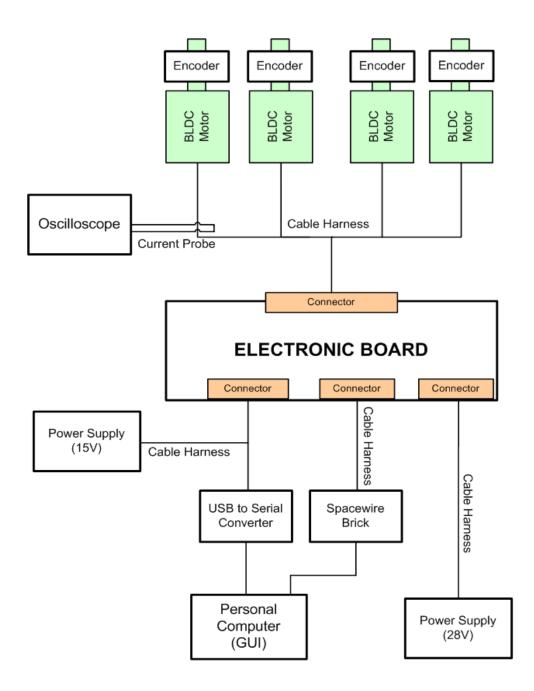

In this section; setup that is used to implement and test the performance of the system will be explained. General diagram of the system is provided in the Figure 2.1. However; structure of the test system will be explained at this part in more detail. Test setup consists of four motors, an electronic board, a graphical user interface, two power supplies, four position sensors, an oscilloscope, a current probe, a RS422/485 USB to serial converter, a spacewire brick and cable harnesses. Structure of the test setup is provided in Figure 2.18.

Board is connected to the motors via a cable harness carrying motor currents, motors' hall sensor data and encoder sensors' data. System was run with the brushless motor, BLM-25-7 manufactured by SL Montevideo Technology, commonly. However; a different model of the brushless motor, is also driven by the system to test the system's adaptability. Functional tests of the system were done with the motors at no-load. On the contrary, performance tests are done with the motors under load. During the functional tests, an oscilloscope with a current

Figure 2.17: Test Results of a Current Control Experiment

Figure 2.18: Structure of the Test Setup

probe is used for verifying the monitor part of the graphical user interface program. Current flowing on three phases of each motor was measured and monitored on the oscilloscope screen with the help of current probe. Comparisons between the graphical results of the oscilloscope and GUI program were made during the functional tests. A Spacewire brick manufactured by Star-Dundee was used for transferring the outputs of the controllers from board to computer via Spacewire protocol. To reduce signal attenuation, crosstalk and skew problems, a specific cable harness was used between the Spacewire brick and board. An overview of the SpaceWire Brick hardware architecture is shown in Figure 2.19.

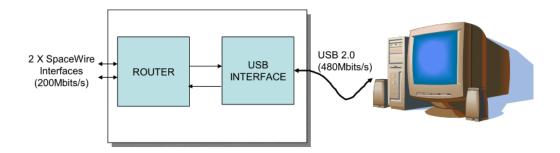

Figure 2.19: An Overview of the SpaceWire Brick Hardware Architecture [18]

A USB to serial converter manufactured by MOXA was used as a translator between the RS422 and USB signals because personal computers don't have a port compatible with RS422 or RS485 electrical standard. Graphical user interface program sends setting parameters and test patterns to the board via UART protocol over the RS422 electrical interface. A single cable harness is used between the board, USB to serial converter module and power supply providing 15V. Digital electronic part of the board is supplied from 15V and other parts are supplied from 28V.

# **CHAPTER 3**

# DESIGN AND IMPLEMENTATION OF CURRENT CONTROLLER

In this study, a current controller is designed and implemented in FPGA to control motor torque. Torque control means controlling the motor current based on the following approximation that

$$Tm = Kt.i \tag{3.1}$$

*Tm* : Motor torque, N-m

Kt : Motor torque constant, N-m/A

*i* : Motor current, A

The performance of the current control system directly affects the position control loop. If the current control loop (inner control loop) cannot trace the current commands coming from the position controller efficiently, position tracking performance of the position controller will degrade dramatically. In the scope of this study, current controller was tested alone firstly to monitor the tracking performance of it. After that; performance of the controller was tested with the position controller loop because the current controller cannot work as stand alone in the system.

In the beginning of design stage; current controller was designed at the conceptual level and simulated in the simulink platform of the MATLAB program. After the conceptual model was verified on the simulation platform, the controller was coded in VHDL. VHDL modules of the current controller were simulated in the MODELSIM simulation program during the coding process. After the completion of these stages, controller was implemented in the FPGA and tested on the board.

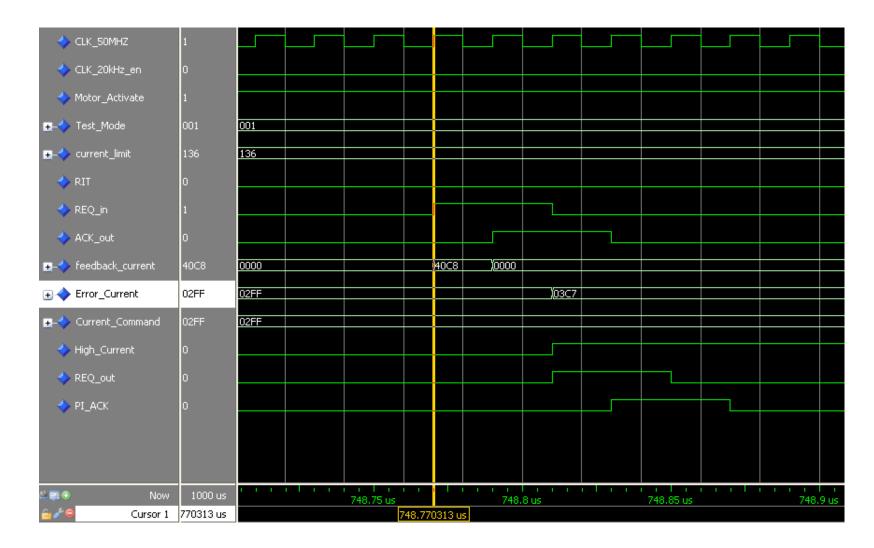

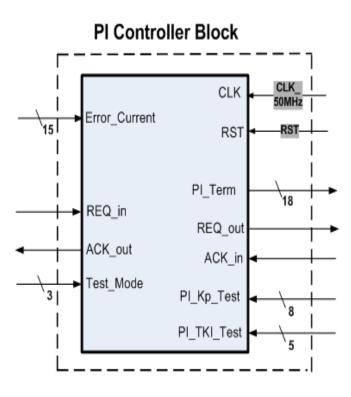

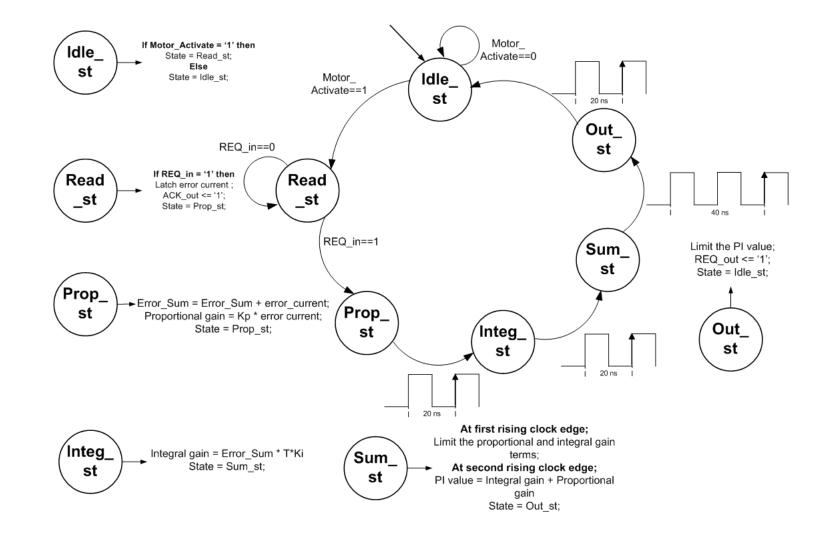

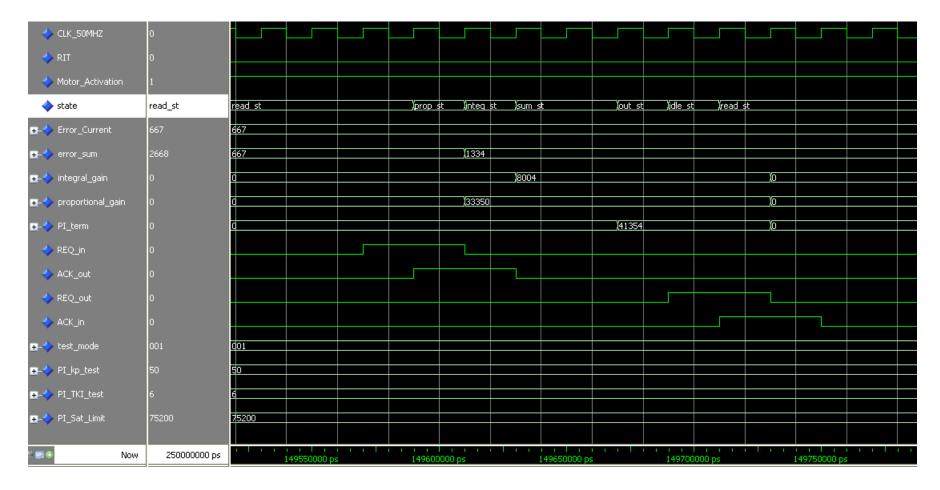

## 3.1 Current Controller Design