#### A NOVEL METHOD FOR 2-18 GHz SWITCHED MULTIPLEXER DESIGN

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

# BÜLENT ALICIOĞLU

#### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2012

Approval of the thesis:

### A NOVEL METHOD FOR 2-18 GHz SWITCHED MULTIPLEXER DESIGN

submitted by **BÜLENT ALICIOĞLU** in partial fulfillment of the requirements for the degree of **Doctor of Philosophy in Electrical and Electronics Engineering Department, Middle East Technical University** by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>              |

|----------------------------------------------------------------------------------------------------|

| Prof. Dr. İsmet Erkmen                                                                             |

| Prof. Dr. Nevzat Yıldırım<br>Supervisor, <b>Electrical and Electronics Engineering Dept., METU</b> |

| Examining Committee Members:                                                                       |

| Prof. Dr. Canan Toker                                                                              |

| Prof. Dr. Nevzat Yıldırım                                                                          |

| Prof Dr. Adnan Köksal                                                                              |

| Prof. Dr. Birsen Saka                                                                              |

| Assoc.Prof.Dr. Şimşek Demir<br>Electrical and Electronics Engineering Dept., METU                  |

**Date:** 14.09.201

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

| Name, Last name | : Bülent ALICIOĞLU |

|-----------------|--------------------|

| Signature       | :                  |

# ABSTRACT

#### A NOVEL METHOD FOR 2-18 GHz SWITCHED MULTIPLEXER DESIGN

Alıcıoğlu, Bülent Ph.D., Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. Nevzat Yıldırım

September 2012, 163 pages

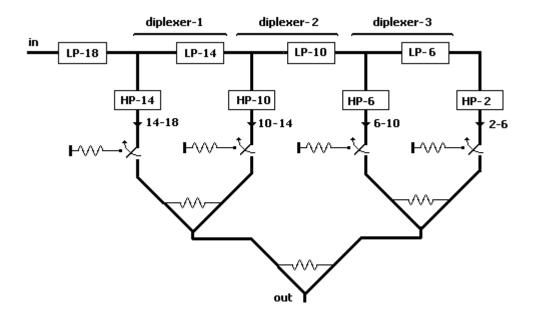

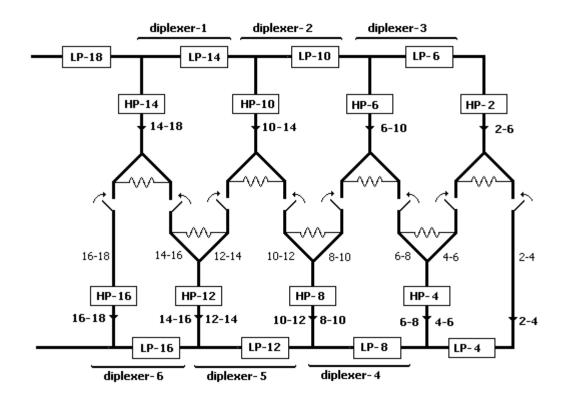

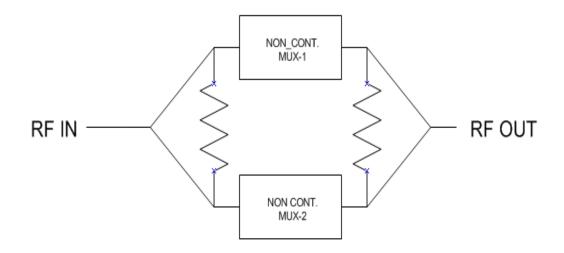

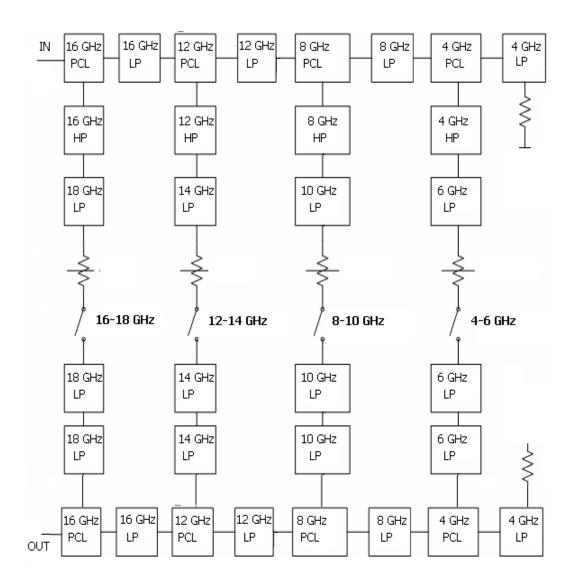

A novel topology is developed and used to design a switched multiplexer. In the new topology there are two noncontiguous switched multiplexer modules containing the channels 2-4 GHz, 6-8 GHz, 10-12 GHz and 14-16 GHz named as odd channels and 4-6 GHz, 8-10 GHz, 12-14 GHz and 16-18 GHz, named as even channels to improve isolation between adjacent channels. The input signal is split at input into the two multiplexer and the outputs of the multiplexers are combined by 2-18 GHz power dividers. The input and output multiplexers are combined through switch + Low Noise Amplifier + attenuator blocks which are also used for amplitude equalization. The input/output multiplexers are designed using a novel technique that transforms a contiguous manifold multiplexer into non-contiguous multiplexers with 2 GHz bandwidth to form guard bands between channels to improve isolation. The HP outputs of the channels are split by LP-HP diplexers with corner frequencies at the centers of the channels. Then only the LP outputs of these diplexers are fed to the output to form a non-contiguous multiplexers. The HP outputs of LP-HP diplexers are terminated in 50 ohms. The incorporation of LP-HP diplexer to form noncontiguous channels is a novel approach which avoids interaction of channels. The diplexers forming the switched multiplexer are designed using a novel approach which incorporate open circuited parallel coupled line as diplexing element. This

structure acts as an integral part of the diplexer and contributes its performance. The LP-HP diplexers are designed and fabricated successfully in suspended stripline. The implemented LP-HP diplexers are then combined to form the even and odd channel multiplexers. The measured results of the individual diplexers are then combined with attenuator+Amplifier blocks to form the circuit model of the targeted switched multiplexer yielding successful performance. Thus, the design is complete and ready for the realization of a switched multiplexer.

Keywords : Stripline, Suspended Stripline, Diplexer, Multiplexer, Switched multiplexer.

# ÖZ

## 2-18 GHz ANAHTARLANABİLİR ÇOĞULLAYICI TASARIMI İÇİN YENİ BİR YÖNTEM

Alıcıoğlu, Bülent Doktora, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Prof. Dr. Nevzat Yıldırım

Eylül 2012, 163 sayfa

Bu tez çalışmasında, 2-18 GHz aralığında çalışan eşit band genişlikli 8 kanaldan oluşan askılı şerit hatlı anahtarlamalı çoğullayıcı, tasarımı özgün bir yöntem kullanılarak tasarlanmıştır. Özgün topolojide iki ayrı süreksiz anahtarlamalı çoğullayıcı ki biri tanesi tek kanallar olarak adlandırılan, 2-4 GHz, 6-8 GHz, 10-12 GHz ve 14-16 GHz kanallarını içermektedir Diğeri ise çift kanallar olarak adlandırılan. 4-6 GHz, 8-10 GHz, 12-14 GHz ve 16-18 GHz kanallarını içermektedir Gelen işaret 2-18 GHz güç bölücü ile her iki çoğullayıcıya da verilmekte ve bu çoğullayıcıların çıkışları 2-18 güç bölücü ile toplanmaktadır. Her iki anahtarlamalı çoğullayıcıdaki giriş ve çıkış çoğullayıcıları, genlik dengeleyici olarak ta kullanılan, yükselteç+zayıflatıcı bloğuyla aralarına bir anahtar konmak suretivle birleştirilmektedir. Giriş ve çıkış çoğullayıcıları, özgün bir yöntem ile tasarlanmaktadır. Bu yöntemde sürekli bir manifold süreksiz bir manifolda dönüştürülerek 2 GHz band genişliğinde kanallar elde edilmekte ve kanallar arasına koruma bandları yerleştirilmektedir. Bu hem yapının anahtarlanabilir olmasını sağlamakta hem de kanallar arası yalıtımı artırmaktadır. Sürekli çoğullayıcıdaki yüksek geçiren kanalların çıkışına ilgili kanalın merkez frekansında ikileyiciler

yerleştirilerek , yerleştirilen ikileyicinin alçak geçiren kanalı çıkışa bağlanarak tek ve çift kanalları içeren süreksiz anahtarlamalı çoğullayıcılar elde edilmektedir. İkileyicilere ait yüksek geçiren kanal 50 ohm ile sonlandırılmaktadır. Bu özgün yöntemin en önemli getirisi kanallar arası etkileşimi en az seviyeye indirmesidir. Hem manifold hem de bunların sonuna eklenen ikileyiciler özgün bir yöntem ile tasarlanmıştır. Bu yöntemde ikileyicide, kanal ayracı olarak açık devre edilmiş bağlaşık hat kullanılmıştır. Bu yapı ikileyicinin bir parçası gibi davranmakta ve performansına katkıda bulunmaktadır. Bu tip ikileyiciler asklı şerit hat kullanılarak bu tezde başarıyla gerçeklenmiştir. Gerçeklenen ikileyiciler daha sonra birleştirilerek çoğullayıcı ve anahtarlamalı çoğullayıcı blokları oluşturulmuştur. Elde edilen ölçüm sonuçları kullanılarak 2-18 GHz mikrodalga anahtarlamalı çoğullayıcının ölçüm sonuçları kullanılarak gerçekçi bir devre modeli oluşturulmuştur. Bu model kullanılarak elde edilen sonuçlara bakıldığında tasarımın tamamlandığı ve üretime hazır olduğu sonucuna varılmıştır.

Anahtar Kelimeler : Şerit Hat, Askılı Şerit Hat, İkileyici, Çoğullayıcı, Anahtarlamalı çoğullayıcı.

To my beloved family

# ACKNOWLEDGEMENTS

I would like to acknowledge the invaluable help and encouragement of my supervisor Prof. Dr. Nevzat Yıldırım. I thank him for his patience, guidance and knowledgeable advice throughout the development of this study.

I would like to thank Zeynep Eymür, Gökhan Boyacıoğlu, Sacid Oruç Arda Özgen, Onur Özgür, Şerif Can Tekin, Galip Keçelioğlu and for their precious suggestions and technical advices during the improvement of this thesis. My thanks also go to all clean room staff especially Tülay Can Nuretdin Şahin and Murat Özdemir, Murat Mutluol and Turan Yıldırım for their great help in assembling and measurement processes. I need to acknowledge to Ahmet Öztekin for his efforts in producing the PCB designs. I would also like to thank to ASELSAN Inc. that provides me facilities and resources to complete the fabrication and measurement processes.

I sincerely thank to my wife Yasemin, my parents Atalay and Şerife, my sisters Buket and Nüket, without their encouragement and support, this work would never be possible.

I thank my daughter İdil Bilge who brought a new meaning to my life, and my nephews Deniz, Can and Emir for being such adorable.

# TABLE OF CONTENTS

| ABSTRA   | ACTi                                                                    | v  |

|----------|-------------------------------------------------------------------------|----|

| ÖZ       |                                                                         | vi |

| ACKNO    | WLEDGEMENTSi                                                            | X  |

| TABLE (  | OF CONTENTS                                                             | X  |

| LIST OF  | FIGURESx                                                                | ii |

| LIST OF  | ABBREVIATIONSxv                                                         | ii |

| CHAPTE   | ERS                                                                     |    |

| 1.INTRO  | DUCTION                                                                 | 1  |

| 1.1      | Scope and Objective                                                     | 1  |

| 1.2      | CAD Tools                                                               | 2  |

| 1.3      | Organization Of the Thesis                                              | 3  |

| 2.A SUR  | VEY ON SWTCHED MULTIPLEXERS                                             | 5  |

| 2.1      | General Information                                                     | 5  |

| 2.2      | Basic Multiplexer Types                                                 | 6  |

| 2.3      | Simple Ladder Type HP-LP Switched Multiplexers (SW_MUX) 1               | 2  |

| 2.4      | Ladder Type HP-LP Switched Multiplexers with Power Dividers             | 2  |

| 2.5      | Manifold Type Stripline Multiplexers With Tee-Junctions                 | 4  |

| 2.6      | Hybrid Coupled Manifold Multiplexer 1                                   | 5  |

| 2.2.1    | 1 3 dB Impedance Transforming Branchline Couplers With Ideal Inverter   | S  |

|          | 1                                                                       | 6  |

| 2.7      | Circulator Coupled Multiplexers                                         | 0  |

| 2.8      | Multiplexers Using Directional Filters                                  | 1  |

| 2.9      | Parallel Coupled Line Type Manifolds                                    | 2  |

| 2.9.1    | 1.Series Multiplexing Manifold2                                         | 3  |

| 2.9.2    | 2. Parallel Multiplexing Manifold2                                      | 6  |

| 2. 10. 4 | A Novel Switched Multiplexer Topology2                                  | 9  |

| 3.THE U  | SE OF PARALLEL COUPLED LINES AS DIPLEXING ELEMENTS 3                    | 5  |

| 3. 1. C  | ircuit Models of Parallel Coupled LIines                                | 6  |

| 3.2. Se  | ries and Parallel Diplexeing Using Two Parallel Coupled Line Sections 4 | 8  |

| 3.3. Comparison of Return Loss Performances of PCL and T-Junction Diplexing |   |

|-----------------------------------------------------------------------------|---|

|                                                                             | 5 |

| 3.4. Comparison of Isolation performances of PCL and T-Junction Diplexing 6 | 2 |

| 4.EM MODELING OF DIPLEXERS                                                  | 4 |

| 4.1 Why Do We Need EM Modelling?7                                           | 4 |

| 4.2.Design of 14 GHz Highpass Filter7                                       | 6 |

| 4.3.Design of 6 GHz Diplexer                                                | 5 |

| 4.4 Measurement Results For Other Diplexers                                 | 5 |

| 5.INTEGRATION OF DIPLEXERS                                                  | 4 |

| 5.1 Design of 2 GHz HP Filter10                                             | 9 |

| 5.2 Design of 18 GHz LP Filter 11                                           | 6 |

| 5.3 Design of 2-18 GHz Power Divider/Combiner                               | 0 |

| 5.4 Design Of Manifold Multiplexers12                                       | 2 |

| 5.5 Design of Non-Contiguous Channel Multiplexers                           | 0 |

| 5.6 Design of Non-Contiguous Channel Switched Multiplexers                  | 7 |

| 6.CONCLUSION                                                                | 5 |

| REFERENCES                                                                  | 8 |

| CURRICULUM VITAE                                                            | 3 |

# LIST OF FIGURES

# FIGURES

| Figure 2.1 Some Parallel Connected Diplexers                                     |

|----------------------------------------------------------------------------------|

| Figure 2.2 Typical Parallel Connected Multiplexer Structures7                    |

| Figure 2.3 A Simple SW_MUX Based on LP-HP Diplexers 12                           |

| Figure 2.4 A Switchable LP-HP Multiplexer Using Power Dividers                   |

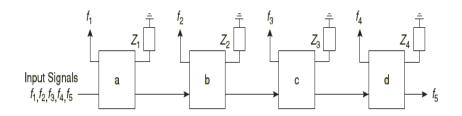

| Figure 2.5 An 8 Channel 2-18GHz SW_MUX14                                         |

| Figure 2.6 A Manifold (Extended Junction) Stripline Multiplexer15                |

| Figure 2.7 Hybrid Coupled Manifold Multiplexer16                                 |

| Figure 2.8 Schematics of a 3 dB Impedance Transforming Branchline Coupler with   |

| Different Input-Output Terminations                                              |

| Figure 2.9 Power Flow in One Channel of Hybrid Manifold Multiplexer 19           |

| Figure 2.10 A Switchable Hybrid Multiplexer                                      |

| Figure 2.11 A Circulator Coupled Multiplexer                                     |

| Figure 2.12 A Directional Filter Multiplexer                                     |

| Figure 2.13 Series Diplexing PCL                                                 |

| Figure 2.14 Parallel diplexing PCL                                               |

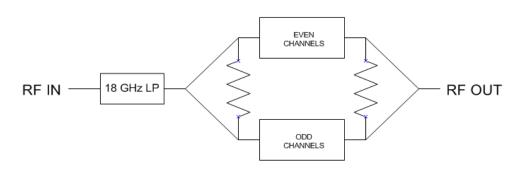

| Figure 2.15 Combining two non-contiguous multiplexers                            |

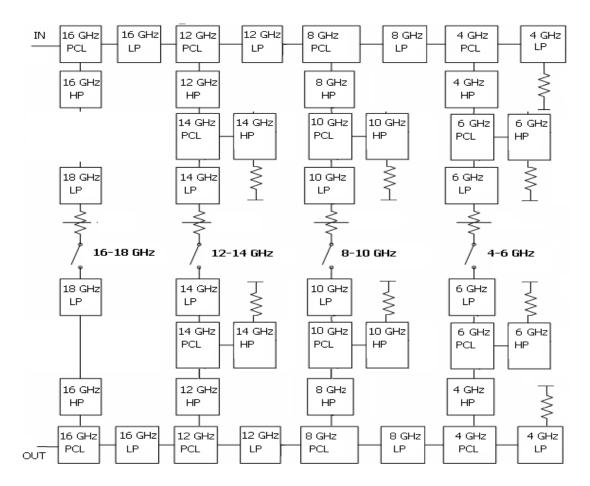

| Figure 2.16 Even Half of SW_MUX with LP filter                                   |

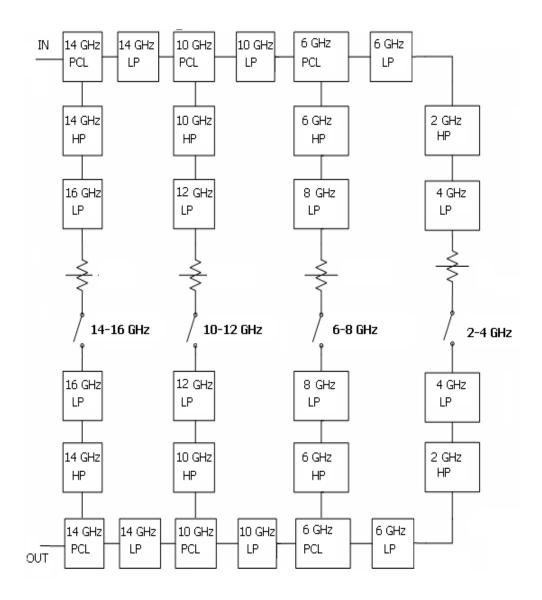

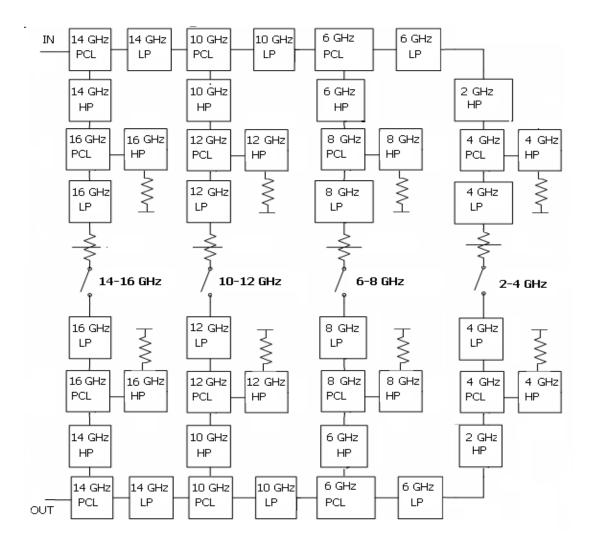

| Figure 2.17 Odd Half of SW_MUX with LP filter                                    |

| Figure 2.18 Connection of even and odd channel multiplexers through splitters 32 |

| Figure 2.19 Even Half of SW_MUX with diplexers in place of extra attenuators 33  |

| Figure 2.20 Odd Half of SW_MUX with diplexers in place of extra attenuators 34   |

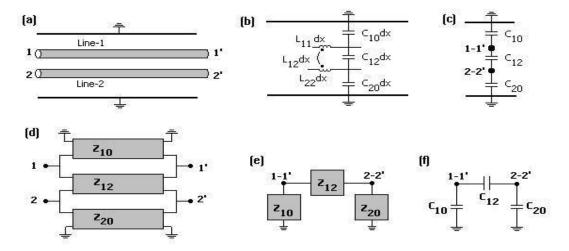

| Figure 3.1Three Line model of a parallel coupled line pair               | . 36 |

|--------------------------------------------------------------------------|------|

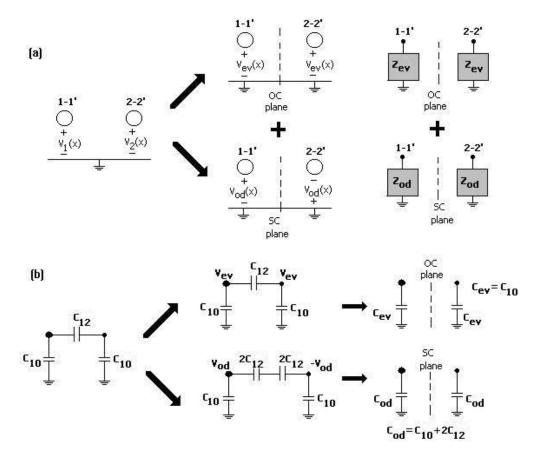

| Figure 3.2 Even-odd mode decomposition of a symmetric PCL pair           | . 39 |

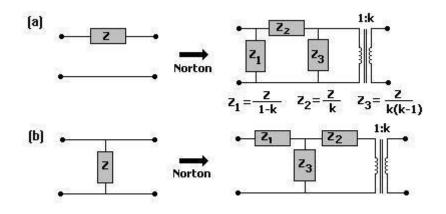

| Figure 3.3.Norton Transformations                                        | . 40 |

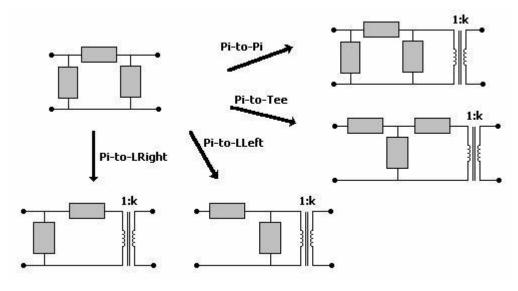

| Figure 3.4 Pi-Tee-L Transformations                                      | . 40 |

| Figure 3.5 Pi to Pi Transformatiom applied on a coupled line             | . 42 |

| Figure 3.6 Equating shunt impedances of an N-coupled line system for N=5 | . 43 |

| Figure 3.7 Pi -to- Lright and Pi -to- Lleft transformations applies to a PCL      | 46 |

|-----------------------------------------------------------------------------------|----|

| Figure 3.8 Type-1 series diplexing PCL circuit                                    | 50 |

| Figure 3.9 Various possible series multiplexing circuits                          | 50 |

| Figure 3.10 Type-2 Series Diplexing Circuit                                       | 52 |

| Figure 3.11 Type-1 Parallel Diplexing Circuit                                     | 53 |

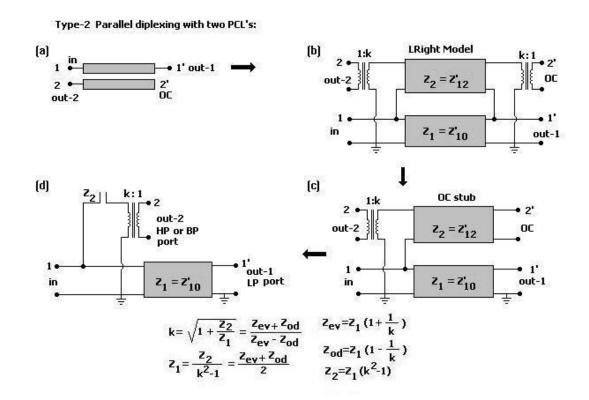

| Figure 3.12 Type-2 Parallel Diplexing Circuit                                     | 54 |

| Figure 3.13 . LP channel Filter Schematics                                        | 55 |

| Figure 3.14 . HP channel Filter Schematics                                        | 56 |

| Figure 3.15 Formation of the Diplexer with T-junction                             | 57 |

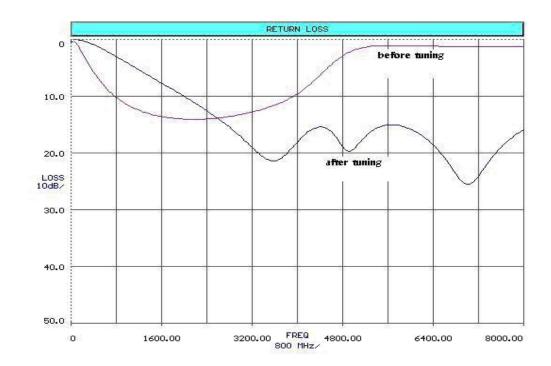

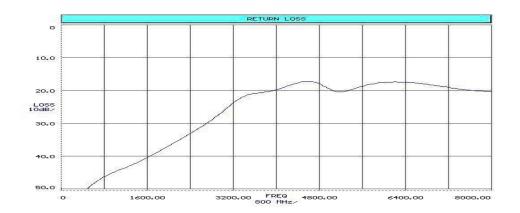

| Figure 3.16 . Return Loss of the diplexer with t-Junction before and after tuning | 57 |

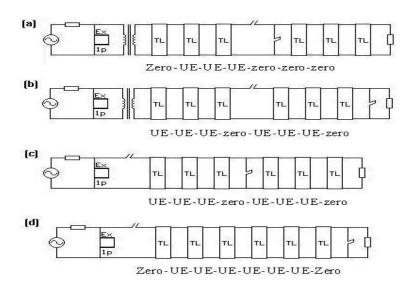

| Figure 3.17 Four different forms of extraction for HP channel Option-2            | 58 |

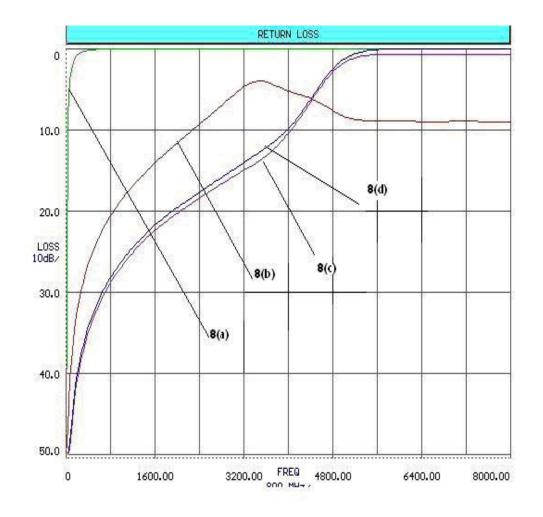

| Figure 3.18 Comparison of different extraction schemes for Option-2               | 59 |

| Figure 3.19. Formation of HP channel for Option-2                                 | 60 |

| Figure 3.20 . Return loss for HP channel Option-2                                 | 61 |

| Figure 3.21 . Final HP channel schematics for Option-2                            | 61 |

| Figure 3.22 LP channel schematics                                                 | 63 |

| Figure 3.23. HP channel schematics after the extraction of TZ's                   | 64 |

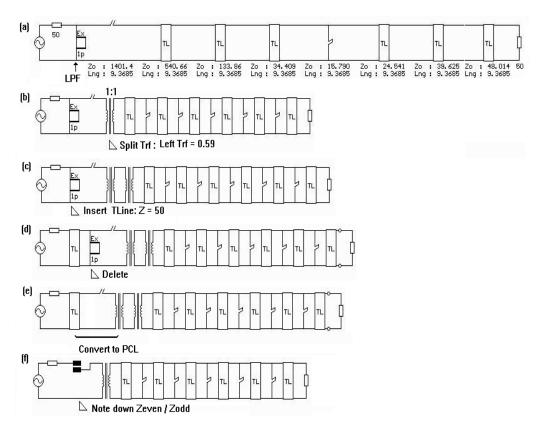

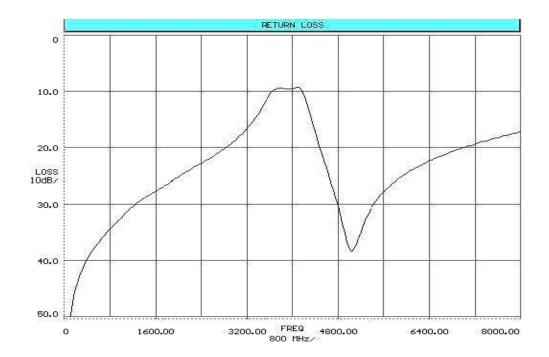

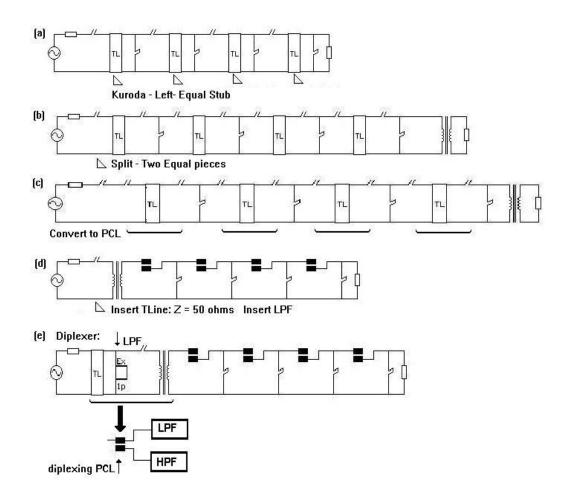

| Figure 3.24 Design steps for HP channel and diplexer                              | 64 |

| Figure 3.25. Diplexer return loss after tuning transformer in HP channel          | 65 |

| Figure 3.26. HP channel schematics after the extraction of TZ's                   | 65 |

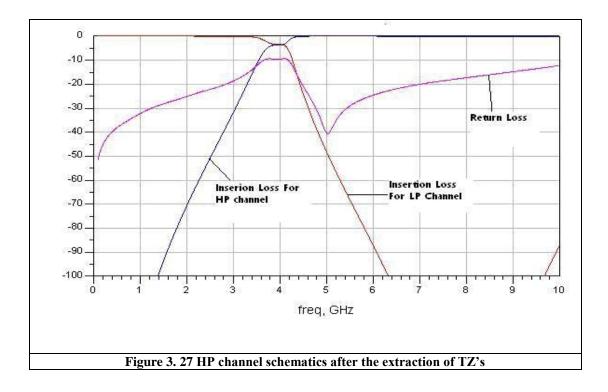

| Figure 3.27 HP channel schematics after the extraction of TZ's                    | 66 |

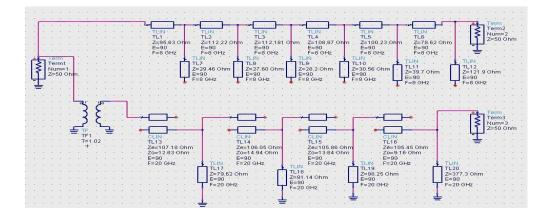

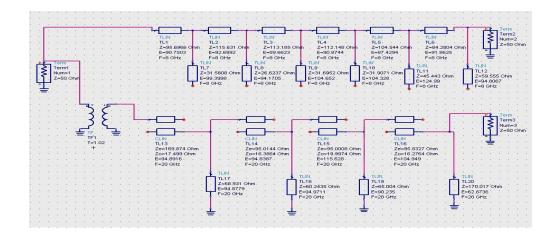

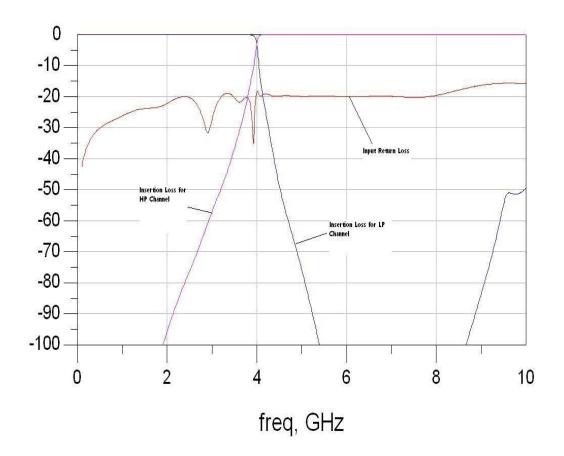

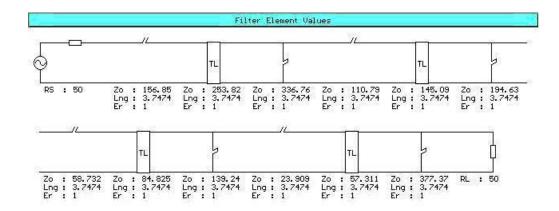

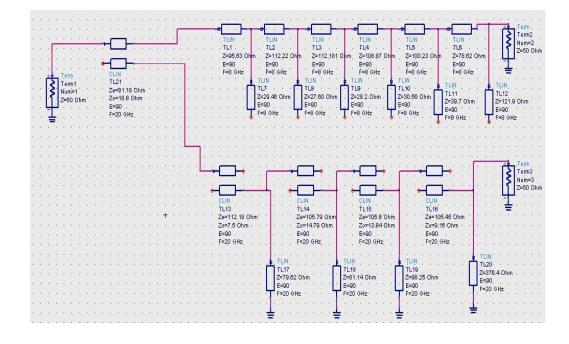

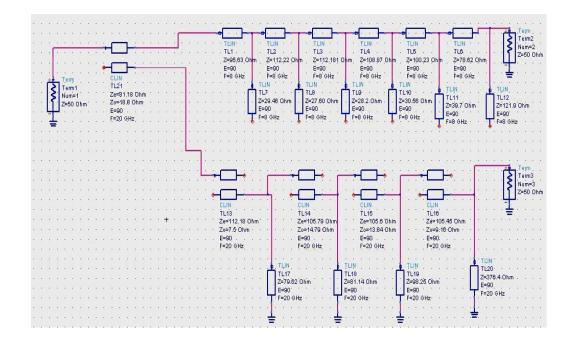

| Figure 3.28 Diplexer after optimization in ADS                                    | 66 |

| Figure 3.29. Diplexer response after optimization in ADS                          | 67 |

| Figure 3.30. HP channel after extraction                                          | 68 |

| Figure 3.31 Formation of the Diplexer                                             | 69 |

| Figure 3.32 Diplexer before optimization                                          | 70 |

| Figure 3.33. Diplexer after optimization                                          | 70 |

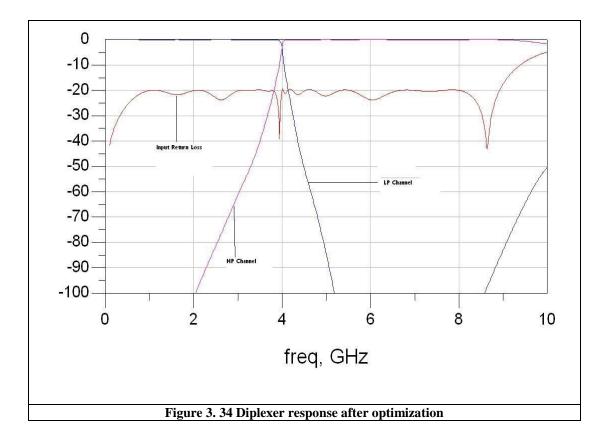

| Figure 3.34 Diplexer response after optimization                                  | 71 |

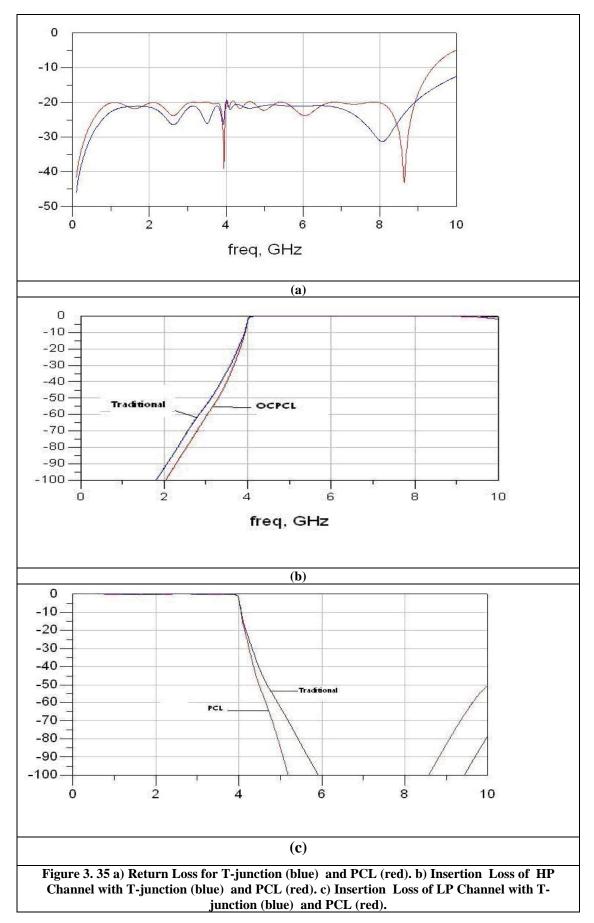

| Figure 3.35 Diplexer with T-junction diplexing                                    | 72 |

|                                                                                   |    |

|                                                                                   |    |

| Figure 4.1 Design steps for the 14 GHz HPF in FILPRO | 76 |

|------------------------------------------------------|----|

| Figure 4.2 14 GHz HPF in ADS                         | 77 |

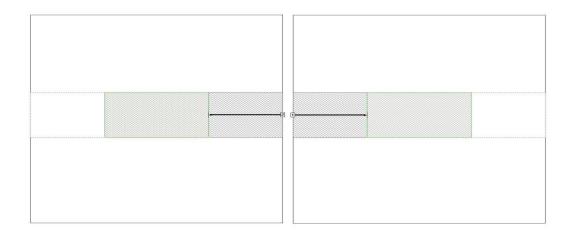

| Figure 4.3 Capacitors to be replaced                 | 78 |

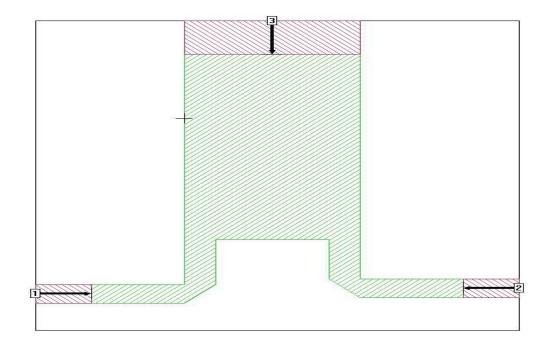

| Figure 4.4 Simulation layout for broadside coupled line replacing capacitors |

|------------------------------------------------------------------------------|

| Figure 4.5 TL+cap+TL and TL+stub+TL triplets                                 |

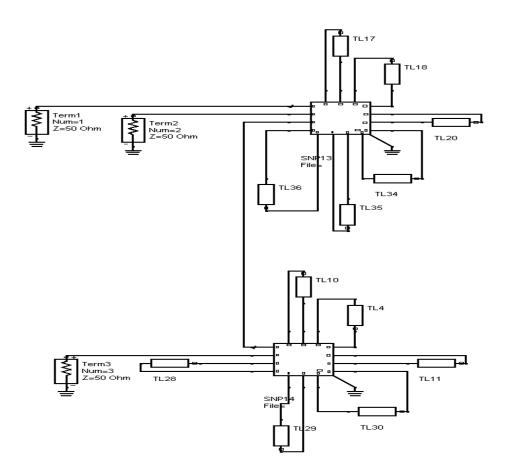

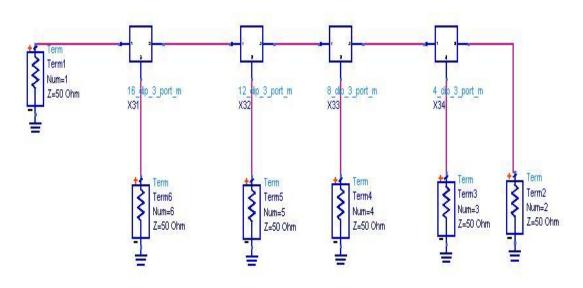

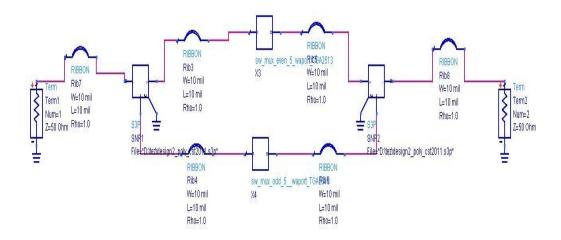

| Figure 4.6 28 port circuit in ADS to optimize SONNET modeling                |

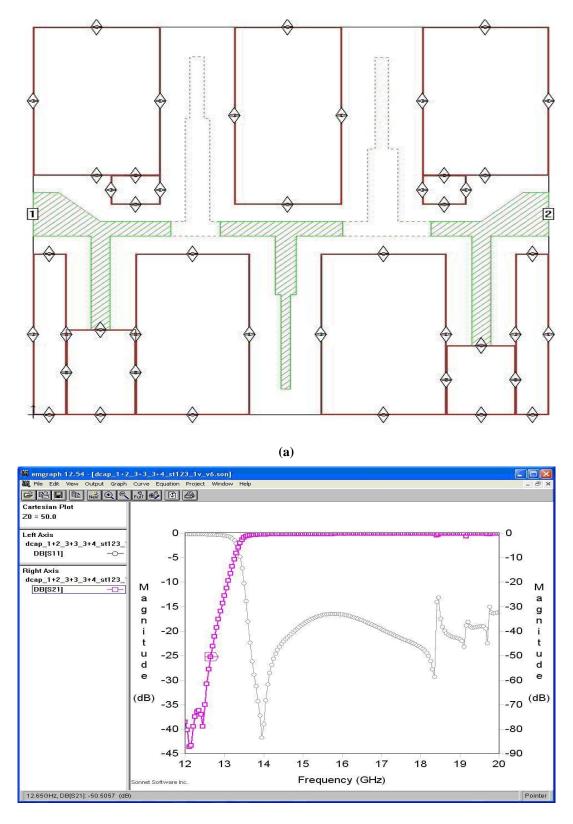

| Figure 4.7 Final SONNET layout and Its response for 14 GHz HPF               |

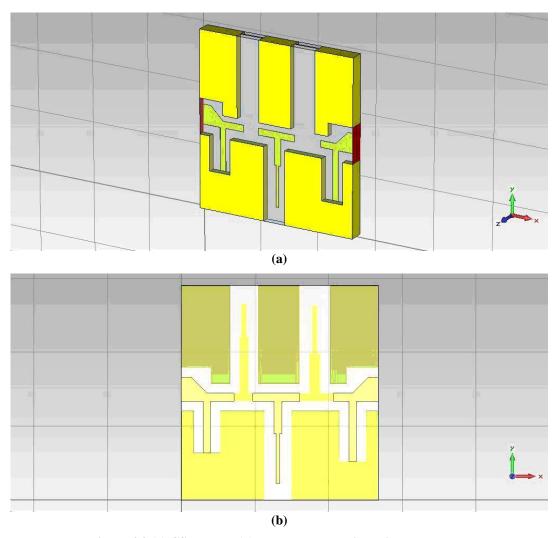

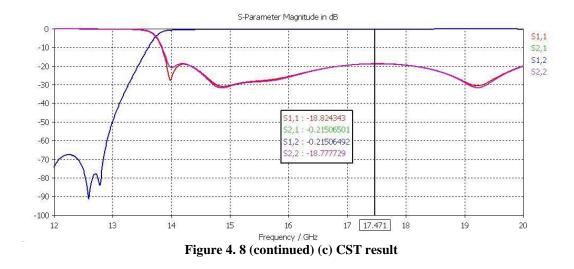

| Figure 4.8 CST results for 14 GHz HPF                                        |

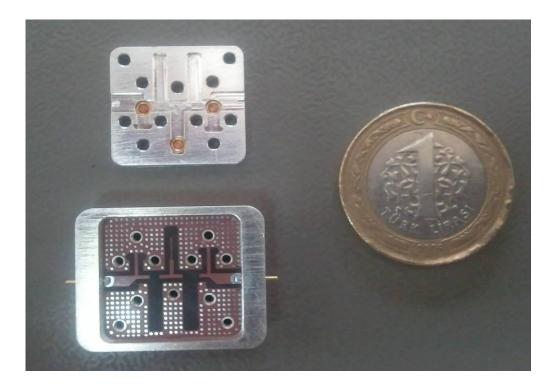

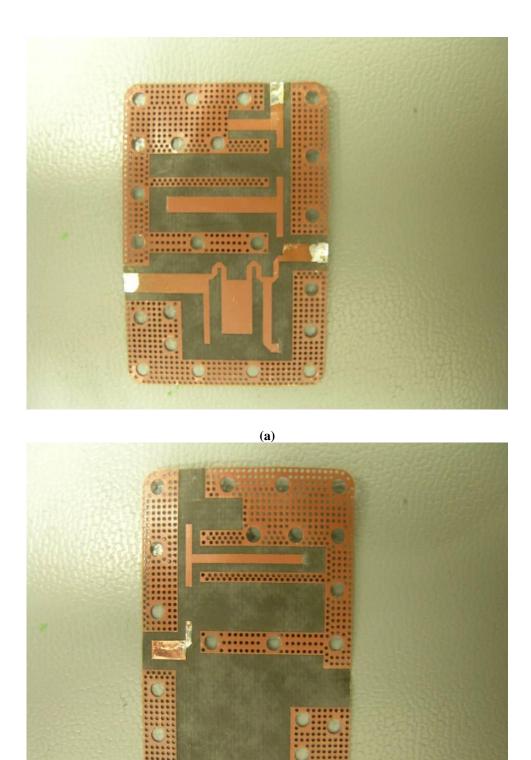

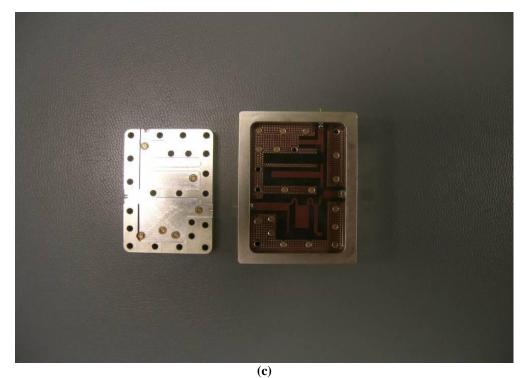

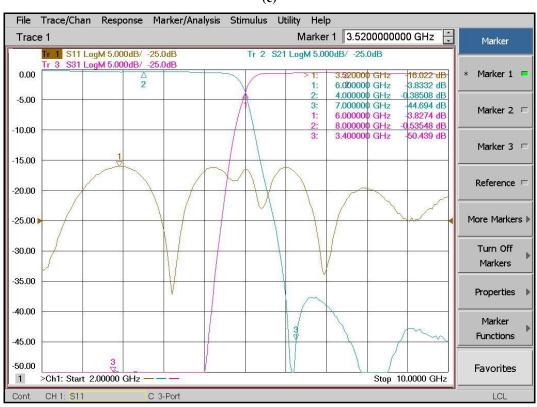

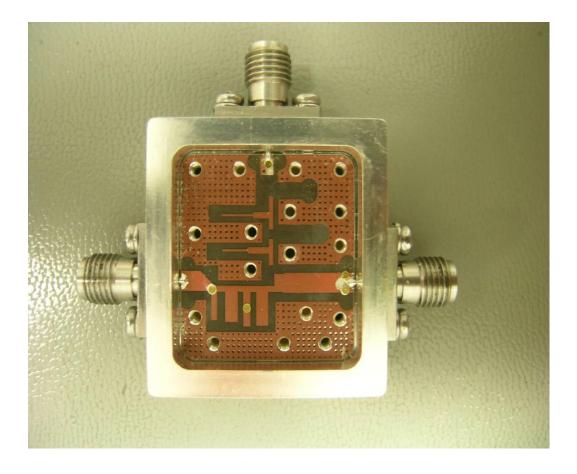

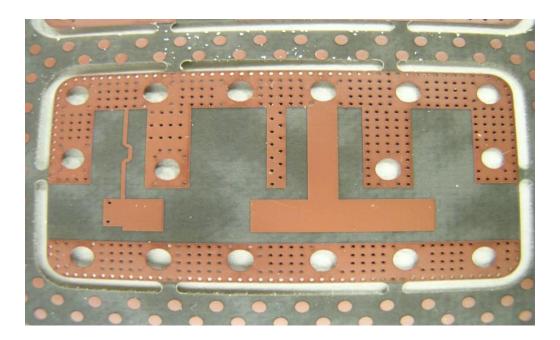

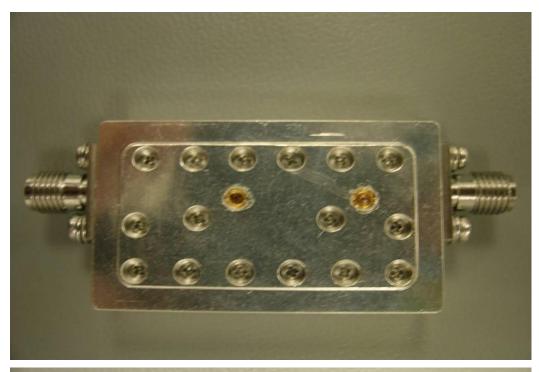

| Figure 4.9 14 GHz HP filter module                                           |

| Figure 4.14 GHZ HPF measurement results                                      |

| Figure 4.11 Design steps for HP channel of 6 GHz diplexer                    |

| Figure 4.12 FILPRO circuit of LP channel of 6 GHz diplexer                   |

| Figure 4.13 ADS circuit of 6 GHz diplexer                                    |

| Figure 4.14 TL-stub-TL triplet                                               |

| Figure 4.15 N-port circuit for optimizing diplexer response                  |

| Figure 4.16 LPF of 6 GHz diplexer90                                          |

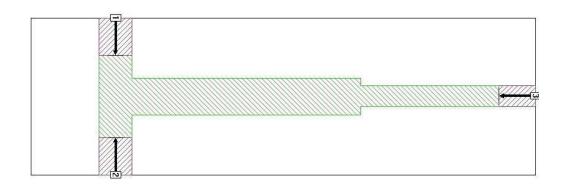

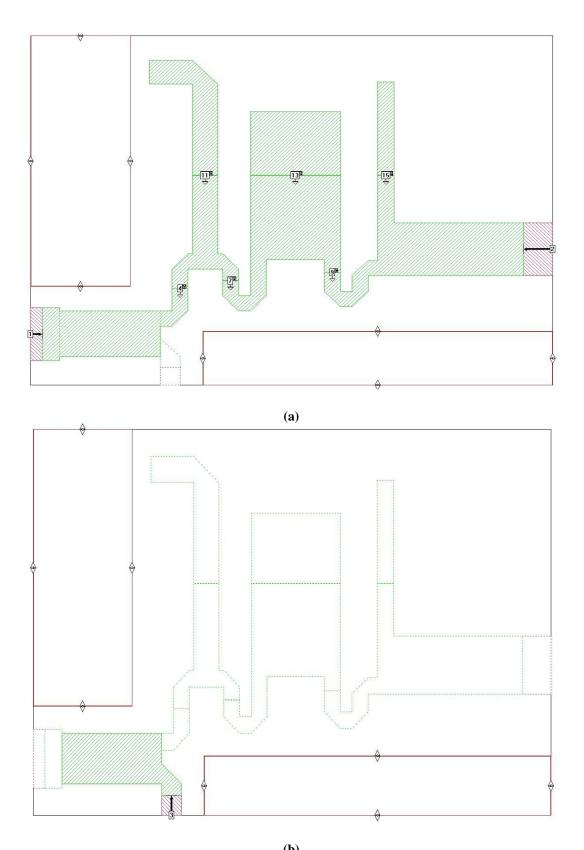

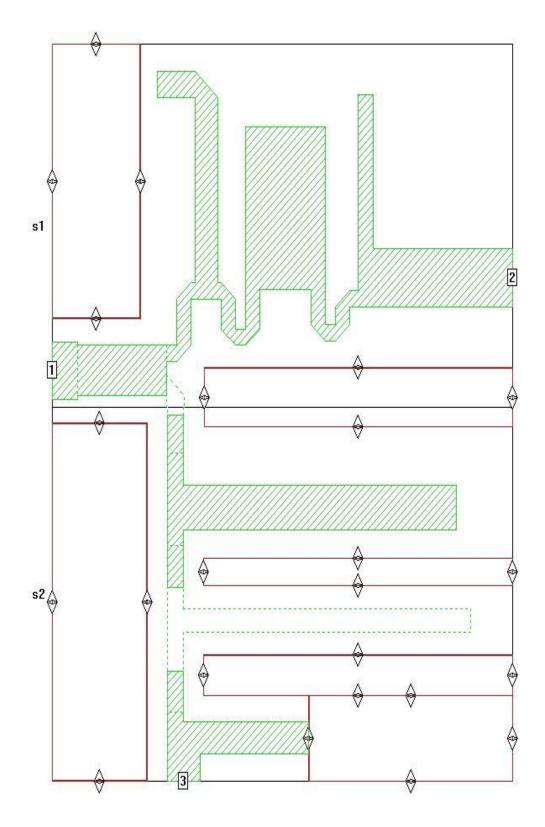

| Figure 4.17 Layout for 6 GHz diplexer                                        |

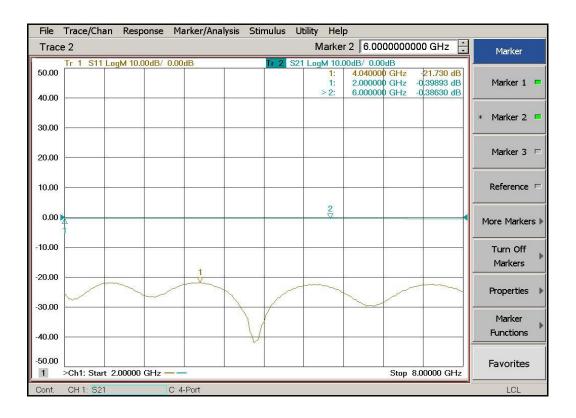

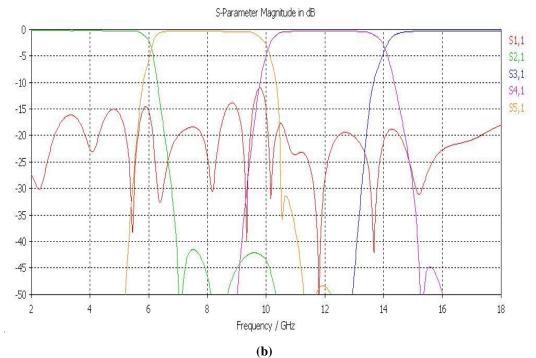

| Figure 4.18 Responses of first batch of diplexers                            |

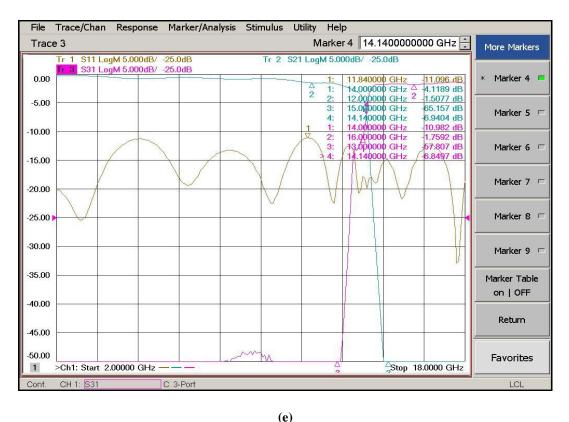

| Figure 4.19 Mechanical view of connector                                     |

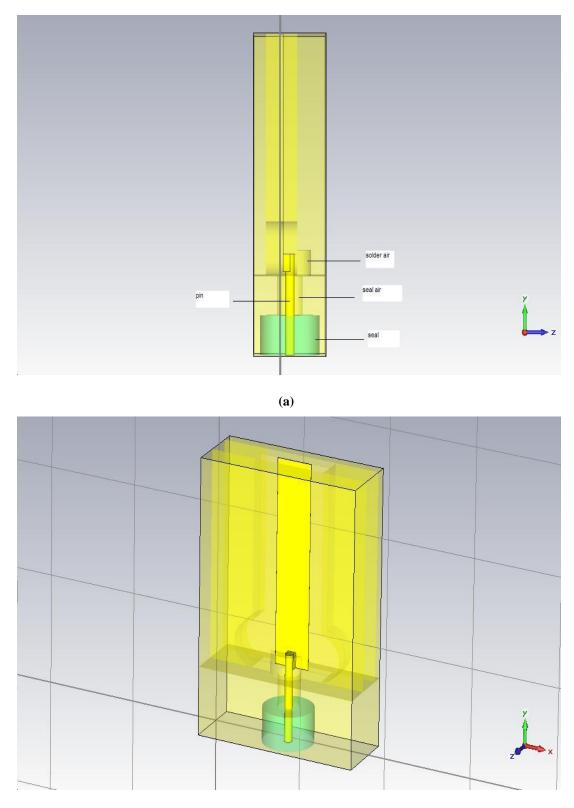

| Figure 4.20 CST simulation results after modification                        |

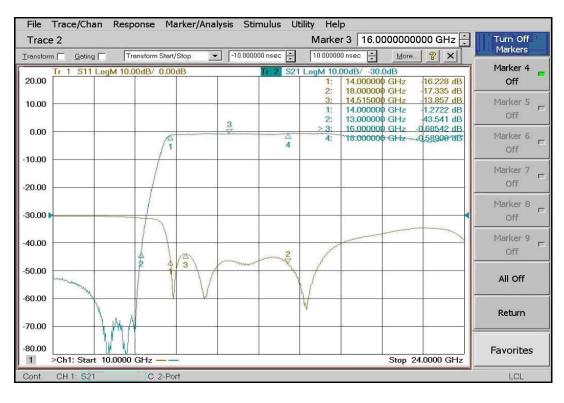

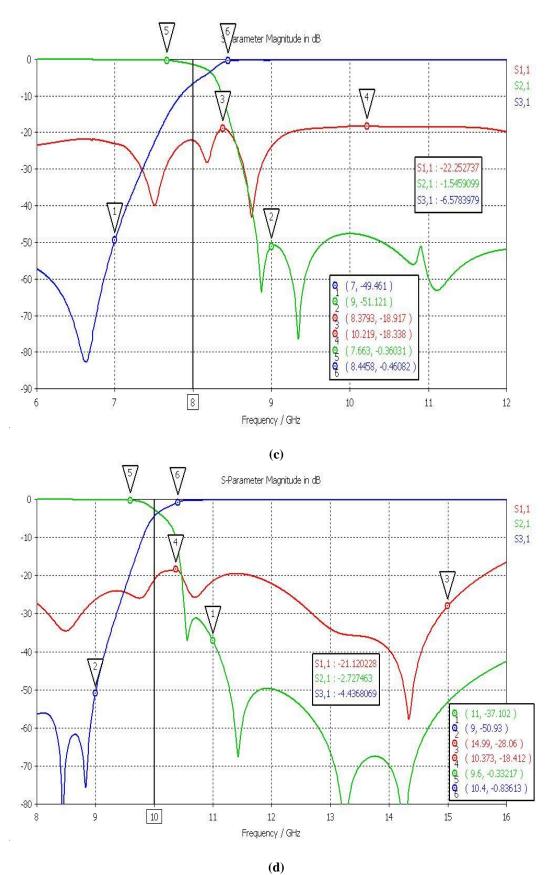

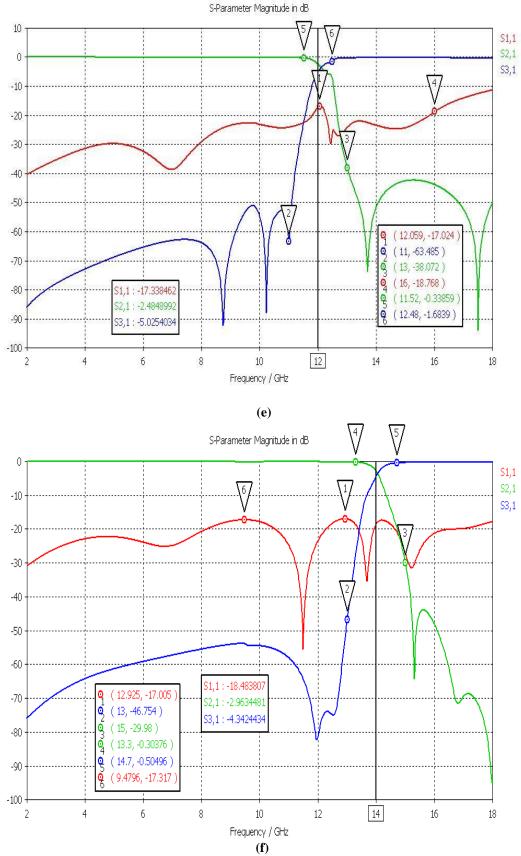

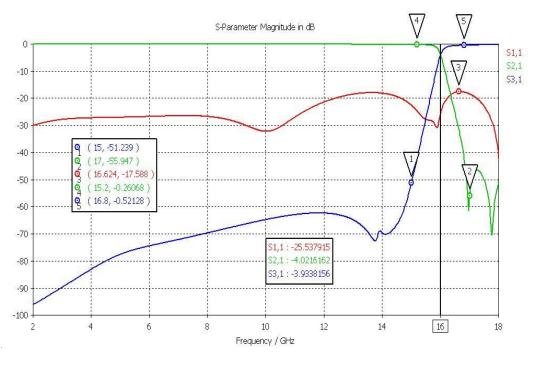

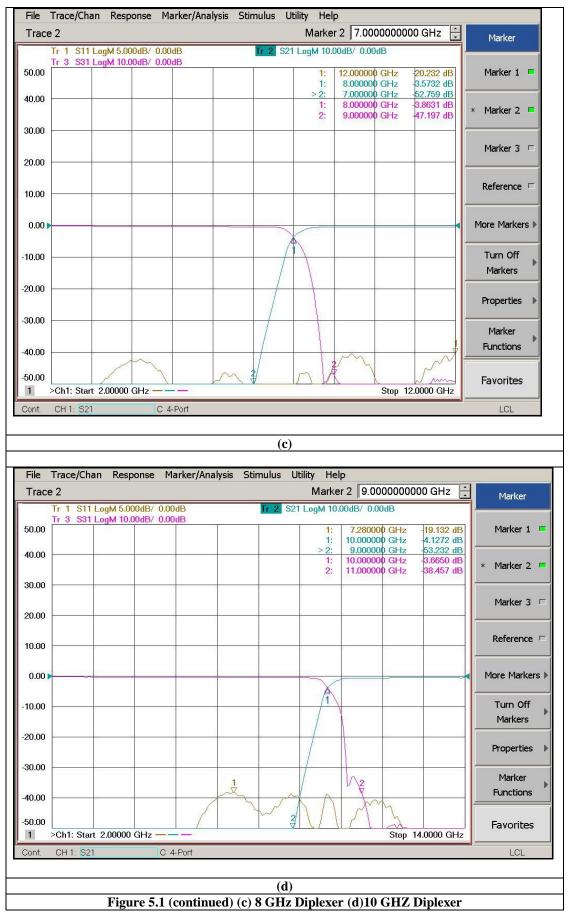

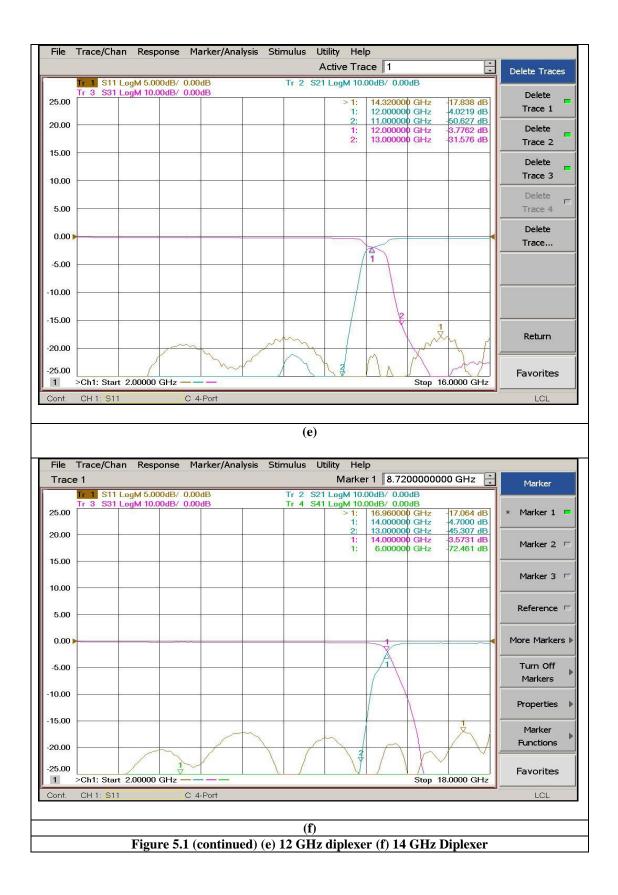

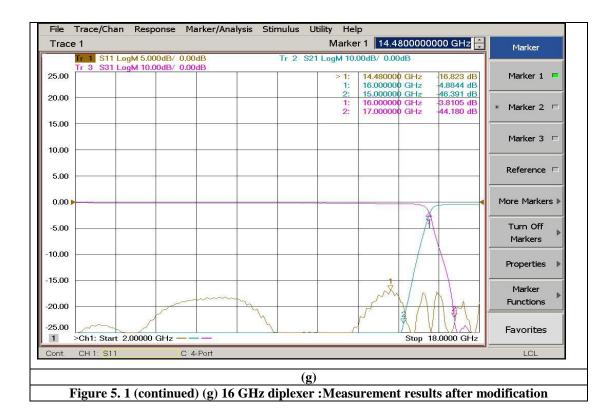

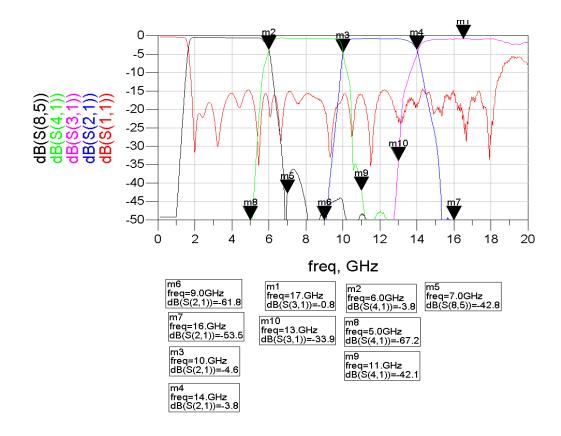

| Figure 5.1 Measurement results after modification                            | 108      |

|------------------------------------------------------------------------------|----------|

| Figure 5.2 12 GHz Diplexer Layout                                            | 108      |

| Figure 5.3 14 GHz diplexer                                                   | 109      |

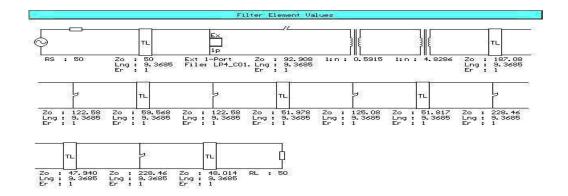

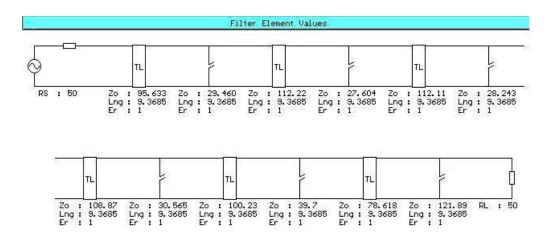

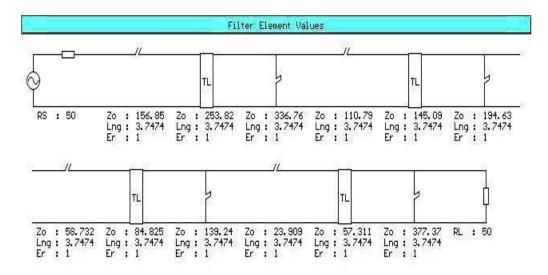

| Figure 5.4 Design of 2 GHz HP filter in FILPRO                               | 110      |

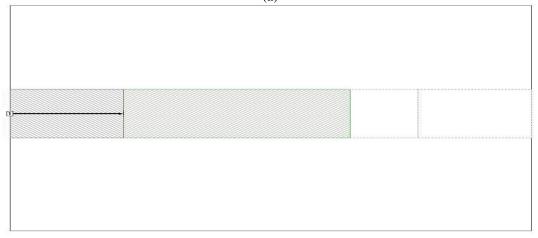

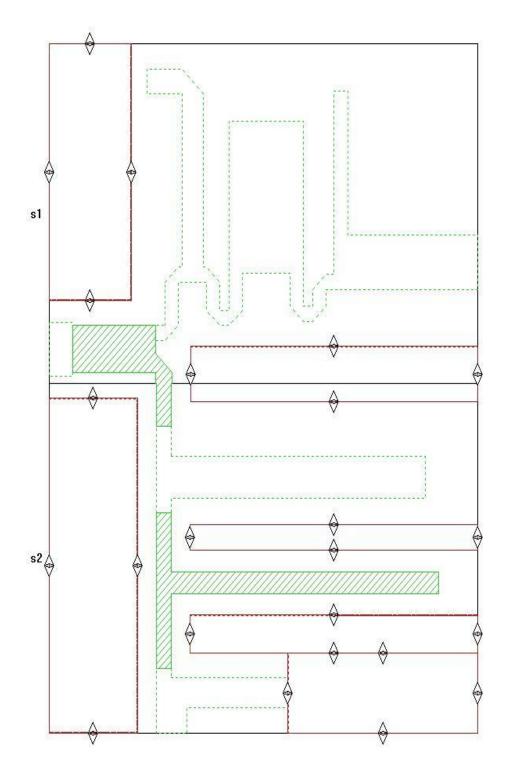

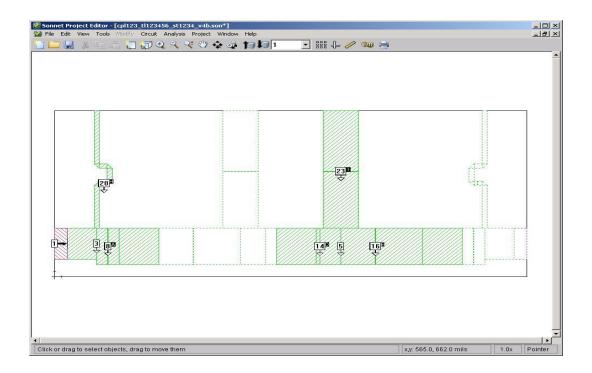

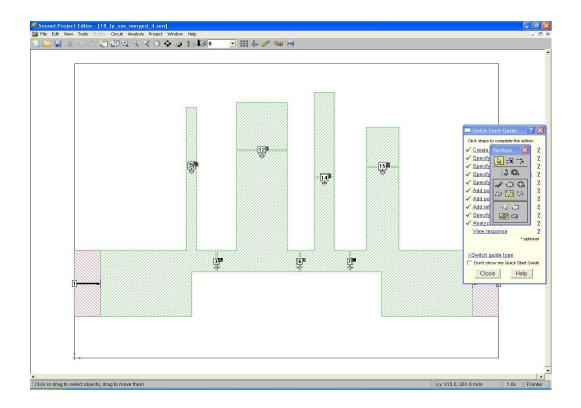

| Figure 5.5 N-port SONNET layout for 2 GHz HP filter:                         | 111      |

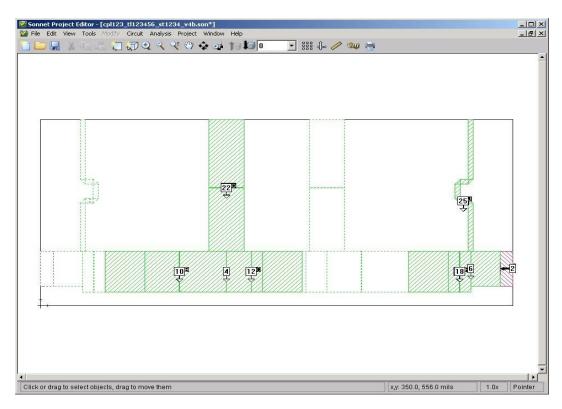

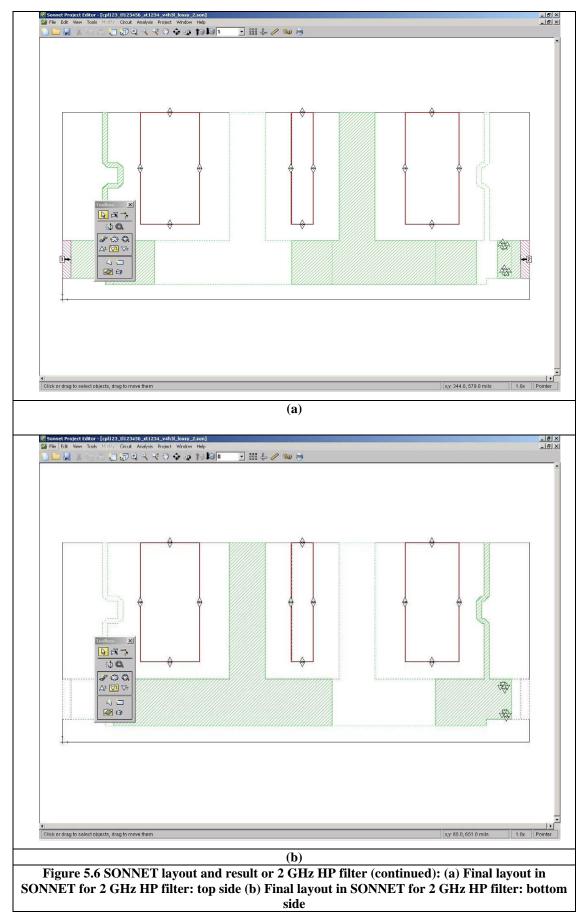

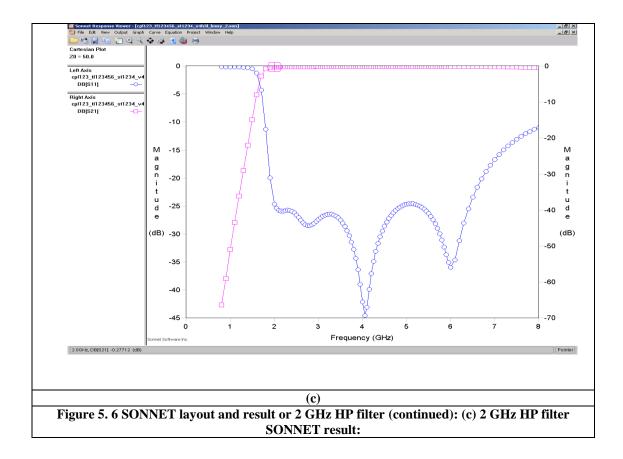

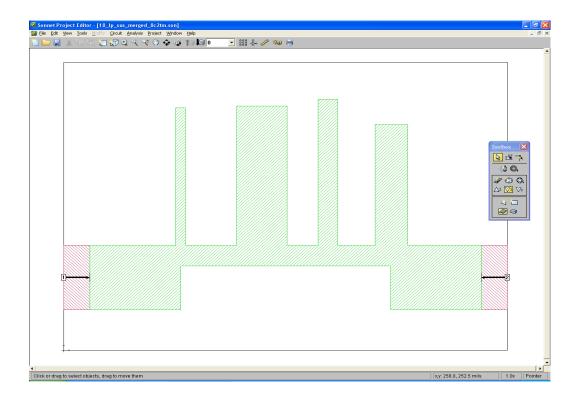

| Figure 5.6 SONNET layout and results or 2 GHz HP filter                      | 113      |

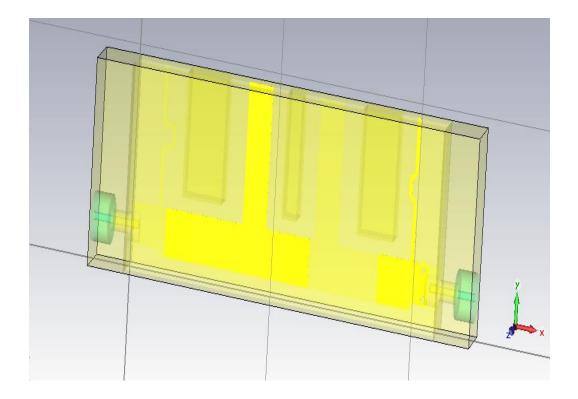

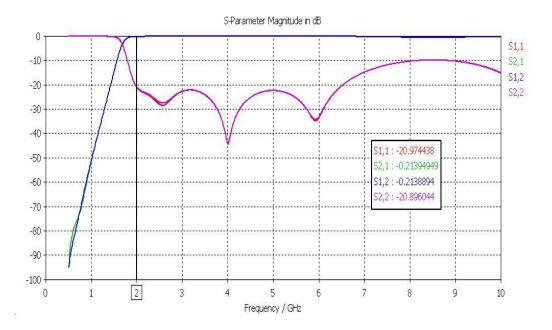

| Figure 5.7 CST results and layout for 2 GHz HP filter                        | 114      |

| Figure 5. 8 18 GHz LP filter                                                 | 117      |

| Figure 5.9 18 GHz LP filter : N-port SONNET layout                           | 117      |

| Figure 5.10 18 GHz LP filter (a) 18 GHz LP filter final circuit (b) 18 GHz L | P filter |

| final circuit: SONNET results                                                | 118      |

| Figure 5.11 CST simulation results and 3-D structure for 18 GHz LP filter    | 119      |

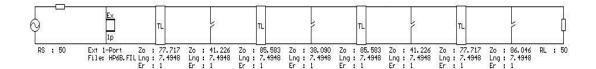

| Figure 5.12 2-18 GHz power divider                                           | 121      |

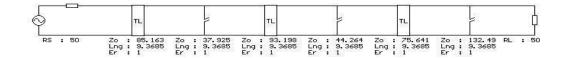

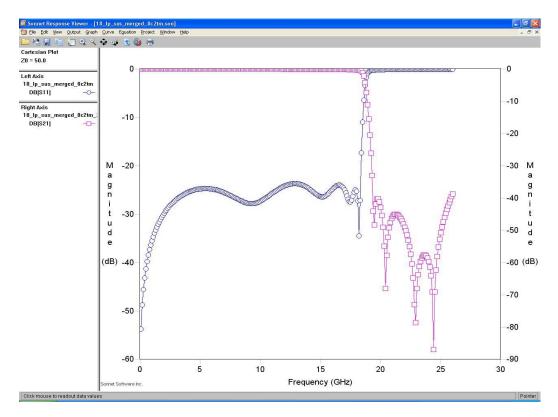

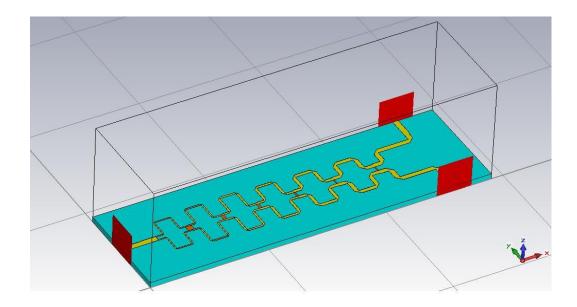

| Figure 5.13 Manifold for odd numbered channels                               | 122      |

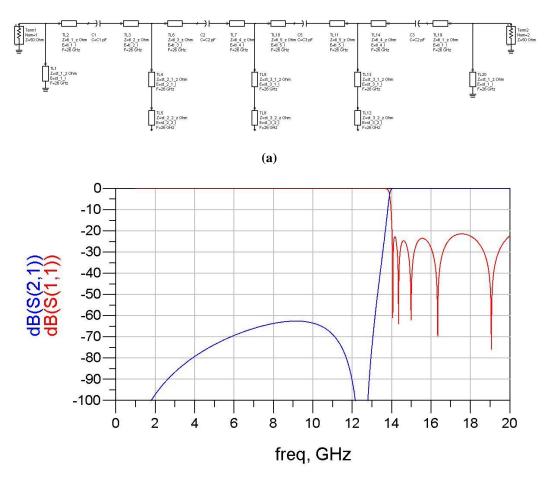

| Figure 5.14 ADS Simulation of the manifold for odd numbered channels         | 123      |

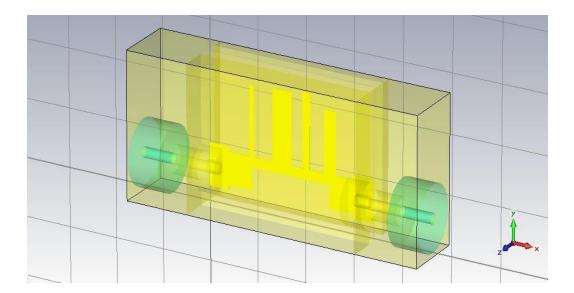

| · · · · · · · · · · · · · · · · · · ·                                        |          |

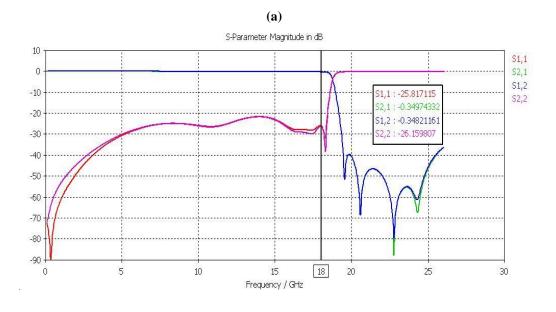

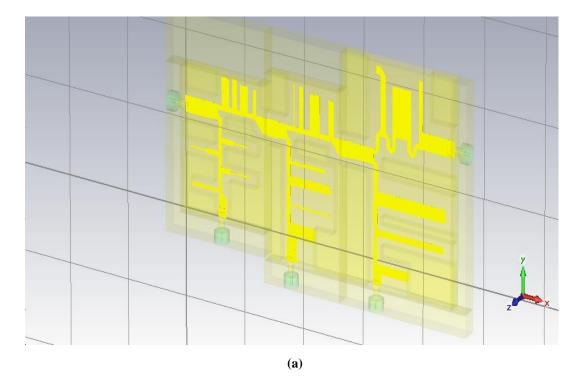

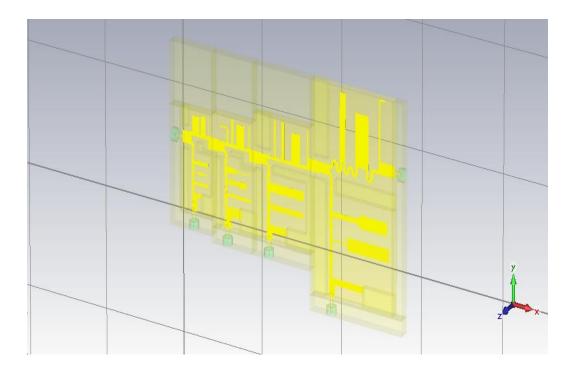

| Figure 5.15 Manifold for odd numbered channels : CST layout                | . 123 |

|----------------------------------------------------------------------------|-------|

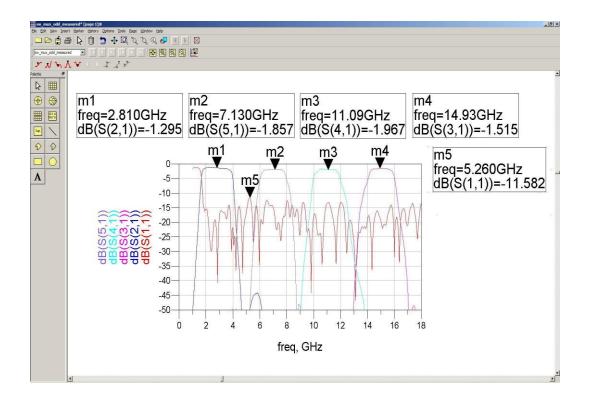

| Figure 5.16 Measurement results and layout for odd numbered channels       | . 124 |

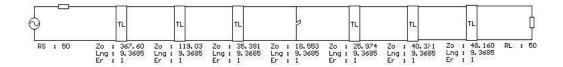

| Figure 5.17 Manifold for even numbered channels                            | . 127 |

| Figure 5.18 ADS Simulation of the manifold for even numbered channels      | . 127 |

| Figure 5.19 CST layout and results for even numbered channels manifold     | . 128 |

| Figure 5.20 Measurement results and mechanical layout for manifold for odd |       |

| numbered channels                                                          | . 130 |

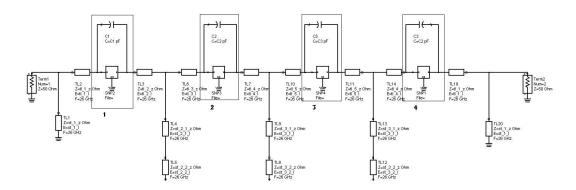

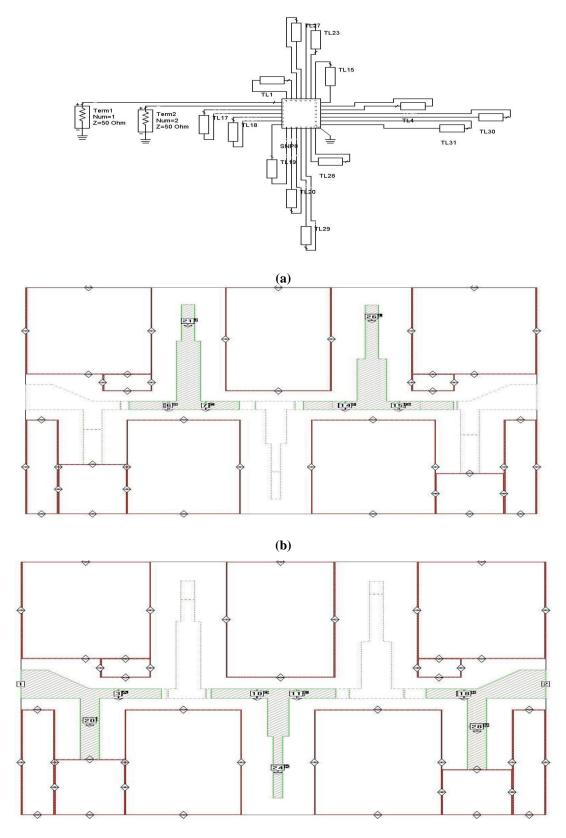

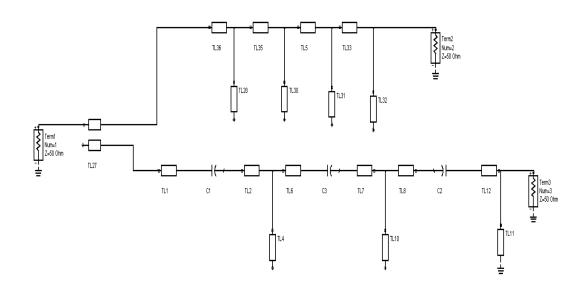

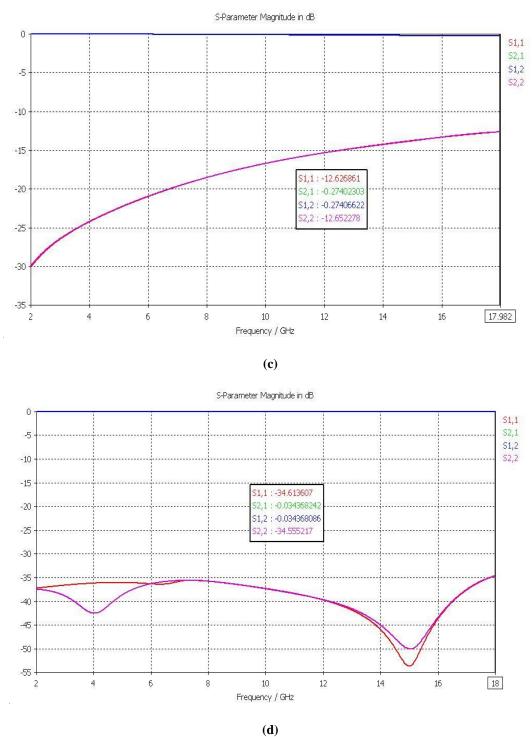

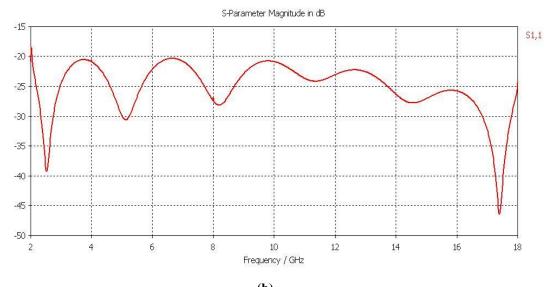

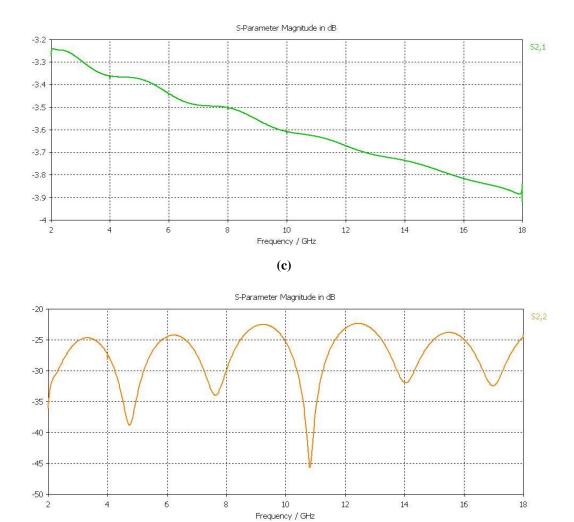

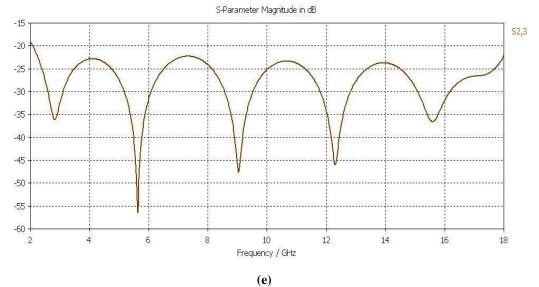

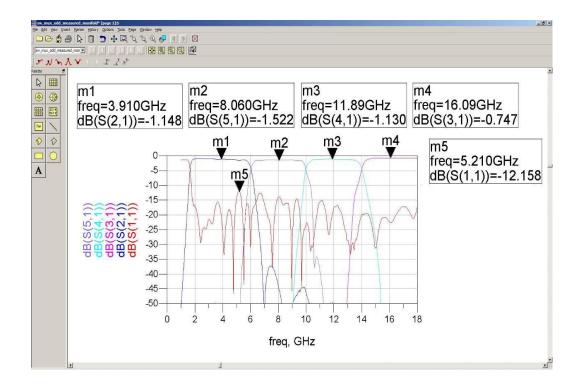

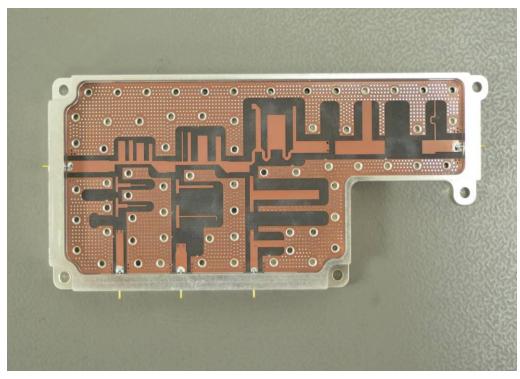

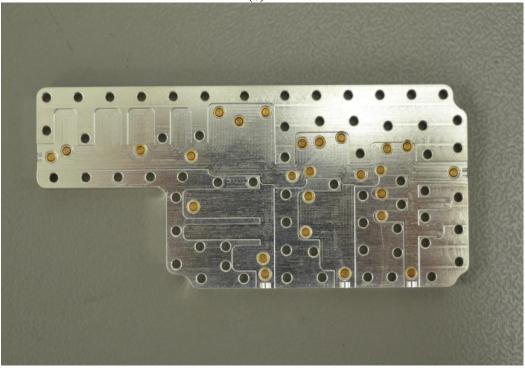

| Figure 5.21 Multiplexer containing odd numbered channels                   | . 131 |

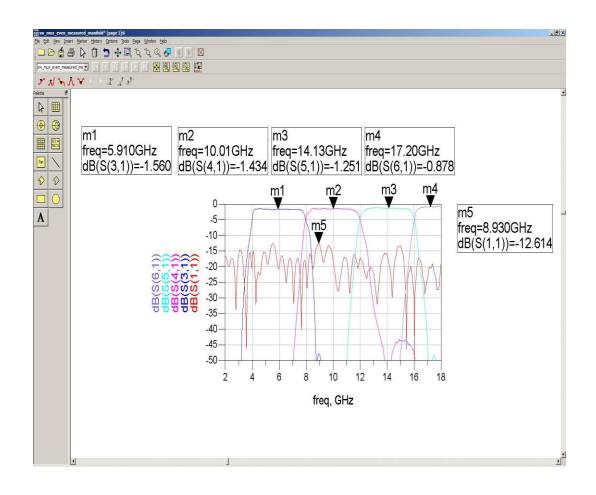

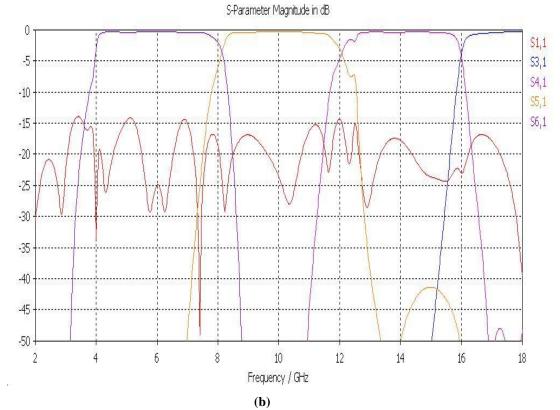

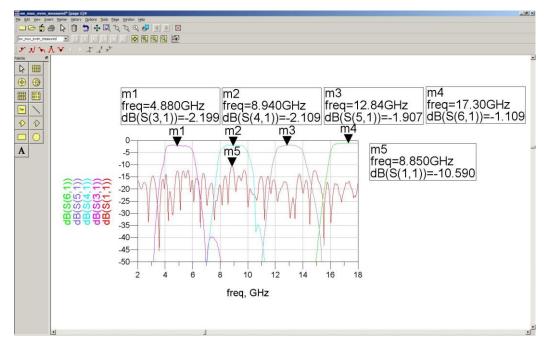

| Figure 5.22 ADS results for multiplexer containing odd numbered channels   | . 132 |

| Figure 5.23 Measurement results and layouts for multiplexer containing odd |       |

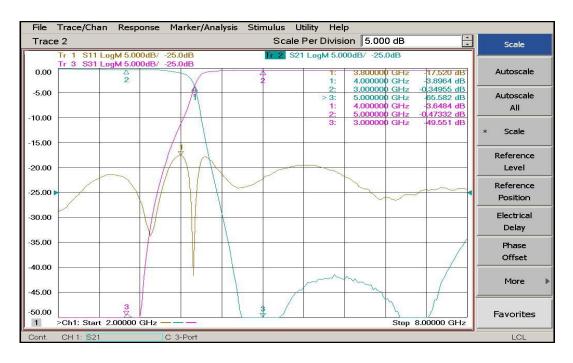

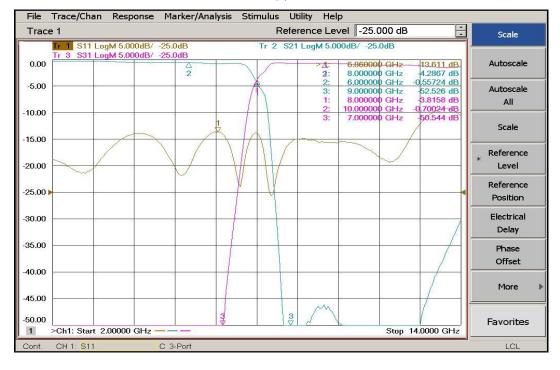

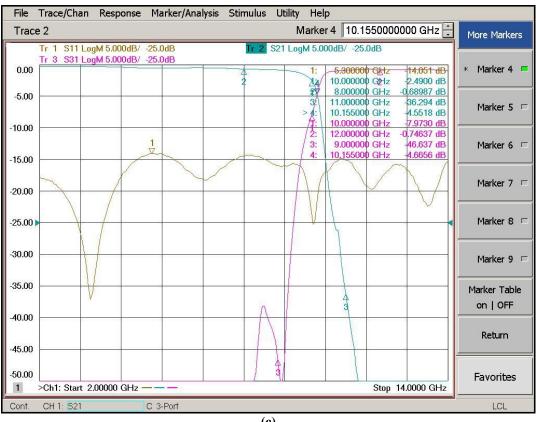

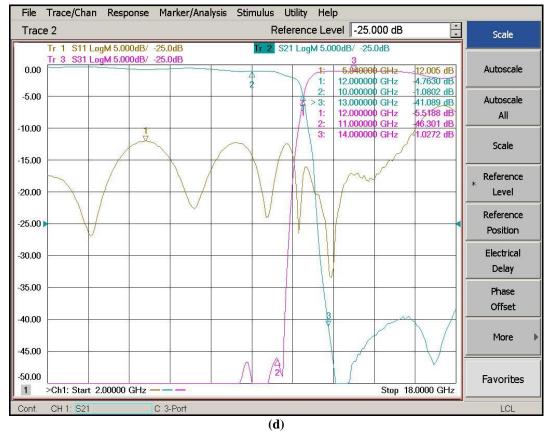

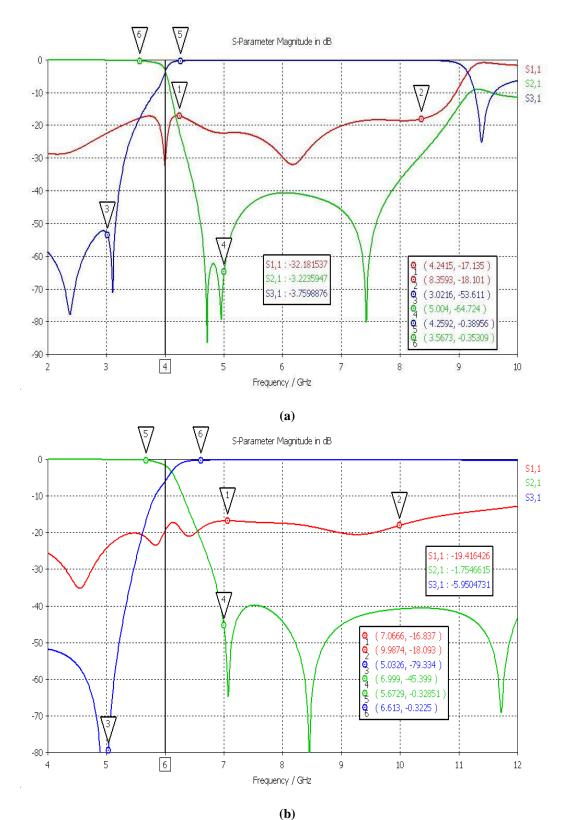

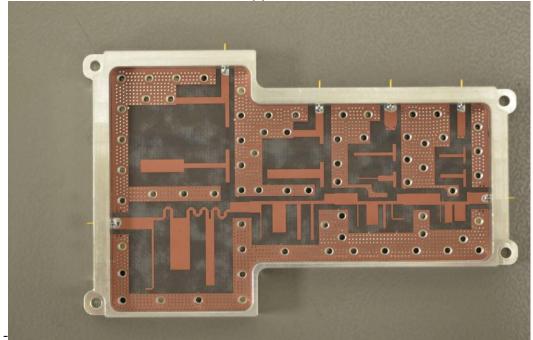

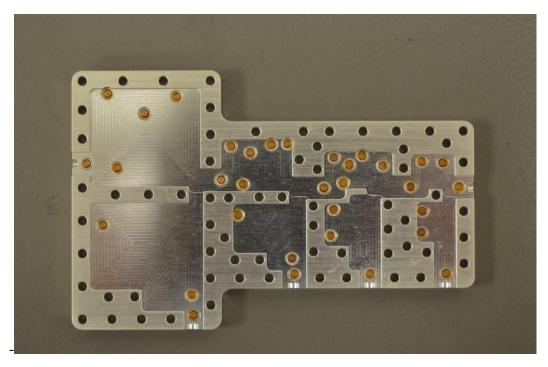

| numbered channels:                                                         | . 133 |

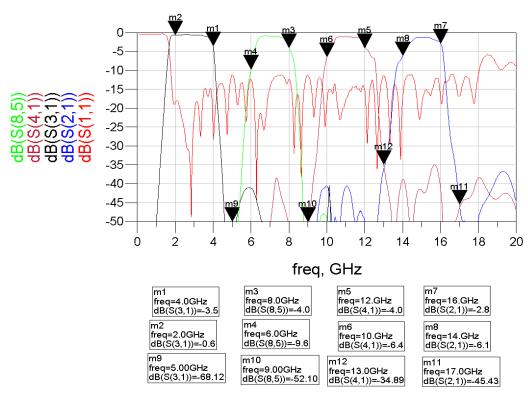

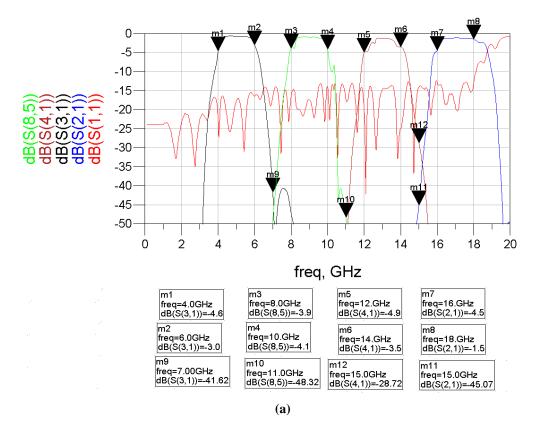

| Figure 5.24 Multiplexer containing even numbered channels                  | . 134 |

| Figure 5.25 ADS results for multiplexer containing even numbered channels  | . 135 |

| Figure 5.26 Measurement results and layout for multiplexer containing even |       |

| numbered channels                                                          | . 136 |

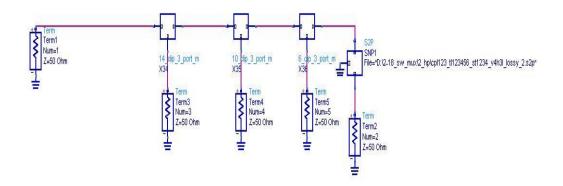

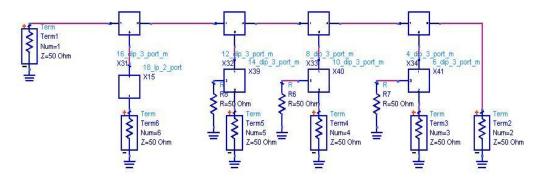

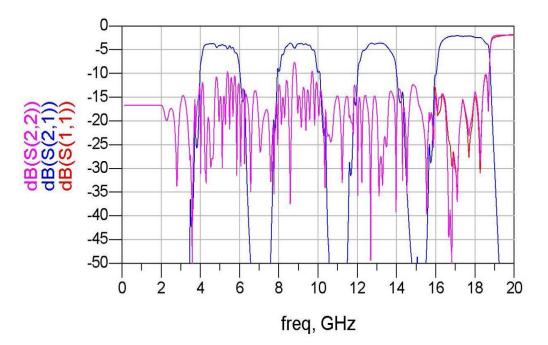

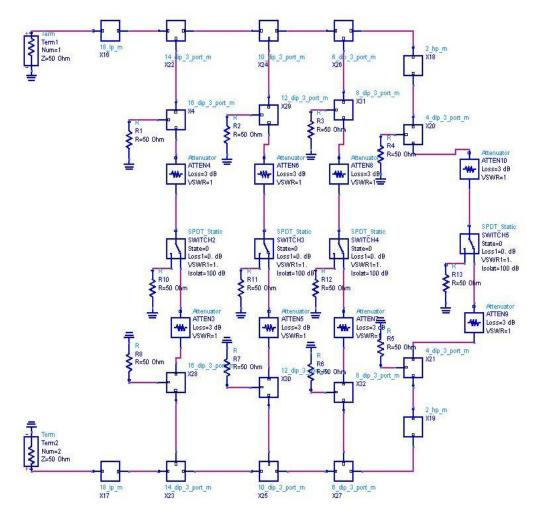

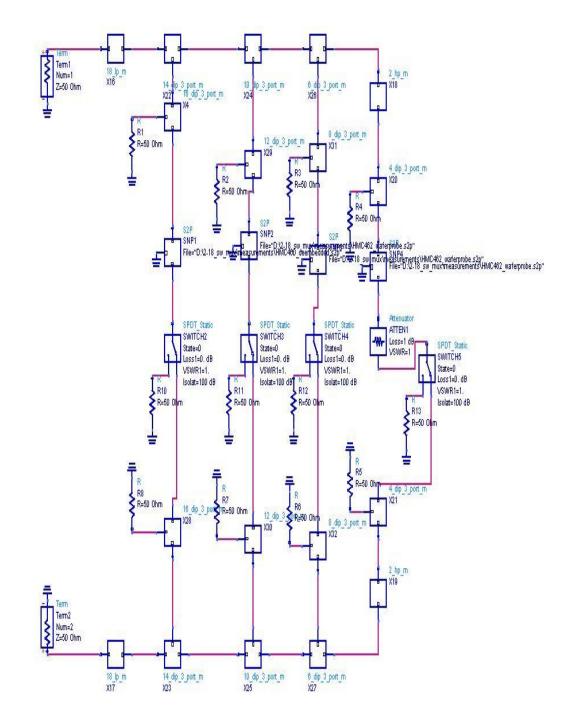

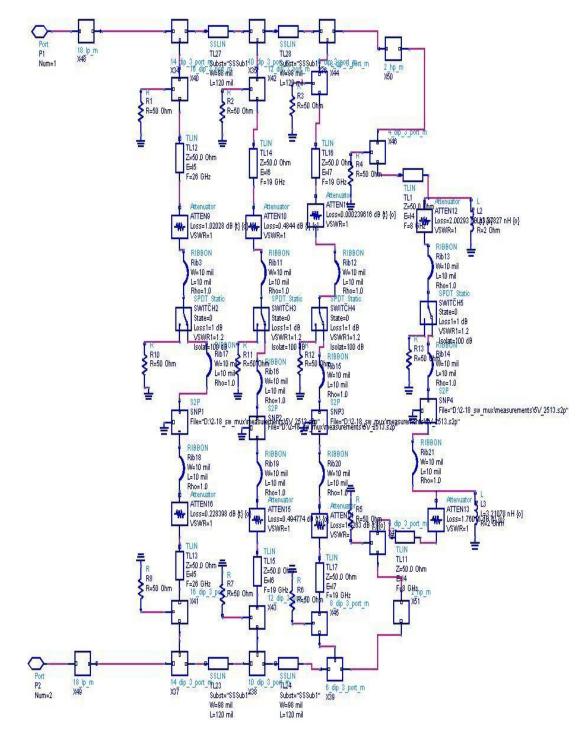

| Figure 5.27 Odd channel SW_MUX                                             | . 137 |

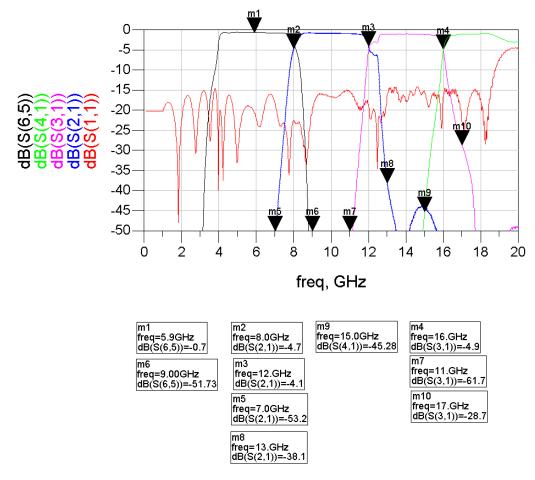

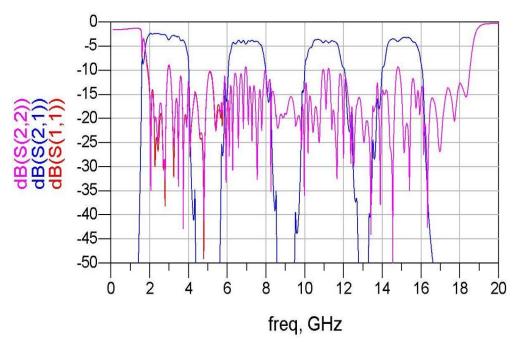

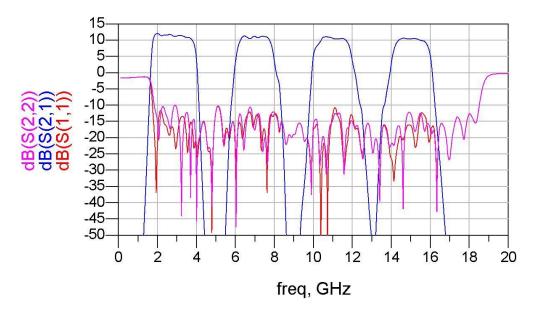

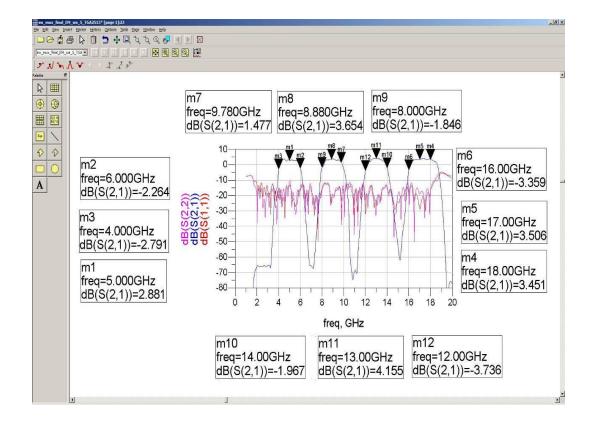

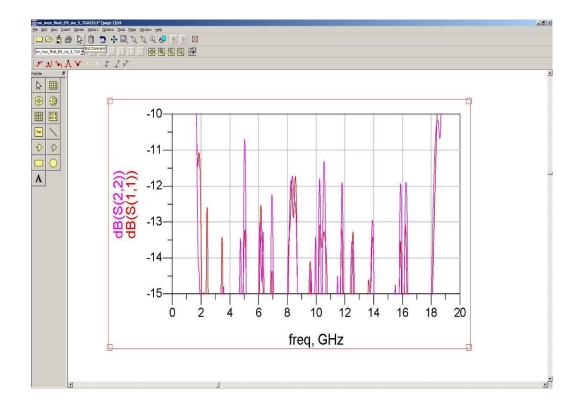

| Figure 5.28 Odd channel SW_MUX results                                     | . 138 |

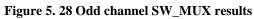

| Figure 5.29 Even channel SW_MUX results                                    | . 138 |

| Figure 5.30. Even channel SW_MUX                                           | . 139 |

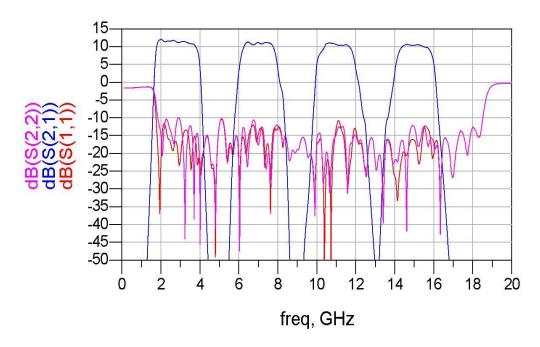

| Figure 5.31 Odd channel SW_MUX with attenuators                            | . 140 |

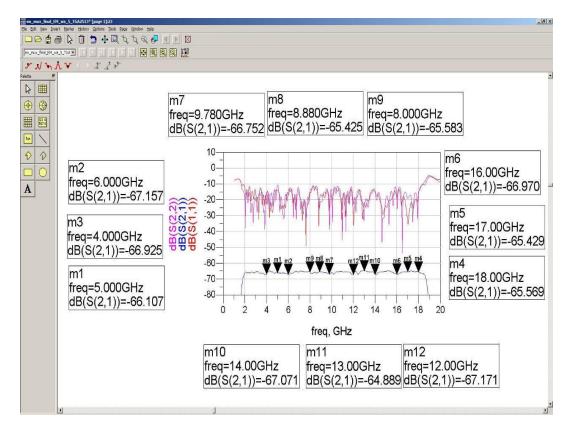

| Figure 5.32 Odd channel SW_MUX with attenuators: results                   | . 141 |

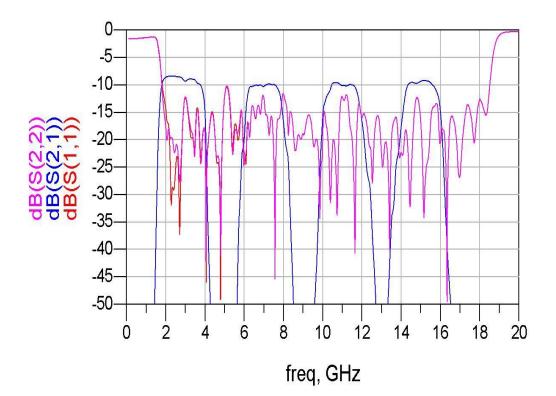

| Figure 5.33 Even channel SW_MUX with attenuators: results                  | . 141 |

| Figure 5.34 Even channel SW_MUX with attenuators                           | . 142 |

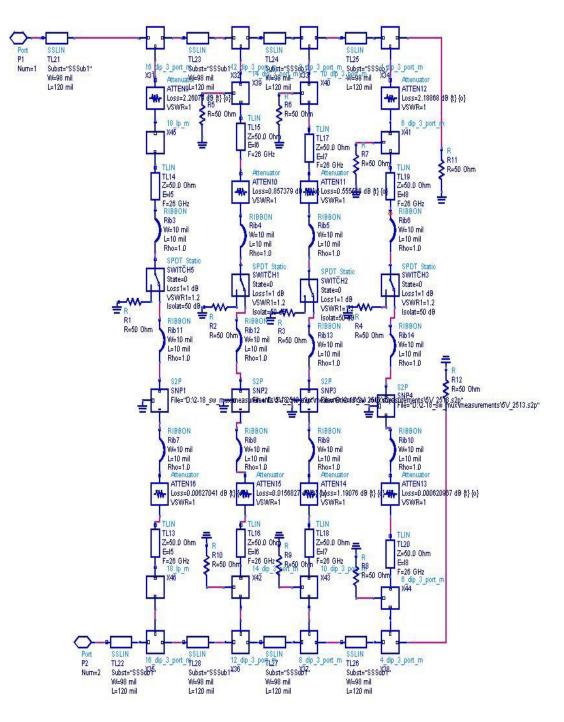

| Figure 5.35 Odd channel SW_MUX with amplifiers                             | . 143 |

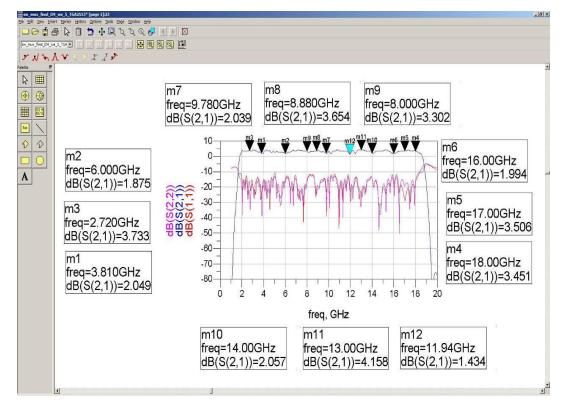

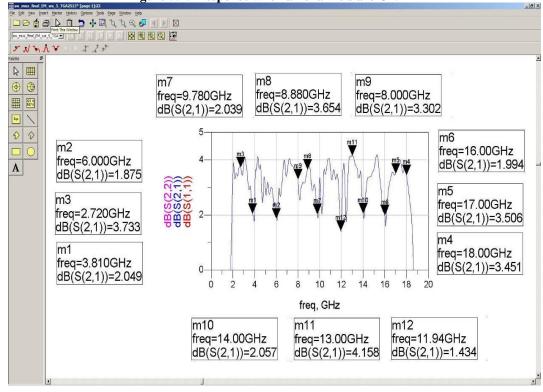

| Figure 5.36 Odd channel SW_MUX with amplifiers: results                    | . 144 |

| Figure 5.37 Even channel SW_MUX with amplifiers: results                   | . 144 |

| Figure 5.38 Even channel SW_MUX with amplifiers                            | . 145 |

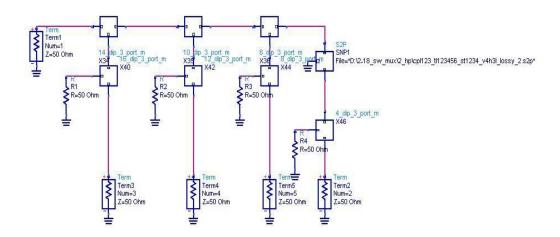

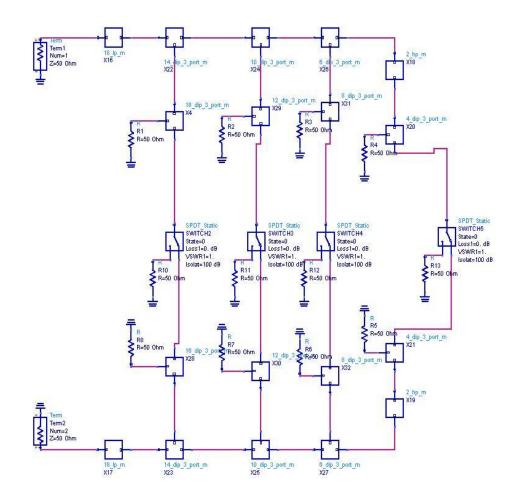

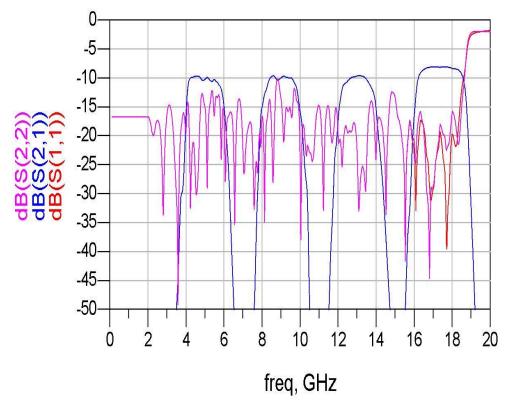

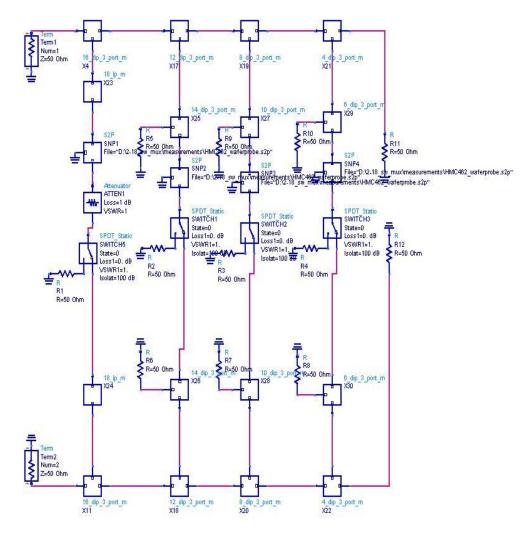

| Figure 5.39 Final SW_MUX structure                                         | . 147 |

| Figure 5.40 Final SW_MUX structure: odd half                               | . 148 |

| Figure 5.41 Final SW_MUX structure: even half                              | . 149 |

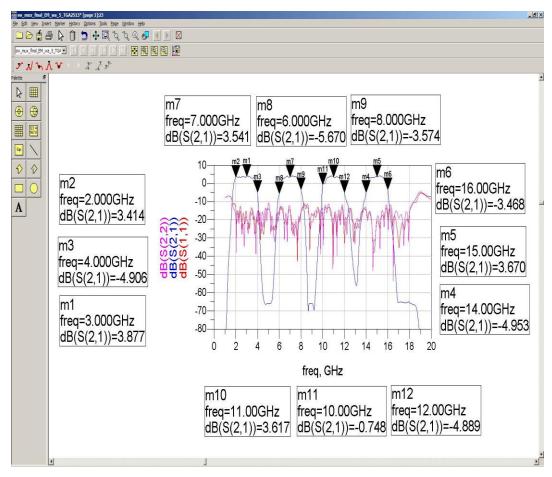

| Figure 5.42 Response when odd channels are ON, even channels are OFF       | . 150 |

| Figure 5.43 Response when odd channels are OFF, even channels are ON       | . 151 |

| Figure 5.44 Response when all channels are OFF                             | . 151 |

| Figure 5.45 Response when all channels are ON               | 152 |

|-------------------------------------------------------------|-----|

| Figure 5.46 Insertion Loss when all channels are ON: zoomed | 152 |

| Figure 5.47 Return Loss when all channels are ON: zoomed    | 153 |

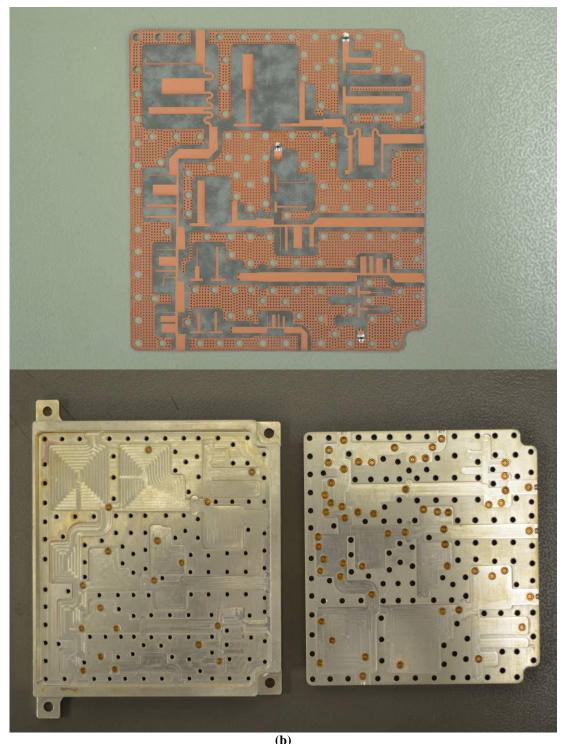

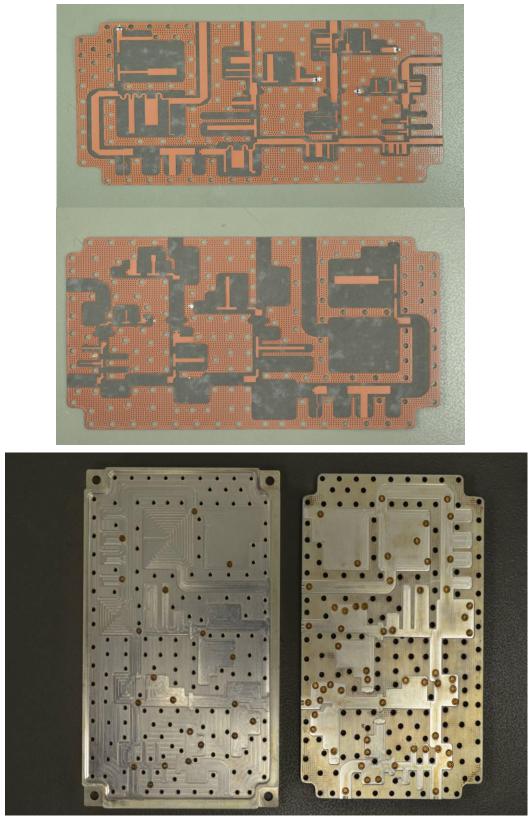

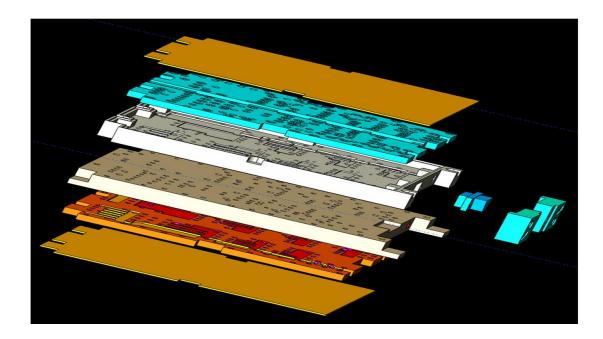

| Figure 5.48 Exploded view of the compact prototype module   | 153 |

# LIST OF ABBREVIATIONS

| ADS   | : Advanced Design System                  |

|-------|-------------------------------------------|

| ATC   | : American Technical Ceramics             |

| BPF   | : Bandpass Filter                         |

| CST   | : Computer Simulation Technology          |

| BW    | : Bandwidth                               |

| CPW   | : Coplanar Waveguide                      |

| DC    | : Direct Current                          |

| EW    | : Electronic Warfare                      |

| EM    | : Electromagnetic                         |

| HPF   | : Highpass Filter                         |

| IL    | : Insertion Loss                          |

| LPF   | : Lowpass Filter                          |

| MMIC  | : Monolithic Microwave Integrated Circuit |

| OCPCL | : Open Circuited Parallel Coupled Line    |

| PIN   | : Positive-Intrinsic-Negative             |

| PCB   | : Printed Circuit Board                   |

| PCL   | : Parallel Coupled Line                   |

| OCPCL | : Open Circuited Parallel Coupled Line    |

| RF    | : Radio Frequency                         |

| RL    | : Return Loss                             |

| SCPCL | : Short Circuited Parallel Coupled Lie    |

| SPDT  | : Single Pole Double Throw                |

| TL    | : Transmission Line                       |

| VSWR  | : Voltage Standing Wave Ratio             |

# **CHAPTER 1**

# **INTRODUCTION**

#### **1.1 Scope and Objective**

For electronic warfare systems operating in microwave frequency spectrum, whose signal density is very high and increasing day by day, cancellation of unwanted signals such as interference, jamming etc. and observing desired signals in a narrower bandwidth compatible with instantaneous bandwidth of the system, is a must. Constructing such components in a compact and easily realizable form is an essential issue in the electronic warfare industry. Multiplexers are essential components of wideband communication and electronic warfare systems. They are used for signal classification purposes by selecting the frequency band of interest from the microwave frequency spectrum and filtering out the rest of the frequencies.

Switched multiplexers are being used for a long time in modern sophisticated ECM (Electronic Counter Measure) and ESM (Electronic Support Measure) systems. The most typical application of switched multiplexer is its use preceding an IFM (Instantaneous Frequency Measurement) receiver, providing adaptive filtering in the RF section and reducing the incident spectrum in front of the IFM receiver. Switched multiplexers are therefore essential building blocks of adaptive wideband ESM receivers. They allow a rapid and intelligent modification of the system frequency characteristics to match the signal environment.

A switched multiplexer is a two port adaptive filtering network whose filtering characteristics may be electronically controlled to suit the operational environment. They split the input frequency band into a number of channels each of which may be independently switched into a bandpass or all stop state. For a device comprising 'n' channels, it is therefore possible to have '2<sup>n</sup>' switched states.

The main target of this thesis is design and implementation of an eight channel switched multiplexer operating between 2.0-18.0 GHz, with each channel having 2 GHz bandwidth. For this purpose a survey and critical review of the available techniques are made and a novel approach is developed that led to a topology which is simpler to implement with improved properties. It is shown that parallel coupled line (PCL) three ports can be used for synthesizing diplexers with good input return loss and improved isolation between channels compared to the commonly used Tjunction type diplexers. Improvements come from the fact that the parameters of three port PCL are forced to be parts of the channel filters, thus contributing to the responses of the channels while in the T-junction case the parameters of the junction are treated as response degrading factors. It is also shown that such diplexing three ports can be cascaded to form input and output manifolds for parallel or series connection of channel filters to form various types of multiplexers. By incorporating switches into the filters it is possible to form switched multiplexers. The approach enables design of contiguous wide or narrow channels, thus avoiding the necessity of formation of guard bands between channels for preventing channel interactions in different switch combinations.

#### 1.2 CAD Tools

The design stage involves the use of several synthesis, analysis, simulation and optimization tools both in circuit theory and in electromagnetic theory levels. The synthesis of the individual diplexers were carried out in FILPRO.

FILPRO is an integrated synthesis and analysis tool developed in Electrical Engineering Department of METU, mainly for the design of amplitude filtering circuits formed by passive, lumped or distributed elements in cascade topologies.

Analysis of whole switched multiplexer were done by linear tools of ADS ( Advanced Design System) form Agilent Company. This program was also used to determine the dimensions of lines, coupled lines which were essential to prepared the layout. Electromagnetic effects such as parasitics, inter resonator coupling were analyzed in SONNET, the electromagnetic analysis software. SONNET performed analysis of all planar structures such as filters, power divider and diplexers. It solved the current distribution on the metal using the method of moments. Three dimensional interconnects, such as coaxial to suspended transition and the final layout diplexers and manifolds in metal housing, were simulated in CST. CST is capable for using different frequency and time domain solvers.

#### **1.3 Organization Of the Thesis**

In chapter 2, serves a preface to basic multiplexer and switched multiplexer concepts. Basic multiplexer types are introduced, then some theoretical information about design of diplexers, which is a building block in multiplexers, are given. Key concepts such as contiguous or non-contiguous multiplexers, doubly or singly terminated filters are outline in this chapter. This chapter continues with various multiplexer and switched multiplexer topologies, then at then end of the chapter proposed architecture for 2-18 GHz switched multiplexer is stated.

In chapter 3, the coupled line models are examined in order to establish an understanding of how the novel diplexer design method works. In this method instead of directly paralleling the highpass and lowpass channels (it is called t-junction diplexing throughout the thesis), the use of open circuited parallel coupled line is emphasized. For clarity examples are given in this chapter to show the superiority of open circuited parallel coupled line as a diplexing element over t-junction.

In chapter 4, diplexers with open circuited parallel coupled lines to be used in switch multiplexer are designed and realized. The realized diplexers offer a good performance exceeding the simulation results.

In chapter 5, the proposed switch multiplexer is designed step by step beginning from forming to manifolds to forming the final 2-18 GHz, 8 evenly spaced channel, switched multiplexer. the simulation results are based on the actual measurements/3-

D simulation results of each active or passive component and they seem to be promising for the realization of the final 2-18 GHz switched multiplexer.

In chapter 6 conclusions and possible future studies are presented.

# **CHAPTER 2**

# A SURVEY ON SWITCHED MULTIPLEXERS

### 2.1 General Information

The design stage involves the use of several synthesis, analysis, simulation and optimization tools both in circuit theory and in electromagnetic theory levels.

In order to be able to design a switched multiplexer, one should first be able to design a multiplexer, because a switched multiplexer is always a combination of two or more multiplexers in various ways. Multiplexers may be combined in several ways to form switched multiplexers, like connecting two identical multiplexers back to back, connecting an input multiplexer to a frequency shifted output multiplexer using power splitters and combiners etc. There are many problematic points in the design of multiplexers. Some of the critical ones can be summarized as follows:

- Destructive interaction of adjacent and nonadjacent channels leading to degradation in input return loss and isolation between channels.

- Problems in the interconnection of channel filters to input and output manifolds leading to degradation of input return loss and channel filter characteristics.

- Extreme element values in narrow and wide channels in different frequency ranges.

Such problems get more severe in wideband coverage and in the case of closely spaced channels. It is shown that PCL three port approach helps to ease most of such problems.

In the next section basic multiplexer types will be summarized.

## 2.2 Basic Multiplexer Types

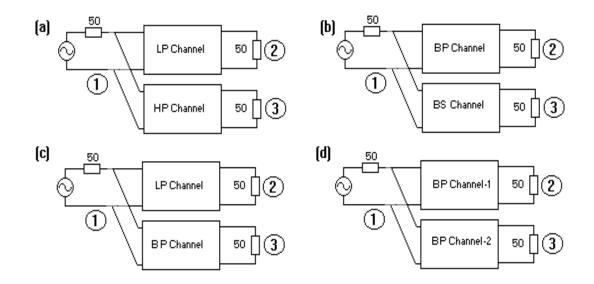

Multiplexers are used to divide frequency band into sub-frequency bands by integrating a number of specially designed channel filters in special ways. A diplexer is a two channel multiplexer, a triplexer is a three channel multiplexer and so on. In Figure 2.1 some typical parallel connected diplexers are shown while in Figure 2.2 typical parallel connected multiplexer structures are shown. The duals of these circuits are named as series connected multiplexers.

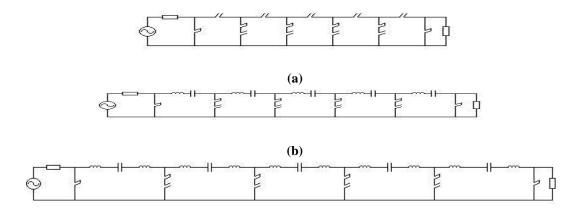

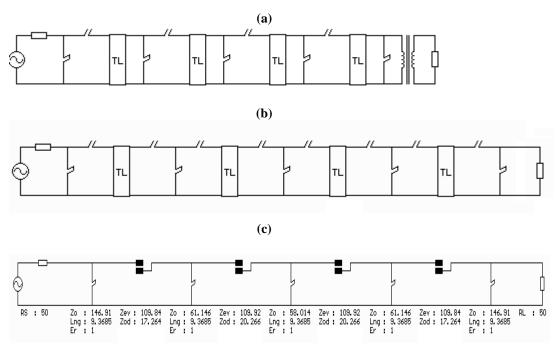

Figure 2.1 Some Parallel Connected Diplexers (a) Lowpass-Highpass Diplexer, (b) Bandpass-Bandstop Diplexer, (c) Lowpass-Bandpass Diplexer and (d) Bandpass-Bandpass Diplexer

Figure 2.2 Typical Parallel Connected Multiplexer Structures (a) Parallel Bandpass Filter Multiplexer, (b) Ladder Type Lowpass-Highpass Multiplexer, (c) Bandpass-Bandstop and Lowpass Multiplexer, (d) Tree Type Multiplexer using Lowpass-Highpass Diplexers and (e) Manifold Type Multiplexer

The topology to be used depends largely on the technology of implementation, number of channels, channel bandwidths, separation (guard bands) between channels, the overall bandwidth to be covered (channelized) by the multiplexer, input return loss and channel isolation requirements, etc. The topology in Figure 2.2.a. is suitable for narrow band multiplexers, commonly used in waveguide type multiplexers with common resonators. However it is severely limited by the number of channels. It is almost impossible to design even planar triplexers using this topology in Figure 2.2.e is used. The topologies of Figure 2.2.c and d are also suitable for narrow medium bandwidth filters. For multiplexers with wide channel bandwidths and wide frequency coverage, the LP-HP ladder type topology shown in Figure 2.2.b is used, as is done in this thesis also.

In applications where a wide frequency band should be covered without any gap between channels, the adjacent channels should be contiguous, that is, they should cross-over at 3 dB. In the usual communication applications, channels should be separated by some guard bands with a specified minimum cross-over loss. Such multiplexers are termed as noncontiguous. In some applications two adjacent channels may overlap. The signals with frequencies in the overlap region are divided equally into the two channels.

Since a multiplexer is a lossless multiport network, all the power available from the source at the input (Port-1) is supposed to be delivered to only one of the output ports depending on frequency, without any reflection. That is, input impedance of a multiplexer must be matched to the source at all frequencies within the passbands of all channels.

The theory for **exact synthesis** of multiplexers is still unresolved [21], [35]. **Exact synthesis** techniques exist only for some simple **lowpass-highpass diplexers** [31], [32], [37], [41], [42]. A survey of literature shows that the design techniques of multiplexers are independent of **exact filter synthesis** techniques. Most of the successful design techniques depend on modifications of independently synthesized channel filters brought together in the topologies shown in Figures 2.1 or 2.2 to work

as multiplexers. As complexity of multiplexing structures increase, circuit theory alone can't cope with design challenges. Circuit theory should work together with electromagnetic field theory [33], [36], supported by powerful optimization techniques [27], [28].

The theory of multiplexers employing **singly terminated filters** [1]-[8] are based on the theory of **complementary pair** of filters. A parallel filter pair with non overlapping passbands must have input admittances  $Y_1$  and  $Y_2$  such that  $Y_1+Y_2=1$  in the passbands of the channels. Similarly, a series connected filter pair input impedances must satisfy the relation  $Z_1+Z_2=1$  in the passbands of the channels. That is, the reactive parts of channel input impedances are of opposite sign so they cancel to yield resistive input impedance matched to the source resistance over both channels. Cancellation is exact at the cross-over frequency for maximally flat channel filters [1]-[6] therefore they take the name **complementary pairs**. For Chebyshev or elliptic channel filters, this effect is still observed but it is approximate, hence they take the name **pseudo-complementary** pairs.

In general the desired channel filters can also be synthesized independently as singly terminated or doubly terminated filters and then combined to form of LP-HP, LP-BP-HP or BP-BP, BP-BS, etc type diplexers and multiplexers, followed by modifications and tuning-optimization to get the targeted response. These filters can also be designed either by first forming a LP prototype and then mapping into LP, HP, BP or BS form or the channel filters can be synthesized directly as LP, HP, BP or BS filters.

In this thesis the software Filpro is used to design both doubly terminated and singly terminated channel filters and LP-HP diplexers. Multiplexer designs are tested by using both singly terminated and doubly terminated channel filters to get some insight on the properties of the selected topologies. It is seen that both approaches have some advantages and disadvantages depending on constraints of the application. However singly terminated designs may contain physically unrealizable element values which needs optimization to get realizable values. Doubly terminated channel filters are easier to design and usually does not to contain unrealizable element values, but the first element must be deleted and the whole circuit must be optimized. In designing LP-HP diplexers, first singly terminated designs are tested to get an idea if the requirements can be met quickly or not because, the two channel filters of a LP-HP diplexer are synthesized in exact manner simultaneously.Then, in the succeeding stages in forming the multiplexer, further information can be generated about the problematic parts of the whole circuit and the designs can be repeated using either singly or doubly terminated approaches.

Usually singly terminated adjacent channel filters form better complements. When doubly terminated filters are used as channel filters their first element on the diplexing inputs are deleted (foreshortening) because if they are used without foreshortening they load each other heavily leading to gross degradation in response. One disadvantage of doubly terminated designs is that foreshortening may lead to degree reduction compared to singly terminated designs to satisfy the same requirements. Theoretically design of the multiplexer as a whole should be possible because, if properly designed, the transfer characteristics of each channel may get contributions of other channels to increase their skirt slopes. That is, if there are M channels and if all channel filters are of degree N, then the transfer function of each path from the input of multiplexer to the output of any channel will have a degree of MxN. This fact may be exploited for improving responses of channels. However exact analytical handling and synthesis of such circuits is a difficult task. Therefore usually special approximate design procedures for special structures a number of solutions. Therefore optimization trials starting with singly or doubly terminated designs may converge to different circuits. However once a topology is selected, after getting insight, experiments indicated that both approaches converge to the same circuit if optimization is made in a controlled and guided manner sa defined in [51].

All these comments are also applicable to all-stub commensurate length distributed element filters. For distributed element filters involving contributing Unit Elements we have the following extra property: A commensurate line highpass filter with N contributing unit elements and M transmission zeros at f=0 has exact lowpass

complements with N+M transmission zeros at  $f=\infty$ . Similarly, a lowpass filter with N contributing unit elements and M transmission zeros at  $f=\infty$  have highpass complements with N+M transmission zeros at f=0 [5], [6].

In general, the synthesized filters may need conversion into the targeted realizable forms by inserting redundant unit elements and using Kuroda transformations. Redundant unit element can be inserted only from to the load side because insertion of any element on source side will degrade the complementary nature of the channel filters. If realizable element values can be obtained, a better way may be direct synthesis of channel filters with contributing unit elements. Both approaches may have difficulties in realization but usually direct synthesis with contributing unit elements give quicker results.

The realization problems due to extreme element values or due to resulting topology can be solved by using circuit transformations. In general all multiplexers require some professional optimization. However, many useful multiplexers can be designed through manual optimization. In fact, especially in multiplexers with high number of channels, direct application of general optimization techniques is usually not practical or feasible. It is the common experience that manual optimization while observing the response is a better way at the initial stages of design, giving hints on the directions to move and on the relative effects of various parameters on response and on possible solution patterns. When the targeted response is approached then automatic optimization tools can be used for fine adjustment of the response and trimming the element values.

Since a very wide frequency coverage with wide channel bandwidths is targeted, in this thesis, ladder type LP-HP type multiplexer topology is selected for the switched multiplexer. In the next section some possible alternative structures and their problematic points are discussed, ending in the final topology to be implemented as the target of this thesis.

## 2.3 Simple Ladder Type HP-LP Switched Multiplexers (SW\_MUX)

A simple switched multiplexer can be formed by connecting two HP-LP ladder multiplexers back to back style as shown in Figure 2.3. Note that the designed multiplexer is used both in the input and output stage so all diplexers are used twice. Since the diplexers used are of LP-HP type, they are contiguous. That is the loss at each cross-over frequency is 3 dB. When they are connected back to back the cross-over losses will be 6 dB. When all channels in SW\_MUX are combined, there will be notches of magnitude 3 dB at cross-over frequencies. This is the main disadvantage of contiguous switched multiplexers. This problem can be resolved only if the channels are made noncontiguous, as will be described in some other switched multiplexer types.

Figure 2. 3 A Simple SW\_MUX Based on LP-HP Diplexers

# 2.4 Ladder Type HP-LP Switched Multiplexers with Power Dividers

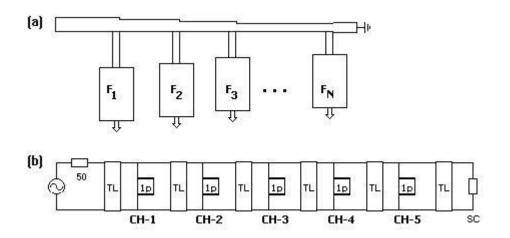

Another way to implement the same switched multiplexer can the through the use of power dividers repeatedly connecting the output of the diplexers until a single output is reached. This topology is shown in Figure 2.4. It is seen that there is an extra 6 dB cross-over loss if SW\_MUX has 4 channels, 9 dB loss if SW\_MUX has 8 channel. That is the loss will increase by 3 dB, each time the number of channels is doubled.

This loss can be limited to 6 dB for any number of channels by the SW\_MUX topology shown in Figure 2.5 described in [49]. In this topology SW\_MUX consists of an input multiplexer and an output multiplexer. Both multiplexers are 4 channel multiplexers, each channel having 4 GHz bandwidth. The output multiplexer is a 2 GHz shifted version of the input multiplexer, so when these two multiplexers are connected using a power divider/switch network as shown in Figure 2.5, an eight channel SW\_MUX with each channel having 2 GHz bandwidth is obtained.

Figure 2. 4 A Switchable LP-HP Multiplexer Using Power Dividers

Figure 2. 5 An 8 Channel 2-18GHz SW\_MUX

Although it is theoretically correct to use singly terminated filters in the design, doubly terminated filters with finite transmission zeros and contributing unit elements, providing highly selective channels can also be used in the construction of HP-LP ladder type multiplexers.

#### 2.5 Manifold Type Stripline Multiplexers With Tee-Junctions

When the number of channels to be paralleled increases physically it may become difficult to connect them at a single junction. In stripline-like structures channels can be placed along a manifold as shown in Figure 2.6.a. In this structure the channel filters are interconnected through Tee-junctions. The channels are thus separated physically by some length of lines (or waveguides, or phase shifters as in Figure 2.2.e) which may also function as parts of immitance compensation elements to reduce interaction between channels. In Figure 2.6.b the channel filters are shown as shunt connected External One-Port elements for simulation on the software Filpro

which is used for synthesis, design and optimization of the channel filters and the whole multiplexer.

Figure 2. 6 A Manifold (Extended Junction) Stripline Multiplexer

It is important to realize that direct connection of the channel filters into the manifold transmission line (forming T-type junctions) may cause serious degradations in multiplexer performance, because each channel filter will load the manifold, thus the other channel filters. The level of degradation increases as the number of channel filters increase, so some alterations should be made in channel filters before integration. One approach to solve this problem is developed by Mobbs [4], known as hybrid coupled manifold multiplexer.

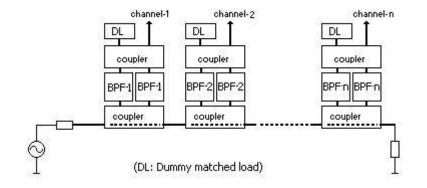

#### 2.6 Hybrid Coupled Manifold Multiplexer

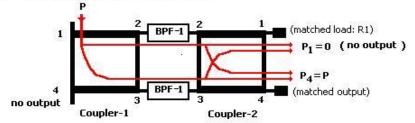

When number of channels is large, channel filters involving directional couplers (3 dB hybrids) are advantageous to use when integration into a multiplexer is considered [4]. A hybrid coupled manifold multiplexer is shown in Figure 2.7. Each channel is made up of two 3 dB hybrids and two identical filters. Coupler-filter-coupler combinations extract the signals within their passbands from the manifold and direct them to one output port of the second coupler forming one channel of the multiplexer. Modularity of multiplexer is clear. New channels may be added or some channels can be switched off without effecting the other channels, if all channel if all

channel bandwidths are within the 3 dB coupling and isolation bandwidths of the couplers.

Figure 2. 7 Hybrid Coupled Manifold Multiplexer

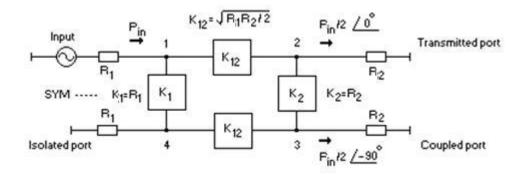

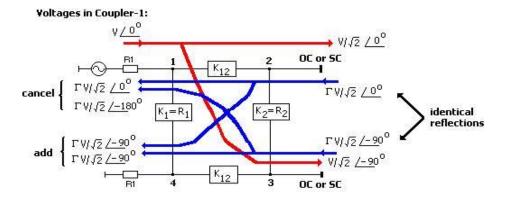

In order to clarify operation of the channels, the basics of directional couplers on a 3 dB branchline directional coupler with two branches should be reviewed. The number of branches may be increased depending on bandwidth requirements and other constraints or one may use other types of directional couplers, like TEM mode parallel coupled line couplers or lumped element couplers .

# 2.2.1 3 dB Impedance Transforming Branchline Couplers With Ideal Inverters

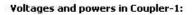

A schematic drawing of a symmetric, impedance transforming two branch coupler is shown in Figure 2.8. The convention for port numbering and signals of these ports when input is applied to port-1 is as follows:

Port-1: Input signal port with termination resistance R<sub>1</sub>.

Port-2: Transmitted signal port with termination resistance R<sub>2</sub>.

Port-3: Coupled signal port with termination resistance R<sub>2</sub>.

Port-4: Isolated port with termination resistance R<sub>1</sub>.

Figure 2. 8 Schematics of a 3 dB Impedance Transforming Branchline Coupler with Different Input-Output Terminations

If the phase of transmitted port signal (Port-2) is taken as reference (0 degree), then the phase of coupled port signal is -90 degrees (Port-3). The arms are formed by ideal inverters. In order that this device work as a 3 dB coupler, the inverter impedances should satisfy the following relations:

Branch -1 inverter impedance:  $K_1 = R_1$

Branch -2 inverter impedance:  $K_2 = R_2$

Main arm inverter impedances:  $K_{12} = (R_1 * R_2/2)^{1/2}$

- In multiplexer applications the filters will appear as loads  $R_2$  at port-2 and port-3 of the first coupler as shown in Figure 2.9.

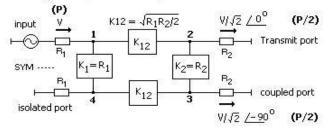

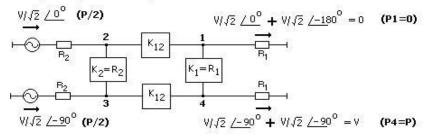

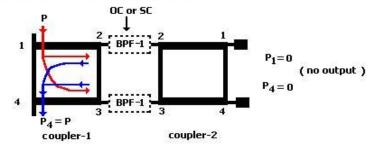

- If the incoming signal frequency is within the passband of a channel then this signal will be extracted from the main arm and split into two parts and directed to port-2 and port-3 of the first coupler with equal amplitudes and 90 degree phase difference as shown in Figure 2.9 (a). Then they will pass through the filters (BPF-1 in the first channel) connected at these ports and will be applied to port-2 and port-3 of the second coupler which is just reversed version of coupler-1. The signals applied to port-2 and port-3 of the second coupler which is difference leading to cancellation of the signals at port-1 and addition at port-1. Thus, the whole signal will appear at port-4 of the second coupler. Details of the signal flows are shown in the same figure.

- The signals with frequencies outside the passband of BPF-1 will see identical reactive mismatches at ports 2 and 3 of coupler-1 (identical input impedances of the two filters). It is preferable to have these mismatches simulating OC or SC. The reflections from these terminations (blue lines in the figure) will cancel at port-1 and add at port-4 of coupler-1. Thus they will be directed to the next hybrid channel as described in Figure 2.9.b.

- If the transmitted and coupled port terminations (input impedances of the two filters connected to Ports 2 and 3 of coupler-1) are different from the specified matched termination R<sub>2</sub>, then reflections will occur from these ports even in the passband of BPF-1. If reflections are identical, then they will be directed to the isolated port (Port-4 of coupler-1). No reflections will appear at input port, thus showing a good match at input, at the expense of some degradations in the adjacent channels.

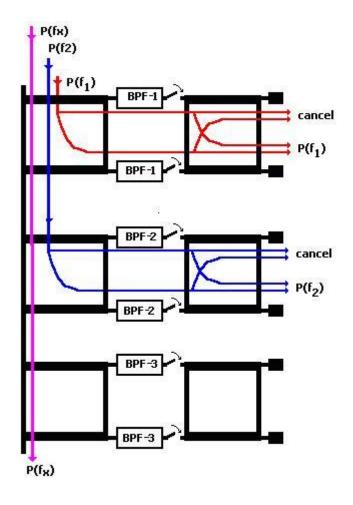

- Figure 2.10 shows signal flow in a hybrid manifold multiplexer where we have also incorporated switches in series with filters for a possible switched channel multiplexer. The signals at frequencies  $f_1$  and  $f_2$  are directed to channel-1 and channel-2 outputs while the signal with frequency  $f_x$  which is assumed to be outside the passbands of the channels flows over the main line towards a dummy matched termination.

(a) For signals inside the passband of BPF1:

Voltages and powers in Coupler-2:

(b) For signals outside the passband of BPF1:

Figure 2. 9 Power Flow in One Channel of Hybrid Manifold Multiplexer

• Realization of inverters of the branch line couplers forms the main barrier for wideband applications. Also interactions between channels may be heavy, degrading responses of the channels. Therefore in practice the use of branch line couplers may have limited applications. Switchable multiplexers for wider bandwidth applications can be formed using different manifolds as will be described in the next section.

Figure 2. 10 A Switchable Hybrid Multiplexer

# 2.7 Circulator Coupled Multiplexers

There are other ways to connect the filters to the manifold to form a multiplexer. As an example circulators may be used to achieve better isolation between channels. In this approach [50], there would be no need to use singly terminated or foreshortened doubly terminated filters, therefore exact filter synthesis can be used as shown in the Figure 2.11.

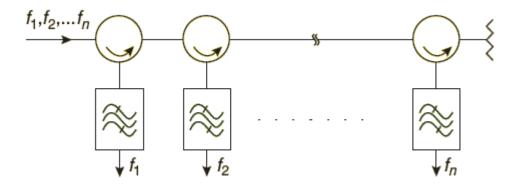

Figure 2. 11 A Circulator Coupled Multiplexer

Each channel in this case consists of a channel-dropping circulator and one filter, as shown in Figure 2.11. The unidirectional property of the circulator provides the same advantages as the hybrid-coupled approach in terms of amenability to modular integration and ease of design and assembly. The insertion loss of the first channel is the sum of the insertion loss of the channel filter and the insertion loss of the circulator. The subsequent channels exhibit a relatively higher loss due to the insertion loss incurred during each trip through the channel-dropping circulators. This is the most common realization for input multiplexers in satellite communications. The problem here is that circulators cost much and they are usually narrow bandwidth structures.

# 2.8 Multiplexers Using Directional Filters

The circulators described in the previous section may be eliminated by using directional filter structures [50] as shown in Figure 2.12.

Figure 2. 12 A Directional Filter Multiplexer

Figure 2.12 illustrates a layout of a multiplexer realized by connecting directional filters in series. A directional filter is a four-port device in which one port is terminated in a load. The other three ports of the directional filter essentially act as a circulator connected to a bandpass filter. Power incident at one port emerges at the second port with a bandpass frequency response while the reflected power from the filter emerges at the third port. Directional filters, however, do not require the use of ferrite circulators. This multiplexing approach has the same advantages as the hybrid-coupled and circulator-coupled approaches. It is, however, limited to narrow-band applications.

# **2.9 Parallel Coupled Line Type Manifolds**

In this thesis a novel approach is developed which uses parallel coupled line (PCL) three ports as diplexing elements of manifolds. In the approaches using T-junction type and hybrid coupled type manifolds the junction elements create problems and limitations. In this new approach the parameters of the diplexing PCL three ports are integral parts of the channel filters. Therefore, contrary to the cases of T-junction and hybrid junction, parameters of the PCL three ports will contribute to the responses of channel filters. Thus, besides avoiding the problems and limitations of T-junction hybrid junction manifolds, the junction parameters will help to improve the performance of the multiplexer.

Parallel coupled line three ports are formed.by leaving one of the coupled port of a PCL open circuit or short circuit. In the equivalent circuit of the PCL three ports

there are elements which can be treated as parts of the channel filters. Two types of manifolds can be formed: Series multiplexing manifold and parallel multiplexing manifold, as described below.

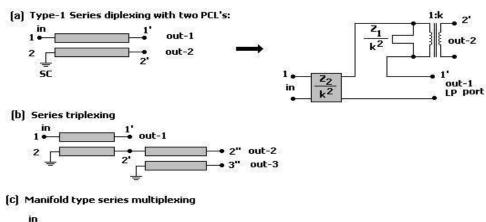

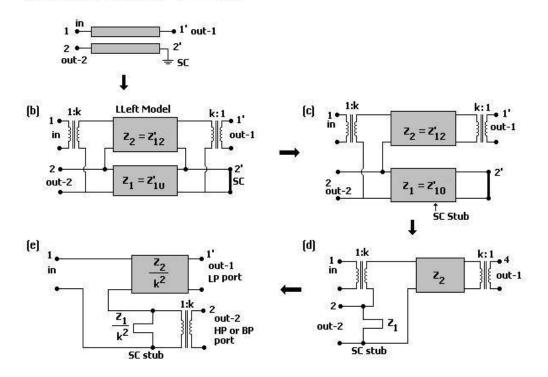

#### 2.9.1.Series Multiplexing Manifold

The series diplexing three port and its equivalent circuit formed by commensurate line and stubs are shown in Figure 2.13 (a). Inspection of the equivalent circuit shows that the filters connected to the ports out-1 and out-2 will be in series. In order that this circuit work as a diplexer the filter connected to one of these ports must show SC input impedance within the passband of the other filter so that the whole input signal will be directed to only one of the two ports.

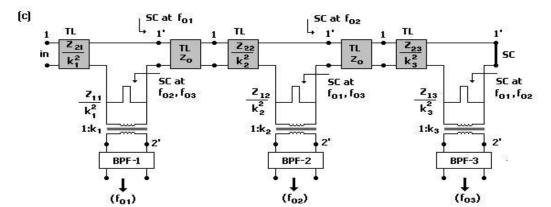

Figure 2.13 (b) shows a possible multiplexing structure (a triplexer). The channel filters are connected to port-2' of the diplexing PCL's. The diplexer sections with appropriate channel filters are cascaded to form multiplexer. The cascaded diplexing sections are separated by transmission line pieces which can be used to make the input impedance seen at port-1' zero at the passband center of the relevant diplexing PCL section on its left. Thus, for example if the frequency of the incoming signal is fo1 (passband center of BPF-1), then it will be directed to port-2' (BPF-1) because the impedance at port-1' is SC at that frequency. Since the circuits at port-1' and port-2' are in series, the BPF's must also present SC at the center frequencies of the other channels. The rightmost port should be a SC.

The equivalent circuit of the triplexer is shown in Figure 2.13 (c). It is seen that if the first elements of the BPF's are shunt SC stubs then the SC stubs of the diplexing PCL's can be treated as part of that filter. For example the comb type filters are suitable for this purpose. Such filters tend to have SC impedance outside their passbands. The shunt SC stubs of the diplexing PCL's and the transformers can be extracted form the combline filter during the synthesis stage. The transformers can be used to scale the impedance levels of the combline filters and also adjust the degree of coupling of the diplexing PCL's. The outputs can be left separate or combined through a power combiner or through a manifold of the same type as the input

manifold as shown in Figure 2.13 (d) to form a single input-single output version of the multiplexer. Switches can also be placed for switching in and out of the channels to convert the structure into a switched multiplexer to get some flexibility for covering targeted bandwidth while being able to reject some frequency bands. The switches may be placed inside the filters as described in [48]. Figure 2.13 (e) shows the layout of a possible realization using combline filters.

Practical realization difficulties may lead to limitations in bandwidths of the channels. Adjacent channels may interact because their input impedance may not be low enough to simulate SC over a sufficient bandwidth. Such problems may be eased by using guard bands between channels. The guard bands can then be covered by using another multiplexer in parallel using power combiners.

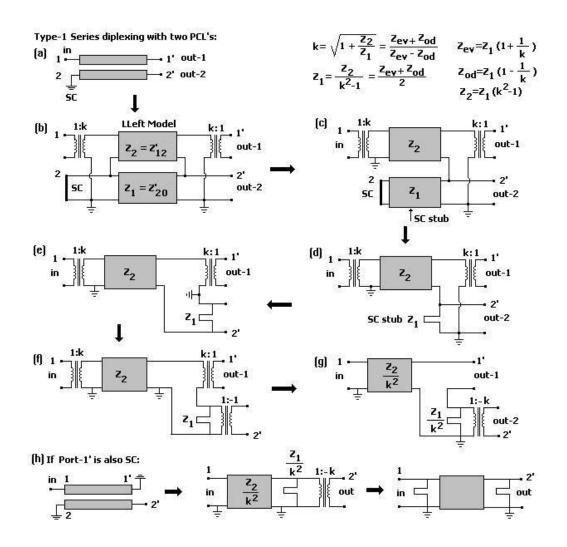

(a) Type-1 Series diplexing with two PCL's:

(b) Manifold type series multiplexing

Figure 2. 13 (a) Series Diplexing PCL and Its Equivalent Circuit, (b) Series Multiplexing Structure (a Triplexer), (c) Equivalent Circuit of Series Multiplexer, (d) A Single Input-Single Output Switched Multiplexer and (e) A Possible Realization Layout Using Combline Filters

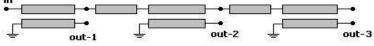

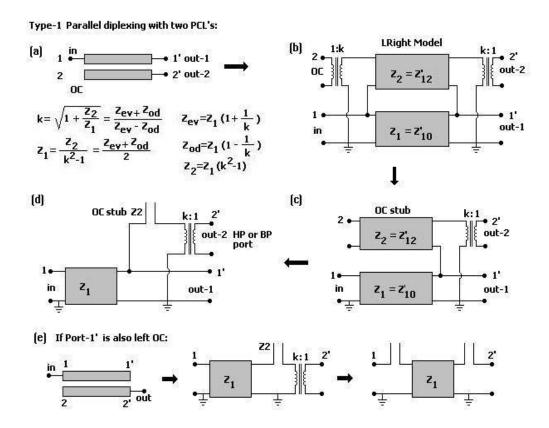

# 2.9.2. Parallel Multiplexing Manifold

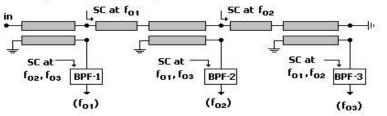

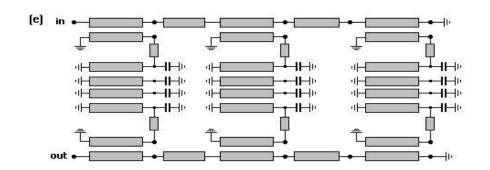

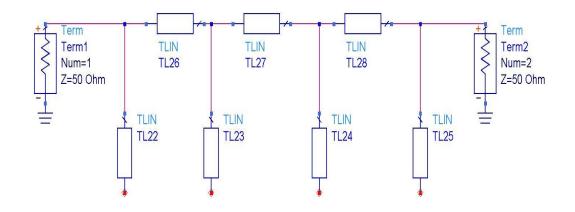

The dual version of the series multiplexing manifold can be formed by using parallel diplexing circuit shown in Figure 2.14.a. The three port diplexing element is formed by leaving one port of the coupled line adjacent to the input port open circuit. It is seen that the filters that will be connected to the output ports out-1 and out-2 will be in parallel. In order that this circuit work as a diplexer the filter connected to one of these ports must show OC input impedance within the passband of the other filter. Figure 2.14.b shows a possible multiplexing structure (a triplexer). The channel filters are connected to port-2' of the diplexing PCL's. The cascaded diplexing sections are separated by transmission line pieces which can be used to make the input impedance seen at port-1' OC at the passband center frequency of the relevant diplexing PCL section on its left. Thus, for example if the frequency of the incoming signal is fo1 (passband center of BPF-1), then it will be directed to port-2' (BPF-1) because the impedance at port-1' is OC at that frequency. Since the circuits at port-1' and port-2' are in parallel, the BPF's must also present OC impedance at the center frequencies of the other channels. The transmission line pieces separating the channel filters form a barrier for channel bandwidths because their transforming action is frequency dependent, valid usually in a limited band. The rightmost port should be left as OC. The equivalent circuit of the triplexer is shown in Figure 2.14.c. It is seen that if the first elements of the BPF's are series OC stubs then the OC stubs of the diplexing PCL's can be treated as part of that filter. For example the OC edge coupled line type filters are suitable for this purpose. Such filters tend to have high impedance outside their passbands so that they will not load the other filter too much. The series OC stubs of the diplexing PCL's and the transformers can be extracted form the edge coupled line filter during the synthesis stage. The transformers can be used to scale the impedance levels of the edge coupled line filters and also adjust the degree of coupling of the diplexing PCL's. The outputs can be left separate or combined through a power combiner or through a manifold of the same type as the input manifold as shown in Figure 2.14.d to form a single input-single output version of the multiplexer. Switches can also be placed for switching in and out of the channels to convert the structure into a switched multiplexer to get some flexibility for covering targeted bandwidth while being able to reject some frequency bands. The switches may be placed inside the filters. Figure 2.14.e shows the layout of a possible realization using a version of OC edge coupled line filters.

Figure 2. 14 a) Parallel diplexing PCL and its equivalent circuit. b) A parallel multiplexing structure (a triplexer). c) Equivalent circuit of parallel multiplexer. d) A single input-single output switched multiplexer. e) A possible realization layout using edge coupled line filters.

In microwave filter practice short circuits in the stubs or PCL's are problematic for realization. Therefore if possible, the filters containing short circuited elements are avoided. For this reason in this thesis parallel diplexing PCL approach is preferred which leads to channel filters with OC stubs and OC PCL types.

Channel interaction problems in contiguous multiplexers can be eased by using guard bands between channels. The guard bands can then be covered by using another multiplexer in parallel using power combiners as shown in Figure 2.15 in which two noncontiguous multiplexers are combined to form a contiguous multiplexer with single input and single output.

Figure 2. 15 Combining two non-contiguous multiplexers to form a contiguous multiplexer.

The phase correction at the crossover frequencies of adjacent channels can be introduced in one path to ensure crossover phase is correct to reduce the ripple at cross-over frequencies. The overall path length in both channels can be made identical, so the phase correction network needs to compensate only the phase difference of the adjacent channel filters at band edges.

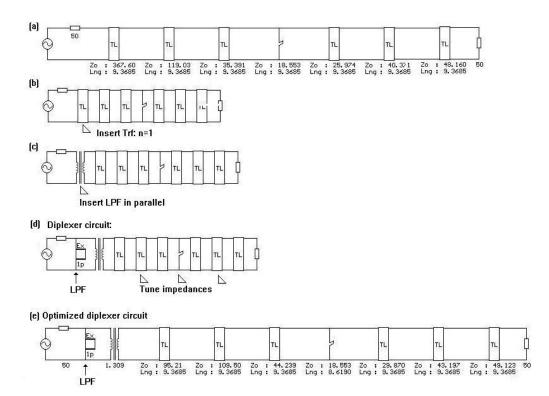

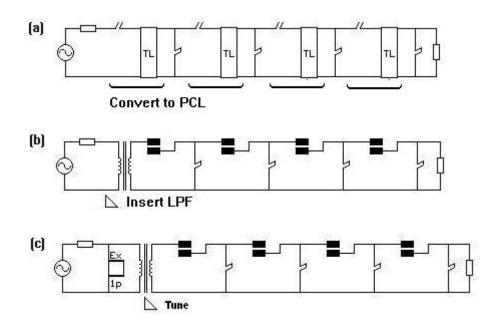

# 2. 10. A Novel Switched Multiplexer Topology

One limitation of the topologies given in Figure 2.14.and 2.15 comes from the frequency dependent nature of the transmission line pieces separating the channels. These lines should behave as an open circuit or short circuit within the passband of the channel filter on its left. This is not possible over a wide band. Therefore the adjacent channels will interact leading to degradation in responses. Therefore these approaches seem to be applicable only to narrow-medium channel bandwidths. In this thesis this problem is solved by using LP filters instead of transmission line pieces to sustain open circuit behaviour over the passband of the adjacent channel, 2-18 GHz switched multiplexer that is targeted to be designed and implemented in this thesis. This novel topology solves also the 3 dB ripple problem of the contiguous multiplexers. In these respects it is radically different from the previously described classical multiplexers, as follows.

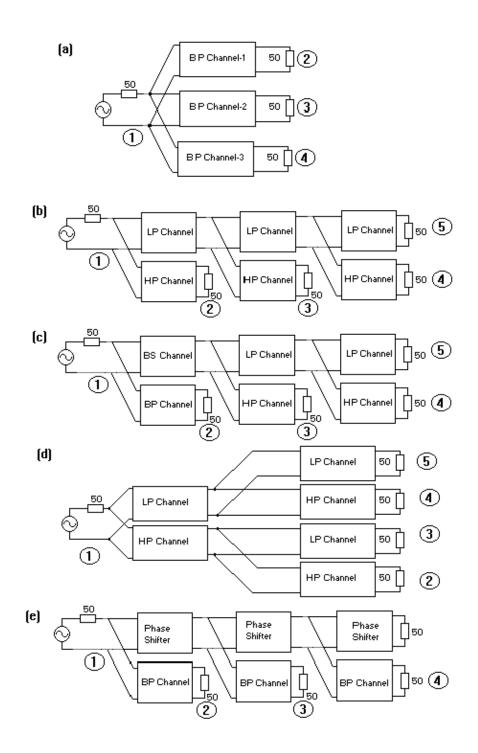

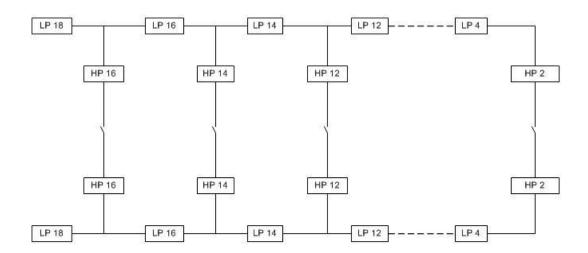

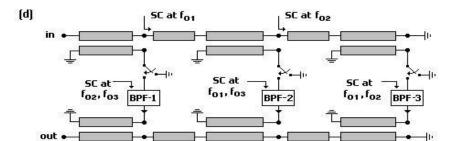

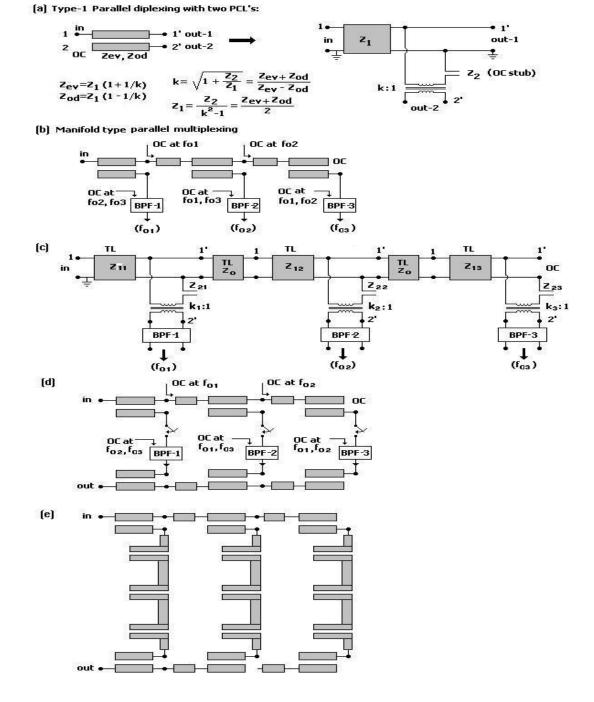

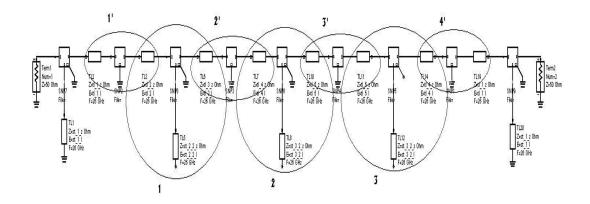

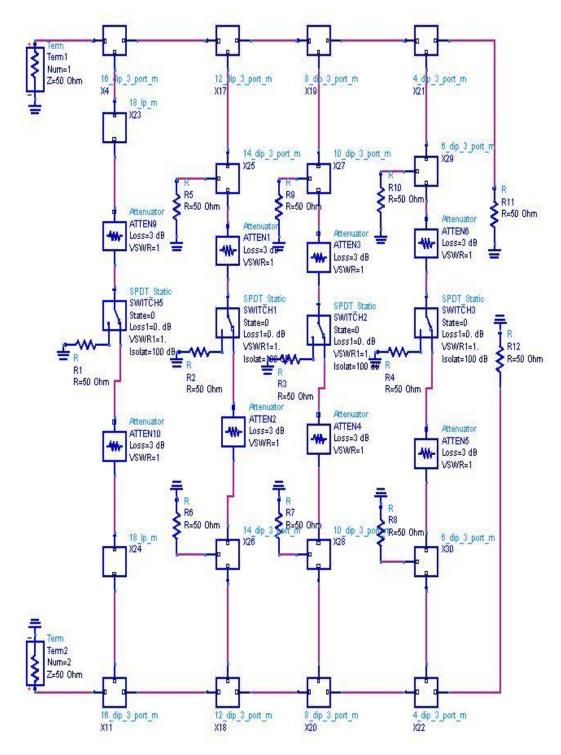

The channel filters are grouped into two LP-HP type multiplexers with adjacent channels placed in different multiplexers to provide guard bands. The first SW\_MUX is formed by integrating channels 1, 3, 5, 7 (2-4 GHz, 6-8 GHz, 10-12 GHz and 14-16 GHz) into a multiplexing manifold, then by connecting the same structure symmetrically with respect to a switch (Figure 1.16). This SW\_MUX is called the odd half as it contains odd numbered channels. The second SW\_MUX is formed by integrating channels 2, 4, 6, 8 (4-6 GHz, 8-10 GHz, 12-14 GHz and 16-18 GHz) into a multiplexing manifold, then by connecting the same structure symmetrically with respect to a switch (Figure 2.17). This SW\_MUX is called the odd half as it contains even numbered channels. Next even and odd halves are connected to form the final switched multiplexer as shown in Figure 2.18.

As mentioned above, the topologies used in these circuits enables to solve both bandwidth limitations and ripples at the corner frequencies of the contiguous multiplexers:

The LP-HP multiplexers are formed by combing contiguous diplexers having 4 GHz bandwidth. It should be noted that that instead of transmission line pieces, now

LPF's are used for isolating the adjacent diplexers by presenting OC (high impedance) to the diplexers on left. These LPF's, besides offering more flexibility for tuning and optimization to improve isolation between channels and to improve the overall return loss, they also serve as band limiters for the subsequent channel filters, to eliminate possible spurious responses.

2 GHz channels are formed by inserting LPF's with 2 GHz offset into the HP channel of the diplexers in cascade with the HPF. The corner frequencies of the LPF's are 2 GHz higher than the corner frequencies of the HPF's. Thus, the HP branch is converted into BP filter with 2 GHz bandwidth.

The main aim of using the 2 GHz offset LPF's is not only for setting the bandwidth, but also to avoid the 3 dB ripples of the classical contiguous multiplexers. Inspection of the circuits shows that there is no attenuation at cross-over frequencies of the channel filters. The signals at the corner frequencies (2 GHz, 4 GHz, 6 GHz, 8 GHz,10 GHz, 12 GHz, 14 GHz, 16 GHz, 18 GHz) will be first splitted then combined, so there will be no loss. However the signals within of the passband of the channels will be attenuated by 6 dB due to splitter-combiners. For perfect recombination the losses at corner frequencies must be 6 dB down with respect to center frequencies. Since channel filters are former by symmetrical combinations, the original designed filter should have 3 dB loss at band edges with respect to center frequencies. Since the LP-HP diplexers are contiguous, the loss at corner frequencies is 3 dB. The other corner frequency for the channel will be coming from the LP filter succeeding it. If the loss at corner frequency of the LP filter is also made 3 dB, when manifolds are connected back to back, the loss at corner frequencies will be 6 dB below the center frequencies, satisfying the above mentioned requirement.

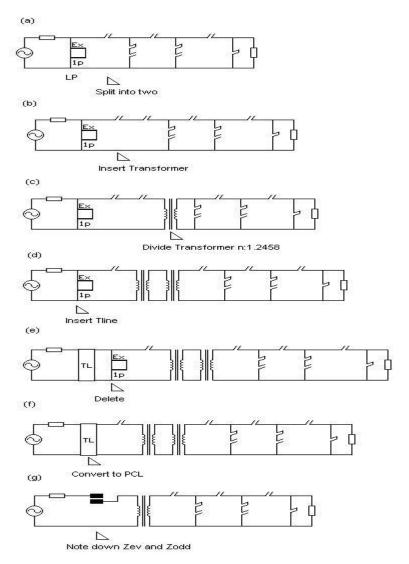

Thus, the topology of the multiplexer is altered as shown in Figures 2.16 -2.17-2.18 where the contiguous HP-LP ladder type multiplexer or a SW\_MUX is converted into two non-contiguous multiplexers with adjacent channels shared alternately by the two multiplexers to provide guard bands between channels as described in Figure 2.15. Thus, only two splitters will be enough to multiplex over any number of

channels. In the scope of this thesis a structure based on this topology will be designed.

Figure 2. 16 Even Half of SW\_MUX with LP filter

Figure 2. 17 Odd Half of SW\_MUX with LP filter

Figure 2. 18Connection of even and odd channel multiplexers through splitters.

Direct integration of the LP filters with HP filters of the HP channels may be problematic, because LP filter will be reflective in the passband of the HP filter, causing mismatches. These reflections may be weakened by using extra attenuators between LP and HP filters. Since the extra attenuators will create unaccounted loss a neater but slightly more complex solution would be to use diplexers in the HP channels as shown in Figure 2.19 and 2.20. The diplexer's corner frequency has again 2 GHz offset. Besides, these diplexers will also be used to form bandpass channels. This will eliminate the design of extra LP filters as well. It is seen that we still have attenuators in the HP branches. They are needed to attenuate the unavoidable reflections at switch-filter junctions. That is, attenuators are usually unavoidable elements in such reflection sensitive multiplexers. This is mostly the case in every manifold coupled switch multiplexer.

Figure 2. 19 Even Half of SW\_MUX with diplexers in place of extra attenuators.

Figure 2. 20 Odd Half of SW\_MUX with diplexers in place of extra attenuators.

# **CHAPTER 3**

# THE USE OF PARALLEL COUPLED LINES AS DIPLEXING ELEMENTS

A diplexer has essentially three parts: 2 channel filters and a diplexing mechanism. As noted in the previous chapter, parallel coupled lines can be used as diplexing mechanisms. In the previous chapter some topologies involving short circuited parallel coupled lines (SCPCL) to be used for series diplexing and open circuited parallel coupled line (OCPCL) for parallel diplexing. In this chapter, first, different circuit models will be presented for parallel coupled lines, then the series diplexing circuits using SCPCL and parallel diplexing circuits using OCPCL will be presented. Finally a comparison between traditional T-junction diplexing and OCPCL diplexing will be made in matching and isolation aspects.

Parallel coupled lines (PCL) are essential elements of distributed element highpass and bandpass filters. Parallel coupled line pairs are four port circuits. They can be converted into three port, two port or one port elements by terminating their unused ports in OC, SC, open or short circuited stubs, etc. as described in literature, for example by Sato and Crystal [7] and Malherbe [18]. In most of the distributed element diplexers and multiplexers parallel coupled lines are used as three port networks which can be used for splitting the input signal into two paths (diplexing PCL). Similarly three coupled lines with no coupling beyond the adjacent line can also be used for splitting input signal into two paths.

In this section a summary of three port parallel coupled lines will be presented. Since derivation of the equivalent circuits of PCL sections are usually confusing and complex for many engineers with different backgrounds, detailed explanations are given below using several different approaches.

# **3. 1. Circuit Models of Parallel Coupled Llines**

In Figure 3.1.a a parallel coupled transmission line pair is shown in a homogeneous nonmagnetic medium in between two ground planes. For pure TEM mode operation the propagation constant is

$$\beta = \frac{\omega}{v} = \omega \sqrt{\mu \varepsilon} = \frac{\omega \sqrt{\varepsilon_r}}{c}$$

(3.1.1)

Such a coupled line pair can be described in several different ways as follows:

## a) Three Line Model of a two-wire line above ground:

A coupled line pair can be characterized through their per unit length line-to-ground and line-to-line inductance and capacitance parameters L11, L12, L22 and C10, C20, C12, as shown in Figure 3.1.b. The pair L11-C10 can be assumed to describe a twowire TEM mode transmission line between Line-1 and ground. Similarly, the pair L22-C20 can be assumed to describe a two-wire TEM mode line between Line-2 and ground. By the same reasoning the pair L12-C12 can be assumed to describe a twowire TEM mode transmission line in between Line-1 and Line-2. So, we can model the coupled line pair as consisting of three two-wire TEM mode transmission lines as sown in Figure 3.1.b. At first sight the terminology of representing a two-line system with three lines may appear to be confusing. However, the two PCL system is actually a three wire system with the ground being the third wire.

Figure 3. 1Three Line model of a parallel coupled line pair.

For pure TEM mode operation the per unit length parameters are related to the propagation constant as follows:

$$\beta = \omega \sqrt{L_{11}C_{10}} = \omega \sqrt{L_{22}C_{20}} = \omega \sqrt{L_{12}C_{12}} = \frac{\omega}{\nu} = \omega \sqrt{\mu\varepsilon} = \frac{\omega \sqrt{\varepsilon_r}}{c}$$

(3.1.2)

Thus, L's and C's of a line are related to each other as follows:

$$L_{11} = \frac{\varepsilon_r}{c^2 C_{10}} \qquad L_{22} \frac{\varepsilon_r}{c^2 C_{20}} \qquad L_{12} = \frac{\varepsilon_r}{c^2 C_{12}}$$

(3.1.3)

Thus, the three lines, hence the coupled line pair can be characterized through the per unit length capacitances C10, C20 and C12 only, as shown in Figure 3.1.c. Characteristic impedances of each transmission line can be calculated through the definitions

$$Z_{10} = \sqrt{\frac{L_{11}}{C_{10}}} = \frac{\sqrt{\varepsilon_r}}{cC_{10}} \quad Z_{20} = \sqrt{\frac{L_{22}}{C_{20}}} = \frac{\sqrt{\varepsilon_r}}{cC_{20}} \quad Z_{12} = \sqrt{\frac{L_{12}}{C_{12}}} = \frac{\sqrt{\varepsilon_r}}{cC_{12}}$$

(3.1.4)

In Figure 3.1.d the three uncoupled transmission lines are described now using their characteristic impedances. The ports of Line-1 are numbered as 1 and 4 while the ports of Line-2 are numbered as 2 and 3. For use in later descriptions, In Figure 3.1.e and f the network is repeated for the case of a single ground plane placed at bottom. On the left we have Line-1 (or Line 1-4) and on the right we have Line-2 (or Line 2-3). This circuit model will be used to derive other equivalent circuits which may be easier to use on different applications.

#### b) Even-Odd Mode Description of a Symmetric Coupled Line Pair

If the two coupled lines are identical then we have L11=L22, C11=C22, thus simplifying the characterization through the impedances also:

$$Z11 = Z22 = \sqrt{\frac{L11}{C10}} = \frac{\sqrt{\varepsilon_r}}{cC10}, \qquad Z12 = \sqrt{\frac{L12}{C12}} = \frac{\sqrt{\varepsilon_r}}{cC12}$$

(3.1.5)

For such cases the excitations, voltage, current, power waves and coupled line pair can be decomposed even and odd mode halves as described in Figure 3.2. Representing the voltage waves on Line-1 and Line-2 as V1(x) and V2(x), we can always write

$$V1(x) = Ve(x) + Vod(x)$$

(3.1.6)

$$V2(x) = Ve(x) - Vod(x)$$

(3.1.7)

Under even mode excitation the two lines have identical voltages, currents and power. Thus, we can place an OC wall on the symmetry plane between the two lines, splitting the mutual capacitor C12 into two equal capacitors, 2C12 as shown in Figure 3.2.c. Since the capacitors are open on the symmetry plane we can disregard them. The two halves form identical lines whose per unit length capacitance to ground is C10 only. It is named as even mode capacitance Cev:

$$Ce = C_{10}$$

(3.1.8)

The characteristic impedance of the two identical lines can thus be calculated using the even mode capacitor as

$$Zev = \frac{\sqrt{\varepsilon_r}}{cCev}$$

(3.1.9)

Under odd mode excitation the voltages on the two lines are equal in magnitude but opposite in phase. Thus, the symmetry plane has zero voltage. That is, it can be assumed as just extension of the ground plane. The mutual capacitor C12 is split by the symmetry plane into two pieces with capacitance 2C12. Since one ends of these capacitors are grounded the capacitors 2C12 become parallel with the line-to-ground capacitor C10. Thus, the total line-to-ground per unit length capacitance is C10+2C12, and it is named as odd mode capacitance:

$$Cod = C_{10} + 2C_{12} \tag{3.1.10}$$

The characteristic impedance of the odd mode half is then evaluated as:

$$Zod = \frac{\sqrt{\varepsilon_r}}{cCod}$$

(3.1.11)

Thus, if the capacitances Cev and Cod can be calculated then the even and odd mode characteristic impedances describing the coupled line pair can be found. It is clear that only two parameters Zev and Zodd are sufficient to describe a symmetric PCL.

Figure 3. 2 Even-odd mode decomposition of a symmetric parallel coupled line pair

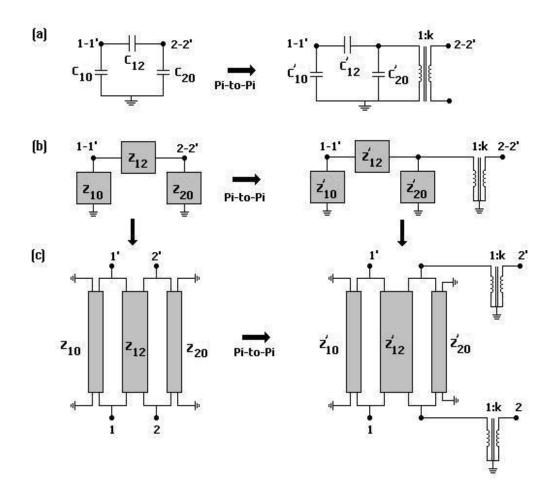

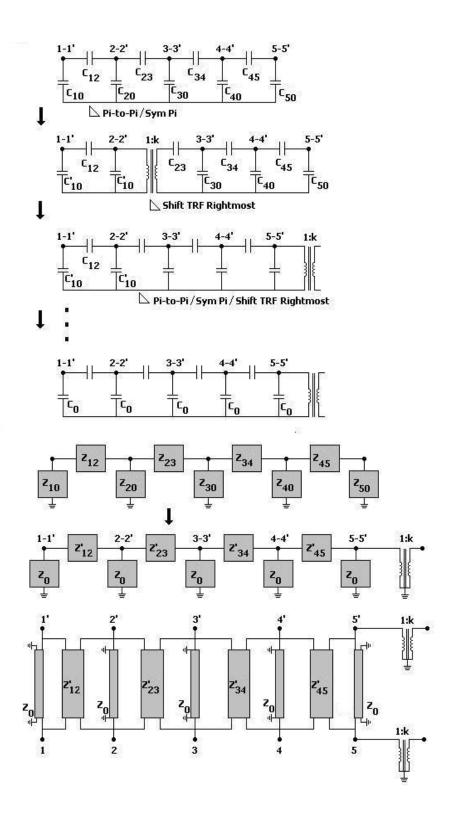

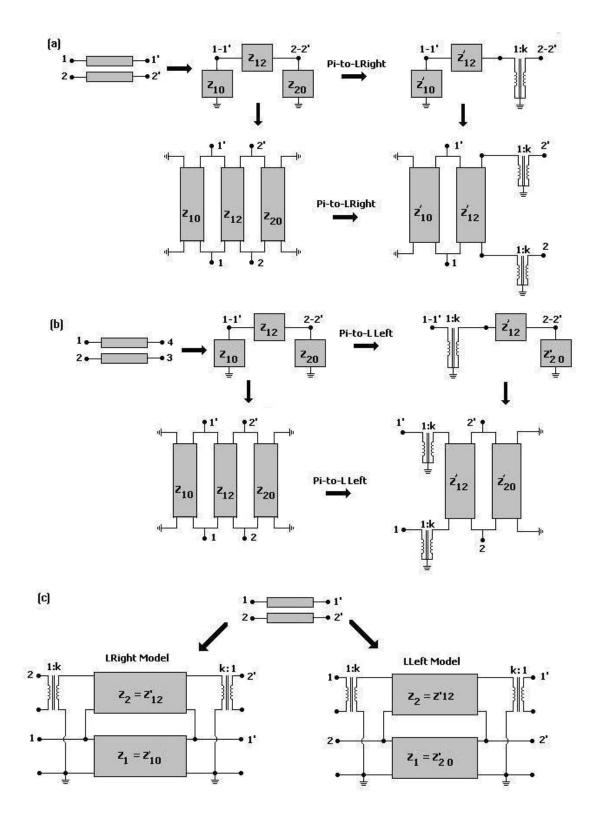

# c) Norton and Pi-Tee-L Transformations on Three Line Network Model

Norton and Pi-Tee-L transformations can be applied on a three line network model of a coupled line pair circuit to form different equivalent four ports. Norton transformation is shown in Figure 3.3. Originally it was defined on lumped elements but can be generalized to cover distributed elements also. Norton transformation converts a series element (R, L, C, Z, jX, OC Stub, SC Stub, TL) into a Pi-section together with a transformer while a shunt element is converted into a Tee-section together with a transformer. The new elements are of the same type as the original element. One of the shunt elements of the Pi-section and one of the series elements of the Tee-section is negative always. So, Norton transformation can be used to find new equivalent circuits at the expense of increased redundancy where one element is replaced by four elements.