## IMPROVING THE EFFICIENCY OF MICROWAVE POWER AMPLIFIERS WITHOUT LINEARITY DEGRADATION USING LOAD AND BIAS TUNING IN A NEW CONFIGURATION

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

AMIN RONAGHZADEH

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ELECTRICAL AND ELECTRONICS ENGINEERING

FEBRUARY 2013

#### Approval of the thesis:

## IMPROVING THE EFFICIENCY OF MICROWAVE POWER AMPLIFIERS WITHOUT LINEARITY DEGRADATION USING LOAD AND BIAS TUNING IN A NEW CONFIGURATION

submitted by **AMIN RONAGHZADEH** in partial fulfillment of the requirements for the degree of **Doctor of Philosophy** in **Electrical and Electronics Engineering Department, Middle East Technical University** by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>                |  |

|------------------------------------------------------------------------------------------------------|--|

| Prof. Dr. İsmet Erkmen<br>Head of Department, <b>Electrical and Electronics Engineering</b>          |  |

| Prof. Dr. Şimşek Demir<br>Supervisor, <b>Electrical and Electronics Engineering Department, METU</b> |  |

| Examining Committee Members:                                                                         |  |

| Prof. Dr. Canan Toker<br>Electrical and Electronics Engineering Department, METU                     |  |

| Prof. Dr. Şimşek Demir<br>Electrical and Electronics Engineering Department, METU                    |  |

| Prof. Dr. Nevzat Yıldırım<br>Electrical and Electronics Engineering Department, METU                 |  |

| Prof. Dr. Abdullah Atalar<br>Electrical and Electronics Engineering Department, Bilkent University   |  |

| Assist. Prof. Dr. Arif Sanlı Ergün<br>Electrical and Electronics Engineering Department, TOBB ETÜ    |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: AMIN RONAGHZADEH

Signature :

## ABSTRACT

## IMPROVING THE EFFICIENCY OF MICROWAVE POWER AMPLIFIERS WITHOUT LINEARITY DEGRADATION USING LOAD AND BIAS TUNING IN A NEW CONFIGURATION

Ronaghzadeh, Amin Ph.D., Department of Electrical and Electronics Engineering Supervisor : Prof. Dr. Şimşek Demir

February 2013, 144 pages

Advanced digital modulation schemes used in the wireless applications, result in the modulated RF signals with high peak to average power ratio which requires linear amplification. On the other hand, the demand for a longer talk time with less battery volume and weight, especially in hand-held radio units, necessitate more power efficient methods to be utilized in power amplifier design. But improved linearity and efficiency have always been contradicting requirements demanding innovative power amplifier and linearizer design techniques.

Dynamically varying the load impedance and bias point of a transistor according to the varying envelope of the incoming RF signal also known as Dynamic Load Modulation (DLM) and Dynamic Supply Modulation (DSM), respectively, are two separate methods for improving the efficiency in power amplifier design. In this dissertation, a combination of both variable gate bias and tunable load concepts is applied in an amplifier structure consisting of two transistors in parallel.

A novel computer aided design methodology is proposed for careful selection of the load and biasing points of the individual transistors. The method which is based on load-pull analysis performs sweeps on the gate bias voltages of the active devices and input drive level of the amplifier in order to obtain ranges of biases that result in the generation of IMD sweet spots. Following that, the amplifier is designed employing the load line theory and bias switching at the same time in order to enhance the efficiency in reduced drive levels while extending the output 1 dB compression point to higher values at higher drives.

Tunable matching networks are implemented utilizing varactor stacks in a II configuration at the input

and output of the amplifier. The amplifier starts to operate in the first state where lowest possible bias levels are chosen for both of the transistors and the output matching network is adjusted to provide PAE matching. As approaching towards the higher output powers, the amplifier switches between different consecutive operational states per about 1 dB increment at output power. In this way, the maximum output  $P_{1dB}$  can be attained from the amplifier. The operational states are selected among a bunch of possible states obtained from the load-pull analysis, based on providing smaller leaps in transition between states in PAE and gain curves.

In order to validate the proposed design methodology, a 2.4 GHz medium-power amplifier is designed, fabricated and tested which demonstrates the feasibility of the proposed structure and design technique for power amplifier applications.

Keywords: power amplifier, efficiency, linearity, tunable impedance matching network, varactor

### MİKRODALGA GÜÇ YÜKSELTEÇLER İÇİN YENİ BİR KONFİGÜRASYONDA YÜK VE BESLEME AYARI İLE DOĞRUSALLIĞI DÜŞÜRMEDEN VERİMLİLİK ARTIRILMASI

Ronaghzadeh, Amin Doktora, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Prof. Dr. Şimşek Demir

Şubat 2013, 144 sayfa

Kablosuz uygulamalarda kullanılan gelişmiş dijital modülasyon teknikleri, doğrusal yükseltme gerektiren, tepe gücü ortalama gücüne göre yüksek olan mödüle olmuş RF sinyallerine neden olur. Öte yandan, özellikle elle taşınır radyo ünitelerinde, daha hafif ve küçük piller ile daha uzun konuşma süresi talebi, güç yükselteç tasarımında daha verimli yöntemlerin kullanılmasını gerektirir. Ancak, yüksek doğrusallık ve yüksek verimlilik isterlerinin birbiri ile çelişmesi, yenilikçi güç yükselteç ve doğrusallaştırıcı tasarım tekniklerini gerektirmektedir.

Sırası ile Dinamik Yük Modülasyonu (DYM) ve Dinamik Besleme Modülasyonu (DBM) olarak bilinen, transistörün yük empedansının veya bias noktasının gelen RF sinyalinin değişken zarfına göre değiştirilmesi, güç yükselteci tasarımında verimliliği artırmak amacı ile uygulanan iki ayrı yöntemdir. Bu tezde, paralel bağlanmış iki transistörden oluşan yükselteç yapısında, hem değişken bias (DBM) hem de ayarlanabilir yük (DYM) kavramları uygulanmıştır.

Her bir transistörün yük ve bias noktalarının dikkatlice seçilmesi için yeni bir bilgisayar destekli tasarım yöntembilimi önerilmiştir. Load-pull analizine dayanmakta olan bu yöntem, IMD sweet spotlarının oluşumuna yol açan bias aralıklarını elde etmek amacıyla, aktif cihazların gate bias gerilimlerinin ve yükselteçin giriş gücünün üzerine tarama yapmaktadır. Ardından load line teorisini ve bias anahtarlamayı aynı anda kullanarak, yüksek sürüşlerde 1 dB çıkış bastırma noktasını yüksek seviyelere taşıyarak düşük sürüş seviyelerinde verimliliği artırmak amacı ile yükselteç tasarlanmıştır.

Yükseltecin giriş ve çıkışına, Π konfigürasyonda olan varaktör kümeleri kullanılarak, ayarlanabilir empedans uyumlama ağları yerleştirilmiştir. Yükselteçte bulunan her iki transistör için mümkün olan en düşük bias seviyesi seçilerek ve güç eklenmiş verimlilik (PAE) uyumu sağlamak amacı ile çıkış empedans uyumlama ağında ayarlama yapılarak yükselteç birinci durumda çalışmaya başlatılır. Daha yüksek çıkış güçlere yaklaşıldıkça, yükselteç çıkış gücünün 1 dB aralıklar ile artmasına karşılık gelen ardışık çalışma durumları arasında geçiş yapar. Böylece yükselteç yapısından maximum çıkış P<sub>1dB</sub> elde edilir. Yükselteçin operasyonel durumları, PAE ve kazanç grafiklerinde belirtilen durumlar arasındaki geçişte küçük sıçramalar sağlayan load-pull analizinden elde edilmiş birçok olası durum arasından seçilmektedir.

Önerilen tasarım yöntembilimini doğrulamak için 2.4 GHz'de çalışan orta-güç seviyeli bir yükselteç tasarlanıp, üretilmiş ve testleri yapılmıştır. Böylece güç yükselteç uygulamalarında önerilen yapının ve tasarım tekniğinin yapılabilirliği gösterilmiştir.

Anahtar Kelimeler: Güç Yükselteç, Verimlilik, Doğrusallık, Ayarlanabilir Empedans Uyumlama Ağı, Varaktör

To my beloved parents

and

sister,

## ACKNOWLEDGMENTS

It is my great pleasure to take this opportunity to thank everyone who made this dissertation possible. First and foremost, I would like to express my sincere gratitude and appreciation to my advisor Professor Şimşek Demir for his unfailing and invaluable guidance and support. I have benefited especially from his constructive comments and suggestions throughout this project. Without him, this long journey would not be so unforgettable and enjoyable.

I would also like to thank the members of my thesis monitoring committee, Professor Nevzat Yıldırım and Assistant Professor Arif Sanlı Ergün, for their suggestions and recommendations.

A special gratitude goes to Professor Abdullah Atalar for dedicating his precious time to a thorough examination of the thesis and for his invaluable comments on the defence day. It was a great honor for me to have him as one of my jury members.

Many thanks would go to my colleagues in Antenna and Microwave Laboratory at METU for their inspiring discussions, suggestions and friendship. I would especially like to acknowledge Ömer Bayraktar for helping me in writing the reports and abstracts in Turkish and Çağrı Çetintepe for his invaluable comments in editing the thesis.

This research was generously supported by Scientific and Technical Research Council of Turkey (TÜBİTAK) under the 2215 PhD fellowship program. I would like to express my gratitude to all of the TÜBİTAK officials who provided me with this opportunity.

This research would not have finalized without the support of a special person in Space Technologies Research Institute (TÜBİTAK UZAY), İlhan Bayramoğlu. I feel deeply indepted to him for his sincere help in fabrication of the circuit boards, in spite of being busy with his own resposibilities at the institute. I would also like to thank Assistant Professor Kağan Topallı, Celal Dudak and Emrah Öncü in TÜBİTAK UZAY for their supporting friendship and suggestions.

I would like to acknowledge my dear friend and housemate Pejman Mohammadi who is really like an older brother to me. He gave me priceless support and advices during my PhD studies that I will never forget.

Last but not the least, I would like to express my deepest gratitute to my parents whithout whom I would never have been able to reach where I am. Their encouragement and support have always been the greatest asset of my life upon which my future is standing. This achievement is as much theirs as it is mine. And finally, my last gratitude goes to my only sister, Samindokht Ronaghzadeh for her love and support. She has always kept me happy and hopeful in my life with her joyful attitudes and encouragements. I wish her the best of luck in her own PhD studies.

# **TABLE OF CONTENTS**

| ABSTRA  | ACT    |           | v                                                         |

|---------|--------|-----------|-----------------------------------------------------------|

| ÖZ      |        |           | vii                                                       |

| ACKNO   | WLEDG  | MENTS .   | x                                                         |

| TABLE   | OF CON | TENTS .   | xii                                                       |

| LIST OF | TABLE  | S         | xvi                                                       |

| LIST OF | FIGUR  | ES        |                                                           |

| CHAPTI  | ERS    |           |                                                           |

| 1       | INTRO  | DUCTION   | J                                                         |

|         | 1.1    | Linearity | and Efficiency in PA Design for Wireless Communications 1 |

|         | 1.2    | Linear Po | ower Amplifiers with an Efficiency-Enhancement Circuit 4  |

|         |        | 1.2.1     | Envelope Elimination and Restoration                      |

|         |        | 1.2.2     | Envelope Tracking                                         |

|         |        | 1.2.3     | Dynamic Bias Switching                                    |

|         |        | 1.2.4     | Outphasing Technique or LINC                              |

|         |        | 1.2.5     | Doherty Amplifier                                         |

|         | 1.3    | Non-linea | ar Power Amplifiers with a Linearization Circuit          |

|         |        | 1.3.1     | Predistortion                                             |

|         |        | 1.3.2     | Feedback                                                  |

|   |       |           | 1.3.2.1      | RF feedback                             | 16 |

|---|-------|-----------|--------------|-----------------------------------------|----|

|   |       |           | 1.3.2.2      | Envelope feedback                       | 16 |

|   |       |           | 1.3.2.3      | Polar feedback                          | 17 |

|   |       |           | 1.3.2.4      | Cartesian feedback                      | 18 |

|   |       | 1.3.3     | Feedforwar   | rd                                      | 19 |

|   | 1.4   | Research  | Objectives   | and Organization of the Thesis          | 20 |

| 2 | TUNAI | BLE MAT   | CHING TEC    | CHNIQUES                                | 23 |

|   | 2.1   | Introduct | tion         |                                         | 23 |

|   | 2.2   | Load-Lir  | ne Theory .  |                                         | 23 |

|   |       | 2.2.1     | Gain Matel   | n and Power Match                       | 23 |

|   |       | 2.2.2     | Optimum I    | Load Matching                           | 24 |

|   | 2.3   | Load-Pu   | ll Analysis  |                                         | 26 |

|   | 2.4   | Providing | g Tunability | in Reconfigurable Matching Networks     | 28 |

|   | 2.5   | Varactor- | -Based Tuna  | ble Matching Networks                   | 29 |

| 3 |       |           |              | ENT WITHOUT DEGRADED LINEARITY IN A NEW | 39 |

|   | 3.1   | Introduct | tion         |                                         | 39 |

|   | 3.2   | Intermod  | lulation Swe | et Spots                                | 41 |

|   | 3.3   | Power A   | mplifier Des | ign                                     | 43 |

|   |       | 3.3.1     | Circuit Cor  | nfiguration                             | 44 |

|   |       | 3.3.2     | Design Me    | thodology                               | 48 |

|   |       |           | 3.3.2.1      | Design step 1                           | 48 |

|   |       |           | 3.3.2.2      | Design step 2                           | 50 |

|   |       |           | 3.3.2.3      | Design step 3                           | 55 |

|   |       |           |              |                                         |    |

| 3.4   | Load-Pu   | Il Analysis Setup and TMN Design    66                        |  |

|-------|-----------|---------------------------------------------------------------|--|

|       | 3.4.1     | Choosing the Configuration                                    |  |

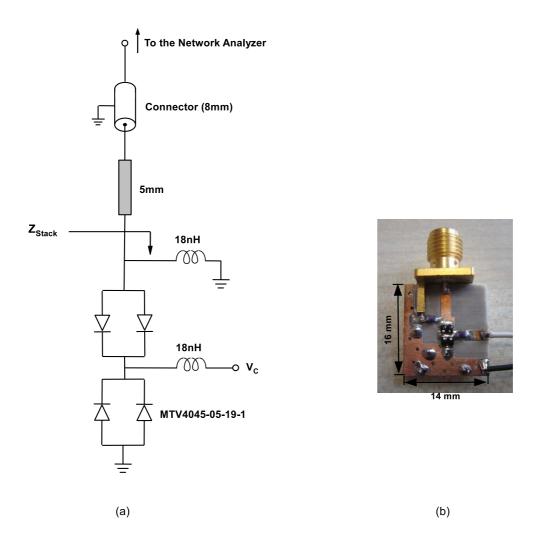

|       | 3.4.2     | Choosing the Varactor Device                                  |  |

|       | 3.4.3     | Applying Additional Modifications                             |  |

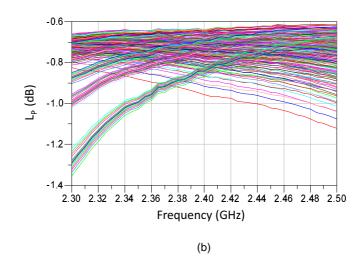

|       | 3.4.4     | Loss Factor                                                   |  |

|       | 3.4.5     | Large-signal Effects                                          |  |

|       | 3.4.6     | Final Design of the Load-Tuner                                |  |

|       | 3.4.7     | Load-Pull Analysis Using Varactor-Based Load-Tuner            |  |

|       | 3.4.8     | Tunable Input Matching Network    80                          |  |

| 3.5   | Simulatio | on Results                                                    |  |

|       | 3.5.1     | One-Tone Harmonic Balance Simulation                          |  |

|       | 3.5.2     | Large-signal S Parameters Simulation                          |  |

|       | 3.5.3     | Bandwidth Simulation                                          |  |

|       | 3.5.4     | Two-Tone Harmonic Balance Simulation    88                    |  |

| EXPER | IMENTA    | L RESULTS                                                     |  |

| 4.1   | Introduct | tion                                                          |  |

| 4.2   | Impleme   | entation and Measurements of the Amplifier                    |  |

| 4.3   | Impleme   | entation and Measurements of the Tunable Matching Networks 96 |  |

|       | 4.3.1     | Characterization of 2×2 Varactor Stack                        |  |

|       | 4.3.2     | Tuning of the Transmission Line Segments                      |  |

|       | 4.3.3     | Implementation of the Input Matching Network                  |  |

| 4.4   | Load-Pu   | ll Measurements                                               |  |

| 4.5   | State Sel | ection                                                        |  |

| 4.6   | Final Re  | sults                                                         |  |

4

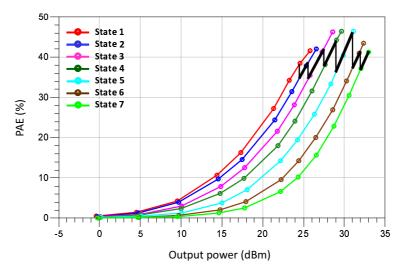

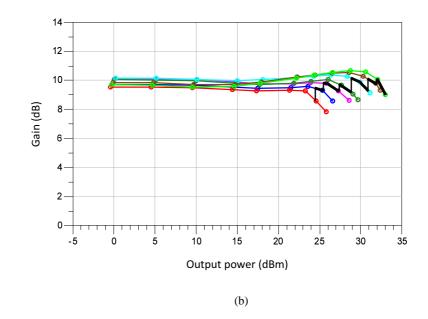

|       |        | 4.6.1    | PAE and Gain                                   |

|-------|--------|----------|------------------------------------------------|

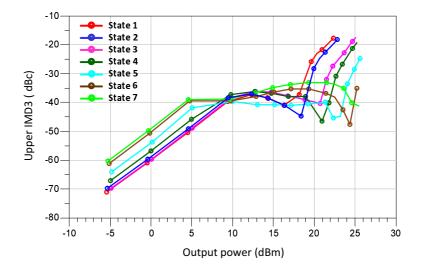

|       |        | 4.6.2    | Third Order Intermodulation                    |

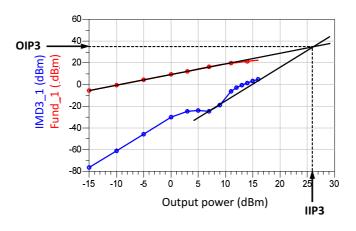

|       |        | 4.6.3    | Third Order Intercept Point                    |

|       | 4.7    | Fabricat | ion of the Completed Circuit on a Common Board |

| 5     | CONC   | LUSION   | AND FUTURE WORK                                |

|       | 5.1    | Summa    | ry and Conclusions                             |

|       | 5.2    | Directio | ns for Future Work                             |

| REFER | RENCES |          |                                                |

| APPEN | DICES  |          |                                                |

| А     | TRUN   | CATED .N | MDF FILE SAMPLE                                |

| CURR  | CULUM  | I VITAE  |                                                |

# LIST OF TABLES

## TABLES

| Table 1.1 | Popular cellular phone standards [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1.2 | Comparison of peak possible efficiency for different classes of power amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2   |

| Table 1.3 | Comparison of different PA linearization technique.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14  |

| Table 3.1 | Summary of 5 sample operational states for $V_{G1}$ = 0.25 V and $V_{G2}$ = 0.3 V $\hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \hfill \h$ | 63  |

| Table 3.2 | Summary of final 11 operational states of the amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65  |

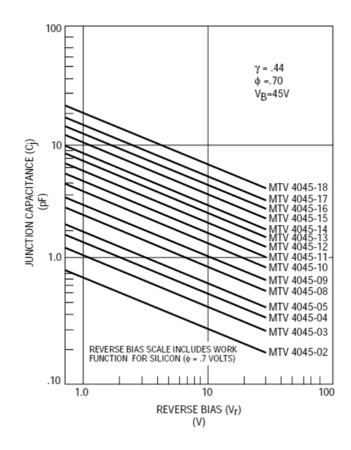

| Table 3.3 | Intrinsic and CS-19 package parameters of MTV 4045-05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69  |

|           | Comparison of the 11 optimum load points obtained by varactor-based load-tuner those of the ideal load-tuner.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79  |

| Table 3.5 | Control voltages of the varactors corresponding to the 11 operational states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80  |

| Table 4.1 | Summary of the load-pull measurement results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 115 |

| Table 4.2 | 1 dB compression points of the amplifier at 25 different biasing and matching condi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| tions.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 117 |

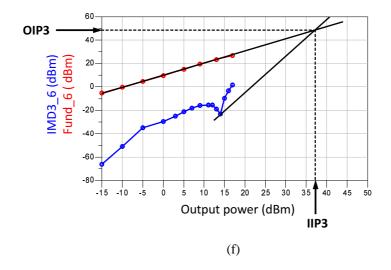

| Table 4.3 | Summary of the input and output third order intercept points at 6 operational states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| of the    | amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 126 |

# LIST OF FIGURES

## FIGURES

| Figure 1.1 Definition of PAs based on conduction angle and signal overdrive            | • •   | ••• | •••  | •   | 3  |

|----------------------------------------------------------------------------------------|-------|-----|------|-----|----|

| Figure 1.2 Efficiency and linearity trade-off in RF power amplifiers                   |       |     |      |     | 3  |

| Figure 1.3 Envelope Elimination and Restoration system.                                |       |     |      |     | 5  |

| Figure 1.4 Envelope Tracking system block diagram.                                     |       |     |      |     | 6  |

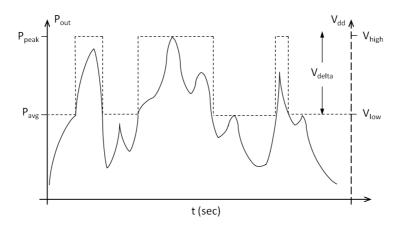

| Figure 1.5 Modulated signal waveform in DBS                                            |       |     |      |     | 8  |

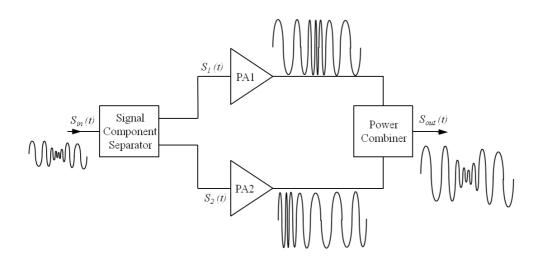

| Figure 1.6 Simplified block diagram of an outphasing system                            |       |     |      |     | 8  |

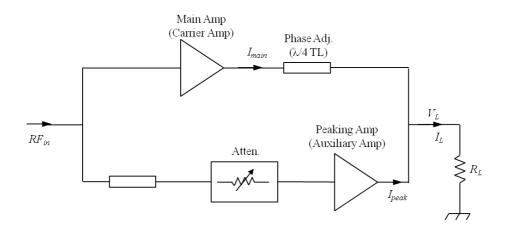

| Figure 1.7 Simplified block diagram of Doherty amplifier.                              |       |     |      |     | 10 |

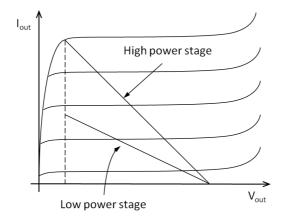

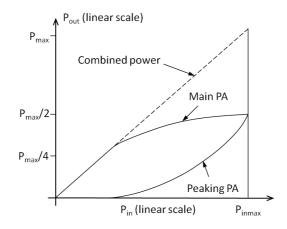

| Figure 1.8 Load line diagram of Doherty amplifier operation.                           |       |     |      |     | 10 |

| Figure 1.9 Power transfer characteristic of Doherty amplifier.                         |       |     |      |     | 11 |

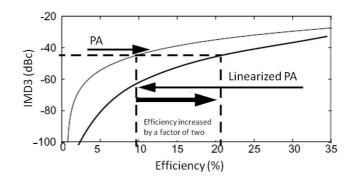

| Figure 1.10 Linearity of a PA as a function of efficiency in standalone and linearized | confi | gur | atic | on. | 13 |

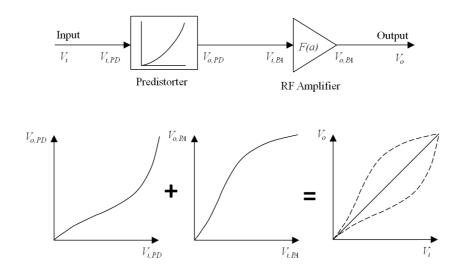

| Figure 1.11 Predistortion concept                                                      |       |     |      |     | 14 |

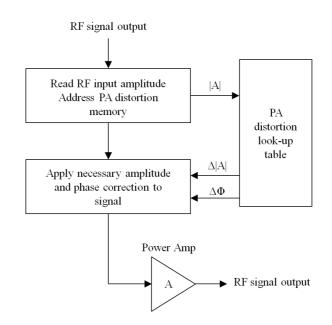

| Figure 1.12 Basic digital predistortion system flow chart                              |       |     |      |     | 15 |

| Figure 1.13 Simplified schematic of RF feedback system                                 |       |     |      |     | 16 |

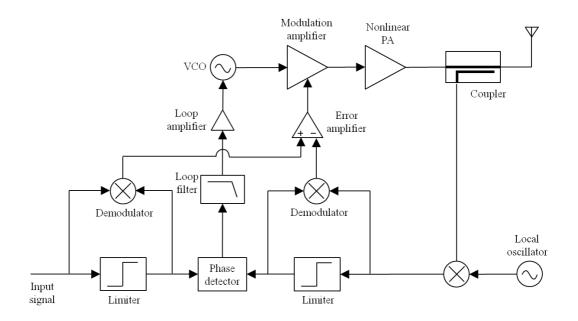

| Figure 1.14 Schematic of polar modulation feedback system                              |       |     |      |     | 17 |

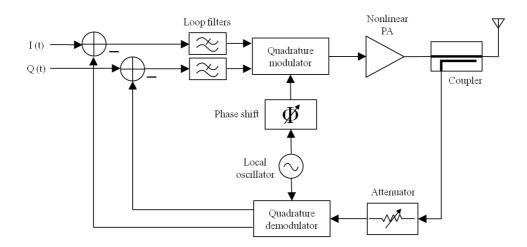

| Figure 1.15 Schematic of Cartesian modulation feedback system                          |       |     |      |     | 18 |

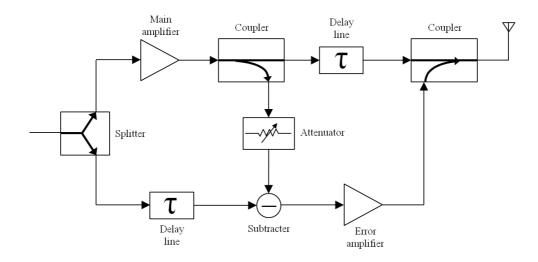

| Figure 1.16 Schematic of feedforward system.                                           |       |     |      |     | 20 |

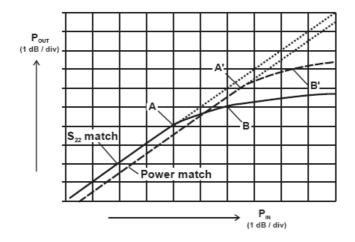

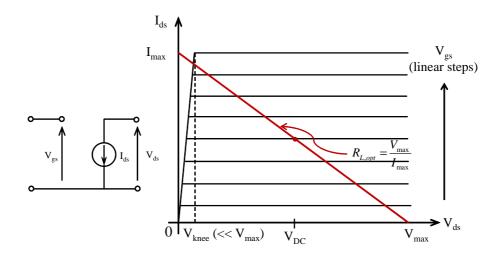

| Figure 2.1 | Compression characteristics for conjugate match and power match [1]                                                                                        | 24 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2 | Ideal nonlinear device model for optimum load explanation.                                                                                                 | 25 |

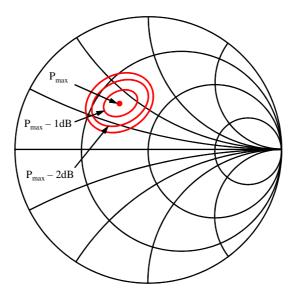

| Figure 2.3 | Typical load-pull contours.                                                                                                                                | 27 |

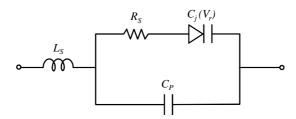

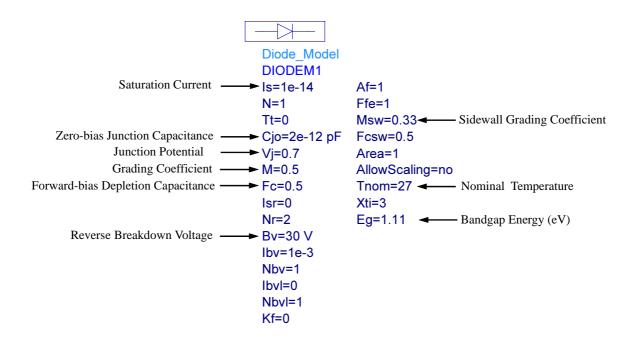

| Figure 2.4 | Simplified equivalent circuit of the packaged varactor.                                                                                                    | 31 |

| Figure 2.5 | SPICE model parameters of a typical varactor diode provide by Agilent ADS                                                                                  | 32 |

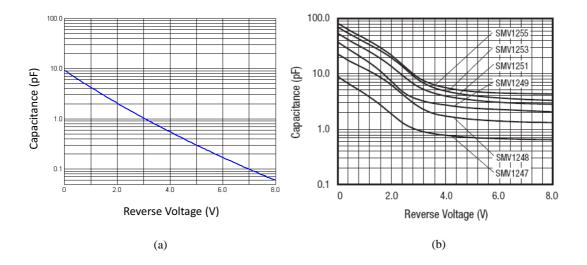

|            | Capacitance of SMV1247 varactor as a function of applied reverse voltage: (a) on based characteristic, (b) measured characteristic given by the data-sheet | 33 |

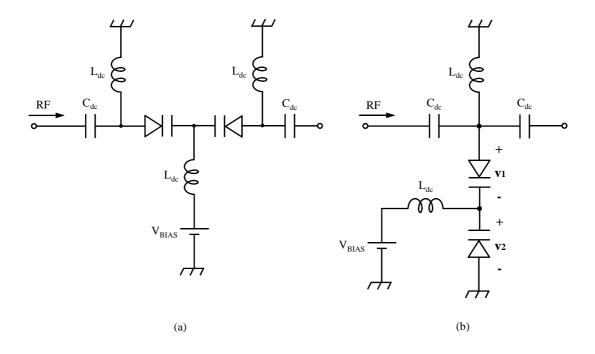

| Figure 2.7 | Anti-series varactor diode configuration. Varactors can be in (a) series or (b) parallel                                                                   |    |

| with th    | he RF path                                                                                                                                                 | 34 |

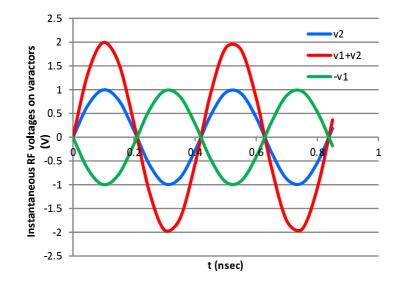

| Figure 2.8 | Instantaneous RF voltages on the varactors in the anti-series configuration                                                                                | 37 |

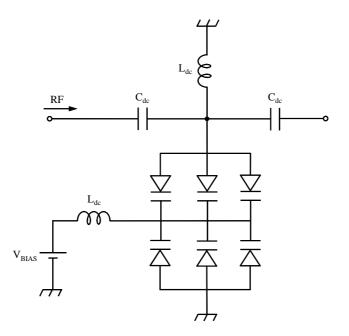

| Figure 2.9 | A 2×3 varactor stack in parallel with the RF path                                                                                                          | 38 |

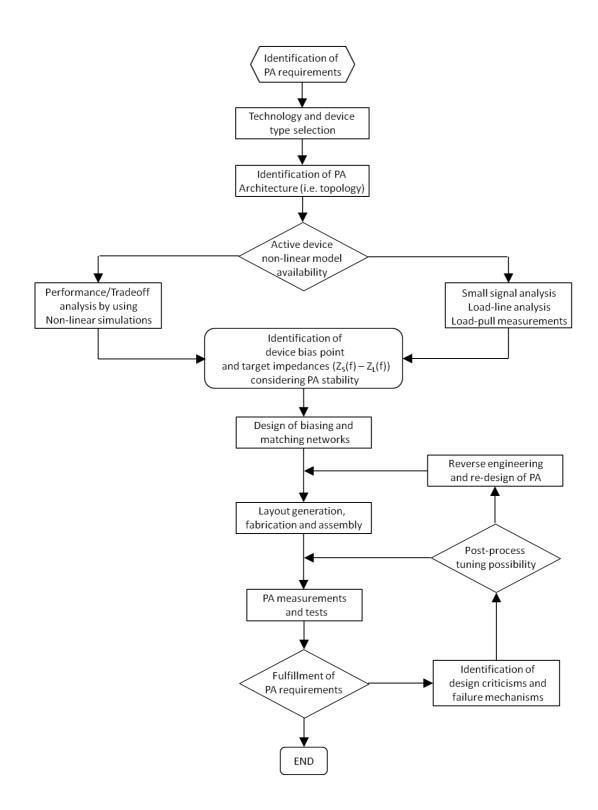

| Figure 3.1 | Typical design steps for the realization of a PA.                                                                                                          | 40 |

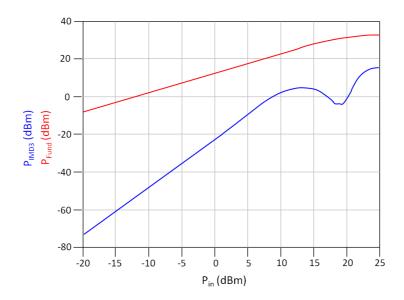

| Figure 3.2 | A sample of generation of a large-signal IMD3 sweet-spot                                                                                                   | 42 |

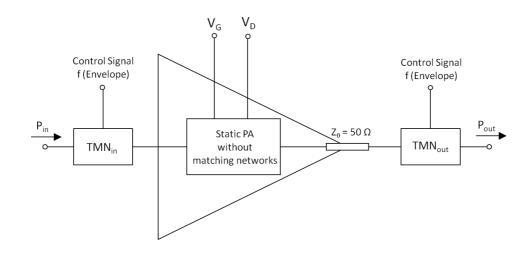

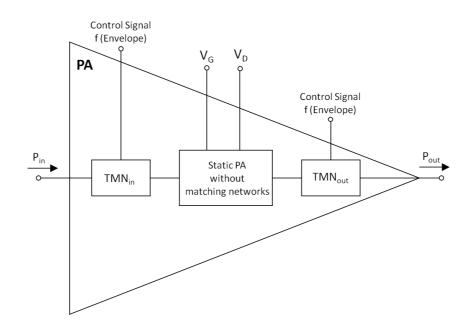

| Figure 3.3 | Schematic of separate design method of PA-TMN                                                                                                              | 44 |

| Figure 3.4 | Schematic of co-design (integrated) method of PA-TMN                                                                                                       | 45 |

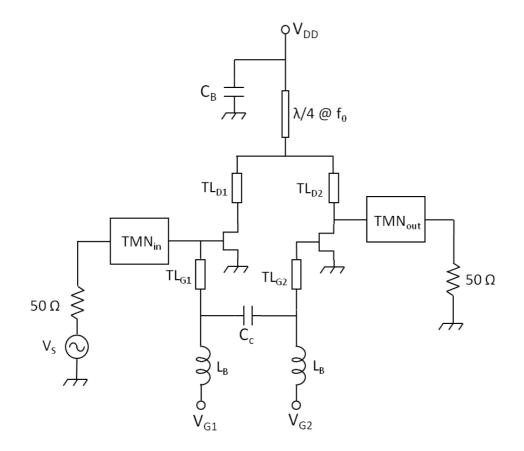

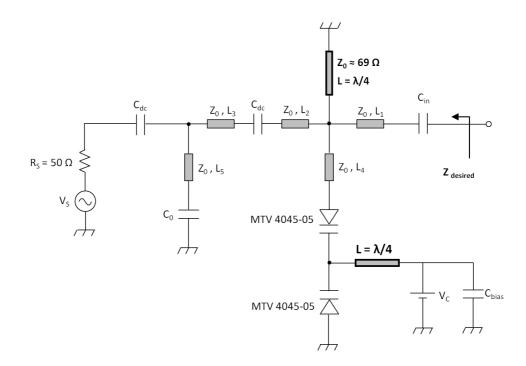

| Figure 3.5 | Schematic of the proposed PA                                                                                                                               | 46 |

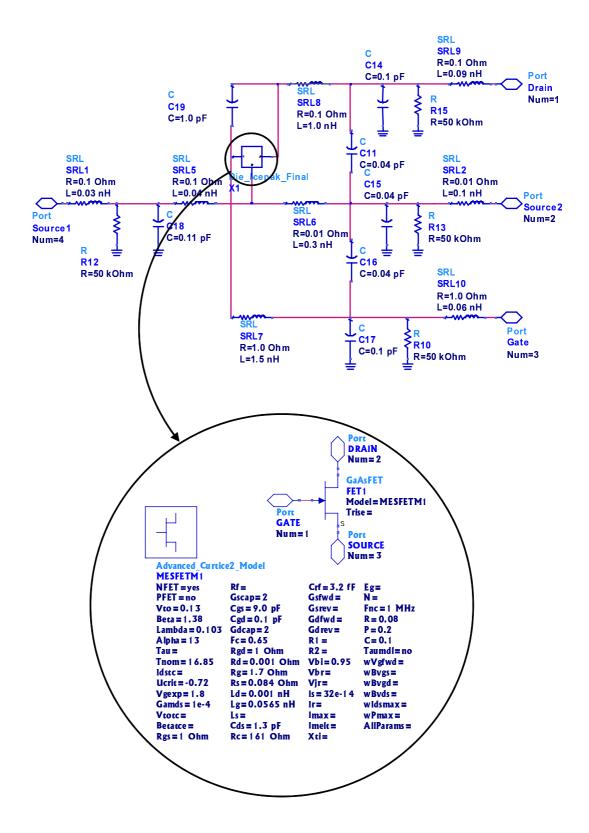

| Figure 3.6 | Nonlinear model of ATF-50189 provided by Avago Tech for ADS users                                                                                          | 47 |

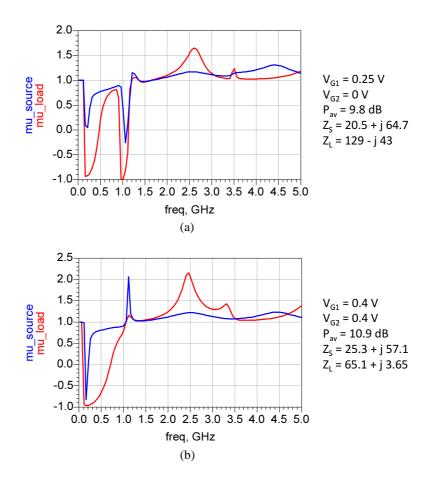

| -          | Samples of stability factor curves as a function of frequency for two bias point sets                                                                      |    |

| of (a)     | $V_{G1} = 0.25 V$ , $V_{G2} = 0 V$ and (b) $V_{G1} = 0.4 V$ , $V_{G2} = 0.4 V$                                                                             | 49 |

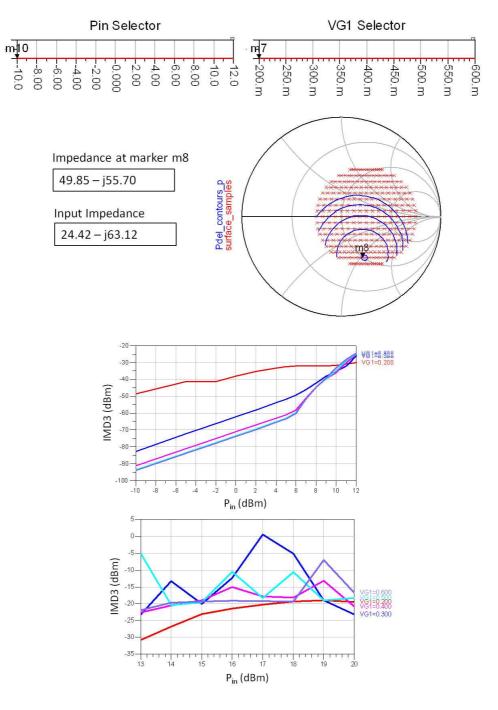

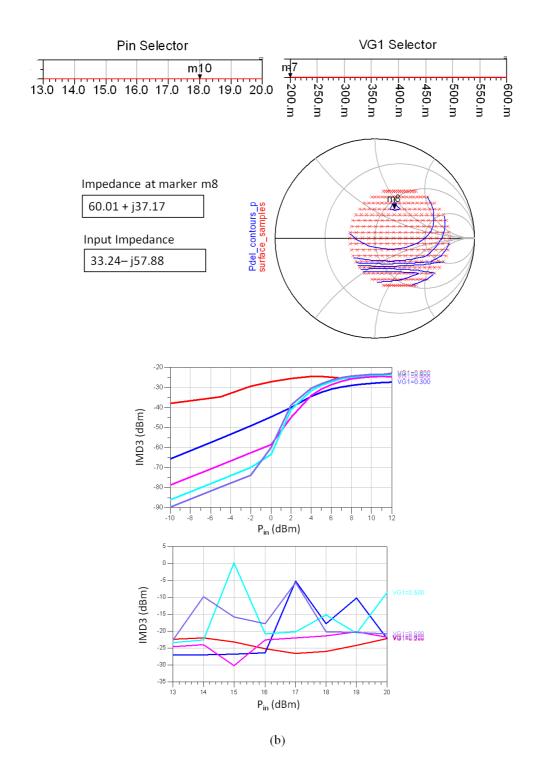

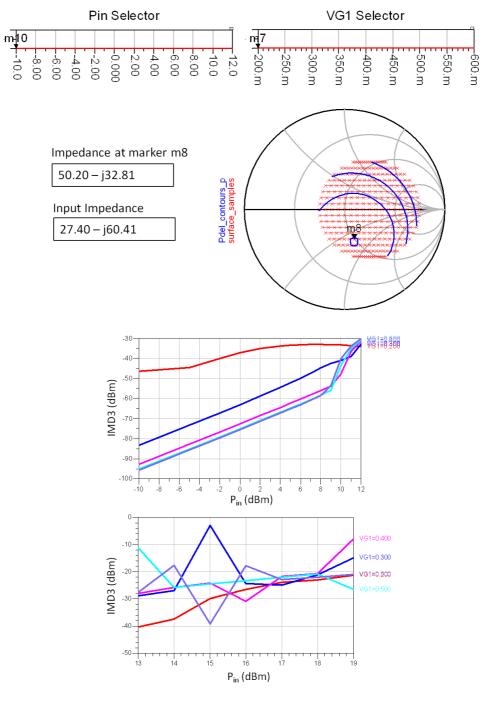

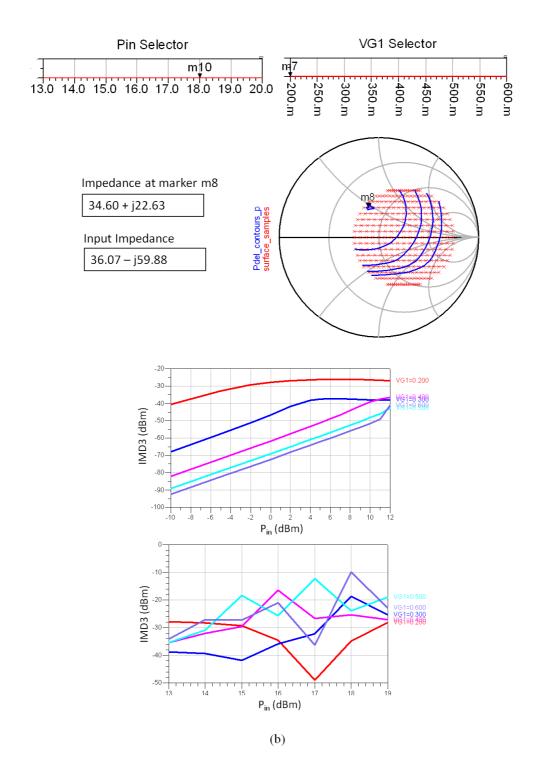

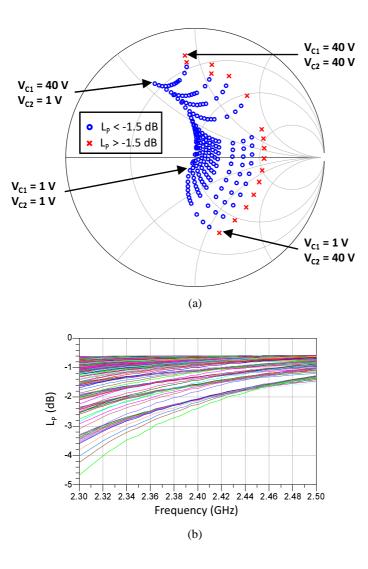

| -          | Sample results of the two-tone load-pull simulation for $V_{G2} = 0$ V at two optimum alues for (a) low and (b) high input power regions.                  | 52 |

| Figure 3.9 | Sample results of the two-tone load-pull simulation for $V_{G2} = 0.6$ V at two optimum                                                                    |    |

| load v     | alues for (a) low and (b) high input power regions                                                                                                         | 54 |

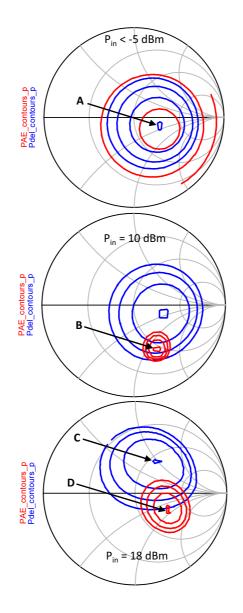

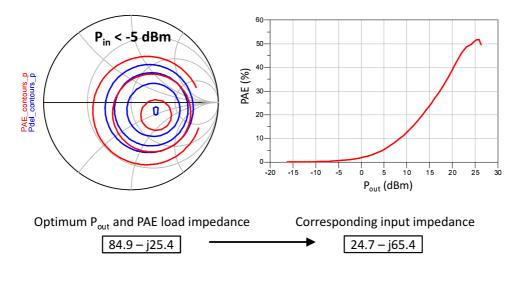

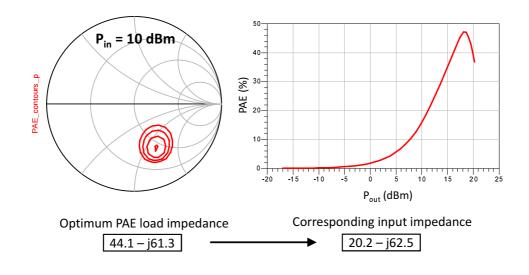

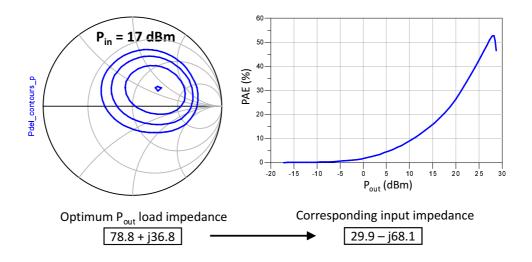

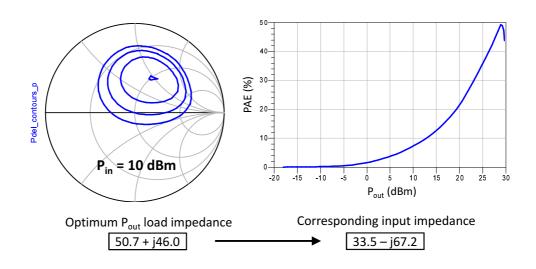

| Figure 3.10 Power and PAE contours after the load-pull analysis at different input powers                                                                                   | 56 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

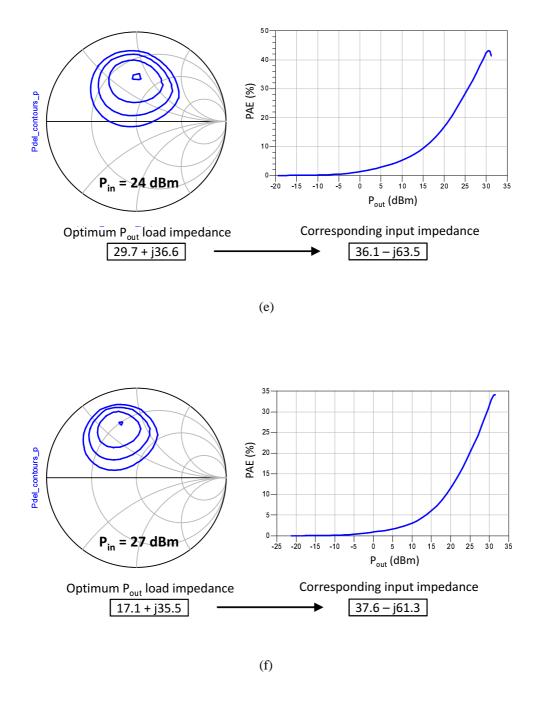

| Figure 3.11 Optimum load impedances and resulting PAE curves while input power in which the optimum load is derived increased from less than -5 dBm in (a) to 27 dBm in (f) | 60 |

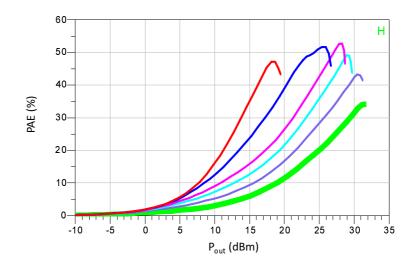

| Figure 3.12 PAE curves of the load points of Figure 3.11 drawn on a common axis for compari-<br>son purposes.                                                               | 61 |

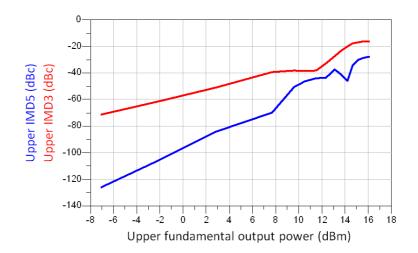

| Figure 3.13 Upper third and fifth order IMD of the first operational <i>state</i> of the amplifier                                                                          | 61 |

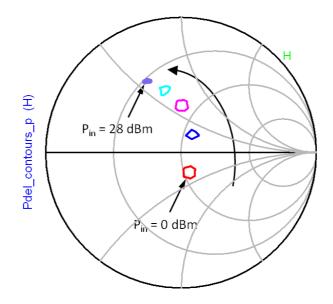

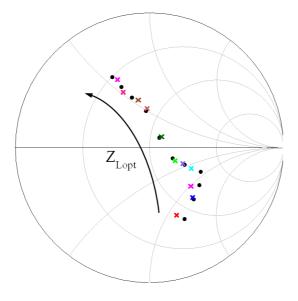

| Figure 3.14 Optimum load impedance and its movement as the driving power increases                                                                                          | 62 |

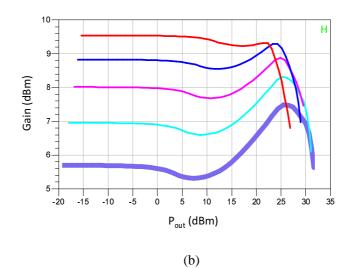

| Figure 3.15 Efficiency plots of the 5 sample operational states for the gate bias points of $V_{G1} = 0.25$ V and $V_{G2} = 0.3$ V                                          | 63 |

| Figure 3.16 Gain plots of the two cases studied before: (a) 6 states of $V_{G1} = 0.25$ V and $V_{G2} = 0$ V and, (b) 5 states of $V_{G1} = 0.25$ V and $V_{G2} = 0.3$ V    | 64 |

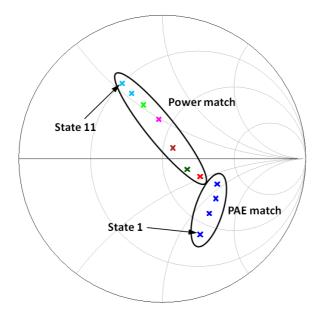

| Figure 3.17 Optimum load impedance points at 11 operational states of the amplifier                                                                                         | 66 |

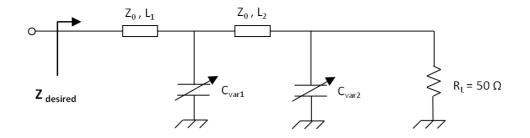

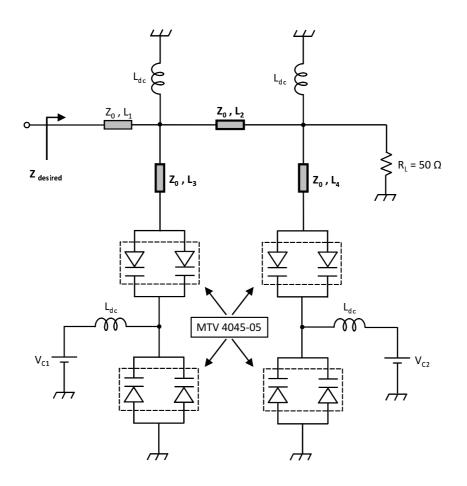

| Figure 3.18 Simplified two-stage network topology for TMN implementation.                                                                                                   | 67 |

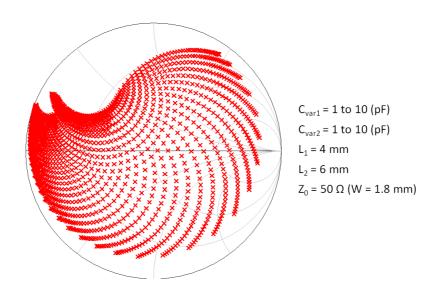

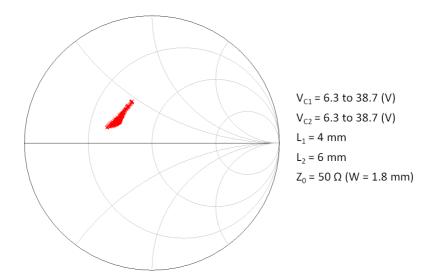

| Figure 3.19 Impedance coverage of the simple two-stage ladder matching network                                                                                              | 67 |

| Figure 3.20 Typical performance of MTV 4045 series varactor diodes [123]                                                                                                    | 69 |

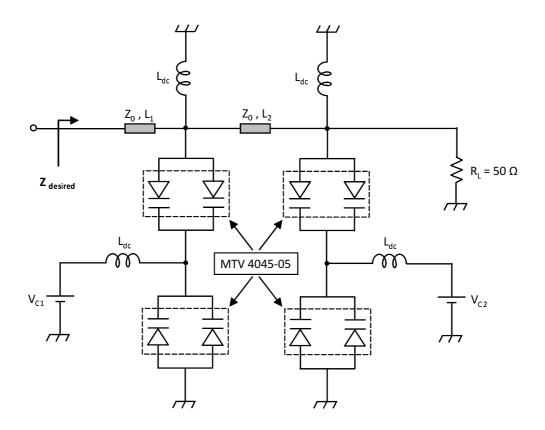

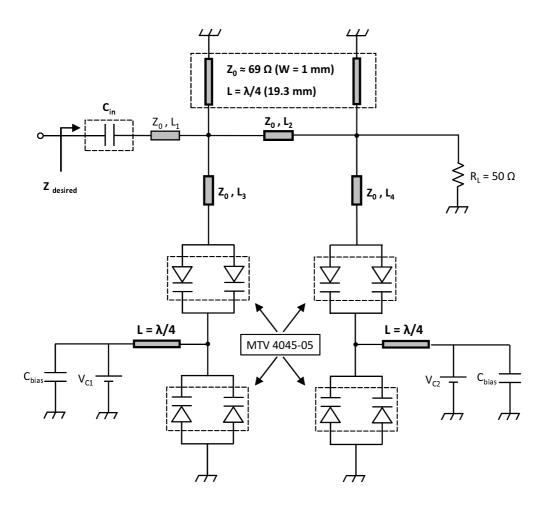

| Figure 3.21 Two-stage ladder TMN with anti-series varactors replaced the capacitors in Figure      3.18.                                                                    | 70 |

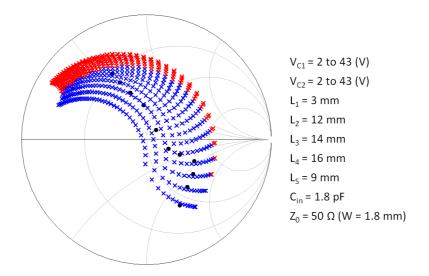

| Figure 3.22 Impedance coverage of the network of Figure 3.21                                                                                                                | 71 |

| Figure 3.23 Two-stage ladder TMN with anti-series varactors and added transmission lines                                                                                    | 72 |

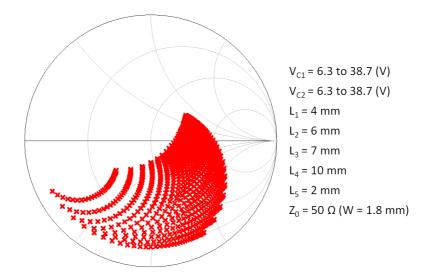

| Figure 3.24 Impedance coverage of the network of Figure 3.23                                                                                                                | 73 |

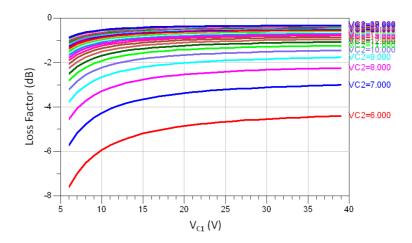

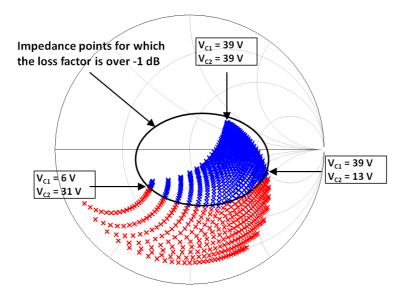

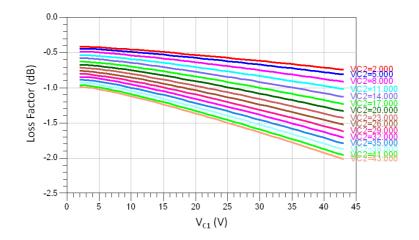

| Figure 3.25 Loss factor of the matching network of Figure 3.23 for small input powers                                                                                       | 73 |

| Figure 3.26 Impedance coverage of the network of Figure 3.23 for small input powers distin-<br>guishing the low-loss and high-loss regions.                                 | 74 |

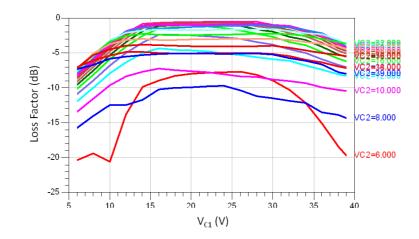

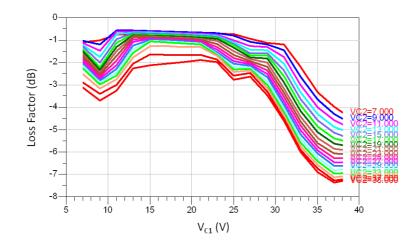

| Figure 3.27 Loss factor of the matching network of Figure 3.23 for the input power of 30 dBm                                                                                | 75 |

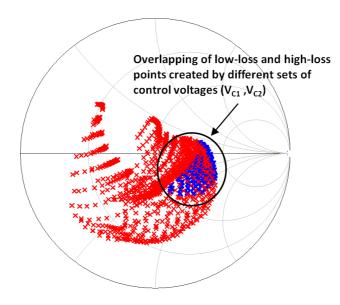

| Figure 3.28 Impedance coverage of the network of Figure 3.23 for the input power of 30 dBm                |            |

|-----------------------------------------------------------------------------------------------------------|------------|

| distinguishing the low-loss and high-loss regions.                                                        | 75         |

| Figure 3.29 Final view of the two-stage ladder TMN with anti-series varactors, added transmis-            |            |

| sion lines and $\lambda/4$ transmission lines for biasing purposes                                        | 76         |

| Figure 3.30 Impedance coverage of the network of Figure 3.29 for small input powers with the              |            |

| given ranges of control voltages and parameter values.                                                    | 77         |

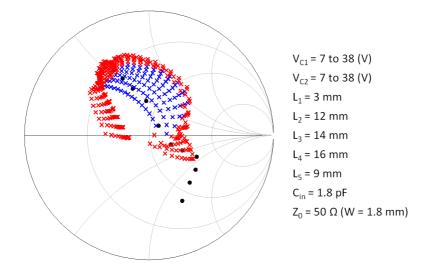

| Figure 3.31 Impedance coverage of the network of Figure 3.29 for the input power of 31 dBm                |            |

| with the given ranges of control voltages and parameter values                                            | 78         |

| Figure 3.32 Loss factor of the matching network of Figure 3.29 for small input powers                     | 78         |

| Figure 3.33 Loss factor of the matching network of Figure 3.29 for the highest input power of             |            |

| 31 dBm                                                                                                    | 79         |

| Figure 3.34 Optimum load impedance points at 11 operational states of the amplifier obtained              |            |

| by varactor-based (colored) and ideal (black) load-tuners.                                                | 80         |

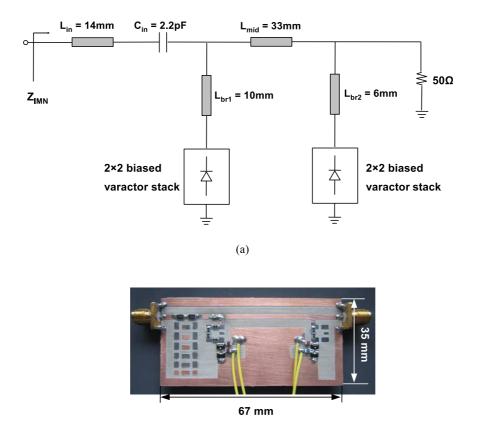

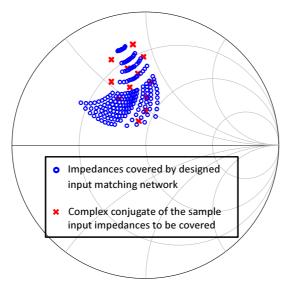

| Figure 3.35 Input tunable matching network                                                                | 81         |

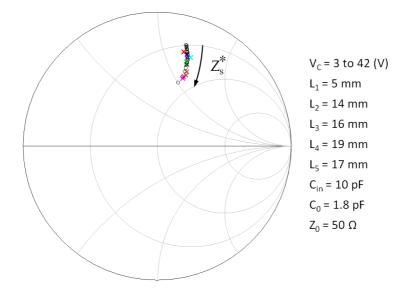

| Figure 3.36 Complex conjugates of the input impedances at 11 operational states of the amplifier          |            |

| together with the coverage area of the input matching network.                                            | 82         |

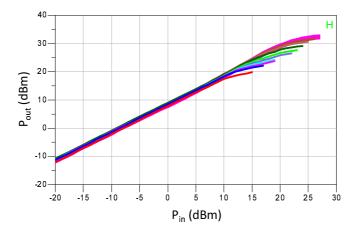

| Figure 3.37 $P_{in}$ - $P_{out}$ characteristic curves of the amplifier at the 11 operational states      | 82         |

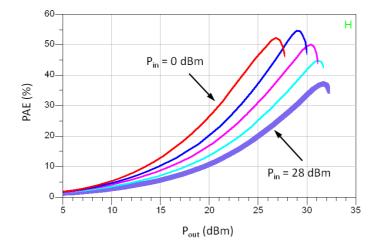

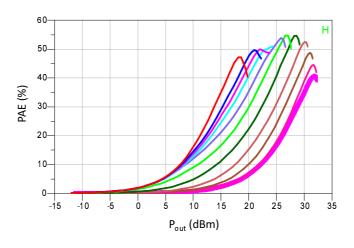

| Figure 3.38 (a) Power added efficiency as a function of the output power at 11 operational states         |            |

| of the amplifier, (b) zoomed view of the PAE where transitions between states at 1 dB                     |            |

| compression points are highlighted                                                                        | 83         |

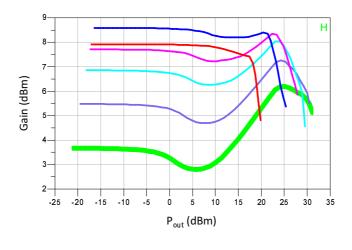

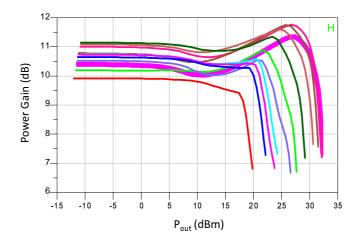

| Figure 3.39 (a) Power gain as a function of the output power at 11 operational states of the              |            |

| amplifier, (b) zoomed view of the gain where transitions between states at 1 dB compression               | <i>c</i> : |

| points are highlighted.                                                                                   | 84         |

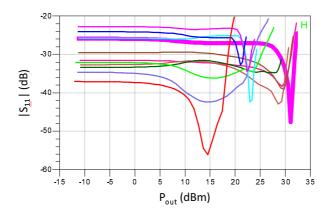

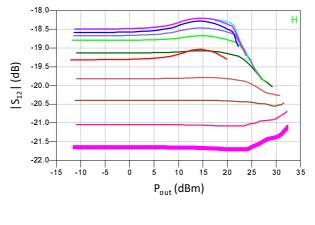

| Figure 3.40 Magnitude in dB of (a) $S_{11}$ , (b) $S_{22}$ and (c) $S_{12}$ as a function of output power | 86         |

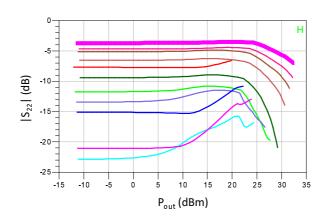

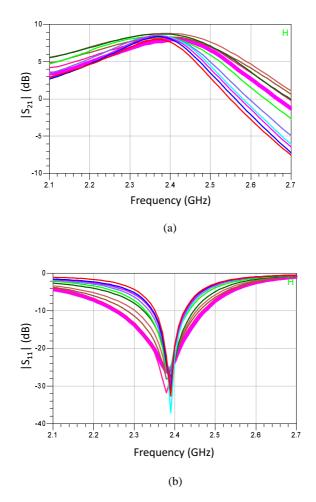

| Figure 3.41 Magnitude in dB of (a) $S_{21}$ , (b) $S_{11}$ and (c) $S_{22}$ as a function of frequency.   | 88         |

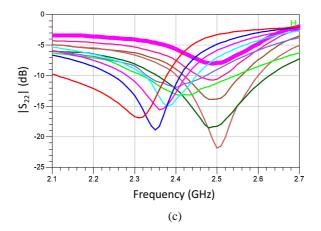

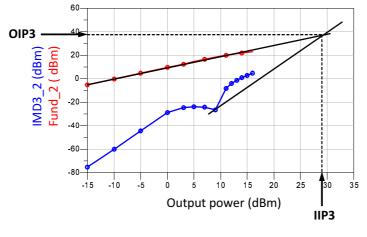

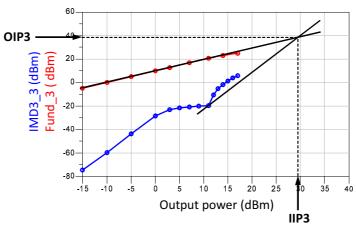

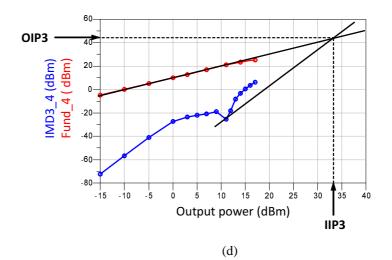

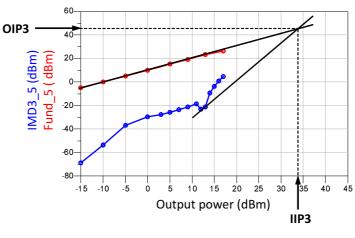

| Figure 3.42 (a) Third and (b) fifth order intermodulation products as a function of fundamental                                                                            |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| output power                                                                                                                                                               | 89  |

| Figure 4.1 Fixture for testing the transistors before mounting on the main board                                                                                           | 92  |

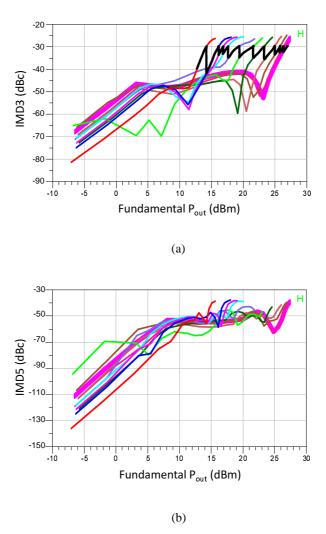

| Figure 4.2 Comparing the measured and datasheet S-parameters of a single ATF-50189 tran-<br>sistor under the biasing condition of $V_{DS} = 4.5$ V and $I_{DS} = 280$ mA   | 93  |

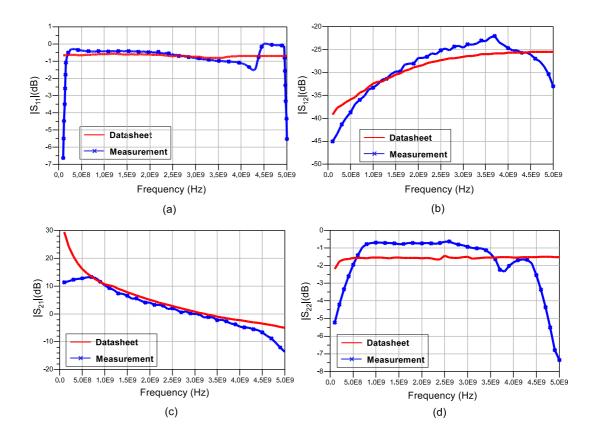

| Figure 4.3 (a) Schematic and (b) fabricated testing board of a single transistor with gate and                                                                             | 0.4 |

| drain biasing lines                                                                                                                                                        | 94  |

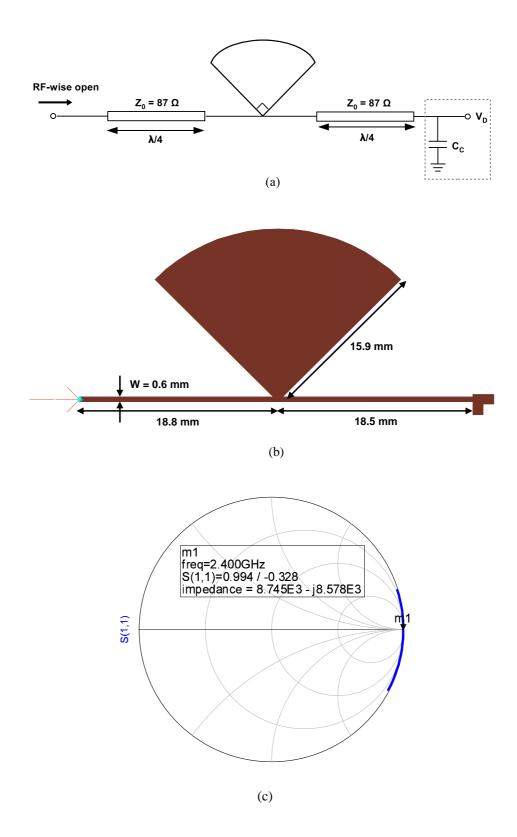

| Figure 4.4 (a) Schematic, (b) ADS Momentum layout and (c) input reflection coefficient of the radial stub biasing structure for the drain.                                 | 95  |

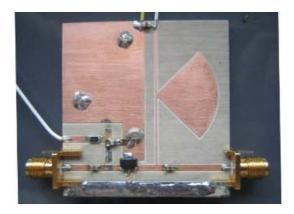

| Figure 4.5 Fabricated circuit of the single transistor amplifier with radial stub drain biasing and three solder-filled via holes.                                         | 96  |

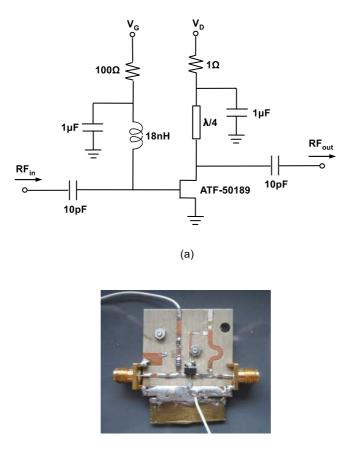

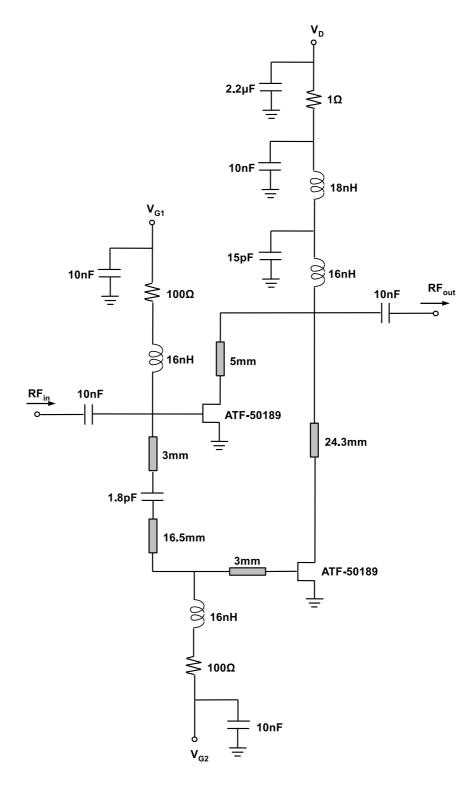

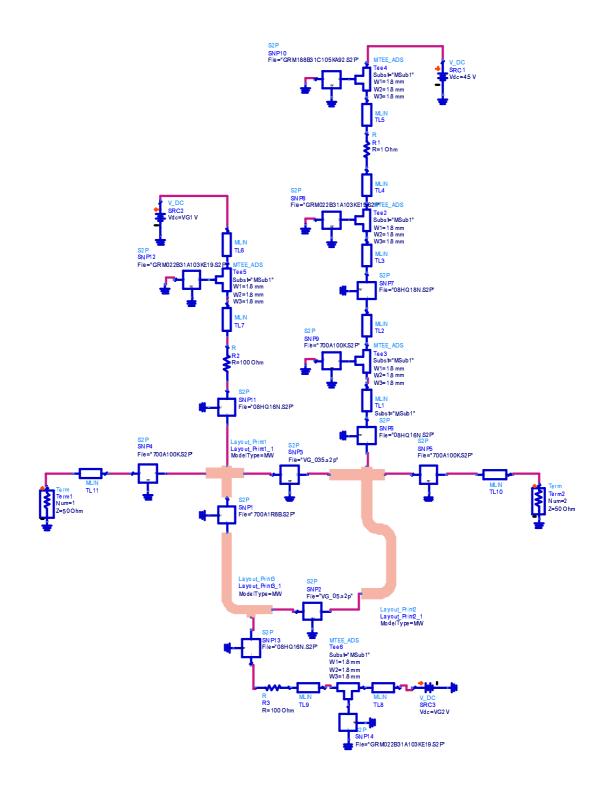

| Figure 4.6 (a) Schematic and (b) fabricated circuit of the two-transistor amplifier proposed in this thesis.                                                               | 98  |

| Figure 4.7 Momentum layout view of transmission lines connected to the gates and drains of the two transistors.                                                            | 98  |

| Figure 4.8 Simulated amplifier circuit in the schematic window of ADS where the critical trans-<br>mission lines connecting the two transistors are analysed in Momentum.  | 99  |

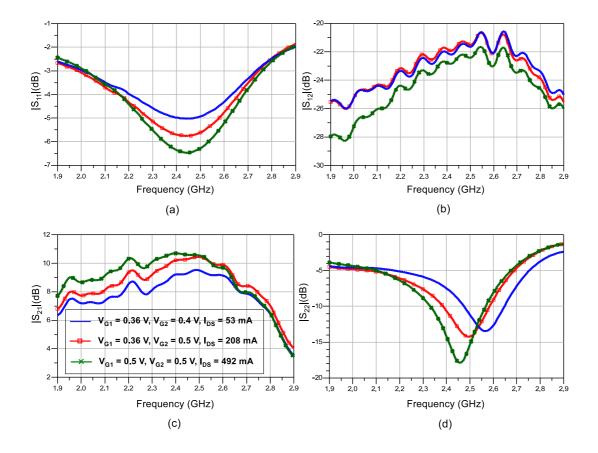

| Figure 4.9 Measured S-parameters of the amplifier of Figure 4.6 at three different bias points                                                                             | 100 |

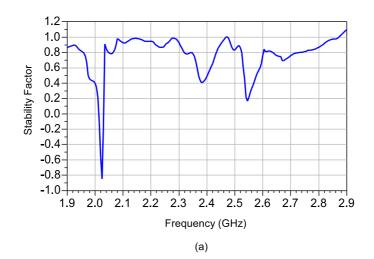

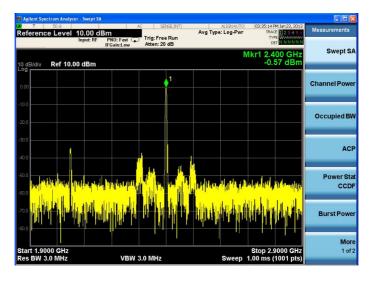

| Figure 4.10 (a) Stability factor and (b) output power spectrum of the amplifier for $V_{G1} = 0.3 \text{ V}$<br>and $V_{G2} = 0.25 \text{ V}$ .                            | 101 |

| Figure 4.11 (a) Schematic and (b) fabricated board of the varactor stack characterization module.                                                                          | 102 |

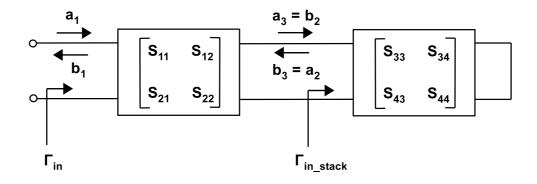

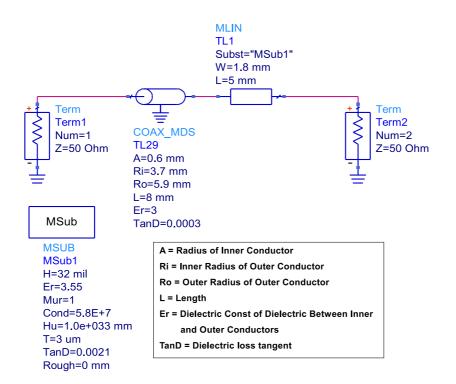

| Figure 4.12 Series connection of two networks terminated with short circuit representing the characterization board of varactor stack.                                     | 103 |

| Figure 4.13 Simulated two port network consisting of the connector and transmission line to be de-embedded from the measured S-parameters of network shown in Figure 4.11. | 104 |

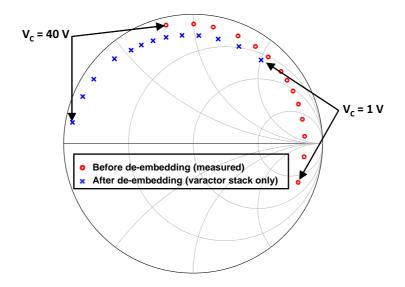

| Figure 4.14 Input impedance points before and after de-embedding the effect of input line and connector                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

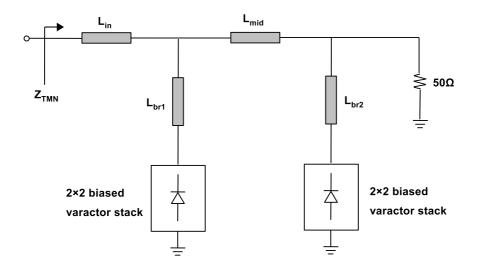

| Figure 4.15 Schematic of the load-tuner showing the critical transmission line segments to be                                           |

| tuned                                                                                                                                   |

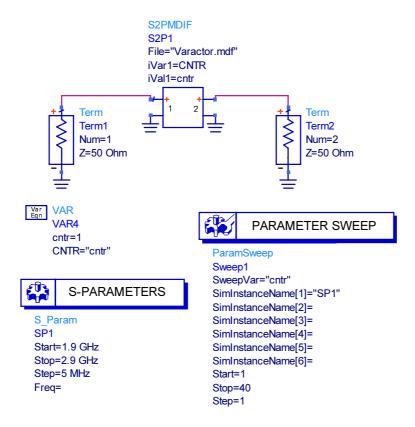

| Figure 4.16 Sample ADS schematic showing how to employ an S2PMDIF data item in order to                                                 |

| sweep between several s2p data                                                                                                          |

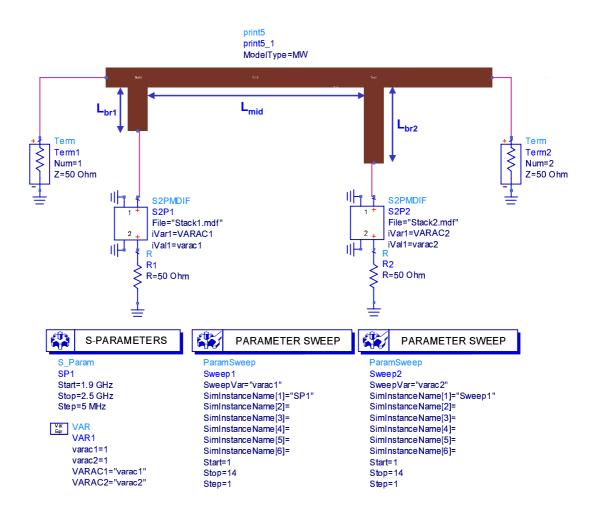

| Figure 4.17 Load-tuner simulation setup in ADS showing S2PMDIF components for each var-                                                 |

| actor stack and the imported layout of the intervening transmission lines                                                               |

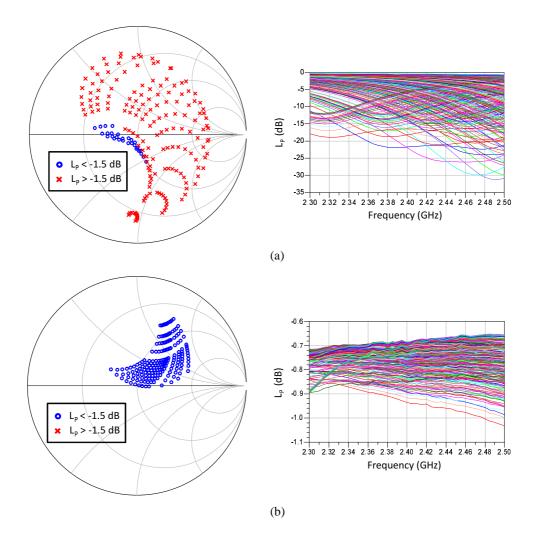

| Figure 4.18 (a) Covered area and (b) loss of the load-tuner for transmission line lengths of $L_{in}$ =                                 |

| 32 mm, $L_{mid} = 16$ mm, $L_{br1} = 7$ mm, $L_{br2} = 6$ mm                                                                            |

| Figure 4.19 (a) Covered area and loss of the load-tuner for transmission line lengths of $L_{in}$ =                                     |

| 30 mm, $L_{mid}$ = 12 mm, $L_{br1}$ = 20 mm, $L_{br2}$ = 25 mm; (b) Covered area and loss of the                                        |

| load-tuner for transmission line lengths of $L_{in} = 10 \text{ mm}$ , $L_{mid} = 32 \text{ mm}$ , $L_{br1} = 8 \text{ mm}$ , $L_{br2}$ |

| = 7 mm                                                                                                                                  |

| Figure 4.20 Fabricated circuit of the load-tuner or output matching network as a separate module                                        |

| from the amplifier                                                                                                                      |

| Figure 4.21 Measurement of the S-parameters of the amplifier with load-tuner connected 110                                              |

| Figure 4.22 Covered area of the impedances seen from the input of the amplifier at different bias                                       |

| and load values                                                                                                                         |

| Figure 4.23 (a) Schematic and (b) fabricated circuit of the input tunable matching network 112                                          |

| Figure 4.24 (a) Covered area and (b) loss of the input tunable matching network                                                         |

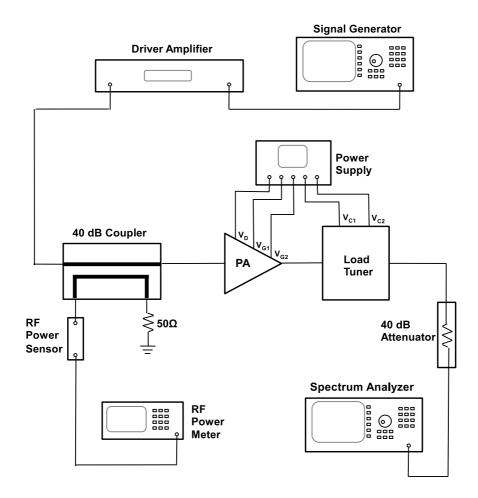

| Figure 4.25 (a) Schematic and (b) on-site photograph of the load-pull measurement setup in                                              |

| ASELSAN                                                                                                                                 |

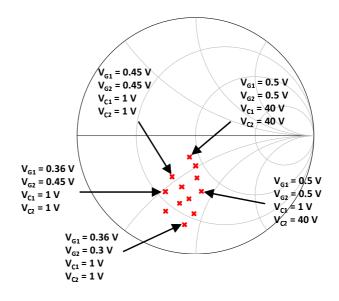

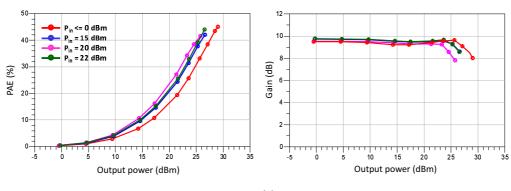

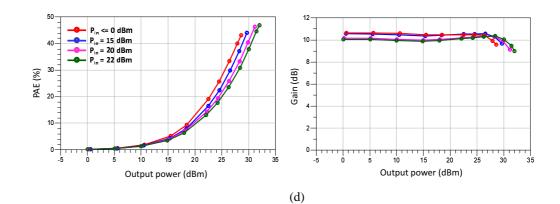

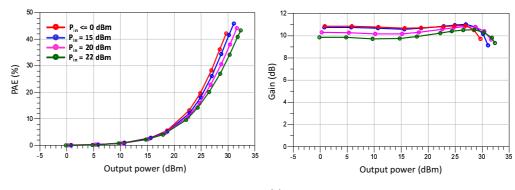

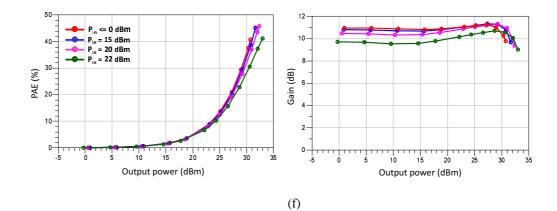

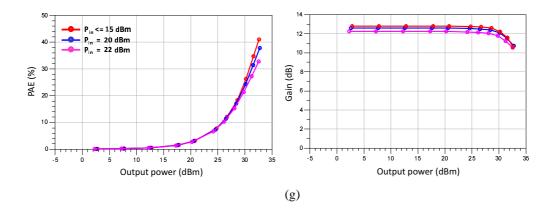

| Figure 4.26 Measured PAE and Gain curves for (a) PAE matching with $V_{G1}$ = 0.36 V and $V_{G2}$                                       |

| = 0.35 V, and Power Matching with (b) $V_{G1}$ = 0.36 V and $V_{G2}$ = 0.35 V, (c) $V_{G1}$ = 0.36 V                                    |

| and $V_{G2} = 0.4$ V, (d) $V_{G1} = 0.36$ V and $V_{G2} = 0.45$ V, (e) $V_{G1} = 0.36$ V and $V_{G2} = 0.5$ V,                          |

| (f) $V_{G1} = 0.36$ V and $V_{G2} = 0.55$ V, (g) $V_{G1} = 0.55$ V and $V_{G2} = 0.55$ V                                                |

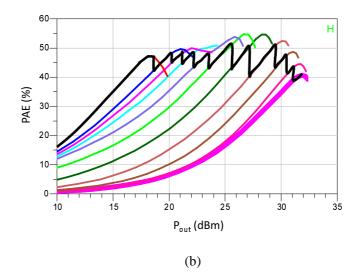

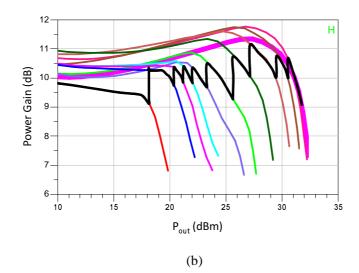

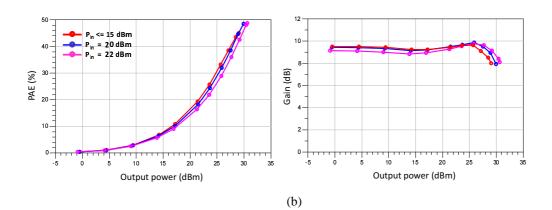

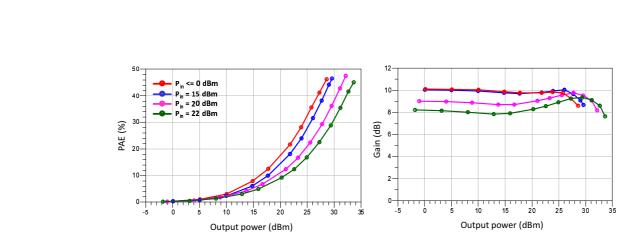

| Figure 4.27 Measured (a) PAE and (b) power gain of the amplifier at 7 selected operational states. 121 |

|--------------------------------------------------------------------------------------------------------|

| Figure 4.28 Producing two-tone signal using two separate signal generators; (a) connection of          |

| the two devices using coaxial T junction, (b) adjusting the signal generators to create two            |

| signals at 2399 MHz and 2401 MHz, (c) spectrum analyzer view of the created two-tone                   |

| signal                                                                                                 |

| Figure 4.29 Measurement results of the upper 3rd order intermodulation distortion of the ampli-        |

| fier at 7 selected operational states                                                                  |

| Figure 4.30 Fundamental and IMD3 curves plotted as functions of the input power for finding            |

| the third order intercept points from the locations of the sweet spots at (a) state 1 up to (f)        |

| state 6                                                                                                |

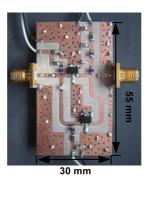

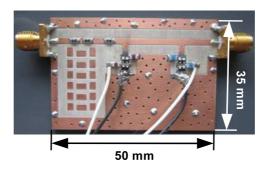

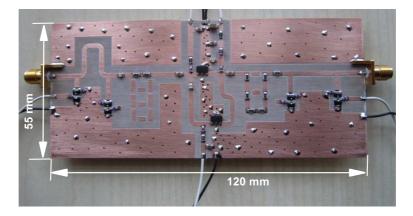

| Figure 4.31 Fabricated amplifier with tunable input and output matching networks integrated on         |

| a common board                                                                                         |

## **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 Linearity and Efficiency in PA Design for Wireless Communications

In modern communication systems like WLAN and CDMA, spectrum is expensive and newer technologies demand transmission of maximum amount of data using the minimum amount of spectrum. Higher spectrum efficiency can be attained by sophisticated non-constant envelope digital modulation schemes such as Quadrature Amplitude Modulation (QAM) and Quadrature Phase Shift Keying (QPSK). In these linear modulation schemes information is transmitted in both the amplitude and phase of the RF signal leading to high Peak to Average Power Ratios (PAPR) [1].

The PAPR of the spectrally efficient modulation formats in use today is about 4-9 dB in CDMA 2000 systems, and can be of the order of 10 dB in IEEE 802.11 d g wireless LAN systems [2]. Table 1.1 lists the characteristics of several popular cellular standards. These standards employ modulation methods that increase the peak to average power of the transmitted signal in proportion to the number of channels being transmitted [3].

| Communications<br>Standard | Modulation<br>Scheme         | PAPR (dB) |

|----------------------------|------------------------------|-----------|

| CDMA                       | QPSK/OQPSK                   | 9 to 10   |

| WCDMA                      | QPSK                         | 8 to 9    |

| TDMA                       | π/4 DQPSK                    | 3 to 4    |

| GSM/EDGE                   | GMSK<br>8-PSK (in EDGE only) | 1 to 2    |

Table1.1: Popular cellular phone standards [3].

The large PAPR of these modulation schemes implies the large envelope fluctuations by time which must be preserved in order to save the full information content of the original message signal. Hence the RF power amplifier as the vital part of any wireless transmitter has to be highly linear, to achieve a high bit error rate, and limit spectral regrowth to acceptable levels. Although linear amplification is achievable, it always comes at the expense of efficiency. Since the RF power amplifiers implemented in such systems are 'backed off' from their saturation into their linear operating region or designed to operate in Class A or AB configurations in order to obtain a satisfactory linearity over the transmitter's dynamic range.

This drastically reduces the efficiency of the power amplifier decreasing the battery life of the handset in mobile systems. On the other hand, as the demand for a longer talk time with less battery volume and weight in hand-held radio units increases, more power efficient techniques are clearly needed since a large portion of battery power is dissipated by these amplifiers. A higher efficiency gives a longer battery lifetime and thus a longer talk time of the mobile device [4]. Before any further proceeding, it is necessary to review the definition of 'efficiency' in the PA design. There are two typical definitions for the efficiency in RF PAs [1]: 'output efficiency' and 'power added efficiency'. Output efficiency is defined as the ratio of the RF output power  $P_{out}$  to the dc power  $P_{dc}$ :

$$\eta = \frac{P_{out}}{P_{dc}} \tag{1.1}$$

However, the above definition does not take into account the input power  $P_{in}$  and power gain G, whose effects are significant in RF PAs. This results in the definition of *Power Added Efficiency (PAE)*:

$$PAE = \frac{P_{out} - P_{in}}{P_{dc}}$$

(1.2)

$$= \frac{P_{out} - P_{out}/G}{P_{dc}}$$

$$= \eta \cdot \left(1 - \frac{1}{G}\right)$$

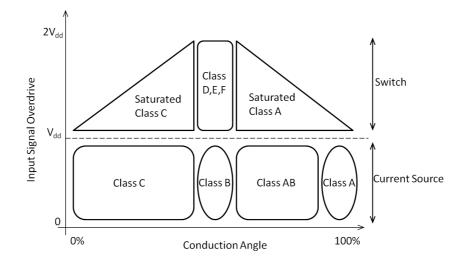

According to their maximum possible efficiencies as shown in Table 1.2, RF power amplifiers can be classified as Class A, AB, B, C, D, E, and F [1], [8]. Figure 1.1 relates the different operational classes of power amplifiers to the conduction angle and input signal overdrive [5].

Table1.2: Comparison of peak possible efficiency for different classes of power amplifiers.

| Classification         | Α  | AB        | В    | С   | D   | Е   | F   |

|------------------------|----|-----------|------|-----|-----|-----|-----|

| Maximum Efficiency (%) | 50 | 50 ~ 78.5 | 78.5 | 100 | 100 | 100 | 100 |

For small input signals, the PA can operate in class A, AB, B or C, depending on the conduction angle. The conduction angle is determined primarily by the DC gate bias. The efficiency can be improved by reducing the conduction angle and moving in the direction of class C at the expense of lower output power. An alternative is to increase the gate overdrive until the PA operates as a switch, while keeping the same conduction angle. This results in operational classes of D, E and F with the efficiency that ideally approaches to 100%. However, the performance of these high-efficiency amplifiers is often non-linear, resulting in significant out-of-band radiation and interference in adjacent channels [5].

Figure 1.1: Definition of PAs based on conduction angle and signal overdrive.

Further study of different classes of PAs is fully available in the literature and is beyond the scope of this dissertation.

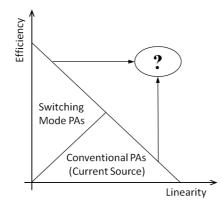

To sum up, improved linearity and efficiency of a communication system have always been conflicting requirements demanding innovative power amplifier design techniques (Figure 1.2). Reported schemes targeted toward improving the efficiency of RF PAs can be broadly classified in two categories, which are: 1) linear PAs with an efficiency-enhancement circuit and 2) non-linear PAs with a linearization circuit.

Figure 1.2: Efficiency and linearity trade-off in RF power amplifiers.

Those techniques which improve efficiency without attempting to quantify the impact on linearity or RF power output are of paramount importance in mobile systems, where battery lifetime and thermal management are critical. However, there are other power amplifier applications where efficiency becomes an important, but secondary consideration, in comparison to linearity. Such applications would

typically be single or multichannel base-station transmitters in ground or satellite communications systems [1].

#### 1.2 Linear Power Amplifiers with an Efficiency-Enhancement Circuit

Power amplifiers are the bottleneck of RF power consumption in handsets. A typical Class AB power amplifier consumes more power than a transmitter IC and therefore the power amplifier is the biggest RF dc power consumer in handsets. Since the dc power consumption remains constant at the low power region, the efficiency of the power amplifier is degraded as the RF output power decreases. Furthermore, more than 90 percent of the output power occurs between -15 dBm and +15 dBm, where the efficiency is low. As a result, average power efficiency (over the full range of output powers), instead of peak power efficiency, is the key factor determining the battery life and talk time for portable wireless applications [6].

An implementation of efficiency enhancement technique that results in a very high efficiency in the linear region of operation of the power amplifier proved to be a good solution for the problem of linearity and efficiency contradiction. The techniques to enhance the efficiency of linear power amplifiers assume immense significance in modern wireless systems. Several efficiency enhancement techniques have been suggested to date. Envelope Elimination and Restoration, Envelope Tracking, Outphasing technique known as LInear amplification using Nonlinear Components (LINC), Doherty amplifier and Dynamic Biasing are the most common methods of enhancing the efficiency which are going to be investigated briefly in the following.

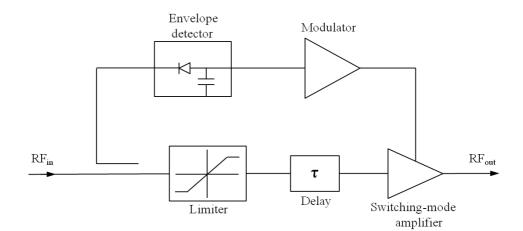

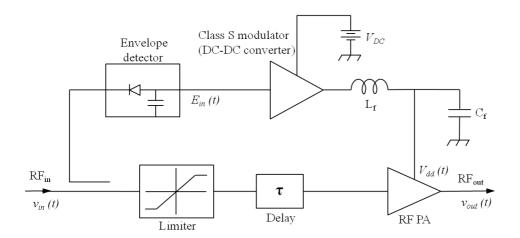

#### 1.2.1 Envelope Elimination and Restoration

The Envelope Elimination and Restoration (EER), known as the Kahn technique, is one of the oldest methods originally proposed by Kahn [7] in 1952 as a more efficient alternative to linear Class AB RF power amplification for single sideband (SSB) transmitters. The general principle is to provide a highly efficient and linear power amplification by combining a highly efficient switching-mode amplifier with a linear low-frequency amplifier (modulator). It combines a highly efficient, but nonlinear RF PA with a highly efficient envelope amplifier to implement a high-efficiency linear RF PA [8].

In its classic form as shown in Figure 1.3, the RF input signal is divided by a power splitter and fed into two branches. The signal in the upper branch is detected producing a Base-Band (BB) modulation signal which in turn, modulates the bias voltage of the RF PA.

In the lower branch, a limiter eliminates the envelope and the output signal is now containing only the phase information. Experiencing some delay the constant-amplitude phase modulated carrier is then amplified efficiently by class-C, -D, -E, or -F RF PAs which operate in saturation at all times. The network delay is adjusted to ensure that the group-delay of the BB branch is identical to that of the RF branch, so that the signal is reconstructed properly both in amplitude and phase. The equalization of the time delay between the BB channel and the RF channel is important to be able to amplify signals that contain phase information. Without phase equalization, only the simplest signals can be amplified with low distortion using this scheme. Amplitude modulation of the final RF PA restores the envelope to the phase-modulated carrier creating an amplified replica of the input signal [9]-[10].

Figure 1.3: Envelope Elimination and Restoration system.

Average efficiencies three to five times those of linear amplifiers have been demonstrated from HF to L-band. Furthermore, transmitters based upon the Kahn technique generally have excellent linearity because linearity depends upon the modulator rather than RF-power transistors. In a modern implementation, both the envelope and phase-modulated carrier are generated by a DSP [11].