### DESIGN OF H.264/AVC COMPATIBLE INTRA-FRAME VIDEO ENCODER ON FPGA PROGRAMMABLE LOGIC DEVICES

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

ÖMER GÜNAY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2014

Approval of the thesis:

# DESIGN OF H.264/AVC COMPATIBLE INTRA-FRAME VIDEO ENCODER ON FPGA PROGRAMMABLE LOGIC DEVICES

submitted by ÖMER GÜNAY in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b> |  |

|---------------------------------------------------------------------------------------|--|

| Prof. Dr. Gönül Turhan Sayan                                                          |  |

| Assist. Prof. Dr. Fatih Kamışlı                                                       |  |

| Energiaine Committee Marchan                                                          |  |

| Examining Committee Members:                                                          |  |

| Prof. Dr. Gözde Bozdağı Akar                                                          |  |

| Assist. Prof. Dr. Fatih Kamışlı                                                       |  |

| Assoc. Prof. Dr. Cüneyt Bazlamaçcı                                                    |  |

| Assoc. Prof. Dr. Çağatay Candan<br>Electrical and Electronics Engineering Dept., METU |  |

| İsmail Özsaraç, M.Sc<br>Electronics Design Dept., ASELSAN                             |  |

| Date:                                                                                 |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name : Ömer GÜNAY

Signature :

# ABSTRACT

# DESIGN OF H.264/AVC COMPATIBLE INTRA-FRAME VIDEO ENCODER ON FPGA PROGRAMMABLE LOGIC DEVICES

Günay, Ömer

M.S., Department of Electrical and Electronics Engineering Supervisor: Assist. Prof. Dr. Fatih Kamışlı

September 2014, 131 pages

Video compression is a technique used to reduce the amount of data in a video to limit the amount of storage space and bandwidth it requires. H.264/AVC is a widely used video compression standard developed together by the ISO (International Organization for Standardization) Moving Picture Experts Group (MPEG) and the ITU (International Telecommunication Union) Video Coding Experts Group (VCEG). H.264/AVC offers an extended range of algorithms for coding digital video to achieve superior compression efficiency with respect to previous standards, which increases computational complexity of H.264/AVC encoders and decoders.

In this thesis, an H.264/AVC compatible intra-frame video encoder is designed and implemented on FPGA devices. First, a reference encoder which includes encoding algorithms such as intra prediction, intra mode selection, transform, quantization and entropy coding, are implemented and tested in MATLAB environment. Then, the reference encoder is coded in VHDL language and tested using the Mentor Graphics Modelsim HDL simulation tool. Next, the overall FPGA implementation is tested by

putting the H.264 coded bitstream into transport stream packets, streaming with UDP over Ethernet and decoding with VLC Player software on a PC. All video resolutions and frame rates defined in H.264 standard are supported by the implemented encoder.

Keywords: Video Coding, H.264, FPGA, Intra Prediction, Integer Transform, Quantization, Exponential-Golomb Coding, CAVLC

# FPGA PROGRAMLANABİLİR ENTEGRELERİ ÜZERİNDE H.264/AVC UYUMLU INTRA-ÇERÇEVE VİDEO KODLAYICI TASARIMI

Günay, Ömer

# Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Yard. Doç. Dr. Fatih Kamışlı

### Eylül 2014, 131 sayfa

Video sıkıştırma, bir video içerisindeki veri miktarını azaltarak o videonun saklanması için gerekli depolama alanını veya iletimi için gerekli bant genişliğini sınırlandırmak için kullanılan bir tekniktir. H.264/AVC Uluslararası Standartlar Teşkilatı (ISO) bünyesindeki Hareketli Görüntü Uzmanları Grubu (MPEG) ve Uluslararası Telekomünikasyon Birliği (ITU) bünyesindeki Video Kodlama Uzmanları Grubu tarafından ortaklaşa geliştirilmiş, geniş çapta kullanım alanına sahip bir video sıkıştırma standardıdır. H.264/AVC önceden oluşturulmuş standartlarla karşılaştırıldığında daha gelişmiş algoritmalar içerir ve bu standartlara göre videoyu daha etkin bir şekilde sıkıştırabilir. Bununla birlikte, artan işlem miktarı H.264 uyumlu kodlayıcı ve çözücü tasarımlarını daha zor bir hale getirmiştir.

Bu çalışmada, FPGA entegreleri üzerinde H.264/AVC uyumlu intra-çerçeve video kodlayıcı tasarlanmıştır. İlk etapta, intra kestirim, intra mod seçim, dönüşüm, niceleme ve entropi kodlama gibi kodlayıcı algoritmaları MATLAB ortamında oluşturulmuş ve test edilmiştir. Daha sonra MATLAB ortamında oluşturulmuş bütün kodlar, VHDL donanım tanımlama dilinde yazılmıştır ve VHDL kodları Mentor

Graphics firmasına ait Modelsim simülasyon yazılımı kullanılarak test edilmiştir. Donanım testleri esnasında kodlanmış bit katarı ilk önce TS (Transport Stream) paketi haline getirilmiş, daha sonra da UDP protokolünde Ethernet üzerinden aktarılmıştır. En son aşamada ise, H.264 kodlanmış bit katarı VLC Player yazılımı kullanılarak başarılı bir şekilde çözümlenmiştir. Tasarlanan kodlayıcı H.264 standardı tarafından desteklenen bütün seviyeleri desteklemektedir.

Anahtar Kelimeler: Video Kodlama, H.264, FPGA, Intra Kestirim, Tamsayı Dönüşüm, Niceleme, Exponential-Golomb Kodlama, CAVLC

To My Mother and Father...

# ACKNOWLEDGMENTS

Firstly, I would like to thank to my supervisor, Assist. Prof. Dr. Fatih Kamışlı, for his support throughout my master study.

I would like to thank to Yüksel Serdar, Hüseyin Atik, Engin Çağlav and İsmail Özsaraç in ASELSAN for their support and help.

I would like to thank to İsmail Özsaraç for his valuable discussion, experience and help during FPGA implementation process.

I would like to thank to İsmail Özsaraç and Erkan Yavuz for his support to implement the test setup.

I would like to thank Ömer Lütfi Nuzumlalı for his assistance during thesis writing.

I also would like to thank to Aselsan Inc., Middle East Technical University and Ministry of Science, Industry and Technology for supporting the project under SANTEZ program.

I would like to thank my father Zübeyir Günay, my mother Necla Günay and my brother Bülent Günay for their infinite support, they are the people who make me as the person I currently am.

# **TABLE OF CONTENTS**

| ABSTRACT v                            |

|---------------------------------------|

| ÖZvii                                 |

| ACKNOWLEDGMENTS x                     |

| TABLE OF CONTENTSxi                   |

| LIST OF TABLES                        |

| LIST OF FIGURESxvii                   |

| ABBREVIATIONS xx                      |

| CHAPTERS1                             |

| 1 INTRODUCTION 1                      |

| 2 AN OVERVIEW OF H.264/AVC            |

| 2.1 Digital Video Basics              |

| 2.1.1 Digital Video                   |

| 2.1.2 Progressive and Interlaced Scan |

| 2.1.3 Video Format 5                  |

| 2.1.4 Color Spaces                    |

| 2.1.5 Chroma Sampling Formats         |

| 2.1.6 Image Buffering                 |

| 2.2 H.264/AVC VIDEO CODING 10         |

| 2.2.1 H264/AVC Profiles and Levels    |

| 2.2.2 H.264/AVC Encoder Path          |

| 2.2.3 H.264/AVC Decoder Path          |

| 2.3 H.264/AVC Syntax                  |

| 2.3.1    | Video Control NAL Units23                                        |

|----------|------------------------------------------------------------------|

| 2.3.2    | Video Coding Layer NAL Unit24                                    |

| 3 H.264  | AVC ENCODER HARDWARE MODEL AND ENCODER DESIGN                    |

| CRITERIA | A27                                                              |

| 3.1 H    | I.264/AVC Encoder Hardware Model                                 |

| 3.1.1    | Symbol28                                                         |

| 3.1.2    | Pins Description                                                 |

| 3.2 E    | ncoder Design Criteria                                           |

| 4 H.264  | AVC INTRA PREDICTION AND FPGA IMPLEMENTATION                     |

| 4.1 H    | I.264/AVC Intra Prediction                                       |

| 4.1.1    | Luma Prediction                                                  |

| 4.1.2    | Chroma Prediction                                                |

| 4.2 Iı   | ntra Mode Selection                                              |

| 4.2.1    | Rate Distortion Optimized (RDO) Mode Selection47                 |

| 4.2.2    | Luma Mode Selection Algorithm48                                  |

| 4.2.3    | Chroma Mode Selection Algorithm51                                |

| 4.3 F    | PGA Implementation of 4x4 Intra Prediction                       |

| 4.4 F    | PGA Implementation of 4x4 Intra Mode Selection Algorithm60       |

| 4.5 R    | esource Usage Summary of 4x4 Intra Prediction and 4x4 Intra Mode |

| Selectio | n Blocks                                                         |

|          | AVC 4x4 TRANSFORM AND QUANTIZATION AND FPGA<br>ENTATIONS         |

| 5.1 T    | ransform Coding71                                                |

| 5.1.1    | Luma 4x4 Transform Processes72                                   |

| 5.1.2    | Chroma Transform Processes74                                     |

| 5.2 Q    | Quantization75                                                   |

| 5.3 4          | x4 Transform and Quantization Examples7                           | 7  |

|----------------|-------------------------------------------------------------------|----|

| 5.4 F          | PGA Implementation of Transform Coding7                           | 8  |

| 5.5 F          | PGA Implementation of Quantization8                               | 3  |

| 5.5.1          | Forward Quantization8                                             | 3  |

| 5.5.2          | Inverse Quantization                                              | 4  |

| 5.6 F          | Resource Usage Summary of Transform and Quantization              | 7  |

|                | ELINE PROFILE ENTROPY CODING TECHNIQUES AND THEI<br>PLEMENTATIONS |    |

| 6.1 F          | Fixed Length Code                                                 | 0  |

| 6.2 E          | Exponential-Golomb Code                                           | 1  |

| 6.3 C          | Context-based Adaptive Variable Length Code (CAVLC)9              | 13 |

| 6.3.1          | Example CAVLC Coding of a 4x4 Block9                              | 94 |

| 6.4 F          | PGA Implementation of Exponential-Golomb Coding9                  | 7  |

| 6.4.1          | EXP-GOLOMB CODING STATE MACHINE9                                  | 9  |

| 6.4.2          | ROM INTRA CBP10                                                   | 0  |

| 6.4.3          | ROM INTER CBP 10                                                  | 0  |

| 6.4.4<br>Codir | Simulation and Implementation Results of Exponential-Golom        |    |

| 6.5 F          | PGA Implementation of CAVLC 10                                    | 12 |

| 6.5.1          | Zigzag Scan 10                                                    | 6  |

| 6.5.2          | Scanned Data Control 10                                           | 17 |

| 6.5.3          | Total Coeff 10                                                    | 18 |

| 6.5.4          | Total Zeros 10                                                    | 18 |

| 6.5.5          | Run Code Control                                                  | 18 |

| 6.5.6          | Level Code Control                                                | 18 |

| 6.5.7          | Bitstream Control11                                               | 0  |

| 6.5.8 Simulation and Implementation Results of CAVLC Coding Block . | .110 |

|---------------------------------------------------------------------|------|

| 7 HARDWARE IMPLEMENTATION AND RESULTS                               | .115 |

| 7.1 Test Setup                                                      | .115 |

| 7.1.1 Video Source                                                  | .117 |

| 7.1.2 Camera Link Interface                                         | .117 |

| 7.1.3 H.264 Encoder                                                 | .118 |

| 7.1.4 Transport Stream Generator                                    | .118 |

| 7.1.5 Ethernet Interface                                            | .118 |

| 7.2 Results                                                         | .118 |

| 8 CONCLUSIONS AND FUTURE WORK                                       | .121 |

| 8.1 Conclusions                                                     | .121 |

| 8.2 Future Work                                                     | .122 |

| REFERENCES                                                          | .125 |

| APPENDICES                                                          | .127 |

| A. EXPONENTIAL- GOLOMB AND CAVLC CODING TABLES                      | .127 |

# LIST OF TABLES

# TABLES

| Table 2.1 Various Video Formats                                         | 6   |

|-------------------------------------------------------------------------|-----|

| Table 2.2 Some Tools Used In Several H.264 Profiles                     | 11  |

| Table 2.3 Minimum Decoder Levels for Some Video Formats                 | 11  |

| Table 2.4 An Example of SPS Syntax Elements                             | 23  |

| Table 2.5 An Example of PPS Syntax Elements                             | 24  |

| Table 3.1 H.264 Encoder Pins Description                                | 30  |

| Table 4.1 Resource Usage Summary of Intra Prediction and Mode Selection | 67  |

| Table 5.1 Chroma Sampling Formats and Corresponding Block Sizes         | 74  |

| Table 5.2 Multiplication Factor (MF)                                    | 76  |

| Table 5.3 Rescaling Factor (V)                                          | 76  |

| Table 5.4 Block of Luma or Chroma Samples                               | 77  |

| Table 5.5 Results of Each Step (Example)                                | 77  |

| Table 5.6 FPGA Resource Usage Summary of Transform and Quantization     | 87  |

| Table 6.1 H.264 Fixed Length Coding Descriptors                         | 90  |

| Table 6.2 Some Fixed Length Coded Syntax Elements                       | 91  |

| Table 6.3 Exp-Golomb Codewords                                          | 93  |

| Table 6.4 I/O Signal Descriptions of the EXP-GOLOMB CODING Block        | 99  |

| Table 6.5 Exp-Golomb Block Delay for Different Mapping Types            | 102 |

| Table 6.6 FPGA Resource Usage of Exp-Golomb Coding Block                | 102 |

| Table 6.7 I/O Signal Descriptions of the CAVLC CODING Block             | 105 |

| Table 6.8 4x4 Zigzag Scan Order                                         | 107 |

| Table 6.9 4x4 Zigzag Scan Order                                         | 107 |

| Table 6.10 FPGA Resource Usage of CAVLC Coding Block                    | 114 |

| Table 7.1 Bitrate Comparison of Three Encoder Models                    | 120 |

| Table 7.2 Resource Usage of Implemented H.264 Encoder                   | 120 |

| Table A-1 CBP Table (ChromaArrayType is Equal to 1 or 2)                | 127 |

| Table A-2 CBP Table (ChromaArrayType is Equal to 0 or 3)                | 128 |

| Table A-3 Total Coeff Tables                                             | .129 |

|--------------------------------------------------------------------------|------|

| Table A-4 Total Zeros Table for 4x4 Blocks                               | .130 |

| Table A-5 Total Zeros Table for Chroma DC Blocks (4:2:0 Chroma Sampling) | .130 |

| Table A-6 Total Zeros Table for Chroma DC Blocks (4:2:2 Chroma Sampling) | .131 |

| Table A-7 Run Before Parameter Table                                     | .131 |

# LIST OF FIGURES

| Figure 2.1 Main Parts of an H.264/AVC Codec                                | . 4 |

|----------------------------------------------------------------------------|-----|

| Figure 2.2 Progressive and Interlaced Scan                                 | . 5 |

| Figure 2.3 Original Frame                                                  | . 7 |

| Figure 2.4 Y Component of Picture in Figure 2.3                            | . 7 |

| Figure 2.5 Cb Component of Picture in Figure 2.3                           | . 7 |

| Figure 2.6 Cr Component of Picture in Figure 2.3                           | . 8 |

| Figure 2.7 Chroma Sampling Formats                                         | 9   |

| Figure 2.8 Interleaved Memory Structure                                    | 9   |

| Figure 2.9 Planar Memory Structure                                         | 10  |

| Figure 2.10 H.264 Encoder Structure                                        | 13  |

| Figure 2.11 Intra Prediction                                               | 14  |

| Figure 2.12 Inter Prediction                                               | 14  |

| Figure 2.13 Inter Prediction Block Sizes                                   | 16  |

| Figure 2.14 Transform Matrixes Used in H.264/AVC                           | 18  |

| Figure 2.15 Transformation and Quantization Results of Two Residual Blocks | 20  |

| Figure 2.16 Decoder Flow                                                   | 21  |

| Figure 2.17 H.264/AVC Syntax                                               | 22  |

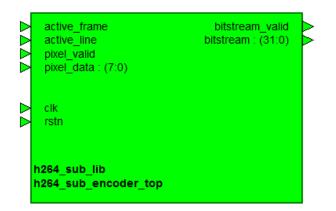

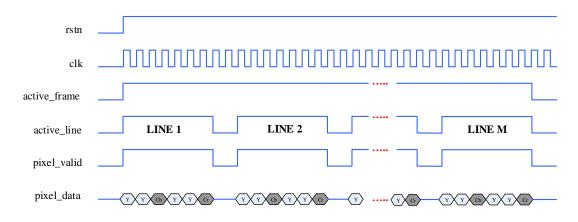

| Figure 3.1 Encoder FPGA Design Top Block                                   | 28  |

| Figure 3.2 Top Level Representation of the Designed H.264 Encoder          | 28  |

| Figure 3.3 Timing Representations of the Input Signals                     | 29  |

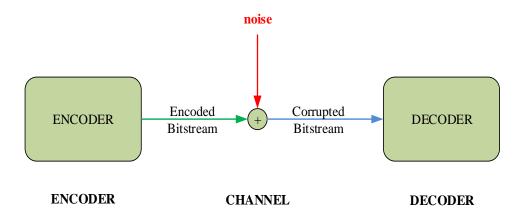

| Figure 4.1 Encoder/Channel/Decoder Block Representation                    | 34  |

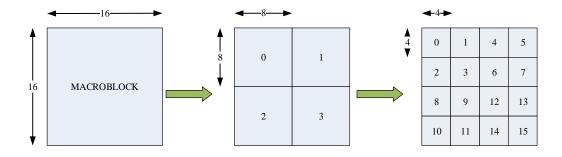

| Figure 4.2 8x8 and 4x4 Scanning of a MB                                    | 35  |

| Figure 4.3 A 4x4 Block and Neighboring Pixels                              | 36  |

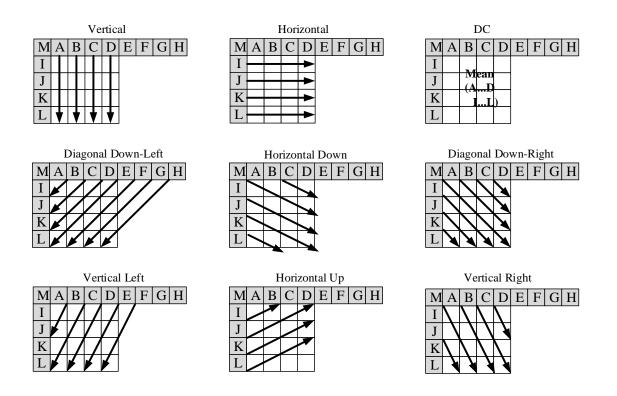

| Figure 4.4 Intra 4x4 Prediction Modes                                      | 36  |

| Figure 4.5 4x4 Luma Prediction Equations                                   | 39  |

| Figure 4.6 Possible 4x4 Prediction Modes at Various Block Locations inside | an  |

| Image                                                                      | 40  |

| Figure 4.7 16x16 Prediction Modes                                          | 40  |

| Figure 4.8 Possible 16x16 Prediction Modes at Various Block Locations inside an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 4.9 8x8 Chroma Prediction Equations45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 4.10 Possible Chroma Prediction Modes at Various Block Locations inside                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| an Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

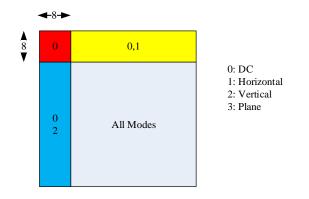

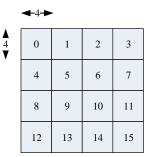

| Figure 4.11 4x4 Representation of a MB50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

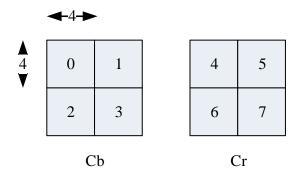

| Figure 4.12 4x4 Representation of Cb and Cr Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

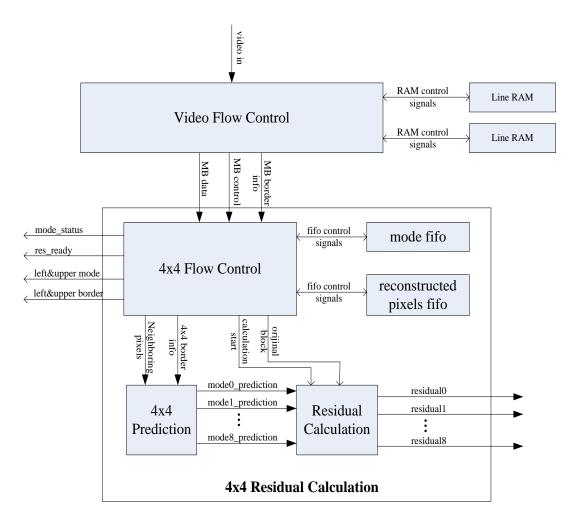

| Figure 4.13 4x4 Intra Prediction and Residual Calculation54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

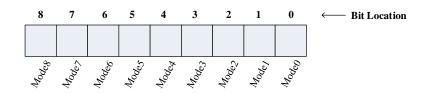

| Figure 4.14 "mode_status" Signal Bits and Corresponding Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 4.15 Similarities between Prediction Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

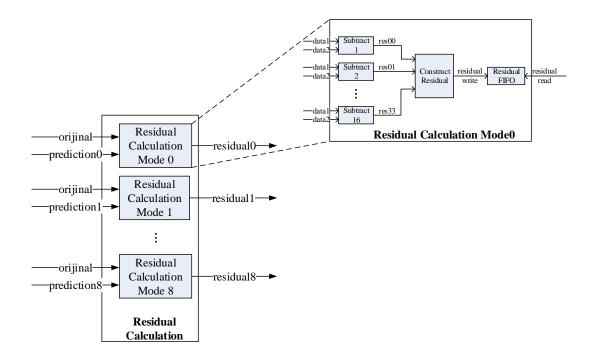

| Figure 4.16 Residual Calculation Block Diagram60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

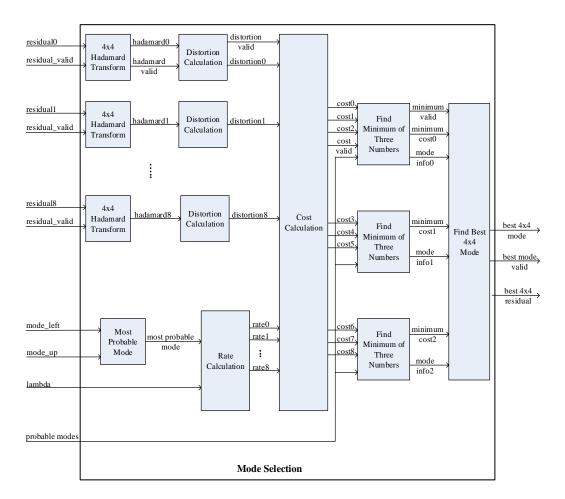

| Figure 4.17 FPGA Design Architecture of 4x4 Intra Mode Selection Algorithm61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

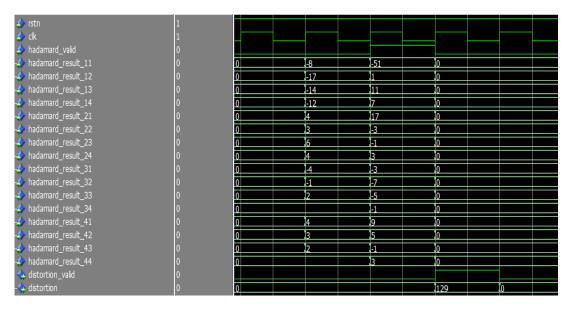

| Figure 4.18 The 4x4 Hadamard Transform Block Modelsim Simulation Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 4.19 The Distortion Calculation Block Modelsim Simulation Results63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 4.20 The Cost Calculation Block Modelsim Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

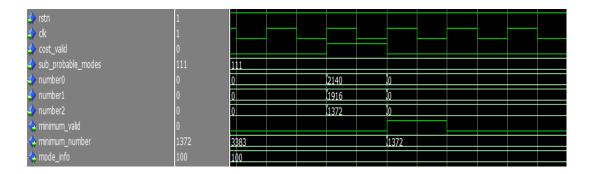

| Figure 4.21 Find Minimum of Three Numbers Block Modelsim Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 4.22 Find Best 4x4 Mode Block Modelsim Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4.22 Find Best 4x4 Mode Block Modelsim Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

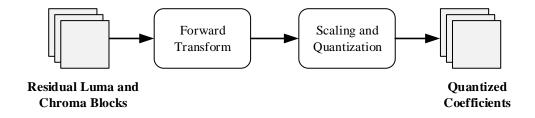

| Figure 5.1 Forward Transform and Quantization70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

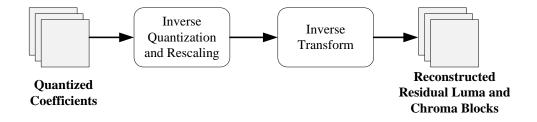

| Figure 5.1 Forward Transform and Quantization70<br>Figure 5.2 Inverse Transform and Quantization70                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

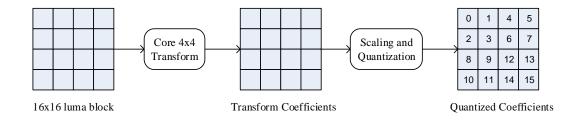

| Figure 5.1 Forward Transform and Quantization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 5.1 Forward Transform and Quantization70Figure 5.2 Inverse Transform and Quantization70Figure 5.3 4x4 and 8x8 Transform Matrixes71Figure 5.4 Luma Forward Transform: Default72                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 5.1 Forward Transform and Quantization70Figure 5.2 Inverse Transform and Quantization70Figure 5.3 4x4 and 8x8 Transform Matrixes71Figure 5.4 Luma Forward Transform: Default72Figure 5.5 Luma Inverse Transform: Default72                                                                                                                                                                                                                                                                                                                                          |

| Figure 5.1 Forward Transform and Quantization70Figure 5.2 Inverse Transform and Quantization70Figure 5.3 4x4 and 8x8 Transform Matrixes71Figure 5.4 Luma Forward Transform: Default72Figure 5.5 Luma Inverse Transform: Default72Figure 5.6 Luma Forward Transform: Intra 16x16 Mode73                                                                                                                                                                                                                                                                                     |

| Figure 5.1 Forward Transform and Quantization70Figure 5.2 Inverse Transform and Quantization70Figure 5.3 4x4 and 8x8 Transform Matrixes71Figure 5.4 Luma Forward Transform: Default72Figure 5.5 Luma Inverse Transform: Default72Figure 5.6 Luma Forward Transform: Intra 16x16 Mode73Figure 5.7 Luma Inverse Transform: Intra 16x16 Mode73                                                                                                                                                                                                                                |

| Figure 5.1 Forward Transform and Quantization70Figure 5.2 Inverse Transform and Quantization70Figure 5.3 4x4 and 8x8 Transform Matrixes71Figure 5.4 Luma Forward Transform: Default72Figure 5.5 Luma Inverse Transform: Default72Figure 5.6 Luma Forward Transform: Intra 16x16 Mode73Figure 5.7 Luma Inverse Transform: Intra 16x16 Mode73Figure 5.8 Chroma Forward Transform: 4:2:0 Sub-sampling74                                                                                                                                                                       |

| Figure 5.1 Forward Transform and Quantization70Figure 5.2 Inverse Transform and Quantization70Figure 5.3 4x4 and 8x8 Transform Matrixes71Figure 5.4 Luma Forward Transform: Default72Figure 5.5 Luma Inverse Transform: Default72Figure 5.6 Luma Forward Transform: Intra 16x16 Mode73Figure 5.7 Luma Inverse Transform: Intra 16x16 Mode73Figure 5.8 Chroma Forward Transform: 4:2:0 Sub-sampling74Figure 5.9 Chroma Inverse Transform: 4:2:0 Subsampling75                                                                                                               |

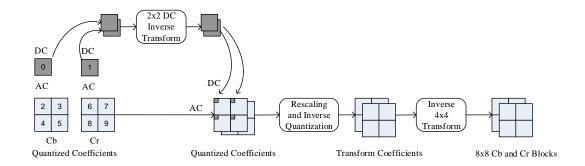

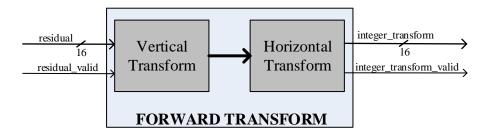

| Figure 5.1 Forward Transform and Quantization70Figure 5.2 Inverse Transform and Quantization70Figure 5.3 4x4 and 8x8 Transform Matrixes71Figure 5.4 Luma Forward Transform: Default72Figure 5.5 Luma Inverse Transform: Default72Figure 5.6 Luma Forward Transform: Intra 16x16 Mode73Figure 5.7 Luma Inverse Transform: Intra 16x16 Mode73Figure 5.8 Chroma Forward Transform: 4:2:0 Sub-sampling74Figure 5.9 Chroma Inverse Transform: 4:2:0 Subsampling75Figure 5.10 Block Diagram of Forward Transform78                                                               |

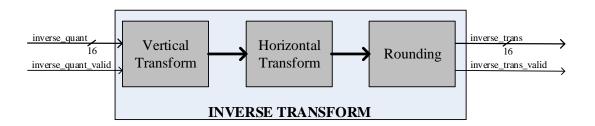

| Figure 5.1 Forward Transform and Quantization70Figure 5.2 Inverse Transform and Quantization70Figure 5.3 4x4 and 8x8 Transform Matrixes71Figure 5.4 Luma Forward Transform: Default72Figure 5.5 Luma Inverse Transform: Default72Figure 5.6 Luma Forward Transform: Intra 16x16 Mode73Figure 5.7 Luma Inverse Transform: Intra 16x16 Mode73Figure 5.8 Chroma Forward Transform: 4:2:0 Sub-sampling74Figure 5.9 Chroma Inverse Transform: 4:2:0 Sub-sampling75Figure 5.10 Block Diagram of Forward Transform78Figure 5.11 Block Diagram of Inverse Transform and Rounding78 |

| Figure 5.15 Modelsim Simulation Result of "Inverse Integer Transform" Block 82 |

|--------------------------------------------------------------------------------|

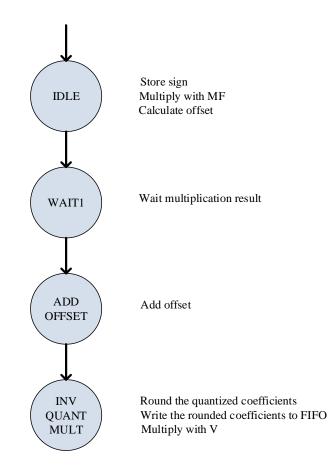

| Figure 5.16 State Diagram of Quantization Process                              |

| Figure 5.17 State Diagram of Inverse Quantization Process                      |

| Figure 5.18 Modelsim Simulation Results of "Quantization" and "Inverse         |

| Quantization" Process                                                          |

| Figure 6.1 Exp-Golomb Codeword Structure                                       |

| Figure 6.2 Algorithmic Flow of CAVLC                                           |

| Figure 6.3 Block Diagram of Exponential-Golomb Coding                          |

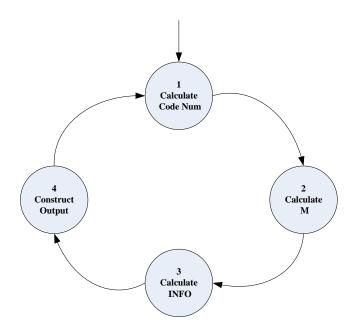

| Figure 6.4 State Diagram of Exponential-Golomb State Machine 100               |

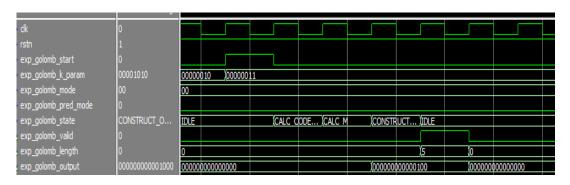

| Figure 6.5 Simulation Result When the Mapping Type is ue(v) 101                |

| Figure 6.6 Simulation Result When the Mapping Type is se(v) 101                |

| Figure 6.7 Simulation Result When the Mapping Type is me(v) 101                |

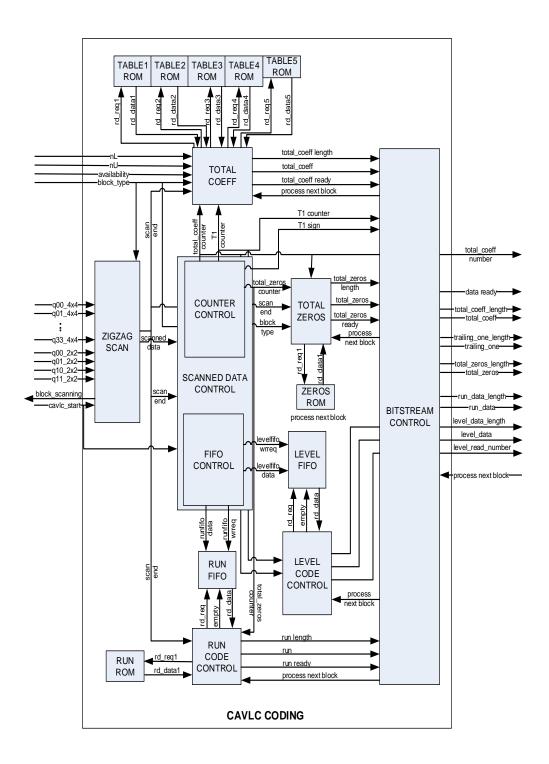

| Figure 6.8 FPGA Architecture of CAVLC Block Design 104                         |

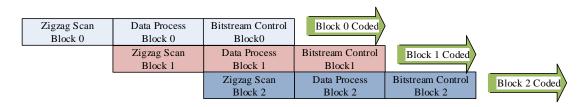

| Figure 6.9 CAVLC Coding Block Working Principle                                |

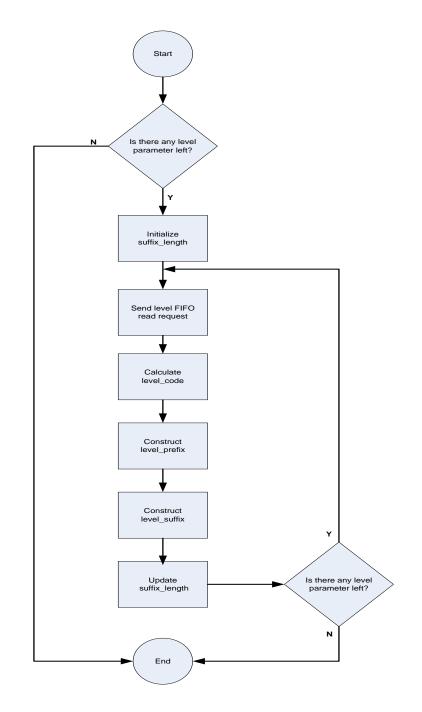

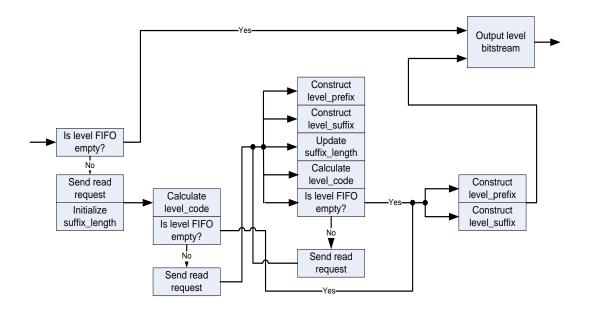

| Figure 6.10 Algorithmic Flow of Level Parameter Coding 109                     |

| Figure 6.11 FPGA Implementation Architecture of Level Parameter Coding 110     |

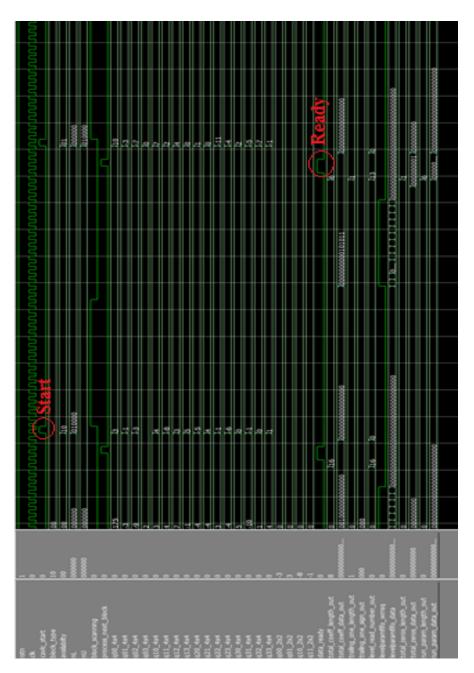

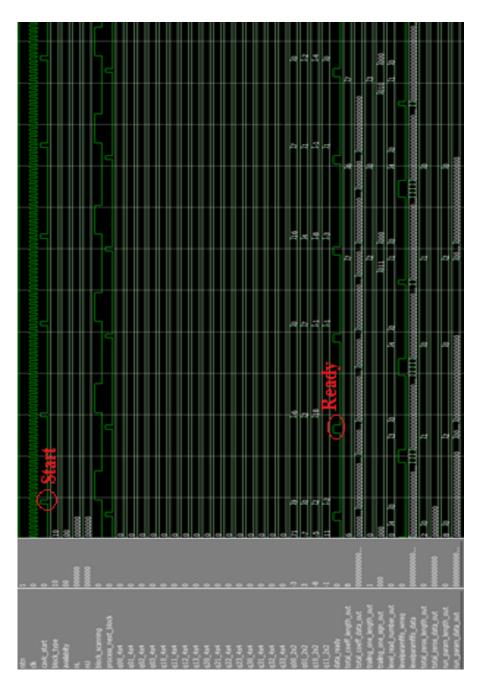

| Figure 6.12 CAVLC Modelsim Simulation Result (Block Size: 4x4) 111             |

| Figure 6.13 CAVLC Modelsim Simulation Result (Block Size: 2x2) 112             |

| Figure 6.14 Maximum Block Delays (Number of Quantized Coefficient: 16) 113     |

| Figure 6.15 Maximum Block Delays (Number of Quantized Coefficient: 15) 113     |

| Figure 6.16 Maximum Block Delays (Number of Quantized Coefficient: 4) 114      |

| Figure 7.1 H.264 Encoder Hardware Block Diagram                                |

| Figure 7.2 STRATIX V FPGA Development Board                                    |

| Figure 7.3 Video Source 117                                                    |

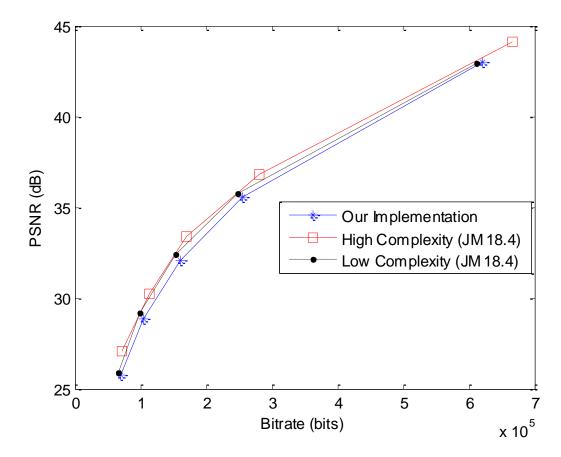

| Figure 7.4 Comparison of Implementation Results                                |

# **ABBREVIATIONS**

| ASIC  | Application Specific Integrated Circuit        |

|-------|------------------------------------------------|

| AVC   | Advanced Video Coding                          |

| BP    | Baseline Profile                               |

| CABAC | Context Adaptive Binary Arithmetic Coding      |

| CAVLC | Context Adaptive Variable Length Coding        |

| CBP   | Coded Block Pattern                            |

| CIF   | Common Intermediate Format                     |

| DCT   | Discrete Cosine Transform                      |

| DDR   | Double Data Rate                               |

| DVD   | Digital Versatile Disk                         |

| FIFO  | First In First Out                             |

| FPGA  | Field Programmable Gate Array                  |

| HD    | High Definition                                |

| HDL   | Hardware Description Language                  |

| HP    | High Profile                                   |

| HSMC  | High Speed Mezzanine Card                      |

| IDR   | Instanteneous Decoder Refresh                  |

| ISO   | International Organization for Standardization |

| ITU   | International Telecommunication Union          |

| JM    | Joint Model                                    |

| JPEG  | Joint Photographic Experts Group               |

| MB    | Macroblock                                     |

| MP    | Main Profile                                   |

| MPEG  | Moving Picture Experts Group                   |

| MSE   | Mean Square Error                              |

| NALU  | Network Abstraction Layer Unit                 |

|       | Personal Computer                              |

| PHY   | Physical                                                          |

|-------|-------------------------------------------------------------------|

| PPS   | Picture Parameter Set                                             |

| PSNR  | Peak Signal-to-Noise Ratio                                        |

| RAM   | Random Access Memory                                              |

| RDO   | Rate Distortion Optimization                                      |

| ROM   | Read Only Memory                                                  |

| QCIF  | Quarter Common Intermediate Format                                |

| QP    | Quantization Parameter                                            |

| SAD   | Sum of Absolute Difference                                        |

| SATD  | Sum of Absolute Transformed Difference                            |

| SDRAM | Synchronous Dynamic Random Access Memory                          |

| SSD   | Sum of Squared Difference                                         |

| VCEG  | Video Coding Experts Group                                        |

| VCL   | Video Coding Layer                                                |

| VHDL  | Very High Speed Integrated Circuits Hardware Description Language |

| VLC   | VideoLAN Client                                                   |

| TS    | Transport Stream                                                  |

| UDP   | User Datagram Protocol                                            |

# **CHAPTER 1**

# **INTRODUCTION**

H.264, also known as MPEG-4 part 10 or Advanced Video Coding (AVC), is a video compression standard, which is a successor to previous H.263 and MPEG-2 standards [1]. It is currently one of the most commonly used formats for the recording, compression, and distribution of video content. H.264/AVC is used in a wide range of applications including internet video streaming, digital cinema applications, Blu-ray and HD DVD, and television broadcasting [2]. H.264/AVC was developed by the ITU-T Video Coding Experts Group (VCEG) together with ISO/IEC Moving Picture Experts Group (MPEG) and ratified as an international standard in 2003. H.264 aims an average bit rate reduction of 50% given fixed fidelity compared to previous standards.

In H.264/AVC, more complicated algorithms are used to achieve superior compression with respect to previous standards. Power consumption, logic usage, design cost and flexibility are some of the design criterions that should be considered while designing an H.264/AVC codec. Depending on the performance requirements of the applications, various platforms have been used, such as general purpose (GP) processors, multimedia co-processors, ASICs and FPGAs. Encoders on general purpose processors have been developed for comparison and development. General purpose processors however are not able to meet the constraints of real-time video encoding. Multimedia co-processors have focused on smaller frame sizes, generally CIF and below with high power consumptions. So they are not a suitable solution for portable applications. Due to the parallel processing architecture of ASICs and

FPGAs, they are more advantageous in terms of video encoding applications. However, the high cost of custom silicon makes ASIC solutions economically feasible only in high volume applications. Therefore, in lower-volume type of applications, FPGAs are typically preferred.

In this thesis, an H.264/AVC compatible intra-frame video encoder is designed and implemented on FPGA programmable devices. First, a reference encoder which includes encoding algorithms such as intra prediction, intra mode selection, transform, quantization and entropy coding, are implemented and tested in MATLAB environment. Then, the reference encoder is coded in VHDL language and tested using the Mentor Graphics Modelsim HDL simulation tool. Next, the overall FPGA implementation is tested by putting the H.264 coded bitstream into transport stream packets, streaming with UDP over Ethernet and decoding with VLC Player software on a PC.

The remainder of this thesis is organized as follows: Chapter 2 provides a basic overview of video encoding and H.264/AVC video coding standard. In Chapter 3, an overview of designed H.264 encoder and some design criteria about encoder design are given. Intra prediction and its FPGA implementation are studied in Chapter 4. Chapter 5 explains the implementation and theory of residual coding processes, i.e. transform and quantization. Entropy coding tools, including Exp-Golomb (Exponential-Golomb) coding and CAVLC (Context Adaptive Variable Length Coding) are studied in Chapter 6. The results are given in Chapter 7. Finally, Chapter 8 concludes the paper.

# **CHAPTER 2**

# **AN OVERVIEW OF H.264/AVC**

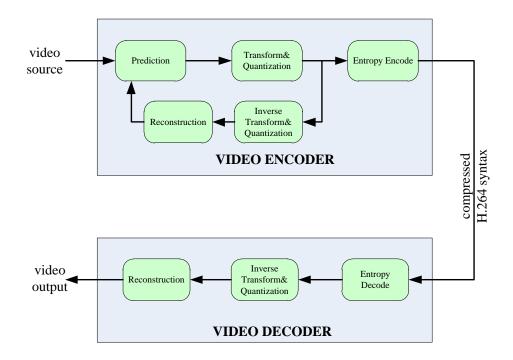

As shown in Figure 2.1, an H.264/AVC codec is composed of two main parts: video encoder and video decoder. The encoder part performs prediction, transforming and encoding operations to generate a compressed bitstream. In H.264, while predicting the current blocks, previously coded pixels are used. For this reason, in an encoder inverse quantization, inverse transformation and reconstruction operations are also applied to quantized transform coefficients in order to produce the previously coded pixels. The video decoder part performs the complementary operations of decoding, inverse transforming and reconstruction to generate a decoded video sequence. The compressed H.264/AVC bitstream can be transmitted or stored in different mediums such as the internet or DVD disks. Because H.264/AVC is a lossy compression standard, in general, there will be some differences between the original video and the decoded one.

Figure 2.1 Main Parts of an H.264/AVC Codec

In this chapter, after defining some basic concepts about digital video and video coding, H.264/AVC encoder data flow, H.264/AVC decoder data flow and H.264/AVC syntax will be explained.

#### 2.1 Digital Video Basics

### 2.1.1 Digital Video

Video is the combination of still pictures that are displayed at a high rate to give the impression that objects in pictures are moving. Frame rate is the number of still pictures per unit of time. Presently, the movie industry uses 24 frame per second (fps), while the TV industry 25 (in PAL and SECAM systems) and 30 fps (in NTSC system). Frame resolution specifies the number of pixels used to represent each frame (1920x1080, 640x512 etc.). Pixel depth specifies the number of bits that are used to represent each pixel (8 bits per pixel, 14 bits per pixel).

#### 2.1.2 Progressive and Interlaced Scan

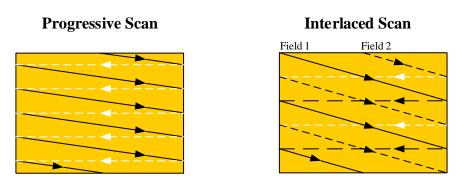

As shown in Figure 2.2, in progressive scan the horizontal lines are scanned successively. In the interlaced scan, each frame is scanned in two fields and each field contains half the number of lines in a frame.

Figure 2.2 Progressive and Interlaced Scan

Interlaced scan increases temporal resolution. However, it also decreases the vertical resolution. So it comes up with a trade-off between temporal and vertical resolution. It may allow us more detailed images to be created than would otherwise be possible within a given amount of bandwidth. But it may also lead to interlacing artifacts especially in high frequency regions.

### 2.1.3 Video Format

In Table 2.1, commonly used video formats are listed. The choice of frame resolution depends on the application. For example, SQCIF or QCIF are appropriate for mobile multimedia applications; CIF and QCIF are popular for videoconferencing applications; 4CIF is appropriate for standard-definition television and DVD-video; HD is appropriate for high-definition television.

| Format      | Resolution |

|-------------|------------|

| Sub-QCIF    | 128x96     |

| Quarter CIF | 176x144    |

| CIF         | 352x288    |

| 4CIF        | 704x576    |

| 720p        | 1280x720   |

| HD          | 1920x1080  |

| UHD         | 3840x2160  |

**Table 2.1 Various Video Formats**

#### 2.1.4 Color Spaces

Color is described by the luminance and chrominance attributes of light. Luminance refers to the perceived brightness of the light, which is proportional to the total energy in the visible band. Chrominance describes the perceived color tone of a light, which depends on the wavelength composition of the light. Human visual system is more sensitive to luminance changes than chrominance. For this reason, representing luminance and chrominance components separately is often more efficient. RGB and YCbCr are commonly used color spaces.

In RGB representation, red, green, and blue light are added together in various ways to reproduce a broad array of colors. All three components are equally important. RGB format is commonly used when displaying and storing an image.

In the YCbCr representation, Y is the luminance component and Cb, Cr are the chroma components. Y, Cb and Cr components of the image shown in Figure 2.3 are represented in Figure 2.4, Figure 2.5 and Figure 2.6, respectively. As shown from these figures, luminance component contains more information than chroma components.

Figure 2.3 Original Frame

Figure 2.4 Y Component of Picture in Figure 2.3

Figure 2.5 Cb Component of Picture in Figure 2.3

Figure 2.6 Cr Component of Picture in Figure 2.3

# 2.1.5 Chroma Sampling Formats

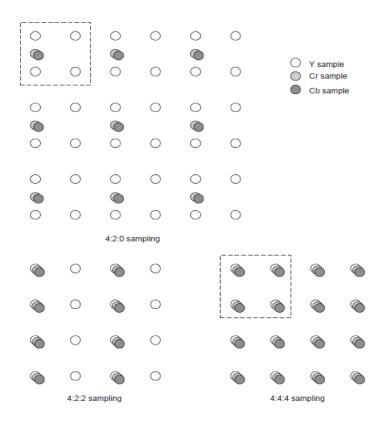

As mentioned in section 2.1.4, luma component of a frame carries more information than chroma components. For this reason, representing chroma components with less data usually may give better results in some video compression applications. This is achieved as follows: Instead of using one Cb and one Cr pair for each Y component, same Cb and Cr pairs are used for more than one Y component.

In Figure 2.7, three sampling formats that are supported by H.264/AVC are shown. In 4:4:4 sampling format, one Cb and one Cr pair is used for each luma component. In 4:2:2 sampling format, chroma components are sampled by two in the horizontal axis which means the same Cb and Cr components are used for each two horizontally neighbor luma components. In 4:2:0 sampling format, which is commonly used format, chroma components are sampled by two both in the horizontal and vertical directions.

**Figure 2.7 Chroma Sampling Formats**

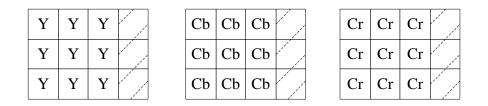

# 2.1.6 Image Buffering

There are two common memory structures for an image: Planar and Interleaved. In planar images, all of the samples are stored consecutively, and they are consecutive in memory as well (YYY...CbCbCb...CrCrCr...). In interleaved images, the samples are interleaved with each other in memory (YCbCrYCbCrYCbCr ...). In Figure 2.8 and Figure 2.9, interleaved and planar images are shown respectively.

| Y | Cb | Cr | Y | Cb | Cr | Y | Cb | Cr | and the second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second s |

|---|----|----|---|----|----|---|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y | Cb | Cr | Y | Cb | Cr | Y | Cb | Cr |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Y | Cb | Cr | Y | Cb | Cr | Y | Cb | Cr |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

**Figure 2.8 Interleaved Memory Structure**

**Figure 2.9 Planar Memory Structure**

# 2.2 H.264/AVC VIDEO CODING

#### 2.2.1 H264/AVC Profiles and Levels

The H.264/AVC standard document does not specify how to encode a digital video. It only defines syntax for compressed video and a method for decoding this syntax. An encoder may choose any tools defined in the standard. However, a decoder must implement a given set of tools and be able to process a given amount of data. These are defined as profile and level of a decoder in H.264/AVC standard.

Each H.264 profile defines a subset of tools and targets specific classes of applications. It places limits on the algorithmic capabilities required of an H.264/AVC decoder. The standard defines 21 profiles. But these 21 profiles are extended or reduced versions of the baseline profile (BP), main profile (MP) and high profile (HP). In general, BP is used for low-cost applications, MP is used for standard-definition digital TV broadcasts and HP is used for broadcast and disc storage. In Table 2.2, several H.264 profiles are compared (see [2] for more information).

| Feature                                               | СВР   | BP    | ХР    | MP    | ProHiP | HiP   | Hi10P   | Hi422P      | Hi444PP           |

|-------------------------------------------------------|-------|-------|-------|-------|--------|-------|---------|-------------|-------------------|

| Bit depth (per sample)                                | 8     | 8     | 8     | 8     | 8      | 8     | 8 to 10 | 8 to 10     | 8 to 14           |

| Chroma formats                                        | 4:2:0 | 4:2:0 | 4:2:0 | 4:2:0 | 4:2:0  | 4:2:0 | 4:2:0   | 4:2:0/4:2:2 | 4:2:0/4:2:2/4:4:4 |

| Interlaced coding (PicAFF, MBAFF)                     | No    | No    | Yes   | Yes   | No     | Yes   | Yes     | Yes         | Yes               |

| B slices                                              | No    | No    | Yes   | Yes   | Yes    | Yes   | Yes     | Yes         | Yes               |

| CABAC entropy coding                                  | No    | No    | No    | Yes   | Yes    | Yes   | Yes     | Yes         | Yes               |

| 4:0:0 (Monochrome)                                    | No    | No    | No    | No    | Yes    | Yes   | Yes     | Yes         | Yes               |

| 8×8 vs. 4×4 transform adaptivity                      | No    | No    | No    | No    | Yes    | Yes   | Yes     | Yes         | Yes               |

| Separate C <sub>b</sub> and C <sub>r</sub> QP control | No    | No    | No    | No    | Yes    | Yes   | Yes     | Yes         | Yes               |

| Separate color plane coding                           | No    | No    | No    | No    | No     | No    | No      | No          | Yes               |

| Predictive lossless coding                            | No    | No    | No    | No    | No     | No    | No      | No          | Yes               |

Table 2.2 Some Tools Used In Several H.264 Profiles

H.264/AVC levels define the maximum data processing rate of a decoder. It puts constraints on some video parameters such as the maximum frame rate and the maximum frame size of a video. In Table 2.3, the minimum required decoder levels are listed for some different video formats at various frame rates.

Profile and level parameters are sufficient to define all the capabilities of a decoder. They also give information about the decoder complexity. From BP (Baseline Profile) to HP (High Profile) and from level 1 to 5, a decoder complexity and capability increase.

| Format (luma resolution) | Max frames per second | Level  |

|--------------------------|-----------------------|--------|

| QCIF (176x144)           | 15                    | 1, 1b  |

|                          | 30                    | 1.1    |

| CIF (352x288)            | 15                    | 1.2    |

|                          | 30                    | 1.3, 2 |

| 525 SD (720x480)         | 30                    | 3      |

| 625 SD (720x576)         | 25                    | 3      |

| 720p HD (1280x720)       | 30                    | 3.1    |

| 1080p HD (1920x1080)     | 30                    | 4, 4.1 |

|                          | 60                    | 4.2    |

| 4Kx2K (4096x2048)        | 30                    | 5.1    |

**Table 2.3 Minimum Decoder Levels for Some Video Formats**

#### 2.2.2 H.264/AVC Encoder Path

H.264/AVC is a block based video compression standard. Video is processed block by block. The main block size in H.264/AVC is 16x16 which is also called as macroblock (MB). After encoding one macroblock, the next macroblock is processed until all the MBs in a frame are processed in that manner.

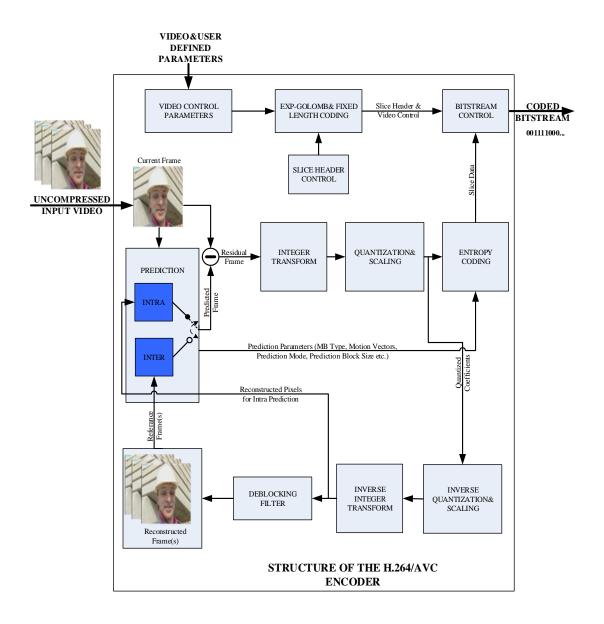

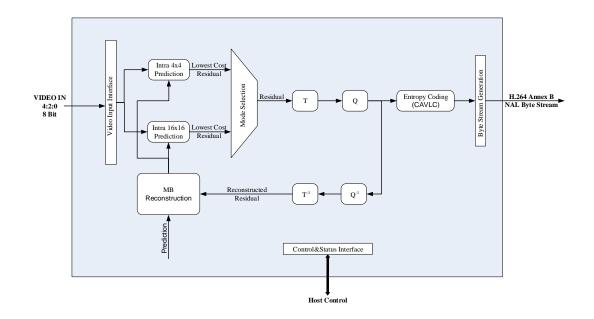

In Figure 2.10, the detailed block diagram of an H.264/AVC encoder is given. An H.264/AVC encoder performs prediction, motion estimation and compensation, transformation, quantization, entropy encoding operations to compress video blocks. It also generates H.264/AVC compatible bitstream from the entropy coded video blocks and entropy coded video control parameters.

Figure 2.10 H.264 Encoder Structure

### 2.2.2.1 Prediction

In H.264/AVC, a prediction is created for every macroblock by using the previously coded pixels. The aim of this operation is to construct a prediction block as close as possible to the original block and send the difference (error or residual) between these blocks instead of the original block. Error between the original block and the prediction block directly affects the compression performance. If the error is small, that means

residual block contains less information, the bitrate to transmit the error will be less. So the compression efficiency increases.

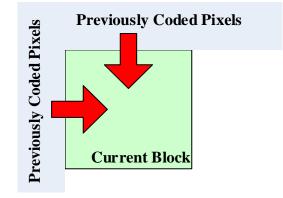

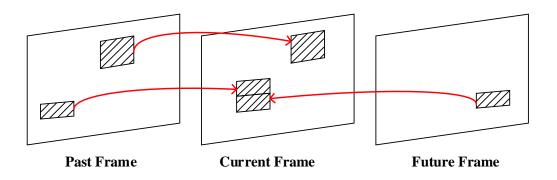

H.264/AVC supports two types of prediction methods: Intra prediction and Inter prediction. Intra prediction method uses the previously coded data in the current frame (Figure 2.11); on the other hand, inter prediction method uses the previously coded data in other frame(s) (Figure 2.12).

**Figure 2.11 Intra Prediction**

**Figure 2.12 Inter Prediction**

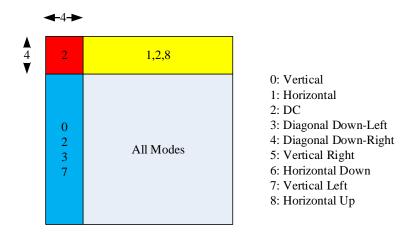

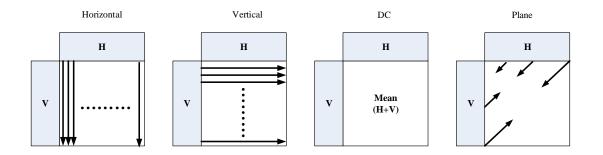

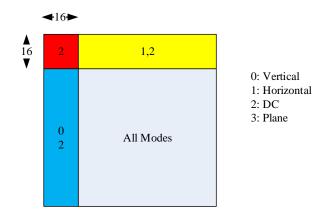

In intra prediction method, there are three choices of block sizes for luma components and there is single choice of block size for chroma components. Block sizes for luma components are 16x16, 8x8 and 4x4 (8x8 block size is only used in high profiles) and for chroma 8x8. There are 9 different prediction modes for each 4x4 and 8x8 luma blocks; 4 for a 16x16 luma block and 4 for chroma blocks.

An efficient encoder should try to decide the optimum prediction size and prediction mode before constructing the bitstream. Smaller block sizes commonly provide better prediction, but require more bits for signaling the prediction modes. The details of intra prediction modes and an efficient mode selection algorithm are represented in Chapter 4.

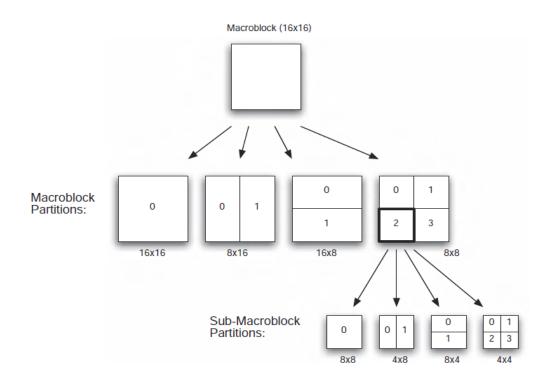

As mentioned earlier, in contrast to intra prediction, inter prediction uses blocks from different frame(s) other than the current frame while constructing the prediction block. In H.264/AVC, several inter prediction block sizes are allowed from 16x16 to 4x4 (Figure 2.13). A macroblock can be divided into two 16x8 blocks or two 8x16 or four 8x8 blocks which are called as macroblock partitions. Further, an 8x8 macroblock partition can be divided into two 4x8 blocks or two 8x4 blocks or four 4x4 blocks which are called as sub-macroblock partitions. A macroblock can be predicted using macroblock partitions from different frames, however, sub-macroblock partitions of a macroblock partition must be in the same frame.

**Figure 2.13 Inter Prediction Block Sizes**

If a macroblock is inter predicted, the reference frame index or indexes and motion vector or vectors must be signaled to the decoder side to properly construct the decoded picture.

Some operations, such as reference picture interpolation and loop filtering, may be applied before inter prediction to increase the prediction performance. By doing the interpolation of the reference pictures, extra pixels are added into the reference frame and motion estimation can be achieved at the 1/4 pixel resolution for luma components and 1/8 pixel resolution for chroma components. Also an in-loop deblocking filter [3] reduces the blocking artifacts.

#### 2.2.2.2 Transform & Inverse Transform

As done in the former standards, transform operation is applied after the prediction operation to code the prediction error signal. Because of the characteristics of an image, the correlation between the pixels is commonly high in the horizontal and vertical directions. There is typically also correlation left in the prediction error signal. Transform coding reduces the spatial redundancy of the prediction error signal. Former standards such as JPEG, MPEG-2 Video and MPEG-4 Visual applied a two dimensional Discrete Cosine Transform (DCT) [4] of size 8x8.

In H.264/AVC, different types of integer transforms are used to minimize the computational complexity and to avoid encoder/decoder mismatch. Equation 2.1 shows the general transformation equation, where **A** is the transform matrix, **X** is the residual block and **Y** is the transformation result. The core transform in H.264/AVC is 4x4 or 8x8 integer transform. 8x8 transform is only used in High profiles.

$$\mathbf{Y} = \mathbf{A}\mathbf{X}\mathbf{A}^{\mathrm{T}} \tag{2.1}$$

As mentioned earlier, the size and type of the transform matrix **A** varies. In Figure 2.14, transform matrixes used in H.264/AVC are shown.  $A_1$  and  $A_4$  are the 4x4 and 8x8 core transforms matrices, respectively. When the luma prediction type is Intra 16x16, a second transform (also called Hadamard transform) is applied to the DC coefficients of each 4x4 blocks after the core transform by using the  $A_2$  matrix.  $A_3$  matrix is used for the similar purpose as  $A_2$ , but this matrix is used for chroma components. After the core transformation of chroma blocks, all DC coefficients are collected and a second transform is applied to these DC coefficients using the  $A_3$  matrix.

Figure 2.14 Transform Matrixes Used in H.264/AVC

The inverse integer transform operation shown in Equation 2.2 is similar to the integer transform operation. Here W is the inverse transform matrix, X is the matrix obtained after the inverse quantization process and Z is the result of the inverse transformation.

$$\mathbf{Z} = \mathbf{W}^{\mathrm{T}} \mathbf{X} \mathbf{W} \tag{2.2}$$

In Chapter 5, more details about the transform & inverse transform operations are given.

#### 2.2.2.3 Quantization & Inverse Quantization

After transform operation, transform coefficients are quantized in order to reduce the precision of the transform coefficients according to a quantization parameter. The basic forward quantizer operation is shown in equation (2.3), where  $X_{ij}$  is a transform coefficient,  $Y_{ij}$  is the quantized output and  $Q_{step}$  is the quantization step size.

$$Y_{ij} = round(X_{ij}/Q_{step})$$

(2.3)

The quantization is the only part of the H.264/AVC that adds intentional errors into coding systems. The reason to do is to increase the compression performance with a reasonable distortion. If the quantization step size increases, more quantized coefficients will be zero which means less data to represent. This leads to keeping only a few coefficients for efficient representation and results in more distortion. It is important to note that quantization process directly controls the quality and compression ratio for applications. In H.264/AVC 52 different QP values, from 0 to 51, are supported. An encoder can control the QP parameter to control the trade-off between compression ratio and distortion.

The inverse quantization does the inverse operation of the quantization process. The basic inverse quantizer operation (or rescale) is shown in equation (2.4), where  $Y_{ij}$  is a quantized coefficient,  $Z_{ij}$  is the inverse quantization output and  $Q_{step}$  is the quantization step size.

$$Z_{ij} = Y_{ij}.Q_{step} \tag{2.4}$$

In Chapter 5, more details about the quantization and inverse quantization operations are given.

#### 2.2.2.4 Entropy Coding

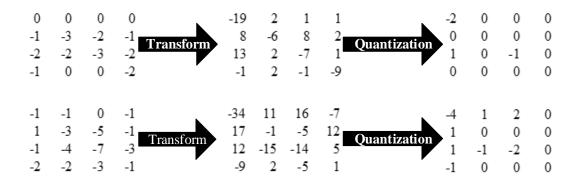

In Figure 2.15, two 4x4 residual blocks, their transforms and quantization results are given (used H.264/AVC JM reference software of version 18.4 and QP is set to 10). As seen from these results, after the quantization operation most of the quantized coefficients (especially high frequency components) become zero and occurrence of some values are more probable than others. Actually we do not need to send all these zero-valued coefficients one by one and represent all the symbols with the same length of bits.

Figure 2.15 Transformation and Quantization Results of Two Residual Blocks

Entropy coding is a lossless data compression technique. Entropy coding algorithms try to assign shortest codes to the most commonly occurred symbols at the input in order to produce smaller bitstream.

H.264 specifies several methods for coding of symbols. These are fixed length code, Exponential-Golomb (Exp-Golomb) variable length code, CAVLC (Context-Adaptive Variable Length Coding) and CABAC (Context-Adaptive Binary Arithmetic Coding).

While entropy coding quantized transform coefficients, CABAC or CAVLC techniques are used. They have major improvements in terms of coding efficiency compared to the techniques used in prior video coding standards. Both methods of H.264/AVC offer a high degree of adaptation to the underlying source, even though at a different complexity-compression trade-off.

CAVLC is commonly used in baseline profile and simpler than CABAC. However, CABAC algorithm can represent the same video data with about 10% fewer bits when compared to CAVLC [5].

In Chapter 6, more details about the entropy coding techniques including Exp-Golomb and CAVLC are given.

#### 2.2.2.5 Bitstream Control

Bitstream Control block is responsible from the construction of H.264/AVC coded bitstream properly. It manages the data flow, takes coded symbols from different blocks and combines them with a correct H.264/AVC syntax as will be described in section 2.3.

#### 2.2.3 H.264/AVC Decoder Path

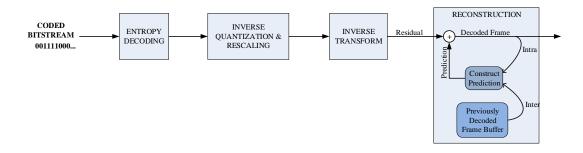

An H.264/AVC decoder constructs the video from the H.264/AVC coded bitstream. As shown in Figure 2.16, firstly the coded bitstream is entropy decoded, then inverse quantized and inverse transformed, and finally reconstruction process is applied by using prediction parameters and reference pictures or pixels. The inverse quantization, inverse transform and reconstruction operations are the same as in the encoder side.

**Figure 2.16 Decoder Flow**

Although an H.264/AVC encoder must generate a standard compliance bitstream, a decoder must decode all the encoded bitstreams for a specific profile and level pair. So we can say that, the computational complexity of an encoder is more than a decoder but a decoder must cover all the tools defined in a specific profile and level.

#### 2.3 H.264/AVC Syntax

H.264 syntax is defined in the H.264 standard and specifies the exact structure of an H.264-compliant video sequence. It defines the syntax elements and the construction of the coded bitstreams from these syntax elements.

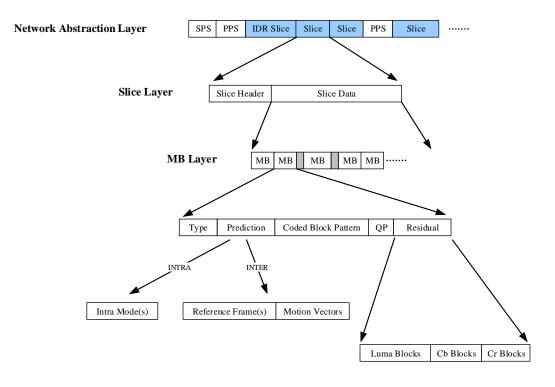

Figure 2.17 shows the H.264/AVC syntax hierarchy [6]. H.264/AVC syntax consists of different Network Abstraction Layer Unit (NALU). Sequence Parameter Sets (SPS) and Picture Parameter Sets (PPS) are NAL units that signal the common control parameters about the video and video data is represented by different type of slices (IDR slice, I slice, P slice, B slice etc.).

Figure 2.17 H.264/AVC Syntax

#### 2.3.1 Video Control NAL Units

As mentioned above, SPS and PPS contain the common control parameters about the video. SPS signals the control parameters about the coded video sequences such as profile, level, video resolution and maximum frame number. In Table 2.4, one example of SPS is shown (JM 18.4 is used in trace mode). 'profile\_idc' and 'level\_idc' parameters shown in this table signal the profile and level values of the coded video sequence, respectively. More details about the meaning and coding of each syntax element shown in Table 2.4 can be found in the H.264 standard [1].

| Bit<br>Position | NALU<br>Type | Parameter                            | <b>Binary Code</b> | Symbol |

|-----------------|--------------|--------------------------------------|--------------------|--------|

| @0              | SPS:         | profile_idc                          | 1000010            | (66)   |

| @8              | SPS:         | constrained_set0_flag                | 0                  | (0)    |

| @9              | SPS:         | constrained_set1_flag                | 0                  | (0)    |

| @10             | SPS:         | constrained_set2_flag                | 0                  | (0)    |

| @11             | SPS:         | constrained_set3_flag                | 0                  | (0)    |

| @12             | SPS:         | reserved_zero_4bits                  | 0                  | (0)    |

| @16             | SPS:         | level_idc                            | 11111              | (31)   |

| @24             | SPS:         | seq_parameter_set_id                 | 1                  | (0)    |

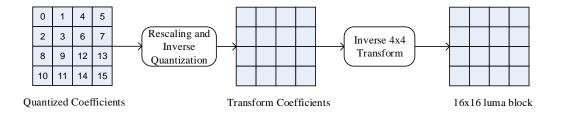

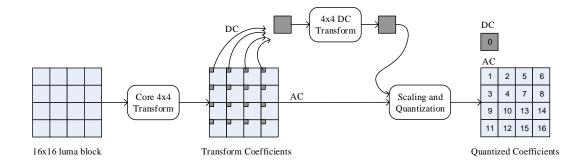

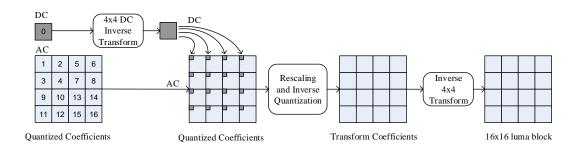

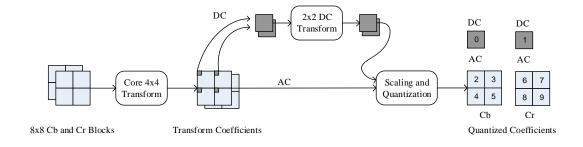

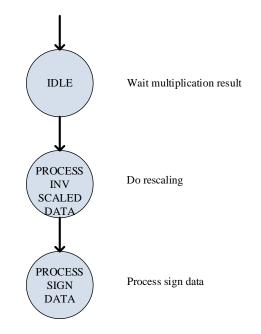

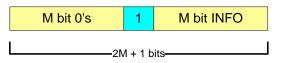

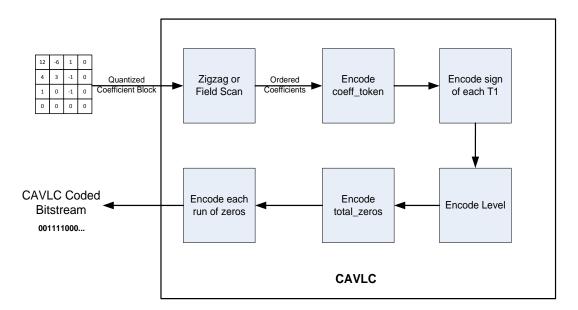

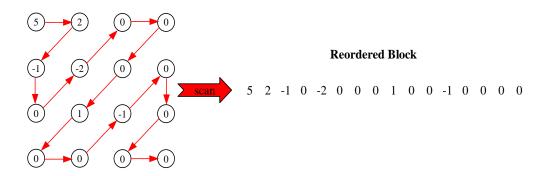

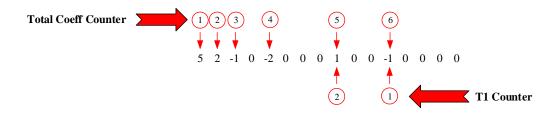

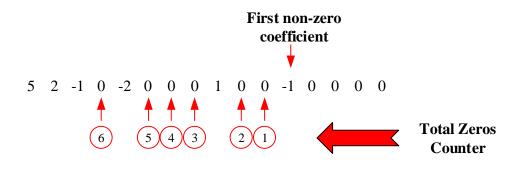

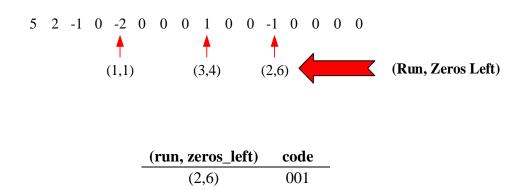

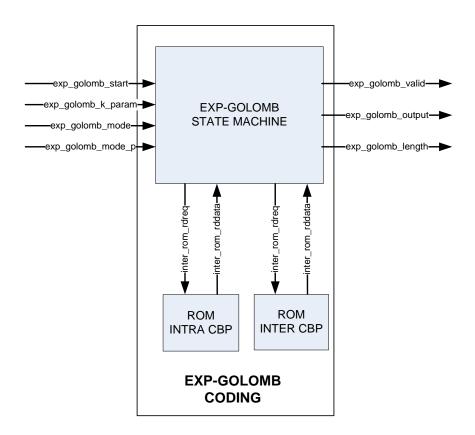

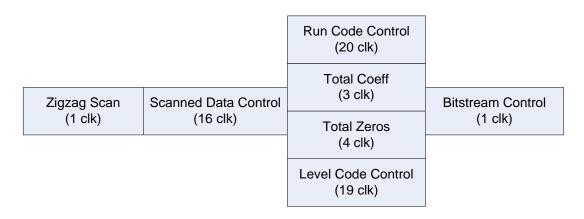

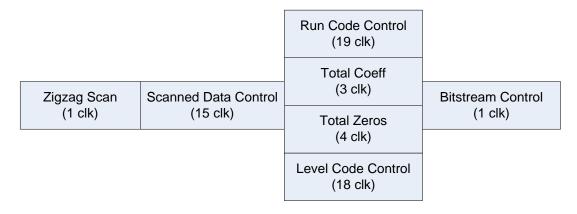

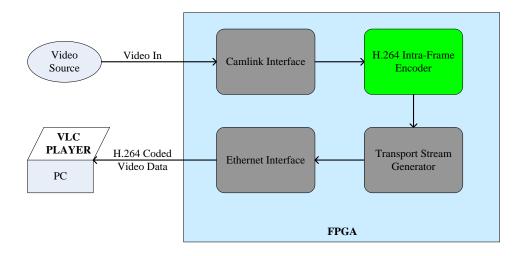

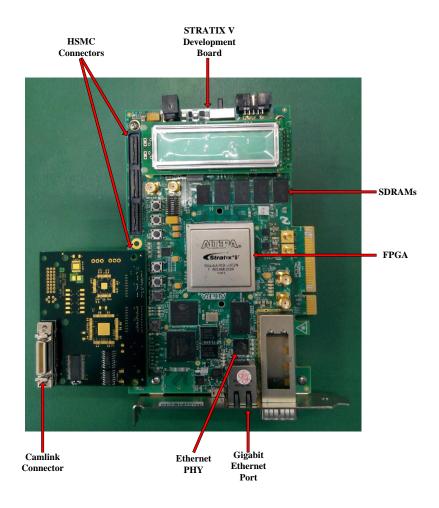

| @25             | SPS:         | log2_max_frame_num_minus4            | 1                  | (0)    |