## ONLINE APPLICATION OF SHEM TO GRID-CONNECTED INVERTERS WITH VARIABLE DC LINK VOLTAGE BY PARTICLE SWARM OPTIMIZATION

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

## UMUT GÜVENGİR

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2014

### Approval of the thesis:

## ONLINE APPLICATION OF SHEM TO GRID-CONNECTED INVERTERS WITH VARIABLE DC LINK VOLTAGE BY PARTICLE SWARM OPTIMIZATION

submitted by UMUT GÜVENGİR in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Gülbin Dural Ünver<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>      |  |

|---------------------------------------------------------------------------------------------------|--|

| Prof. Dr. Gönül Turhan Sayan<br>Head of Department, <b>Electrical and Electronics Engineering</b> |  |

| Prof. Dr. Muammer Ermiş<br>Supervisor, <b>Electrical and Electronics Eng. Dept., METU</b>         |  |

| Prof. Dr. Işık Çadırcı<br>Co-supervisor, Electrical and Electronics Eng. Dept., HU                |  |

| Examining Committee Members:                                                                      |  |

| Prof. Dr. M. Kemal Leblebicioğlu<br>Electrical and Electronics Engineering Department, METU       |  |

| Prof. Dr. Muammmer Ermiş<br>Electrical and Electronics Engineering Department, METU               |  |

| Prof. Dr. Işık Çadırcı<br>Electrical and Electronics Eng. Dept., Hacettepe University             |  |

| Assoc. Prof. Dr. Ahmet M. Hava<br>Electrical and Electronics Engineering Department, METU         |  |

| Assoc. Prof. Dr. Umut Orguner<br>Electrical and Electronics Engineering Department, METU          |  |

Date: 02/12/2014

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: UMUT GÜVENGİR

Signature :

## ABSTRACT

### ONLINE APPLICATION OF SHEM TO GRID-CONNECTED INVERTERS WITH VARIABLE DC LINK VOLTAGE BY PARTICLE SWARM OPTIMIZATION

Güvengir, Umut

M.S., Department of Electrical and Electronics EngineeringSupervisor : Prof. Dr. Muammer ErmişCo-Supervisor : Prof. Dr. Işık Çadırcı

December 2014, 151 pages

In this thesis, online selective harmonic elimination method (SHEM) has been applied to a voltage source converter (VSC) based grid-connected three-phase two-level inverter with variable DC link input voltage eliminating  $5^{th}$ ,  $7^{th}$ ,  $11^{th}$ ,  $13^{th}$ ,  $17^{th}$ , and  $19^{th}$  harmonics in the output voltage. The switching angles of SHEM are given by a set of nonlinear transcendental equations. Particle swarm optimization (PSO) algorithm is used for the solution of this equation set, and this algorithm is implemented in the field-programmable gate array (FPGA) for a fast and online calculation of switching angles in real time without using a lookup table. FPGA is used as the main and sole controller in the implemented voltage source inverter (VSI) to provide gating signals for IGBTs.

In applications where input DC link voltage varies in a wide range, usage of lookup table for switching angle sets might be disadvantageous due to discretization of modulation index values, large lookup table storage, and infeasible region of solution space, which are investigated in detail in the thesis, with explanatory examples. The effects of PSO algorithm parameters on searching performance are also elaborated. FPGA implementation of PSO algorithm for solution of SHEM equation sets is described in detail. A 1.6 kVA, 380 V, three-phase VSI is successfully implemented and tested in the laboratory. Hardware co-simulation, computer simulation, and experimental results have shown that SHEM can be successfully applied online for the control of grid-connected inverters.

Keywords: Online Selective Harmonic Elimination Method (SHEM), Grid Connected Inverter, Variable DC Link Voltage, Particle Swarm Optimization (PSO), Field-Programmable Gate Array (FPGA)

### ŞEBEKEYE BAĞLI DEĞİŞKEN DA BAĞ GERİLİMLİ EVİRGEÇLERE PARÇACIK SÜRÜ OPTİMİZASYONU İLE ÇEVRİMİÇİ SHEM UYGULANMASI

Güvengir, Umut Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Prof. Dr. Muammer Ermiş Ortak Tez Yöneticisi : Prof. Dr. Işık Çadırcı

Aralık 2014, 151 sayfa

Bu tez çalışmasında, çevrimiçi seçici harmonik eliminasyon metodu (SHEM) gerilim kaynaklı çevirgeç (GKÇ) temelli, şebekeye bağlı ve değişken DA bağ giriş gerilimine sahip üç faz iki seviyeli evirgece uygulanmış ve evirgecin çıkış gerilimindeki 5., 7., 11., 13., 17. ve 19. harmonikler yok edilmiştir. SHEM anahtarlama açıları lineer olmayan transandantal denklemler halinde ifade edilir. Parçacık sürü optimizasyonu (PSO) algoritması bu denklem kümesinin çözümü için kullanılmış ve bu algoritma, anahtarlama açılarının hızlı ve çevrimiçi bir şekilde gerçek zamanlı olarak başvuru tablosu kullanılmadan hesaplanabilmesi için alanda programlanabilir kapı dizisinde (FPGA) uygulanmıştır. FPGA, uygulanmış olan gerilim kaynaklı evirgeçteki IGBT'lerin anahtarlama sinyallerinin sağlanması için ana ve tek kontrolcü olarak kullanılmıştır.

Giriş DA bağ geriliminin geniş bir aralıkta değiştiği uygulamalarda, anahtar-

lama açısı kümeleri için başvuru tablolarının kullanılması, modülasyon indeksi değerlerinin ayrıklaştırılması, büyük başvuru tablolarının depolanması ve çözüm uzayının uygulanamaz bölgesi nedeniyle elverişsiz olabilir. Bu tezde bu nedenler açıklayıcı örneklerle birlikte detaylı olarak incelenmiştir. PSO algoritmasının değişkenlerinin arama performansı üzerindeki etkileri de ayrıca ayrıntılandırılmıştır. SHEM denklem kümelerinin çözümü için PSO algoritmasının FPGA üzerinde uygulanması detaylı olarak açıklanmıştır. 1.6 kVA, 380 V, üç faz gerilim kaynaklı bir evirgeç başarıyla gerçekleştirilmiş ve laboratuvar ortamında test edilmiştir. Donanımla birlikte simülasyon sonuçları, bilgisayar simülasyonu sonuçları ve deney sonuçları SHEM'in çevrimiçi olarak şebekeye bağlı evirgeçlerin kontrolü için başarıyla uygulanabileceğini göstermektedir.

Anahtar Kelimeler: Çevrimiçi Seçici Harmonik Eliminasyon Metodu (SHEM), Şebekeye Bağlı Evirgeç, Değişken DA Bağ Gerilimi, Parçacık Sürü Optimizasyonu (PSO), Alanda Programlanabilir Kapı Dizisi (FPGA) To my family

### ACKNOWLEDGMENTS

I would like to thank my supervisor Prof. Dr. Muammer Ermiş and my cosupervisor Prof. Dr. Işık Çadırcı for their constant support and guidance. It was a great honour to work with them on this novel subject. Their great experience on power electronics area and their confidence in me has provided me with the encouragement I needed during my research. At each stage of this thesis work, they have actively participated in the process with their novel ideas and solutions to the problems I have encountered, which greatly reduced the workload upon my shoulders and helped me not only finish this thesis in time but also acquire new qualifications in power electronics area.

I would like express my special gratitude to my colleague Mustafa Deniz at TÜBİTAK Marmara Research Center Ankara Branch for his invaluable support during all phases of my thesis work. His great experience on power electronics, converters, solar energy area, and FPGA programming helped me a lot during the simulation, design, production, and testing phases of my thesis work. Without his support and experience, it would take me more time than I can ever imagine to finish my work.

A lot of my colleagues influenced and supported this work with their ideas and experience in the field. My dear friend and colleague Kamil Gökberk Ergin always helped me with his creative ideas whenever I needed solutions to the problems I encountered. Dr. Cem Özgür Gerçek and Emre Durna were among the great people who contributed theoretically and practically to my work with their experience on STATCOMs. Dr. Gökhan Şen was also among the people who provided me with his invaluable experience on power electronics and converters.

I would like to thank our technicians Mehmet Açar and Mehmet Arslan for their participation in the production stage of printed circuit board, Samil Arslan, Savaş Çataltepe, Mustafa Çayan, Ünsal Gege, Tolga Gürhayta, Mustafa Kılınç, İsmail Ünal, Cihan Yavuz, and Cahit Zeren for their participation in the installation stage of solar panels on the roof of electrical machines and power electronics laboratory in our department, and Bünyamin Bostan for his help during the tests conducted in the laboratory. I would also like to thank our procurement staff, Nevriye Sönmez and Vedat Şeker, during the allocation of materials needed for my thesis.

There were always people at our institute who contributed to my work at various times with their experience, and sometimes just with their positive outlook, which gave me the energy I needed at difficult times. All of our technicians have always showed their support for me with their technical abilities. Our drivers Mustafa Çalışkan and Okan Kılıçoğlu have helped me whenever I needed for allocation of materials to be used in the thesis work and gave me the positive energy I desired. My dear friend Uğur Anuk from Renpro Solar has also supported my work with his experience on renewable energy area.

Finally, and most importantly, I would like to express my gratitude to my dear family, my grandparents Hasan Hilmi Engin, Şafak Engin, my aunt Fatma Yurdagül Engin, my parents Ayşegül Güvengir and Haluk Güvengir for their never-ending support and confidence in me, without which I would not even be able to start my studies and work for my thesis. They will always be the ones whom I will acknowledge most for any success I acquire in this life.

## TABLE OF CONTENTS

| ABSTRACT                                   | r      |

|--------------------------------------------|--------|

| ÖZ                                         | i      |

| ACKNOWLEDGMENTS                            | Ξ      |

| TABLE OF CONTENTS xii                      | i      |

| LIST OF TABLES                             | i      |

| LIST OF FIGURES                            | i      |

| NOMENCLATURE xxii                          | ii     |

| LIST OF ABBREVIATIONS                      | /i     |

| CHAPTERS                                   |        |

| 1 INTRODUCTION 1                           | L      |

| 1.1 Overview                               | L      |

| 1.2 Switch-Mode Inverters                  | }      |

| 1.3 Selective Harmonic Elimination Method  | ,<br>) |

| 1.3.1 Application Areas                    | ,<br>) |

| 1.3.2 Algorithms Used for SHEM Equations 7 | 7      |

| 1.3.3 Offline and Online Applications 9    | )      |

|   | 1.4           | Scope of  | the Thesis   |                                      | 10 |

|---|---------------|-----------|--------------|--------------------------------------|----|

| 2 | PROB          | LEM DEI   | FINITION     |                                      | 13 |

|   | 2.1           | Variable  | DC Link V    | Voltage                              | 13 |

|   |               | 2.1.1     | Photovolta   | aic Applications                     | 15 |

|   |               | 2.1.2     | Traction A   | Applications                         | 19 |

|   | 2.2           | Discretiz | zation of Mo | odulation Index                      | 22 |

|   | 2.3           | Lookup    | Table Stora  | ge                                   | 25 |

|   | 2.4           | Infeasibl | e Region of  | Solution Space                       | 26 |

| 3 | APPLI<br>SHEM |           |              | CLE SWARM OPTIMIZATION TO            | 29 |

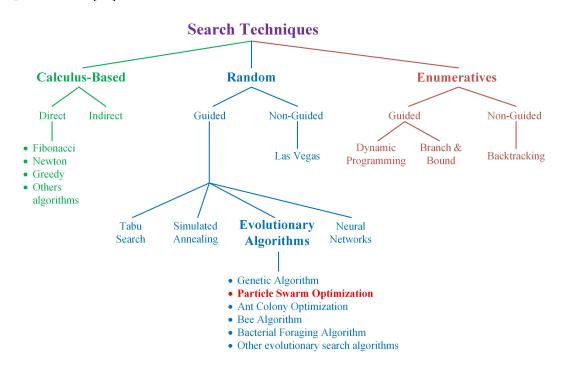

|   | 3.1           | Evolutio  | nary Search  | Algorithms                           | 29 |

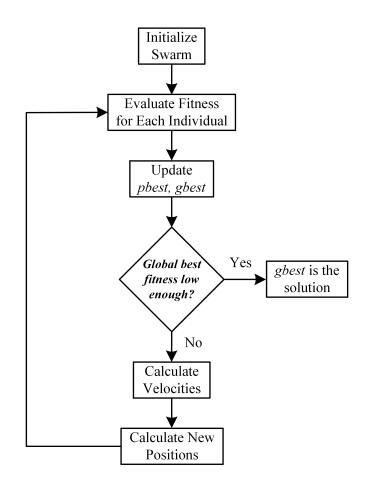

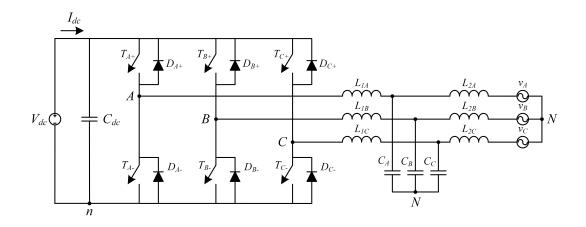

|   | 3.2           | Particle  | Swarm Opt    | imization                            | 32 |

|   | 3.3           | Problem   | Formulatio   | on                                   | 35 |

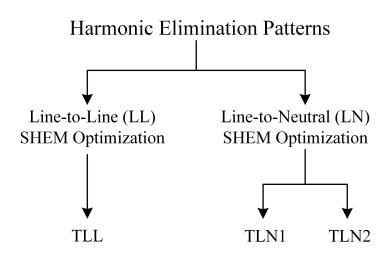

|   |               | 3.3.1     | SHEM Pat     | tterns                               | 37 |

|   |               |           | 3.3.1.1      | TLN1 Technique                       | 38 |

|   |               |           | 3.3.1.2      | TLN2 Technique                       | 40 |

|   |               |           | 3.3.1.3      | TLL Technique                        | 41 |

|   |               | 3.3.2     | Cost Func    | tion of the Problem                  | 42 |

|   |               | 3.3.3     | Results of   | the PSO Algorithm                    | 46 |

|   |               | 3.3.4     | Effects of . | Algorithm Parameters on the Solution | 48 |

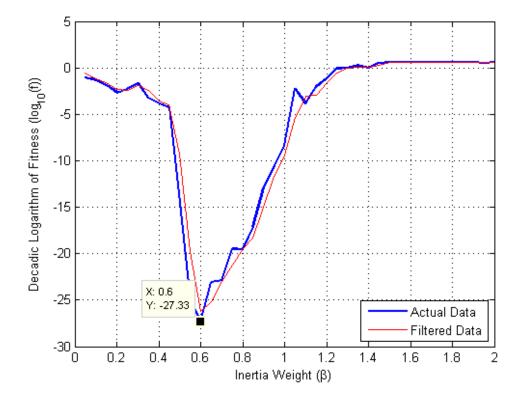

|   |               |           | 3.3.4.1      | Inertia Weight                       | 49 |

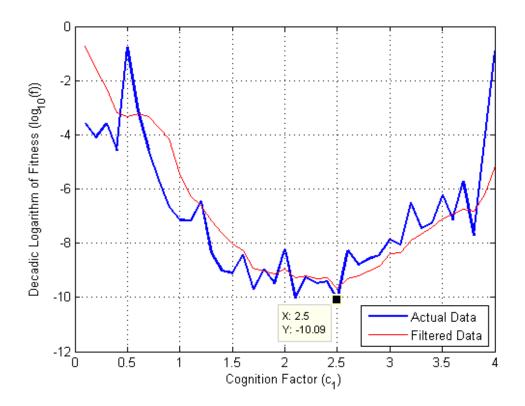

|   |               |           | 3.3.4.2      | Cognition Factor                     | 50 |

|   |               |           |              | xiii                                 |    |

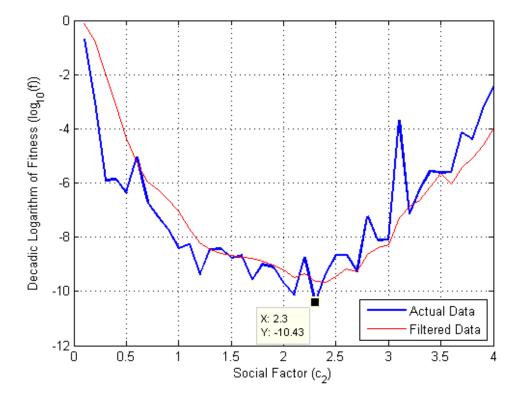

|   |       |          | 3.3.4.3    | Social Factor                        | 51 |

|---|-------|----------|------------|--------------------------------------|----|

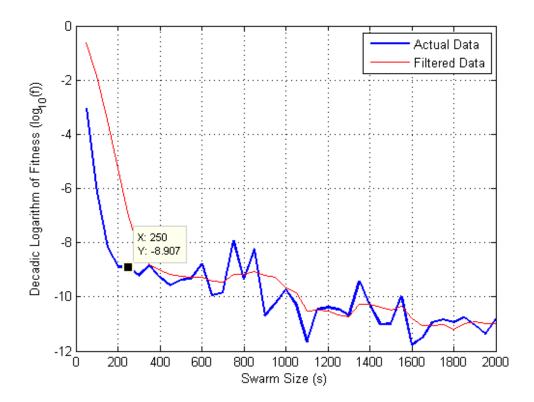

|   |       |          | 3.3.4.4    | Swarm Size                           | 52 |

|   |       |          | 3.3.4.5    | Number of Time Frames                | 53 |

|   |       |          | 3.3.4.6    | Modulation Index Penalty             | 54 |

| 4 | FPGA  | IMPLEN   | IENTATIO   | N OF ONLINE SHEM                     | 55 |

|   | 4.1   | Overview | w of FPGA  | S                                    | 55 |

|   |       | 4.1.1    | Structure  | and Application Areas                | 55 |

|   |       | 4.1.2    | Merits .   |                                      | 57 |

|   |       | 4.1.3    | Design Flo | DW                                   | 58 |

|   |       | 4.1.4    | Fixed-Poin | nt Arithmetic                        | 59 |

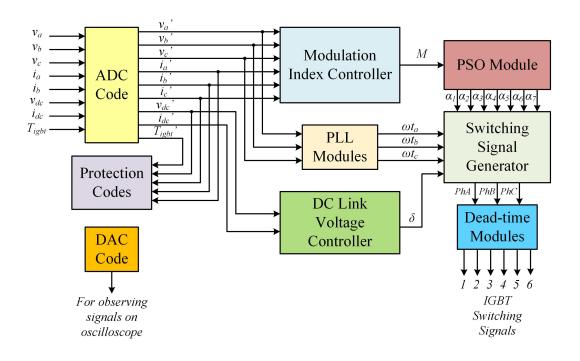

|   | 4.2   | Impleme  | ented FPGA | A Code                               | 60 |

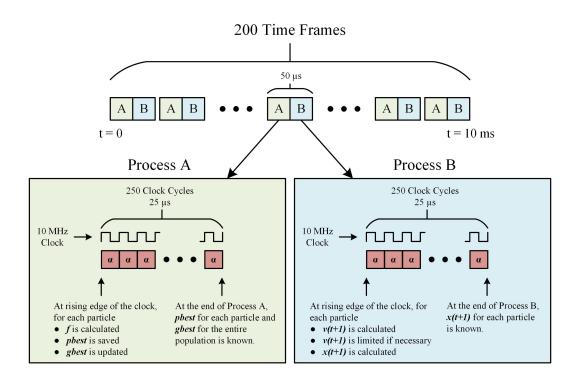

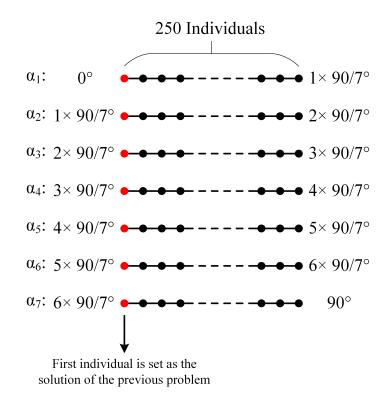

|   |       | 4.2.1    | PSO Mod    | ule                                  | 62 |

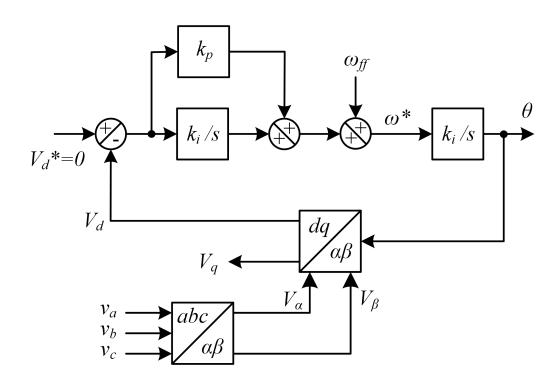

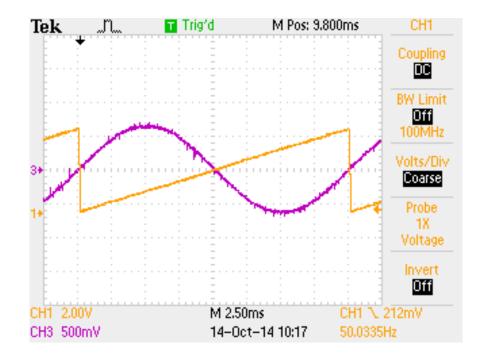

|   |       | 4.2.2    | PLL Mod    | ule                                  | 67 |

|   |       | 4.2.3    |            | on Index and DC Link Voltage Control | 69 |

|   |       | 4.2.4    | Dead-time  | e Module                             | 70 |

|   |       | 4.2.5    | ADC and    | DAC Code Processes                   | 71 |

|   |       | 4.2.6    | Protection | a Code Process                       | 72 |

| 5 | RESUI | LTS      |            |                                      | 73 |

|   | 5.1   | Simulati | ions       |                                      | 73 |

|   |       | 5.1.1    | ISim Simu  | llations of FPGA Code                | 73 |

|   |       | 5.1.2    | Hardware   | Co-simulation of FPGA Code           | 77 |

|   |       |          |            |                                      |    |

|       |       | 5.1.3   | Simulink I  | Results                                   | 84  |

|-------|-------|---------|-------------|-------------------------------------------|-----|

|       |       |         | 5.1.3.1     | Grid Voltage and PLL Output               | 88  |

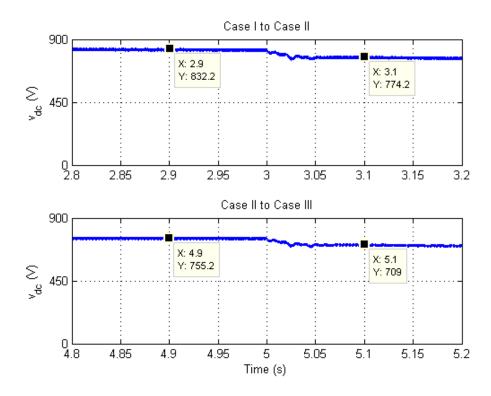

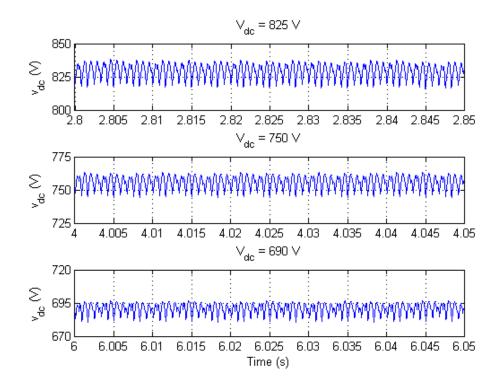

|       |       |         | 5.1.3.2     | Input DC Link Voltage                     | 88  |

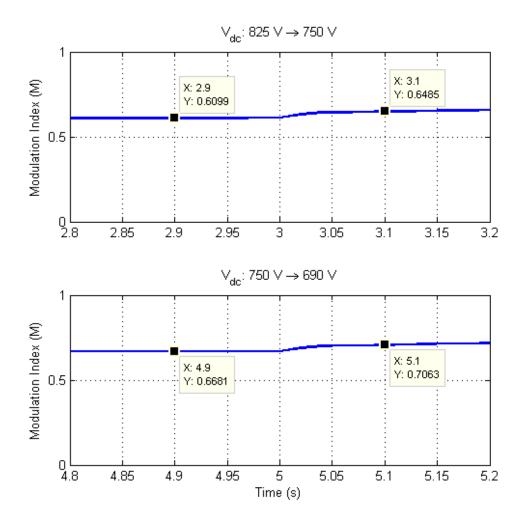

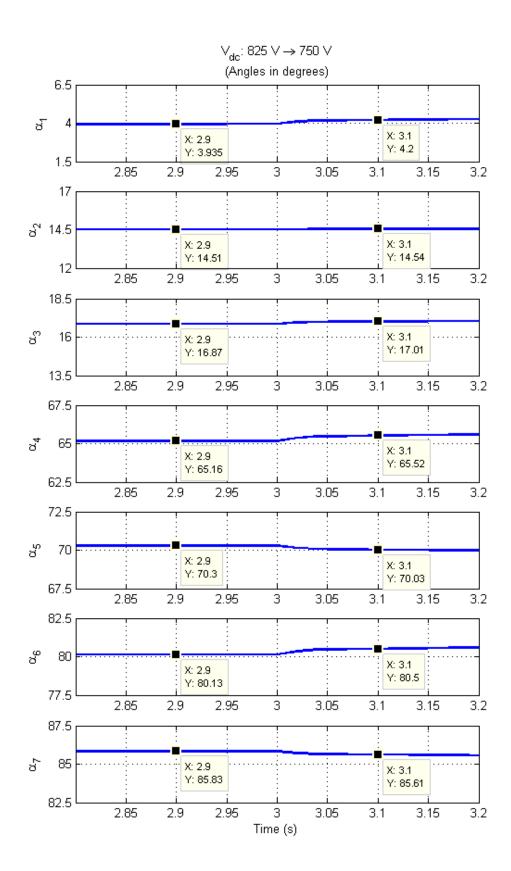

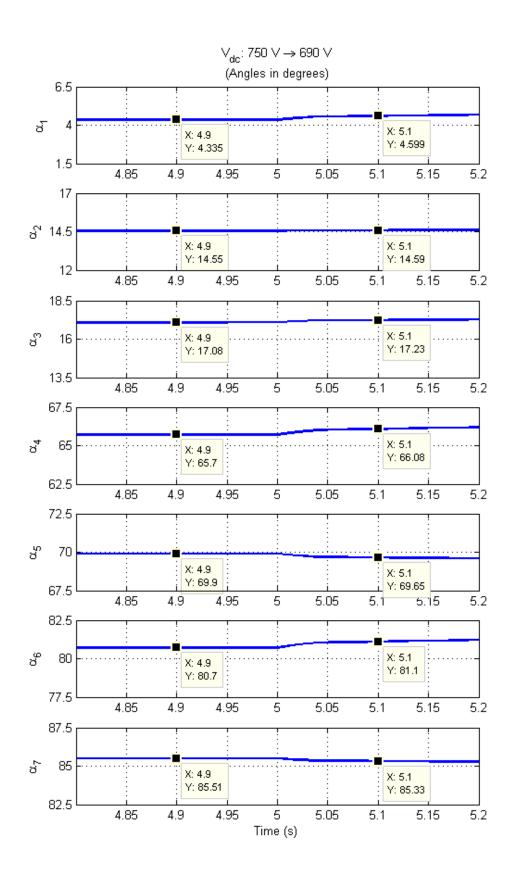

|       |       |         | 5.1.3.3     | Modulation Index and Switching<br>Angles  | 90  |

|       |       |         | 5.1.3.4     | Inverter Output Voltage                   | 93  |

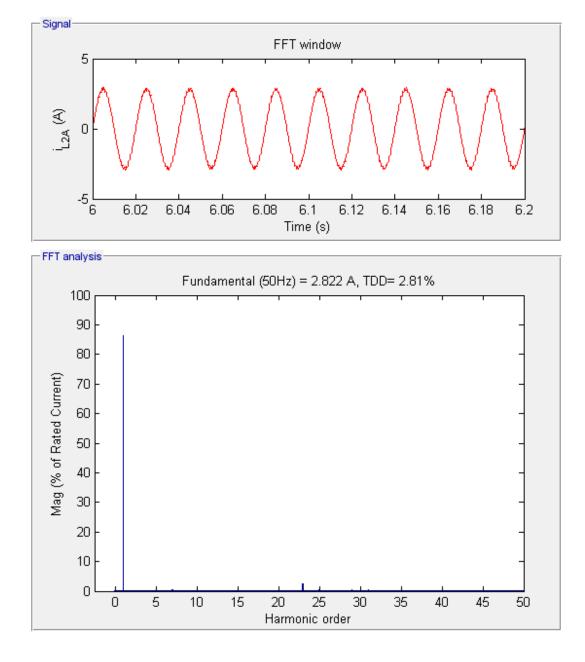

|       |       |         | 5.1.3.5     | Inverter and Grid Side Output<br>Currents | 99  |

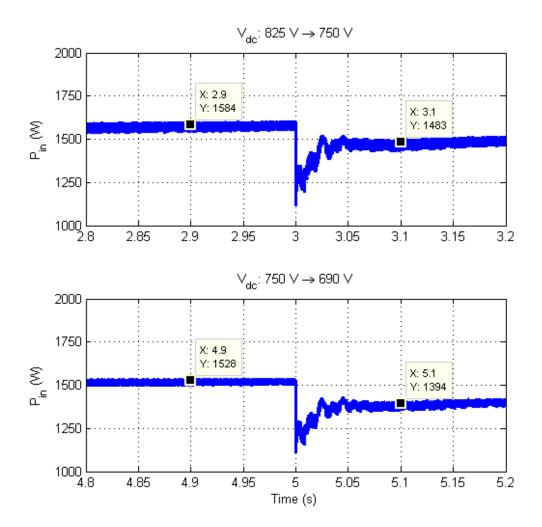

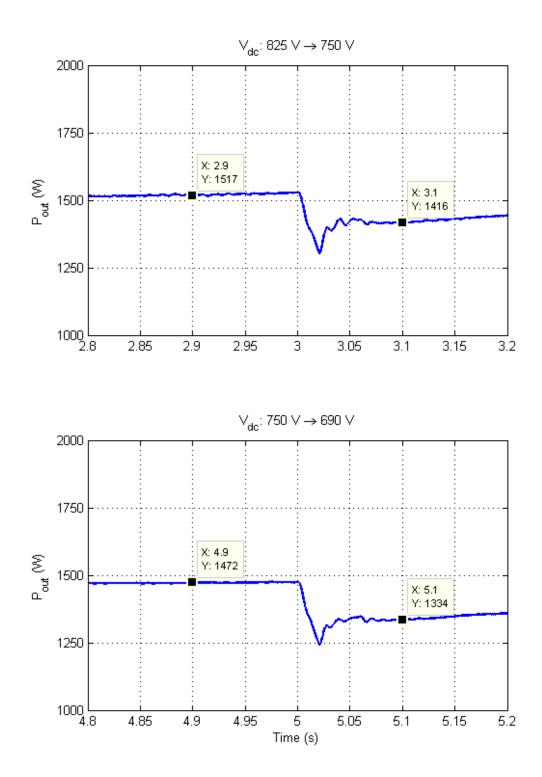

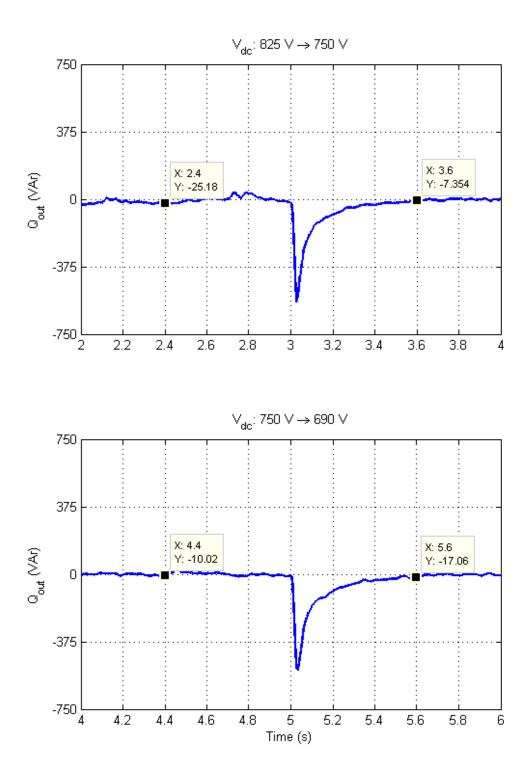

|       |       |         | 5.1.3.6     | Input and Output Power of the<br>Inverter | 106 |

|       | 5.2   | Experim | ental Resul | ts                                        | 109 |

|       |       | 5.2.1   | Grid Volta  | age and PLL Output                        | 111 |

|       |       | 5.2.2   | Input DC    | Link Voltage                              | 111 |

|       |       | 5.2.3   | Modulatio   | n Index and Switching Angles              | 113 |

|       |       | 5.2.4   | Inverter O  | utput Voltage                             | 113 |

|       |       | 5.2.5   | Inverter a  | nd Grid Side Output Currents              | 120 |

|       |       | 5.2.6   | Input and   | Output Power of the Inverter              | 129 |

| 6     | CONC  | LUSION  |             |                                           | 131 |

| REFER | ENCES |         |             |                                           | 137 |

| APPEN | DICES |         |             |                                           |     |

| А     | PCB S | СНЕМАТ  | TICS DRAV   | VN IN PROTEUS PROFESSIONAL                | 145 |

B LABORATORY EQUIPMENT USED FOR TESTS . . . . . . . 151

## LIST OF TABLES

# TABLES

| Table 2.1 | Variation of MPP Voltage Against Changing Solar Irradiance |     |

|-----------|------------------------------------------------------------|-----|

| and A     | Ambient Temperature                                        | 18  |

| Table 2.2 | Nominal Voltages and Their Permissible Limits for Traction |     |

| Syste     |                                                            | 21  |

| U         |                                                            |     |

| Table 2.3 | Example Lookup Table for Switching Angles for Different    |     |

| Modu      | lation Index Values                                        | 23  |

|           |                                                            |     |

| Table 3.1 | Specifications of the Inverter and Components              | 36  |

| Table 3.2 | PSO Algorithm Default Parameters                           | 46  |

|           |                                                            | -   |

| Table 3.3 | Switching Angle Sets Found for Different Modulation Index  |     |

| Value     | s by the PSO Algorithm                                     | 47  |

|           |                                                            |     |

| Table 4.1 | Examples of Two's Complement Signed Fixed-Point Arithmetic | 59  |

| Table 4.2 | Specifications of XEM6010-LX150 Module                     | 61  |

|           |                                                            | -   |

| Table 4.3 | Device Utilization Summary Report for PSO Module           | 66  |

| Table 4.4 | Device Utilization Summary Report for Entire VHDL Code .   | 67  |

|           |                                                            |     |

| Table 5.1 | Switching Angles Found from Hardware Co-simulation         | 80  |

| 10010 011 |                                                            | 00  |

| Table 5.2 | Specifications of the Inverter and Components              | 85  |

| Table 5.3 | Switching Angles Found by PSO Module of FPGA for Each Case | 113 |

| 10010 0.0 |                                                            |     |

## LIST OF FIGURES

## FIGURES

| Figure 1.1 (  | General Classification of Inverters                         | 4  |

|---------------|-------------------------------------------------------------|----|

| Figure 1.2    | Application of SHEM to Two-Level VSI                        | 5  |

| Figure 1.3 (  | Output Voltage of Nine-Level Multilevel Inverter            | 6  |

| Figure 1.4    | Algorithms Used for Solution of SHEM Equations              | 9  |

| Figure 2.1 S  | Single-Phase Half-Bridge Inverter                           | 14 |

| Figure 2.2    | Single-Phase Full-Bridge Inverter                           | 14 |

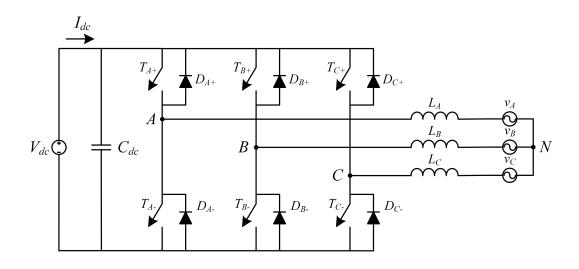

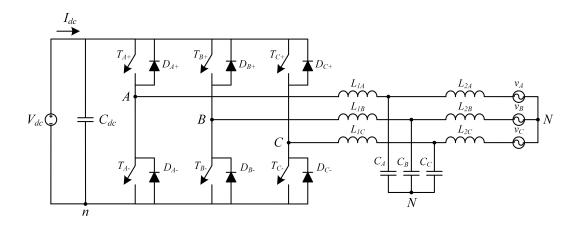

| Figure 2.3    | Three-Phase Full-Bridge Inverter                            | 14 |

| Figure 2.4    | Worldwide Growth Rate of Installed Capacity for Different   |    |

| Renewa        | ble Technologies in 2012 and between 2007 and 2012 $\ldots$ | 16 |

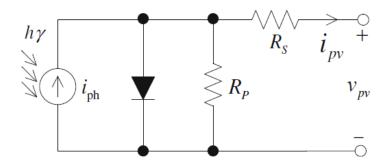

| Figure 2.5 1  | PV Cell Electrical Equivalent Circuit                       | 17 |

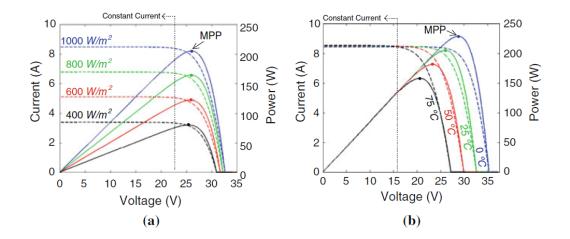

| Figure 2.6 l  | I-V and P-V Characteristics of a PV Panel                   | 18 |

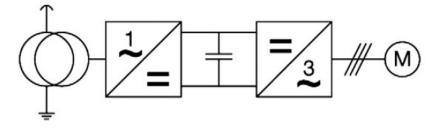

| Figure 2.7    | AC Railway Power Supply Systems                             | 19 |

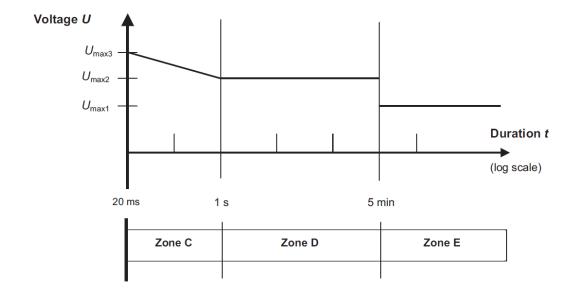

| Figure 2.8    | Maximum Value of the Catenary Voltage According to the      |    |

| Duratio       | n                                                           | 21 |

| Figure 2.9    | Circuit Diagram of Three-Phase Two-Level Inverter           | 23 |

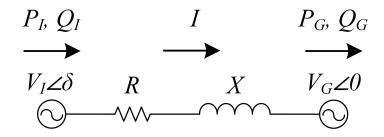

| Figure 2.10 S | Single-Line Diagram of the Three-Phase System               | 24 |

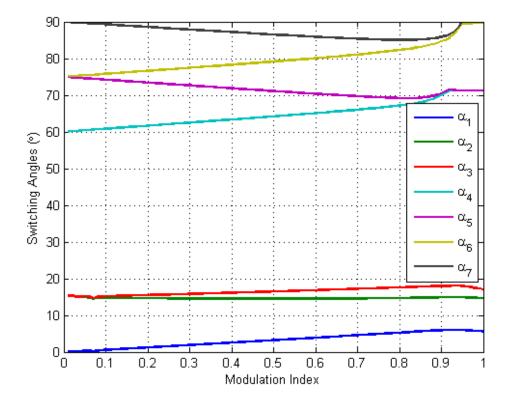

| Figure 2.11 S | Switching Angles vs Modulation Index Graph for the VSI      | 27 |

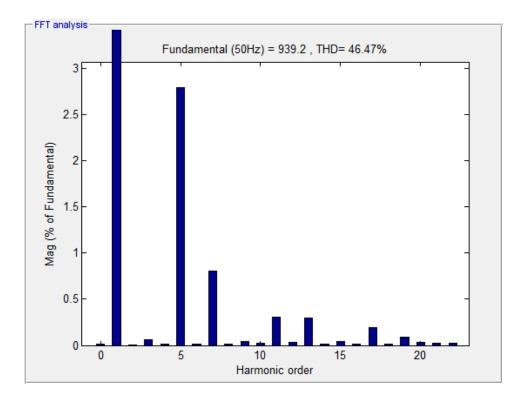

| Figure 2.12 | FFT Analysis of the Output Voltage Waveform with M=0.95 $$   | 28 |

|-------------|--------------------------------------------------------------|----|

| Figure 3.1  | Search Techniques Tree                                       | 30 |

| Figure 3.2  | Basic Flowchart of PSO                                       | 35 |

| Figure 3.3  | Three-Phase Two-Level Grid-Connected Inverter                | 36 |

| Figure 3.4  | Harmonic Elimination Patterns for Three-Phase Inverters      | 37 |

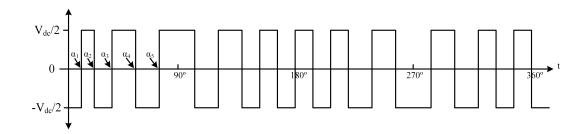

| Figure 3.5  | Line-to-Neutral Voltage for TLN1 Technique                   | 39 |

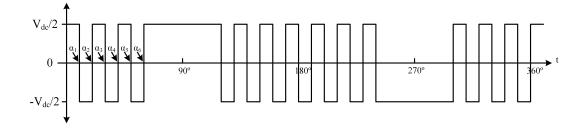

| Figure 3.6  | Line-to-Neutral Voltage for TLN2 Technique                   | 40 |

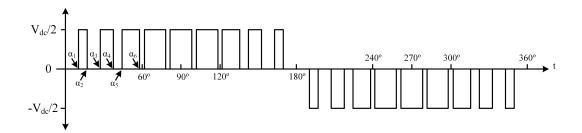

| Figure 3.7  | Line-to-Neutral Voltage for TLL Technique                    | 41 |

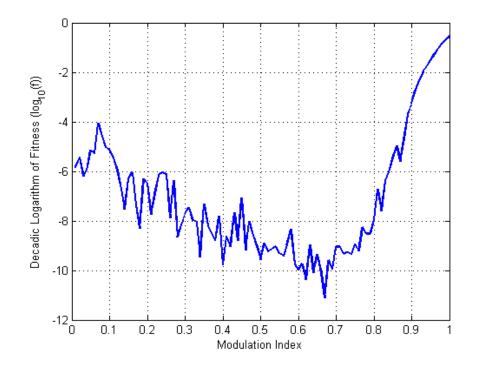

| Figure 3.8  | Decadic Logarithm of Fitness vs Modulation Index             | 47 |

| Figure 3.9  | Decadic Logarithm of Fitness vs Inertia Weight               | 49 |

| Figure 3.10 | Decadic Logarithm of Fitness vs Cognition Factor             | 50 |

| Figure 3.11 | Decadic Logarithm of Fitness vs Social Factor                | 51 |

| Figure 3.12 | Decadic Logarithm of Fitness vs Swarm Size                   | 52 |

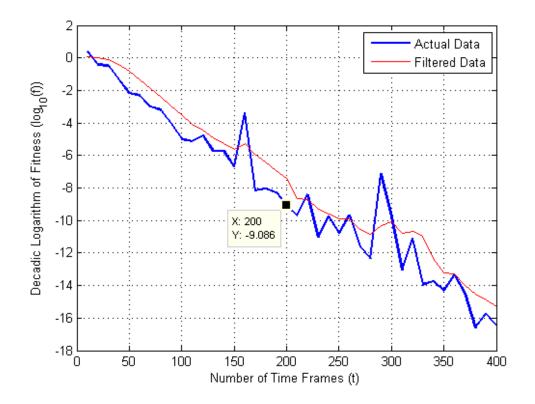

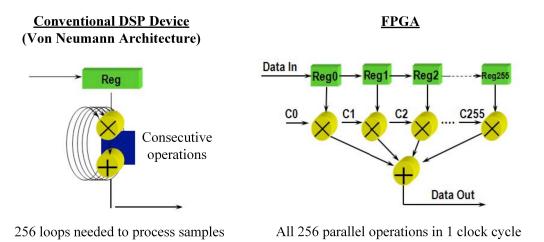

| Figure 3.13 | Decadic Logarithm of Fitness vs Number of Time Frames        | 53 |

| Figure 3.14 | Time Frame vs Modulation Index Penalty                       | 54 |

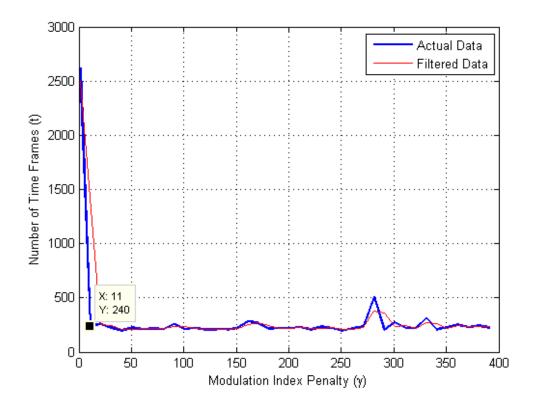

| Figure 4.1  | Internal Structure of a Generic FPGA                         | 56 |

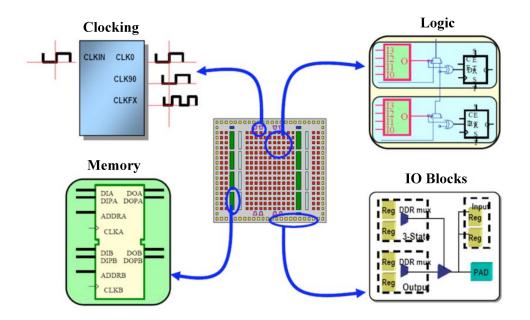

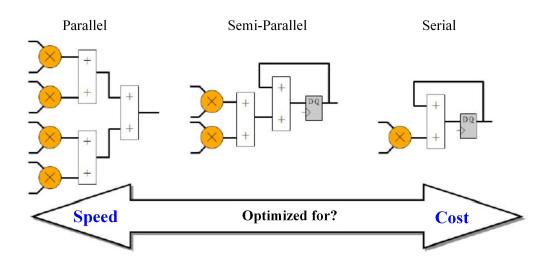

| Figure 4.2  | FIR Filter Comparison between DSP and FPGA                   | 57 |

| Figure 4.3  | Speed/Area Trade-off in FPGAs $\hdots$                       | 58 |

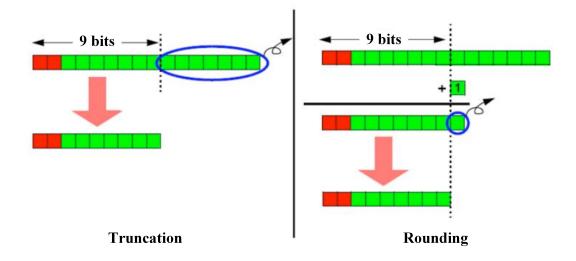

| Figure 4.4  | Truncation vs Rounding in Fixed-Point Representation         | 60 |

| Figure 4.5  | Schematic of the VSI Control Blocks Implemented in FPGA      | 61 |

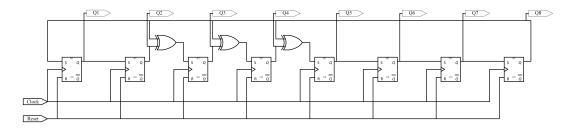

| Figure 4.6  | Diagram of an 8-bit LFSR                                     | 63 |

| Figure 4.7  | Mindset Behind the PSO Module in the VHDL Code $\ . \ . \ .$ | 65 |

| Figure 4.8 Lattice Structure Used for Initialization of the Population         | 65 |

|--------------------------------------------------------------------------------|----|

| Figure 4.9 Three-Phase Synchronous Reference Frame PLL Diagram                 | 68 |

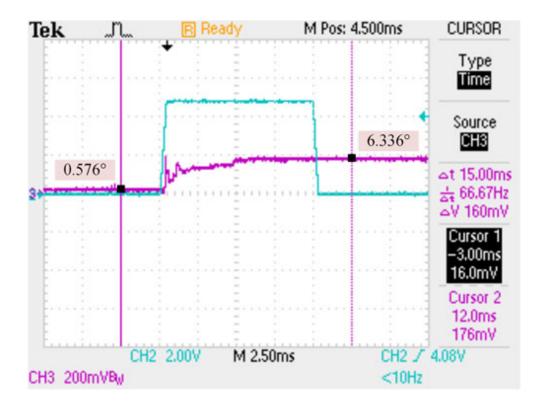

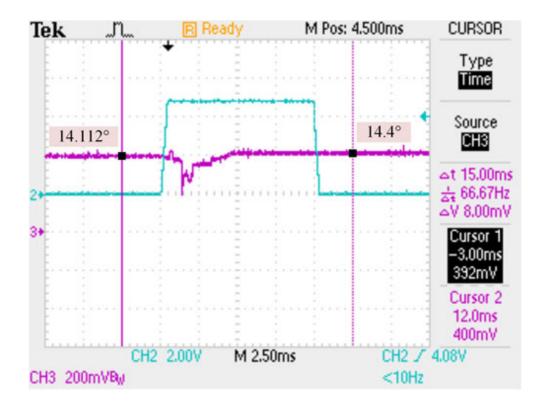

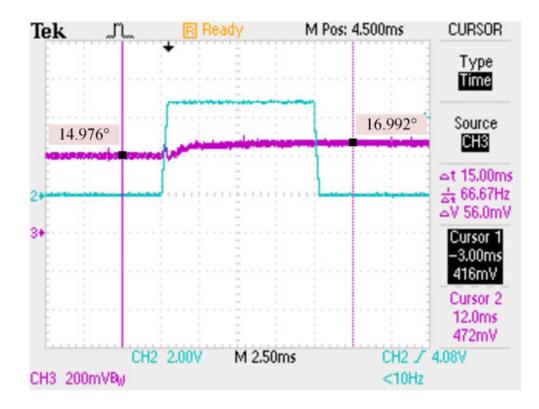

| Figure 4.10 Acquired PLL Output from the Implemented FPGA Code $$ .            | 69 |

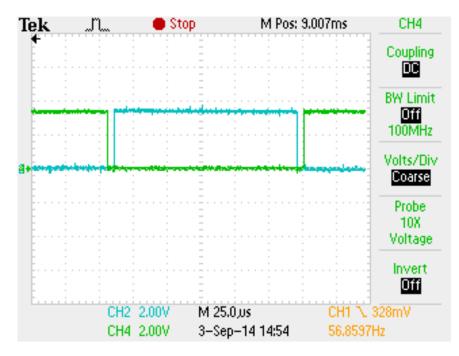

| Figure 4.11 Implemented Dead-time between Upper and Lower Switching<br>Signals | 70 |

| Figure 5.1 Screenshot of the ISim Simulator                                    | 75 |

| Figure 5.2 Gradual Decrease in Global Best Fitness and Consequent              |    |

| Changes in Switching Angles                                                    | 76 |

| Figure 5.3 Opal Kelly FrontPanel Interface                                     | 77 |

| Figure 5.4 Implemented GUI for Observing and Controlling Signals               | 78 |

| Figure 5.5 Online Change in Switching Angle $\alpha_1$                         | 81 |

| Figure 5.6 Online Change in Switching Angle $\alpha_2$                         | 81 |

| Figure 5.7 Online Change in Switching Angle $\alpha_3$                         | 82 |

| Figure 5.8 Online Change in Switching Angle $\alpha_4$                         | 82 |

| Figure 5.9 Online Change in Switching Angle $\alpha_5$                         | 83 |

| Figure 5.10 Online Change in Switching Angle $\alpha_6$                        | 83 |

| Figure 5.11 Online Change in Switching Angle $\alpha_7$                        | 84 |

| Figure 5.12 Three-Phase Two-Level Grid-Connected Inverter                      | 84 |

| Figure 5.13 Solver Parameters for Simulink Simulation                          | 86 |

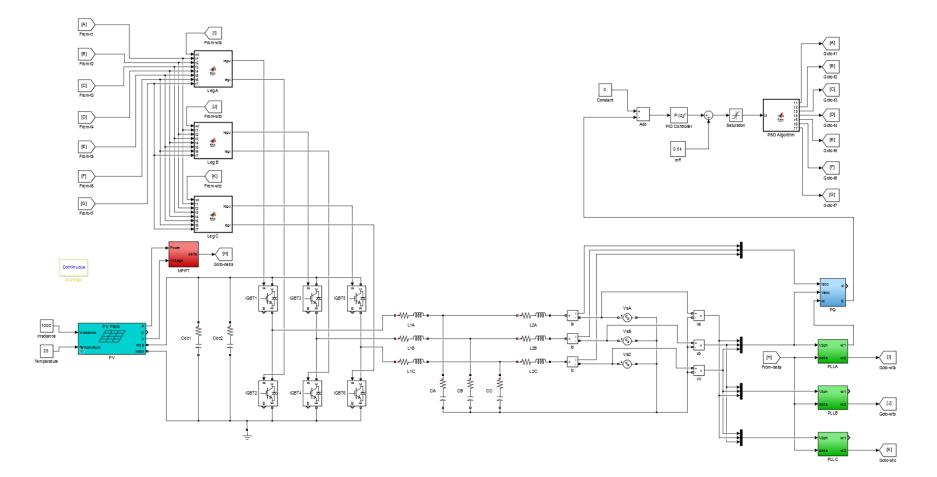

| Figure 5.14 Diagram of the Circuit Simulated in Simulink                       | 87 |

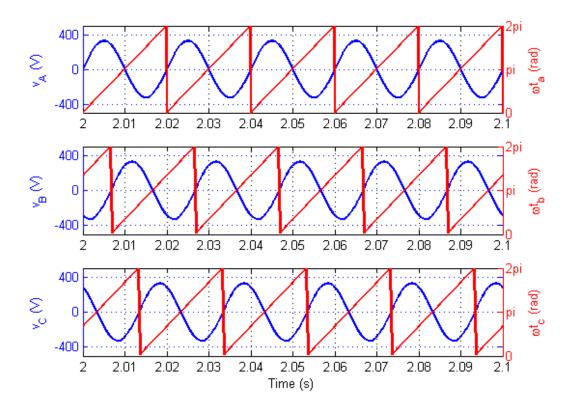

| Figure 5.15 Three-Phase Grid Voltage and PLL Output for Each Phase (Simulink)  | 88 |

| Figure 5.16 Changes in Input DC Link Voltage of the Inverter (Simulink)        | 89 |

| Figure 5.17 Input DC Link Voltage Ripple of the Inverter (Simulink) $\therefore$ 89                     |

|---------------------------------------------------------------------------------------------------------|

| Figure 5.18 Changes in Modulation Index of the Inverter (Simulink) 90                                   |

| Figure 5.19 Changes in Switching Angles (Case I to Case II) (Simulink) . $91$                           |

| Figure 5.20 Changes in Switching Angles (Case II to Case III) (Simulink) 92                             |

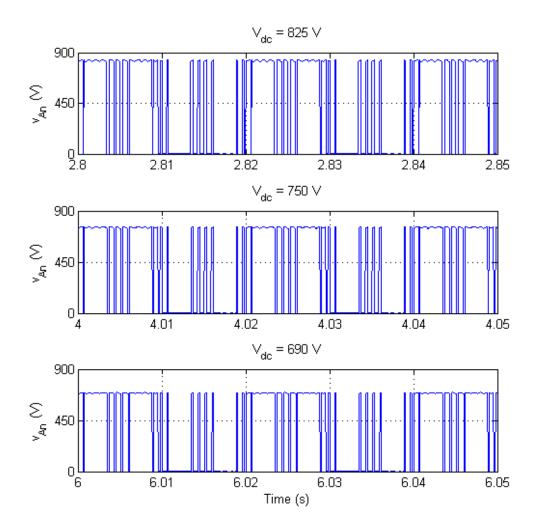

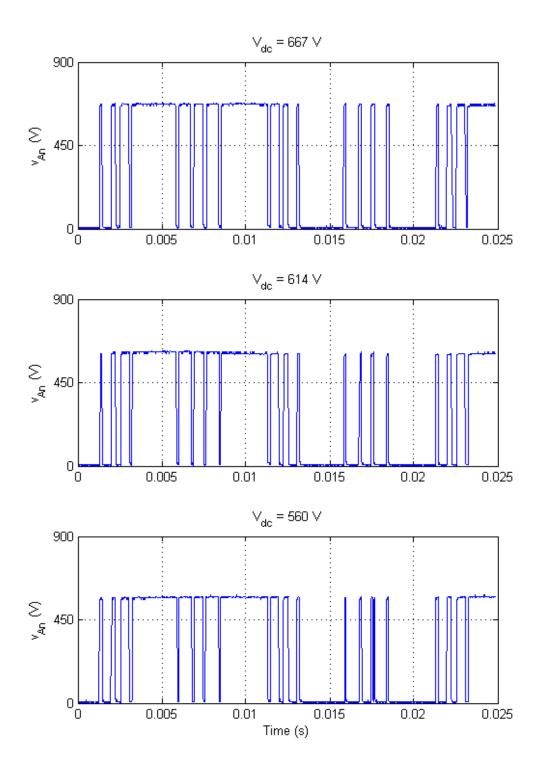

| Figure 5.21 Inverter Midpoint Output Voltage for Each Case (Simulink) . 93                              |

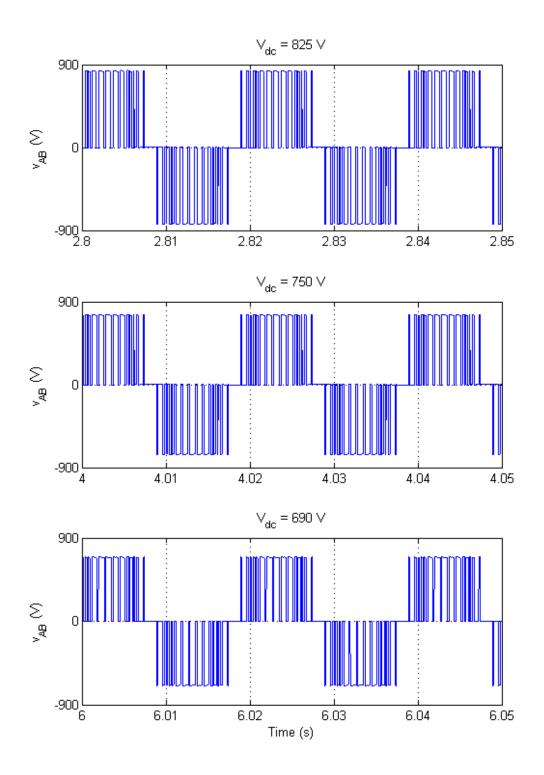

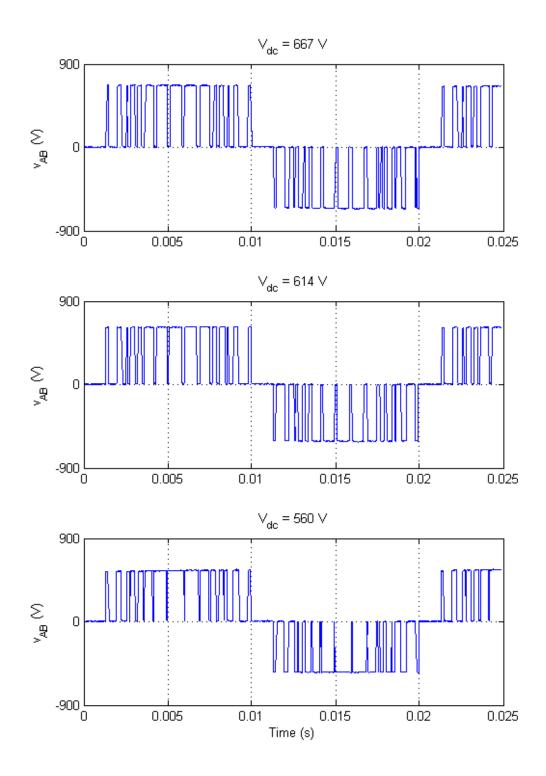

| Figure 5.22 Inverter Line-to-Line Output Voltage for Each Case (Simulink) 94                            |

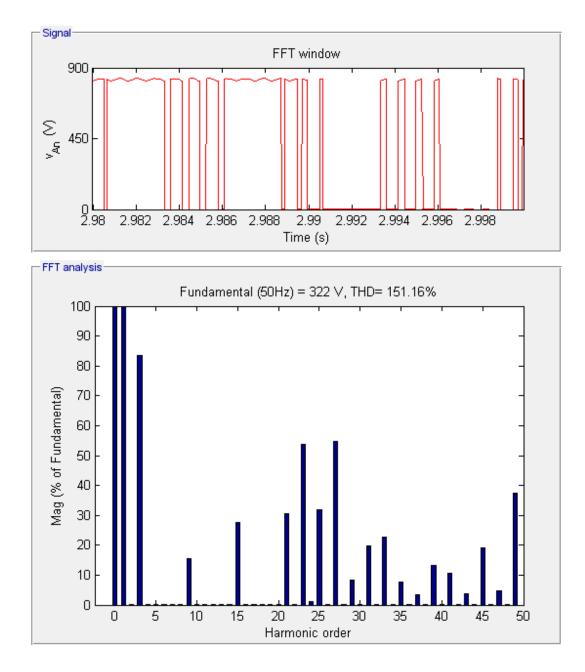

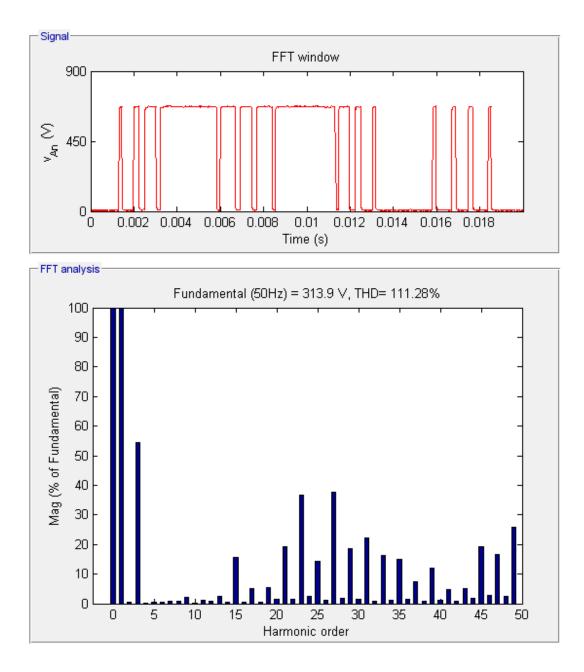

| Figure 5.23 FFT Analysis of the Inverter Midpoint Output Voltage for         Case I (Simulink)       95 |

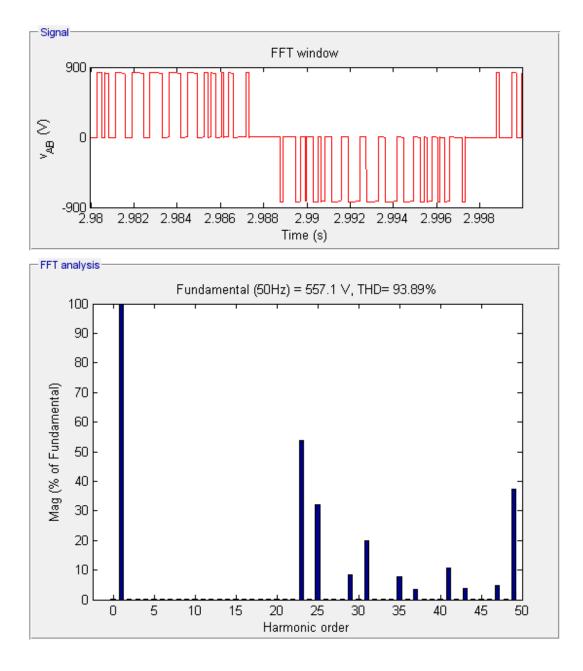

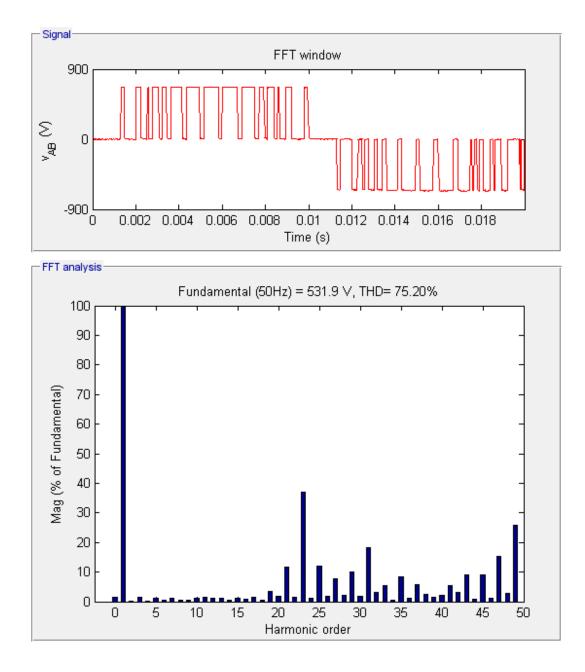

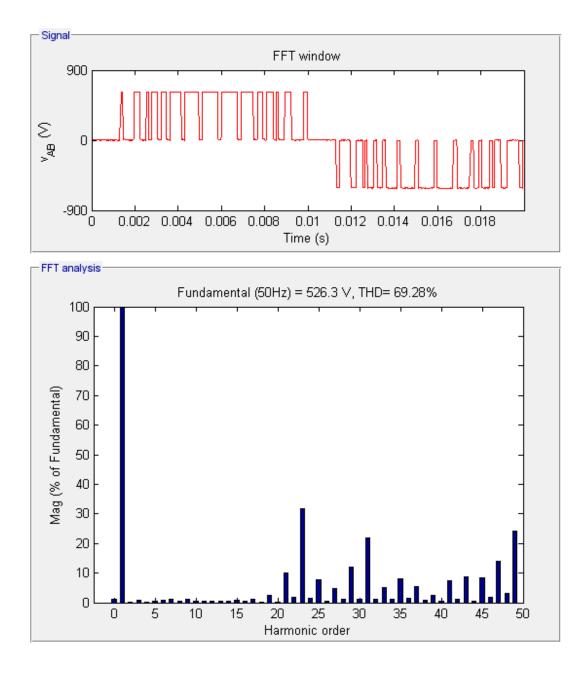

| Figure 5.24 FFT Analysis of the Line-to-Line Output Voltage for Case I         (Simulink)       96      |

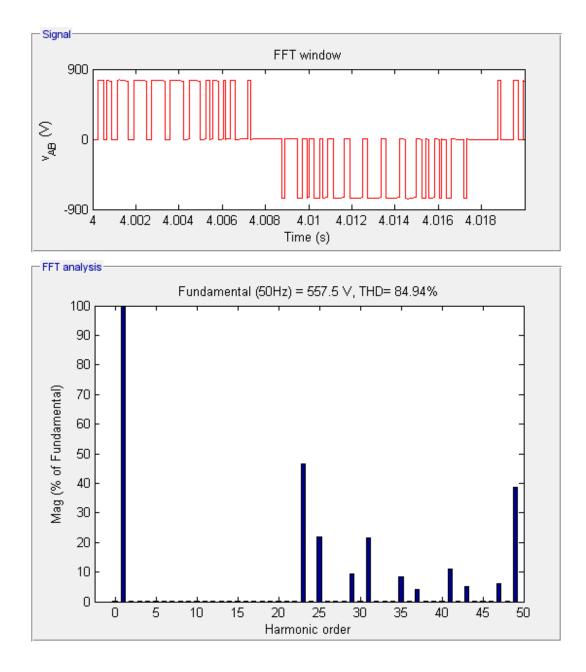

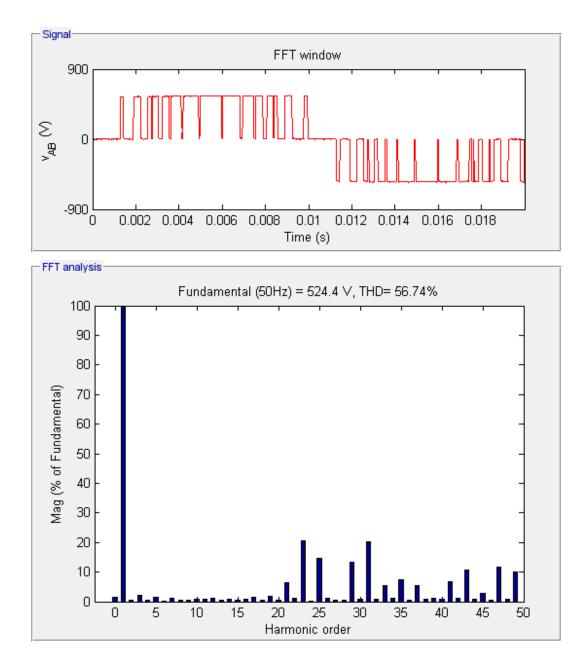

| Figure 5.25 FFT Analysis of the Line-to-Line Output Voltage for Case II         (Simulink)       97     |

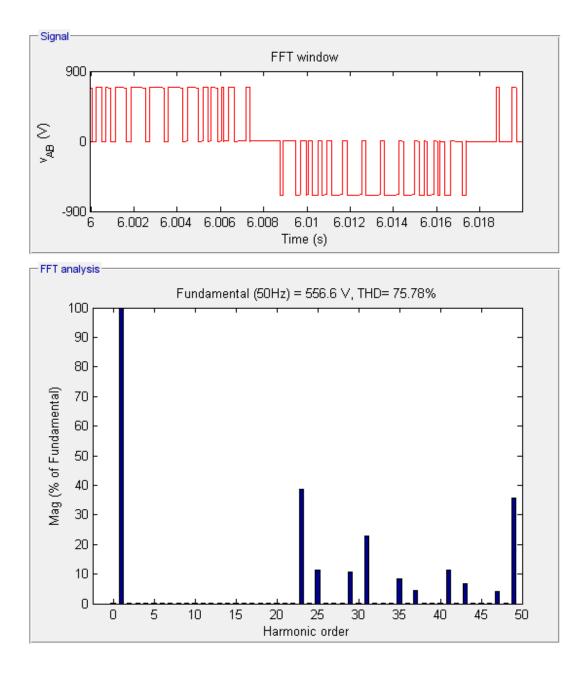

| Figure 5.26 FFT Analysis of the Line-to-Line Output Voltage for Case III         (Simulink)       98    |

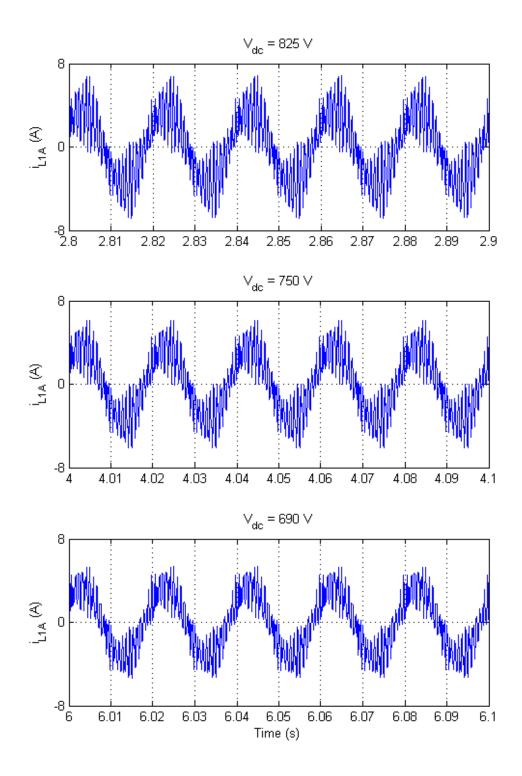

| Figure 5.27 Inverter-Side Current for Each Case (Simulink) 100                                          |

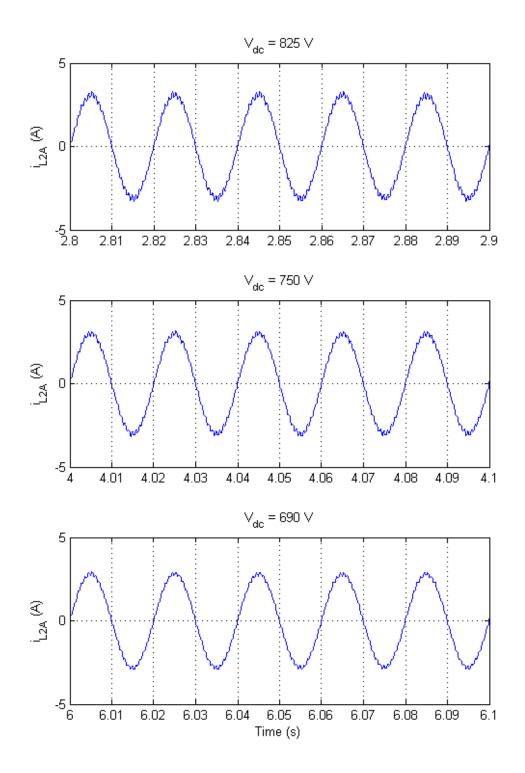

| Figure 5.28 Grid-Side Current for Each Case (Simulink)                                                  |

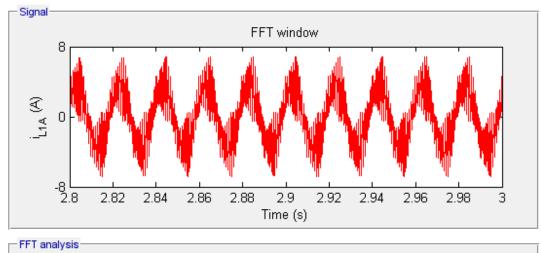

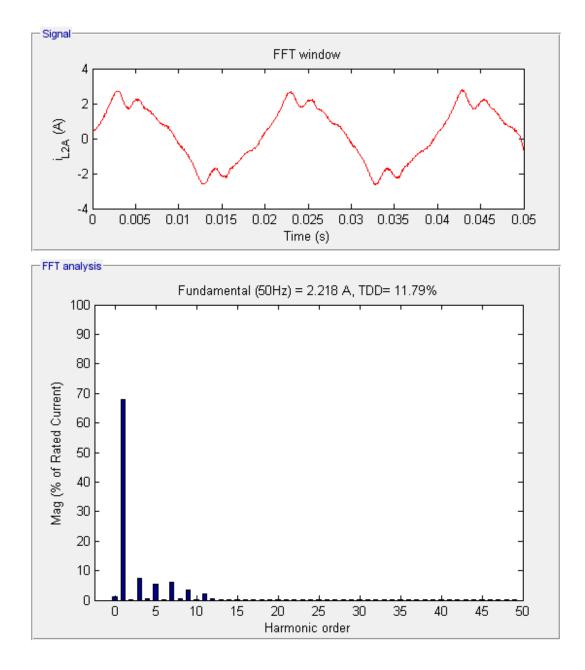

| Figure 5.29 FFT Analysis of the Inverter-Side Current for Case I (Simulink)102                          |

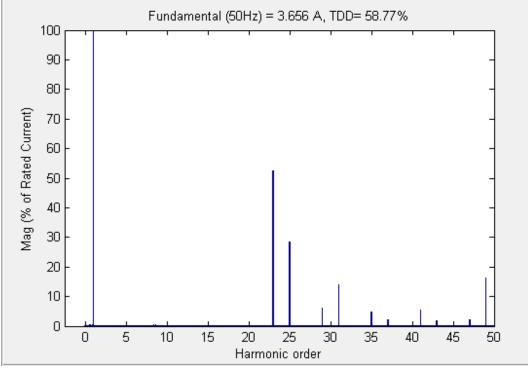

| Figure 5.30 FFT Analysis of the Grid-Side Current for Case I (Simulink) 103                             |

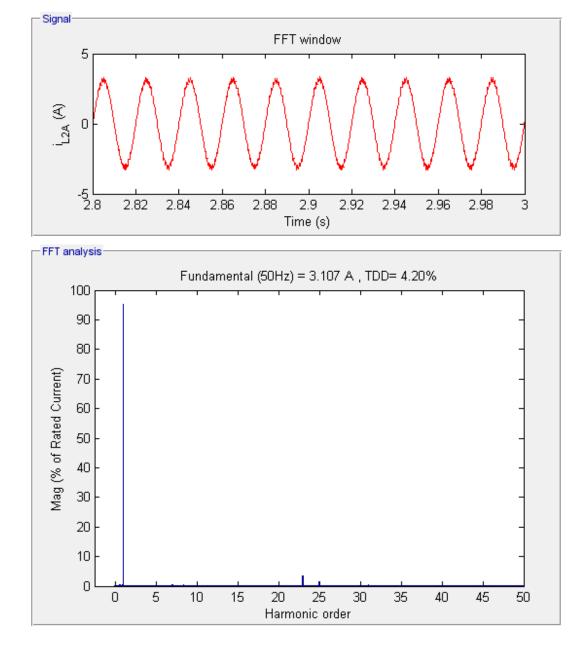

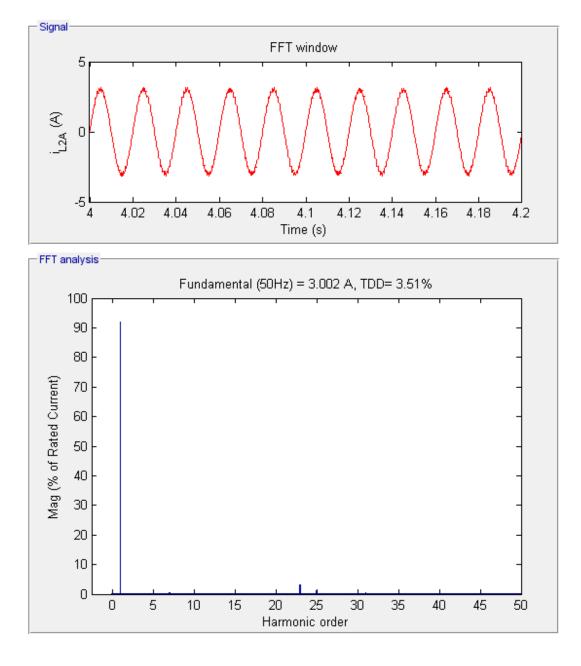

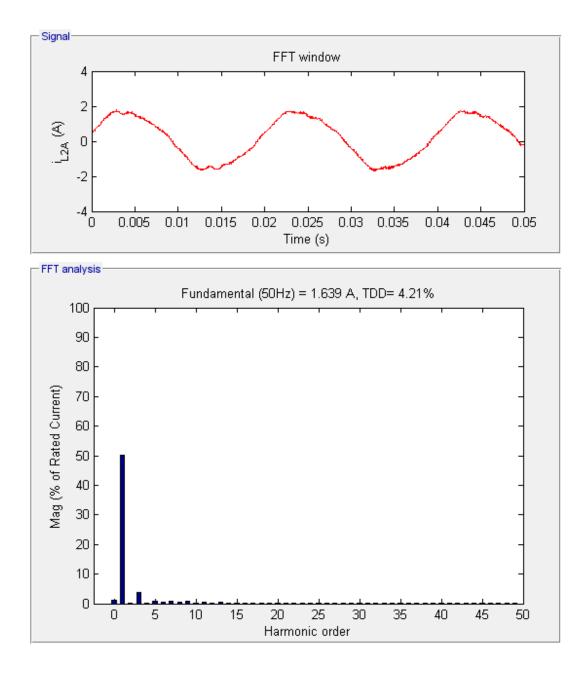

| Figure 5.31 FFT Analysis of the Grid-Side Current for Case II (Simulink) 104                            |

| Figure 5.32 FFT Analysis of the Grid-Side Current for Case III (Simulink) 105                           |

| Figure 5.33 Changes in Active Power Input of the Inverter (Simulink) 106                                |

| Figure 5.34 Changes in Active Power Output of the Inverter (Simulink) . $107$                           |

| Figure 5.35 Changes in Reactive Power Output of the Inverter (Simulink) 108                             |

| Figure 5.36 Close-up Photograph of the Implemented PCB $\ldots$ .                                                      | 110  |

|------------------------------------------------------------------------------------------------------------------------|------|

| Figure 5.37 Test Setup in the Laboratory                                                                               | 110  |

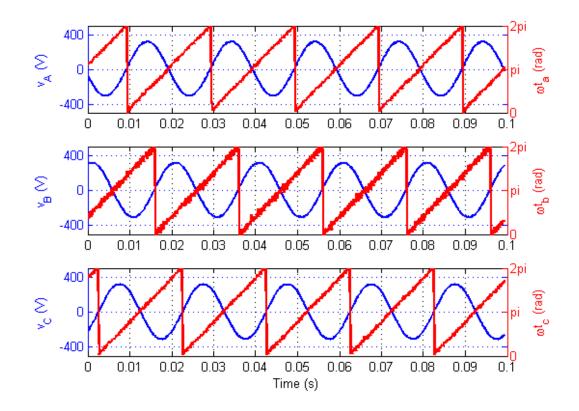

| Figure 5.38 Three-Phase Grid Voltage and PLL Output for Each Phase (Experimental)                                      | 111  |

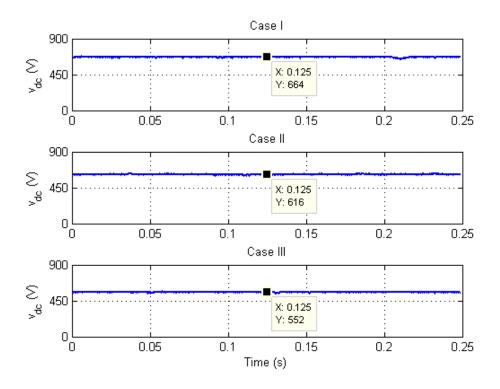

| Figure 5.39 Input DC Link Voltage of the Inverter (Experimental)                                                       | 112  |

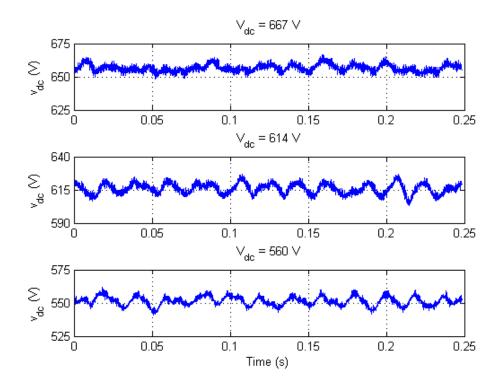

| Figure 5.40 Input DC Link Voltage Ripple of the Inverter (Experimental)                                                | 112  |

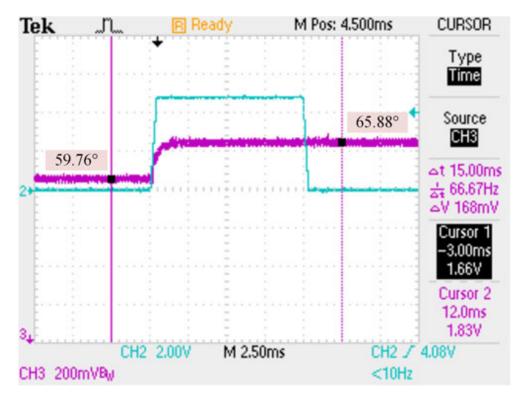

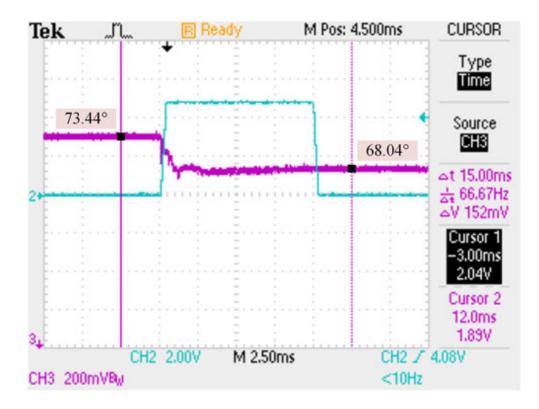

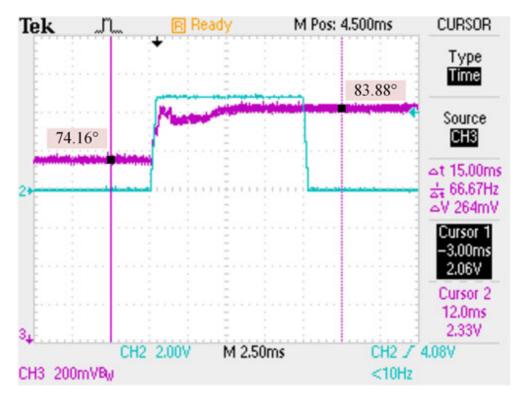

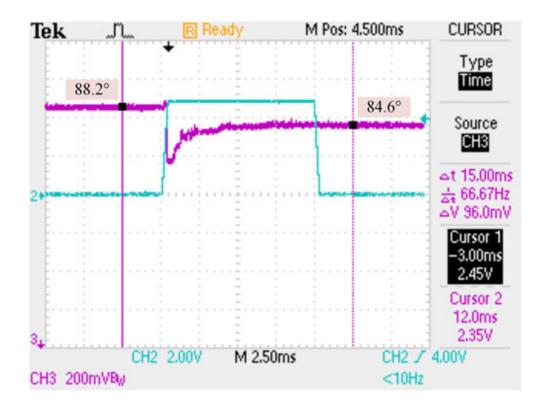

| Figure 5.41 Inverter Midpoint Output Voltage for Each Case (Experimental)                                              | )114 |

| Figure 5.42 Inverter Line-to-Line Output Voltage for Each Case<br>(Experimental)                                       | 115  |

| Figure 5.43 FFT Analysis of the Inverter Midpoint Output Voltage for<br>Case I (Experimental)                          | 116  |

| Figure 5.44 FFT Analysis of the Line-to-Line Output Voltage for Case I (Experimental)                                  | 117  |

| Figure 5.45 FFT Analysis of the Line-to-Line Output Voltage for Case II (Experimental)                                 | 118  |

| Figure 5.46 FFT Analysis of the Line-to-Line Output Voltage for Case III (Experimental)                                | 119  |

| Figure 5.47 Grid-Side LCL Filter Current Recorded in TÜBİTAK<br>Laboratory When the Inverter is Idle (Experimental)    | 121  |

| Figure 5.48 Grid-Side LCL Filter Current Recorded in Department<br>Laboratory When the Inverter is Idle (Experimental) | 122  |

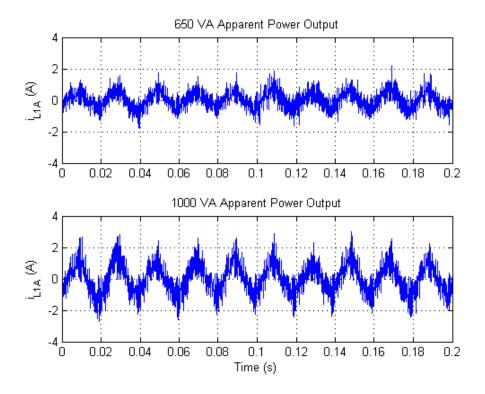

| Figure 5.49 Inverter-Side Current for Different Power Outputs<br>(Experimental)                                        | 124  |

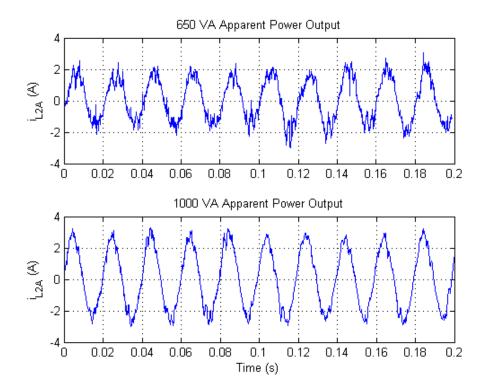

| Figure 5.50 Grid-Side Current for Different Power Outputs (Experimental)                                               | 124  |

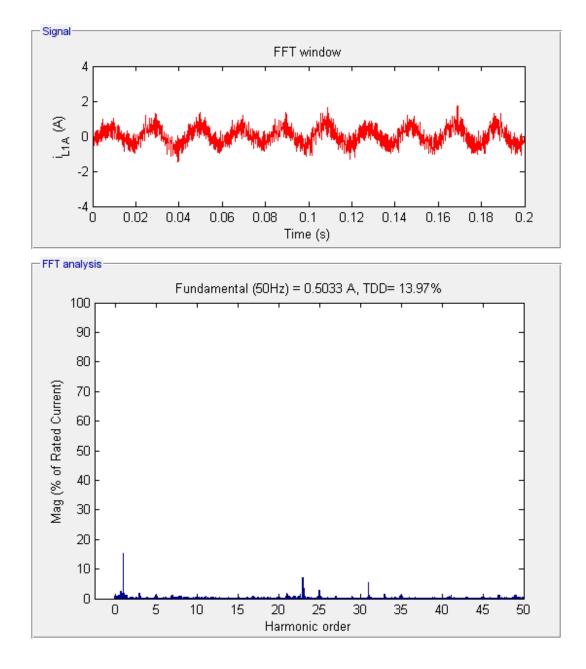

| Figure 5.51 FFT Analysis of the Inverter-Side Current for 650 VA Output (Experimental)                        | 125 |

|---------------------------------------------------------------------------------------------------------------|-----|

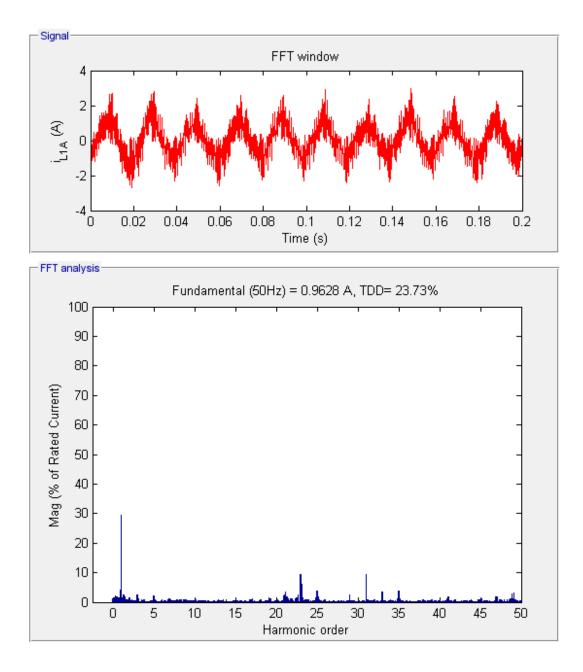

| Figure 5.52 FFT Analysis of the Inverter-Side Current for 1000 VA Output (Experimental)                       | 126 |

| Figure 5.53 FFT Analysis of the Grid-Side Current for 650 VA Output (Experimental)                            | 127 |

| Figure 5.54 FFT Analysis of the Grid-Side Current for 1000 VA Output (Experimental)                           | 128 |

| Figure 5.55 Total Apparent, Active and Reactive Output Power of the Inverter ( $Q_G=0$ VAr) (Experimental)    | 129 |

| Figure 5.56 Total Apparent, Active and Reactive Output Power of the Inverter ( $Q_G$ =500 VAr) (Experimental) | 129 |

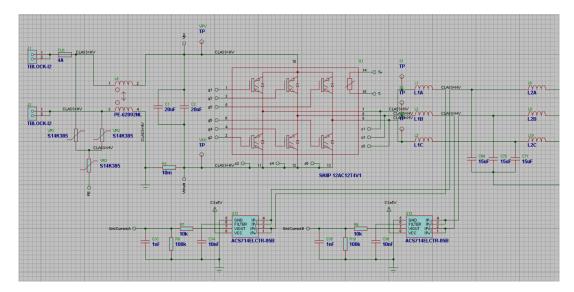

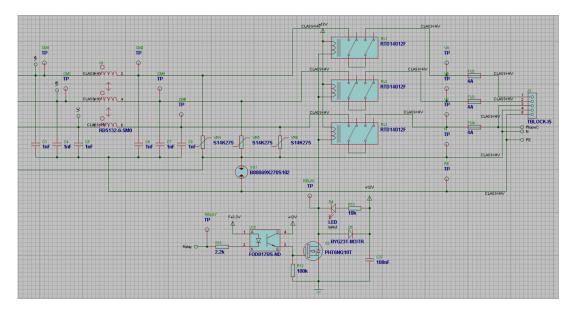

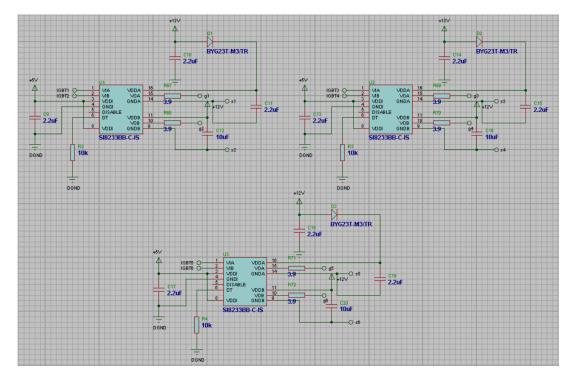

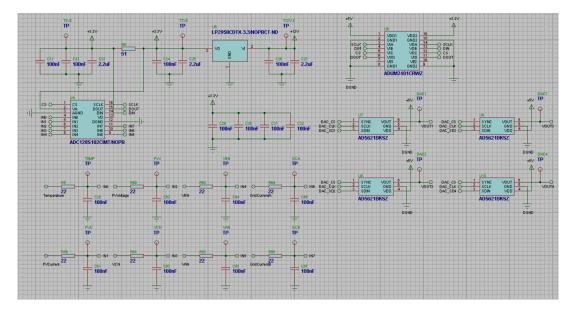

| Figure A.1 Input Protection, Inverter, and Current Measurement<br>Components                                  | 145 |

| Figure A.2 Output Common-Mode Filter and Protection Components .                                              | 146 |

| Figure A.3 Gate Driver Components                                                                             | 146 |

| Figure A.4 ADC, ADC Isolator, and DAC Components                                                              | 147 |

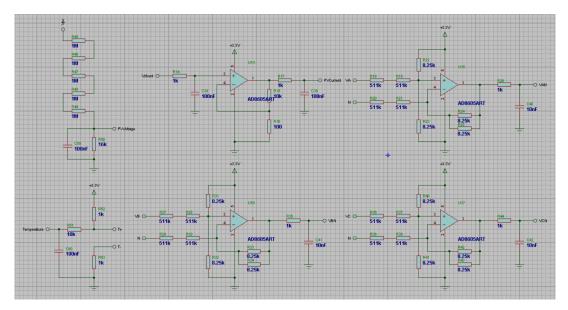

| Figure A.5 Measurement Circuit Components                                                                     | 147 |

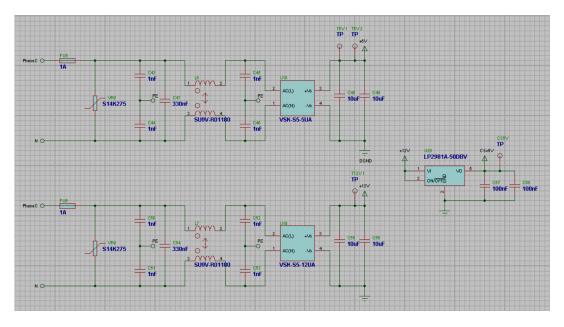

| Figure A.6 Power Supply Components                                                                            | 148 |

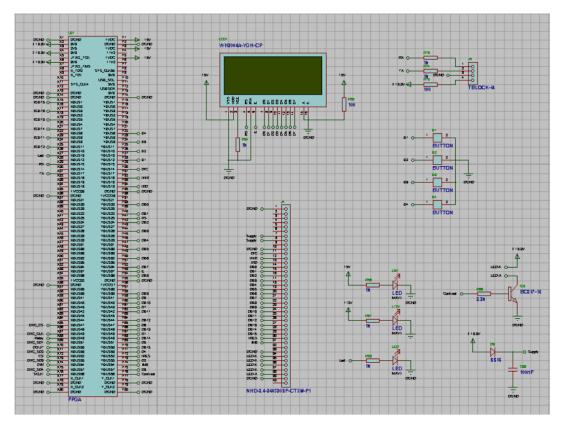

| Figure A.7 FPGA and Other Circuit Components                                                                  | 148 |

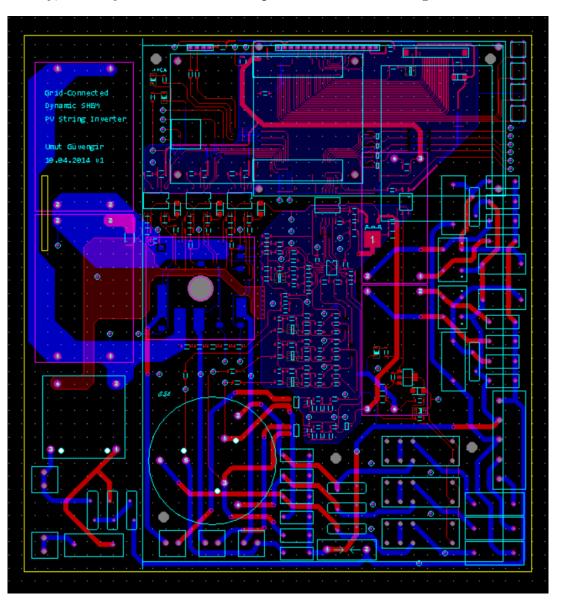

| Figure A.8 PCB Layout Drawn in ARES Platform                                                                  | 149 |

# NOMENCLATURE

| $lpha_k$           | Switching Angle                              |

|--------------------|----------------------------------------------|

| β                  | Inertia Weight                               |

| δ                  | Load Angle                                   |

| $\gamma$           | Modulation Index Penalty                     |

| $\mu$              | Angle Constraint Penalty                     |

| ω                  | Grid Frequency                               |

| $\omega_{ff}$      | Feed-forward Component of the Grid Frequency |

| $\omega t_{a,b,c}$ | PLL Information of the Grid Voltage          |

| arphi              | Sum of Cognition and Social Factors          |

| heta               | Phase Angle                                  |

| C                  | LCL Filter Capacitance                       |

| $c_1$              | Cognition Factor                             |

| $c_2$              | Social Factor                                |

| $C_{dc}$           | DC Link Capacitance                          |

| d                  | Dimension of the Problem Space               |

| D                  | Reverse Diode of Switching Semiconductor     |

| f                  | Fitness Value of the Particle                |

| $f_1$              | Frequency of the Fundamental Component       |

| $f_c$              | Converter Switching Frequency                |

| $f_{res}$          | LCL Filter Resonant Frequency                |

| $gbest_i$          | Global Best Fitness of the $i^{th}$ Particle |

| Ι                  | RMS Current From Inverter to Grid            |

| $i_{a,b,c}$        | Grid Current                                 |

| $I_{dc}$           | DC Link Current                              |

| $i_{L1}$           | Inverter-Side LCL Filter Current             |

| $i_{L2}$           | Grid-Side LCL Filter Current                 |

| $i_{ph}$           | Photo-Current Source                         |

| K                  | Constriction Factor                          |

| $k_i$          | Integral Constant of PI Control                                          |

|----------------|--------------------------------------------------------------------------|

| $k_p$          | Proportional Constant of PI Control                                      |

| $L_1$          | Inverter-Side LCL Filter Inductance                                      |

| $L_2$          | Grid-Side LCL Filter Inductance                                          |

| M              | Modulation Index                                                         |

| $pbest_i$      | Personal Best Fitness of the $i^{th}$ Particle                           |

| $P_G$          | Grid-Side Active Power                                                   |

| $P_I$          | Inverter-Side Active Power                                               |

| $P_{in}$       | Inverter Input Active Power                                              |

| $P_{out}$      | Inverter Output Reactive Power                                           |

| $Q_G$          | Grid-Side Reactive Power                                                 |

| $Q_I$          | Inverter-Side Reactive Power                                             |

| $Q_{out}$      | Inverter Output Reactive Power                                           |

| R              | Total Reactor Loss Resistance                                            |

| rand           | Random Number                                                            |

| $R_p$          | PV Cell Shunt Resistance                                                 |

| $R_s$          | PV Cell Series Resistance                                                |

| s              | Swarm Size                                                               |

| t              | Time Frame                                                               |

| T              | Switching Semiconductor                                                  |

| $T_{igbt}$     | Temperature of the IGBT                                                  |

| $U_{max1}$     | Highest Permanent Catenary Voltage                                       |

| $U_{max2}$     | Highest Non-Permanent Catenary Voltage                                   |

| $U_{max3}$     | Highest Long-Term Catenary Overvoltage                                   |

| $V_{lpha,eta}$ | $\alpha$ and $\beta$ Component of the Voltage                            |

| $v_{a,b,c}$    | Grid Voltage                                                             |

| $v_{AB}$       | Inverter Line-to-Line Output Voltage                                     |

| $v_{An}$       | Inverter Midpoint Output Voltage for Leg A                               |

| $V_{CE}$       | IGBT Collector-Emitter Voltage                                           |

| $V_{dc}$       | DC Link Voltage                                                          |

| $V_{d,q}$      | D and Q Component of the Voltage                                         |

| $\hat{V_f}$    | Peak Value of the Fundamental Line-to-Neutral Inverter<br>Output Voltage |

| $v_i$          | Velocity of the $i^{th}$ Particle                                        |

| $V_I$          | Line-to-Neutral Inverter RMS Voltage |

|----------------|--------------------------------------|

| $V_G$          | Line-to-Neutral Grid RMS Voltage     |

| $V_{max}$      | Maximum Velocity                     |

| $V_{rms, l-l}$ | Line-to-Line RMS Voltage             |

| $V_{rms, l-n}$ | Line-to-Neutral RMS Voltage          |

| X              | Reactor Reactance                    |

| $x_i$          | Position of the $i^{th}$ Particle    |

| $X_{max}$      | Dynamic Range of the Particle        |

|                |                                      |

# LIST OF ABBREVIATIONS

| AC             | Alternating Current                               |

|----------------|---------------------------------------------------|

| ADC            | Analog-to-Digital Converter                       |

| ANN            | Artificial Neural Network                         |

| CMT            | Clock Management Tile                             |

| CSI            | Current Source Inverter                           |

| DAC            | Digital-to-Analog Converter                       |

| DC             | Direct Current                                    |

| DFF            | D Flip Flop                                       |

| DLL            | Delay Locked Loop                                 |

| DSP            | Digital Signal Processor                          |

| $\mathbf{FFT}$ | Fast Fourier Transform                            |

| FIR            | Finite Impulse Response                           |

| FPGA           | Field-Programmable Gate Array                     |

| GA             | Genetic Algorithm                                 |

| GUI            | Graphical User Interface                          |

| HDL            | Hardware Description Language                     |

| IGBT           | Insulated-Gate Bipolar Transistor                 |

| I/O            | Input/Output                                      |

| JTAG           | Joint Test Action Group                           |

| LFSR           | Linear Feedback Shift Register                    |

| LUT            | Lookup Table                                      |

| MOSFET         | Metal-Oxide-Semiconductor Field-Effect Transistor |

| MPPT           | Maximum Power Point Tracking                      |

| MULT           | Multiplier                                        |

| PCB            | Printed Circuit Board                             |

| PI             | Proportional-Integral                             |

| PLL            | Phase Locked Loop                                 |

| PRNG           | Pseudo Random Number Generator                    |

|                |                                                   |

| PSO     | Particle Swarm Optimization           |

|---------|---------------------------------------|

| p.u.    | Per-Unit                              |

| PV      | Photovoltaic                          |

| PWM     | Pulse-Width Modulation                |

| RAM     | Random Access Memory                  |

| RMS     | Root Mean Square                      |

| SHEM    | Selective Harmonic Elimination Method |

| SiC     | Silicon Carbide                       |

| SPI     | Serial Peripheral Interface           |

| STATCOM | Static Synchronous Compensator        |

| TDD     | Total Demand Distortion               |

| THD     | Total Harmonic Distortion             |

| TLL     | Three-Phase Line-to-Line              |

| TLN     | Three-Phase Line-to-Neutral           |

| TRNG    | True Random Number Generator          |

| UPS     | Uninterruptible Power Supply          |

| VHDL    | VHSIC HDL                             |

| VHSIC   | Very High Speed Integrated Circuit    |

| VLSI    | Very Large Scale Integrated           |

| VSC     | Voltage Source Converter              |

| VSI     | Voltage Source Inverter               |

xxviii

### CHAPTER 1

### INTRODUCTION

#### 1.1 Overview

It is a basic fact that the human civilization is living in an era in which energy resources are regarded as the most important asset of the planet. The need for finding energy resources in order to compensate the ever-increasing energy consumption of people has driven several nations to seek new and alternative ways of supplying energy for their industry and household, especially in the  $21^{st}$  century.

Fossil fuels have been the primary source of energy until the end of last century. Over 79 % of the primary resources of energy consumed in the world consists of fossil fuels. 57.7 % of this amount is utilized for the transportation sector, which is rapidly decreasing. It is predicted that the fossil-based oil, coal, and gas reserves will run out in the next ten decades by the World Energy Forum [1]. It has become a must to utilize alternative energy resources for highly efficient energy conversion with low emission due to concerns about increasing oil prices, fossil fuel deficit, global warming, and damages to environment and ecosystem [2]. Worldwide renewable energy resources other than hydroelectric energy has exceeded 480 gigawatts by 2012 due to the growth in their installed capacity. This generation of power compensates 5.2 % of the worldwide electricity consumption, and half of the newly installed generation capacity consists of this power [3].

Although the focus for supplying energy in more efficient ways has been on the

resource side recently, the conversion of energy resources to electrical energy, which is injected into the power grid to be used by industry and household, highly depends on the efficiency of the power converter. Implementing a robust and stable power converter is very essential for increasing the cumulative efficiency of the system. Energy resources have fluctuated and unpredicted features, which is not preferable for power grid operators. Therefore, power electronics has an important role for obtaining more controllable and robust energy production and reducing system costs. Moreover, more advanced control methods and configurations for power electronic converters are needed due to new challenges and considerations in alternative energy conversion [4].

Along with the demands of renewable energy resources, their conversion and distribution to the power grid, power converters also play an essential role in driving motors. Several topologies and control methods have been investigated in the literature to build efficient motor drives, and the research for developing the conversion process always continues. With the advance of new generation of semiconductors such as Trench 4 insulated-gate bipolar transistors (IGBTs), long lifetime, high reliability, high operating temperatures, and reduced switching losses can be achieved [5]. Silicon carbide (SiC) metal-oxide-semiconductor field-effect transistors (MOSFETs) and diodes are examples of other new semiconductor families, with which it is possible to design and implement high density power modules operating with low switching losses at high junction temperatures [6]. These new generation of semiconductors contribute to the desire for low switching power losses in power converters in a revolutionary way.

The control of power converters has become more important and interesting due to emerging microcontroller technologies. The ever-increasing computing power and speed of microcontrollers enables engineers to implement algorithms in real time easily, which was once recognized as impossible due to complexity and high computing power demand of algorithms in the past. By utilizing the features of fast and powerful microcontrollers such as field-programmable gate arrays (FPGAs), one can apply various control methods to implement efficient, robust, dynamic, and reliable conversion process, which will bring about new possibilities and horizons for power electronics and alter its history.

#### **1.2** Switch-Mode Inverters

Inverters are basically DC-to-AC converters and widely used for variable-speed AC motor drives, uninterruptible power supplies, induction heating, and many other industrial applications. DC sources such as batteries, solar cells, or fuel cells can be inputs to inverters, and the duty of the inverter is to convert this DC input voltage to a symmetric AC output voltage with specified magnitude and frequency. Although the output voltage waveform of an inverter should be sinusoidal ideally, it is non-sinusoidal due to certain harmonics caused by the switching action of semiconductors in practice. Low and medium power applications can be implemented with square-wave or quasi-square-wave voltages, but high power applications require lowly-distorted sinusoidal voltages. By utilizing high-speed power semiconductor devices and several advanced switching techniques, the harmonic contents of the non-sinusoidal output voltage can be minimized or reduced considerably [7].

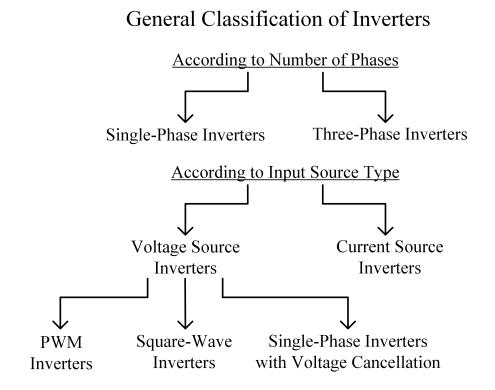

Inverters can be classified according to different features. When classified by the number of phases, single-phase inverters and three-phase inverters are the two main categories. In general, pulse-width-modulation (PWM) control signals are used to generate AC output voltage; however, there are many other switching methods in the literature. Inverters are called as voltage source inverter (VSI) if their input is a DC voltage source, or current source inverter (CSI) if their input is a DC current source [8].

The VSIs can be categorized into three general categories:

- *Pulse-width-modulated inverters:* For these inverters, the AC output voltage magnitude and frequency is controlled by the inverter by utilizing PWM for semiconductor switches since the input DC voltage is constant in magnitude.

- Square-wave inverters: For these inverters, the AC output voltage magnitude is controlled by altering the input DC voltage. The frequency of the output voltage is determined by the inverter control method, and the output voltage has square-wave waveform.

• Single-phase inverters with voltage cancellation: If the inverter is singlephase inverter, the output voltage magnitude and frequency can be controlled with voltage cancellation method although the input DC voltage is constant, and the switching technique is not PWM. These inverters have the properties of the previous two inverters; however, their utilization area is not as wide as others [8].

Figure 1.1 summarizes the classification of the inverters. In some applications, which will be discussed in the next chapter, the input DC link voltage to the inverter is variable throughout the course of operation, and this requires a dynamic control approach for the switches in the inverter if the output harmonic content is desired to be low. Several control methods have been investigated in the literature and implemented in the industry, and one of these methods, which is selective harmonic elimination method, will be introduced in the next section.

Figure 1.1: General Classification of Inverters

### 1.3 Selective Harmonic Elimination Method

#### 1.3.1 Application Areas

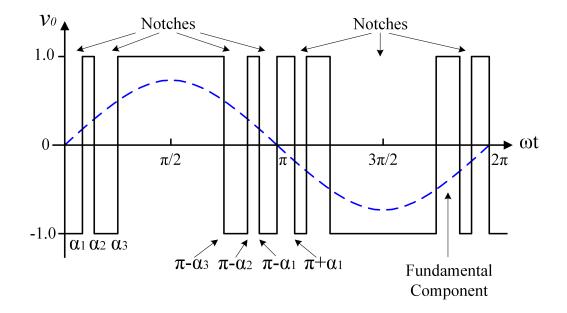

Selective harmonic elimination method (SHEM) combines square-wave switching and PWM switching to control the fundamental output voltage. Moreover, it is possible to eliminate specific harmonics in the output voltage of the inverter via selection of specific notch angles in the switching pattern of the semiconductors. Each notch in a half-cycle provides one degree of freedom so that one notch is used for the control of fundamental, and the others are used for cancelling the undesirable lower-order harmonics. The higher-order harmonics can be filtered by a small filter. By utilizing very large scale integrated (VLSI) circuits and microcontrollers, SHEM can be implemented for inverters without making the switching frequency and switching losses very high. Figure 1.2 shows an example application of SHEM to a two-level VSI in order to control the fundamental and eliminate two harmonics [8].

Figure 1.2: Application of SHEM to Two-Level VSI

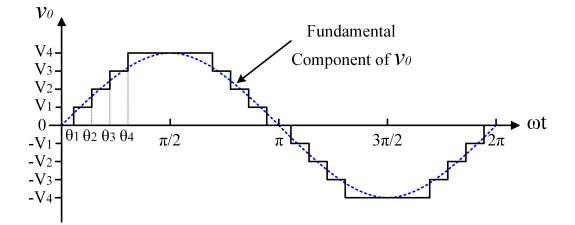

The use of two-level inverters is disadvantageous due to high switching losses at high switching frequencies for high-power and high-voltage applications. Therefore, switching semiconductor devices should be used with series or parallel combinations to handle high voltages and currents. Multilevel inverters are found to be effective for high-power high-voltage applications since the power rating can be increased by increasing the number of voltage levels and thereby using switching semiconductors with lower voltage ratings. By this way, higher output voltage levels can be reached with lower harmonic content without use of transformers between the inverter and the grid. Figure 1.3 depicts the typical output voltage of a nine-level multilevel inverter [7].

Figure 1.3: Output Voltage of Nine-Level Multilevel Inverter

SHEM can also be applied to multilevel inverters. As can be seen from Figure 1.3, the selection of switching angles,  $\theta_1$ ,  $\theta_2$ ,  $\theta_3$ ,  $\theta_4$ , affects the shape of the output voltage waveform. Moreover, the magnitudes of fundamental output voltage and harmonics in this waveform can be controlled by selecting the switching angles deliberately, which makes it possible to eliminate lower-order harmonics just as in the case of selecting notch angles for two-level inverters. As the number of voltage levels increases, more switching angles and, in turn, more degrees of freedom are acquired so that more harmonics can be eliminated. By this way, filtering requirements in the output connection are reduced considerably.

Both two-level and multilevel inverter topologies have been implemented in a wide range of applications in the industry. Reactive power control in utility systems is an example of these applications. An inverter can generate a controlled reactive current and operate as a static synchronous compensator (STATCOM) in the steady-state. By this way, it can either generate or consume reactive power from the grid according to the demands of the grid operator. The harmonic content in the inverter output can be reduced with SHEM; thus, the efficiency of the system can be improved [7]. In [9], a two-level three-leg voltage-source converter (VSC) was designed and implemented for a medium-size distribution-type STATCOM application. 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, 13<sup>th</sup>, 17<sup>th</sup>, 19<sup>th</sup>, 23<sup>rd</sup>, and 25<sup>th</sup> harmonics in the output voltage are eliminated by SHEM. Another STATCOM application with SHEM has been presented in [10]. In this research, a 154-kV  $\pm$ 50-MVAr transmission STATCOM was designed and implemented to realize compensation of reactive power, regulation of terminal voltage, and stability of power system. The implementation includes five 10.5-kV  $\pm$ 12-MVAr cascaded multilevel converter modules with five series-connected H-bridges in each phase for each module operating in parallel. SHEM technique is utilized to determine five switching angles which eliminate  $5^{th}$ ,  $7^{th}$ ,  $11^{th}$ , and  $13^{th}$  harmonics by keeping the harmonic distortion of the line-to-neutral output voltage at minimum. Therefore, there is no need to utilize a larger series filter reactor at the output.

#### 1.3.2 Algorithms Used for SHEM Equations

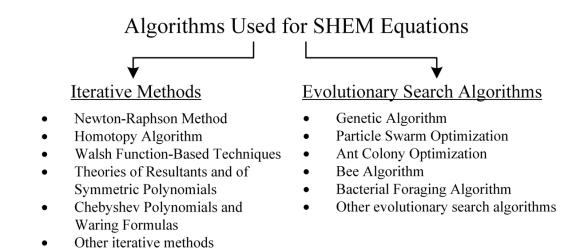

In both cases of two-level inverter and multilevel inverter, it is necessary to solve a set of nonlinear equations in order to find the switching angles of SHEM. These equations consist of mainly sinusoidal terms, and the number of equations in the set equals the number of switching angles. Although using more switching angles eliminates more harmonics, the complexity of the problem increases as the number of switching angles increases, and finding the solution set becomes very hard via conventional methods. In order to solve this set of nonlinear equations, there has been two general groups of techniques presented in the literature.

The first group includes iterative methods such as Newton-Raphson method. Iterative methods are affected by the choice of initial points in general, and divergence of the algorithm is possible. Although Newton-Raphson method is fast, it can only find one solution set [11]. In [12], the roots of the equation set is found by using MATLAB function *fsolve*, which relies on a Gauss-Newton method with a mixed quadratic and cubic line search method. Homotopy algorithm is another approach, applied in [13–16]. The authors in [17–20] proposed other iterative numerical techniques whereas in [21], the Walsh function-based analytical technique is adopted. In [22] and [23], theories of resultants and of symmetric polynomials were used to characterize the existence of solutions for each modulation index value and then to solve polynomial equations obtained from transcendental equations. Modulation index is defined as the ratio of the output voltage to the input voltage of the converter multiplied by a constant. For some infeasible modulation index values, SHEM equations does not have a solution set. The iterative methods do not offer optimum solutions for infeasible modulation index values, which may be problematic for implementations working for a continuous range of modulation index values.

The second group takes the selective harmonic elimination problem as an optimization problem, and the solution is sought with evolutionary search algorithms. Evolutionary search algorithms have been found to be effective in solving various problems in industry in recent years. These algorithms allow the solution of the problem to be found more easily than analytical methods, and in some cases, where the analytical methods cannot be applied, they are the only way to reach a feasible solution. These algorithms can find the global optimum solution if certain harmonics can be completely eliminated, or they can offer optimum notch angles if a feasible solution cannot be found. Some of the notable evolutionary search algorithms applied to the problem include genetic algorithm (GA) [24–26], particle swarm optimization (PSO) [11,27,28], ant colony optimization [29], bee algorithm [30], and bacterial foraging algorithm [31]. Figure 1.4 below summarizes the algorithms used for solution of SHEM equations.

Figure 1.4: Algorithms Used for Solution of SHEM Equations

# **1.3.3** Offline and Online Applications

Almost all of the aforementioned methods require heavy computing which may not be realized in a fast and effective way unless a microcontroller whose clock frequency is considerably high is utilized. Therefore, in practice, SHEM switching angle sets have been solved for by one of the aforementioned methods beforehand and then stored as a lookup table in the microcontrollers up to now. In [9] and [10], for example, the switching angles are solved by a hybrid algorithm which combines the genetic algorithm and the gradient-based steepest descent method. Genetic algorithm is utilized to determine proper initial points whereas these initial points are processed by the steepest descent method to find the global optimum in a fast way. Obtained values of switching angles for different modulation index values are stored as a lookup table in the microcontroller.

Although storing the switching angle sets for different modulation index values in the microcontroller is effective, the use of discrete modulation index values may lead to some disadvantages in some cases, resulting in nonoptimum commutations. Moreover, significant amount of memory is needed in the microcontroller if the number of stored lookup tables is increased [32]. There is also possibility that the solutions might be missing for some problems, and interpolation techniques may be required [33]. This problem has led the researchers to search for online application of SHEM in an effective way.

As mentioned before, solving the equations for switching angles require heavy computing effort. In [33], the authors used the generalization ability of artificial neural network (ANN) to circumvent this problem. The GA is used to calculate switching angles beforehand for different DC source values, and then the ANN is used to train the controller to determine the switching angles for different DC sources in real-time at each phase of the multilevel inverter. By this way, the ANN replaces the lookup table and introduces its inherent capability to generalize the solution space into the problem with proper training.

Another approach for online application of SHEM is investigated in [32]. The authors proposed an analytical procedure for computation of all pairs of valid switching angles used in pattern generation in five-level H-bridge cascaded inverters. The proposed procedure allows fully analytical calculation of switching angles using Chebyshev polynomials and Waring formulas. It is asserted in the research that due to its limited complexity, the procedure can be easily implemented in real time using digital signal controller, programmable logic device or FPGA. However, elimination of only one harmonic is investigated in the research. Although it has been asserted that the procedure can be extended to multiple harmonic elimination, this has been left as a future work, and it is not known yet how the procedure will perform when it is applied to multiple harmonic elimination.

## 1.4 Scope of the Thesis

Within the scope of this thesis, SHEM has been applied in real time to find optimum switching angles with the application of particle swarm optimization, eliminating  $5^{th}$ ,  $7^{th}$ ,  $11^{th}$ ,  $13^{th}$ ,  $17^{th}$ , and  $19^{th}$  harmonics in the output voltage of a grid-connected inverter with a variable DC link input voltage. The PSO algorithm has been implemented in the FPGA, which has been used as the main and sole controller in order to provide gating signals for IGBTs utilized in the inverter.

The outline of this thesis is given as follows:

In Chapter 2, the problem definition is given for offline application of SHEM. Inverters with variable DC link voltage are investigated in two different applications, photovoltaic and traction applications. It is shown that the modulation index values for inverters with variable DC link voltage varies in a wide range. The disadvantages of offline calculation of SHEM switching angles and then storing the angle sets in the microcontroller as lookup tables are shown by investigating discretization of modulation index values, lookup table storage requirement, and infeasible region of solution space.

In Chapter 3, particle swarm optimization algorithm is elaborated. The mindset behind evolutionary search algorithms are introduced, and their common features are mentioned along with their advantages over traditional iterative methods. Then, PSO algorithm is introduced, and its process flow is given along with equations used in the algorithm. SHEM patterns are elaborated in detail, and the application of PSO algorithm to the cost function of the formulated SHEM problem is shown. Finally, the effects of parameters in the PSO algorithm on the solution of the problem are investigated along with related data and figures.

In Chapter 4, FPGA implementation of online SHEM by PSO algorithm is elaborated. An overview of FPGAs is given along with its structure and application areas, merits of using FPGAs, a general design flow used for projects with FPGA, and features of fixed-point arithmetic. Then, the implemented VHDL code for FPGA is investigated for each of the modules used in the code, which are PSO, PLL, dead-time modules and ADC, DAC, and protection codes. The workflow of the PSO module is investigated along with related diagrams, and the theories of concepts utilized for the algorithm are given.

In Chapter 5, simulations of the grid-connected inverter system with online application of SHEM in Simulink platform are discussed along with figures and tables. Simulation of implemented VHDL code in ISim platform and its hardware co-simulation are elaborated with the results acquired from the calculation of SHEM switching angles in real time. Finally, experimental results are given for the implemented grid-connected three-phase two-level inverter with necessary figures, tables, and data.

In Chapter 6, a summary of the work done for the thesis is given with some predictions and suggestions for future work.

In Appendix A, the related schematics of the grid-connected inverter drawn in ISIS platform and its PCB design drawn in ARES platform of Proteus Professional software are given.

Finally in Appendix B, the list of laboratory equipments used during the tests conducted on the inverter can be found.

# CHAPTER 2

# PROBLEM DEFINITION

In this chapter, the problems of offline SHEM application will be discussed. As mentioned in the previous chapter, implementing SHEM switching angles as a lookup table for different modulation index values in the microcontroller has some disadvantages which affect the normal operation of the inverter. The incentives for seeking online application of SHEM can be summarized as variable DC link voltage of single-stage inverters, discretization of modulation index values, lookup table storage requirement, and infeasible region of SHEM solution space.

# 2.1 Variable DC Link Voltage

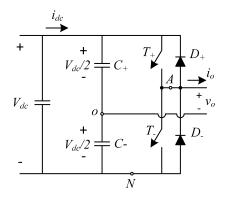

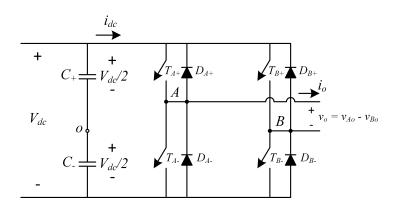

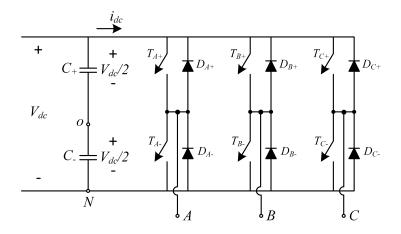

As introduced in the previous chapter, inverters convert the DC input voltage to a symmetric AC output voltage with controllable magnitude and frequency. The simplest form of an inverter is a single-phase half-bridge inverter. As shown in Figure 2.1, the upper and lower semiconductors in this arrangement are switched so that they connect  $+V_{dc}/2$  or  $-V_{dc}/2$  to the output, whose reference is taken as the midpoint of the input capacitors. Therefore, the DC input voltage is converted to the AC output voltage which alternates between positive and negative. Single-phase full-bridge inverters and three-phase full-bridge inverters are derived from this configuration by adding additional legs of semiconductors as shown in Figure 2.2 and Figure 2.3 [8].

Figure 2.1: Single-Phase Half-Bridge Inverter

Figure 2.2: Single-Phase Full-Bridge Inverter

Figure 2.3: Three-Phase Full-Bridge Inverter

Modulation index is defined as the ratio of the output voltage to the input voltage of the inverter multiplied by a constant, which is specific to the topology and control method of the inverter. By changing the modulation index, the fundamental output voltage can be controlled, and, in turn, active and reactive power flow can be controlled according to the demands. Therefore, the changes to the input DC link voltage directly affects the operation of the inverter, and the control loop has to take care of these changes in order to provide stable and robust service.

In some applications where the input voltage is not high enough to supply the DC-AC inverter, an additional DC-DC boost converter stage is used between the supply and the inverter. By adjusting the duty cycle of this converter, the DC link voltage can be held at a constant value, thus relieving the inverter control of taking care of variable input voltage. However, two-stage inverters have lower power conversion efficiency, higher cost, and lower reliability since the chance of component failure is higher with respect to the single-stage converter [34].

A variable DC link voltage at the input to a single-stage inverter causes the modulation index value to be variable, and this results in different switching angle sets if SHEM is used as the control method. Therefore, all of these angle sets should be stored for discretized values of modulation index in the microcontroller beforehand so that the inverter can handle the input DC link voltage variations. This requirement causes the discretization, storage, and solution space problems for modulation index values, which will be explained later in this chapter.

Two of the applications where the input DC voltage changes according to the conditions outside the inverter are introduced briefly as follows.

## 2.1.1 Photovoltaic Applications

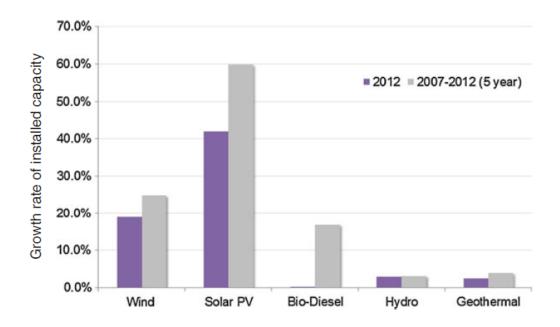

Photovoltaic (PV) power generation has a large share of installed capacity along with the wind power as one of the fast-developing renewable energy resources. As can be seen from Figure 2.4, the worldwide PV power generation reached the fastest growth rate of installed capacity at 60 % between 2007 and 2012 and at 40 % only in 2012. It is foreseen that the cost of PV systems will continue decreasing in the future, which will make it possible for the grid-connected PV systems to compete with other renewable energy systems [3].

Figure 2.4: Worldwide Growth Rate of Installed Capacity for Different Renewable Technologies in 2012 and between 2007 and 2012 [3]

The solar energy is immensely affected by the environmental conditions such as irradiance level and ambient temperature, which makes it essential for a gridconnected PV power system to transfer and convert the solar energy efficiently and reliably. This system has to harvest the maximum power from the PV panels for changing environmental conditions, to operate with grid synchronization, and to comply with grid connection requirements. PV panels are the basic building blocks of a PV system, in which they are connected to a grid-connected inverter for power conversion. They consist of PV cells connected in series and parallel to achieve increased output voltage and current levels, respectively. If the total DC link voltage is low, a DC-DC boost converter may be needed to increase this voltage to a sufficient input voltage level for the inverter [4].

PV cells may be made of various materials such as mono- and poly-crystalline silicon, or cadmium telluride, amorphous silicon, copper indium gallium selenide for thin-film cells. However, the selection of material does not affect the operating principle of the PV technology, which is based on the photovoltaic effect. This effect converts the sunlight to an electromotive force, creating a DC current when the PV cell is short-circuited. This short-circuit current depends on the solar irradiance level and the ambient temperature. Figure 2.5 shows the electrical circuit equivalent of a PV cell, where  $i_{ph}$  is the photocurrent source, with which a diode is connected in parallel,  $R_p$  is the shunt resistance, and  $R_s$  is the series resistance [4].

Figure 2.5: PV Cell Electrical Equivalent Circuit [4]

The electrical I-V and P-V characteristics of a PV panel are not linear and depends on the ambient conditions, as can be seen from Figure 2.6 for (a) various solar irradiance levels at 25°C and (b) various ambient temperatures at 1000  $W/m^2$ . A maximum power point tracking (MPPT) algorithm is needed to extract the most of the solar energy and convert it from the PV panels because of their non-linear characteristics and environmental dependency [4].

As can be observed from Figure 2.6, the maximum power point (MPP) voltage should be the operating input voltage of the grid-connected inverter, and it is dependent on the solar irradiance and ambient temperature. Solar irradiance does not affect the MPP voltage as much as ambient temperature does. If the inverter is a two-stage one with a DC-DC boost converter, this converter takes care of the MPP voltage variation by adjusting its duty cycle to harvest the maximum power from the PV panel and to increase the PV output DC voltage to a level which exceeds the peak grid voltage, making the DC link voltage of the DC-AC inverter invariable [35]. However, for single-stage inverters, the input voltage of the inverter should be high enough to inject power to the grid. For this

Figure 2.6: I-V and P-V Characteristics of a PV Panel [4]

reason, a PV string is created with series-connected PV panels. The variation of MPP voltage against changing solar irradiance and ambient temperature for an example PV field, which consists of 20 thin-film solar panels in two parallel strings rated at 1600 W, is shown in Table 2.1 below. As can be seen from this table, the variation of voltage caused by the ambient temperature is so high that it varies between 584 V and 786 V. As explained before, this causes a wide variation of modulation index values for the inverter, and this means that a wide range of switching angles should be stored as a lookup table in the microcontroller if the control method is chosen as SHEM for the single-stage inverter.

|        | $egin{array}{c} 200 \ W/m^2 \end{array}$ | $\frac{400}{\mathrm{W/m^2}}$ | $\frac{600}{{\rm W}/{\rm m}^2}$ | $\frac{800}{\mathrm{W/m^2}}$ | $\frac{1000}{\mathrm{W/m^2}}$ |

|--------|------------------------------------------|------------------------------|---------------------------------|------------------------------|-------------------------------|

| -10 °C | 747.6 V                                  | 777.1 V                      | 784.7 V                         | 785.8 V                      | 783.6 V                       |

| 10 °C  | $706.5~\mathrm{V}$                       | 736.6 V                      | 745.0 V                         | 746.7 V                      | 745.0 V                       |

| 30 °C  | 665.6 V                                  | 696.3 V                      | $705.5 { m V}$                  | 707.8 V                      | 706.6 V                       |

| 50 °C  | 624.9 V                                  | 656.3 V                      | 666.3 V                         | 669.1 V                      | 668.4 V                       |

| 70 °C  | 584.4 V                                  | 616.5 V                      | 627.3 V                         | 630.8 V                      | 630.6 V                       |

Table 2.1: Variation of MPP Voltage Against Changing Solar Irradiance and Ambient Temperature

#### 2.1.2 Traction Applications

Railways are the most energy-efficient land-based means of transport, and the most efficient way to deliver the required power to electric motors used in railways is via an electric power supply system alongside the railway tracks. Railway power supply systems are either AC or DC systems. The AC railway power supply system is summarized in Figure 2.7, where the upper image (a) illustrates a railway power supplying converter which converts three-phase AC public grid electricity to single-phase AC railway network electricity, whereas the lower image (b) depicts a vehicle unit converter which delivers the energy from the singlephase AC railway network to three-phase AC traction motor. The AC systems can either be operated at the same public grid frequency or at a different frequency which is normally lower. DC systems, however, require only the second conversion where the electricity from the DC supply is converted to three-phase electricity to be delivered to AC traction motor [36].

(a) Railway Power Supplying Converter

(b) Vehicle Unit Converter

Figure 2.7: AC Railway Power Supply System [36]

There are several different standards for the contact line voltages for both AC and DC railway systems. Electricity is delivered to the trains in different ways, often via an overhead contact line called the catenary. The catenary is actually a geometrical shape in mathematics, namely it is the shape of a cord hanging freely from two fixed points. The physical catenary goes above the actual overhead contact line. Therefore, it is normal to denote the entire system of conductors hanging from the poles alongside the railway line as the catenary system [36]. Railway locomotives and other units are supplied with the electrical energy acquired from the catenary, which makes it possible for them to operate without a prime mover. Utilization of AC motors for electric traction is advantageous since it has higher power-to-weight ratio than diesel or steam powered traction. Moreover, faster acceleration can be achieved via electric traction [37].

The standard EN 50163 is related to supply voltages of traction systems for railway applications [38]. AC systems have voltages ranging from 15 to 25 kV (at 16.7 or 50-60 Hz) and are usually found in long distances or routes with heavy traffic. DC systems, on the other hand, are generally utilized for trams, suburb trains, and medium distances. Light rail and metro services can use either aerial catenaries or third rail, with operating voltages ranging from 600 to 1500 V. Higher power applications require catenary voltages up to 3 kV [39]. The supply voltages of traction systems are summarized in Table 2.2, and Figure 2.8 shows the maximum value of the catenary voltage according to the duration, where Zone C is for overvoltages between highest long-term overvoltage  $U_{max3}$ and highest non-permanent voltage  $U_{max2}$ , Zone D is for  $U_{max2}$ , and Zone E is for highest permanent voltage  $U_{max1}$  [37,38].

As can be seen from Table 2.2 and Figure 2.8, the catenary voltage of the traction system may change considerably between lowest non-permanent voltage and highest non-permanent voltage. For a DC traction system, this causes the input voltage of the DC-AC inverter to fluctuate considerably, which is the same situation as that seen for PV applications, explained in the previous section. If the inverter output harmonics are to be eliminated via SHEM, the requirement that a large lookup table of switching angles should be stored in the microcontroller of the inverter is again necessary for changing values of the modulation index.

| Traction<br>system   | Lowest<br>non-<br>permanent<br>voltage<br>$(U_{min2})$<br>(V) | Lowest<br>permanent<br>voltage<br>$(U_{min1})$<br>(V) | Nominal<br>voltage<br>$(U_n)$<br>(V) | Highest<br>permanent<br>voltage<br>$(U_{max1})$<br>(V) | Highest<br>non-<br>permanent<br>voltage<br>$(U_{max2})$<br>(V) |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------|--------------------------------------|--------------------------------------------------------|----------------------------------------------------------------|

| 600 V DC             | 400                                                           | 400                                                   | 600                                  | 720                                                    | 800                                                            |

| 750 V DC             | 500                                                           | 500                                                   | 750                                  | 900                                                    | 1000                                                           |

| 1.5 kV DC            | 1000                                                          | 1000                                                  | 1500                                 | 1800                                                   | 1950                                                           |

| 3 kV DC              | 2000                                                          | 2000                                                  | 3000                                 | 3000                                                   | 3000                                                           |

| 15 kV AC,<br>16.7 Hz | 11000                                                         | 12000                                                 | 15000                                | 17250                                                  | 18000                                                          |

| 25 kV AC,<br>50 Hz   | 17500                                                         | 19000                                                 | 25000                                | 27500                                                  | 29000                                                          |

Table 2.2: Nominal Voltages and Their Permissible Limits for Traction Systems

Figure 2.8: Maximum Value of the Catenary Voltage According to the Duration [38]

#### 2.2 Discretization of Modulation Index

When implemented in a microcontroller as a lookup table, SHEM switching angles for discretized modulation index values are stored as it is not possible to reach a continuous range due to the nature of digital control. For example, in [10], 150 steps of modulation index values are used from -50-MVAr- to +50-MVAr-reactive-power control, and the optimum values of switching angles are found for these modulation index values to be stored in a  $150 \times 5$  lookup table.

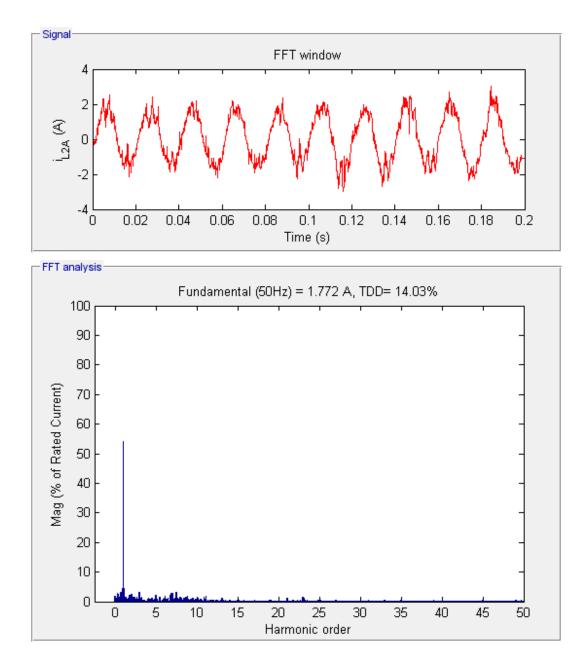

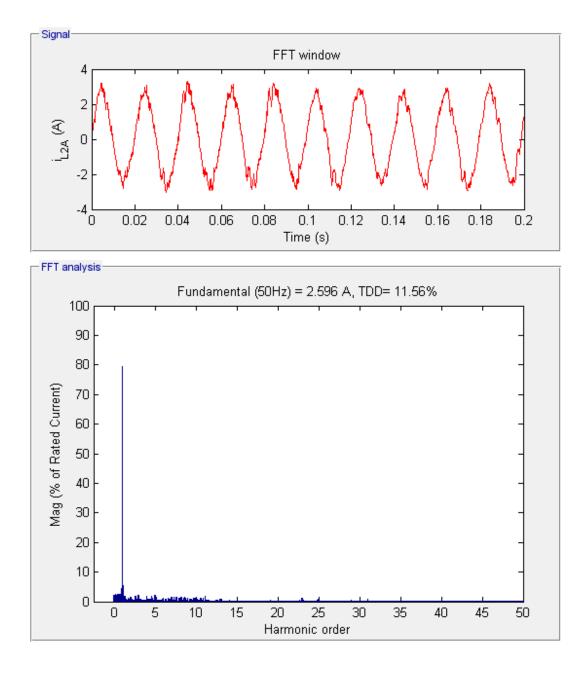

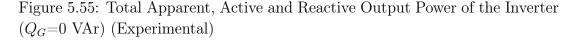

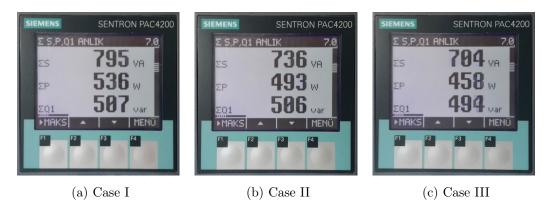

The modulation index value is generally found by a control loop as the output of a PI controller. The value found has to be rounded to a value stored in the lookup table if it is not exactly stored. Therefore, a slightly different value of modulation index than the value, which is required by the control loop, has to be used. Since the application of switching angles stored for this modulation index value will bring about a different fundamental voltage than the required voltage and non-eliminated lower-order harmonics at the inverter output, the active and reactive power injected to the grid and the total harmonic distortion will be different than desired values.