### SELECTION OF SUITABLE PWM SWITCHING AND CONTROL METHODS FOR MODULAR MULTILEVEL CONVERTER DRIVES

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

## BARIŞ ÇİFTÇİ

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2014

Approval of the thesis:

# SELECTION OF SUITABLE PWM SWITCHING AND CONTROL METHODS FOR MODULAR MULTILEVEL CONVERTER DRIVES

submitted by **BARIŞ** ÇİFTÇİ in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Gülbin Dural Ünver<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>      |  |

|---------------------------------------------------------------------------------------------------|--|

| Prof. Dr. Gönül Turhan Sayan<br>Head of Department, <b>Electrical and Electronics Engineering</b> |  |

| Assoc. Prof. Dr. Ahmet M. Hava<br>Supervisor, Electrical and Electronics Eng. Dept., METU         |  |

| Examining Committee Members:                                                                      |  |

| Prof. Dr. Muammer Ermiş<br>Electrical and Electronics Engineering Dept., METU                     |  |

| Assoc. Prof. Dr. Ahmet M. Hava<br>Electrical and Electronics Engineering Dept., METU              |  |

| Prof. Dr. Kemal Leblebicioğlu<br>Electrical and Electronics Engineering Dept., METU               |  |

| Prof. Dr. Ali Nezih Güven<br>Electrical and Electronics Engineering Dept., METU                   |  |

| Eyyup Demirkutlu, M.S.<br>ADULARYA Energy Electric Gen. and Mining Inc.                           |  |

Date: 04/12/2014

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Barış Çiftçi

:

Signature

#### ABSTRACT

# SELECTION OF SUITABLE PWM SWITCHING AND CONTROL METHODS FOR MODULAR MULTILEVEL CONVERTER DRIVES

Çiftçi, Barış

M.S., Department of Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Ahmet M. Hava

December 2014, 239 Pages

The thesis focuses on the determination of suitable carrier based PWM switching and control method for modular multilevel converter drives. Characterization of various level-shifted and phase-shifted carrier based PWM methods are provided in terms of switching pulse patterns and resultant voltage waveforms both for N+1 and 2N+1 level output phase voltages. Modular multilevel converter PWM based control approaches are evaluated. Performances of different control methods are given for output harmonics distortion, submodule capacitor voltage ripple, circulating current ac component, efficiency and other criteria under equal switching count principle, for the dc/ac conversion step of a 10MW HVDC transmission system. Moreover, a 9.1MW induction motor drive application is studied from standstill to full speed range, giving attention to low frequency region operation. The study is conducted by means of mathematical analysis of the converter, topological and controller design, and detailed computer simulations.

Keywords: Modular multilevel converter, carrier based PWM, control, harmonics, submodule capacitor voltage, circulating current, efficiency, grid-interface, motor drive, simulation

# MODÜLER ÇOK SEVİYELİ DÖNÜŞTÜRÜCÜ SÜRÜCÜLERİ İÇİN UYGUN DGM ANAHTARLAMA VE KONTROL YÖNTEMİNİN SEÇİMİ

Çiftçi, Barış

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Ahmet M. Hava

Aralık 2014, 239 Sayfa

Bu tez modüler çok seviyeli dönüştürücü sürücüleri için uygun taşıyıcı tabanlı DGM anahtarlama ve kontrol yönteminin belirlenmesi üzerinde durmaktadır. N+1 ve 2N+1 seviyeli dönüştürücü çıkış faz gerilimleri için, çeşitli seviye kaydırmalı ve faz kaydırmalı taşıyıcı tabanlı DGM yöntemlerinin anahtarlama şablonları ve sonuç olarak meydana gelen gerilim dalga şekillerinin karakterizasyonu sağlanmaktadır. Modüler çok seviyeli dönüştürücülerin DGM tabanlı kontrol yaklaşımları değerlendirilmektedir. Farklı kontrol yöntemlerinin çıkış harmonik bozunma, altmodül kondansatörü gerilim kıpırtısı, dolaşım akımı ac bileşeni, verim ve diğer kıstaslar bakımından başarımları, 10MW'lık bir HVDC iletim sisteminin da/aa dönüşüm aşaması üzerinden karşılaştırılmıştır. Ayrıca düşük hız bölgesinde çalışmaya dikkat çekilerek, durma durumundan tam hızda çalışmaya kadar 9.1MW'lık bir endüksiyon motoru sürücüsü çalışılmıştır. Çalışma, dönüştürücünün matematiksel analizi, topolojik tasarımı, kontrolcü tasarımı ve ayrıntılı bilgisayar benzetimleri aracılığıyla gerçeklenmiştir.

Anahtar Kelimeler: Modüler çok seviyeli dönüştürücü, taşıyıcı temelli DGM, kontrol, harmonikler, altmodül kondansatör gerilimi, dolaşım akımı, verim, şebeke ara yüzü, motor sürücüsü, benzetim

To Göksu and My Parents

#### ACKNOWLEDGEMENTS

I would like to thank my supervisor, Assoc. Prof. Dr. Ahmet M. Hava for his support, encouragement, guidance and critiques on this study throughout my graduate education.

I would like to express my deepest gratitude to my dearest love Göksu for her endless love, support, and encouragements in all aspects of my life. Without her support, I would not be able to finish this work.

I express my deepest gratitude to my parents for their patience and support throughout my life.

I would like to acknowledge my friends Feyzullah Ertürk, Emre Kantar and S. Nadir Usluer for their help and support.

I wish to thank to Middle East Technical University Department of Electrical and Electronics Engineering faculty and staff for their help throughout my graduate studies.

# TABLE OF CONTENTS

| ABST   | 'RACT v                                                           |

|--------|-------------------------------------------------------------------|

| ÖZ     | vi                                                                |

| ACKN   | NOWLEDGEMENTSviii                                                 |

| TABL   | E OF CONTENTS ix                                                  |

| LIST   | OF TABLESxiii                                                     |

| LIST   | OF FIGURES xv                                                     |

| LIST   | OF ABBREVIATIONSxxi                                               |

| 1.     | INTRODUCTION1                                                     |

| 1.1.   | Background and Motivation1                                        |

| 1.1.1. | Typical Application Areas of MMC 4                                |

| 1.2.   | Scope of the Thesis                                               |

| 2.     | MULTILEVEL CONVERTER TOPOLOGIES15                                 |

| 2.1.   | Introduction15                                                    |

| 2.2.   | Classification of Conventional Multilevel Converter Topologies17  |

| 2.2.1. | Diode-Clamped (Neutral-point-clamped) Multilevel Converter 17     |

| 2.2.2. | Flying Capacitor (Capacitor-Clamped) Multilevel Converter 18      |

| 2.3.   | Submodule Based Multilevel Converters (Modular Multilevel Cascade |

| Conve  | erters)                                                           |

| 2.3.1. | Cascaded H-Bridges                                                |

| 2.3.2. | Modular Multilevel Converter                                      |

| 2.3.3. | Other Submodule Topologies                                        |

| 2.4.   | Semiconductor Devices for Multilevel Converters                   |

| 2.4.1. | Thyristor                                                         |

| 2.4.2. | IGBT (HVIGBT)                                                     |

| 2.4.3. | IGCT                                                              |

| 3.      | MATHEMATICAL ANALYSIS OF MODULAR MULTILEVEL                              |

|---------|--------------------------------------------------------------------------|

| CONV    | VERTER                                                                   |

| 3.1.    | Mathematical Model of Modular Multilevel Converter37                     |

| 3.2.    | Energy Dynamics and General Circuit Analysis of MMC42                    |

| 4.      | MODULAR MULTILEVEL CONVERTER SWITCHING METHODS47                         |

| 4.1.    | Introduction                                                             |

| 4.2.    | High Frequency (Carrier based) Switching                                 |

| 4.2.1.  | Scalar PWM [68]49                                                        |

| 4.2.1.1 | 1. Level-shift (LS) (Sub-Harmonic) Methods                               |

| 4.2.1.1 | 1.1. Phase Disposition (PD) Method49                                     |

| 4.2.1.1 | 1.2. Phase Opposition Disposition (POD) Method50                         |

| 4.2.1.1 | 1.3. Alternative Phase Opposition Disposition (APOD) Method51            |

| 4.2.1.2 | 2. Phase-shift (PS) (Carrier Disposition) Method                         |

| 4.2.2.  | Space Vector PWM53                                                       |

| 4.3.    | Low Frequency Switching                                                  |

| 4.3.1.  | Selective Harmonic Elimination                                           |

| 4.3.2.  | Space Vector Control                                                     |

| 4.4.    | Switching Pulse Patterns and Generated Output Voltage Characteristics of |

| Scalar  | • PWM Methods55                                                          |

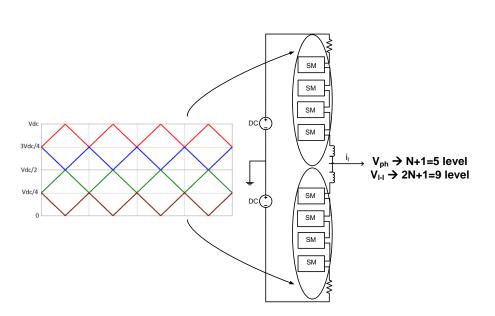

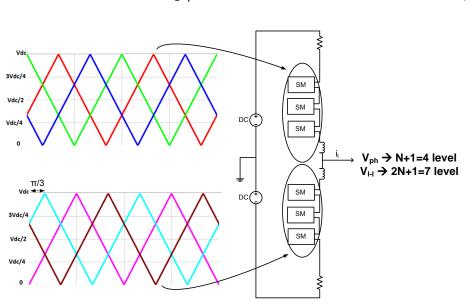

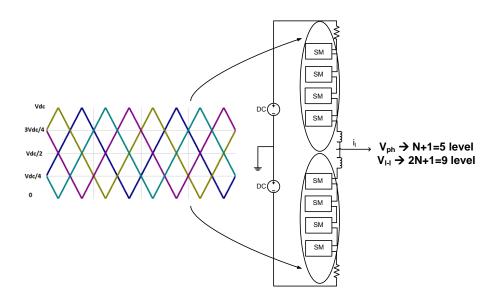

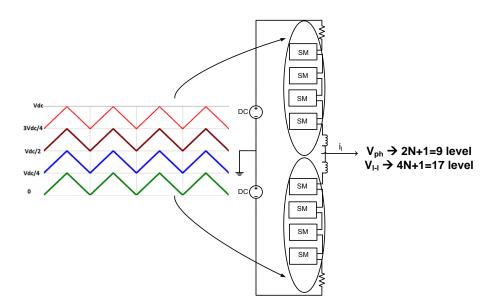

| 4.4.1.  | Discussion on Carrier Sets and Number of Output Voltage Levels           |

| 4.4.1.1 | 1. N+1 Level Phase Voltages                                              |

| 4.4.1.1 | 1.1. Level-shift Methods                                                 |

| 4.4.1.1 | 1.1.1. PD                                                                |

| 4.4.1.1 | 1.1.2. POD                                                               |

| 4.4.1.1 | 1.1.3. APOD                                                              |

| 4.4.1.1 | 1.2. Phase-shift Method59                                                |

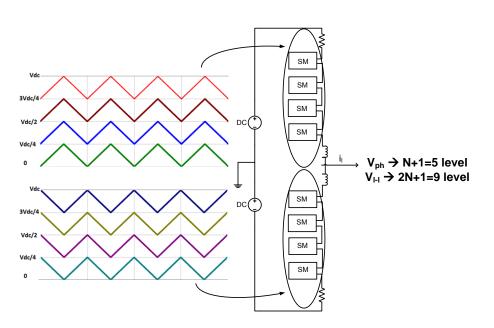

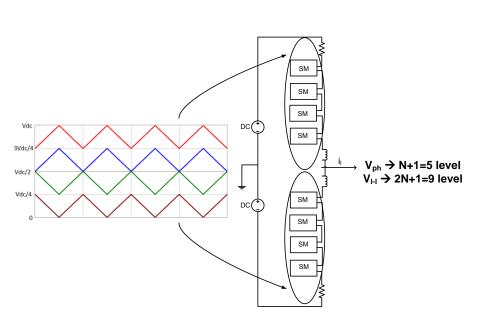

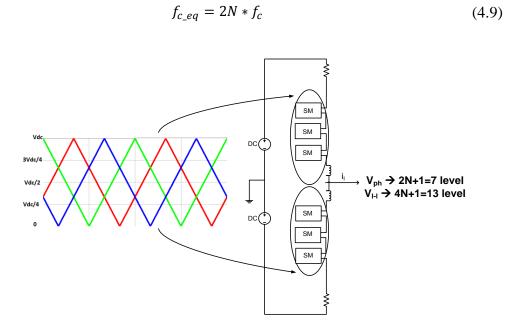

| 4.4.1.2 | 2. 2N+1 Level Phase Voltages61                                           |

| 4.4.1.2 | 2.1. Level-shift Methods61                                               |

| 4.4.1.2 | 2.1.1. PD                                                                |

| 4.4.1.2 | 2.1.2. POD                                                               |

| 4.4.1.2 | 2.1.3. APOD                                                              |

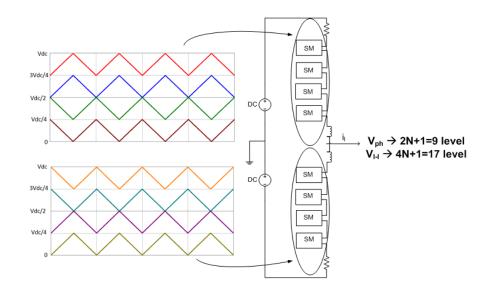

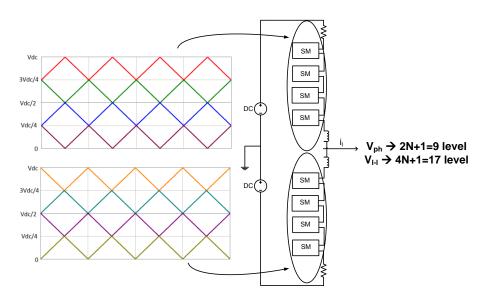

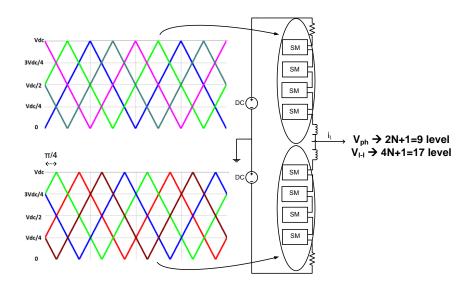

| 4.4.1.2.2. Phase-shift Method                               |                   |

|-------------------------------------------------------------|-------------------|

| 4.4.2. Analysis of Switching Pulse Patterns                 |                   |

| 4.4.3. Analysis of Generated Output Voltage Characteristics | 73                |

| 4.4.3.1. N+1 Level Output Phase Voltage                     | 73                |

| 4.4.3.2. 2N+1 Level Output Phase Voltage                    |                   |

| 4.5. Conclusion                                             |                   |

| 5. MODULAR MULTILEVEL CONVERTER COMPO                       | NENT RATING       |

| DETERMINATION                                               |                   |

| 5.1. Introduction                                           | 91                |

| 5.2. Discussion on Number of Submodules per Arm             |                   |

| 5.3. Arm Inductor Value                                     |                   |

| 5.4. Submodule Capacitor Value                              |                   |

| 6. MODULAR MULTILEVEL CONVERTER SWI                         | TCHING AND        |

| CONTROL                                                     |                   |

| 6.1. Introduction                                           |                   |

| 6.2. Output Power Control                                   |                   |

| 6.3. Direct Modulation                                      |                   |

| 6.3.1. Submodule Capacitor Voltage Balancing                |                   |

| 6.3.1.1. Sort and Select (S&S) Method                       |                   |

| 6.3.1.2. Sort and Select Method with Reduced Switching      | Count (S&S-RS)    |

| Method                                                      | 110               |

| 6.3.1.3. Voltage Balancing with Carrier Rotation            |                   |

| 6.3.2. Circulating Current Control                          |                   |

| 6.3.3. Reference Signal Generation and Modulation           |                   |

| 6.4. Phase-shifted Carrier Based Control                    |                   |

| 6.5. Other Control Approaches: Closed-loop Control and Open | n-loop Control123 |

| 7. SIMULATION STUDY AND CONTROL METHODS                     | PERFORMANCE       |

| COMPARISON                                                  |                   |

| 7.1. Introduction                                           |                   |

| 7.2. Simulated System                                       |                   |

| 7.2.1. Number of Submodules per Arm                         |                   |

| 7.2.2. | Submodule Capacitor Value                                            | 128      |

|--------|----------------------------------------------------------------------|----------|

| 7.2.3. | Arm Inductor Value                                                   | 129      |

| 7.2.4. | Simulation Sets and Limitations                                      | 130      |

| 7.3.   | Simulation Results                                                   | 132      |

| 7.3.1. | Rated Power (10MVA) with Unity Load Angle $(\cos(\phi)=1)$           | 132      |

| 7.3.1. | 1. Case 1: N+1 Output Voltage Levels                                 | 132      |

| 7.3.1. | 2. Case 2: 2N+1 Output Voltage Levels                                | 150      |

| 7.3.1. | 3. Half Rated Power (5MVA) with Unity Load Angle $(\cos(\varphi)=1)$ | 168      |

| 7.3.1. | 4. Case 1: N+1 Output Voltage Levels                                 | 168      |

| 7.3.1. | 5. Case 2: 2N+1 Output Voltage Levels                                | 182      |

| 8.     | MMC BASED MOTOR DRIVE                                                | 201      |

| 8.1.   | Introduction                                                         | 201      |

| 8.2.   | Submodule Capacitor Voltage Ripple Reduction for Low-Speed           | Region   |

| Opera  | ation                                                                | 202      |

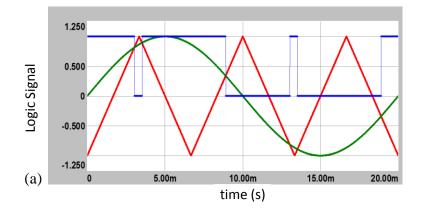

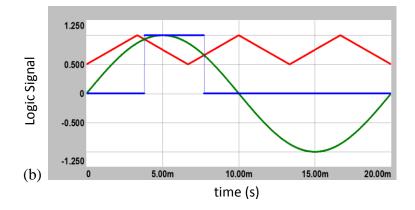

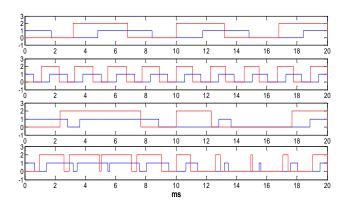

| 8.2.1. | Selection of Waveforms for vcm and icirc                             | 205      |

| 8.2.2. | Control Method with Low Frequency Region Operation                   | 206      |

| 8.3.   | Operation of a 9.1MW Induction Machine with MMC and Sin              | nulation |

| Result | ts                                                                   | 208      |

| 9.     | CONCLUSION                                                           | 215      |

| REFE   | ERENCES                                                              | 221      |

| APPE   | ENDIX A. CLARK AND PARK TRANSFORMATIONS                              | 233      |

| A.1 C  | Clark Transformation                                                 | 233      |

| A.2 P  | ark Transformation                                                   | 234      |

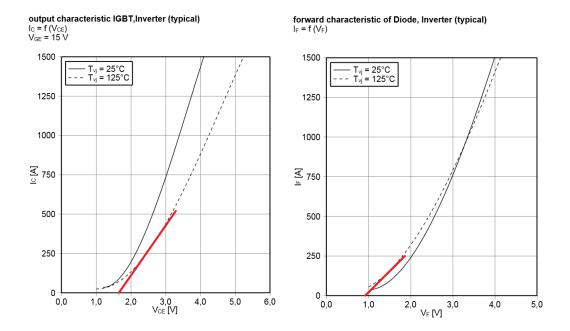

| APPE   | ENDIX B. SIMULATION LOSS CALCULATIONS                                | 237      |

| B.1 S  | witching Losses                                                      | 237      |

| B2C    | Conduction Losses                                                    |          |

## LIST OF TABLES

## TABLES

| Table 1.1 Several HVDC projects based on MMC concept [70], [71]6                      |

|---------------------------------------------------------------------------------------|

| Table 1.2 Several STATCOM projects based on MMC concept [74], [75]9                   |

| Table 2.1 Switch states for the desired output voltage of the five level converter 18 |

| Table 2.2 Switch states for the desired output voltage of the five-level converter 19 |

| Table 2.3 Submodule based multilevel converter topology variations                    |

| Table 2.4 Full-bridge circuit switching states    24                                  |

| Table 2.5 Half-bridge circuit switching states    27                                  |

| Table 2.6 Power semiconductors overview [76]                                          |

| Table 2.7 Development of the main thyristor characteristic values [41]33              |

| Table 2.8 Fundamental characteristics for the HVIGBTs of different manufacturers      |

| [77] -[92]                                                                            |

| Table 2.9 Characteristics overview between IGCTs and IGBT modules [40] 35             |

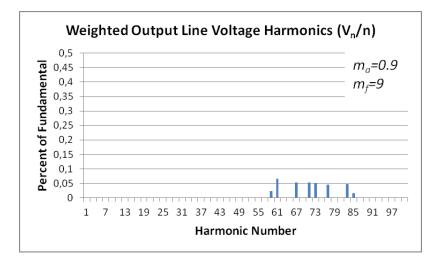

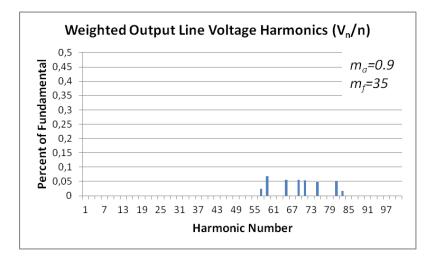

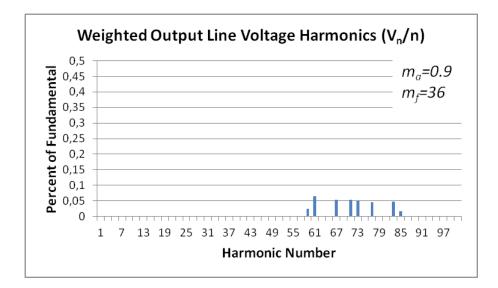

| Table 4.1 $m_a$ and $m_f$ calculation for scalar PWM methods [13]67                   |

| Table 4.2 Locations of output line voltage harmonics for scalar PWM methods 88        |

| Table 7.1 MMC simulation circuit parameters    130                                    |

| Table 7.2 Simulation sets    131                                                      |

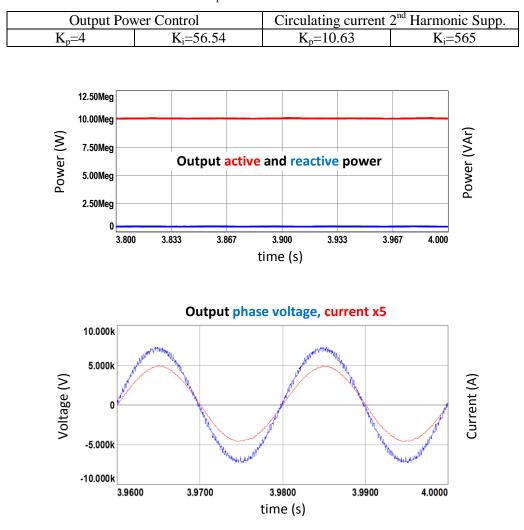

| Table 7.3 $K_p$ and $K_i$ values of S&S method                                        |

| Table 7.4 $K_p$ and $K_i$ values of S&S-RS method                                     |

| Table 7.5 $K_p$ and $K_i$ values of CR method                                         |

| Table 7.6 $K_p$ and $K_i$ values of PSCB method                                       |

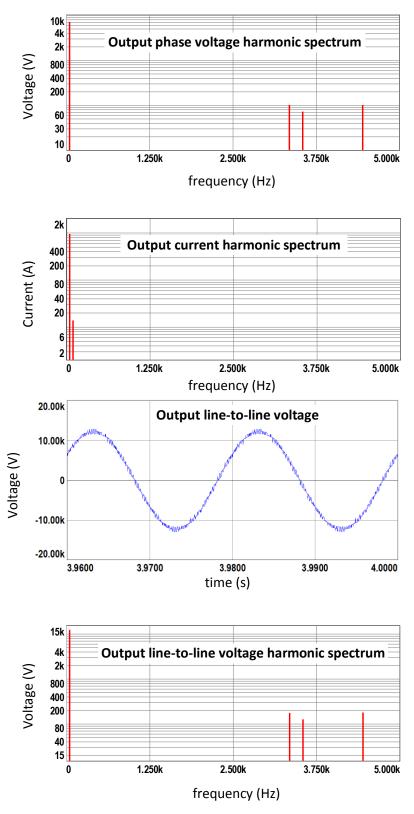

| Table 7.7 Simulation results numerical data for N+1 level output voltage 149          |

| Table 7.8 $K_p$ and $K_i$ values of S&S method                                        |

| Table 7.9 $K_p$ and $K_i$ values of S&S-RS method                                     |

| Table 7.10 $K_{p}$ and $K_{i}$ values of CR method157                           |

|---------------------------------------------------------------------------------|

| Table 7.11 $K_p$ and $K_i$ values of PSCB method161                             |

| Table 7.12 Simulation results numerical data for 2N+1 level output voltage165   |

| Table 7.13 Simulation results numerical data for both N+1 and 2N+1 level output |

| voltage, full load167                                                           |

| Table 7.14 $K_p$ and $K_i$ values of S&S method168                              |

| Table 7.15 $K_p$ and $K_i$ values of S&S-RS method171                           |

| Table 7.16 $K_p$ and $K_i$ values of CR method175                               |

| Table 7.17 $K_p$ and $K_i$ values of PSCB method178                             |

| Table 7.18 Simulation results numerical data for N+1 level output voltage182    |

| Table 7.19 $K_p$ and $K_i$ values of S&S method                                 |

| Table 7.20 $K_p$ and $K_i$ values of S&S-RS method                              |

| Table 7.21 $K_p$ and $K_i$ values of CR method                                  |

| Table 7.22 $K_p$ and $K_i$ values of PSCB method193                             |

| Table 7.23 Simulation results numerical data for 2N+1 level output voltage      |

| Table 7.24 Simulation results numerical data for both N+1 and 2N+1 level output |

| voltage, half load199                                                           |

| Table 8.1 Simulation parameters for MMC motor drive    209                      |

| Table 8.2 Rated parameters of the induction machine*    210                     |

| Table 9.1 Suggested control methods for $N+1$ and $2N+1$ level output voltage   |

| generating methods                                                              |

| Table A.1 Types of Clark transformation    234                                  |

## LIST OF FIGURES

### FIGURES

| Figure 1.1 Modular multilevel converter                                                  |

|------------------------------------------------------------------------------------------|

| Figure 1.2 Output voltage synthesis concepts of two, three and multilevel converters     |

| [4]                                                                                      |

| Figure 1.3 Cost estimations for ac and HVDC transmission by distance [3]                 |

| Figure 1.4 HelWin2 offshore HVDC platform by Siemens [8]7                                |

| Figure 1.5 Submodule (up) and MMC (down) structure of MaxSine (Alstom) [7]7              |

| Figure 1.6 MMC based motor drive for a converter-fed synchronous machine by              |

| ABB and Oberhasli Hydroelectric Power Company                                            |

| Figure 1.7 Kikiva STATCOM project based on MMC by Siemens [12]10                         |

| Figure 2.1 Single-phase five-level diode-clamped converter at left and output voltage    |

| waveform at right                                                                        |

| Figure 2.2 Single-phase five level flying capacitor converter at left and output voltage |

| waveform at right                                                                        |

| Figure 2.3 (a) SSBC (b) SDBC                                                             |

| Figure 2.4 Possible circuit configurations of DSCC and DSBC (a) Power circuit            |

| using coupled arm inductors (b) Power circuit using non-coupled arm inductors            |

| (c) Chopper cell (DSCC) (d) Bridge cell (DSBC)                                           |

| Figure 2.5 The full-bridge circuit topology                                              |

| Figure 2.6 Submodule, arm and typical converter arrangement illustrations of MMC         |

| by Siemens [39]25                                                                        |

| Figure 2.7 Circuit topology of modular multilevel converter                              |

| Figure 2.8 Half-bridge (chopper) circuit                                                 |

| Figure 2.9 States of half-bridge (chopper) circuit and current paths27                   |

| Figure 2.10 (a) The clamp double circuit (b) The five level cross connected circuit |

|-------------------------------------------------------------------------------------|

| (c, d) capacitor-clamped and diode-clamped three-level converters [69]30            |

| Figure 2.11 Semiconductor market according to power ratings [3]31                   |

| Figure 2.12 Power semiconductors by July 2011 [40]                                  |

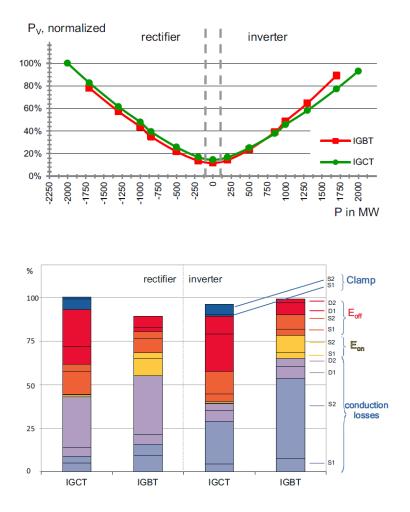

| Figure 2.13 Normalized semiconductor losses at the top and semiconductor losses of  |

| a MMC submodule splitted in its components for P=850MW, Q=350MVar,                  |

| $f_{switch}$ =150Hz, $V_{dc}$ = 600kV at the bottom [40]36                          |

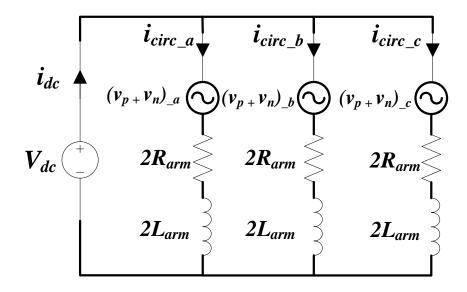

| Figure 3.1 Circuit structure of MMC                                                 |

| Figure 4.1 Switching methods for modular multilevel converters                      |

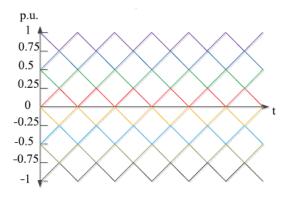

| Figure 4.2 Phase disposition (PD) method                                            |

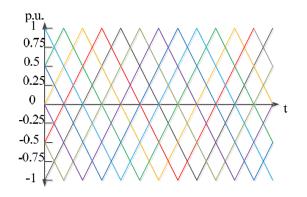

| Figure 4.3 Phase opposition disposition (POD) method                                |

| Figure 4.4 Alternative phase opposition disposition (APOD) method                   |

| Figure 4.5 Phase-shifted carriers method                                            |

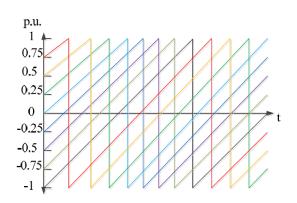

| Figure 4.6 Sawtooth rotation method                                                 |

| Figure 4.7 Space vector diagrams for two-level converter at left and five-level     |

| converter at right                                                                  |

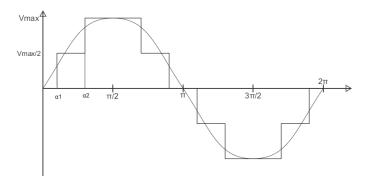

| Figure 4.8 Output voltage waveform for a five-level converter, switching angles     |

| rigue no output voluge wavelorm for a rive level converter, switching angles        |

| determined by selective harmonic elimination method                                 |

|                                                                                     |

| determined by selective harmonic elimination method                                 |

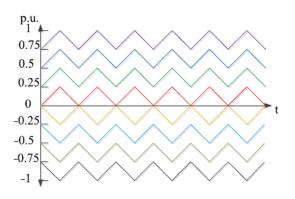

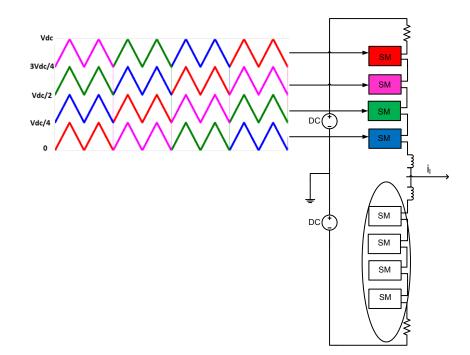

| Figure 4.18 Carrier sets for 2N+1 level phase voltage of phase-shift method with          |

|-------------------------------------------------------------------------------------------|

| even number of submodules                                                                 |

| Figure 4.19 MMC with four submodule per arm                                               |

| Figure 4.20 Carrier, reference and switching pulse signals for (a) PS and (b) PD          |

| methods for $m_a=1$ and $m_f=3$                                                           |

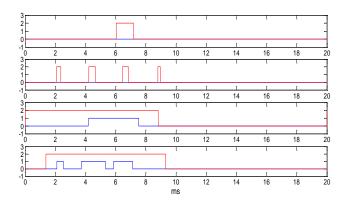

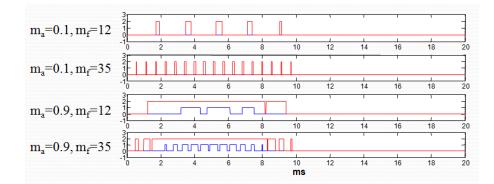

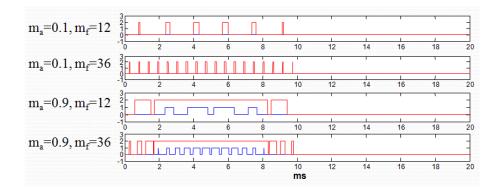

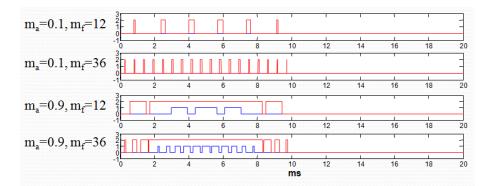

| Figure 4.21 Switching pulse patterns of PS for (ma=0.1, mf=3), (ma=0.1, mf=9),            |

| (ma=0.9, mf=3) and (ma=0.9, mf=9) from the top to the bottom                              |

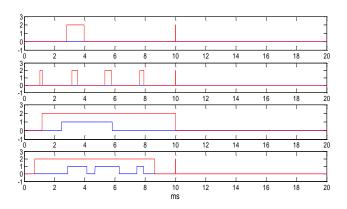

| Figure 4.22 Switching pulse patterns of PD for (ma=0.1, mf=3), (ma=0.1, mf=9),            |

| (ma=0.9, mf=3) and (ma=0.9, mf=9) from the top to the bottom                              |

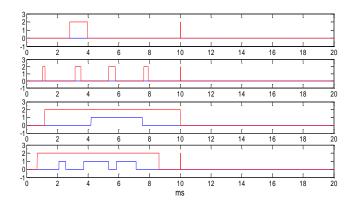

| Figure 4.23 Switching pulse patterns of POD for (ma=0.1, mf=3), (ma=0.1, mf=9),           |

| (ma=0.9, mf=3) and (ma=0.9, mf=9) from the top to the bottom                              |

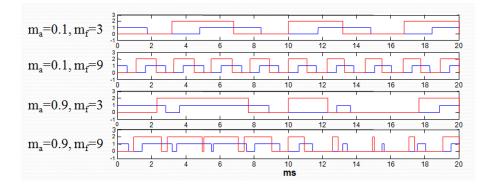

| Figure 4.24 Switching pulse patterns of APOD for (ma=0.1, mf=3), (ma=0.1, mf=9),          |

| (ma=0.9, mf=3) and (ma=0.9, mf=9) from the top to the bottom                              |

| Figure 4.25 Switching pulse patterns of PS                                                |

| Figure 4.26 Switching pulse patterns of PD71                                              |

| Figure 4.27 Switching pulse patterns of POD71                                             |

| Figure 4.28 Switching pulse patterns of APOD                                              |

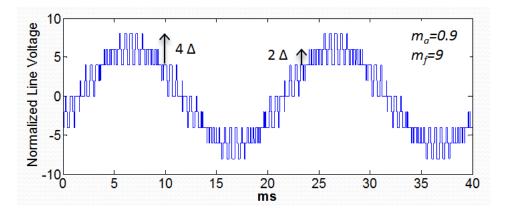

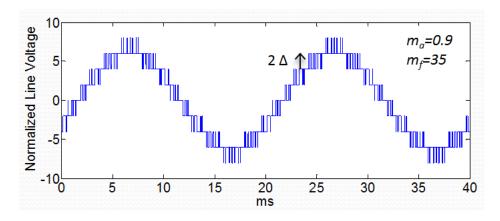

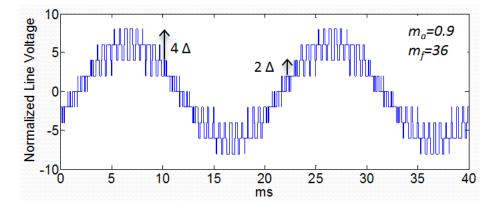

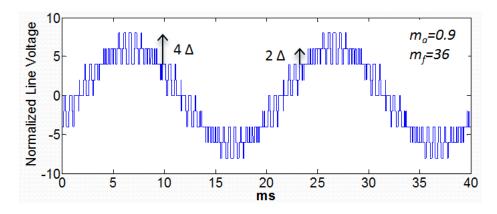

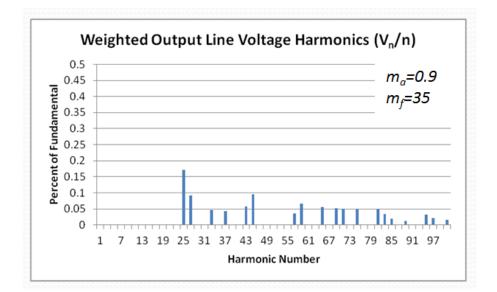

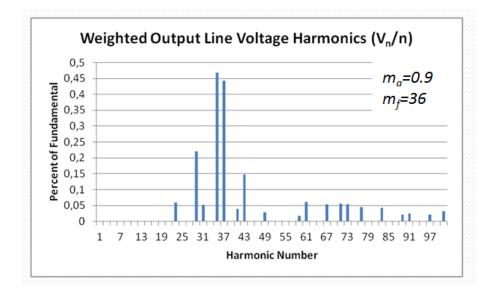

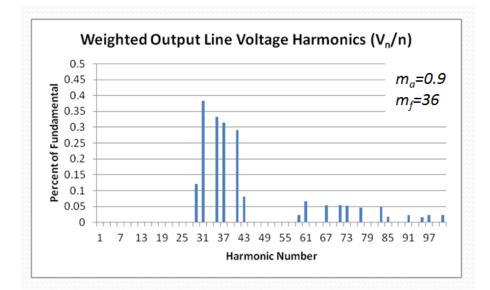

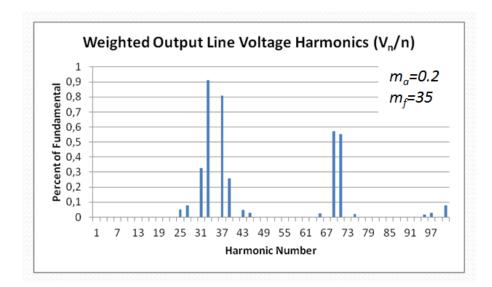

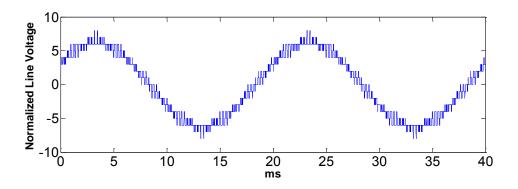

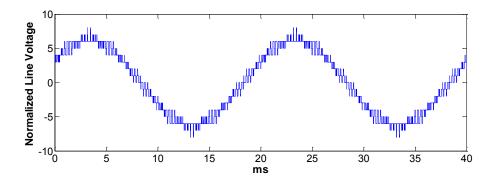

| Figure 4.29 Normalized line voltage of PS for N+1 level V <sub>ph</sub> 74                |

| Figure 4.30 Normalized line voltage of PD for N+1 level V <sub>ph</sub> 74                |

| Figure 4.31 Normalized line voltage of POD for N+1 level V <sub>ph</sub> 74               |

| Figure 4.32 Normalized line voltage of APOD for N+1 level $V_{ph}$                        |

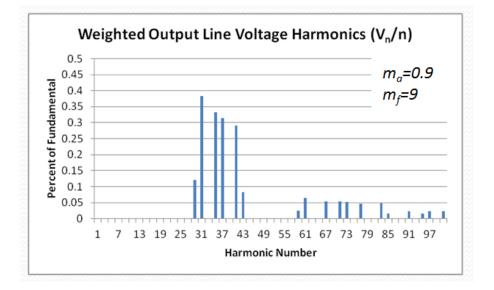

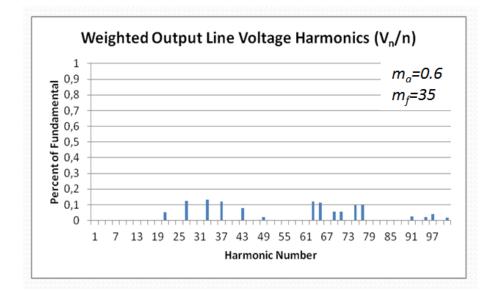

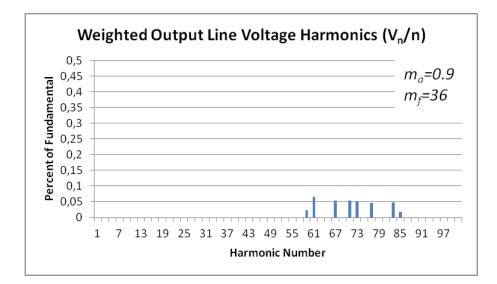

| Figure 4.33 Weighted line voltage harmonics of PS for N+1 level $V_{ph}$ 76               |

| Figure 4.34 Weighted line voltage harmonics of PD for N+1 level $V_{ph}$                  |

| Figure 4.35 Weighted line voltage harmonics of POD for N+1 level $V_{ph}$ 77              |

| Figure 4.36 Weighted line voltage harmonics of APOD for N+1 level $V_{ph}$ 77             |

| Figure 4.37 Weighted line voltage harmonics of PD for N+1 level $V_{ph}$                  |

| Figure 4.38 Weighted line voltage harmonics of PD for N+1 level $V_{ph}$                  |

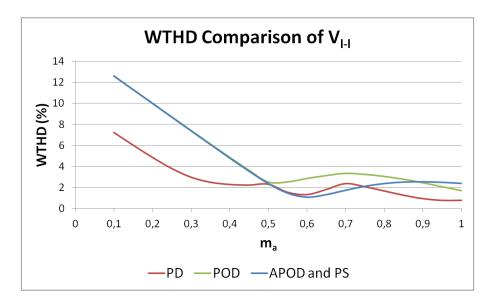

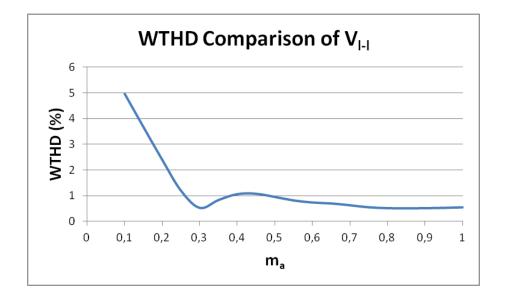

| Figure 4.39 WTHD values for changing $m_a$ and fixed $m_f=3$ and $m_f=9$ at the top and   |

| at the bottom, for N+1 level $V_{ph}$                                                     |

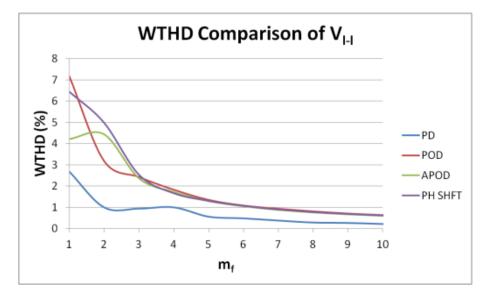

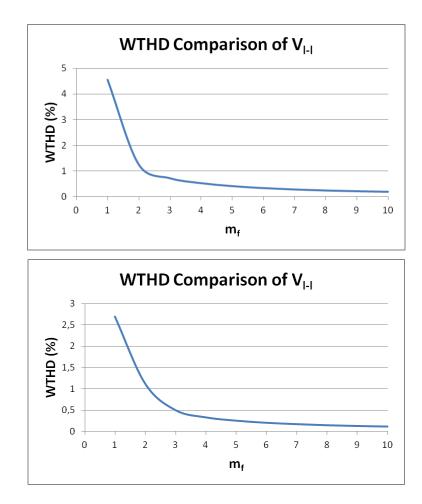

| Figure 4.40 WTHD values for changing $m_f$ and fixed $m_a$ =0.6 and $m_a$ =0.9 at the top |

| and at the bottom, for N+1 level $V_{ph}$                                                 |

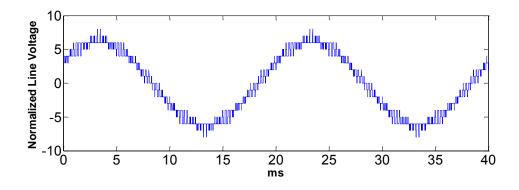

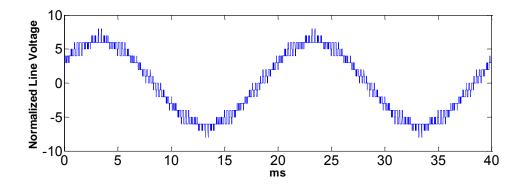

| Figure 4.41 Normalized line voltage of PS for 2N+1 level V <sub>ph</sub>                  |

|-------------------------------------------------------------------------------------------|

| Figure 4.42 Normalized line voltage of PD for 2N+1 level V <sub>ph</sub>                  |

| Figure 4.43 Normalized line voltage of POD for 2N+1 level V <sub>ph</sub>                 |

| Figure 4.44 Normalized line voltage of APOD for 2N+1 level V <sub>ph</sub> 83             |

| Figure 4.45 Weighted line voltage harmonics of PS for 2N+1 level V <sub>ph</sub>          |

| Figure 4.46 Weighted line voltage harmonics of PD for 2N+1 level V <sub>ph</sub>          |

| Figure 4.47 Weighted line voltage harmonics of POD for 2N+1 level V <sub>ph</sub> 85      |

| Figure 4.48 Weighted line voltage harmonics of APOD for 2N+1 level V <sub>ph</sub> 85     |

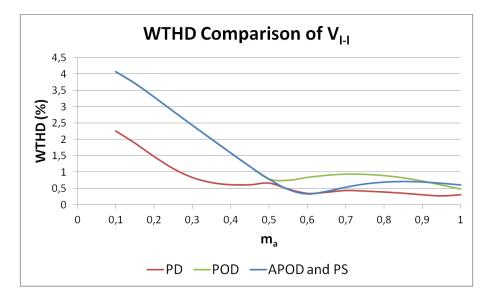

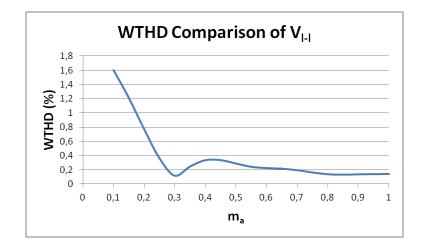

| Figure 4.49 WTHD values for changing $m_a$ and fixed $m_f=3$ and $m_f=9$ at the top and   |

| at the bottom, valid for all the LS and PS methods for 2N+1 level $V_{ph}$                |

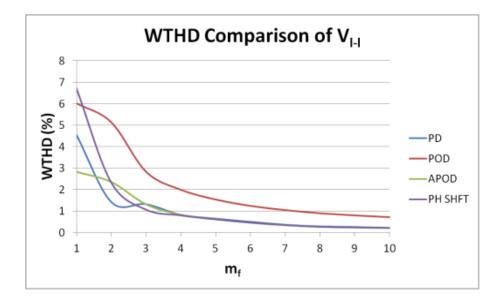

| Figure 4.50 WTHD values for changing $m_f$ and fixed $m_a$ =0.6 and $m_a$ =0.9 at the top |

| and at the bottom, valid for all the LS and PS methods for 2N+1 level $V_{\text{ph}}$ 87  |

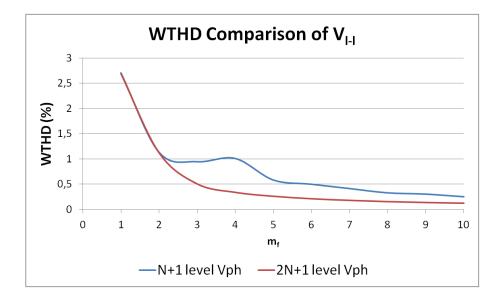

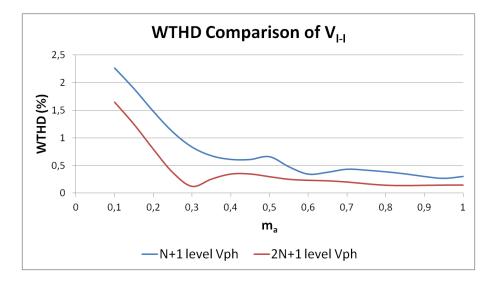

| Figure 4.51 WTHD values for changing $m_f$ and fixed $m_a$ =0.9 at the top and changing   |

| $m_a$ and fixed $m_f\!\!=\!\!9$ at the bottom, for N+1 and 2N+1 level $V_{ph}90$          |

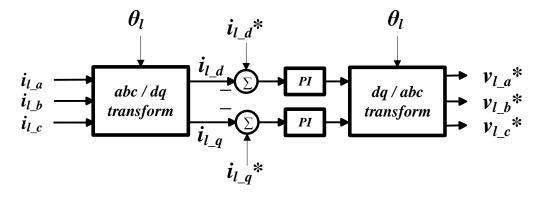

| Figure 6.1 Block diagram of active and reactive power control for MMC101                  |

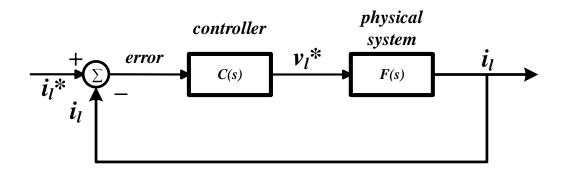

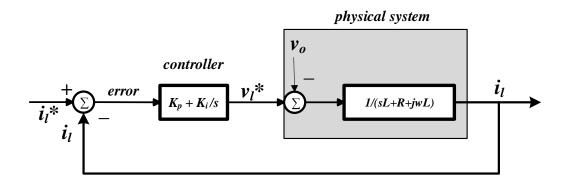

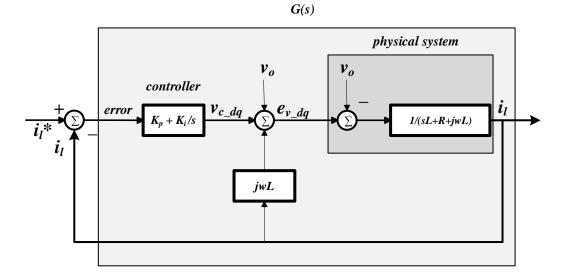

| Figure 6.2 Overview of the output current PI controller and physical system102            |

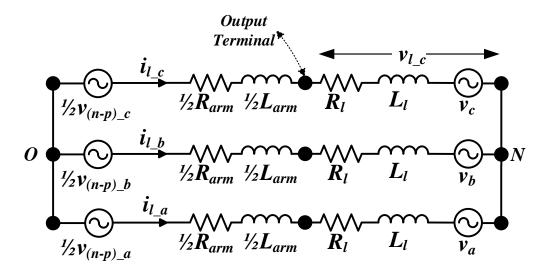

| Figure 6.3 Equivalent circuit of MMC in terms of output currents102                       |

| Figure 6.4 Overview of the output current PI controller and physical system with          |

| output voltage                                                                            |

| Figure 6.5 Feed forward of output dq current coupling term and output voltage of the      |

| converter106                                                                              |

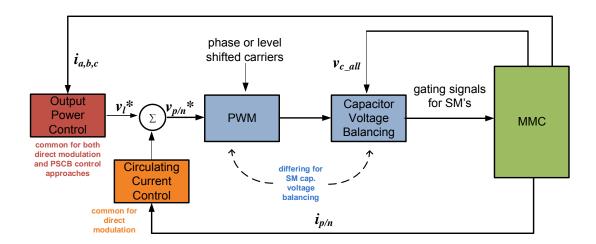

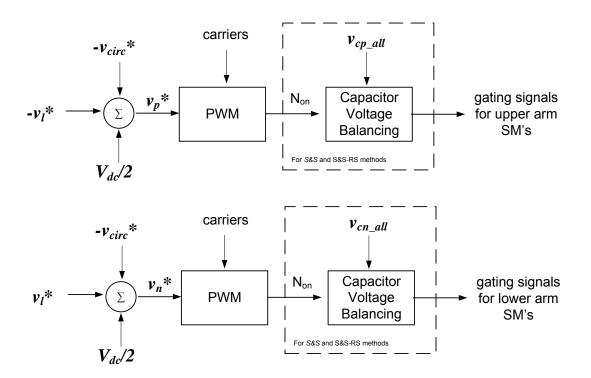

| Figure 6.6 Block diagram of direct modulation method107                                   |

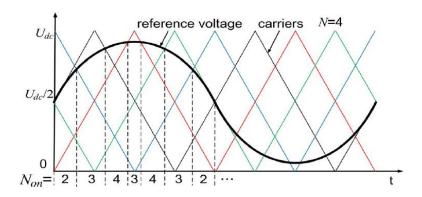

| Figure 6.7 Determination of N <sub>on</sub> [58]109                                       |

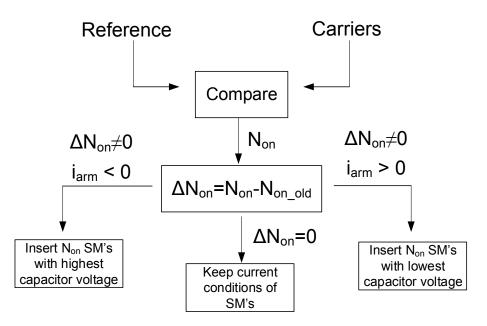

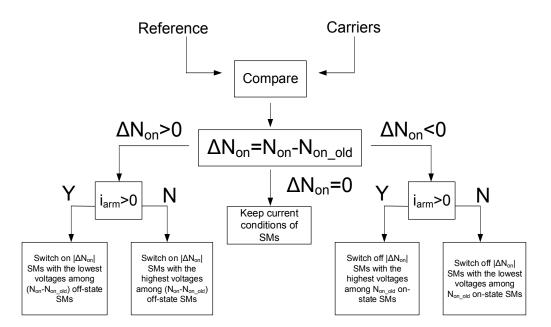

| Figure 6.8 Determination of inserted submodules to the current path for sort and          |

| select method110                                                                          |

| Figure 6.9 Determination of inserted or bypassed submodules for sort and select           |

| method with reduced number of switching                                                   |

| Figure 6.10 Carrier rotation method for submodule capacitor voltage balancing113          |

| Figure 6.11 Circulating current equivalent circuit of MMC115                              |

|                                                                                           |

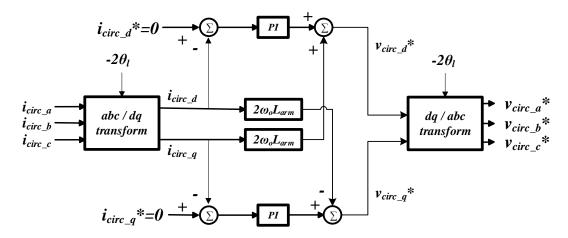

| Figure 6.12 Circulating current second harmonic controller block diagram117               |

| Figure 6.13 Block diagram for generation of reference signals and the remaining                 |

|-------------------------------------------------------------------------------------------------|

| process for obtaining gate signals of submodules                                                |

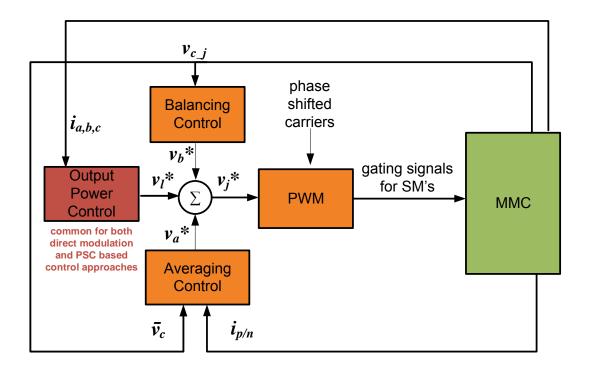

| Figure 6.14 Block diagram of phase-shifted carrier based control 119                            |

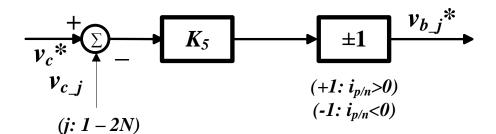

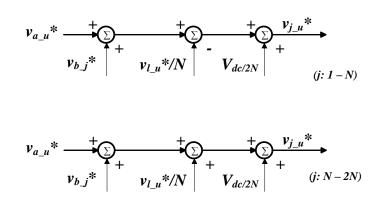

| Figure 6.15 Averaging control of PSCB control                                                   |

| Figure 6.16 Balancing control of PSCB control 122                                               |

| Figure 6.17 Reference signal generation for upper and lower arm submodules 122                  |

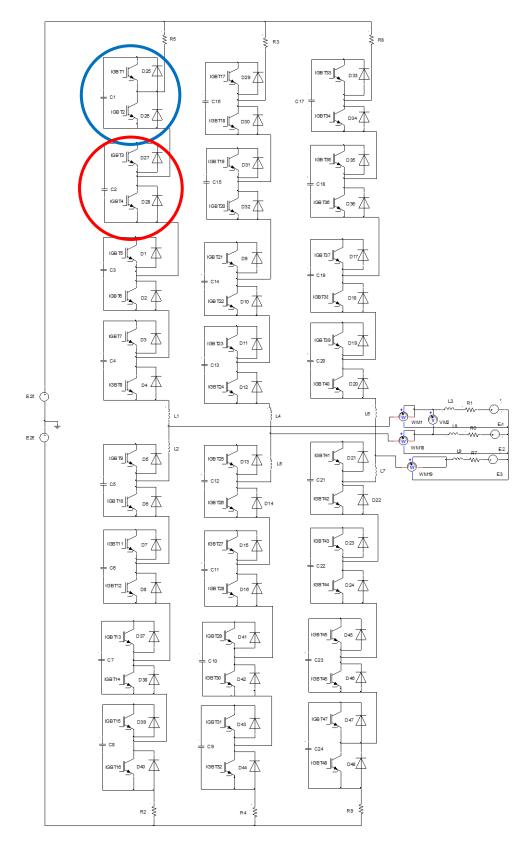

| Figure 7.1 Circuit structure of the simulated dc/ac conversion step of an HVDC                  |

| system in Simplorer 127                                                                         |

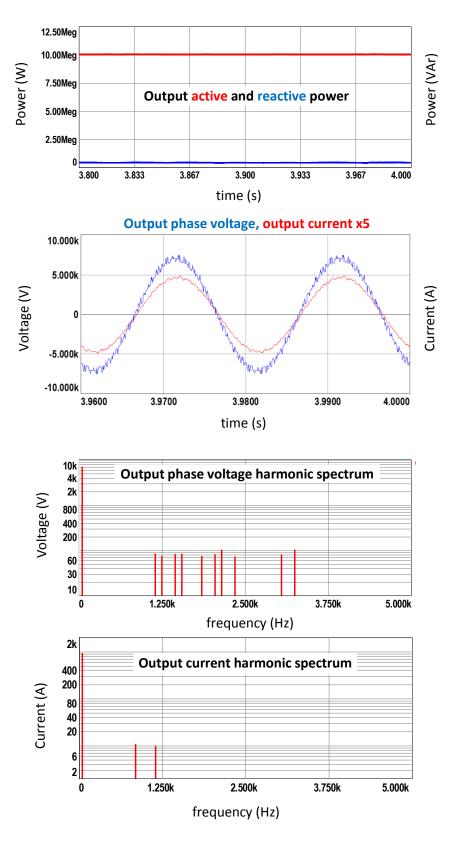

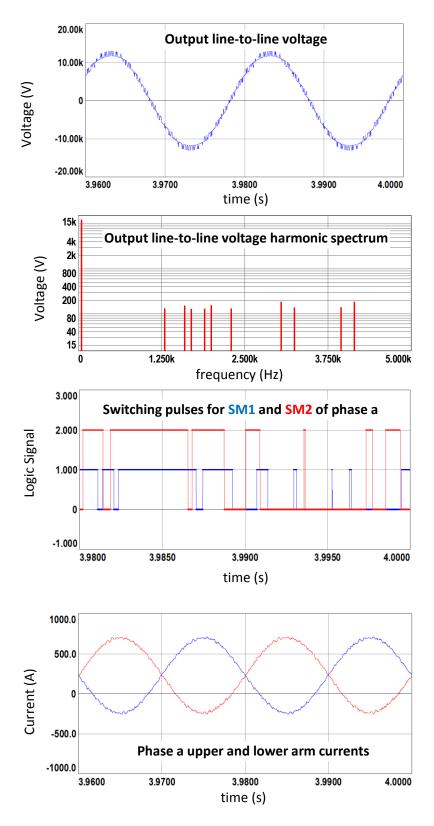

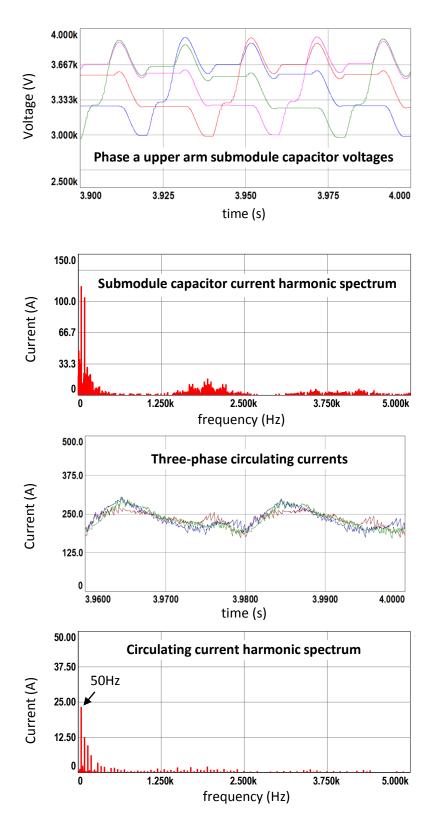

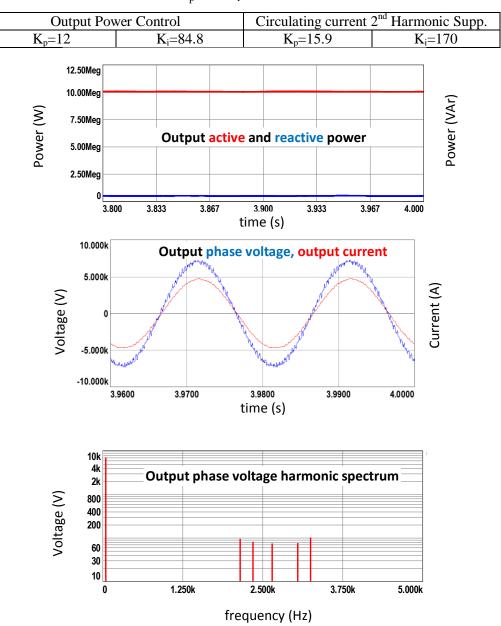

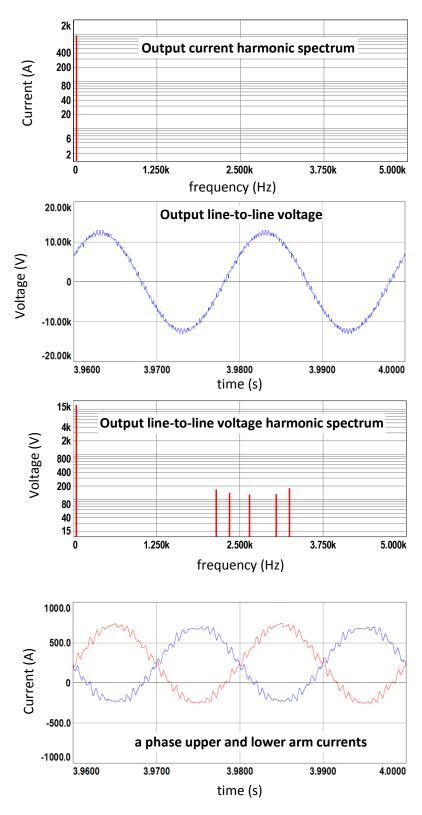

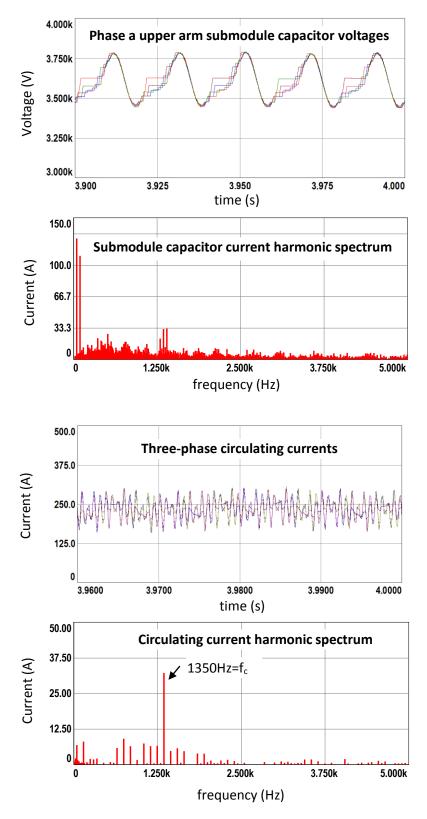

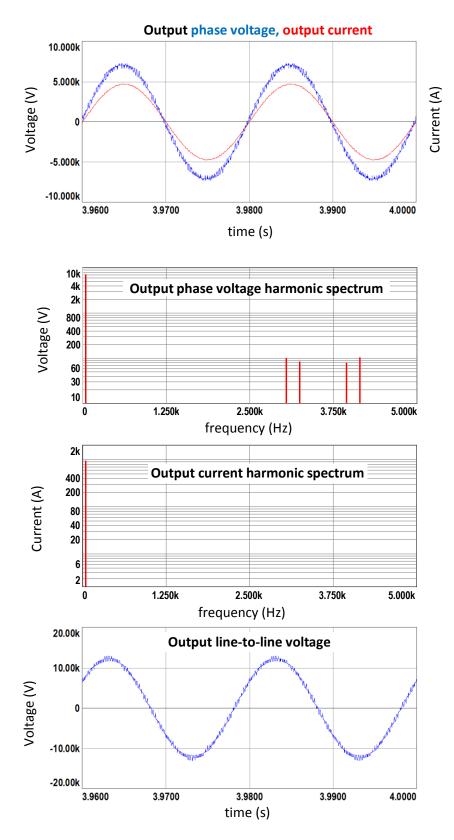

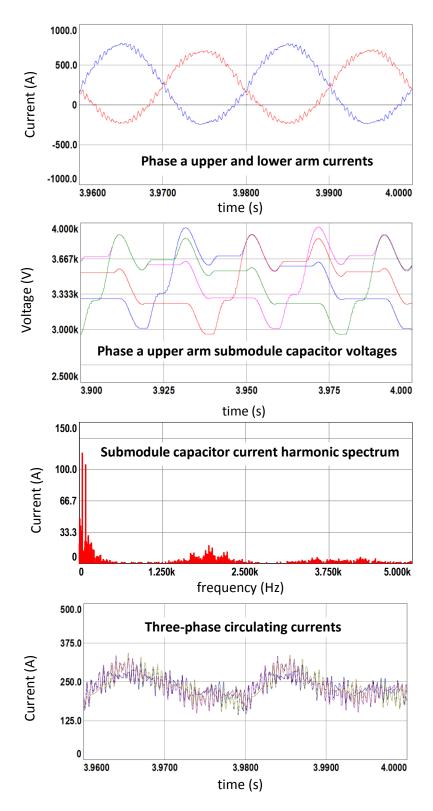

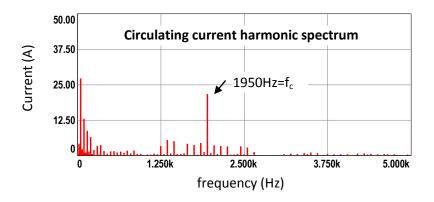

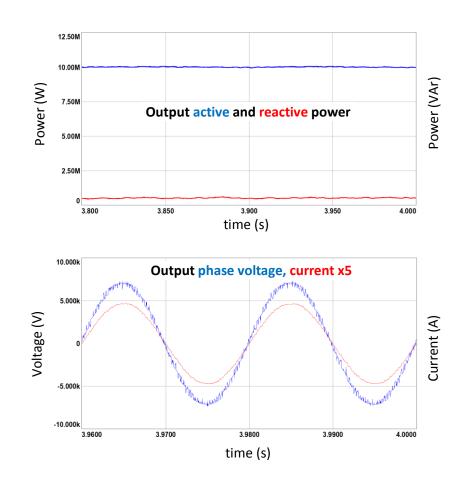

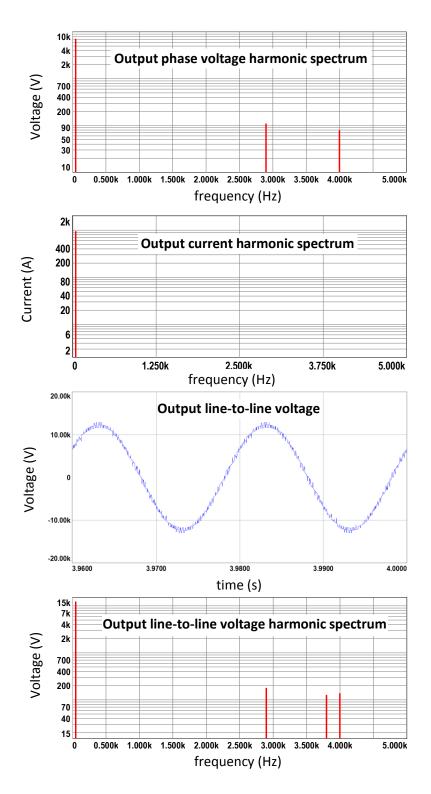

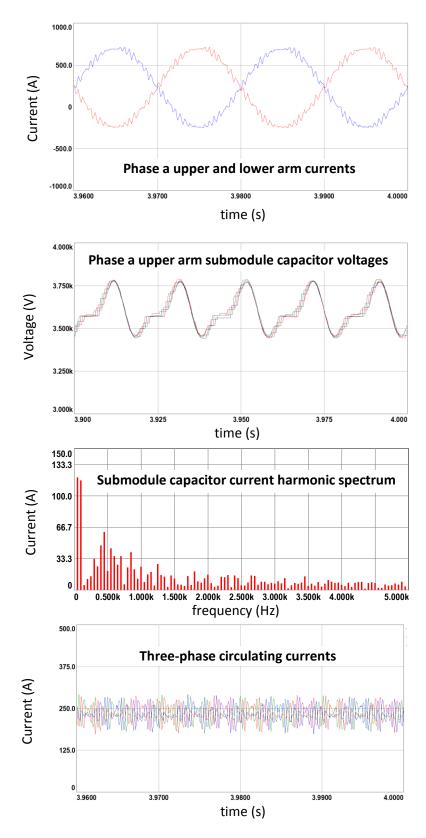

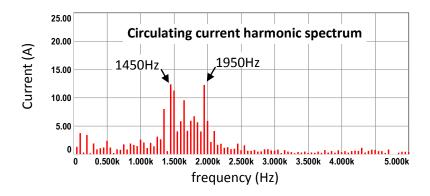

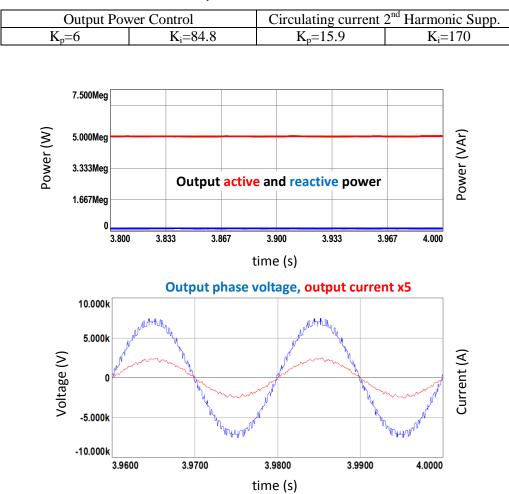

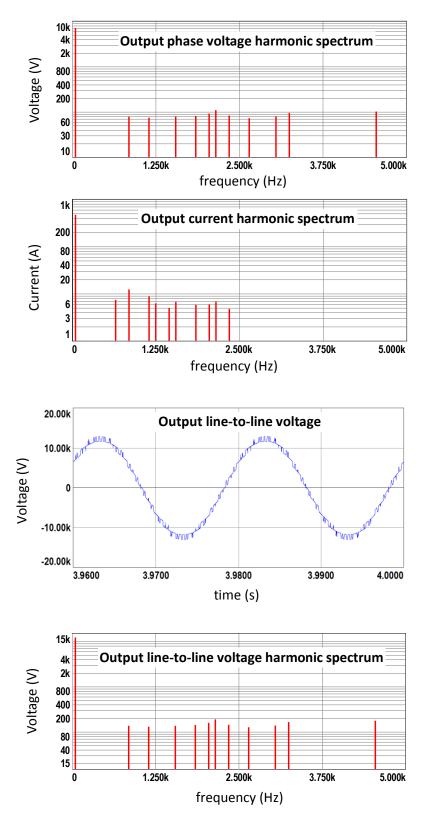

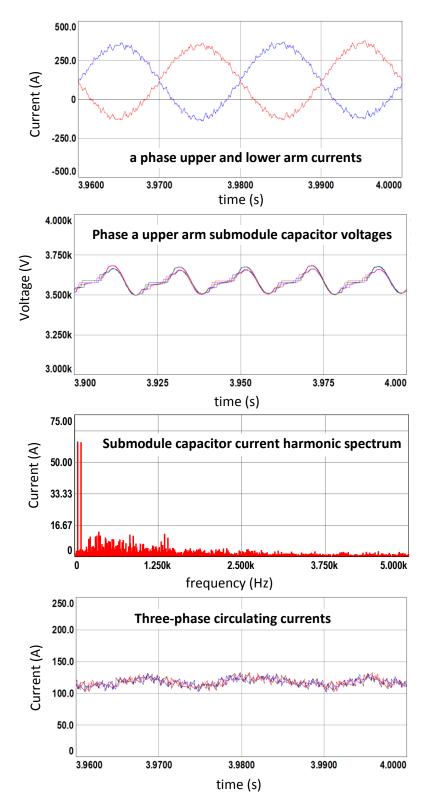

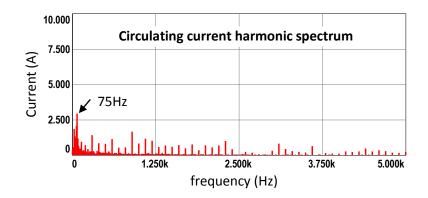

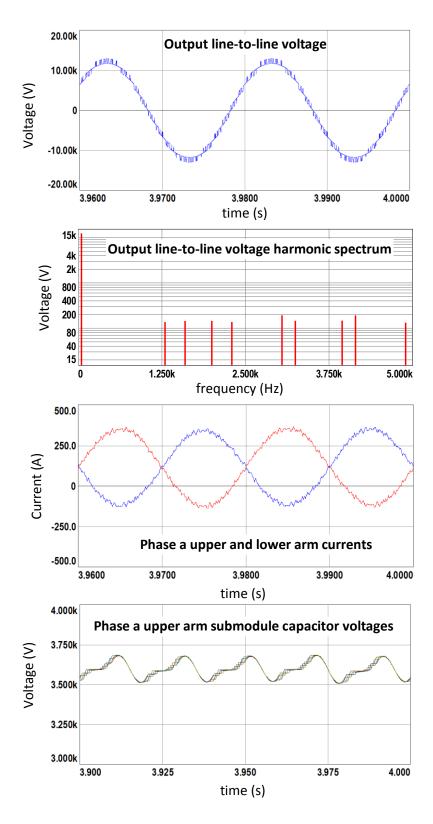

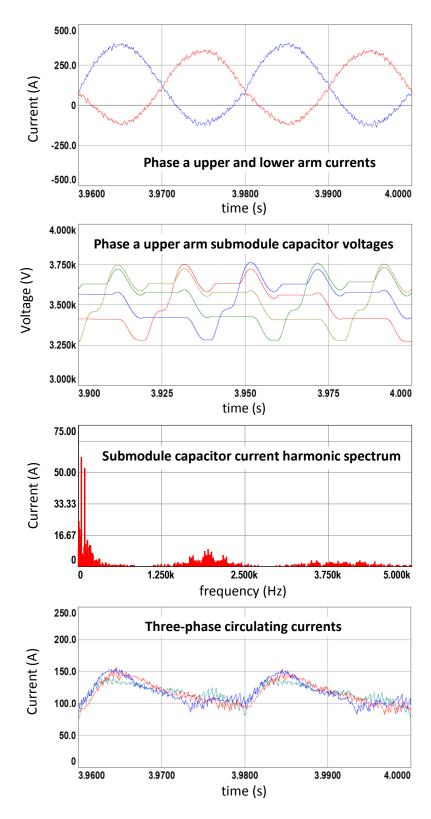

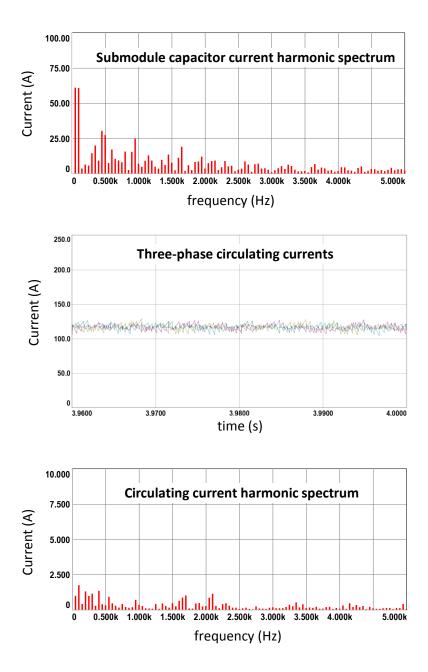

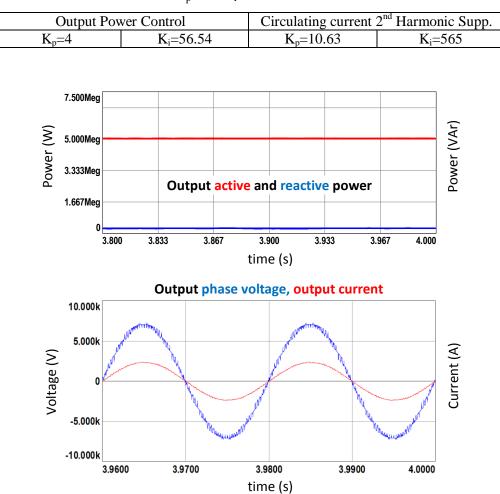

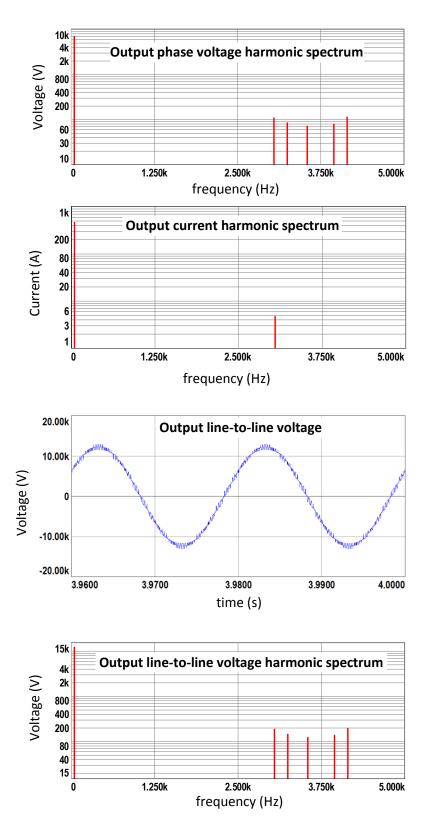

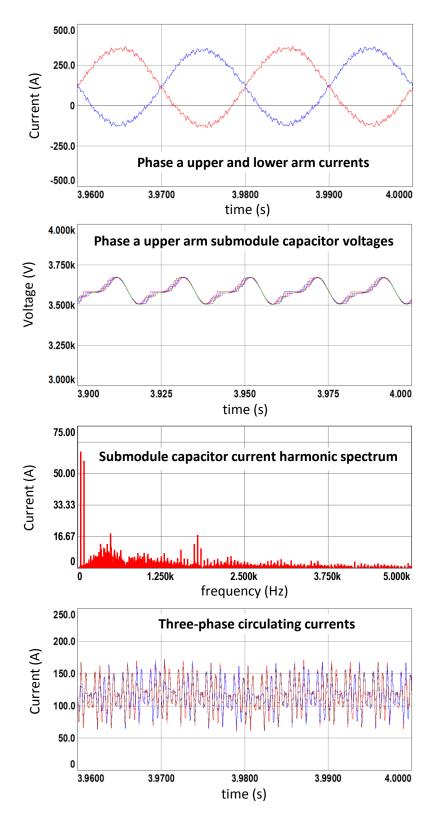

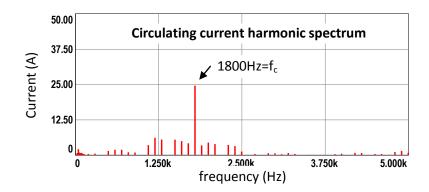

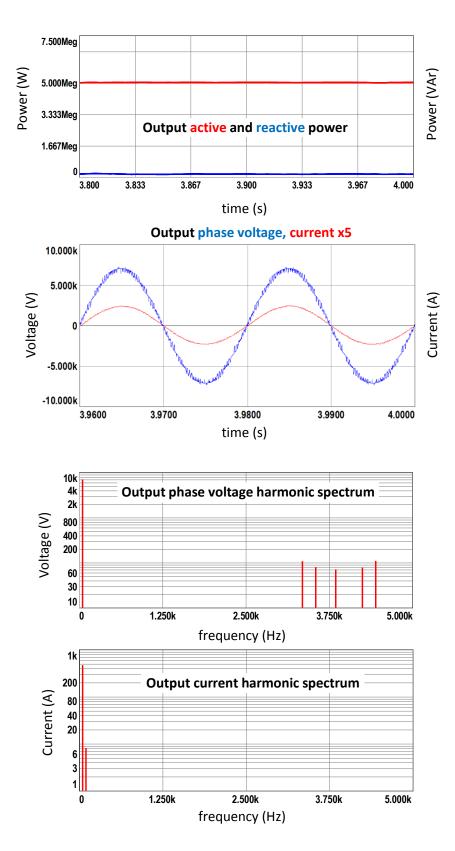

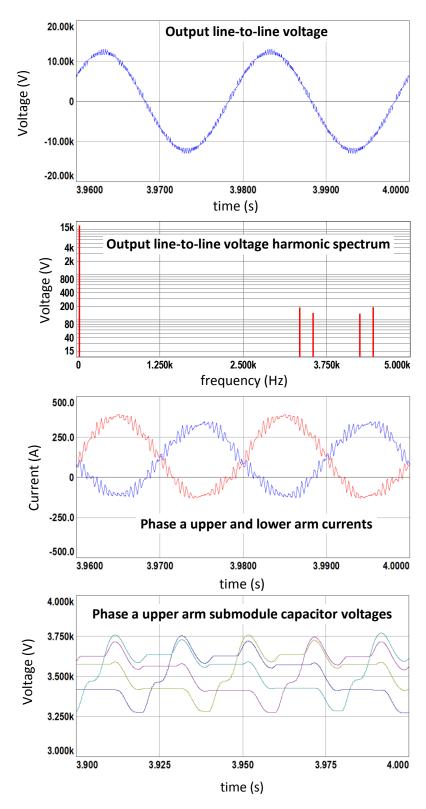

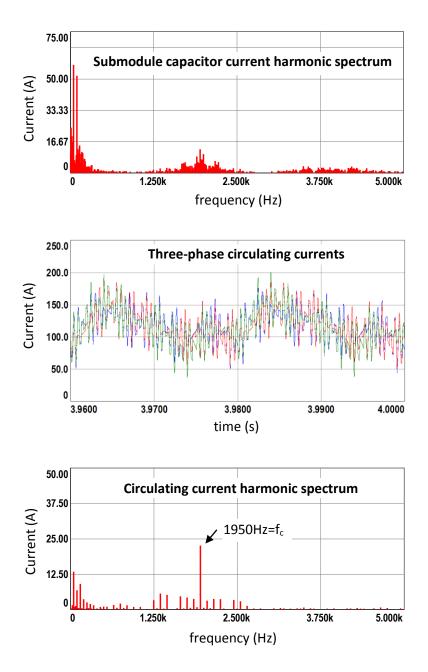

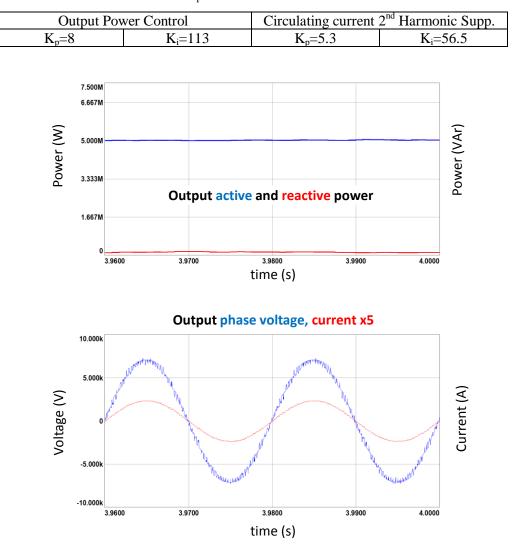

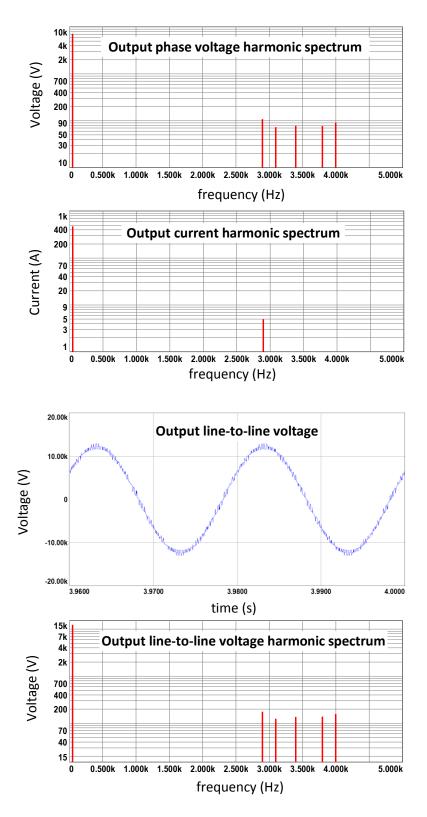

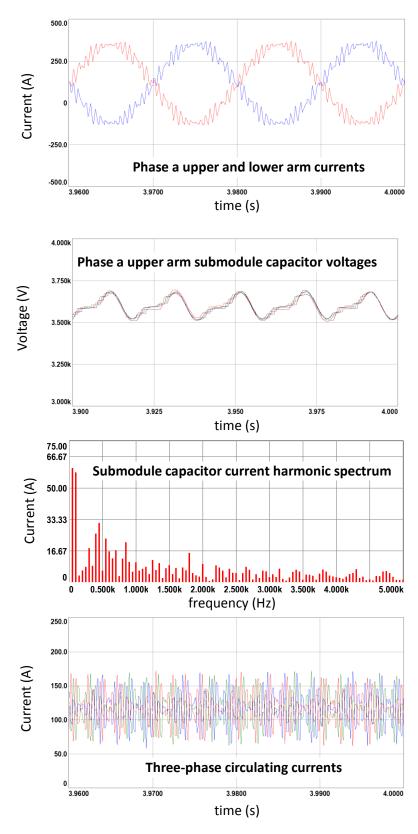

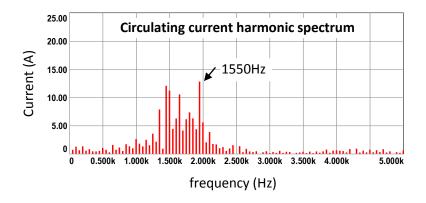

| Figure 7.2 Simulation results for S&S method with N+1 level $V_{ph}$ , full load 133            |

| Figure 7.3 Simulation results for S&S-RS method with N+1 level $V_{ph}$ , full load 137         |

| Figure 7.4 Simulation results for CR method with N+1 level $V_{ph}$ , full load 141             |

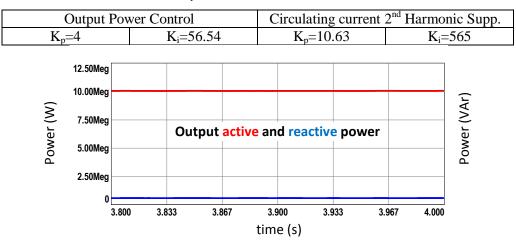

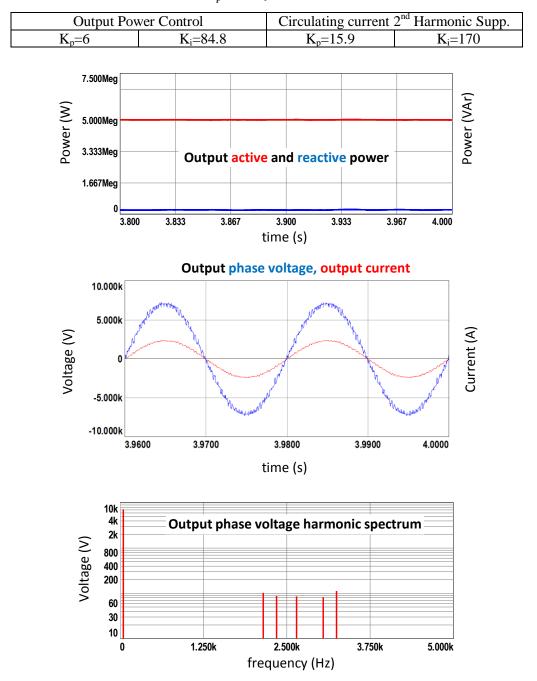

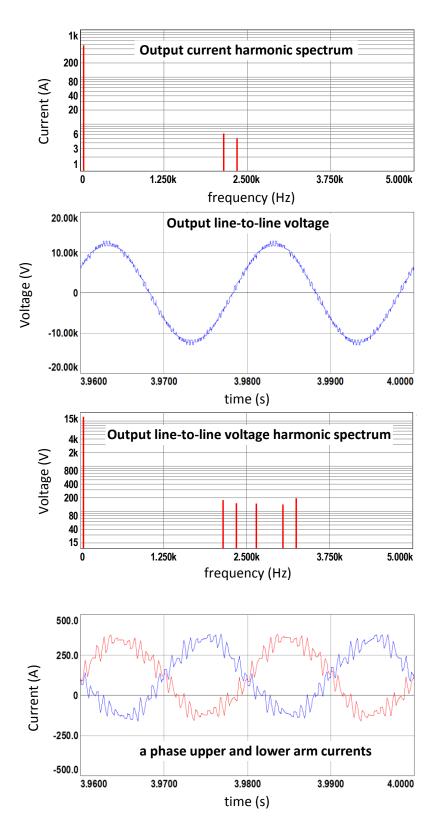

| Figure 7.5 Simulation results for PSCB method with N+1 level $V_{ph}$ , full load 145           |

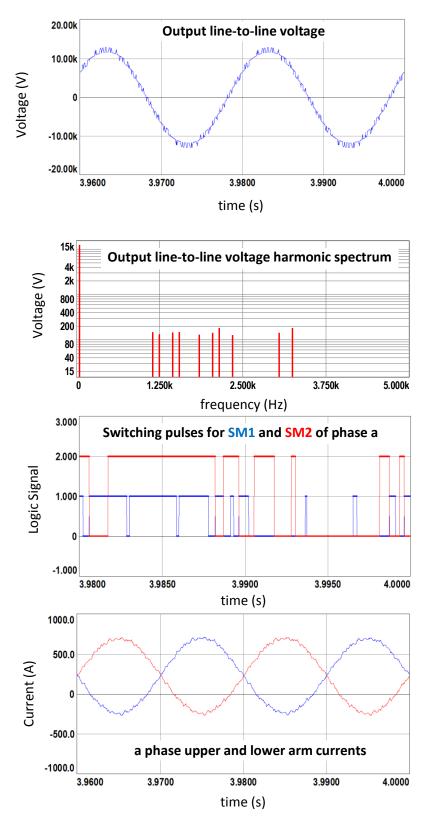

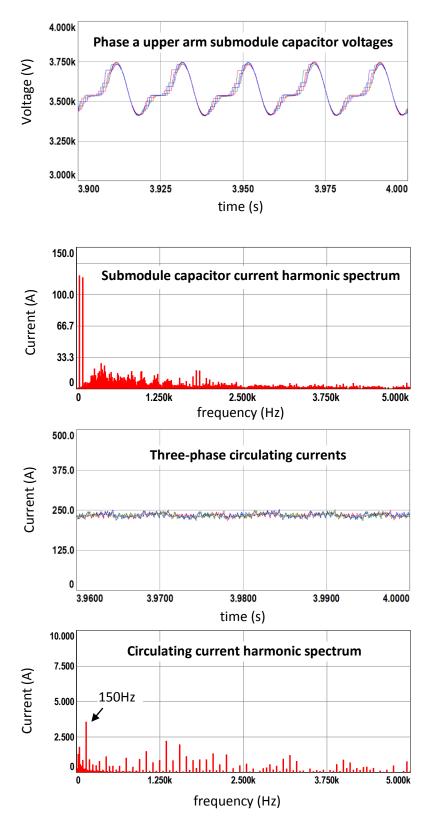

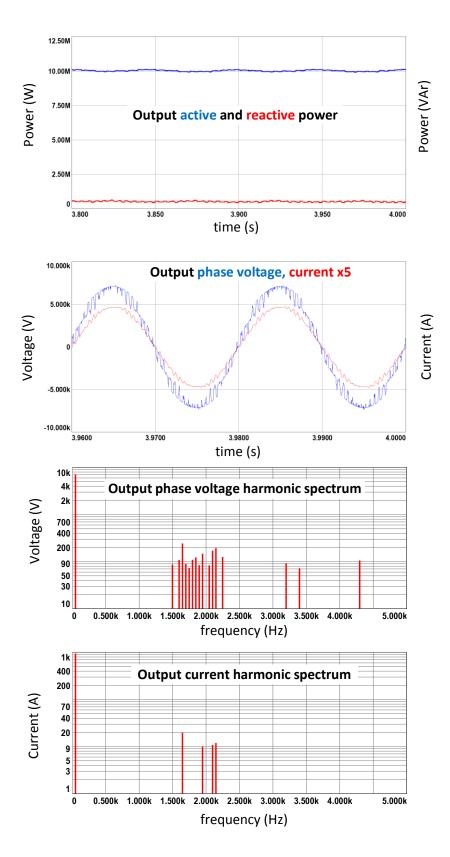

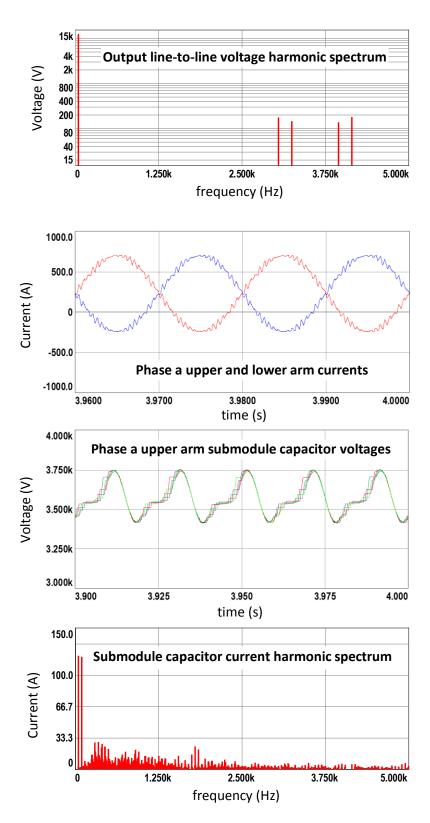

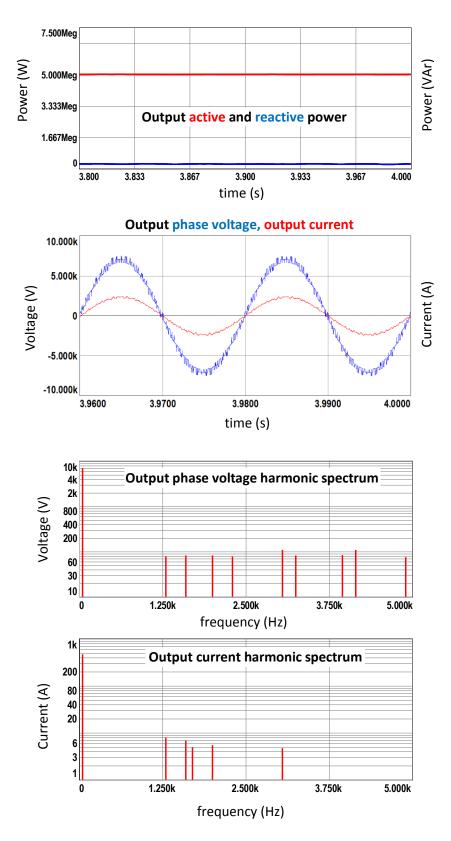

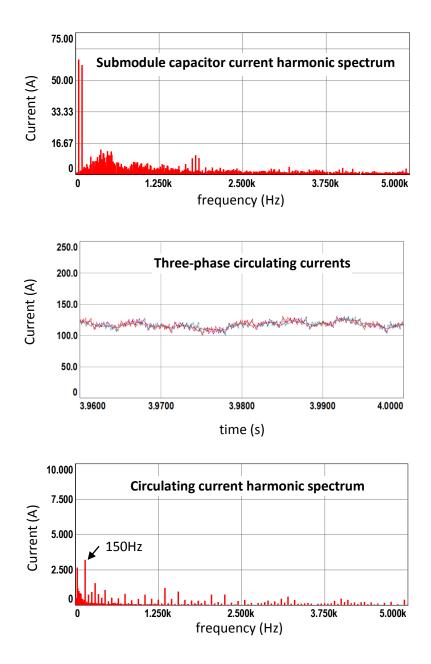

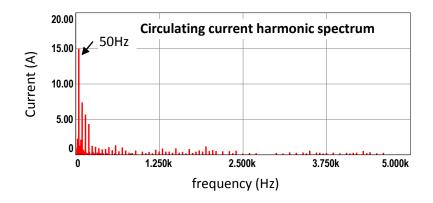

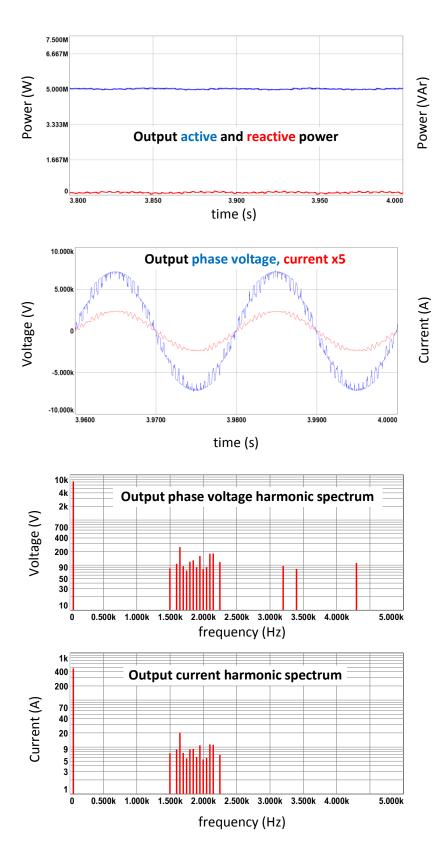

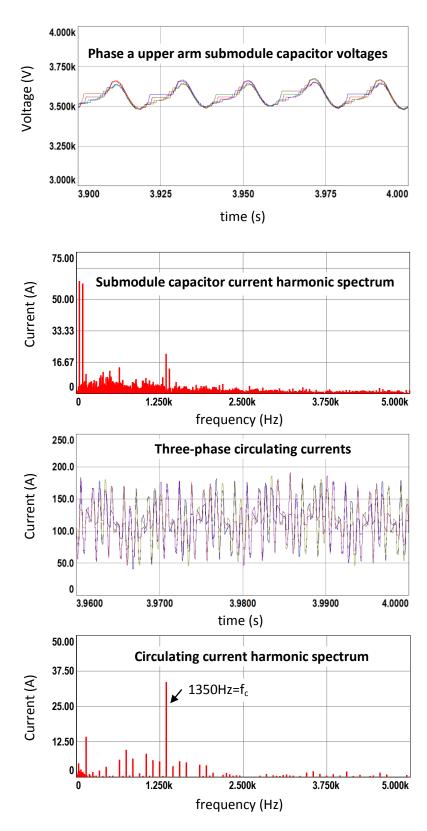

| Figure 7.6 Simulation results for S&S method with $2N+1$ level $V_{ph}$ , full load 150         |

| Figure 7.7 Simulation results for S&S-RS method with 2N+1 level $V_{ph}$ , full load 153        |

| Figure 7.8 Simulation results for CR method with $2N+1$ level $V_{ph}$ , full load 157          |

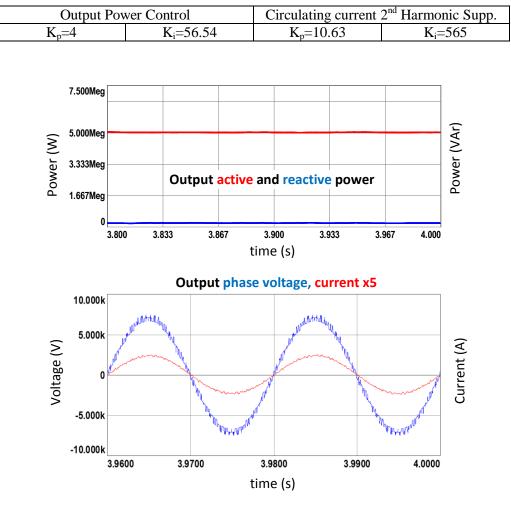

| Figure 7.9 Simulation results for PSCB method with $2N+1$ level V <sub>ph</sub> , full load 161 |

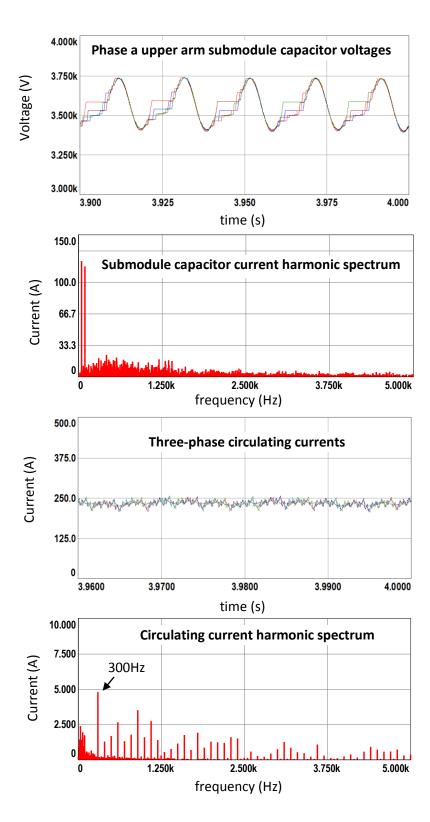

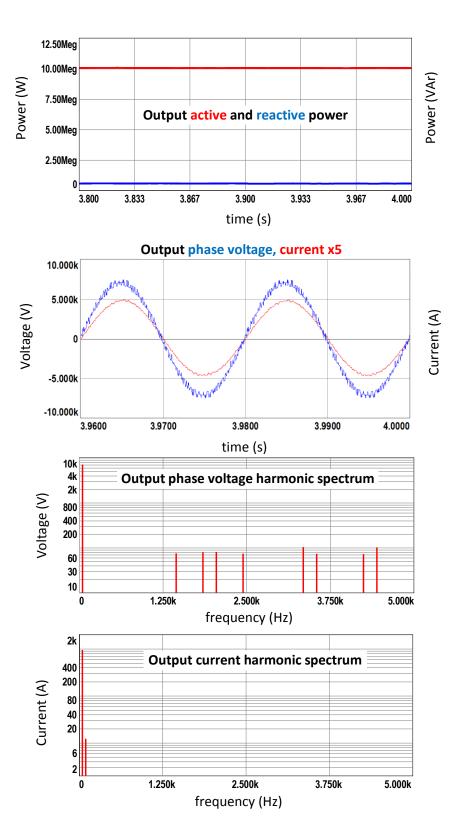

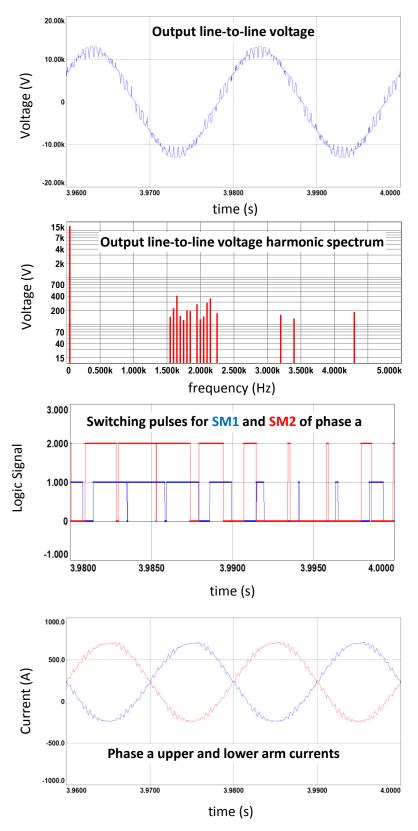

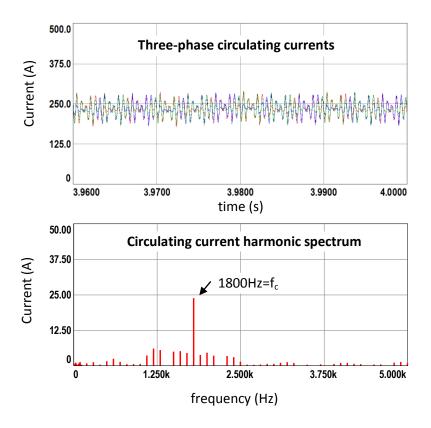

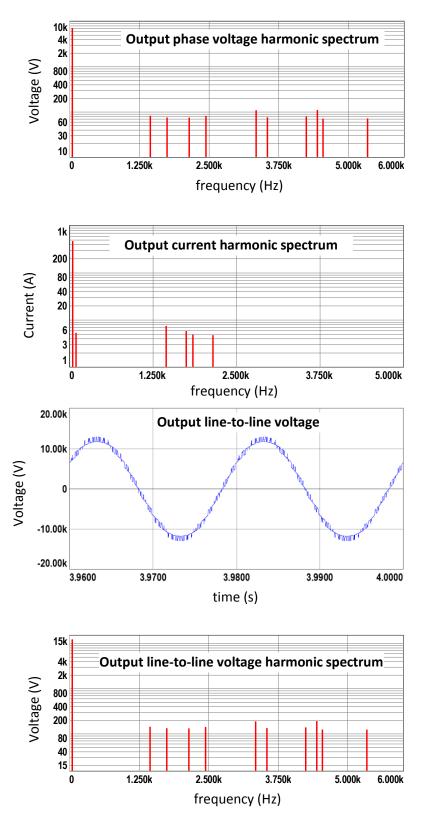

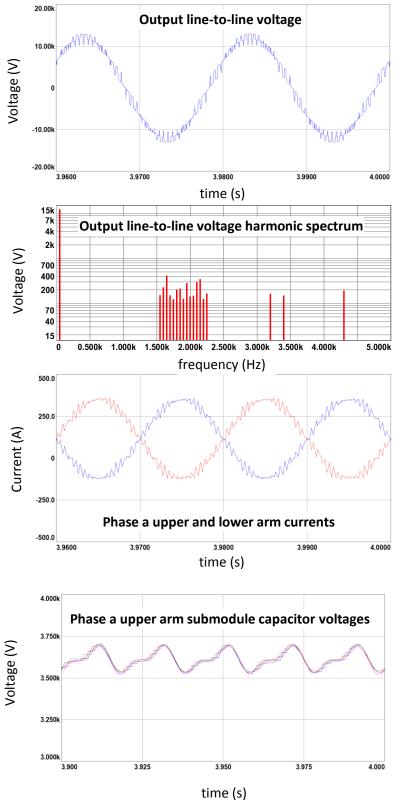

| Figure 7.10 Simulation results for S&S method with N+1 level $V_{ph}$ , half load 168           |

| Figure 7.11 Simulation results for S&S-RS method with N+1 level $V_{ph}$ , half load 172        |

| Figure 7.12 Simulation results for CR method with N+1 level $V_{ph}$ , half load 175            |

| Figure 7.13 Simulation results for PSCB method with N+1 level $V_{ph}$ , half load 179          |

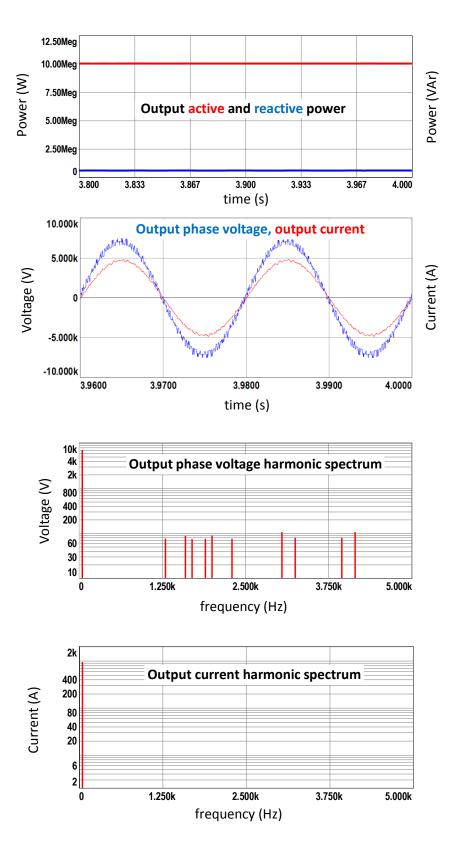

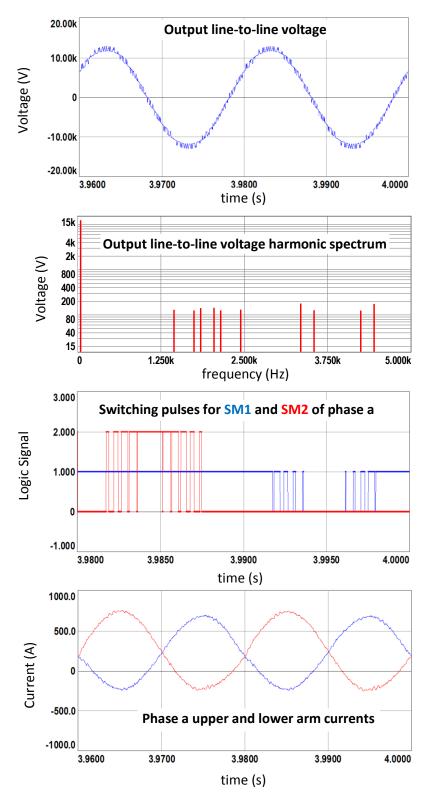

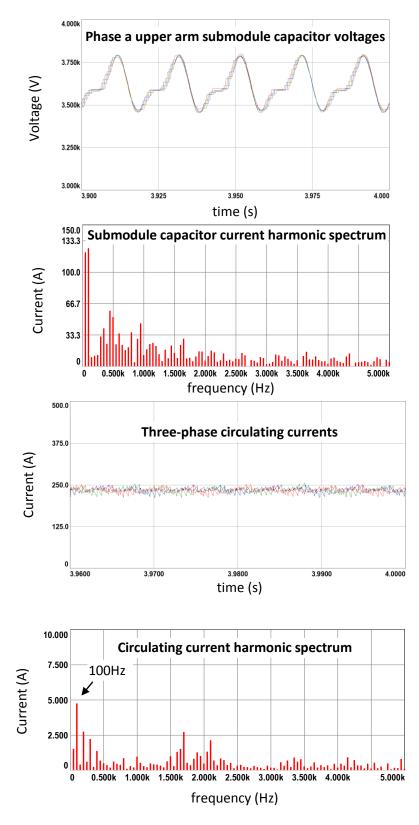

| Figure 7.14 Simulation results for S&S method with 2N+1 level $V_{ph}$ , half load 183          |

| Figure 7.15 Simulation results for S&S-RS method with N+1 level $V_{ph}$ , half load 186        |

| Figure 7.16 Simulation results for CR method with N+1 level $V_{ph}$ , half load 190            |

| Figure 7.17 Simulation results for PSCB method with N+1 level $V_{ph}$ , half load 193          |

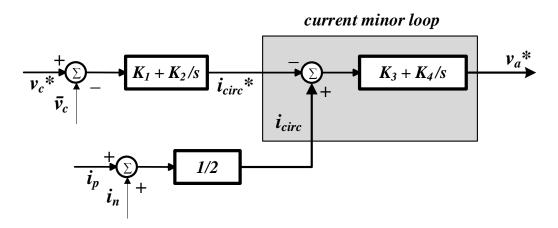

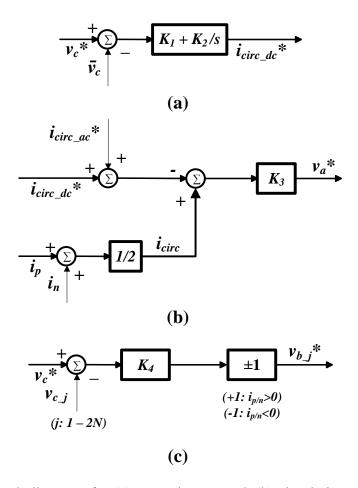

| Figure 8.1 Block diagrams for (a) averaging control, (b) circulating current control            |

| and (c) balancing control while low frequency operation of MMC 207                              |

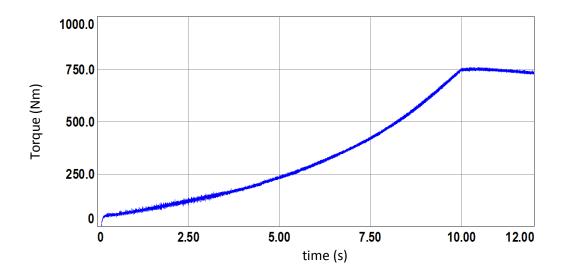

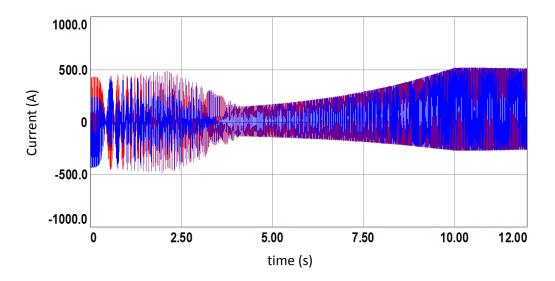

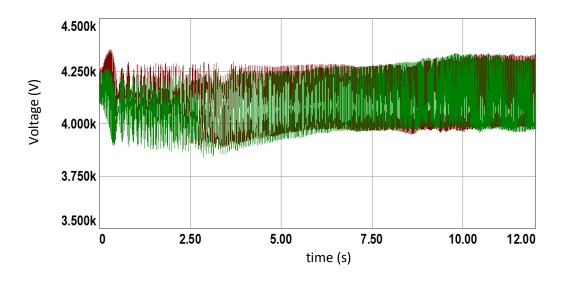

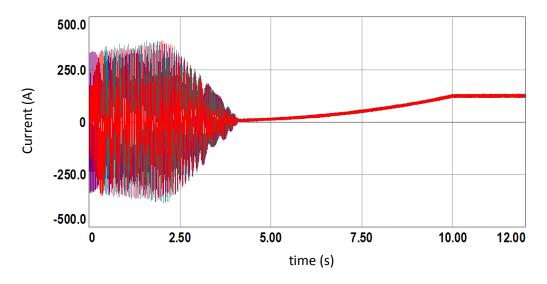

| Figure 8.2 Torque reference and output of the induction machine                                 |

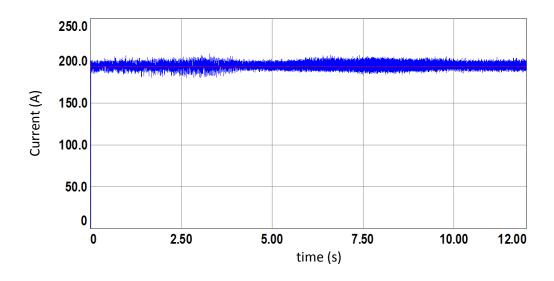

| Figure 8.3 Magnetizing current reference and field current of the induction machine             |

|                                                                                                 |

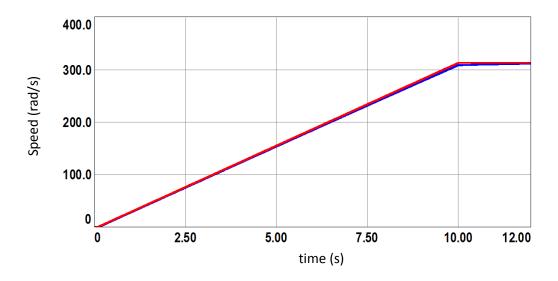

| Figure 8.4 Speed reference and speed of the induction machine                                   |

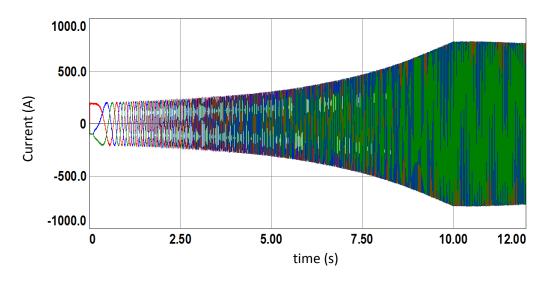

| Figure 8.5 Three-phase stator currents of the induction machine                                 |

| Figure 8.6 Phase a upper and lower arm currents of MMC motor drive        | 212        |

|---------------------------------------------------------------------------|------------|

| Figure 8.7 Phase a upper and lower arm capacitor voltages of MMC motor of | lrive.213  |

| Figure 8.8 Three-phase circulating currents of MMC motor drive            | 213        |

| Figure A.1 Linearization of forward voltage and bulk resistance of IGBT a | t left and |

| diode at right                                                            | 239        |

## LIST OF ABBREVIATIONS

| APOD    | Alternative Phase Opposition Disposition        |

|---------|-------------------------------------------------|

| CR      | Carrier Rotation                                |

| HVDC    | High-Voltage Direct Current                     |

| IGBT    | Insulated Gate Bipolar Transistor               |

| MMC     | Modular Multilevel Converter                    |

| PD      | Phase Disposition                               |

| POD     | Phase Opposition Disposition                    |

| PSC     | Phase-shifted Carriers                          |

| PWM     | Pulse-width Modulation                          |

| RMS     | Root Mean Square                                |

| S&S     | Sort and Select                                 |

| S&S-RS  | Sort and Select with Reduced Count of Switching |

| SM      | Submodule                                       |

| STATCOM | Static Synchronous Compensator                  |

| SVC     | Space Vector Control                            |

| SVPWM   | Space Vector Pulse-width Modulation             |

| THD     | Total Harmonic Distortion                       |

| VSC     | Voltage Source Converter                        |

#### **CHAPTER 1**

#### **INTRODUCTION**

### **1.1. Background and Motivation**

Energy is the most valuable and indispensable asset of countries from the very beginning of the human history. In the 20<sup>th</sup> century, electricity has become the dominant form of energy due to its ease of conversion to other forms. Today, the modern civilization based its operation on an increasing energy demand, substituting human activities with complex and sophisticated machines mainly run by electric power. Indeed, the world energy consumption is expected to increase by more than 54% every ten years [1]. Electricity will be more dominant than ever while supplying this energy demand since the countries try to bypass especially fossil fuels in the supply chain of energy. Therefore, it is obvious that the need of electricity will increase tremendously day after day. In order to meet the increasing demand, electric power generation, transmission, distribution and conversion become more and more important.

The recent attention in environmental protection and preservation has lead countries to shift to sustainable and renewable energy sources. Electric power generation from solar and wind energy is wide spread today. These resources will diffuse and occupy an increasingly important role in energy production in coming years. Therefore, the need of high quality electric power conversion systems to be used in this area is greater than ever. From the beginning of the 21<sup>st</sup> century, many countries have chosen to deregulate their electricity market. The situation resulted in a mix of energy sources while pursuing higher efficiency, particularly with the introduction of private investments in the energy market.

In the light of above mentioned events, in order to accomplish all requirements both from users and legal regulations, and to reduce the environmental impact, power conversion and control is needed to be reliable, safe, efficient, and available.

Voltage Source Converter (VSC) technology has been becoming common in many of modern demanding electric power systems, such as high-voltage direct current (HVDC) transmission systems (especially in offshore wind power transmission), medium-voltage motor drives, STATCOM applications, electric traction/propulsion systems or grid connected energy storage systems. Today, the majority of the applications of these electric power systems are driven by conventional two- or three-level VSC's. However, these conventional VSC's are not able to respond properly to emerging requirements such as high power, high efficiency, reliability of the system, and environmental compatibility. The solution to these problems has been evolved through the use of combinable, standardized, distributed, and simpler converter structures with lower voltage steps. Indeed, standardized and distributed systems have become the recommended solution to achieve modern projects requirements in all engineering areas. These configurations provide a more reliable operation, facilitates fault diagnosis, maintenance, and reconfigurations of control system. Especially in fail safe situations, distributed configuration allows control system to isolate the problem, drive the process in safe state easily, and in many cases allows continuing almost normal operation in faulty conditions.

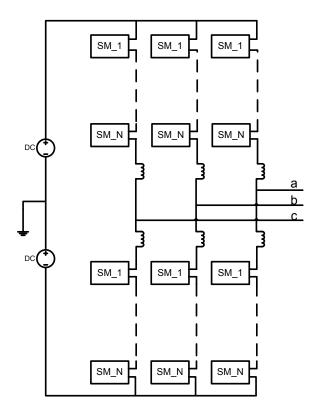

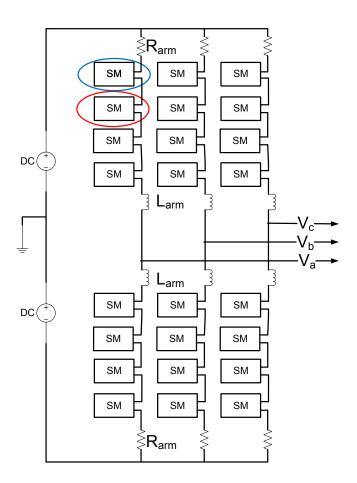

Multilevel converters have been progressed as significant competitors to the conventional VSCs in order to overcome the abovementioned limitations. At present, modular multilevel converter (MMC, MMLC, M2LC, M2C) (Figure 1.1) is at the heart of research and development studies in power electronics area, both for

academic and industrial scope. Its unique chopper cell based topological structure was firstly proposed by Lesnicar and Marquardt in 2003 [2]. The initial target was very high-voltage applications, especially network interties in power generation and transmission. Since then, the topology had a great attraction due to its promising features. Compared to conventional VSC technology, MMC offers advantages such as higher voltage and power levels, modular and redundant construction, longer maintenance intervals, improved reliability, and higher efficiency.

Figure 1.1 Modular multilevel converter

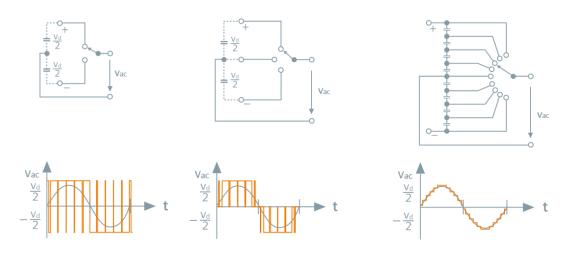

Synthesis of output voltage waveform in conventional two- or three-level VSCs is done by reflecting half of the dc-link voltage to the output, which results in high harmonic content and requirement for output harmonic filters which increase both the cost and footprint of the system. On the other hand, that of the MMC topology is based on the sum of small voltage steps reducing harmonic content, and removing the need of harmonic filter at the output. Output voltage synthesis concepts of two, three and multilevel converters are illustrated in Figure 1.2.

Figure 1.2 Output voltage synthesis concepts of two, three and multilevel converters [4]

#### 1.1.1. Typical Application Areas of MMC

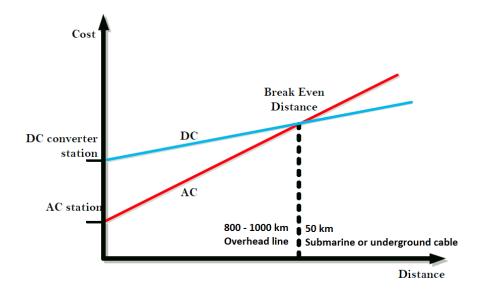

HVDC transmission is an important and efficient alternative to three-phase ac transmission of electric power over long distances. Advantages for choosing HVDC transmission instead of three-phase ac transmission can be numerous and should be considered in individual situation apart. However, the mostly acknowledged advantages could be summarized as follows: lower transmission losses, the capacity to transfer more power over the same right of way, the ability to interconnect systems that are not synchronized or using different frequencies, short-circuit currents limitation, long distance water crossing capability. One of the most important advantages of HVDC transmission accurately, while ac lines power flow cannot be controlled in the same direct way. Moreover, in [3] it is shown that the cost of HVDC transmission is less than ac transmission above a distance of 800km overhead line or 50km underground or submarine cables. This is due to the fact that the higher cost of HVDC converters is overcome by the cost of reduced number of

transmission line conductors. Figure 1.3 shows the cost estimations for ac and HVDC transmission by distance via overhead line and submarine or underground cable.

Figure 1.3 Cost estimations for ac and HVDC transmission by distance [3]

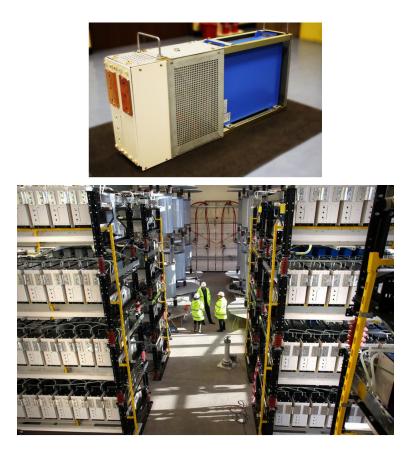

Today, HVDC technology has evolved from current source converters to voltage source converters, and even more to modular multilevel converters. Its smaller footprint due to smaller filter size or even no filter at the output, made the topology especially suitable for offshore wind farm HVDC transmission systems to the mainland. There are various commercial products with brand names "HVDC Plus" (Siemens) [4], "HVDC MaxSine" (H-bridge based, Alstom) [5] and "HVDC Light" (ABB) [6]. In Table 1.1, several HVDC projects based on MMC concept are shown. An offshore wind power station HVDC platform is shown in Figure 1.4 and a submodule and the MMC structure of MaxSine (Alstom) are shown in Figure 1.5.

| Project          | Installed | Manufacturer | Dc-link      | Power  | Location  |

|------------------|-----------|--------------|--------------|--------|-----------|

|                  | year      |              | voltage (kV) | (MW)   |           |

| Trans Bay Cable  | 2010      | Siemens      | ±200         | 400    | USA       |

| Caprivi Link     | 2010      | ABB          | 350          | 300    | Namibia-  |

| -                |           |              |              |        | Zambia    |

| Valhall          | 2011      | ABB          | 150          | 78     | Norway    |

| BorWin2          | 2013      | Siemens      | 300          | 800    | Germany   |

| HelWin1          | 2013      | Siemens      | 259          | 576    | Germany   |

| DolWin1          | 2013      | ABB          | ±320         | 800    | Germany   |

| East West        | 2013      | ABB          | ±200         | 500    | UK-       |

| Interconnector   |           |              |              |        | Ireland   |

| SylWin1          | 2014      | Siemens      | ±320         | 864    | Germany   |

| South-West Link  | 2014      | Alstom       | N/A          | 1440   | Sweden    |

| Mackinac         | 2014      | ABB          | ±71          | 200    | USA       |

| Skagerrak 4      | 2014      | ABB          | 500          | 700    | Norway-   |

|                  |           |              |              |        | Denmark   |

| BorWin1          | 2015      | ABB          | ±150         | 400    | Germany   |

| HelWin2          | 2015      | Siemens      | ±320         | 690    | Germany   |

| DolWin2          | 2015      | ABB          | ±320         | 900    | Germany   |

| INELFE           | 2015      | Siemens      | ±320         | 2x1000 | France-   |

|                  |           |              |              |        | Spain     |

| Aland            | 2015      | ABB          | $\pm 80$     | 100    | Finland   |

| Troll A 3-4      | 2015      | ABB          | ±60          | 2x50   | Norway    |

| Nordbalt         | 2015      | ABB          | ±300         | 700    | Sweden-   |

|                  |           |              |              |        | Lithuania |

| Tres Amigas      | 2016      | Alstom       | 345          | 750    | USA       |

| Superstation VSC |           |              |              |        |           |

| BorWin3          | 2019      | Siemens      | ±320         | 900    | Germany   |

Table 1.1 Several HVDC projects based on MMC concept [70], [71]

Figure 1.4 HelWin2 offshore HVDC platform by Siemens [8]

Figure 1.5 Submodule (up) and MMC (down) structure of MaxSine (Alstom) [7]

Medium-voltage motor drives are another application area of MMC. Many researchers and manufacturers are working on the issue. The medium-voltage drives cover power ratings from 250kW to more than 100MW at the medium-voltage (MV) level of 2.3 to 13.8kV. In this way, the majority of the installed MV drives are in the 1 to 4 MW range with voltage ratings from 3.3kV to 6.6kV [9]. One of the major markets for the MV drive is retrofit applications intended to improve the efficiency and achieve energy saving. It is reported that 97% of the currently installed MV motors operate at a fixed speed; only 3% of them being driven by variable speed drives [9]. For pump/blower like motors, fixed speed operation results in a substantial amount of energy loss because of mechanical methods used for control of fluid. It is reported in [10] that an MMC based motor drive for a converter-fed synchronous machine for pumped hydro storage plant with a power rating of 100MVA has been installed in Switzerland in 2013 by ABB (Figure 1.6). Currently, commercialization of MMC based motor drives is not as wide spread as in HVDC case. However, there is a big opportunity for MMC to penetrate into the variable frequency motor drive applications, since the need of efficiency improvement in this field, as explained above.

Figure 1.6 MMC based motor drive for a converter-fed synchronous machine by ABB and Oberhasli Hydroelectric Power Company in Switzerland [11]

As mentioned, STATCOM applications are one of the fields for MMC to penetrate in. In order to improve dynamic stability and power quality of power systems which have been deregulated and liberalized especially from the beginning of the 21<sup>st</sup> century, STATCOM applications are widely used. The MMC topology provides improved dynamic stability of transmission systems, increased power quality, flexibility to adapt to different power ratings, compact design with low footprint as well as redundancy and minimized engineering costs to STATCOM systems. Different manufacturers have MMC based STATCOM systems, some of which are SVC Plus (full-bridge based, Siemens) [72] and SVC Light (full-bridge based, ABB) [73]. In Table 1.2, several STATCOM projects based on MMC topology and in Figure 1.7 an example of projects are shown.

| Project                                | Installed<br>year | Manufactu<br>rer | System<br>voltage<br>(ac)(kV) | Power<br>(MVAr) | Location       |

|----------------------------------------|-------------------|------------------|-------------------------------|-----------------|----------------|

| Kikiwa                                 | 2009              | Siemens          | 220                           | 2x(±50)         | New<br>Zealand |

| The Thanet offshore wind farm          | 2009              | Siemens          | 11                            | N/A             | UK             |

| Mocuba                                 | 2010              | Siemens          | 33                            | N/A             | Mozambi<br>que |

| Cerro Navia                            | 2011              | ABB              | 220                           | +65/<br>-140    | Chile          |

| The Greater Gabbard offshore wind farm | 2011              | Siemens          | 13.9                          | N/A             | UK             |

Table 1.2 Several STATCOM projects based on MMC concept [74], [75]

Figure 1.7 Kikiwa STATCOM project based on MMC by Siemens [12]

### **1.2.** Scope of the Thesis

As explained in section 1.1, MMC was firstly proposed in 2003 and it is still in the development progress. Thus, it is a topical subject in academic and industrial research studies at present. From the advent of the topology, many studies have been carried out for the modulation, control, modeling, design and protection of the converter.

The framework of the thesis is selection of suitable carrier based PWM method and control technique for MMC topology used for used for grid-interface and electrical motor drives. The procedure also involves devising the optimal circuit parameters. Then, the design is verified by means of detailed computer simulations and computer based mathematical tool outputs with different PWM and control techniques. Several power ratings are considered to provide a thorough performance evaluation of the designed system.

The main objectives of this thesis are:

- i. Evaluation and discussion of MMC among other VSCs and multilevel converter topologies

- ii. Studying the basic operation principle of MMC topology

- iii. Evaluation and comparison of different carrier based PWM techniques of MMC

- iv. Analysis and comparison of different control strategies of MMC

- v. Design, simulation, and performance analysis of a grid connected MMC system

- vi. Design, simulation and performance analysis of an MMC based motor drive

Carrier based PWM techniques for MMC are widely studied [13]-[15]. There are several studies that consider carrier based PWM methods for MMC switching. One of the earliest studies [15], introduces LS PWM methods and compares their performances. Carrier based PWM methods comparisons for specific m<sub>a</sub> (amplitude modulation index) and m<sub>f</sub> (carrier to fundamental frequency ratio) values are given in [16] and [17]. Another work [13], also rates sinusoidal PWM methods, for specific m<sub>a</sub> and m<sub>f</sub> values in terms of harmonics performances. Variations in the output voltage levels are studied in [18]. However, still there is a need for a systematic analysis and comparison of different carrier based PWM methods. Switching pulse patterns, and output harmonics of methods should be analyzed with equal switching count per leg. In high power systems, which are the main application area for MMC, minimum switching losses are aimed. The energy cost lost for the switching or cooling system cost for the converter sums up to big amounts, because of the high power rating of the converter. Therefore, it is

important to evaluate the methods with equal switching count principle, keeping the switching losses low and similar to each other. The first main contribution of this thesis is to provide the fundamental characteristics of different carrier based PWM methods, level-shifted and phase-shifted carriers, used for MMC switching. Pulse pattern, switching manner and output harmonic content of PD, POD, APOD and phase-shift methods are investigated under equal total count of switching in a phase leg principle, throughout broad  $m_a$  and  $m_f$  ranges. Also, principles of switching methods for N+1 and 2N+1 phase-to-neutral output voltage levels are explained.

Control of MMC with different control approaches are studied in [19]-[24]. Output power control, circulating current control and submodule capacitor voltage balancing techniques are explained. However, there is no general agreement about the suitability of the characteristics and comparison of different control strategies. Systematizing the analysis and evaluation of control and modulation strategies for MMCs are still need to be studied. The second main contribution of the thesis is to provide the performance comparisons of different MMC control techniques with N+1 and 2N+1 phase voltage levels, in terms of output harmonic content, submodule capacitor voltage ripple and circulating current ac component for a grid connected system under different loading conditions.

Motor drive with MMC is intensively studied at present. Being relatively a developing area compared to HVDC and STATCOM, motor drives, especially the low frequency region where MMC is problematic, are the topical subject for MMC studies [10], [25]-[31]. In this thesis, a motor drive application with MMC is considered. Low frequency operation of the converter is covered with a multi MW electrical machine. From the start-up, low frequency operation of the machine as well as steady state high frequency operation with a fan/blower like load is presented and characteristics of the converter such as submodule capacitor voltages, circulating current and arm currents under these circumstances are given.

This thesis consists of nine chapters.

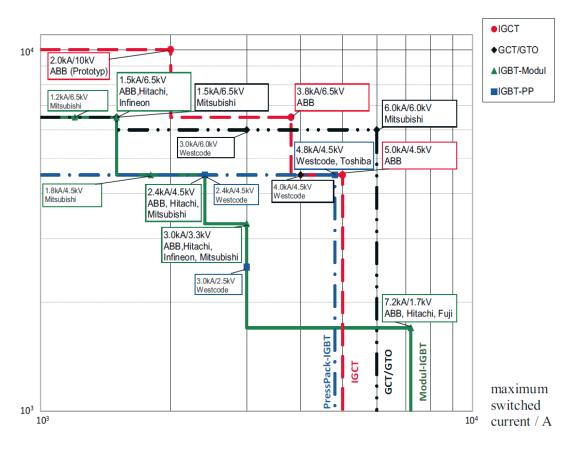

Chapter 2 gives the classification of multilevel converters. Diode-clamped, capacitor clamped and submodule based (cascaded H-bridge and MMC) multilevel converters are considered. Submodule structures, specifically full-bridge and chopper cell, are detailed. Characteristics, topological features, and switching of these converters are covered. Advantages and disadvantages of different topologies are listed. Additionally, the power semiconductors used in multilevel converters are explained. Thyristor, IGBT and IGCTs are considered and their characteristics are provided.

Chapter 3 gives the mathematical model and circuit analysis of MMC. Topological structure of the converter is provided in detail. Upper/lower arm and phase leg quantities, current and voltage loops, energy and power equations of the converter are analyzed. State variables for the control of the converter are detected.

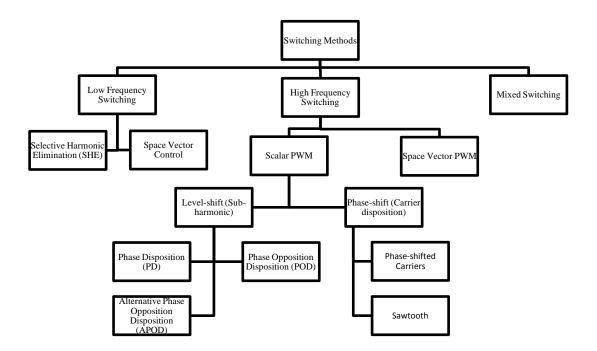

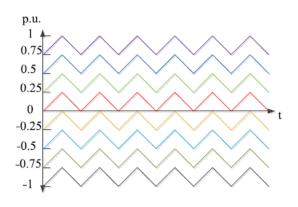

Chapter 4 provides a comprehensive explanation of switching methods for MMC. Low frequency and high frequency switching methods are classified. Application and characteristics of these methods are provided and carrier based PWM methods analyzed deeply. Level-shift and phase-shift methods are detailed. Switching pulse patterns, resultant output voltage waveforms and their harmonic contents are analyzed, throughout broad  $m_a$  and  $m_f$  values. Moreover, the branching in the application of carrier based PWM methods to the converter which results in N+1 or 2N+1 phase-to-neutral voltage levels at the output is shown.

Chapter 5 discusses the component rating determination of MMC. Number of submodules per arm, submodule capacitor and arm inductor values are the fundamental design issues of MMC. Right choice of these values is critically important in the waveform quality, efficiency and initial cost of the converter. The determination processes are covered mathematically.

In chapter 6, control of MMC with carrier based PWM methods is considered. The fundamental control targets of the converter, output power control, submodule capacitor voltage balancing control, and circulating current ac component suppression control, are introduced. The mostly acknowledged control approaches in the literature, direct modulation and phase-shifted carrier based control, are detailed. Application of the control methods and determination of control parameters are given.

Chapter 7 merges the content studied in the previous chapters and uses them as background and input to the analyses conducted herein. In this chapter, a grid connected MMC is designed and simulated. For the dc/ac conversion step of a 10MW HVDC system, MMC component ratings are determined and the converter is run by different control and carrier based PWM methods for different loading conditions. Comparisons of different control and modulation methods are done in terms of output harmonics performance, submodule capacitor voltage ripple, circulating current ac component, and efficiency with equal switching count per phase leg principle. By this way, the suitable control and modulation method for the mentioned criteria are discovered.

In chapter 8, motor drive application of MMC is explained. The problems of the topology in motor drive applications are clarified. The solution methods to these problems found in the literature are provided and one of them is verified via a 9.1MW induction machine simulation from the start up to the full speed range.

Finally, the thesis concludes with a summary of information and experience gained throughout the study. Developments and future work are also addressed.

## **CHAPTER 2**

#### MULTILEVEL CONVERTER TOPOLOGIES

## 2.1. Introduction

The concept of multilevel converters goes back to the mid 1970s. Baker and Bannister gave the very first examples of the multilevel topology [34]. The topology was achieved by connecting single-phase inverters in series. Separate dc sources were used to build up multilevel voltage at the output.

In conventional two-level voltage source converters, the converter simply connects the positive or negative dc-link voltage to the output; and in three-level converters, an additional neutral voltage is seen at the output. Therefore the signal created on the ac side of two- or three-level converters is a series of pulses containing the required fundamental frequency and higher harmonic signals, which can be removed by appropriate filters. Multilevel converters, on the other hand, synthesize smaller voltage steps in a sinusoidal manner at the ac output terminals which are obtained either from capacitors or separate dc sources. As the number of voltage levels increase at the ac side, generated voltage waveform is much like a sinusoid. Therefore, output voltage harmonic distortion of the multilevel converters is much less than two- or three-level converters, which is the principal advantage of multilevel converters over two- or three-level converters. Other advantages of multilevel converters can be listed as below: - Multilevel converters, especially submodule based ones, are easily expandable to broad power and voltage levels, by simply increasing the series connected submodule number.

- Due to stepped output waveform, voltage change speed, namely dv/dt rate, is reduced, also reducing electromagnetic compatibility problems.

- Multilevel converters can be switched at lower frequencies (even at fundamental frequency). Thus, switching losses per switching device decrease and semiconductor thermal management can be handled easier.

- Input current distortion and output common-mode voltage of multilevel converters are lower compared two-level converters.

- Multilevel converters are relatively independent from the fast changing state of the art of semiconductor devices. They can be made up using standard and proven semiconductor devices.

- In conventional two-level converters, a number of semiconductors should be serially connected and operated simultaneously. A delay of operation among one of them results in a failure. However, in multilevel converters, the voltage ratings of semiconductors are limited by the voltage level step size, enabling single semiconductor usage. Therefore, failure rates of multilevel converters are lower.

On the other hand, the two basic disadvantages of multilevel converters are listed as below:

- Multilevel converters consist of a greater number of semiconductors and circuit elements, increasing their initial cost.

- Switching and control of multilevel converters are more difficult than two-level converters because of their complex topological structures.

#### 2.2. Classification of Conventional Multilevel Converter Topologies

#### 2.2.1. Diode-Clamped (Neutral-point-clamped) Multilevel Converter

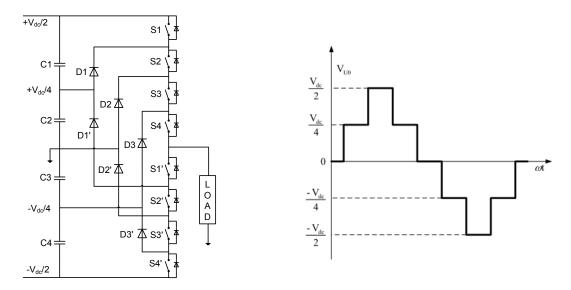

Diode-clamped multilevel converter was proposed by Nabae, Takahashi, and Akagi in 1981 [35]. Several papers had been published in the 1990s covering four-, five- or six-level diode-clamped multilevel converters for static VAR compensation, variable speed motor drives, and high-voltage system interconnections. A phase leg of five level diode-clamped converter and its output voltage waveform are shown in Figure 2.1. Each of the phases shares a common dc-link, which is subdivided into five levels,  $-V_{dc}/2$ ,  $-V_{dc}/4$ , 0,  $V_{dc}/4$  and  $V_{dc}/2$ , by four capacitors. All the capacitors are charged to  $V_{dc}/4$  and the voltage stress across the switching devices is limited to  $V_{dc}/4$  through the clamping diodes. However, the clamping diodes need to block different voltage levels; D1 and D3' being  $V_{dc}/4$ , D1' and D3 being  $3V_{dc}/4$ , D2 and D2' being  $V_{dc}/2$ . Table 2.1 shows the required switch states for the desired output voltage of the five-level converter, "1" corresponding to the switch is "ON" and "0" to "OFF".

The diode-clamped multilevel converter has 2N-1 voltage levels line-to-line if used as three-phase converter, where N being the number of per phase-to-neutral voltage levels. Therefore, a single-phase five-level converter as in Figure 2.1 has nine voltage levels line-to-line when used as three-phase.

The diode-clamped multilevel converter was initially built up in order to expand the power ratings of converters to megawatt ranges other than paralleling or series connecting the power semiconductors. Today, the converter is utilized in many few kilowatts to megawatt applications, including general purpose adjustable speed drives. However, the converter has the drawback of increasing complexity of control and capacitor voltage balancing problems as the number of voltage levels increase.

Figure 2.1 Single-phase five-level diode-clamped converter at left and output voltage waveform at right

| Output Voltage       | S1 | S2 | <b>S</b> 3 | S4 | S1' | S2' | S3' | S4' |

|----------------------|----|----|------------|----|-----|-----|-----|-----|

| $V_{dc}/2$           | 1  | 1  | 1          | 1  | 0   | 0   | 0   | 0   |

| $V_{dc}/4$           | 0  | 1  | 1          | 1  | 1   | 0   | 0   | 0   |

| 0                    | 0  | 0  | 1          | 1  | 1   | 1   | 0   | 0   |

| - V <sub>dc</sub> /2 | 0  | 0  | 0          | 1  | 1   | 1   | 1   | 0   |

| - V <sub>dc</sub> /4 | 0  | 0  | 0          | 0  | 1   | 1   | 1   | 1   |

Table 2.1 Switch states for the desired output voltage of the five level converter

## 2.2.2. Flying Capacitor (Capacitor-Clamped) Multilevel Converter

Flying capacitor multilevel converter was proposed by Meynard and Foch in 1992 [36]. The topology is similar to diode-clamped converter except for clamping diodes, whereas in flying capacitor topology, capacitors are used for clamping purpose. A phase leg of five level flying capacitor converter and its output voltage waveform are shown in Figure 2.2. Each of the phases shares a common dc-link, which is subdivided into five levels,  $-V_{dc}/2$ ,  $-V_{dc}/4$ , 0,  $V_{dc}/4$  and  $V_{dc}/2$ , by four capacitors. The required number of dc-link capacitors for N level converter is N-1 and auxiliary capacitors is (N-1) x (N-2) / 2. Table 2.2 shows the required switch

states for the desired output voltage of the five-level converter, again "1" corresponding to the switch is "ON" and "0" to "OFF".

The topology has the advantage of phase redundancy for inner voltage levels; in other words, a desired output voltage may be obtained by two or more switching combinations. This feature can be exploited appropriately for capacitor voltage balancing issue. However, as the number of voltage levels increase, again control of the converter and capacitor voltage balancing become highly complicated. Also the number of required capacitors increases dramatically, resulting in increase of cost, and also packaging and dimension problems of the converter. The topology is mainly employed for utility power electronics applications [93]-[94].

Figure 2.2 Single-phase five level flying capacitor converter at left and output voltage waveform at right

| Output Voltage       | <b>S</b> 1 | <b>S</b> 2 | <b>S</b> 3 | <b>S</b> 4 | S1' | S2' | S3' | S4' |

|----------------------|------------|------------|------------|------------|-----|-----|-----|-----|

| $V_{dc}/2$           | 1          | 1          | 1          | 1          | 0   | 0   | 0   | 0   |

| $V_{dc}/4$           | 1          | 1          | 1          | 0          | 1   | 0   | 0   | 0   |

| 0                    | 1          | 1          | 0          | 0          | 1   | 1   | 0   | 0   |

| - V <sub>dc</sub> /2 | 1          | 0          | 0          | 0          | 1   | 1   | 1   | 0   |

| - V <sub>dc</sub> /4 | 0          | 0          | 0          | 0          | 1   | 1   | 1   | 1   |

Table 2.2 Switch states for the desired output voltage of the five-level converter

# 2.3. Submodule Based Multilevel Converters (Modular Multilevel Cascade Converters)

Apart from conventional multilevel converter topologies explained in the previous chapter, the most attractive topology for the researchers have been the submodule based multilevel converters which are also called as modular multilevel cascade converters.

Submodule based multilevel converters have three degrees of freedom in their circuit topology: one is connection of submodules to each other, being either star or delta connection. The second is the circuit topology of the submodules, being half-bridge (chopper cell) or full-bridge (H-bridge). Moreover, from the point of usage of delta connected or star connected clusters (serially connected submodules) as a single cluster or dual clusters, the third degree of freedom is obtained in terms of converter topology. As a result, theoretically  $2^3$ =8 different converter topologies are present for submodule based multilevel converters. However, not all of them are practically implementable. Table 2.3 shows all the possible variations by a tick corresponding to an implementable topology or by a cross corresponding to an irrelevant topology [37].

|             | St           | ar           | Delta        |        |  |  |

|-------------|--------------|--------------|--------------|--------|--|--|

|             | Single       | Double       | Single       | Double |  |  |

| Chopper     | Х            | $\checkmark$ | Х            | Х      |  |  |

| Full-bridge | $\checkmark$ | $\checkmark$ | $\checkmark$ | Х      |  |  |

Table 2.3 Submodule based multilevel converter topology variations

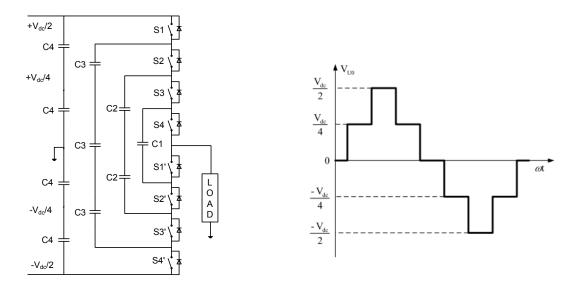

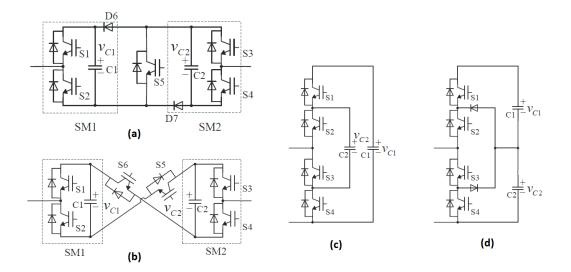

The four practically implementable submodule based multilevel converter topologies are listed as below and illustrated in Figure 2.3 and Figure 2.4 [38]:

- i. Single-Star Bridge-Cells (SSBC)

- ii. Single-Delta Bridge-Cells (SDBC)

- iii. Double-Star Chopper-Cells (DSCC)

- iv. Double-Star Bridge-Cells (DSBC)

Figure 2.3 (a) SSBC (b) SDBC

Figure 2.4 Possible circuit configurations of DSCC and DSBC (a) Power circuit using coupled arm inductors (b) Power circuit using non-coupled arm inductors (c) Chopper cell (DSCC) (d) Bridge cell (DSBC)

Irrelevance of the other four topologies could be explained as follows: As Figure 2.3 (b), SDBC topology, is investigated, it is realized that "double-delta" structure is irrelevant since in delta connection, there is no common neutral point as in star connection. Therefore, a double-delta structure is actually equivalent to two separate parallel connected single-delta structure. In case of single-star or single-delta structures, in order to generate ac voltage at the output, bridge cell usage is a must. With chopper cells, it is not possible to generate ac voltage at the output. As a result, "single-star chopper cells" or "single-delta chopper cells" could not be used practically. Consequently, four of submodule based multilevel topologies among eight theoretical combinations are practically not implementable.

In the literature, above mentioned four practical topologies are termed as "modular multilevel cascade converter" in general [38]. More specifically, these topologies can be classified as either being "cascaded H-bridges" or "modular multilevel converter". Some researchers give the name "modular multilevel converter" to both chopper cell and bridge-cell based double-star configured multilevel converters, while some others refer only the chopper cell based DSCC structure. In this thesis hereafter, bridge-cell based topologies, namely SSBC, SDBC and DSBC, will be referred as cascaded H-bridges; while chopper cell based structure, DSCC, will be referred as modular multilevel converter (MMC). The common features of all these four topologies are the serial connection of submodules, either being chopper cell or bridge cell, and the serially connected inductor (arm inductor) to these submodules. For the double-star case, the arm inductor may be a single coupled inductor for both of the phase arms or two separate inductors for each of the arms. In the former case, the size and weight of the inductor is less than the total of two uncoupled inductors. Topological characteristics of cascaded H-bridges and modular multilevel converters are explained in the next sections.

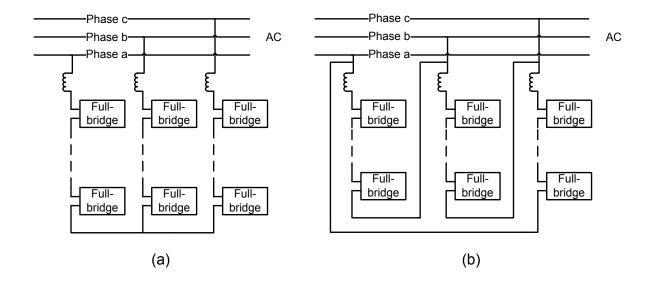

#### 2.3.1. Cascaded H-Bridges

Cascaded H-bridges topology can be implemented with three different structures as explained in previous chapter, SSBC, SDBC and DSBC. SSBC and SDBC topologies do not have a common dc-link as in the case of DSBC. Thus, in case there exists a single dc-link (energy source) in the system, it is not possible to use SSBC and SDBC structures for applications in which active power transfer should be done from dc-link to the output, or in inverse direction such as motor drives. In these cases, separate isolated dc sources connected parallel to the bridge capacitors are required to use the SSBC and SDBC topologies. However, providing separate isolated dc sources for each submodule requires heavy and bulky transformers which also increase the cost of the converter. DSBC structure, on the other hand, can be connected to a single dc-link from the neutral points of the star connection. It can be used in motor drive and HVDC applications practically.

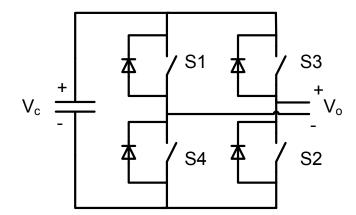

The full-bridge circuit, seen in Figure 2.5, can generate three different output voltages,  $+V_c$ , 0 and  $-V_c$ , where  $V_c$  is the submodule capacitor voltage. Switch states corresponding to these output voltages are listed in Table 2.4. The ac outputs of each of the different full-bridge inverters are connected in series such that the synthesized voltage waveform is the sum of full-bridges' outputs. Serial addition of one full-bridge results in an increase of two in the number of output voltage levels.

Figure 2.5 The full-bridge circuit topology

| <b>S</b> <sub>1</sub> | $S_2$ | <b>S</b> <sub>3</sub> | S <sub>4</sub> | Vo  |

|-----------------------|-------|-----------------------|----------------|-----|

| 1                     | 1     | 0                     | 0              | Vc  |

| 0                     | 0     | 1                     | 1              | -Vc |

| 1                     | 0     | 1                     | 0              | 0   |

| 0                     | 1     | 0                     | 1              | 0   |

Table 2.4 Full-bridge circuit switching states

SSBC and SDBC topologies are mainly considered for STATCOM and battery energy storage systems. DSBC topology can be used as motor drive for fans/blowers. Also, since it is able to tolerate a broad range of variations in the dclink voltage due to its buck and boost functions, it is applicable to wind/solar power systems where dc-link voltage varies with wind and weather conditions [38].

The cascaded H-bridge topology is attractive in terms of doubling output voltage level for the same number of submodules per phase, compared to the counterpart with chopper cells. Also, in case separate dc sources are used in submodules, there is no need for submodule capacitor voltage balancing, resulting in easier of control of the converter. However, separate dc source requirement of the topology itself is the major drawback in terms of size, weight, and cost, since each separate dc sources are obtained generally by a transformer and active front end combination.

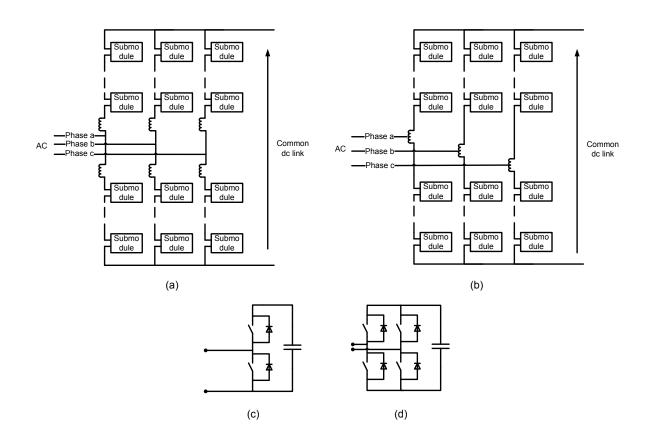

## 2.3.2. Modular Multilevel Converter

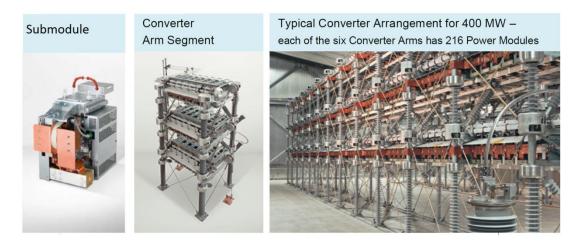

Modular multilevel converter (MMC) topology was firstly proposed by Lesnicar and Marquardt in 2003 [2]. Since then many researchers have investigated this topology and it has become the most attractive topology among the multilevel converters especially for high power applications. Voltage source converter high-voltage direct current (VSC-HVDC) transmission systems, medium-voltage motor drives, STATCOM applications, and renewable energy interconnection systems to the grid are the typical application areas of MMC. An example "submodule", "arm" and typical converter arrangement of MMC are illustrated in Figure 2.6, while the terms are detailed in the next paragraph.

Figure 2.6 Submodule, arm and typical converter arrangement illustrations of MMC by Siemens [39]

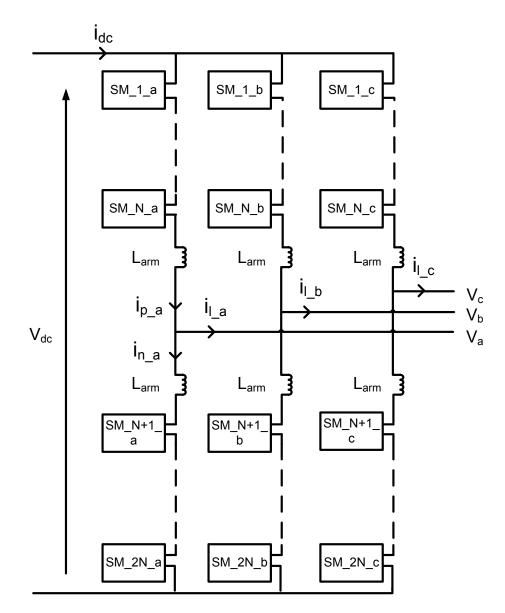

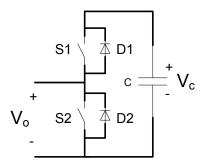

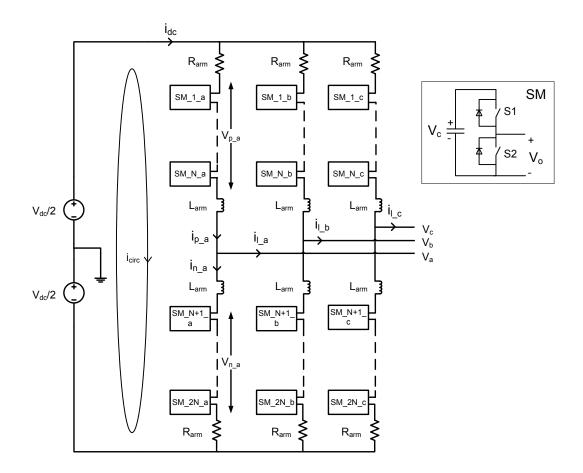

Among submodule based multilevel converters, DSCC topology is acknowledged as MMC in this thesis, as explained in section 2.3. Circuit topology of a three-phase MMC is shown in Figure 2.7. All the phases share the common dc-link. The converter is comprised of three "phase legs", while each phase leg is comprised of "upper phase arm" and "lower phase arm". Each phase arm contains N (nominally) identical, cascade connected submodules and an arm inductor,  $L_{arm}$ . The arm inductor filters the high frequency component in arm current, limits the fault current and controls the circulating current as will be explained in chapter 4. The submodules produce the required ac phase voltage. Ac side terminals of the converter branch out between the two inductors of upper and lower arms. The submodule topology, being half-bridge circuit as shown in Figure 2.8, is composed of only two switches in cascade and a submodule capacitor paralleled to the switches. This simple and efficient structure allows the half-bridge circuit to dominate the others as the common submodule structure.

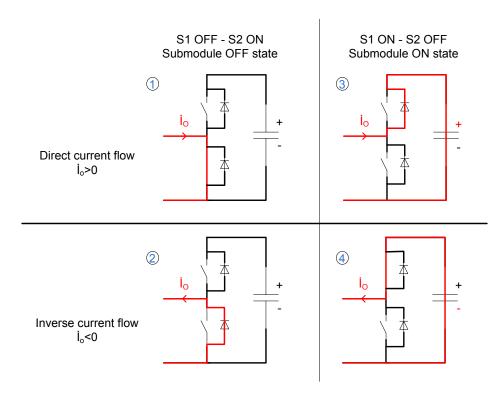

At any time, only one of the switches of half-bridge circuit should be ON. If S1 is ON and S2 is OFF, then the half-bridge circuit is "switched on" or "inserted to the current path". Else if S2 is OFF and S2 is ON, then the half-bridge circuit is "switched off" or "bypassed". The terminal voltage of half-bridge circuit is equal to the voltage across the submodule capacitor,  $V_c$ , if switched on/inserted; or zero, if switched off/bypassed. If both of the switches are ON, then the submodule capacitor is short-circuited. If both of the switches are OFF, terminal voltage of the submodule is undetermined and according to the direction of the current, different voltages may occur at the terminals. Depending on the states of half-bridge circuit and the direction of submodule current, submodule capacitor is either charged or discharged. All above mentioned switching combinations, terminal voltage of the half-bridge and capacitor charge/discharge conditions are illustrated in Figure 2.9 and Table 2.5.

Figure 2.7 Circuit topology of modular multilevel converter

Figure 2.8 Half-bridge (chopper) circuit

Figure 2.9 States of half-bridge (chopper) circuit and current paths

| State number in<br>Figure 2.9 | $S_2$ | $S_1$ | Vo             | Current<br>direction | Current<br>path | Capacitor<br>charge |

|-------------------------------|-------|-------|----------------|----------------------|-----------------|---------------------|

| 1                             | 1     | 0     | 0              | i <sub>o</sub> >0    | $S_2$           | -                   |

| 2                             | 1     | 0     | 0              | i <sub>o</sub> <0    | $D_2$           | -                   |

| 3                             | 0     | 1     | V <sub>c</sub> | i <sub>o</sub> >0    | $D_1$           | Charge              |

| 4                             | 0     | 1     | V <sub>c</sub> | i <sub>o</sub> <0    | $S_1$           | Discharge           |

Table 2.5 Half-bridge circuit switching states

In an MMC, the energy of the dc-link is not stored in a single large capacitor, as in the case of conventional VSCs, but it is distributed among the submodule capacitors. There are 6N capacitors in the converter and energy values of these capacitors should be kept as equal as possible, in order to prevent generation of extra currents inside the converter which result from the voltage imbalance. Submodule capacitor voltage balancing methods are presented in chapter 4. For now, it is assumed that all the capacitors are equally charged. In steady state open loop operation of the converter, among 2N submodules in a phase leg, N of them are inserted to the current path. Therefore, the natural average voltage of submodule capacitors,  $V_c$ , is expressed as in Equation (2.1):

$$V_c = \frac{V_{dc}}{N} \tag{2.1}$$