### UNIBUS: A UNIVERSAL HARDWARE ARCHITECTURE FOR SERIAL BUS INTERFACES WITH REAL-TIME SUPPORT

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

## MEHDI DUMAN

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

JANUARY 2015

Approval of the thesis:

## UNIBUS: A UNIVERSAL HARDWARE ARCHITECTURE FOR SERIAL BUS INTERFACES WITH REAL-TIME SUPPORT

submitted by **MEHDI DUMAN** in partial fulfillment of the requirements for the degree of **Master of Science in Electrical and Electronics Engineering Department**, **Middle East Technical University** by,

| Prof. Dr. Gülbin Dural Ünver<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>               |  |

|------------------------------------------------------------------------------------------------------------|--|

| Prof. Dr. Gönül Turhan Sayan<br>Head of Department, <b>Electrical and Electronics Engineering</b>          |  |

| Assoc. Prof. Dr. Şenan Ece Güran Schmidt<br>Supervisor, <b>Electrical and Electronics Eng. Dept., METU</b> |  |

|                                                                                                            |  |

| Examining Committee Members:                                                                               |  |

| Prof. Dr. Gözde Bozdağı Akar<br>Electrical and Electronics Engineering Dept., METU                         |  |

| Assoc. Prof. Dr. Şenan Ece Güran Schmidt<br>Electrical and Electronics Engineering Dept., METU             |  |

| Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı<br>Electrical and Electronics Engineering Dept., METU                |  |

| Dr. Nizam Ayyıldız<br>ASELSAN,REHİS                                                                        |  |

| Dr. Salih Zengin<br>TÜBİTAK SAGE                                                                           |  |

|                                                                                                            |  |

| Date:                                                                                                      |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: MEHDI DUMAN

Signature :

# ABSTRACT

### UNIBUS: A UNIVERSAL HARDWARE ARCHITECTURE FOR SERIAL BUS INTERFACES WITH REAL-TIME SUPPORT

Duman, Mehdi

M.S., Department of Electrical and Electronics Engineering Supervisor : Assoc. Prof. Dr. Şenan Ece Güran Schmidt

January 2015, 61 pages

Serial bus communication is widely used in different application areas such as Ethernet in computer networking, CAN bus in in-vehicle communications, MIL-STD 1553B in military avionics and UART for peripheral device communication. This thesis work presents UNIBUS (Universal Bus); an abstract, generic block level hardware architecture for implementing serial bus interfaces. UNIBUS realizes the physical and data link layer functions supporting the strict timing requirements for bit operations and synchronization.

The hardware blocks and signal interfaces among these blocks are designed to separate the protocol specific and protocol independent components to increase reusability. A specific serial bus protocol can be implemented using UNIBUS by defining the protocol specific operations and interfaces.

The versatility of UNIBUS is demonstrated by realizing CAN, UART, ARINC-708, ARINC-717 and MIL-STD-1553B on this architecture. These serial bus interfaces are purposely selected to be from different application areas and levels of complexity. All these interfaces are implemented using MODELSIM simulation tool and tested by realizing a sender and receiver that exchange messages as specified. Furthermore MIL-STD- 1553B is fully implemented on FPGA and its correctness is verified by communication to a commercial chip. The analysis of the resource and power con-

sumption of the realizations shows that the generality of the architecture does not decrease the efficiency of the implementations.

UNIBUS decreases the hardware development time for existing and possibly new serial bus protocols by providing the readiliy designed blocks and signal interfaces. Furthermore UNIBUS increases the reliability of the design as the reused protocol independent components that are common among different protocols need to be verified only once and the blocks together with their interfaces are clearly defined. UNIBUS can be both used for the development of full scale serial bus interface components to be used in real systems as well as developing test benches for existing products. In such deployment, a given bus interface's desired functions can be implemented on UNIBUS to achieve a communicating counterpart for the tested component.

Keywords: Real time, serial, embedded bus protocol, generic architecture, encoder, decoder, field programmable gate array (FPGA), hardware, universal bus, serial bus

## UNIBUS: SERİ VERİYOLU ARAYÜZLERİ İÇİN GERÇEK ZAMAN DESTEKLİ GENEL BİR DONANIM MİMARİSİ

Duman, Mehdi Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Doç. Dr. Şenan Ece Güran Schmidt

Ocak 2015, 61 sayfa

Seri veriyolu haberleşmesi genel olarak, bilgisayar ağlarındaki Ethernet veriyolu, araç içi haberleşmesindeki CAN veriyolu, havacılıkdaki MIL-STD-1553B veriyolu, çevre birimi cihaz haberleşmesindeki UART veriyolu gibi uygulamalarda kullanılmaktadır. Bu tez çalışması, seri veriyolu arayüzleri uygulamaları için UNIBUS (genel veriyolu); blok seviyesinde öz ve genel bir donanım mimarisi sunmaktadır. UNIBUS, bit operasyonları ve bit senkronizasyonu için gerekli olan katı zamanlama ihtiyaçlarını destekleyerek veri bağı ve fiziksel katman fonksiyonlarını gerçeklemektedir.

Donanım blokları ve bu bloklar arasındaki sinyal arayüzleri, yeniden kullanılabilirliği artırmak için protokole özel ve protokolden bağımsız bileşenleri ayıracak şekilde tasarlanmaktadır. Belirli bir seri veriyolu protokolü, protokole özgü operasyonlar ve arayüzler tanımlanarak UNIBUS ile gerçeklenebilir.

UNIBUS mimarisinin çok yönlülüğü, CAN, UART, ARINC-708, ARINC-717 and MIL-STD-1553B protokolleri gerçeklenerek gösterilmektedir. Bu protokoller, farklı uygulama alanlarından ve farklı karmaşıklık seviyelerinden olması maksadıyla seçilmiştir. Bütün bu arayüzler MODELSIM simülasyon aracı kullanılarak gerçeklenmektedir ve protokolde tanımlanan şekilde mesajları değiştiren gönderici ve alıcı gerçeklenerek test edilmektedir. Buna ek olarak, MIL-STD-1553B protokolü FPGA üzerinde tamamıyla gerçeklenmektedir ve bu uygulamanın doğruluğu ticari bir yonga ile haberleşilerek kanıtlanmaktadır. Gerçeklemelerin kaynak ve güç tüketim analizleri, mimarinin genelliğinin ve uygulamaların etkinliğinin azaltılmadığını göstermektedir.

UNIBUS, hazır tasarlanmış bloklar ve sinyal arayüzleri sağlayarak, mevcut ve yeni seri veriyolu protokolleri için donanım geliştirme süresini azaltmaktadır. Buna ek olarak, UNIBUS, farklı protokoller arasında ortak olan protokolden bağımsız bileşenler bir kereye mahsus olarak doğrulandığında ve bloklarla birlikte arayüzleri açık bir şekilde tanımlandığında, tasarımın güvenilirliğini artırmaktadır. UNIBUS gerçek sistemlerde kullanılmak üzere tam boyutlu veriyolu arayüzü bileşenlerinin geliştirilmesinde ve varolan ürünlerin testlerinin geliştirilmesinde kullanılabilir. Bu tarz işlemde, verilen veriyolu arayüzünün gerekli fonksiyonları, test edilen bileşen için iletişime geçen karşı parçayı oluşturmak üzere UNIBUS üzerinde uygulanabilir.

Anahtar Kelimeler: Gerçek zamanlı, seri, gömülü veriyolu protokolü, genel mimari, kodlayıcı, kod çözücü, alanda programlanabilir kapı dizileri, donanım, genel veriyolu, seri veriyolu

To My Family

# ACKNOWLEDGMENTS

I would like to express my special thanks to my supervisor Assoc. Prof. Dr. Şenan Ece Schmidt. My special thanks go to TÜBİTAK SAGE. Finally, I would like to thank my family and friends who supported me throughout the whole time.

# **TABLE OF CONTENTS**

| ABSTRA  | ACT     |                                                                   |

|---------|---------|-------------------------------------------------------------------|

| ÖZ      |         |                                                                   |

| ACKNO   | WLEDG   | MENTS                                                             |

| TABLE   | OF CON  | TENTS                                                             |

| LIST OF | F TABLE | S                                                                 |

| LIST OF | FIGUR   | ES                                                                |

| LIST OF | FABBRI  | EVIATIONS                                                         |

| CHAPT   | ERS     |                                                                   |

| 1       | INTRO   | DUCTION 1                                                         |

| 2       | SERIAI  | L BUS STANDARDS AND THEIR IMPLEMENTATION 5                        |

|         | 2.1     | Serial Bus Standards                                              |

|         | 2.2     | Implementation Challenges and Performance Metrics 6               |

|         | 2.3     | Related Work on Implementation of Serial Buses 7                  |

|         | 2.4     | Hardware Implementation Platforms                                 |

|         | 2.5     | Previous Implementations of the MIL-STD-1553B protocol<br>on FPGA |

| 3       | UNIBU   | S HARDWARE ARCHITECTURE                                           |

| 4     |       |          | ION AND EVALUATION OF SELECTED BUS PRO-<br>UNIBUS | 23 |

|-------|-------|----------|---------------------------------------------------|----|

|       | 4.1   | Design a | nd Implementation                                 | 23 |

|       |       | 4.1.1    | CAN Bus                                           | 26 |

|       |       | 4.1.2    | UART                                              | 27 |

|       |       | 4.1.3    | ARINC-708 and ARINC-717                           | 28 |

|       |       | 4.1.4    | MIL-STD-1553B                                     | 29 |

|       |       | 4.1.5    | Summary and Overview of Signal Interfaces         | 30 |

|       |       | 4.1.6    | MIL-STD-1553B Hardware Realization                | 30 |

|       | 4.2   | Performa | nce Evaluation                                    | 45 |

| 5     | CONC  | LUSIONS  | AND FUTURE WORK                                   | 55 |

| REFER | ENCES |          |                                                   | 57 |

# LIST OF TABLES

# TABLES

| Table 3.1 | Signal interface between the Application Layer and BPC                                                                                                                         | 16 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2 | BPC control signals sent to the transceiver                                                                                                                                    | 16 |

| Table 3.3 | Signal interface between BPC and DBM                                                                                                                                           | 17 |

| Table 3.4 | Signal interface between BPC and CG                                                                                                                                            | 17 |

| Table 3.5 | Signal interface between BPC and the Encoder Controller                                                                                                                        | 19 |

| Table 3.6 | Signal interface between the Encoder Controller and the Line Encoder.                                                                                                          | 20 |

| Table 3.7 | Signal interface between Decoder Controller and the Line Decoder                                                                                                               | 21 |

| Table 3.8 | Signal interface between BPC and the Decoder Controller                                                                                                                        | 21 |

|           | Signal interface between the Encoder Controller and the Decoder roller.                                                                                                        | 22 |

| Table 4.1 | Comparison table of the implemented bus protocols                                                                                                                              | 24 |

|           | The detailed PS signal interface between the Application layer and block for the implemented serial protocols.                                                                 | 31 |

| coder     | The detailed PS signal interface between the BPC, DBM, CG, En-<br>Controller and Decoder Controller blocks for the implemented se-<br>rotocols.                                | 32 |

| Enco      | The detailed PS signal interface between the Decoder Controller and der Controller blocks and the Decoder Controller and Line Decoder as for the implemented serial protocols. | 33 |

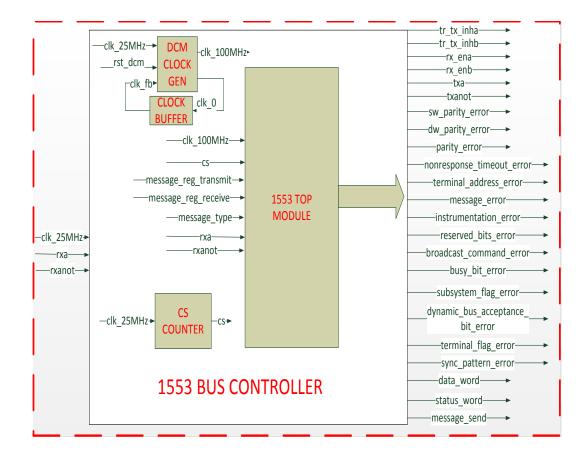

| Table 4.5 | Signal interface of the MIL-STD-1553 bus controller block                                                                                                                      | 38 |

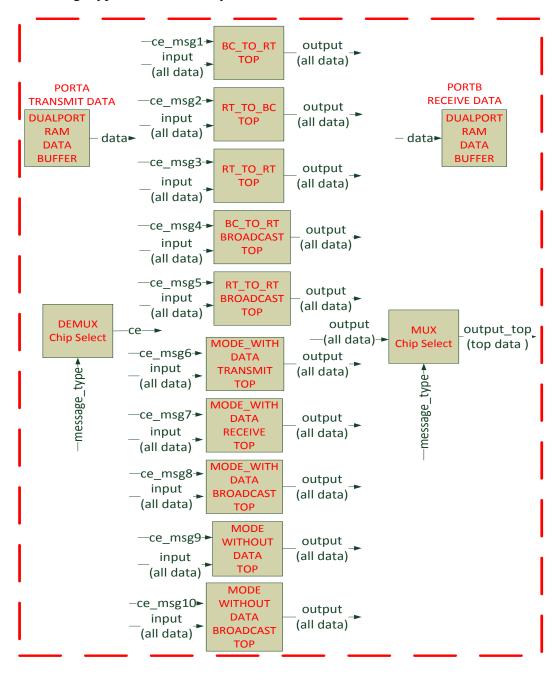

| Table 4.6 | Signal interface of the 1553 TOP MODULE block                                                                                                                                  | 41 |

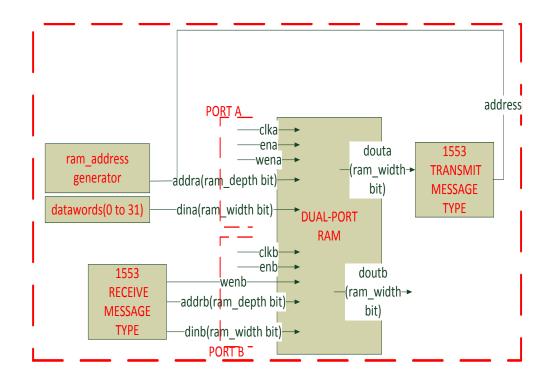

| Table 4.7 | Signal interface of the dual port memory block                                                                                                                                 | 42 |

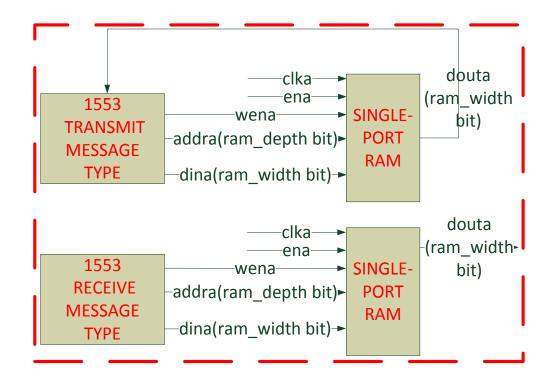

| Table 4.8    Signal interface of a single port memory block.                                            | 44 |

|---------------------------------------------------------------------------------------------------------|----|

| Table 4.9 The required hardware resources for the implementation of five different bus protocols.       | 47 |

| Table 4.10 The power consumptions for the implementation of five different bus protocols.               | 48 |

| Table 4.11 The common blocks for the implementation of five different bus protocols.         protocols. | 49 |

| Table 4.12 The comparison between our proposed work and the commercial products.                        | 52 |

# LIST OF FIGURES

# FIGURES

| Figure 3.1 Tl  | he functional block diagram of UNIBUS architecture                                                             | 14 |

|----------------|----------------------------------------------------------------------------------------------------------------|----|

| Figure 3.2 H   | ardware Block Diagram of UNIBUS architecture                                                                   | 15 |

| e              | lock diagram for the simulation of the MIL-STD-1553B, UART, 708, and ARINC-717 bus protocols.                  | 25 |

| Figure 4.2 B   | lock diagram for the simulation of the CAN bus protocol                                                        | 25 |

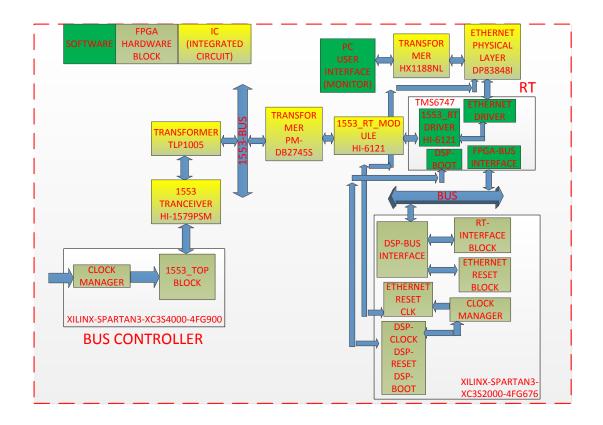

| U              | lock diagram of the hardware platform for the implementation of coller terminal of the MIL-STD-1553B protocol. | 33 |

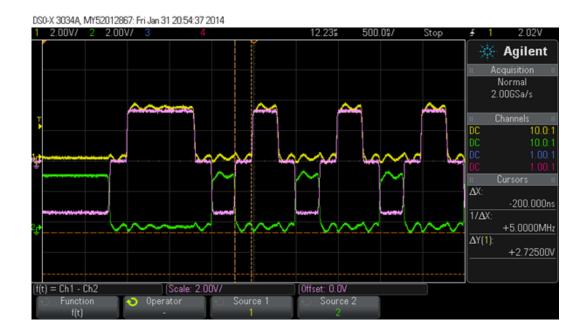

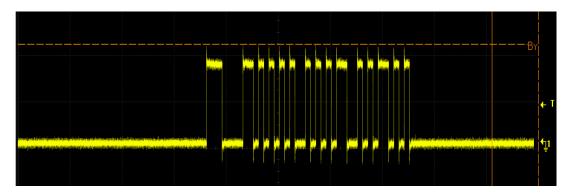

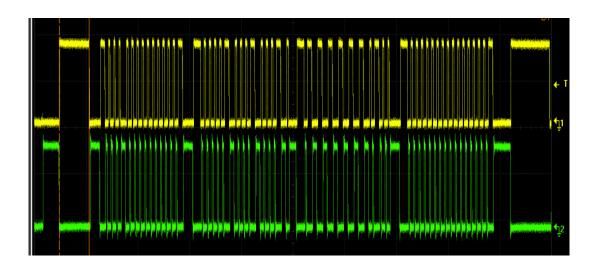

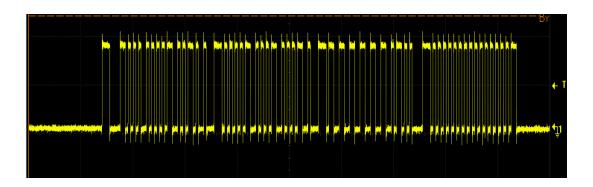

| •              | creen shot of the scope screen. Outputs of the transceiver (HI-<br>A)                                          | 35 |

| •              | lock diagram for the bus controller block of the MIL-STD-1553                                                  | 37 |

| Figure 4.6 B   | lock diagram for 1553 TOP MODULE block                                                                         | 40 |

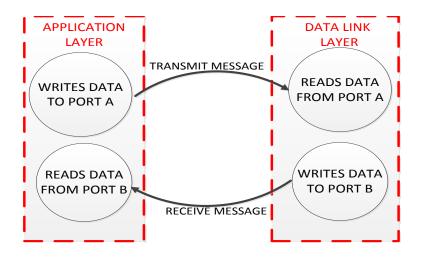

| -              | lock diagram for the data buffer between the application layer lata link layer.                                | 42 |

|                | ycle diagram for the data buffer between the application layer and link layer.                                 | 43 |

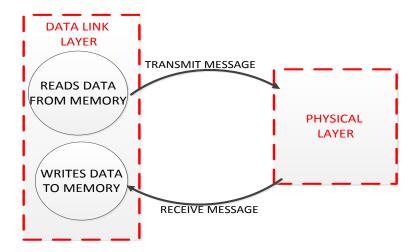

| e              | lock diagram for the data buffer between the data link layer and ical layer.                                   | 43 |

| 0              | ycle diagram for the data buffer between the data link layer and cal layer.                                    | 44 |

| Figure 4.11 Sc | creen shot of the receive command word                                                                         | 45 |

| Figure 4.12 Sc | creen shot of the received status and data words                                                               | 45 |

| Figure 4.13 Sc | creen shot of the transmit command word                                                                        | 46 |

| Figure 4.14 Screen shot of the monitor screen          | 46 |

|--------------------------------------------------------|----|

| Figure 4.15 Cycle diagram for the loopback test        | 47 |

| Figure 4.16 The comparison of the UART implementation. | 50 |

# LIST OF ABBREVIATIONS

| ARINC  | Aeronautical Radio Incorporated                                       |

|--------|-----------------------------------------------------------------------|

| BPC    | Bus Protocol Controller                                               |

| CAN    | Controller Area Network                                               |

| CG     | Checksum Generator                                                    |

| CRC    | Cyclic Redundancy Check                                               |

| DBM    | Data Buffer Memory                                                    |

| DSP    | Digital Signal Processor                                              |

| FPGA   | Field Programmable Gate Array                                         |

| HDL    | Hardware Description Language                                         |

| LIN    | Local Interconnect Network                                            |

| MOST   | Media Oriented Systems Transport                                      |

| PI     | Protocol Independent                                                  |

| PIC    | Peripheral Interface Controller                                       |

| PS     | Protocol Specific                                                     |

| TTCAN  | Time Triggered Controller Area Network                                |

| TTP    | Time Triggered Protocol                                               |

| UART   | Universal Asynchronous Receiver Transmitter                           |

| UNIBUS | Universal Bus                                                         |

| VHDL   | Very High Speed Integrated Circuit Hardware Description Lan-<br>guage |

# **CHAPTER 1**

# **INTRODUCTION**

Serial communication is widely used in computer networks and embedded systems because of its simplicity and small number of connectors which result in better physical properties such as less crosstalk. Furthermore high data rates are possible with fast clocking.

Examples for serial communication protocols include Ethernet in desktop computing, Controller Area Network (CAN) in in-vehicle networking and manufacturing systems, MIL-STD 1553B in avionic systems, ARINC-708 in Airborne weather radar systems, ARINC-717 in flight data acquisition and recording systems and Universal Asynchronous Receiver/Transmitter (UART) in the communication with peripheral devices.

Serial communication protocols realize the data link layer and the physical layer functionality of the OSI (Open System Interconnection) model [1]. To this end, each protocol defines the physical layer features including the mechanical and electrical characteristics of connectors and communication channel, characteristics of electrical signals and clock synchronization functions. Furthermore, data link layer features are defined including framing, addressing, channel access arbitration, encoding and decoding. Reliable data transmission is achieved by acknowledgement mechanisms, error controlling and handling. One should note that functions related to bit timing and clock synchronization should be carried out with stringent timing.

Despite the high-level similarity, these functions are defined differently for each protocol leading to specific realizations. Recognizing this high-level similarity, this thesis proposes a modular, generic and abstract hardware architecture UNIBUS (Universal Bus) for implementing serial bus protocols. The architecture supports the timing requirements for bit transmissions and synchronization. The universal designation is because of the high flexibility and configurability of the architecture that enables the realization of different serial bus protocols.

UNIBUS consists of a number of different hardware blocks. All of them differ from each other by the kind of data processing they perform and operate independent of each other. Each block has *protocol independent* (PI) signal interfaces and *protocol specific* (PS) signal interfaces where PS interfaces have to be customized for the specific bus protocol. The design philosophy of UNIBUS is separating the PS and PI functionality and interfaces to increase the re-usability of the PI components and signals as much as possible when implementing different serial bus protocols.

The versatility of UNIBUS is demonstrated by implementing five different serial bus protocols with it. These protocols are MIL-STD-1553B, ARINC-708, ARINC-717, CAN and UART. These protocols are selected to include standards that are similar in terms of functionality and interfaces such as ARINC-708 and ARINC-717 and completely different such as CAN. Also they have different levels of complexity such as the complex MIL-STD-1553B and simple UART.

All of these protocols are simulated by using MODELSIM platform, and then MIL-STD-1553B bus controller is implemented on hardware by using FPGA platform. An experimental set-up with MIL-STD-1553B implemented on UNIBUS and a commercial chip is constructed and the correctness of the implementation is verified by establishing communication between these two parties. We evaluate the hardware resource consumption as well as power consumption for all these implementations. Our results show that despite the architecture is generic the resulting specific realizations are highly efficient. We propose a solution for the decoder design of the hardware framework architecture. Consequently, our proposed decoder design does not require a specific clock signal. Hence, it is possible to design the hardware framework more efficiently and more simply by means of our decoder design.

UNIBUS significantly reduces the workload and the design time of the implementation by reconfiguring the logical organization of the functions of the bus protocols. The protocol independent components that are common among different protocols need to be verified only once and the protocol specific components are clearly defined. Hence, UNIBUS improves the reliability of the serial bus implementation.

The remainder of the paper is organized as follows. Chapter 2 describes the operation principles of the hardware framework for the serial bus protocols in general and the challenges and performance metrics that we focus on in this thesis during the hardware implementation. The possible hardware implementation platforms and previous works on the implementation of serial bus protocols are also discussed in Chapter 2. We introduce the detailed description of UNIBUS architecture in Chapter 3. Chapter 4 describes in detail the implementation and performance evaluation of the five specific serial bus protocols. Chapter 5 discusses the conclusions and introduces the next stage of our work.

### **CHAPTER 2**

# SERIAL BUS STANDARDS AND THEIR IMPLEMENTATION

A real-time system receives data, processes them, and returns the results in a specified time. Real-time bus protocols are intended to serve the communication requirements such real-time systems therefore, they must guarantee response within strict time constraints.

#### 2.1 Serial Bus Standards

Serial bus protocols are the standards that are defined for the bitwise transport of the data on the Serial Bus. Serial bus protocols are used for communication and computer platforms, where the cost of cable and synchronization difficulties make parallel communication impractical.

The functions of the data link layer and the physical layer as defined in OSI layered model are the main functions of the serial bus protocols. Error detection and correction, arbitration, frame generation and frame processing, data stream synchronization and addressing are the functions of the data link layer. Bit decoding, bit encoding, clock synchronization of a bit are the functions of the physical layer. However, each serial bus protocol has own set of algorithm for data processing, the bitwise transmission, and the reception methods.

#### 2.2 Implementation Challenges and Performance Metrics

We identify the following metrics to evaluate UNIBUS both as a generic real time serial bus architecture and for the specific realization of the components.

- Clock frequency requirements (Design of the decoder)

- Structure of the bus architecture (modularity and signal interfaces)

- Logic resource and power consumption

- Memory requirements

Hardware area utilization and hardware power consumption requirements give the performance of our proposed hardware framework. These parameters are used when the simulations of five different bus protocols explained in Chapter 4 are compared.

Memory requirements, and clock frequency requirements are used to compare our implementation of the bus controller terminal of the MIL-STD-1553B bus protocol with the commercial products.

The decoder block for such kind of embedded serial bus protocols continuously monitors its data input lines for a valid character. However, capturing such a valid character is a challenging process. So that, the design of the decoder is important for the complexity of the hardware design. The decoder's method of measuring its two inputs determines its sensitivity to bus line signal changes caused by amplitude variance. Therefore, the transceiver and decoder design must be considered together and the characteristics of the transceiver must be the main guide for the algorithm of the decoding process.

The decoder must estimate the actual zero crossing times while gaps occur between receiver output transitions. The gaps become wider as receive signal amplitude decreases. Decoder must solve this issue in order to decode the received signal correctly.

[65], [66], [60], [58], [18], [21], [28] use specific clock frequency, which is equal to the 12 times of the desired data rate, in their decoder design. They use this clock in order to sample and decode the incoming data. However, in their decoder block

they assume that comparator thresholds are balanced, and zero crossing will be at the midpoint of the input signal. However, this prediction can introduce an additional zero crossing error into the received signal seen by the decoder. Such kind of decoder poorly estimates actual zero crossing times, and it could reject a frame word because of zero crossing errors.

In this thesis, the decoder design in UNIBUS architecture captures the zero crossing points in the encoded data instead of using a specific clock signal. Hence, our decoder design is tolerant of actual zero-cross distortion in the received signal and zero crossing errors are eliminated for our decoder design by means of this method.

Performance evaluation and the comparison results are explained in the Performance Evaluation section of the Chapter 4.

#### 2.3 Related Work on Implementation of Serial Buses

In this Section, we discuss the previous works related to the real-time embedded bus implementation on hardware and specific FPGA implementations.

Works have been done in [41] and [40] to provide a different kind of physical layers for MIL-STD-1553B bus protocol. In [41], new physical layer is analyzed to provide high-speed communication for MIL-STD-1553B protocol whereas in [40] new physical layer is designed to evaluate the channel attenuation of the MIL-STD-1553B protocol system. However, in our work, for implementing such kind of a physical layer integrated circuits are used.

The implementation of UART protocol was presented in [62], [64], [42], and [50]. In [62], three main hardware blocks such as transmitter, receiver, and baud rate generator were designed. In addition, in [64], the analysis of CRC generation algorithm was performed in order to improve the error capability of the design. In [42], a solution for the problems of inefficient data transmission and data bus utilization ratio was proposed whereas in [50], a bidirectional shift converter technique was realized to control package bits of data for data transmission and reception processes. All of these works were implemented on FPGA by using VERILOG hardware description

language.

CAN and UART protocols were studied together in [67]. They used these protocols at the highest transmission rate to investigate the data communication between FPGA and the observer. On the other hand, the design and implementation of UART-SPI Interface were proposed in [38]. SPI slave devices can communicate with a UART port by means of their design.

The implementation of CAN protocol was presented in [46], [39], [37], [56], [45], [61], and [55]. Eight-to-Eleven Modulation technique was proposed for bit-stuffing process to reduce the timing variation caused by bit-stuffing in [46]. A programmable controller was realized in [39]. CAN protocol was used as data communication protocol between the host controller and its various extension modules for their proposed design. In [37], different communication protocols such as LIN, CAN, ByteFlight, TTCAN, FlexRay, MOST, TTP were compared and CAN and LIN protocols were implemented on PIC. In [56], CAN protocol was also implemented on PIC for monitoring parameters such as temperature, battery voltage, and cobalt level in the exhaust. On the other hand, a hardware based CAN sniffer was studied in [45]. The CAN message frame architecture, bit coding techniques and CAN bit sampling techniques were examined in their work. In [61], CAN bus based control system was studied by using FPGA platform whereas in [55], CAN bus based real-time Data Visualization system was studied.

An experimental system for the CAN bus was proposed in [47]. Their design was based on both hardware and software by using micro controller called as STC89C52 and CAN protocol controller called as SJA1000. In addition, in [43], an intelligent controller of charge and discharge machine was implemented. CAN bus communication network was used in their implementation to monitor and control the software of host computer.

A bit-level interference test method was studied in [35], and [54]. Both studies were performed on FPGA. Besides these works, a simulation model for CAN bus was studied in [36]. In [63], a kind of customized dual redundancy CAN bus controller was proposed. Their design was based on FPGA in order to provide high real-time performance and reliability. Physical layer of this design has two independent channels.

If one of them fails during message transmission process, the other one will be used to transmit the message.

The ARINC-659 bus protocol, which is a standard for digital data transfer, was implemented in [34]. Their design was modeled using VERILOG language and their host was modeled by using soft processor core called as NIOS II. HDL modules are interfaced with the soft processor core to achieve the real-time system requirements. On the other hand, in [59], 6-way serial data communication was introduced. Their data processing system was performed on the soft processor called as NIOS II.

#### 2.4 Hardware Implementation Platforms

In this Section, we present the hardware platforms for real-time embedded serial bus architectures concluding that FPGA is the most versatile technology for implementation.

ASIC (Application Specific Integrated Circuit) design yields the fastest implementations for real-time embedded serial bus implementations. However, ASIC design is expensive, and it has a very long time to market and lacks such flexibility.

*FPGA (Field Programmable Gate Array)* technology is a compromise between the speed of ASIC and the flexibility of the network processors. One of the main reasons for using FPGAs within an embedded system is performance. A very high number of logic gates and embedded blocks in today's FPGAs enables the design of complex hardware platforms with reduced engineering cost and rapid turnaround time. In addition, FPGAs are highly suitable for time critical applications so that they are increasingly employed in safety and mission critical applications within the aerospace and defense sectors. On the other hand, if the final implementation platform is ASIC, FPGA can be used for prototype production [44]. Consequently, it is possible to convert a hardware design on FPGA to ASIC provided that power source design, packaging and boundary scan testing constraints are taken into consideration [51].

Since FPGAs are highly flexible and programmable, the implementation of a realtime embedded serial bus protocols can be done with great ease and flexibility. While FPGAs are configurable devices, reconfigurable hardware architectures can be easily implemented on FPGAs.

#### 2.5 Previous Implementations of the MIL-STD-1553B protocol on FPGA

Historically, serial communication buses were implemented using commercial off the shelf components. This approach was however not so efficient since the changing application requirements often rendered the system obsolete. Recently, several serial communication protocols are designed to be implemented on the FPGA because more than one communication protocol can be integrated in a single chip and the system can be programmed whenever required by means of the FPGA. However, using FPGAs in such applications has its challenges since time, power, reliability and data integrity are highly crucial factors. Because of that reason, careful designs should be prepared.

There is a large amount of literature on hardware implementation of the serial bus protocols. In this section, we provide an overview of the already existing approaches specifically with respect to MIL-STD-1553B protocol applications, and highlight the non-reconfigurable hardware bus architectures in such kind of systems since we implement MIL-STD-1553B protocol bus controller unit in our implementation. All of the previous studies select FPGA as the target hardware platform, however, the implementations are limited to the VHDL model synthesis without any actual measurements collected on hardware.

A work has been done in developing a specific hardware bus architecture for a serial communication system based on MIL-STD-1553B communication protocol [49] and [52]. However, the authors only state that the MIL-STD-1553B protocol bus controller unit is designed without any further details. Furthermore, no discussion is provided related to the implementation of their designs. The experimental results are provided only for target device utilization in [49] and the simulation result of sending a command word in [52]. Another related work also proposes an implementation of MIL-STD-1553B protocol in an FPGA [65]. In this work, instead of implementing a separate clock, digital phase lock loop is used for data clock recovery,

The work in [66] is also for the implementation of MIL-STD-1553B bus controller

unit. It uses a specific hardware bus architecture for its implementation. It is important to note that their proposed design requires 12 MHz clock frequency for its decoder design since it uses this clock for capturing the encoded data. On the other hand, in [60] VHDL implementation of the Manchester encoder and decoder is purposed. The decoder design for this work also requires a specific clock that has a frequency of 12 times the desired data rate. However, using such kind of specific clock frequency decreases the performance of the system and increases the complexity of the hardware architecture. Therefore, their approach for their decoder design is not preferable for such avionic applications. Another similar work is also proposed in [48]. Encoder and decoder are modeled as a state machine and they are simulated in MODELSIM platform.

A very recent study proposed in [57] suggests a low-cost design of MIL-STD-1553 bus terminal devices. They use DSP(Digital Signal Processor) having on-chip multichannel buffered serial port in order to perform all the necessary functions of MIL-STD-1553B protocol. However, using a DSP for such kind of serial data bus protocols will be slower and more complicated. Using an FPGA for serial bus protocols increases simplicity and the reliability of the system design.

In [58] the authors propose a methodology for studying of MIL-STD-1553 architecture and studying of Core1553BRM IP core from Actel. They implement it on FPGA. Although the title of the paper suggests a VHDL implementation of MIL-STD-1553B protocol, only data transfer between the bus controller unit and remote terminal is demonstrated in this work. For the realization of the MIL-STD-1553B bus protocol, they use IP core so that they didn't design any bus architecture for their implementation.

Specific bus architectures are used for all mentioned previous works. However, in [53] a generic hardware and software architecture for the implementation of serial bus protocols was proposed. The data link layer functions were implemented in software while physical level functions were implemented in hardware. In order that to estimate the efficiency of offered method, a system with 1-Wire interface controller based on UART was implemented. Software and hardware modules were implemented directly in FPGA. Spartan-3E FPGA family [25] was used as a hardware de-

vice whereas soft microcontroller core PicoBlaze [20] provided by Xilinx company for free was used as a soft-core processor.

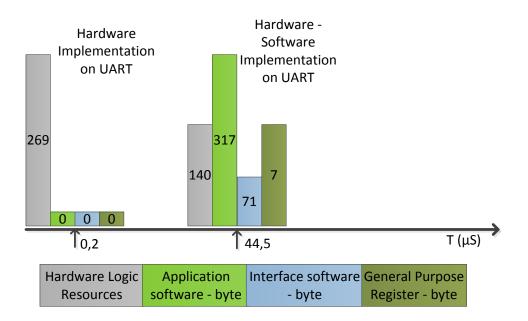

The efficiency estimation of their UART implementation was made by two criteria: (i) the hardware expenses of system implementation; (ii) time interval required for executing of data exchange. They used a histogram to show their results. Each column in their histogram presents the hardware expenses, the size of application software, the size of interface support software and the amount of used general purpose registers.

Same method is used in order to compare our UART implementation results with this work. Comparison results are explained in the Performance Evaluation section of the Chapter 4.

Furthermore, in most of the proposed works the implementation is limited to the HDL model synthesis without any real-world implementation and test or experiments carried out on hardware. Therefore, based on existing works in the field of avionics, we aim to propose a new generic reconfigurable hardware framework for serial bus communication systems. To the best of our knowledge there is no hardware implementation based on FPGA which uses a generic and reconfigurable hardware architecture like our design.

## **CHAPTER 3**

## **UNIBUS HARDWARE ARCHITECTURE**

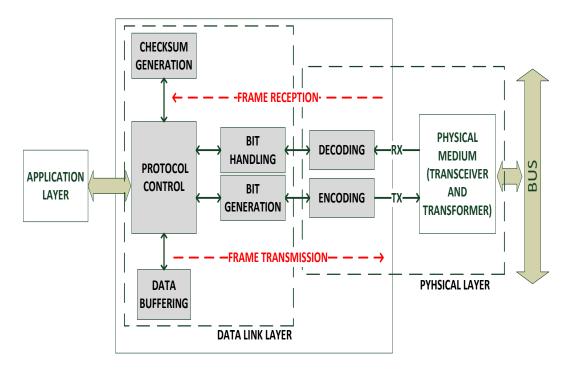

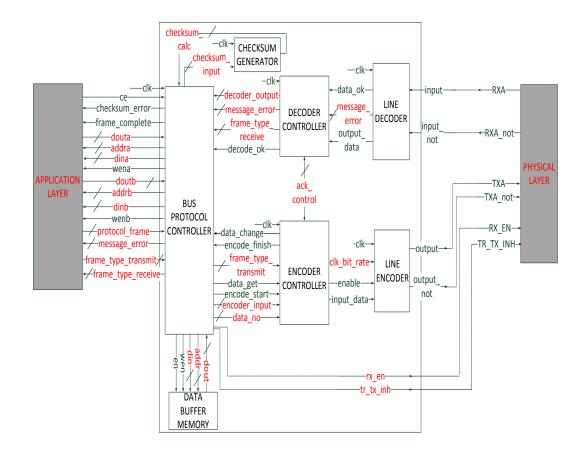

In this section, we propose a generic block-level hardware design for the implementation of Real-time Embedded Bus Architectures for serial bus interfaces as depicted in Fig. 3.2.

We define seven different hardware blocks in UNIBUS architecture according to our functional decomposition of the serial bus interfaces presented in Chapter 1 and Chapter 2 as shown in Fig. 3.2. These hardware blocks are bus protocol controller (BPC), Data Buffer Memory (DBM), Checksum Generator, Encode Controller, Line Encoder, Decode Controller and Line Decoder. These blocks operate independent of each other and have both *protocol independent* (PI) signal interfaces and *protocol specific* (PS) signal interfaces.

The design philosophy of UNIBUS is separating the PS and PI functionality and interfaces to increase the re-usability of the PI components and signals as much as possible when implementing different serial bus protocols.

The high-level functional block diagram and the corresponding hardware block and signal diagram of the UNIBUS architecture are shown in Fig. 3.1 and Fig. 3.2 respectively. The signals with PS functions in Fig. 3.2 are indicated with red color. The width of all multi-bit signals are protocol specific.

Frame transmission and frame reception are two sets of separate processes, interacting with each other. Frame reception consists of the detection of a frame start condition, determining the bit time interval, data stream synchronization, detection of the logical value of the received bit, marking the beginning of a new frame, constructing a frame

out of received bits, address checking, detection and possible correction of frame errors and extraction of the data array (payload) out of a frame, which is read from the data bus.

Frame transmission consists of indication of a frame start condition, determining of the bit time interval, bitwise transmission of the frame, clock synchronization of bits, data stream synchronization, bit stuffing, reception of data array from the application layer and frame generation.

Figure 3.1: The functional block diagram of UNIBUS architecture.

Bus Protocol Controller (BPC) Block is the main block of UNIBUS initiating and controlling the data transfers between UNIBUS and the Application and Physical Layers as well as the data flow among UNIBUS blocks. Frame generation and frame processing, detection and correction of errors in received frames, data stream control, addressing and arbitration are the functions that are implemented in this block. These functions vary according to the type of the bus protocol. Therefore, the logic design of this block should be customized for the implemented protocol.

BPC has input and output signal interfaces with DBM, Checksum Generator, Decoder Controller and Encoder Controller. It communicates with the Checksum Generator

Figure 3.2: Hardware Block Diagram of UNIBUS architecture.

to detect checksum errors, and it communicates with DBM to store the transmitted and received frames. Furthermore BPC realizes frame transmission to the bus and the frame reception from the bus by communicating with the Encoder Controller and Decoder Controller.

BPC has external signal interfaces to application and physical layers. The signal interface between the application layer and BPC is shown in Table 3.1. BPC communicates via a dual port memory with the application layer which enables the users to initiate and monitor the data flow.

BPC sends control signals to the transceiver chip via physical layer signal interface as shown in Table 3.2.

DBM is the data buffer between UNIBUS and physical layer. Its width and depth should be customized for the amount of data that are going to be stored during the frame transmission. BPC communicates with DBM to control the frame transmission

| Table 3.1: Signal interface | between the Application Layer and BPC. |

|-----------------------------|----------------------------------------|

|                             |                                        |

| Signal              | Width | Description                                                                                                   | Туре |

|---------------------|-------|---------------------------------------------------------------------------------------------------------------|------|

| се                  | 1     | '1':Enables frame transmission, '0':Disables frame transmission                                               | PI   |

| checksum_error      | 1     | '1': Checksum error, '0':No Checksum error                                                                    | PI   |

| frame_complete      | 1     | '1':Frame transmission or frame reception is finished,<br>'0':Frame transmission or frame reception continues | PI   |

| douta               | PS    | Data Output for PORTA of DBM, VALID: Before frame transmission                                                | PI   |

| addra               | PS    | Address for PORTA of DBM, VALID: Before frame transmission                                                    | PI   |

| dina                | PS    | Data Input for PORTA of DBM, VALID: Before frame transmission                                                 | PI   |

| wena                | 1     | '1':Enables writing on PORTA of DBM, '0':Disables writing on PORTA of DBM                                     | PI   |

| doutb               | PS    | Data Output for PORTB of DBM, VALID: After frame reception                                                    | PI   |

| addrb               | PS    | Address for PORTB of DBM, VALID: After frame re-<br>ception                                                   | PI   |

| dinb                | PS    | Data Input for PORTB of DBM, VALID: After frame reception                                                     | PI   |

| wenb                | 1     | '1':Enables writing on PORTB of DBM, '0':Disables writing on PORTB of DBM                                     | PI   |

| protocol_frame      | PS    | The frame content, VALID: Before frame transmission and reception                                             | PS   |

| message_error       | PS    | Protocol related error signals, VALID: After frame transmission and reception                                 | PS   |

| frame_type_transmit | PS    | Frame type to be encoded, VALID: Before frame trans-<br>mission                                               | PS   |

| frame_type_receive  | PS    | Decoded frame type, VALID: After frame reception                                                              | PS   |

Table 3.2: BPC control signals sent to the transceiver.

| Port      | Width | Description                                          | Туре |

|-----------|-------|------------------------------------------------------|------|

| rx_en     | 1     | '1':Receiver port of the transceiver is enabled,     | PS   |

|           |       | '0':Receiver port of the transceiver is disabled     |      |

| tr_tx_inh | 1     | '1':Transmitter port of the transceiver is disabled, | PS   |

|           |       | '0':Transmitter port of the transceiver is enabled   |      |

and reception via the signal interface shown in Table 3.3.

BPC specifies the address to read with "addr" and reads the data array from DBM on "dout" before frame transmission. In a reverse procedure, after the frame reception, BPC writes the data array extracted from the received frame to DBM by enabling write with "we". The data are transmitted on "din" interface and stored in the address specified by "addr" signal.

| Port | Width | Description                                     | Туре |

|------|-------|-------------------------------------------------|------|

| dout | PS    | Data output of DBM, VALID: During frame gener-  | PS   |

|      |       | ation.                                          |      |

| addr | PS    | Address for DBM, VALID: During frame genera-    | PS   |

|      |       | tion and after frame decoding.                  |      |

| din  | PS    | Data input of DBM, VALID: After frame decoding. | PS   |

| we   | 1     | '1':Enables writing DBM, '0':Disables writing   | PI   |

|      |       | DBM                                             |      |

| en   | 1     | '1':Enables DBM, '0':Disables DBM               | PI   |

Table 3.3: Signal interface between BPC and DBM.

Checksum Generator (CG) block generates the checksum value for the frames to be transmitted and as well as the frames that are received. The logic of CG is customized for the implemented protocol to implement different algorithms such as parity error checking or CRC(Cyclic Redundancy Check).

BPC controls and detects the protocol errors. Hence, CG communicates with BPC via the signal interface is shown in Table 3.4. The width of the input for CG depends on the frame length of the implemented protocol.

Table 3.4: Signal interface between BPC and CG.

| Port           | Width | Description                                     | Туре |

|----------------|-------|-------------------------------------------------|------|

| checksum_calc  | PS    | Calculated Checksum value, VALID: During frame  | PS   |

|                |       | generation and after frame decoding             |      |

| checksum_input | PS    | Input for Checksum Generator block, VALID: Dur- | PS   |

|                |       | ing frame generation and after frame decoding   |      |

We partition the encoding of the data to be transmitted into two blocks that are Encoder Controller and Line Encoder to separate the functions and signals which are PI and PS to increase signal reusability.

The Encoder Controller receives the Application data to be encoded in parallel from BPC. It serializes the data, forwards it to the Line Encoder and enables the Line Encoder. The Line Encoder executes the bit transmission functions. It encodes the serial bit stream received from the Encoder Controller in the specific line coding format such as non-return to zero (NRZ), Manchester bi-phase or Harvard bi-phase. It provides clock synchronization by placing synchronization bits at the beginning of the frame, and it executes bit stuffing if specified.

The design of Decoder Controller and Line Decoder is similar as they reverse the processing of Encoder Controller and Line Encoder. The Decoder Controller converts the serial data received from the Line Decoder to parallel and sends it to BPC. It further establishes the data stream synchronization to enable the decoder to resynchronize at the beginning of each frame received. The Line Decoder executes the bit reception functions. It decodes the serial bit stream received from the data bus in the specific line coding format. The logic design of the blocks is customized for a specific protocol that is implemented.

We next describe UNIBUS operations for the data reception from the Application Layer and frame transmission on the Physical Layer.

The Application layer starts sending data to UNIBUS by setting "ce" signal. "ce" is reset when the transmission is finished. The data from the Application Layer are read on PORTA of the dual port memory by BPC. First, BPC indicates the address of memory to read the data from on "addra" then reads the data on "douta". After reading, BPC writes the data to DBM in order to use them for frame generation.

During frame generation, BPC sends the data to Checksum Generator for the calculation of the checksum value on "checksum\_input" and reads the calculated checksum value on "checksum\_calc". After this calculation, BPC generates the frame by concatenating data, which are read from the application layer, the checksum value and the necessary frame bits related to the bus protocol.

When frame generation is finished, BPC sets "encode\_start" to activate the Encoder Controller. BPC sends the data to the Encoder Controller in blocks. The Encoder Controller reads the number of data blocks to encode on "data\_no" together with the first block on "encoder\_input". Then, it converts the parallel "encoder\_input" signal into a serial stream by shifting it from LSB(least significant bit) to MSB(most significant bit) or vice-versa and sends it to the Line Encoder.

When there are more than one blocks of data transfer, "data\_change" and "data\_get"

indicate the time of the getting the next data block from BPC. After encoding one block of data, the Encoder Controller sets "data\_change" signal to inform BPC for the preparation of the new data block. After that, BPC sets "data\_get" signal to inform Encoder Controller for the getting of the new data block. Data blocks are transmitted continuously with no gaps via this handshaking procedure. Therefore, it is a performance requirement that the Encoder Controller ensures no gaps in the encoded data array to support real-time data transmission.

"frame\_type\_transmit" signal shows the type of the frame that will be encoded. BPC uses this signal for defining the frame type to be generated, and Encoder Controller uses it for defining the synchronization pattern at the beginning of the frame.

The signal interface between BPC and Encoder Controller is shown in Table 3.5.

| Port               | Width | Description                                          | Туре |

|--------------------|-------|------------------------------------------------------|------|

| data_change        | 1     | '1':New data can be sent by BPC, '0': New data       | PI   |

|                    |       | can't be sent by BPC                                 |      |

| encode_finish      | 1     | '1':Encoding is finished, '0': Encoding is continued | PI   |

| frame_type_transmi | t PS  | Frame type to be encoded, VALID: During frame        | PS   |

|                    |       | encoding                                             |      |

| data_get           | 1     | '1':New data can be read by the Encoder Controller,  |      |

|                    |       | '0':New data can't be read by the Encoder Con-       |      |

|                    |       | troller                                              |      |

| encode_start       | 1     | '1':Encoding is enabled,'0': Encoding is disabled    | PI   |

| encoder_input      | PS    | Input signal for Encoder Controller, VALID: Dur-     |      |

|                    |       | ing frame encoding                                   |      |

| data_no            | PS    | Number of the data array, VALID: During frame en-    |      |

|                    |       | coding                                               |      |

Table 3.5: Signal interface between BPC and the Encoder Controller.

When "encode\_start" is set by BPC, the Encoder controller in turn sets "enable" to activate Line Encoder. Signal interface between Encoder Controller and Line Encoder is shown in Table 3.6. The Encoder Controller sends the data serially to the Line Encoder on "input\_data". The Line Encoder carries out the bit encoding and sends the encoded bits to the physical layer on "output" and "output\_not" signals.

When the last block of data is sent to the Line Encoder on "encoder\_input" the

Encoder Controller sets "encode\_finish" to indicate the end of the encoding of the frame and resets "enable". "clk\_bit\_rate" signal is the encoding clock to implement the bit encoding with the proper frequency.

| Table 3.6: Signal interface between the Encoder Controller and the Line Encoder. |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

| Port         | Width | Description                                      | Туре |

|--------------|-------|--------------------------------------------------|------|

| clk_bit_rate | 1     | '1':Encoding clock signal is high,'0': Encoding  | PS   |

|              |       | clock signal is low                              |      |

| enable       | 1     | '1':Enables Line Encoder,'0': Disables Line En-  | PI   |

|              |       | coder                                            |      |

| input_data   | 1     | Input bit to be encoded, VALID: During frame en- |      |

|              |       | coding                                           |      |

Finally, we describe UNIBUS operations for the frame reception from the Physical Layer and data transmission to the Application Layer.

Signal interface between Decoder controller and Line Decoder is presented in Table 3.7.

The "input" is the input bit which is read from the data bus and "input\_not" is the complement of it. The Line Decoder continuously monitors "input" and "input\_not" starts decoding when it detects a valid character. When the decoding of each data bit is completed, the Line Decoder puts the data bit on "output\_data" and sets "data\_ok". If the Line Decoder detects a decoding error caused by the input lines, it sets "message error".

The Decoder Controller reads the decoded data from the "output\_data" when the "data\_ok" is set. Then, it shifts this decoded bit serially into a shift register. When the last bit is in the shift register, the Decoder Controller sets "decode\_ok" to indicate the end of the decoding and puts the decoded data in the shift register on "decoder\_output" in order to transmit it to BPC in parallel.

The signal interface between BPC and the Decoder Controller is in Table 3.8. The type of the decoded frame is indicated by "frame\_type\_receive" signal. It is valid when "decode\_ok" signal is set.

BPC writes the data array extracted from "decoder\_output" to DBM. After that,

it reads this data array from DBM and writes it on the PORTB of the dual port memory of the application layer.

Firstly, BPC puts the Application Layer Memory address to write the data on "addrb" and sets "wenb" signal to enable writing. Then, it puts the data on "dinb" in order to write them.

Table 3.7: Signal interface between Decoder Controller and the Line Decoder.

| Port          | Width | Description T                                        |    |

|---------------|-------|------------------------------------------------------|----|

| data_ok       | 1     | '1': Bit decoding is valid ,'0': Bit decoding is in- | PI |

|               |       | valid                                                |    |

| message_error | PS    | Message error signal, VALID: During frame decod-     | PS |

|               |       | ing                                                  |    |

| output_data   | 1     | Decoded output signal, VALID: During frame de-       |    |

|               |       | coding                                               |    |

Table 3.8: Signal interface between BPC and the Decoder Controller.

| Port               | Width | Description                                         | Туре |

|--------------------|-------|-----------------------------------------------------|------|

| decoder_output     | PS    | Output signal for Decoder Controller, VALID: Af-    | PI   |

|                    |       | ter frame decoding                                  |      |

| message_error      | PS    | Error signal for Decoder Controller, VALID: After   | PS   |

|                    |       | frame decoding                                      |      |

| frame_type_receive | PS    | Decoded frame type, VALID: After frame decoding     | PS   |

| decode_ok          | 1     | '1': Decoding is finished, '0': Decoding is contin- |      |

|                    |       | ued                                                 |      |

During frame transmission, the transmitter unit can also read the bus to compare whether the sent bit and the read bit are the same or not. Furthermore, during the frame reception, any receiver unit that correctly receives a message can send an acknowledgment bit. In that case, the transmitter unit checks for the presence of this bit at the end of the frame transmission.

Therefore, there is a signal interface between Encoder Controller and Decoder Controller in UNIBUS architecture as shown in Table 3.9. These bit error and acknowledgment bit checking are PS functions. Table 3.9: Signal interface between the Encoder Controller and the Decoder Controller.

| Port        | Width | Description                                  | Туре |

|-------------|-------|----------------------------------------------|------|

| ack_control | PS    | Acknowledgment and bit error control signal, | PS   |

|             |       | VALID: During frame encoding and decoding    |      |

## **CHAPTER 4**

# IMPLEMENTATION AND EVALUATION OF SELECTED BUS PROTOCOLS WITH UNIBUS

#### 4.1 Design and Implementation

In this Section we implement a number of different serial bus protocols for different applications to demonstrate the use of UNIBUS framework. We choose to implement MIL-STD-1553B bus protocol [3], [12], [19], [6], ARINC-708 bus protocol, ARINC-717 bus protocol [13], [2], CAN bus protocol [26], [5], [10], [27] and UART protocol [33], [14], [15]. Table 4.1 presents a comparative overview of these protocols.

It can be seen in the comparison table that usage areas for these protocols are different. MIL-STD-1553B protocol is used in military applications and ARINC-708 bus protocol is used in radar systems whereas ARINC-717 bus protocol is used in data acquisition and recording systems, CAN bus is used in vehicle applications and UART protocol is the serial communications subsystem of a computer. Consequently, their basic protocol parameters such as bit rate, frame length, data bits per word, message length, message formats, coding type, checksum, synchronization type, operation and terminal are different than each other.

In this section, we provide detailed implementations, which fully demonstrate the features of our proposed generic hardware framework, of these five protocols.

All of the protocols are compiled on FPGA by ISE 14.5 [23] software, and simulated by MODELSIM simulation tool [31]. Furthermore, bus controller terminal of the MIL-STD-1553B bus protocol is fully implemented on a hardware platform.

Table 4.1: Comparison table of the implemented bus protocols.

|                       | MIL-STD-1553B        | ARINC-708     | ARINC-717     | CAN                  | UART          |

|-----------------------|----------------------|---------------|---------------|----------------------|---------------|

| Application           | Military specifica-  | Airborne      | Flight data   | In-vehicle           | Serial-       |

|                       | tion. Digital Time   | weather       | acquisi-      | commu-               | parallel      |

|                       | Division Com-        | radar sys-    | tion and      | nication,            | conversion    |

|                       | mand/Response        | tems          | recording     | control and          | with config-  |

|                       | Multiplexed Data     |               | systems       | automation           | urable data   |

|                       | Bus                  |               |               | systems              | format and    |

|                       |                      |               |               |                      | transmission  |

|                       |                      |               |               |                      | speeds.       |

| Terminal Types        | Bus Controller, Re-  | Transceiver   | Transceiver   | Transceiver          | Transceiver   |

|                       | mote Terminal, Bus   |               |               |                      |               |

|                       | Monitor              |               |               |                      |               |

| Operation             | Asynchronous         | Asynchronous  | Asynchronous  | Synchronous          | Asynchronous  |

| Baud Rate             | 1 MHz                | 1 MHz         | 768           | 20KHz to             | Depends on    |

|                       |                      |               | Hz(nominal    | 1MHz                 | UART model    |

|                       | 2011                 | 160611        | rate)         | 100                  | 101:          |

| Frame length          | 20 bits              | 1606 bits     | 768 bits      | Max. 108             | Max. 12 bits  |

| Data hita nan         | 16 bits              | 1600 bits     | 12 bits       | bits<br>Max. 64 bits | 5 to 8 bits   |

| Data bits per<br>word | 10 DIIS              | 1000 bits     | 12 DIIS       | Max. 64 dits         | 5 to 8 bits   |

| Application           | Max. of 32 data-     | 1 frame       | 1 frame (128, | 1 frame              | 1 frame       |

| Message               | words + command-     | 1 france      | 256, and 512  | (data, re-           | 1 munic       |

| Length                | word + synchro-      |               | 12-bit words  | mote, error,         |               |

|                       | nization bits        |               | per second)   | overload)            |               |

| Message Types         | - Bus Controller to  | - Transmit, - | - Transmit, - | - Transmit, -        | - Transmit, - |

|                       | RT, - RT to bus con- | Receive       | Receive       | Receive              | Receive       |

|                       | troller, - RT to RT, |               |               |                      |               |

|                       | - Broadcast, - Sys-  |               |               |                      |               |

|                       | tem Control          |               |               |                      |               |

| Coding type           | Manchester II bi-    | Manchester    | Harvard       | Non Return           | Non Return    |

|                       | phase                | II bi-phase   | bi-phase      | to Zero with         | to Zero       |

|                       |                      |               |               | bit stuffing         |               |

| Checksum              | Parity               | Parity        | None          | CRC                  | Parity        |

| Synchronization       | 3 synchronization    | 6 synchro-    | 4 synchro-    | Start of             | Start of      |

| type                  | bits                 | nization      | nization      | frame                | frame         |

|                       |                      | bits          | words         |                      |               |

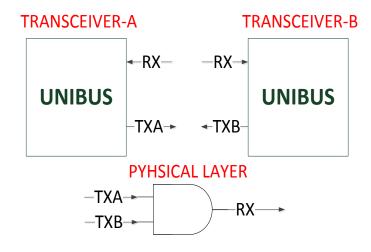

UNIBUS is used for both transmitter and receiver models for all protocols. Both data transmission and data reception are simulated for all protocols using separate transmitter and receiver implementations. A bus controller terminal for MIL-STD-1553B is implemented and verified by communicating with a commercial MIL-STD-1553B chip that is used as a remote terminal.

The block diagram for the simulation of MIL-STD-1553B, UART, ARINC-708, and

#### ARINC-717 bus protocols is shown in Fig. 4.1.

Figure 4.1: Block diagram for the simulation of the MIL-STD-1553B, UART, ARINC-708, and ARINC-717 bus protocols.

The nondestructive bitwise arbitration is used in the CAN protocol. Accordingly, if just one node drives logic low(dominant bit) to the bus, the whole bus is at logic low regardless of the transmitted logic high signals(recessive bit). This process is also realized for our simulation process by using an AND gate between the outputs of the node A and node B. By means of this AND gate logical 0 becomes a dominant bit and logical 1 becomes a recessive bit. The block diagram of the simulation model of the CAN bus protocol is shown in Fig. 4.2.

Figure 4.2: Block diagram for the simulation of the CAN bus protocol.

#### 4.1.1 CAN Bus

The CAN bus [26],[5],[10],[27] is a broadcast type of bus and it works as a multimaster system. This means that all nodes can hear all transmissions. CAN protocol defines four different message types which are data frame, remote frame, error frame, and overload frame. Data frame is used to send data information from a source to multiple receivers. Remote frame is used to request the transmission of data information from a remote node. Error frame is used to indicate the detected errors and overload frame is used to request an additional time delay.

We implement two CAN nodes Node A and Node B. These nodes send and receive data frame and remote frames in our simulation. Firstly, node A block sends a remote frame to the node B. After reception process, node B sends corresponding data frame to node A. Nodes listen to the bus as they transmit. Bit error is detected when the bit value that is sent is different from the bit value that is monitored. In addition, acknowledgment error is also detected by a transmitter if a recessive bit (logical 1) is found on the acknowledgment slot of the message frame. CRC error is detected if the CRC computed by the receiver differs from the one stored in the received frame.

According to the CAN protocol, each bit time consists of segments for synchronization. These segments are called Synchronization, Propagation, Phase 1 and Phase 2. Synchronization Segment is used for synchronization of the clocks, and it has one quantum. Propagation Segment compensates the delay in the data bus. Phase 1 segment can be shortened, and Phase 2 segment can be extended to keep the clocks in synchronization. The sample point facilitates continuous synchronization, and it is between Phase 1 segment and Phase 2 segment.

In our simulation model, bit time is divided into ten equal time quanta: one quantum is for synchronization segment, three quanta are for propagation segment, three quanta are for Phase 1 segment and three quanta are for Phase 2 segment. Therefore, receiver samples incoming data bit on the 70% of the bit time.

In this implementation, only two types of frames called as remote frame and data frame were realized during the data transmission and data reception processes. The other defined frames for CAN protocol called as error frame and overload frame will

be implemented as a future work. On the other hand, three types of errors such as CRC error, acknowledgment error, and bit error were checked during the error management process. The other defined errors called as form error and stuff error will be checked as a future work.

#### 4.1.2 UART

UART [33], [14], [15] is used for serial communications with configurable data format and baud rates. It is widely used for communicating to peripheral devices.

Each UART frame begins with a logic low start bit. After the start bit, the data bits (5 to 8 bits, Least Significant Bit (LSB) first) are sent followed by an optional parity bit to be used by the receiver for parity error checking. Lastly, stop bits are sent to indicate the end of transmission.

Because of the asynchronous transmission process of the UART protocol, the transmitter and receiver must agree on protocol parameters (Baud Rate, character length, parity, and stop bits).

According to the UART protocol, a clock signal, which runs at much faster rate than the baud rate, should be used to control the operation of the UART hardware. The receiver looks for the beginning of the start bit by testing the state of the incoming signal. A valid start bit is detected with a high to low voltage transition on the bus line. After waiting for a bit time, the receiver samples the bus line and clocks the result into the shift register.

In [62], [64], [38],and [50] a frequency equal to 16 times of the baud rate is used as a reference clock for their UART designs. However, in our simulation model, we choose the baud rate as 1 Mbps and the UART module has an internal clock (100 MHz) that runs 100 times faster than the baud rate. By means of this clock, the UART receiver samples the incoming data with the sampling rate of 100. This causes greater immunity against baud rate error.

UART protocol works as a transceiver. Therefore, We implement two UART nodes Node A and Node B as transceivers and test transmit and receive messages in the simulation.

Firstly, message is sent by Node A and then it is received by Node B terminal. After that, received message is sent by Node B and then it is received by Node A.

In this implementation, UART protocol was completely simulated by implementing both data transmission and data reception processes. In addition, parity error checking process was also realized for both processes. A hardware implementation of this protocol will be realized as a future work.

#### 4.1.3 ARINC-708 and ARINC-717

Only data frame is defined for both ARINC-708 and ARINC-717 [13],[2] protocols. Data frame is 1600 bits long and baud rate is 1 MHz for ARINC-708. Each frame starts with a 3 us sync pattern (1.5 us high, 1.5 us low) and ends with another 3 us sync pattern (1.5 us low, 1.5 us high). Therefore, a complete frame takes 1606 us. On the other hand, data frame is 768 bits long and bit rate is 768 Bps for ARINC-717. This consists of 64 words(12 bits length). Complete frame has four subframes (one subframe per second) because of that reason it takes 4 s. The first word in each subframe provides a synchronization pattern for this protocol.

These bus protocols also work as a transceiver. It means that, terminals can either transmit or receive messages. Because of that reason, during the simulation process both transmit and receive messages are tested. Firstly, message is sent by transceiver A terminal and then it is received by the transceiver B terminal. After that, received message is sent by transceiver B terminal and then it is received A terminal and then it is received B terminal.

In this implementation, ARINC-708 and ARINC-717 protocols were completely simulated by implementing both data transmission and data reception processes. In addition, parity error checking process was also realized for both protocols. A hardware implementation of these protocol will be realized as a future work.

#### 4.1.4 MIL-STD-1553B

In the scope of this thesis, we fully implement MIL-STD-1553B protocol using UNIBUS architecture. To this end the hardware design is carried out according to the UNIBUS block definitions and signal interfaces. Then the design is implemented on Xilinx SPARTAN3-XC3S4000-4FG900 [25] FPGA device.

We select MIL-STD-1553B for full implementation as it is both a widely used and complicated protocol with many different message types.

MIL-STD-1553B is one of the oldest and the most common serial data bus used in avionic systems. It is used in various military, avionics and aerospace systems for last four decades because of its robust performance, high level of reliability and fault tolerance in harsh environments.

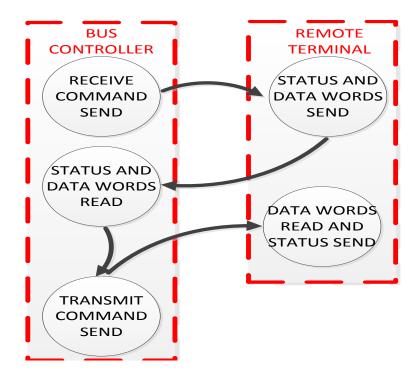

There are two node types for MIL-STD-1553B which are called bus controller and remote terminal (RT) [3], [12],[19],[6]. The bus controller works as a master and issues commands, which are for the transfer of data or the control and management of the bus, onto the data bus. The remote terminal works as a slave. We implement the bus controller using UNIBUS.

There are two types of message transfer formats which are Information transfer format and broadcast information transfer format. Six message types which are bus controller to RT transfer, RT to bus controller transfer, RT to RT transfer, mode command without data word, mode command with data word (transmit) and mode command with data word (receive) are defined for information transfer format. Four message types such as bus controller to RT(s) broadcast, RT to RT(s) broadcast, mode command without data word and mode command with data word (receive) are defined for the broadcast information transfer format.

For all message types, firstly the bus controller sends a command word to the bus to indicate the data flow and then corresponding remote terminal responds this command word by sending status or data words. If the command word sent by bus controller corresponds to the transmit command, bus controller block sends data words to the remote terminal. After that, remote terminal sends status word to the bus controller. If the command word sent by bus controller corresponds to the receive command, remote terminal sends data and status words. Because of that reason, both bus controller and remote terminal blocks are designed as transceiver blocks in our simulation.

In this implementation, MIL-STD-1553B bus protocol was completely simulated. All of the defined message types and error checking processes were realized during the data transmission and data reception processes. Detailed error management process for the validation test of this protocol will be implemented as a future work.

#### 4.1.5 Summary and Overview of Signal Interfaces

Serial bus protocols have similar functionality such as bit encoding, bit decoding, error detection, addressing, arbitration, data stream control and frame generation. However, the content of these functions differ from one protocol to another. Therefore, PS signal interface is used between the sub-blocks of the UNIBUS architecture to provide generic signal interface for all serial bus protocols.

In this Section, we demonstrate the versatility of UNIBUS in Table 4.2, Table 4.3 and Table 4.4 by listing the signal interfaces of the different serial protocols that we implement. We indicate the PS signal widths as well as their functions.

## 4.1.6 MIL-STD-1553B Hardware Realization

The simulated model for the MIL-STD-1553B bus controller is further implemented on FPGA. We present the hardware block diagram of the implementation and the test bench in Fig. 4.3.

The implementation platform contains an FPGA, a Digital Signal Processor (DSP), a PROM to keep the FPGA code, a flash memory to store non-volatile data for DSP, a remote terminal chip for MIL-STD-1553B bus protocol, an ethernet interface to provide a monitor interface, physical layers for MIL-STD-1553B bus and ethernet port and power converters to produce the different voltage levels required by the FPGA and the DSP.