## PERFORMANCE AND THERMAL RELIABILITY COMPARISONS OF 2-LEVEL AND 3-LEVEL NPC VOLTAGE SOURCE INVERTERS FOR ELECTRIC VEHICLE DRIVE APPLICATIONS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

# ALİCAN MADAN

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2019

### Approval of the thesis:

## PERFORMANCE AND THERMAL RELIABILITY COMPARISONS OF 2-LEVEL AND 3-LEVEL NPC VOLTAGE SOURCE INVERTERS FOR ELECTRIC VEHICLE DRIVE APPLICATIONS

submitted by ALİCAN MADAN in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Halil Kalıpçılar<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>   |            |

|----------------------------------------------------------------------------------------------|------------|

| Prof. Dr. İlkay Ulusoy<br>Head of Department, <b>Electrical and Electronics Engineering</b>  |            |

| Assist. Prof. Dr. Emine Bostancı<br>Supervisor, Electrical and Electronics Engineering, METU |            |

|                                                                                              |            |

|                                                                                              |            |

| Examining Committee Members:                                                                 |            |

| Prof. Dr. Işık Çadırcı<br>Electrical and Electronics Engineering, Hacettepe Uni.             |            |

| Assist. Prof. Dr. Emine Bostancı<br>Electrical and Electronics Engineering, METU             |            |

| Assoc. Prof. Dr. Murat Göl<br>Electrical and Electronics Engineering, METU                   |            |

| Assist. Prof. Dr. Ozan Keysan<br>Electrical and Electronics Engineering, METU                |            |

| Assist. Prof. Dr. Taner Göktaş<br>Electrical and Electronics Engineering, İnönü Uni.         |            |

| Date:                                                                                        | 09.09.2019 |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Surname: Alican Madan

Signature :

#### ABSTRACT

### PERFORMANCE AND THERMAL RELIABILITY COMPARISONS OF 2-LEVEL AND 3-LEVEL NPC VOLTAGE SOURCE INVERTERS FOR ELECTRIC VEHICLE DRIVE APPLICATIONS

Madan, Alican M.S., Department of Electrical and Electronics Engineering Supervisor: Assist. Prof. Dr. Emine Bostancı

September 2019, 101 pages

Two-level and multilevel inverters are widely used in electric vehicle drive applications with different switching techniques. Selection of the topology and the switching technique for electric vehicle drives are getting more important with the trend of designing more compact and more efficient drive circuitry. Reliability of semiconductors in power electronics are under investigation in recent years as well. In this thesis, a multidimensional comparison of two common topologies for a 120 kW electric vehicle PMSM (Permanent Magnet Synchronous Machine) drive system is conducted. Two-level topology and three-level NPC (Neutral Point Clamped) type voltage source inverters are compared in terms of output voltage and current quality, thermal performance, efficiency, switching frequency limitation and semiconductor thermal reliability aspects. Also SPWM (Sinusoidal Pulse Width Modulation) and SVPWM (Space Vector Pulse Width Modulation) techniques are under investigation.

Keywords: Two-level Voltage Source Inverter, Three-Level NPC Type Voltage Source

Inverter, Semiconductor Thermal Reliability, Electric Vehicle Traction System, Thermal Analysis

## ELEKTRİKLİ ARAÇ MOTOR SÜRÜCÜ UYGULAMALARI İÇİN 2-DÜZEY VE 3-DÜZEY NÖTR KENETLEMELİ GERİLİM BESLEMELİ EVİRİCİLERİN PERFORMANS VE ISIL GÜVENİLİRLİK AÇISINDAN KARŞILAŞTIRILMASI

Madan, Alican Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Dr. Öğr. Üyesi. Emine Bostancı

Eylül 2019, 101 sayfa

Farklı anahtarlama tekniklerine sahip iki seviyeli ve çok seviyeli eviriciler, elektrikli araç tahrik uygulamalarında yaygın olarak kullanılmaktadırlar. Elektrikli araç motor sürücü sistemleri için topoloji seçimi ve anahtarlama teknikleri, daha kompakt ve daha verimli tahrik devreleri tasarlama eğilimiyle daha da önem kazanmaktadır. Yarı iletkenlerin güç elektroniğinde ısıl güvenilirliği de son yıllarda incelenmektedir. Bu tez çalışmasında, elektrikli araçlarda kullanılacak 120 kW sabit mıknatıslı senkron motor sürücü devresi için iki yaygın topolojinin çok boyutlu bir karşılaştırması yapılmaktadır. İki seviyeli topoloji ve üç seviyeli nötr nokta kenetli tip gerilim beslemeli evirici çıkış gerilim ve akım kalitesi, ısıl performans, verimlilik, anahtarlama frekansı sınırlaması ve yarı iletken ısıl güvenilirliği açısından karşılaştırılmıştır. Ayrıca sinüzoidal darbe genişliği modülasyonu ve uzay vektör darbe genişliği modülasyonu teknikleri incelenmektedir.

Anahtar Kelimeler: İki Seviyeli Gerilim Beslemeli Evirici, Üç Seviyeli Nötr Nokta Kenetli Gerilim Beslemeli Evirici, Yarıiletken Isıl Güvenilirliği, Elektrikli Araç Çekiş Sistemi, Isıl Analiz To my family

#### ACKNOWLEDGMENTS

First, I would like to express my deepest gratitude to my supervisor Assist. Prof. Dr. Emine Bostancı, for her guidance and support throughout this study. Her endless positive energy was not only the source of encouragement for this study but also an inspiration for life.

Besides, I would like to thank to the members of the examining committee: Prof. Dr. Işık Çadırcı, Assoc. Prof. Dr. Murat Göl, Assist. Prof. Dr. Ozan Keysan and Assist. Prof. Dr. Taner Göktaş for their valuable comments. I would also like to thank to Prof. Dr. Ahmet M. Hava not only for his valuable contribution during my thesis study but also for being great inspiration for my engineering career.

I would also like to thank to Elsis A.Ş. for their support throughout the study. The company shareholders Behçet Tonak and Pekin Tonak's encouragement was invaluable throughout the study.

I would like to thank to Oğuzhan Öztoprak, Merih Eren and Arın Cengiz for all beneficial technical discussions during this study.

I would like to thank to my mother Nevin Madan, my father Ahmet Madan, my sister Ekin Madan and my grandmother Perihan Özcan for their endless belief in me. I am really grateful for their love.

Finally, I am grateful for love of my life Özge Karaman Madan for her endless support in every part of my life. Without her deepest love and support, this study would not have been possible. I am very excited to set sail for new horizons with her.

# TABLE OF CONTENTS

| ABSTRACT                                                             | V  |

|----------------------------------------------------------------------|----|

| ÖZ                                                                   | ii |

| ACKNOWLEDGMENTS                                                      | X  |

| TABLE OF CONTENTS    x                                               | i  |

| LIST OF TABLES                                                       | V  |

| LIST OF FIGURES                                                      | 'n |

| LIST OF ABBREVIATIONS                                                | X  |

| CHAPTERS                                                             |    |

| 1 INTRODUCTION                                                       | 1  |

| 1.1 Scope of the Thesis                                              | 3  |

| 1.2 Thesis Outline                                                   | 4  |

| 2 STATE OF ART ELECTRIC DRIVES IN VEHICLE TRACTION APPLI-<br>CATIONS | 5  |

| 2.1 Electric Drive Technologies                                      | 5  |

| 2.2 Voltage Source Inverter Topologies and Applications              | 8  |

| 2.3 Modulation Techniques                                            | 9  |

| 3 TWO LEVEL AND THREE LEVEL NPC TYPE VOLTAGE SOURCE IN-<br>VERTERS 1 | 3  |

| 3.1 Two-level Voltage Source Inverter                                | 3  |

|   | 3.1   | .1 Modulation Techniques                                                        | 14 |

|---|-------|---------------------------------------------------------------------------------|----|

|   | 3.2 T | Three-level NPC Type Voltage Source Inverter                                    | 20 |

|   | 3.2.  | .1 Modulation Techniques                                                        | 21 |

|   |       | Design, Analysis and Implementation of a 750 W Three-Level NPC<br>Type Inverter | 25 |

|   | 3.3   | .1 Design                                                                       | 25 |

|   | 3.3.  | .2 Test Results                                                                 | 29 |

| 4 | SEMIC | ONDUCTOR LOSSES AND THERMAL MODELLING                                           | 37 |

|   | 4.1 S | Semiconductor Losses                                                            | 37 |

|   | 4.1   | .1 IGBT Losses                                                                  | 38 |

|   | 4.1   | .2 Diode Losses                                                                 | 39 |

|   | 4.2 7 | Thermal Modeling                                                                | 40 |

|   | 4.2.  | .1 Thermal Equivalent Circuit Models                                            | 41 |

| 5 |       | DIMENSIONAL COMPARISON OF A 120 KW ELECTRIC VE-<br>DRIVE                        | 45 |

|   | 5.1 F | PMSM Fundamentals                                                               | 46 |

|   | 5.2 S | Semiconductor Module Selection                                                  | 47 |

|   | 5.3 E | Electrical Performance Comparison                                               | 50 |

|   | 5.4 E | Efficiency and Thermal Performance Comparison                                   | 51 |

|   | 5.5 0 | Common Mode Voltage Comparison                                                  | 55 |

|   | 5.6 0 | Conclusion                                                                      | 58 |

| 6 | THERN | AAL RELIABILITY                                                                 | 61 |

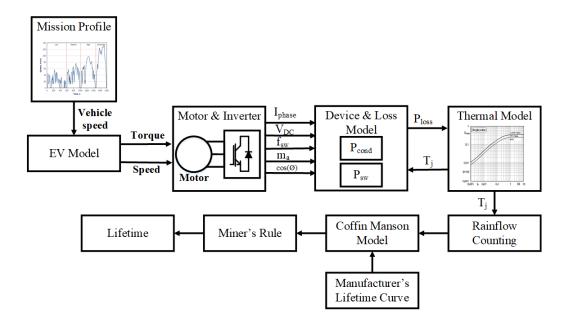

|   | 6.1 N | Method Overview                                                                 | 64 |

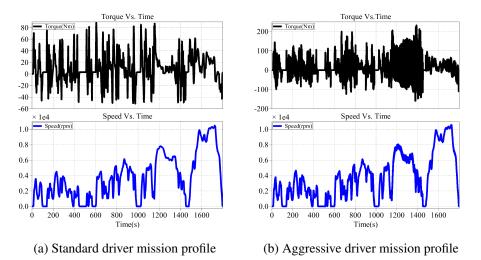

|   | 6.1   | .1 Mission Profiles                                                             | 65 |

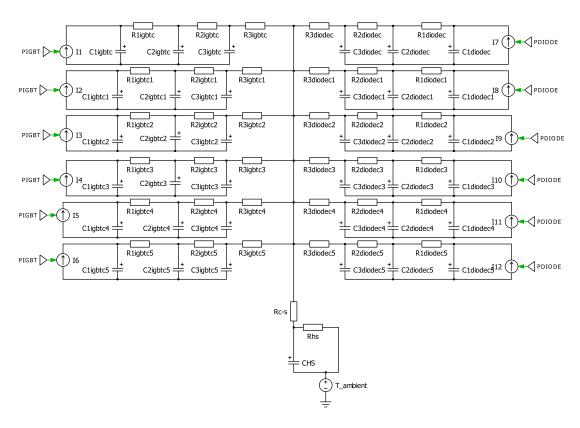

|      | 6.1.2   | Electro-thermal Model of Inverter | 66 |

|------|---------|-----------------------------------|----|

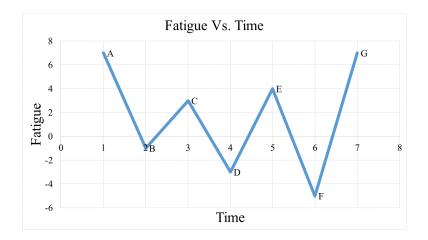

|      | 6.1.3   | Rainflow Counting Algorithm       | 68 |

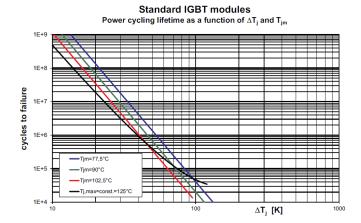

|      | 6.1.4   | Coffin Manson Law                 | 69 |

|      | 6.1.5   | Miner's Rule                      | 70 |

| 6.2  | 2 Therr | nal Reliability Results           | 71 |

| 6.3  | 3 Conc  | lusion                            | 78 |

| 7 CC | NCLUSI  | ON                                | 79 |

| REFE | RENCES  |                                   | 81 |

| APPE | NDICES  |                                   |    |

| A TH | REE-LE  | VEL NPC SVPWM GATE SIGNALS        | 89 |

# LIST OF TABLES

# TABLES

| Table 2.1 | Motor drive performances of commercial products [1]                            | 6  |

|-----------|--------------------------------------------------------------------------------|----|

| Table 3.1 | Switch logic for corresponding space vectors                                   | 15 |

| Table 3.2 | Regions and positions of reference vector                                      | 16 |

| Table 3.3 | Calculated times and regions in two-level topology                             | 17 |

| Table 3.4 | Switch pattern and node voltage in one leg                                     | 21 |

| Table 3.5 | Symbols, corresponding switch states and phase voltages                        | 23 |

| Table 3.6 | Calculated times and sub-sectors in three-level                                | 25 |

| Table 3.7 | Hardware test parameters                                                       | 30 |

| Table 4.1 | Thermal and electrical analogy                                                 | 41 |

| Table 5.1 | Selected modules                                                               | 47 |

| Table 5.2 | PMSM and inverter parameters                                                   | 48 |

| Table 6.1 | Cycles that cause damage from the fatigue profile                              | 69 |

| Table 6.2 | Thermal model parameters of SKiiP39GB12E4V1                                    | 72 |

| Table 6.3 | Thermal model parameters of SkiM401MLI07E4                                     | 72 |

|           | Lifetime of IGBT and diode with different mission profiles in two-<br>topology | 76 |

| Table 6.5 | Lifetime of IG | BT an | d dioc | le wit | h dif | ferent | missio | n prof | iles i | n thi | ree- |    |

|-----------|----------------|-------|--------|--------|-------|--------|--------|--------|--------|-------|------|----|

| level     | NPC topology   |       |        |        |       |        |        |        |        |       |      | 77 |

# LIST OF FIGURES

# FIGURES

| Figure 2.1  | One phase leg of inverter with two-level, three-level and n-level |    |

|-------------|-------------------------------------------------------------------|----|

| node        | voltages [2]                                                      | 8  |

| Figure 2.2  | Switching techniques for multilevel inverters [3]                 | 9  |

| Figure 2.3  | Scalar PWM carrier signals of a 5-level VSI                       | 11 |

| Figure 3.1  | Two-level topology                                                | 13 |

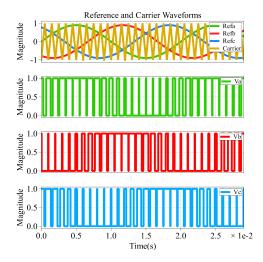

| Figure 3.2  | Reference and carrier waveforms for two-level SPWM                | 14 |

| Figure 3.3  | Two-level space vectors                                           | 18 |

| Figure 3.4  | Switching patterns and on times for each region                   | 19 |

| Figure 3.5  | Three-level NPC topology                                          | 20 |

| Figure 3.6  | Three-level SPWM phase A switching signals                        | 22 |

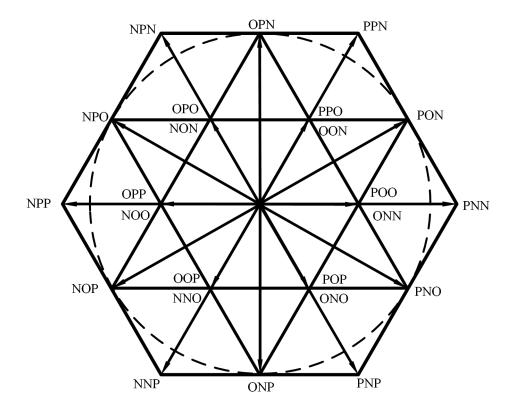

| Figure 3.7  | Three-level space vectors                                         | 23 |

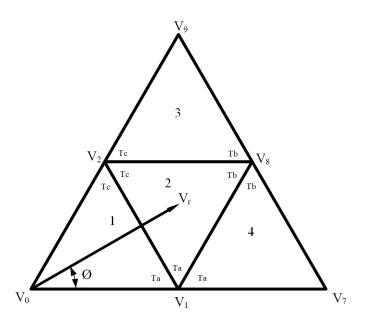

| Figure 3.8  | Sub-sectors in three-level SVPWM                                  | 24 |

| Figure 3.9  | F28379D experimenter kit                                          | 26 |

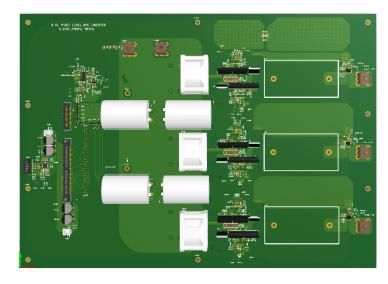

| Figure 3.10 | Top view of PCB                                                   | 29 |

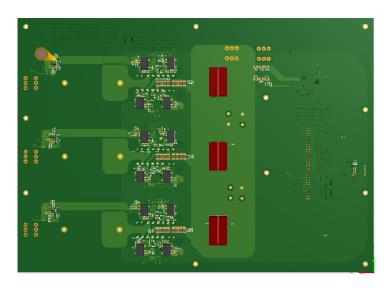

| Figure 3.11 | Bottom view of PCB                                                | 29 |

| Figure 3.12 | Test setup circuitry                                              | 30 |

| Figure 3.13 | Test setup                                                        | 31 |

| Figure 3.14<br>160Ω      | Phase current waveform and harmonic spectrum with $R_{load} =$<br>and $m_a = 0.6$          |

|--------------------------|--------------------------------------------------------------------------------------------|

| Figure 3.15<br>80Ω a     | Phase current waveform and harmonic spectrum with $R_{load} =$<br>and $m_a = 0.6 \dots 33$ |

| Figure 3.16<br>53Ω a     | Phase current waveform and harmonic spectrum with $R_{load} =$<br>and $m_a = 0.6 \dots 33$ |

| Figure 3.17<br>160Ω      | Phase current waveform and harmonic spectrum with $R_{load} =$<br>and $m_a = 0.8 \dots 34$ |

| Figure 3.18<br>80Ω a     | Phase current waveform and harmonic spectrum with $R_{load} =$<br>and $m_a = 0.8 \dots 34$ |

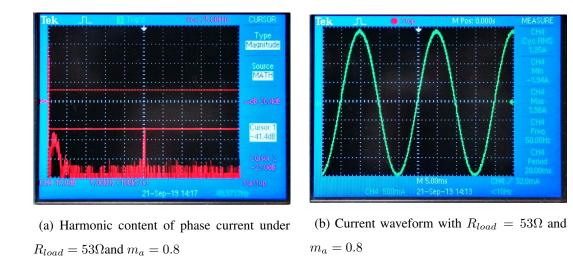

| Figure 3.19 $53\Omega$ a | Phase current waveform and harmonic spectrum with $R_{load} =$<br>and $m_a = 0.8 \dots 35$ |

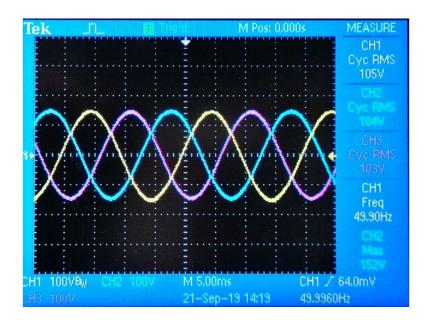

| Figure 3.20              | Line to line voltages of resistor bank with $m_a=0.6$ and $R_{load}=53\Omega$ 35           |

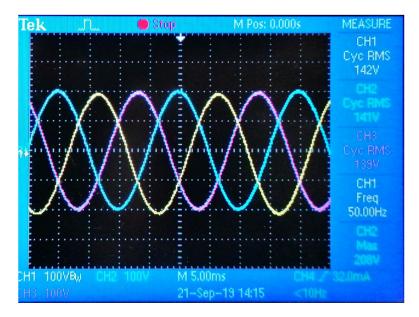

| Figure 3.21              | Line to line voltages of resistor bank with $m_a=0.8$ and $R_{load}=53\Omega$ 36           |

| Figure 3.22              | Drain-source voltage of MOSFET with 300 V DC bus 36                                        |

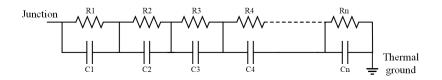

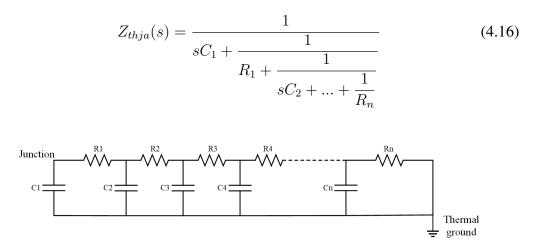

| Figure 4.1               | Foster model representation                                                                |

| Figure 4.2               | Cauer model representation                                                                 |

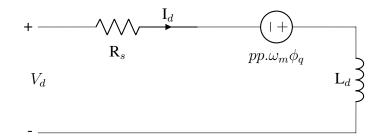

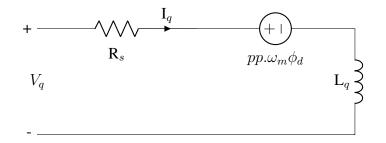

| Figure 5.1               | d axis equivalent circuit of PMSM 46                                                       |

| Figure 5.2               | q axis equivalent circuit of PMSM                                                          |

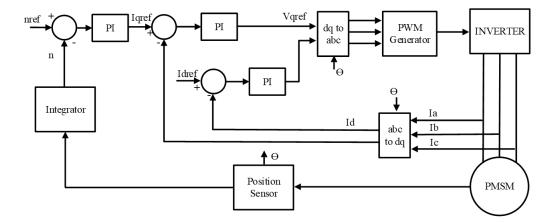

| Figure 5.3               | FOC block diagram                                                                          |

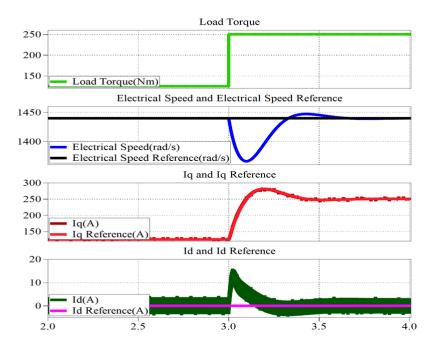

| Figure 5.4               | Step response of controller                                                                |

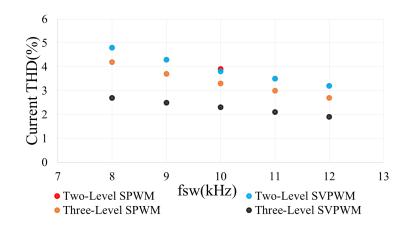

| Figure 5.5               | Current THD (%) vs. switching frequency at 2291 rpm 51                                     |

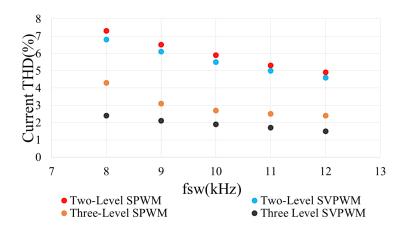

| Figure 5.6               | Current THD (%) vs. switching frequency at 4583 rpm 51                                     |

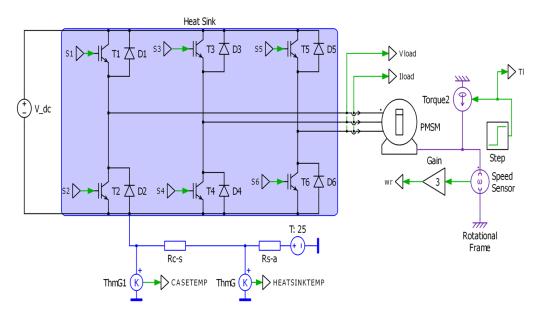

| Figure 5.7  | Two-level topology electro-thermal model                        | 52 |

|-------------|-----------------------------------------------------------------|----|

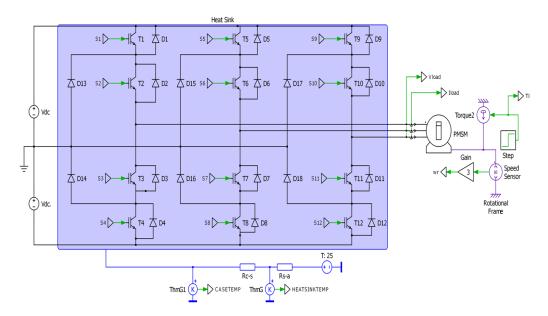

| Figure 5.8  | Three-level NPC topology electro-thermal model                  | 53 |

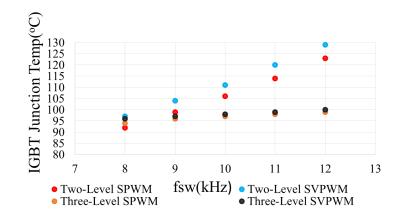

| Figure 5.9  | IGBT junction temperatures with different switching frequencies | 53 |

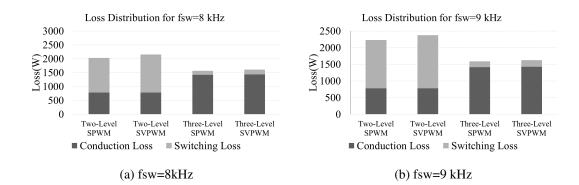

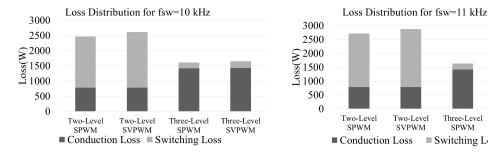

| Figure 5.10 | Loss distribution with different switching frequencies          | 54 |

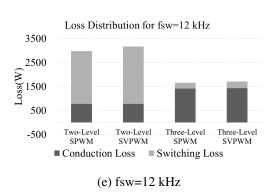

| Figure 5.11 | Two-level topology SPWM CMV and harmonic spectrum               | 56 |

| Figure 5.12 | Two-level topology SVPWM CMV and harmonic spectrum              | 56 |

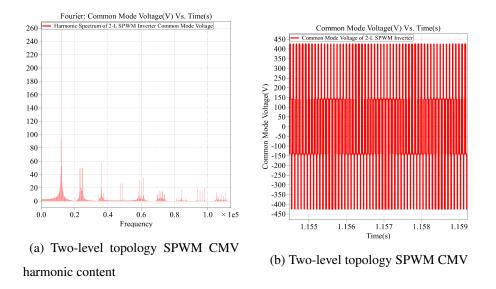

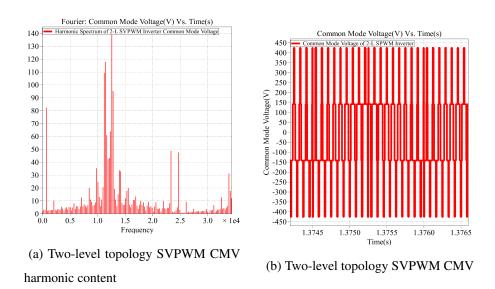

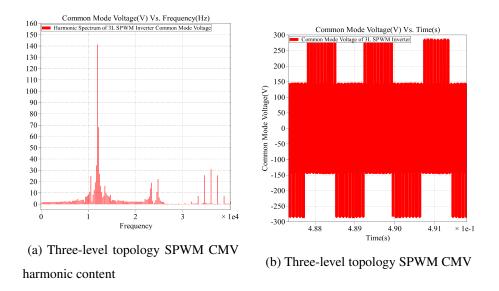

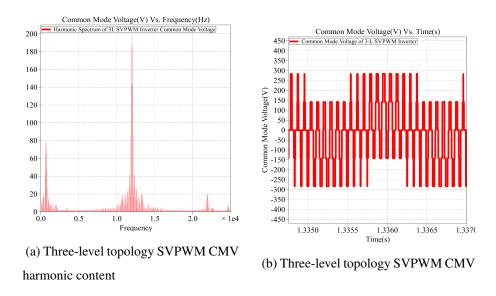

| Figure 5.13 | Three-level topology SPWM CMV and harmonic spectrum             | 57 |

| Figure 5.14 | Three-level topology SVPWM CMV and harmonic spectrum            | 57 |

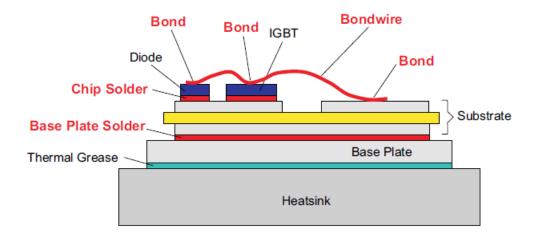

| Figure 6.1  | IGBT structral details [4]                                      | 63 |

| Figure 6.2  | Lifetime approach flowchart                                     | 64 |

| Figure 6.3  | Two different mission profile as drive cycle                    | 66 |

| Figure 6.4  | Two-level topology thermal model                                | 67 |

| Figure 6.5  | Example fatigue profile                                         | 68 |

| Figure 6.6  | Lifetime curve with different mean junction temperatures [4]    | 74 |

| Figure 6.7  | IGBT and diode temperatures of two-level topology               | 75 |

| Figure 6.8  | Three-levöel topology IGBT and diode temperatures               | 76 |

| Figure A.1  | Sector 1, sub-sector 1                                          | 89 |

| Figure A.2  | Sector 1, sub-sector 2                                          | 90 |

| Figure A.3  | Sector 1, sub-sector 3                                          | 90 |

| Figure A.4  | Sector 1, sub-sector 4                                          | 91 |

| Figure A.5  | Sector 2, sub-sector 1                                          | 91 |

| Figure A.6  | Sector 2, sub-sector 2                                          | 92 |

| Figure A.7  | Sector 2, sub-sector 3 | 92  |

|-------------|------------------------|-----|

| Figure A.8  | Sector 2, sub-sector 4 | 93  |

| Figure A.9  | Sector 3, sub-sector 1 | 93  |

| Figure A.10 | Sector 3, sub-sector 2 | 94  |

| Figure A.11 | Sector 3, sub-sector 3 | 94  |

| Figure A.12 | Sector 3, sub-sector 4 | 95  |

| Figure A.13 | Sector 4, sub-sector 1 | 95  |

| Figure A.14 | Sector 4, sub-sector 2 | 96  |

| Figure A.15 | Sector 4, sub-sector 3 | 96  |

| Figure A.16 | Sector 4, sub-sector 4 | 97  |

| Figure A.17 | Sector 5, sub-sector 1 | 97  |

| Figure A.18 | Sector 5, sub-sector 2 | 98  |

| Figure A.19 | Sector 5, sub-sector 3 | 98  |

| Figure A.20 | Sector 5, sub-sector 4 | 99  |

| Figure A.21 | Sector 6, sub-sector 1 | 99  |

| Figure A.22 | Sector 6, sub-sector 2 | .00 |

| Figure A.23 | Sector 6, sub-sector 3 | .00 |

| Figure A.24 | Sector 6, sub-sector 4 | 01  |

# LIST OF ABBREVIATIONS

# ABBREVIATIONS

| APOD    | Alternative Phase Opposition Disposition          |

|---------|---------------------------------------------------|

| BEV     | Battery Electric Vehicle                          |

| СМС     | Common Mode Current                               |

| CMV     | Common Mode Voltage                               |

| CTE     | Coefficient of Thermal Expansion                  |

| GaNFet  | Gallium Nitride Field Effect Transistor           |

| HVDC    | High Voltage Direct Current                       |

| IGBT    | Insulated Gate Bipolar Transistor                 |

| MMC     | Modular Multilevel Converter                      |

| MOSFET  | Metal Oxide Semiconductor Field Effect Transistor |

| NEDC    | New European Drive Cycle                          |

| NPC     | Nuetral Point Clamped                             |

| PD      | Phase Disposition                                 |

| PMSM    | Permanent Magnet Synchronous Motor                |

| POD     | Phase Opposition Disposition                      |

| PWM     | Pulse Width Modulation                            |

| RMS     | Root Mean Square                                  |

| SiC     | Silicon Carbide                                   |

| SPWM    | Sinusoidal Pulse Width Modulation                 |

| STATCOM | Static Synchronous Compensator                    |

| SVPWM   | Space Vector Pulse Width Modulation               |

| VSI     | Voltage Source Inverter                           |

WLTP World Harmonized Light Vehicle Test Procedure

### **CHAPTER 1**

#### **INTRODUCTION**

Hybrid electric vehicles, battery electric vehicles and fuel cell electric vehicles have been gaining popularity in recent times. There are many reasons behind this fact. One of them is environmental concerns. In 2009, 25% of the green house gas (GHG) emission was due to transportation sector [5]. Climate change and global warming have been reached a threatening level due to GHG emissions. In [6], it is stated that GHG emmission would be doubled if necessary precautions are not taken. Regarding this issue, integration of electric vehicles (EVs) into the transportation sector would decrease our dependency on fossil fuel based energy sources. EVs use more efficient power trains compared with internal combustion engine vehicles [7]. Also, EVs are able to improve energy security by diversifying energy sources. Especially, integration of EVs to the renewable energy sources are highly promising in order to picture a better near future. Besides, electric mobility will enable us to reshape and restructure our transportation.

Electric drive systems are one of the most important key components in an EV. Therefore, design of more compact, more efficient and more reliable electric drive systems is crucial. This thesis aims to contribute literature by investigating motor drive inverter of battery electric vehicle (BEV) in terms of getting more efficient and more reliable designs.

Two-level voltage source inverters (VSI) are the commercial converter type used in PMSM drives. As semiconductor switches, conventional Si IGBT and diode pairs are used for driving PMSMs in traction applications. However, in recent years, SiC MOSFETs and SiC diodes have been involved in the motor drive market to account for the need in higher switching frequency modulation [8]. As stated in [9], switch-

ing frequency should be at least 9-12 times of the maximum fundamental frequency. However, conventional Si IGBT diode pairs suffer from high switching losses in twolevel VSI topology. SiC MOSFET and Si based IGBT diode pair comparison is done for an 80 kW PMSM drive in [8]. Usage of SiC MOSFETs instead of Si IGBT results with 5 percent loss decrease in motor drive. SiC MOSFETs are now preferable with two-level topology due to their lower switching losses, which enables system operation at higher switching frequencies.

Three-level NPC topology is expected to be used at higher switching frequency operations with conventional Si IGBT diode pairs due to lower switching losses. The reasons are as follows: First, blocking voltage requirement of the main switch is halved in three-level topology. Second, switching losses do not linearly change with blocking voltage. An exponent of 1.3, 1.4 is used to calculate even in the same IGBT device [4]. That means switching losses are expected to drop below 50 percent in a 3-level topology, giving us the opportunity for increasing the switching frequency.

In the literature, advantages of three-level inverter over two-level inverter are discussed for PMSM drive applications. Three-level NPC and two-level topologies are compared in terms of output voltage THD, efficiency, and fault tolerance in [10] and in all aspects, three-level NPC topology found to have a superior performance. Similarly, three-level NPC topology is shown to be more compatible with PMSM drives in vehicle traction in terms of current THD, torque ripple, and lower switching losses aspects in [11]. Cost comparison between two-level and three-level topologies is done in [9], where it is shown that three-level NPC topology has a slightly higher initial cost. On the other hand, three-level topology results with a lower operational cost due to its higher efficiency. Although superior performance stated in the literature, manipulation of higher number of switches and floating capacitor balancing are main design challenges of the three-level NPC topology.

Considering the increase in DC bus voltage levels, topology selection is also getting as important as switch selection. Commercially available semiconductor switches have discrete steps of blocking voltage levels. In DC bus voltage levels around 700-900 V, switches with 1200 V voltage blocking capability are required in 2-level VSIs. At this point, semiconductor technologies with lower switching losses are the choice of the developers. On the other hand, a multi-level VSI may provide solution with conventional semiconductor switches thanks to lower turn-on and turn-off energies compared to two-level topologies.

#### **1.1** Scope of the Thesis

The most commonly used three-phase voltage source inverter topologies that are twolevel and three-level NPC type VSIs and switching techniques that are sinusoidal pulse width modulation (SPWM) and space vector pulse width modulation (SVPWM) are implemented and examined with the help of numeric analyses. Moreover, a small scale three-level NPC type inverter is implemented and hardware design steps as well as challenges in designing a three-level inverter are addressed.

Results of multidimensional comparisons of the topologies and the switching techniques that are mentioned above in terms of output quality, thermal performance and switching frequency limitations are provided for a 120 kW EV traction system.

Finally, two VSI topolgies are compared in terms of semiconductor thermal reliability point of view under two mission profiles representing two driver characteristics including the driver behavior in lifetime estimation is a novel contribution to the field.

The analyses presented in this study can be summarized as follows:

i. Studying basic principles of two-level and three-level NPC VSI topologies

ii. Building and testing a three-level NPC type inverter.

iii. Analyzing both topologies by means of electrical and thermal characteristics for an electric vehicle drive application

iv. Studying semiconductor losses and thermal modelling of selected topologies

v. Studying methodologies to estimate lifetime of topologies considering thermal reliability of semiconductors

### 1.2 Thesis Outline

Chapter 2 gives a brief information on trends in both electric machines and voltage source inverter topologies for electric vehicle drive applications. This chapter also includes a general literature review on the performance and reliability improvement of VSIs.

In Chapter 3, fundamentals of the selected VSI topologies and common modulation techniques are explained in details. Also, design steps of a 750 W three-level NPC type topology are discussed. Test results under different load conditions are presented.

In Chapter 4, semiconductor losses of VSIs with Si IGBTs and Si diodes are analyzed. For two-level and three-level NPC type topologies, losses of IGBTs and diodes are analyzed and mathematical approaches to calculate semiconductor losses are given. Additionally, the most common thermal models are explained with the help of electrical and thermal analogies.

In Chapter 5, electric drive system simulation models are constructed with two-level and three-level NPC type topologies. By the help of electro-thermal simulations, a multidimensional comparison of topologies for the same electric drive application is conducted. Semiconductor loss calculations defined in Chapter 4 are used in the electro-thermal simulations.

In Chapter 6, semiconductor thermal reliability fundamentals are discussed and the reasons of semiconductor failures due to thermal stresses are described briefly. Moreover, lifetime estimation methodology of a power semiconductor and flow-chart of lifetime estimation are explained in details. Semiconductor losses methodology defined in Chapter 4 is used to observe thermal stresses of semiconductors. Finally, VSI topologies are compared in terms of their estimated lifetimes for two different mission profiles.

In Chapter 7, a general conclusion is given and suggestions for future studies are included.

#### **CHAPTER 2**

# STATE OF ART ELECTRIC DRIVES IN VEHICLE TRACTION APPLICATIONS

#### 2.1 Electric Drive Technologies

Electric vehicles have been significantly improved in last decade. At first, hybrid and plug-in hybrid cars have been introduced besides conventional gasoline-based models. These improvements have been followed by battery electric vehicle (BEV) models. In the state of art, there are BEVs in the market with a range of more than 300 miles [12].

Power converters of electric vehicles have to comply with strict requirements because of space and weight limitations. Every part of electrical and mechanical system needs to be designed as compact and light as possible. A lighter weight results in reduced load, so faster acceleration and higher efficiency.

A review of commercial electric vehicle drive systems including electric machine and power electronics is given in [13]. Table 2.1 shows electric drive train of electrified vehicles that have a high market share. The values in the paranthesis represent only the inverter that is boost converters are excluded. In [1], it is stated that power density expectation of an electric vehicle system increases rapidly. Acording to US Department of Energy (DOE), 33 kW/L for a 100 kW traction drive system is estimated by 2025. It is an increment by a factor of 5.5 compared to the state of art. It can be inferred that in the near future electric vehicle drive systems will be much compacter than the today's commercial products.

| Parameter               | 2004   | 2007   | 2008   | 2010     | 2012 | 2014   | 2016 | 2017   |

|-------------------------|--------|--------|--------|----------|------|--------|------|--------|

| 1 arameter              |        |        |        |          |      |        |      |        |

|                         | Prius  | Camry  | Lexus  | Prius    | Leaf | Accord |      | Prius  |

|                         | (50    | (70    | (110   | (60      | (80  | (124   | i3   | (53    |

|                         | kW)    | kW)    | kW)    | kW)      | kW)  | kW)    | (125 | kW)    |

|                         |        |        |        |          |      |        | kW)  |        |

|                         |        |        | M      | otor     |      |        |      |        |

| Peak power              | 3.3    | 5.9    | 6.6    | 4.8      | 4.2  | 8.5    | 9.1  | 5.7    |

| density                 |        |        |        |          |      |        |      |        |

| (kW/L)                  |        |        |        |          |      |        |      |        |

| Peak spe-               | 1.1    | 1.7    | 2.5    | 1.6      | 1.4  | 2.9    | 3.0  | 1.7    |

| cific                   |        |        |        |          |      |        |      |        |

| power                   |        |        |        |          |      |        |      |        |

| (kW/kg)                 |        |        |        |          |      |        |      |        |

|                         |        |        | Inv    | erter    | 1    | II     |      |        |

| Peak power              | 4.5    | 7.4    | 10.6   | 5.9      | 5.7  | 12.1   | 18.5 | 11.5   |

| density                 | (7.4)  | (11.7) | (17.2) | (11.1)   |      | (18.5) |      | (21.7) |

| (kW/L)                  |        |        |        |          |      |        |      |        |

| Peak spe-               | 3.8    | 5.0    | 7.7    | 6.9      | 4.9  | 9.1    | 14.1 | 8.6    |

| cific                   | (6.2)  | (9.3)  | (14.9) | (16.7)   |      | (21.7) |      | (19.0) |

| power                   |        |        |        |          |      |        |      |        |

| (kW/kg)                 |        |        |        |          |      |        |      |        |

|                         |        |        | Specif | ications | -    |        |      |        |

| DC Voltage              | 500    | 650    | 650    | 650      | 375  | 700    | 355  | 600    |

| Current                 | 225    | 282    | 304    | 170      | 442  | 300    | 375  | 160    |

| (Arms)                  |        |        |        |          |      |        |      |        |

| Number of               | 12     | 18     | 12     | 12       | 18   | 12     | 24   | 6      |

| IGBT                    |        |        |        |          |      |        |      |        |

| Total IGBT              | 1582.8 | 2165   | 1959.6 | 1312     | 4050 | 2213   | 2382 | 958    |

| Si                      |        |        |        |          |      |        |      |        |

| area (mm <sup>2</sup> ) |        |        |        |          |      |        |      |        |

|                         | 1      |        |        |          | 1    |        |      |        |

Table 2.1: Motor drive performances of commercial products [1]

In [1], it is also stated that DC bus voltage should be increased in order to achieve higher speeds and more compact designs as well. Increase in DC bus voltage allows designer to reach up higher speeds and result in more compact designs. It can be inferred from [14] that increase in DC bus voltage from 500 to 600/650 V level has a significant effect on the increase of motor speed of Toyota Prius from 6000 rpm to 17000 rpm. Higher DC bus results in lower losses at the inverter side and enables the design of more compact electric drive systems. This is important because another trend in electric motors and drive systems is to increase speed of the motor. In [15], benchmarking of different commercial electric vehicle products are represented. Accordingly, speed rating of the motors varies between 6000 rpm to 14000 rpm.

As cooling technologies, natural cooling with heatsink, forced air cooling and liquid cooling are the most common methodologies in power electronics. For lower power electronics circuitry, natural cooling is widely used with bulky heatsinks. In order to design more compact power converters, forced air cooling could be used to shrink power converter size. On the other hand, in electric vehicle applications, liquid cooling is the most common method. In [15], cooling system of the commercial electric vehicles drive systems are explained. Most of them use heatsink with water-glycol loop as cooling system. Liquid cooling allows more compact design, in terms of volume by sacrificing cost effectiveness.

A general overview of voltage source inverter topologies is given in next section. On the other hand, state of art voltage source inverter for electric vehicle applications is conventional two-level topology due to its simplicity, robustness and easy controllability. Also, conventional Si IGBT and diode pairs are used as power semiconductor switches [1]. In two-level topology, high dV/dt is observed at the switch node of each phase due to swing between 0 and  $V_{dc}$ . In order to achieve lower dV/dt at the output and achieve higher efficiency, three-level NPC topology could be a good candidate for near future commercial products.

#### 2.2 Voltage Source Inverter Topologies and Applications

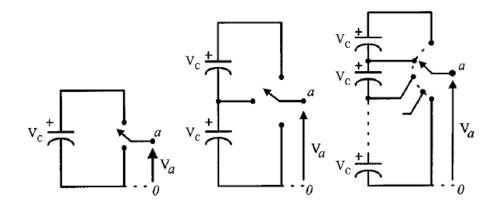

Three-phase voltage source converters can be divided into two main groups. The first one is two-level voltage source converters that are widely used in industry in many applications due to their simplicity and control ease. On the other hand, another major topology group is called multilevel inverters. Multilevel inverters consist of an array of semiconductors and capacitors, which generate output voltage with stepped waveforms. The need to use of multilevel inverters is due to high DC bus voltage levels of medium voltage grid. Power semiconductor blocking voltage specifications are not able to match with DC bus voltage level especially in AC drives of MW ranges. Due to these reasons, multilevel inverters emerged. Level of an inverter is determined by checking the number of possible voltage steps at the switch node of its legs. Basic models of two-level, three-level and multilevel inverters is shown in Figure 2.1.

Figure 2.1: One phase leg of inverter with two-level, three-level and n-level node voltages [2]

Voltage source inverters are widely used in high voltage direct current (HVDC) transmission systems, medium-voltage motor drive systems, static compensator (STAT-COM) applications, electric traction systems and grid connected energy storage systems. Conventional two-level and three-level topologies are still widely used in most of these applications. On the other hand, multilevel topologies are used for some of the applications above when there are high power, high reliability and high efficiency constraints. Also modular multilevel converters (MMCs) which consist of sub-modules instead of one semiconductor are widely used in the high power applications as well. In this thesis, only two-level and three-level NPC type converters are investigated. In Chapter 3, detailed information on the selected inverter topologies are given. Information on different multilevel topologies and specific application areas can be found in [16] and [2].

#### 2.3 Modulation Techniques

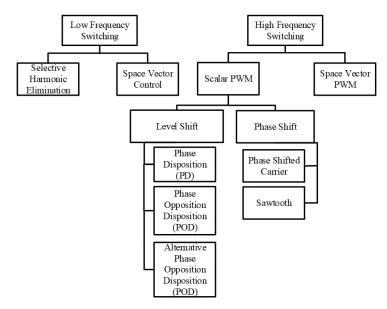

There are various pulse width modulation (PWM) techniques used to manipulate semiconductors in voltage source inverters. In two-level topology, the most common methods are sinusoidal pulse width modulation (SPWM), space vector pulse width modulation (SVPWM) and hysteresis current controller based PWM. The first two techniques are discussed in Chapter 3 in details. On the other hand, various modulation techniques can be implemented in multi-level inverters. These switching techniques can be categorized into two main groups as low frequency switching and high frequency switching as shown in Figure 2.2.

Figure 2.2: Switching techniques for multilevel inverters [3]

In low frequecy switching, the first method is selective harmonic elimination in which switching angles are pre-calculated such that desired harmonic component at the output is cancelled. The methodology is explained in details in [17] and [18]. Second low frequency techinque is space vector control method. Space vector control method aims to generate output voltage with minimum error with respect to the reference vector. In SVPWM technique, the aim is to generate exactly the same mean voltage of the reference vector at the output. In space vector control method, the aim is just to minimize error between the reference vector and the output voltage. Space vector control method is detailly explained in [3]. Low frequency switching methods decrease switching losses significantly. On the other hand, they have a bad dynamic response.

High switching frequency techniques consist of space vector pulse width modulation (SVPWM) and sinusoidal pulse width modulation (SPWM) techniques. Application of these modulation methods for two-level and three-level NPC type topology are explained in Chapter 3. In SPWM, gate signals are generated by comparing a reference sine wave having fundamental output frequency and carrier signal having switching frequency.

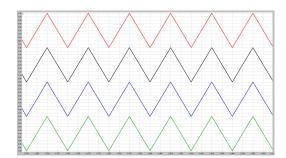

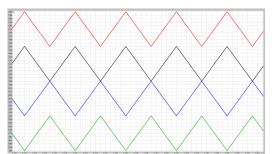

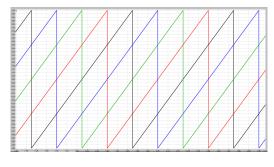

SPWM techniques for MMCs differ by means of carrier signals. Carrier signals of a five-level inverter topology with phase disposition, phase opposition disposition, alternative phase opposition disposition, phase shifted carriers and sawtooth rotation methods are given in Figure 2.3. SVPWM and SPWM with phase disposition method are selected for analyses in the thesis. Selected topologies and switching techniques are detailly explained in the following two chapters.

(a) Phase disposition carrier signals

(b) Phase opposition disposition carrier signals

(c) Alternative phase disposition carrier signals

(d) Phase shifted carrier signals

(e) Sawtooth rotation method

Figure 2.3: Scalar PWM carrier signals of a 5-level VSI

#### **CHAPTER 3**

# TWO LEVEL AND THREE LEVEL NPC TYPE VOLTAGE SOURCE INVERTERS

There are various techniques to generate AC voltage at the output of switch nodes. Sinusoidal PWM, Space Vector PWM, hysteresis controller etc. In this thesis, SPWM and SVPWM methods are considered for two-level and three-level NPC type voltage source inverter topologies since they are the most commonly applied PWM methods.

### 3.1 Two-level Voltage Source Inverter

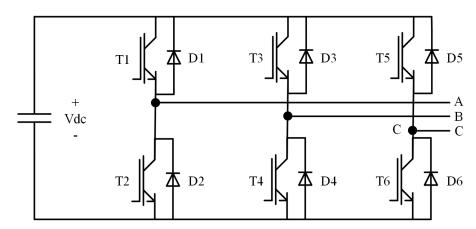

A two-level three-phase voltage source inverter is shown in Figure 3.1.

Figure 3.1: Two-level topology

This topology consists of 6 bi-directional switches. Depending on the current and voltage rating of the converter, Si MOSFETs, SiC MOSFETs, GaNFETs and IGBT-diode pairs can be used as main bi-directional switches in two-level inverters. Among them, IGBT-diode pairs are widely used in electric vehicle drive applications. Two

switches in one leg of inverter work complementarily in two-level topology in order to avoid short circuit of DC bus. Thus, Each semiconductor in the topology should block  $V_{dc}$  voltage when they are in off state.

### 3.1.1 Modulation Techniques

#### **SPWM**

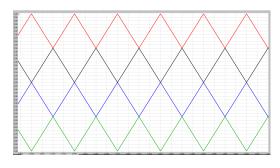

In SPWM modulated two-level three phase inverter, three reference sine waves  $120^{\circ}$  shifted wrt. each other are used as reference for each phase. Freuqency of reference sine waves are the same as output frequency. By comparing reference sine waves with the carrier triangle waveforms, gate signals are obtained for upper and lower switches of each leg. Frequency of the carrier signal determines the switching frequency. Carrier signal, three reference signals and node voltages of each leg with respect to DC bus ground are given in Figure 3.2. In the figure, exampilary 50 Hz reference signals and 1 kHz carrier signal are shown.

Figure 3.2: Reference and carrier waveforms for two-level SPWM

#### **SVPWM**

Space Vector PWM (SVPWM) technique is widely used in many inverter applications. The main advantage of SVPWM is the degree of freedom to place vectors in a switching period compared with SPWM method. SVPWM also provides a better DC bus utilization. So, due to better DC bus utilization, voltage level of DC bus can be reduced. For two-level inverter topology, 61.2% DC bus utilization can be achieved with SPWM and 70.7% with SVPWM. DC bus utilization corresponds to percent of the ratio between line-line rms voltage at the output of inverter and DC bus voltage value. However; SVPWM technique needs higher computational power due to its nature. In recent years, microcontrollers and DSPs allow designers to implement SVPWM algorithms easily.

SVPWM technique is based on selection of the optimum switching state of the inverter in each switching period. In order to achieve this purpose, three phase reference signals are transformed to  $\alpha - \beta$  axis by applying Clarke's transformation using (3.1). Each switching state corresponds to a voltage vector on  $\alpha - \beta$  plane and the created vector is called space vector. This vector is created as a combination of  $2^3 = 8$  voltage vectors in two-level three-phase topology. Two of them are zero vectors that are represented by 000 and 111 vectors. Space vectors and their switch logic signals are given in Table 3.1.

|   |       |       | T1,T3,T5 |    |    | T  | 2,T4,7 | Г6 |

|---|-------|-------|----------|----|----|----|--------|----|

|   | Vec   | ctors | T1       | T3 | T5 | T2 | T4     | T6 |

| 1 | $V_0$ | 000   | 1        | 1  | 1  | 0  | 0      | 0  |

| 1 | $V_1$ | 100   | 0        | 1  | 1  | 1  | 0      | 0  |

| ١ | $V_2$ | 110   | 0        | 0  | 1  | 1  | 1      | 0  |

| 1 | $V_3$ | 010   | 1        | 0  | 1  | 0  | 1      | 0  |

| 1 | $V_4$ | 011   | 1        | 0  | 0  | 0  | 1      | 1  |

| ١ | $V_5$ | 001   | 1        | 1  | 0  | 0  | 0      | 1  |

| 1 | $V_6$ | 101   | 0        | 1  | 0  | 1  | 0      | 1  |

| ١ | $V_7$ | 111   | 0        | 0  | 0  | 1  | 1      | 1  |

Table 3.1: Switch logic for corresponding space vectors

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{a} \\ V_{b} \\ V_{c} \end{bmatrix}$$

(3.1)

Then reference vector  $V_r$  is defined as in (3.2).

$$\vec{V_r} = V_\alpha + jV_\beta \tag{3.2}$$

In SVPWM algorithm, amplitude  $\vec{V_r}$  and phase  $\alpha$  of the reference vector is required. These quantities are determined as in (3.3) and (3.4).

$$|V_r| = \sqrt{V_{\alpha}^2 + V_{\beta}^2}$$

(3.3)

$$\alpha = \tan^{-1}(\frac{V_{\beta}}{V_{\alpha}}) \tag{3.4}$$

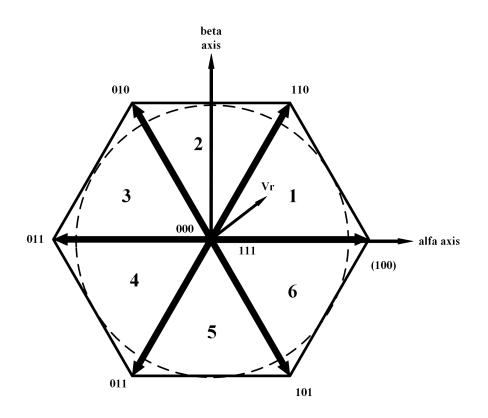

With magnitude and phase calculation, sector determination is done as in Table 3.2. These vectors are shown in Figure 3.3. It should be noted that zero vectors are equally shared in terms of time.

| Sector | Position of $V_r$          |

|--------|----------------------------|

| 1      | $0^o < \omega t < 60^o$    |

| 2      | $60^o < \omega t < 120^o$  |

| 3      | $120^o < \omega t < 180^o$ |

| 4      | $180^o < \omega t < 240^o$ |

| 5      | $240^o < \omega t < 300^o$ |

| 6      | $300^o < \omega t < 360^o$ |

Table 3.2: Regions and positions of reference vector

After this magnitude and phase calculation, the space vectors and their on-times must be calculated. In order to calculate on times for each vector, volt-seconds law is applied as in 3.5. On time calculation of vectors in sector 1 can be done using (3.5) and (3.6).  $T_s$  corresponds to switching period,  $T_0$  corresponds to application time of  $V_0$ ,  $T_1$  corresponds to application time of  $V_1$  and  $T_2$  corresponds to application time of  $V_2$ . Sum of  $T_0$ ,  $T_1$  and  $T_2$  is equal to switching period  $T_s$ .  $m_a$  is modulation index defined as in 3.7 in order to simply mathematical formulation for on time calculations.

$$\int_{0}^{T_{s}} \vec{V_{r}} = \int_{0}^{T_{1}} \vec{V_{1}} dt + \int_{0}^{T_{2}} \vec{V_{2}} dt + \int_{0}^{T_{0}} \vec{V_{0}} dt$$

(3.5)

$$\vec{V_r} = |V_r|e^{j\alpha}, \vec{V_0} = 0, \vec{V_1} = \frac{2}{3}, \vec{V_2} = \frac{2}{3}e^{\frac{j\pi}{3}}$$

(3.6)

$$m_a = \frac{3V_r}{2V_{dc}} \tag{3.7}$$

On time durations of space vectors in all six sectors are given in Table 3.3 as a function of switching period  $T_s$ , modulation index  $m_a$  and phase of reference vector  $\alpha$ . Finally, switching patterns in each sector are given in Figure 3.4.

| Sector | $T_1$                                  | $T_2$                                  | $T_0$             |

|--------|----------------------------------------|----------------------------------------|-------------------|

| 1      | $T_s m_a sin(\frac{\pi}{3} - \alpha)$  | $T_s m_a sin(\alpha)$                  | $T_s - T_1 - T_2$ |

| 2      | $T_s m_a sin(\frac{2\pi}{3} - \alpha)$ | $T_s m_a sin(\alpha - \frac{\pi}{3})$  | $T_s - T_1 - T_2$ |

| 3      | $T_s m_a sin(\pi - \alpha)$            | $T_s m_a sin(\alpha - \frac{2\pi}{3})$ | $T_s - T_1 - T_2$ |

| 4      | $T_s m_a sin(\frac{4\pi}{3} - \alpha)$ | $T_s m_a sin(\alpha - \pi)$            | $T_s - T_1 - T_2$ |

| 5      | $T_s m_a sin(\frac{5\pi}{3} - \alpha)$ | $T_s m_a sin(\alpha - \frac{4\pi}{3})$ | $T_s - T_1 - T_2$ |

| 6      | $T_s m_a sin(2\pi - \alpha)$           | $T_s m_a sin(\alpha - \frac{5\pi}{3})$ | $T_s - T_1 - T_2$ |

Table 3.3: Calculated times and regions in two-level topology

Figure 3.3: Two-level space vectors

|                   | 100                   | 110                   | 111               | 111               | 110                   | 100                   | 000                      | 000                                 | 100                   | 110                   | 111               | 111               | 110            | 100                   | 000                      |

|-------------------|-----------------------|-----------------------|-------------------|-------------------|-----------------------|-----------------------|--------------------------|-------------------------------------|-----------------------|-----------------------|-------------------|-------------------|----------------|-----------------------|--------------------------|

| T <sub>0</sub> /2 | T <sub>1</sub>        | T <sub>2</sub>        | T <sub>0</sub> /2 | T <sub>0</sub> /2 | T <sub>2</sub>        | T <sub>1</sub>        | T <sub>0</sub> /2        | T <sub>0</sub> /2                   | <b>T</b> <sub>1</sub> | T <sub>2</sub>        | T <sub>0</sub> /2 | T <sub>0</sub> /2 | T <sub>2</sub> | T <sub>1</sub>        | T <sub>0</sub> /2        |

|                   |                       |                       |                   |                   |                       |                       |                          |                                     |                       |                       |                   |                   |                |                       |                          |

| 3                 |                       |                       |                   |                   |                       |                       |                          | 83                                  |                       |                       |                   |                   |                |                       |                          |

| 5                 |                       |                       |                   |                   |                       |                       |                          | <b>S</b> 5                          |                       |                       |                   |                   |                |                       |                          |

| 2                 |                       |                       |                   |                   |                       |                       |                          | 82                                  |                       |                       |                   |                   |                |                       |                          |

| 4                 |                       |                       |                   |                   |                       |                       |                          |                                     |                       |                       |                   |                   |                |                       |                          |

| 6                 |                       |                       |                   |                   |                       |                       |                          | <u>S4</u>                           |                       |                       |                   |                   |                |                       |                          |

| •                 |                       |                       |                   |                   |                       |                       |                          | <b>S6</b>                           |                       |                       |                   |                   |                |                       |                          |

|                   |                       |                       | (a) Se            | ector 1           |                       |                       |                          |                                     |                       |                       | (b) Se            | ector 2           |                |                       |                          |

| 000               | 100                   | 110                   | 111               | 111               | 110                   | 100                   | 000                      | 000                                 | 100                   | 110                   | 111               | 111               | 110            | 100                   | 000                      |

| T <sub>0</sub> /2 | <b>T</b> 1            | T <sub>2</sub>        | T <sub>0</sub> /2 | T <sub>0</sub> /2 | T <sub>2</sub>        | <b>T</b> <sub>1</sub> | T <sub>0</sub> /2        | T <sub>0</sub> /2                   | T <sub>1</sub>        | T <sub>2</sub>        | T <sub>0</sub> /2 | T <sub>0</sub> /2 | T <sub>2</sub> | T <sub>1</sub>        | T <sub>0</sub> /2        |

| 51                |                       |                       |                   |                   |                       |                       |                          | <b>S1</b>                           |                       |                       |                   |                   |                |                       |                          |

| 3                 |                       |                       |                   |                   |                       |                       |                          | 83                                  |                       |                       |                   |                   |                |                       |                          |

| 5                 |                       |                       |                   |                   |                       |                       |                          | 85                                  |                       |                       |                   |                   |                |                       |                          |

|                   |                       |                       |                   |                   |                       |                       |                          |                                     |                       |                       |                   |                   |                |                       |                          |

| 2                 |                       |                       |                   |                   |                       |                       |                          | S2                                  |                       |                       |                   |                   |                |                       |                          |

| 64                |                       |                       |                   |                   |                       |                       |                          | <b>S</b> 4                          |                       |                       |                   |                   |                |                       |                          |

| 6                 |                       |                       |                   |                   |                       |                       |                          | 86                                  |                       |                       |                   |                   |                |                       |                          |

|                   |                       |                       | (a) S             | ector 3           |                       |                       |                          |                                     |                       |                       | (d) Se            | ector 4           | ł              |                       |                          |

|                   |                       |                       | (c) 36            |                   |                       |                       |                          |                                     |                       |                       |                   |                   |                |                       |                          |

| 000               | 100                   | 110                   | 111               | 111               | 110                   | 100                   | 000                      | 000                                 | 100                   | 110                   | 111               | 111               | 110            | 100                   | 000                      |

| T <sub>0</sub> /2 | 100<br>T <sub>1</sub> | 110<br>T <sub>2</sub> |                   |                   | 110<br>T <sub>2</sub> | 100<br>T <sub>1</sub> | 000<br>T <sub>0</sub> /2 | T <sub>0</sub> /2                   | 100<br>T <sub>1</sub> | 110<br>T <sub>2</sub> |                   | 1                 | 1              | 100<br>T <sub>1</sub> |                          |

| T <sub>0</sub> /2 |                       |                       | 111               | 111               |                       |                       |                          | T <sub>0</sub> /2                   |                       |                       | 111               | 111               | 110            |                       |                          |

| T <sub>0</sub> /2 |                       |                       | 111               | 111               |                       |                       |                          | T <sub>0</sub> /2                   |                       |                       | 111               | 111               | 110            |                       |                          |

| T <sub>0</sub> /2 |                       |                       | 111               | 111               |                       |                       |                          | T <sub>0</sub> /2                   |                       |                       | 111               | 111               | 110            |                       | 000<br>T <sub>0</sub> /2 |

|                   |                       |                       | 111               | 111               |                       |                       |                          | T <sub>0</sub> /2<br>S1<br>S3       |                       |                       | 111               | 111               | 110            |                       |                          |

| T <sub>0</sub> /2 |                       |                       | 111               | 111               |                       |                       |                          | T <sub>0</sub> /2<br>S1<br>S3<br>S5 |                       |                       | 111               | 111               | 110            |                       |                          |

Figure 3.4: Switching patterns and on times for each region

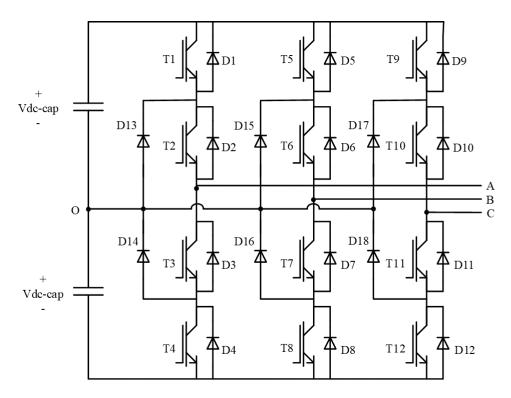

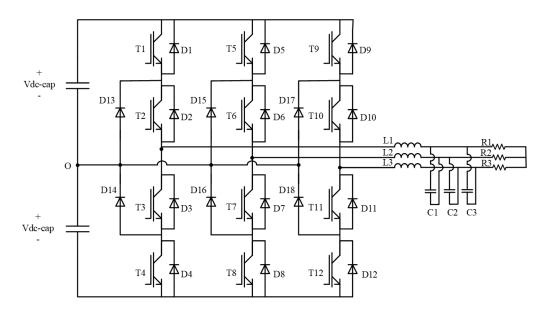

## 3.2 Three-level NPC Type Voltage Source Inverter

Figure 3.5: Three-level NPC topology

Three-Level NPC type inverter topology was firstly introduced in [19] in 1981. After that the topology is widely used in industry along with T-type three-level inverter topology and two-level topology. In the literature, there are various studies on T-type topology as well. On the other hand, in [20] it is shown that NPC topology can work under higher switching frequencies compared with T-type topology in three-level applications due to its lower losses. Since higher switching frequencies are aimed in this thesis, three-level NPC type topology is selected. In NPC type three-level inverter topology, each leg has four bi-directional switches and two zero potential clamping diodes as shown in Figure 3.5. It should be noted that  $V_{dc}=2V_{dc-cap}$ . Diodes are used to clamp different voltage states in each leg. Three different voltage levels that can be obtained in the first leg and corresponding switching patterns are given in Table 3.4.

| Vout         | <b>T</b> 1 | T2 | T3 | T4 |

|--------------|------------|----|----|----|

| $0.5V_{dc}$  | 1          | 1  | 0  | 0  |

| 0            | 0          | 1  | 1  | 0  |

| $-0.5V_{dc}$ | 0          | 0  | 1  | 1  |

Table 3.4: Switch pattern and node voltage in one leg

#### **3.2.1** Modulation Techniques

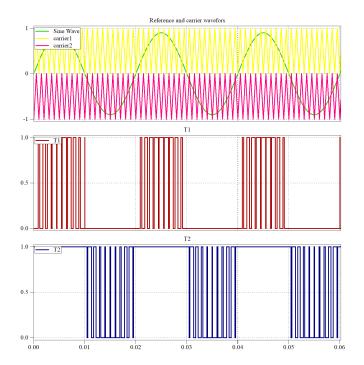

In modular multilevel converters (MMCs), various switching techniques were studied in the literature. These methods are not only available for three-level NPC type converter , but also applicable for other multilevel converter topologies. A general switching technique review is given in [21] for MMCs. In this study, in order to make a multidimensional comparison, two switching techniques are selected. The first one is SPWM technique with phase disposition method. The second one is SVPWM method by aiming a lower THD at the output current.

#### **SPWM**

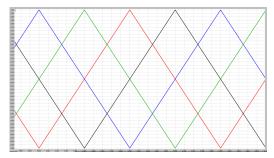

There are various ways to apply SPWM in three-level topology which were briefly explained in Chapter 2. In this study, SPWM is applied with two different carrier waveforms separated by a DC offset from each other that is called phase disposition method. Carrier waveforms and reference waveforms are shown in Figure 3.6. Phase B and C legs have shifted reference sine waves by  $120^{\circ}$  wrt. each other. carrier1 is used for upper top switches of each leg (T1, T5, T9). carrier2 is responsible for lower switches (T2, T6, T10). Bottom two switches in each leg works complementarily with top side corresponding switch. For example  $T_1$  and  $T_3$  are complementary switches.

Figure 3.6: Three-level SPWM phase A switching signals

#### **SVPWM**

In three level topology there are in total of  $3^3 = 27$  space vectors. 24 of them are active vectors from which 12 are short vectors, 6 are medium vectors and 6 are long vectors. Other 3 vectors are zero vectors located in the center. In three level inverter, six main sectors are the same as in two-level case and each sector consists of four sub-sectors. Figure 3.7 and 3.8 show space vectors and four sub-sectors in three level inverter, respectively. Sub-sector representation in Figure 3.8 represents first main sector as in two-level inverter where  $0^{\circ} < \alpha < 60^{\circ}$ . Due to the additional degree of freedom, there are many strategies to manage space vectors to generate PWM signals. In this study, symmetrical SVPWM method that is commonly used to achieve a low current THD at the output is used [22].  $V_{dc-cap}$  is defined as voltage of one of the floating capacitors as can be seen in Figure 3.5. Each connection point can attain three different voltage levels in a 3-level VSI; P represents  $0.5V_{dc}$ , O represents zero potential and N represents  $-0.5V_{dc}$  at the switching node of a phase leg as listed in Table 3.5.

Small vectors (POO, ONN, etc.) have magnitude of  $V_{dc}/3$ . Medium vectors (PON,

| Symbol | T1 | T2 | T3 | T4 | Voltage      |

|--------|----|----|----|----|--------------|

| Р      | 1  | 1  | 0  | 0  | $0.5V_{dc}$  |

| 0      | 0  | 1  | 1  | 0  | 0            |

| N      | 0  | 0  | 1  | 1  | $-0.5V_{dc}$ |

Table 3.5: Symbols, corresponding switch states and phase voltages

OPN, etc.) have magnitude of  $(\sqrt{3}/3)V_{dc}$ . Large vectors (PNN, PPN, etc..) have magnitude of  $2V_{dc}/3$ .

Figure 3.7: Three-level space vectors

Main sector detection is done the same way as in two-level inverter. Sub-sector detection is done with the angle and magnitude of  $V_r$  vector. On-time calculation in sector 1 and sub-sector 1 can be carried out using (3.8), (3.9) and (3.10).

$$T_a + T_b + T_c = T_s \tag{3.8}$$

Figure 3.8: Sub-sectors in three-level SVPWM

$$\vec{V_1}T_a + \vec{V_2}T_c = \vec{V_r}T_s, \ T_b = 0$$

(3.9)

$$\frac{2V_{dc}}{3}e^{j0}T_a + \frac{2V_{dc}}{3}e^{j\frac{\pi}{3}}T_c = |\vec{V_r}|T_s$$

(3.10)

where,

$$V_{\alpha} = V_{aref} - 0.5V_{bref} - 0.5V_{cref} \tag{3.11}$$

$$V_{\beta} = (V_{bref} - V_{cref})\frac{\sqrt{3}}{2} \tag{3.12}$$

$$\alpha = \tan^{-1}(\frac{V_{\beta}}{V_{\alpha}}) \tag{3.13}$$

Then the on times are calculated for each sub-sector by using the equations as in Table 3.6. Ta, Tb and Tc are on-time of each vector as shown in Figure 3.8. Variable k is defined as:

$$k = \sqrt{3} \frac{|\vec{V_r}|}{V_{dc}} \tag{3.14}$$

| S | $T_a$                                  | $T_b$                                 | $T_c$                                  |

|---|----------------------------------------|---------------------------------------|----------------------------------------|

| 1 | $2ksin(\frac{\pi}{3}-\alpha)$          | $T_s - 2ksin(\frac{\pi}{3} + \alpha)$ | $2ksin(\alpha)$                        |

| 2 | $T_s - 2ksin(\alpha)$                  | $2ksin(\frac{\pi}{3} + \alpha) - T_s$ | $T_s - 2ksin(\frac{\pi}{3} - \alpha)$  |

| 3 | $2ksin(\alpha) - T_s$                  | $2ksin(\frac{\pi}{3} - \alpha)$       | $2T_s - 2ksin(\frac{\pi}{3} + \alpha)$ |

| 4 | $2T_s - 2ksin(\frac{\pi}{3} + \alpha)$ | $2ksin(\alpha)$                       | $2ksin(\frac{\pi}{3} - \alpha) - T_s$  |

Table 3.6: Calculated times and sub-sectors in three-level

Detailed PWM patterns of SVPWM for each region and sub-region are given in Appendix A.

# 3.3 Design, Analysis and Implementation of a 750 W Three-Level NPC Type Inverter

In this section, a three-level NPC type inverter was designed an implemented. The hardware infrastructure of PCB is designed for a 750 W PMSM drive having 350  $V_{dc}$  and 230  $V_{rms}$  line-line voltage parameters. The main purpose of this section is to investigate hardware challenges of three-level NPC type topology. First, design procedure is explained and the critical steps to design a three-level NPC type inverter's PCB are shown in this section. Finally, design challenges of hardware and open loop test results up to half of the rated power are given in this chapter.

#### 3.3.1 Design

As control hardware, F28379D Delfino Experimenter Kit as shown in Figure 3.9 is used from Texas Instruments C2000 family. In order to operate three-level NPC type inverter, at least 12 PWM outputs from the DSP or microcontroller are needed. There-

fore; it can be inferred that one of the most developed DSPs should be used in order to design a three-level NPC type inverter. EPWM peripheral of F28379D is used to manipulate semiconductors of hardware.

Figure 3.9: F28379D experimenter kit

As the first step, voltage and current rating of hardware are determined. Hardware setup is designed for a PMSM drive rating at 750 W output rating and 350 V dc bus voltage rating. The PMSM has 230  $V_{rms}$  line-line voltage with four pole-pairs.

Desired control method is Field Oriented Control method as used in previous chapters. Therefore; speed sensing is critical for the design. There are various methods of PMSM speed sensing. One of the most common method for speed sensing in PMSMs is incremental encoder method. In this application, power hardware of motor drive circuitry is designed to meet the incremental encoder sensing criterion. Incremental encoder generates square wave pulses as output. Output frequency of sensor is dependent on the speed of the motor. In F28379 DSP module, eCAP (Enhanced Capture Module) captures the rise and fall of the DSP input signal. This peripheral is actually specified to incremental encoder output. With a simple analog circuitry, output of the incremental encoder is connected to the DSP eCAP peripheral easily.

For the Field Oriented Control, phase currents of at least two phases are needed to be sensed. In order to achieve this, hall-effect current sensors are used for each phase. Since output of the hall-effect sensors have high impedance characteristics, they are directly connected to F28379D ADC peripheral inputs. Three-level NPC topology

could face voltage unbalances of floating capacitors due to its nature. In order to avoid such unbalances, floating capacitor voltages should be sensed and with control algorithms undesired unbalances should be avoided. This issue results in increase of both hardware and software complexity. In order to sense floating capacitor voltages, analog sense circuitry was built in the hardware and they are sensed with F28379D ADC peripheral inputs.

The above mentioned issues were implemented in order to prepare PCB board for a closed loop operation while driving the PMSM.

The most critical issue is to construct gate-drive circuitry and power loop construction in power converter design. On the other hand; in three-level NPC topology, each phase leg consists of four bi-directional switches and two clamping diodes. Four bidirectional switches construct a large power loop inductance by nature. In order to avoid such parasitic loop inductance based oscillations, film capacitors, which have good high frequency current capability, are used between high voltage DC positive and center of floating capacitors. Also, by-pass capacitors are added between high voltage DC negative and center of floating capacitors as suggested in [23],[24] and [25].

Another design challenge of a three-level NPC power loop is as follows: Center of floating capacitors are chosen as power ground of the layout. Therefore; digital and analog signals are referenced with regard to center of floating capacitors of DC bus. This application results with a crucial reqirement that all gate drivers should be selected for high side driving. High-side driving can be defined as follows: Source of MOSFET or emitter of IGBT swings between low and high voltages. Therefore; while driving gate of the semiconductor, designer should consider to generate a supply voltage having a reference ground as source or emitter. Therefore; isolated supplies should be generated for each bi-directional semiconductor. In some topologies and switching techniques, this reference voltage generation could be achieved with a method called bootstrap gate driving. Bootstrap gate driving method is simple but maximum on time of the semiconductors are limited. In three level SPWM and SVPWM switching techniques, each switch is completely on or off during half of the fundamental period. Thus it is not a desired application of bootstrap gate driving.

ing. Therefore; total of 12 isolated DC-DC converters are employed for each of the bi-directional semiconductor, which increase complexity of the power hardware.

Selection of switches are important for a power converter. In this application, the main purpose of the design is to build a three-level NPC topology for a specific PMSM. On the other hand, second purpose is to build a generic power converter that can be used in future research activities. For this reason, switches, DC bus capacitors and heatsinks are overdesigned. Although blocking voltage is 175V at this application standard TO-247 packages MOSFETs with 650 V blocking voltages are used as main switches. As clamping diodes SiC diodes are used in order to avoid reverse recovery effect of standard silicon diodes. Clamping diodes have standard TO-220 package. By using industry standard through hole semconductors in the design, an adjustable power board was designed for the future developments.

Three dimensional view of designed PCB's top and bottom layers are shown in Figures 3.10 and 3.11, respectively. Power MOSFETs and clamping diodes are placed at the top side of the PCB. Also, DSP board is placed at the top side. Analog circuitry to sense DC bus voltages and hall effect sensors are placed at the top side. At the bottom side, isolated power supplies for gate driving circuitry are placed.

In this prototype, fan cooling with heatsink is assumed as the cooling solution. Each phase of three-level NPC topology is cooled with one heatsink. Total of six switches are packaged with one heatsink and fan.

Figure 3.10: Top view of PCB

Figure 3.11: Bottom view of PCB

## 3.3.2 Test Results

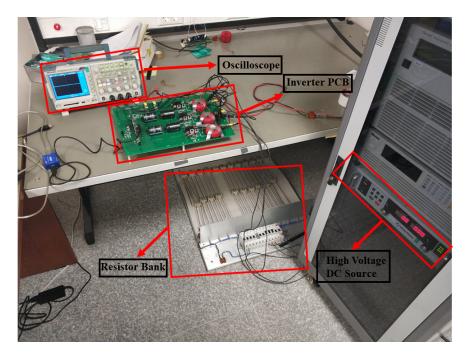

In test setup, tests were conducted under 120 W, 240 W and 360 W input power with passive load variations. Resistor bank is adjusted to provide three different output power conditions. Also two different modulation index  $(m_a)$  values are used in the tests. An L-C filter is employed at the output of the inverter and resistor bank is used as load. The circuitry schematic in order to conduct tests are given in Figure 3.12.

Figure 3.12: Test setup circuitry

Test setup is constructed in the laboratory environment. Test setup is shown in Figure 3.13. It consists of the inverter PCB, a high voltage DC source, oscilloscope, a resistor bank. Test parameters are given in Table 3.7

| $V_{dc}(V)$         | 300         |

|---------------------|-------------|

| $f_{sw}(kHz)$       | 25          |

| $f_{out}(Hz)$       | 50          |

| $R_{load}(\Omega)$  | 160, 80, 53 |

| $L_1, L_2, L_3(mH)$ | 2.6         |

| $C_1, C_2, C_3(nF)$ | 470         |

| $m_a$               | 0.8,0.6     |

Table 3.7: Hardware test parameters

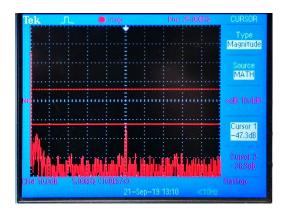

In the test procedure, two different observations are done from oscilloscope screen, phase currents and line-line voltages of resistor bank. Since three high bandwidth current probes are not able to be employed in the laboratory environment, line to line voltages of resistor bank for three phases are observed as indicators of phase currents. Six open loop tests are conducted with two different modulation indexes

Figure 3.13: Test setup

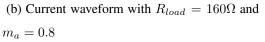

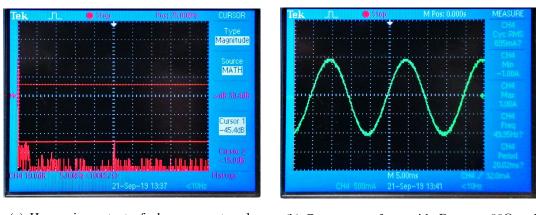

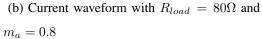

and three loading conditions. Harmonic content of the phase currents and dominant components are also observed in the tests. Open loop phase current waveforms and harmonic content results are given in Figures 3.14 to 3.19.

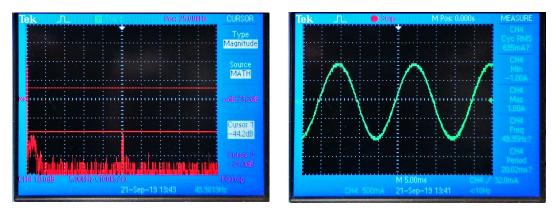

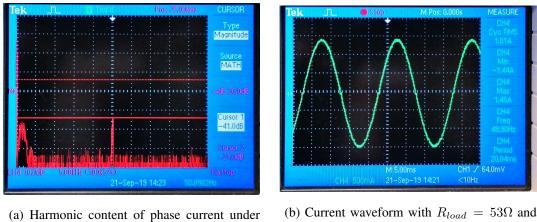

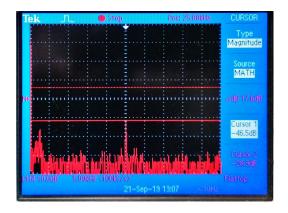

From the test results, it is clearly seen that fundamental harmonic and switching frequency component is dominant in three-level NPC inverter. Also in every harmonic analysis, it is observed that component at the resonant frequency of the L-C filter is seen at the output. 470 nH capacitor and 2.6 mH inductor filter have resonance at 2.6 kHz since capacitors are delta connected.

By conducting those tests, hardware is prepared for its real application of PMSM drive. Since tests are conducted with passive balanced loads, unbalance between floating capacitors are not observed. Requirement of isolated power supplies for each semiconductor increases initial cost of the hardware. Also manipulation of 12 controlled bi-directional power semiconductors increases complexity of PWM generation unit. An advanced DSP or microcontroller is needed to use in the hardware. Therefore; three-level NPC topology is not suitable for low power and cost critical applications. On the other hand, halved blocking voltage is one of the major advantages of three-level NPC topology hardware.

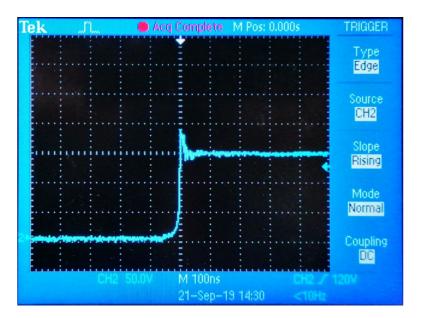

Also one of the main advantages of three-level NPC topology is observed in the experiments. Blocking voltage requirement of the semiconductors is half of the DC bus voltage. Drain-source voltage of one MOSFET in the hardware during tun-off is shown in Figure 3.22. As can be seen, the switch need to block 150 V.

In this chapter, the two switching techniques are selected and detailly explained for the two common inverter topologies for electric vehicle drive systems. Also implementation of a threelevel NPC type inverter is detaily explained and test results are given. In the next chapter, semiconductor losses and thermal modelling fundamentals are given for the two topologies. Then multidimensional comparison of the two topologies and two switching techniques are done in the fifth and fourth chapters.

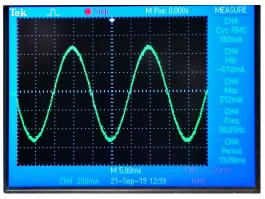

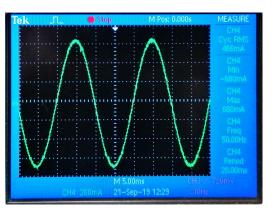

(b) Current waveform with  $R_{load} = 160\Omega$  and  $m_a = 0.6$

Figure 3.14: Phase current waveform and harmonic spectrum with  $R_{load} = 160\Omega$  and  $m_a = 0.6$

(a) Harmonic content of phase current under  $R_{load} = 80\Omega \text{ and } m_a = 0.6$

(b) Current waveform with  $R_{load} = 80\Omega$  and  $m_a = 0.6$

Figure 3.15: Phase current waveform and harmonic spectrum with  $R_{load} = 80\Omega$  and  $m_a = 0.6$

(a) Harmonic content of phase current und  $R_{load} = 53\Omega$  and  $m_a = 0.6$

(b) Current waveform with  $R_{load} = 53\Omega$  and  $m_a = 0.6$

Figure 3.16: Phase current waveform and harmonic spectrum with  $R_{load} = 53\Omega$  and  $m_a = 0.6$

(a) Harmonic content of phase current under  $R_{load} = 160\Omega \text{ and } m_a = 0.8$

Figure 3.17: Phase current waveform and harmonic spectrum with  $R_{load} = 160\Omega$  and  $m_a = 0.8$

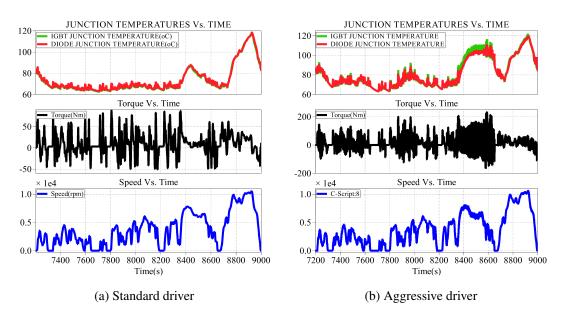

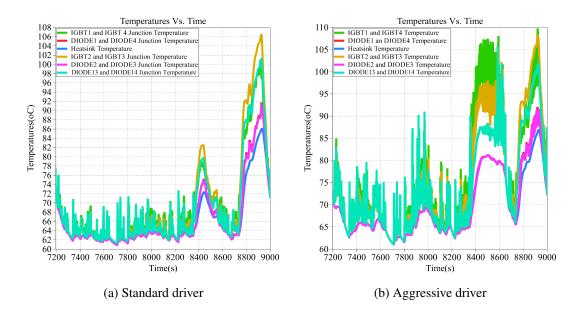

(a) Harmonic content of phase current under  $R_{load}=80\Omega \text{ and } m_a=0.8$