## TÜRKİYE BİLİMSEL VE TEKNİK ARAŞTIRMA KURUMU

Dup

THE SCIENTIFIC AND TECHNICAL RESEARCH COUNCIL OF TURKEY

201/62

Elektrik, Elektronik ve Enformatik Araştırma Grubu

Electric, Electronics and Informatics Research Grant Committee

## TÜRKİYE BİLİMSEL VE TEKNİK ARAŞTIRMA KURUMU

# THE SCIENTIFIC AND TECHNICAL RESEARCH COUNCIL OF TURKEY

## Biçimsel Yöntemler ile Dağılımlı Yazılımların Doğrulanması ve Geçerlileştirilmesi

Proje No: 194E017 (COST-247)

Elektrik, Elektronik ve Enformatik Araştırma Grubu

Electric, Electronics and Informatics

Research Grant Committee

#### **ÖNSÖZ**

Bu proje Avrupa Topluluğu kuruluşu olan COST'a sunulup kabul ettirilmiş olan ve 18 Avrupa ülkesinin katılımı ile başkanlığı ve sekreteryasının Türkiye tarafından yürütüldüğü COST 247 kodlu ve Verification/Validation of Communication Software by Formal Methods adlı projenin Türkiye içindeki etkinliklerini TÜBİTAK-EEEAG desteği ile sürdüren projedir.

Projede endüstriyel uygulamaya yönelik olarak SDL dili üzerinde betimlemeler, SDL/COSPAN derleyicisi gibi yazılım aygıtları, entegre donanım/yazılım tasarımı için tanımlar ve aygıtlar ve doğrulayıcılar üzerinde karmaşıklık azaltan (complexity relief) teknikler geliştirilmiş ve bunun yanısıra uyum sınama (conformance testing) ve ayrık olay dizgeleri (discrete event systems) üzerinde kuramsal çalışmalar yapılmıştır.

## İÇİNDEKİLER

| ÖZET (ARSTRACT)                                              |

|--------------------------------------------------------------|

| 1 - GİRİŞ6                                                   |

| 1.1 - AVRUPA TOPLULUĞU ÇERÇEVESİNDE COST 247 PROJE           |

| PLATFORMUNUN OLUŞUMU VE ETKİNLİKLER6                         |

| 1.2 - TÜBİTAK COST 247 PROJESİNİN AMACI VE PLATFORMA KATILIM |

| STRATEJISI8                                                  |

| 2 - ARAŞTIRMANIN GELİŞME AŞAMALARI10                         |

| 2.1 - SDL DİLİ ÜZERİNE ÇALIŞMALAR10                          |

| 2.1.2 - SISTEM BETIMLEME10                                   |

| 2.1.2 - SISTEM DOĞRULAMA10                                   |

| 2.2 - UYUM SINAMA12                                          |

| 2.3 - YAN CALIŞMA : AYRIK OLAY DİZGE YAKLAŞIMI14             |

| 3 - YAYINLAR VE TEZLER                                       |

| 3.1 - YAYINLAR16                                             |

| 3.2 - TEZLER                                                 |

| 4 - MALÍ HARCAMALAR                                          |

| 5 - SONUÇ                                                    |

| 6 - EKLERÎN LÎSTESÎ                                          |

| BİBLİYOGRAFİK BİLGİ FORMU                                    |

| EKLER                                                        |

|                                                              |

| Şekil 1 - Protokol katmanları arasında bağlantı 15           |

| Table 1 - Mali Harcamalar                                    |

#### ÖZET

Gerçek zaman iletişim yazılımlarında kullanılan dağımlı yazılımların betimlenmesi ve doğrulanması için iki ticari SDL ürünü olan SDT (Telelogic) ve GEODE (Verilog) paketleri kullanılarak uygulamalar yapıldı ve yeni teknikler geliştirildi. Özellikle Lucent Technologies'de geliştirilmiş olan COSPAN doğrulayıcısının SDL platformunda kullanılabilmesi için SDL-S/R derleyicisi gerçekleştirildi ve SDL dili ile COSPAN doğrulayıcısının donanım/yazılım entegre tasarımı (HW/SW co-design) için genişletilmiş SDL tanımı yapıldı Bunun yanısıra SDL kullanımında durum patlaması olarak anılan karmaşıklık sorununa çözüm getirmek üzere teknikler geliştirildi.

#### **ABSTRACT**

In order to specify and validate embedded real-time software used in communication systems the commercial products SDT and GEODE were applied to numerous examples and techniques were developed for that purpose. In particular to use COSPAN verifier developed at Lucent Technologies within an SDL platform a restricted SDL to S/R compiler was implemented and SDL was extended as the first step of implementing a HW/SW codesign tool using the COSPAN verifier. In addition complexity relief techniques were developed to overcome the problem of state explosion when using SDL

#### 1 - GİRİŞ

1.1 - AVRUPA TOPLULUĞU ÇERÇEVESİNDE COST 247 PROJE PLATFORMUNUN OLUŞUMU VE ETKİNLİKLERİ

COST 247 projesinin bir Avrupa Topluluğu COST projesi olarak oluşumunun ilk tohumları 10-13 Aralık 1992 tarihinde Ankara'da yapılan bir ön çalıştay ( preliminary workshop )ile atıldı. Bu çalıştayda 9 Avrupa ülkesinden katılan temsilciler kendi istek ve araştırma ilgi alanlarını ortaya koyarak COST Telekomünikasyon grubu içinde yer alacak ve telekom yazılımlarına ilişkin sorunları içerecek bir projeyi yönlendirdiler (bkz. Ek 1). Bu aşamadan sonra COST kuruluşuna yaptığımız proje başvurusu (bkz. Ek 2) COST Telekom grubu tarafından kabul edildi ve katılım kararları ülkelerin imzalarına açıldı. Kurucu toplantı (inaugural meeting) 9 Aralık 1993 tarihinde Brüksel'de gerçekleşti. Ancak COST kuruluşunun bir gereği olarak projenin resmen başlaması için en az 5 COST üyesi ülkenin büyükelçiliklerinin imzalarının daha yer almamış olması nedeniyle resmi başlangıç 14,15 Mart 1994 tarihinde yapılan Utrecht yönetim kurulu toplantısında gerçekleşti. Bu toplantıda, katılan ülke temsilcilerinden oluşan COST 247 yönetim kurulu, öneriyi yapan ülkenin temsilcisi K. İnan'ı proje başkanlığına ve Fransa temsilcisi S. Budkowski'yi ikinci başkanlığa seçti. Aynı toplantıda 4 ayrı çalışma grubu (ÇG) ve başkanları :

- (1) E-LOTOS grubu (H. Garavel, Fransa),

- (2) Biçimsel betimleme analiz ve doğrulama grubu

- (J. F. Groote, Holanda),

- (3) Uyum sınaması grubu (K. Tarnay, Macaristan),

- (4) Simülasyon ve başarım analizi grubu (P. Dembinski, Polonya),

olarak belirlendi. Üç yıllık bir proje olan ve 18 Avrupa ülkesinin katıldığı COST 247 projesi 1996 Aralık ayında sona erdi ve üye ülkelerin isteği ve COST Telekom grubunun onayı ile Aralık 1997 tarihine kadar uzatıldı. Bu tarihte COST kuruluşuna yapılan tüm sunuş özetleri ve diğer etkinlikleri içeren dokümanlarla beraber bir sonuç raporu olarak COST'a sunuldu (bkz. Ek 3) . Bu süre içinde hemen hepsi iki gün süren ve yarım günü yönetim kurul toplantısı ve kalan sürenin teknik sunuşları içerdiği 11 toplantı yapıldı. Bu toplantılara ek olarak 5 tane özel çalıştay toplantısı, bu çalıştay toplantılarından iki tanesinin proceeding 'lerini ve Science of Computer Programming , vol. 29, No. 1 & 2 sayısının "Methods of Software Design : Techniques and Applications" teması altında özel COST 247 sayısını içeren yayın etkinlilerini ve COST tarafından finanse edilen karşılıklı kısa süreli ziyaretleri (short term missions) ve E-LOTOS grubunun özel bir çıktısı olan LOTOS dilinin teknolojik gelişmelere uyumlu bir sonraki versiyonunun ITU standardlarını COST 247 platformunun çıktıları arasında sayabiliriz.

COST 247 projesi COST Telekom grubu içinde telekom yazılımları (embedded real-time software) son derece kritik bir alanı kapsayan önemli bir boşluğu dolduruyordu. İlgili alanının genişliği, yazılıma ilişkin konuların ticari boyutunun getirdiği özellikler — yani ticari değere sahip bir yazılım ürünü geliştirmenin gerektirdiği bütçenin, COST 247 bütçesinin çok üstünde olması — COST 247 projesini ortaklaşa yürütülen tek amaçlı bir proje yerine, çok amaçlı bir bilgi alışverişi platformu olarak gelişmesini gerektirmiştir. EEEAG COST 247 projesi de bu genel platforma katılan ve daha önce desteklenen EEEAG Yazılım 2 projesinin birikimleri üzerine sürdürülen bir proje olarak gelişti.

## 1.2 - TÜBİTAK COST 247 PROJESININ AMACI VE PLATFORMA KATILIM STRATEJISI

EEEAG COST 247 projesi Türkiye'nin kendi önermiş olduğu COST 247 projesine katılımını sağladı. Bu projeyi, gerek birikim, gerek oluşmuş olan altyapı açısından COST 247 ile yaklaşık 9 aylık bir çakışma süresi olan ve onun doğmasını sağlayan EEEAG Yazılım 2 projesinin devamı olarak nitelemek gerekir. Türkiye'deki telekomünikasyon sektörünün görece gelişmişliği belirleyici bir veri olarak alındı ve buna bağlı olarak yaklaşım stratejimizde birkaç istisna dışında akademik yön yerine, pratik yöne daha fazla ağırlık verildi. Örneğin pratik kullanım boyutu gitgide kaybolan LOTOS ve ESTELLE gibi akademik dünyanın doğurduğu dillere ilişkin çalışmalara yer

verilmedi. Bunun yerine ticari uygulaması gitgide yaygınlaşmakta olan SDL diline yönelik çalışmalar ön plana alındı. SDL dilinin ticari kullanım ürünü olarak pazarlanan İsveç kökenli Telelogic şirketinin SDL ürünü olan SDT paketi ile Fransa kökenli Verilog şirketinin SDL ürünü olan GEODE paketi çalışma boyunca kullanıldı ve COST 247 platformu içinde bu ürünleri kullanan gruplar ile yakın ilişki kuruldu. EEEAG Yazılım 2 projesi içinde satın alınmış olan SDT paketinin bir sonraki versiyonu olan nesneye yönelik ve SDL 92 dilini içeren yeni SDT paketinin GEODE ile beraber ücretsiz olarak sağlanabilmesinde COST 247 platformu içindeki liderlik konumumuz önemli rol oynadı. Bunun yanısıra, EEEAG Yazılım 2 projesinden beri incelemekte ve kullanmakta olduğumuz Bell-Labs'de geliştirilen COSPAN doğrulayıcı aygıtının FormalCheck adlı bir donanım doğrulayıcısı olarak piyasaya sürülmesi de, pratik uygulamalar konusundaki öngörülerimizi doğrular nitelikte oldu. Proje boyunca karşılaştığımız en büyük zorluk, genelde yazılım sanayilerinin, mütevazi araştırma kaynaklarını aşan ticari boyutları ve bu boyutların gerektirdiği insan ve finansman kaynaklarına erişememizden doğdu. Başta TÜBİTAK Doprog programı ile getirmiş olduğumuz ve daha sonra NATO desteği, sanayi desteği (TELETAŞ projesi) ve TÜBİTAK-BİLTEN desteği ile projede çalışan Rus bilgisayarcıları V. Levin ve E. Bouminova'nın Bell-labs tarafından kendi ticari atılımlarında ( FormalCheck ) kullanılmak üzere işe alınması, bu görüşümüze somut bir örnek oluşturmakta.

### 2 - ARAŞTIRMANIN GELİŞME AŞAMALARI

2.1 - SDL ÜZERİNE ÇALIŞMALAR

#### 2.1.1 - SISTEM BETIMLEME

SDL dilinin dünya piyasasında iki ticari uygulama aygıtı olan Telelogic SDT ve Verilog GEODE çeşitli uygulamalarda kullanılmıştır. Sistematik bir uygulama EEEAG Yazılım 2 projesi ile çakışan süre içinde gerçekleştirilen TELETAŞ —ALCATEL üretimi Levent Santralının seçilmiş bazı işlevlerinin SDL ile betimlenmesidir (bkz Ek 4). Bunun yanısıra yüksek lisans tezlerinden bir bölümü (bkz. Ek 12, tezler : 3,7 ve 8) dolaysız olarak, bazıları da (bkz. Ek 12, tezler : 1,2 ve 9) dolaylı olarak kapsamlı SDL betimlemelerini içermektedir.

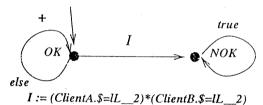

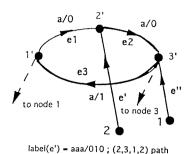

#### 2.1.2 - SISTEM DOĞRULAMA

Projedeki önemli bir etkinlik önce SDL — C++ derleyicisi (animatör) çerçevesinde yapılan ön çalışmalardan sonra (bkz Ek 5 ve Ek 6) SDT ve GEODE gibi ticari ürünlerin varlığında bunun verimli bir yaklaşım olmayacağı düşünülmüş ve proje, SDL—COSPAN derleyici tasarımına dönüştürülmüştür. Bu tasarımdan önce daha önceki çalışmadan yansıyan kısım SDL den herhangi bir dile derleme yapılmasında kullanılan ön yüz (front end) gösteriminin tasarımı ve gerçekleştirimi ile (bkz. Ek 12 tez 6) genel derleyici arayüz tasarım yaklaşımına ilişkin bir yayın yer almaktadır (bkz. Ek 8). Buradaki yaklaşımın altında yatan

motivasyon, betimleme amacı ile kullanımı görece kolay ve yaygın, ancak semantik yapısındaki boşluklardan dolayı doğrulanması zor olan SDL aygıtlarının, tam tersi özelliklere sahip COSPAN ile dengelenmesiydi. Gerçekten de gerek SDT gerek GEODE'un doğrulayıcıları denenerek çok yetersiz bulunmuş ve temas ettiğimiz ve bu aygıtları kullanan sanayiler bu veya başka nedenlerden dolayı aygıtın doğrulayıcısının özelliklerinden pek haberdar olmadıklarını ifade etmişlerdir. Öte yandan daha çok donanım doğrulanması amacı ile geliştirilmiş olan COSPAN'in bir yazılım betimlenme aygıtı olarak kullanılmasının çok kısıtlı olacağı, ancak doğrulama özellikleri son derece güçlü olması nedeni ile SDL-COSPAN derleyicisi ile SDL'e nitelikli bir doğrulayıcı sağlanmış olacağı düşünülmüştür. Söz konusu derleyicide karşılaşılan temel zorluk geniş semantikli SDL'in dar semantikli COSPAN'a (senkron iletişimli sonlu durum makinaları) sığdırılması için gereken varsayım ve kısıtların oluşturulmasıydı (ön sonuçlar için bkz. Ek 7, kullanılan derleyici tasarımı için bkz. Ek 8). SDL-COSPAN derleyicisinin kullanılabileceği diğer bir alan, beraber yazılım/donanım tasarımında (SW/HW co-design) yazılım ekibinin sistem yazılımını SDL ile ; donanım ekibinin ise sistem donanımını COSPAN ile betimlemesi ve yazılım-donanım arabirimleri için SDL diline ek tanımlar getirerek sonuçta tanımlanan tüm sistemi COSPAN'a diline derlemek ve böylece doğrulamayı COSPAN üzerinden yapabilmek olarak tasarımlandı (bkz. Ek 9). Bu tasarımın bir ürüne dönüşmesi aşamasına ülke

içinde bu konuda herhangi bir talep oluşturacak ve ticari boyutlarda destek verecek bir grup olmadığı için varılamadı.

Son olarak yazında kısmi sıra (partial order) teknikleri olarak geçen ve sonlu durumlu makinalarda doğrulamak için erişilmesi gereken durumlarda önemli azaltma sağlamak fikrine dayalı teknikler SDL diline uygulanmış ve doğrulayıcıda sistem karmaşıklığını azaltan kolaylık sağlama teknikleri geliştirilmiş ve uygulanmıştır (bkz. Ek 10 ve Ek 12, A. Şen MS Tezi özeti).

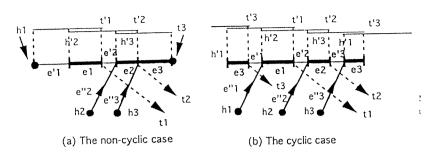

#### 2.2 - UYUM SINAMA

Telekom yazılımları için uyum sınaması konusu sanayide karşılaşılan önemli konulardan biridir. Uyum sınama, belli bir donanım üzerinde yer alan bir yazılımın girdi-çıktı davranış biçiminin verilmiş olan standard davranış modeline uyumlu olmasının sınanmasıdır. Bu konuda yazında yer alan temel kuramsal sonuçlar, sonlu bir girdi-çıktı otomatı modeline uyumu sınamak için sisteme uygulanacak girdi dizininin (denetleme dizini (checking sequence)) hesaplanma ve uygulanma yöntemlerini içermektedir. Uyum modelinin durum sayısının çok olması, hatta birçok durumda sonsuz olması sözkonusu denetleme dizininin hesaplanmasını ve/veya uygulanmasını ya pratik-dışı ya da kuramsal olarak olanaksız kılabilmektedir. Bu durumlarda izlenen yöntem çoğu kez somut pratik senaryolarda oluşabilecek girdi dizinlerinin bir sınama dizini olarak sisteme uygulanması

ve izlenen çıktı dizinlerinin beklenen çıktıklar ile karşılaştırılmasıdır. Bu yöntemin en önemli yetersizliği çoğu kez yakalanması zor sistem hatalarının tipik senaryolarda değil hiç beklenmeyen senaryolarda ortaya çıkmasıdır. Bu tür marjinal senaryolar ise sayıca çok olabildiği için hata yakalama veriminin artması genelde konuya daha sistematik bir yaklaşımı gerektirmektedir. Uyum sınama konusunun pratiğe dönük diğer bir boyutu gerçek zaman içinde testlerin uygulanması için gereken test uygulama mimarilerinin özelliklerinden kaynaklanmaktadır. Özellikle sınanacak sistem cografi olarak dağılımlı bir yapıdaysa sınama mimarisinin de dağımlı olma gereği ortaya çıkmakta ve beraber çalışacak sınama birimleri arasında eşgüdüm gerekmektedir. Pratikte kullanılmak üzere sınama dizinleri ve yöntemleri için geliştirilmiş bir ITU standardı olan TTCN (Tree and Tabular Combined Notation) sınama dizinlerinin sınıflandırılması, betimlenmesi ve sonuçların yorumlanması üzerinde bir notasyon (formel dil) sistemidir. Uygun test dizinlerinin tanımlanması ve sonuçların bir rapor olarak kaydedilmesi TTCN aygıtları sayesinde (örneğin ticari bir ürün olan SDT aygıtının ek bir TTCN aygıtı mevcuttur) kolaylaştırılmaktadır.

Bu proje çerçevesinde uyum sınama konusundaki yaklaşımımız, diğer yönlerdeki yaklaşımımızın tersine, yani kuramsal yönde olmuştur. İki tane MS tezi (bkz. Ek 12, H. Çalgın ve O. Gücün tez özetleri) çeşitli varsayımlar altında optimal denetleme dizinlerinin hesabını içermektedir. Daha sonra Ottawa

Üniversitesinden H. Ural ile beraber bu sonuçlar, yazında dağınık birçok sonucu ve yenilerini içeren bir makale olarak sunulmuş ve basılmıştır (bkz. Ek 11).

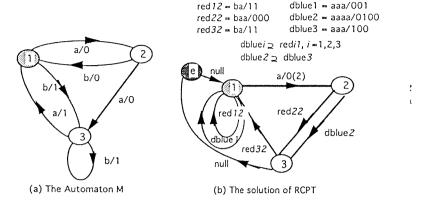

#### 2.3 - YAN CALIŞMA : AYRIK OLAY DİZGE YAKLAŞIMI

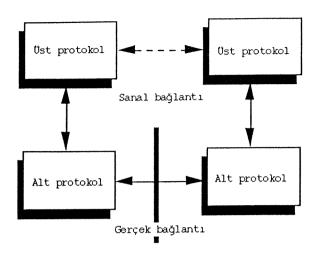

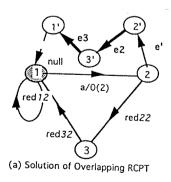

Kontrol ve bilgisayar alanlarının kesişmesinde yer alan ayrık olay dizgeleri disiplini ile incelenen bir konu hiyerarşik danışmalı denetim konusuna ilişkindir. Konu aşağıdaki şekilde görüldüğü gibi alt düzeyde çalışan ve gerçek bağlantıyı sağlayan protokolun üst sisteme yansıtılma sorunudur. Alt düzeydeki protokolun verdiği hizmeti üst düzeyde hangi primitiflerin (ayrık olayların) kontrol edilebildiği ve hangilerinin gözlenebildiğine yansıtılması ve böylece alt düzeyde karmaşıklığı ortadan kaldırarak üst düzeyde yazılabilecek yazılımların otomatik olarak alt düzeydeki gereken programlara derlenebilmesini sağlayacak bir derleme düzeni kurmaktır. Bu konudaki çalışma A. Nergis'in doktora çalışması olarak sonuçlandırılmıştır (bkz. Ek 8; A. Nergis tez özeti)

Şekil 1 — Protokol katmanları arasındaki bağlantı

#### 3 - YAYINLAR VE TEZLER

- 3.1 YAYINLAR

- 1 V. Levin, A. Sulimov, H. Yenigün and K. Inan, "Preliminary Concepts for a C++ Animator Design for SDL 92", published in Russian Academy of Sciences, Novosibirsk Informatics Institute Journal

- 2 V. Levin, H. Yenigün and K. İnan,

- "An Implementation of SDL 92 Communication Semantics",

Proceedings ISCIS X, Oct.30 Nov. 1, 1995, Kuşadası, Turkey,

pp. 457-464.

- 3 O. Başbuğoğlu, K. İnan,

- "Compiling SDL into the Finite State Specification Language Cospan", Proceedings ISCIS X, Oct.30 Nov. 1, 1995, Kuşadası, Turkey, pp. 643-650

- 4 V. Levin, E. Bounimova and K. Inan,

- "An Interface Implementation Using a Compiler Specification Method", Proceedings ISCIS XI, Nov.6-8, 1996, Antalya, Turkey, pp.385-394

- 5 V. Levin, E. Bounimova, O. Başbuğoğlu and K. İnan,

"A Verifiable Software/Hardware Co-design Using SDL and

COSPAN", Proceedings of COST 247 International Workshop on

Applied Formal Methods in System Design, June 17-19,1996

Maribor, Slovenia, pp.6-16.

- 6 H. Yenigün, K. İnan,

- "A Verifiable Software/Hardware Co-design Using SDL and COSPAN", Proceedings of the Second COST 247 International

Workshop on Applied Formal Methods in System Design, June 18-19,1996 Zagrep, Croatia, pp. 11-16.

7 - K. Inan, H. Ural, "Efficient Checking Sequences for Testing Finite State Machines", Journal of Information and Software Technology, vol. 41 1999, pp. 799-812.

#### 3.2 - TEZLER

- 1- "SDL ve ERPAL dillerini kullanarak yapılan süreç belirtmelerinin karşılaştırılması", Ali Sezgin, 1994 ODTÜ Y.L. Tezi

- 2- "Yeni bir cebirsel dil ERPAL ve SDL-92'nin bir altkümesinin ERPAL'e çevrilmesi" , Hüsnü Yenigün, 1995 ODTÜ. Y.L. tezi.

- 3- "Bir abone kimlik birimi yöneticisinin betimleme dili SDL kullanarak gerçekleştirilmesi" , Cenk Tuğçetin, 1995 ODTÜ. Y.L. tezi.

- 4- "Ayırt edici diziler ve uyarlanmış kırsal postacı algoritması kullanarak eniyi uyum sınama dizisi üreten bir yöntemin gerçeklenmesi", Hüsyin Çalgın, 1996 ODTÜ. Y.L. tezi. 5- "Bir sonlu durum makinası için tanımlayıcı kümeler kullanarak test dizisi üretimi", Onur Gücün, 1996 ODTÜ. Y.L. tezi.

- 6- "SDL 92 derleyicisi ön-yüzünün tasarımı ve geliştirilmesi", Uygar Doyuran, 1996 ODTÜ. Y.L. tezi.

- 7- "ISDN katmanının SDL 92 kullanılarak belirtimi ve geçerlilik sınaması", Doğuş Çenberci, 1997 ODTÜ. Y.L. tezi.

- 8- "XPRESS taşıyıcı protokolunun SDL 92 kullanılarak belirtimi ve geçerlilik sınaması" , İsmail Dalkıran, 1997 ODTÜ. Y.L. tezi.

- 9- "SDL sistemlerinin kısmi sıralama metodları ile doğrulanması" , Alper Şen, 1997 ODTÜ. Y.L. tezi.

- 10- "Ayrık olay dizgeleri için kontrol içerme/seçme yaklaşımı ve katmanlı kontrole uygulanması" , Aydın Nergis, 1997 ODTÜ. Doktora tezi.

- 11- "Uyum sınaması üretilmesi için algoritmalar" , Burak Serdar, 1998 ODTÜ. Y.L. tezi.

#### 4 - MALÍ HARCAMALAR

| COST-247   | PERSONEL      | TEÇHİZAT    | SARF        | SEYAHAT       | HIZMET      | BILGI İŞLEM | KIRTASIYE   | DIGER       | TELIF        | TOPLAM        | AÇIKLAMA      |

|------------|---------------|-------------|-------------|---------------|-------------|-------------|-------------|-------------|--------------|---------------|---------------|

| ODENEK94   | 300.000.000   | 700.000.000 | 50.000.000  | 300,000,000   | 20.000.000  |             | 40.000.000  | 40.000.000  |              | 1.450.000.000 |               |

| AKTARMA    | 103.000.000   |             |             | -103.000.000  |             |             |             |             |              | 0             |               |

| R.ÖDENEK94 | 403.000.000   | 700.000.000 | 50.000.000  | 197.000.000   | 20.000.000  | 0           | 40.000.000  | 40.000.000  | 0            | 1.450.000.000 |               |

| HARCAMA94  | 291.044.090   | 0           | 410.000     | 143.851.663   | 2.104.500   | 0           | 1.000.000   | 24.716.000  | 0            | 463.126.253   |               |

| KALAN94    | 111.955.910   | 700.000.000 | 49.590.000  | 53.148.337    | 17.895.500  | 0           | 39,000,000  | 15.284.000  | 0            | 986.873.747   |               |

| ODENEK95   | 720.000.000   |             | 50.000.000  | 300.000.000   | 35.000.000  |             | 30.000.000  | 70.000.000  | 200,000,002  | 1.405.000.000 |               |

| A.ÖDENEK95 | 831.955.910   | 700.000.000 | 99.590.000  | 353.148.337   | 52.895.500  | 0           | 69.000.000  | 85.284.000  | 200.000.000  | 2.391.873.747 |               |

| AKTARMA    |               | -55.000.000 |             |               | 55.000,000  |             |             |             |              | 0             |               |

| R.ÖDENEK95 | 831.955.910   | 645.000.000 | 99.590.000  | 353.148.337   | 107.895.500 | 0           | 69.000.000  | 85.284.000  | 200.000.002  | 2.391.873.747 |               |

| HARCAMA95  | 385.614.774   | 574.627.500 | 58.176.650  | 256.952.866   | 40.000.000  | 0           | 51.825.902  | 64.266.500  | 39.200,000   | 1.470.664.192 |               |

| KALAN95    | 446.341.136   | 70.372.500  | 41,413,350  | 96.195.471    | 67.895.500  | 0           | 17.174.098  | 21.017.500  | 160.800.000  | 921.209.555   |               |

| ODENEK96   | 864.000.000   |             | 50.000.000  | 400.000.000   | 45.000.000  |             | 30.000.000  | 90.000.06   | 325.000.000  | 1.804.000.000 |               |

| A.ÖDENEK96 | 1.310.341.136 | 70.372.500  | 91.413.350  | 496.195.471   | 112.895.500 | 0           | 47.174.098  | 111.017.500 | 485.800.000  | 2.725.209.555 |               |

| AKTARMA    |               | -70.372.000 | 70.372.000  |               |             |             |             |             |              | 0 1           | 0 12.9.96     |

| AKTARMA    |               |             | 200.000.000 |               |             |             |             |             | -200.000.000 | 0 1           | 0 11.11.96    |

| R.ÖDENEK96 | 1.310.341.136 | 200         | 361.785.350 | 496.195.471   | 112.895.500 | 0           | 47.174.098  | 111.017.500 | 285.800.000  | 2.725.209.555 |               |

| HARCAMA96  | 1.052.820.777 | 0           | 228.794.736 | 232.780.642   | 5.750.000   | 0           | 47.130.546  | 109.512.000 | 8.400.000    | 1.685.188.701 |               |

| KALAN96    | 257.520.359   | 200         | 132.990.614 | 263.414.829   | 107.145.500 | 0           | 43.552      | 1.505.500   | 277.400.000  | 1.040.020.854 |               |

| ODENEK97   | 216.000.000   |             |             |               |             |             |             |             | 225.000.000  | 441.000.000   |               |

| A.ÖDENEK97 | 473.520.359   | 200         | 132.990.614 | 263.414.829   | 107.145.500 | 0           | 43.552      | 1,505,500   | 502.400,000  | 1,481,020,854 |               |

| AKTARMA    |               |             | 100.000.000 |               |             |             |             |             | -100.000.000 | 0 2           | 0 28.4.1997   |

| AKTARMA    |               | 402.400.000 |             |               |             |             |             |             | -402.400.000 | 0             | 0 13.5.1997   |

| EK ÖDENEK  |               |             |             | 250.000.000   |             |             |             |             |              | 250.000.000   |               |

| R.ÖDENEK97 | 473.520.359   | 402.400.500 | 232.990.614 | 513.414.829   | 107.145.500 | 0           | 43.552      | 1.505.500   | 0            | 1.731.020.854 |               |

| HARCAMA97  | 444.975.052   | 270.412.725 | 233.362.588 | 490.217.448   | 0           | 0           | 0           | 0           | 0            | 1.438.967.813 |               |

| KALAN97    | 28.545.307    | 131.987.775 | -371.974    | 23.197.381    | 107.145.500 | 0           | 43.552      | 1.505.500   | 0            | 292.053.041   |               |

| T.ODENEK   | 2.203.000.000 | 977.028.000 | 520.372.000 | 1.147.000.000 | 155,000,000 | 0           | 100.000.000 | 200.000.000 | 47.600.000   | 5.350.000.000 | HARCAMA ORANI |

| T.HARCAMA  | 2.174.454.693 | 845.040.225 | 520.743.974 | 1.123.802.619 | 47.854.500  | 0           | 99.956.448  | 198.494.500 | 47.600.000   | 5.057.946.959 | 0,95          |

| T.KALAN    | 28.545.307    | 131.987.775 | -371.974    | 23.197.381    | 107.145.500 | 0           | 43.552      | 1.505.500   | 0            | 292.053.041   |               |

#### 5 - SONUÇ

EEEAG COST 247 TÜBİTAK projesi, tarafımızdan önerilip sürdürülmüş olan genel COST 247 projesine Türkiye'nin katılımını finanse etmiştir. Bu proje çerçevesinde çeşitli Avrupa ülkelerinde biçimsel yöntemleri telekom yazılımlarının tasarımında kullanan gruplar ile ilişki kurulmuş ve bu alanda geniş bir deneyim kazanılmıştır. Proje süresi içinde üretilmiş olan makale, bildiri ve diğer yayınların yanısıra üretilen en önemli yazılım ürünü SDL—COSPAN derleyicisi olmuştur. Bu yazılımın üretilmesindeki kazanılan deneyim, bu konuda Türkiye'de bir ticari girişim olmadığı için Lucent Technologies (Bell—labs) içinde süren ticari boyutlu çalışmalara, gerek ürün, gerekse yetişmiş eleman (V. Levin, E. Bounimova ve H. Yenigün) olarak katkıda bulunmuştur.

Projenin geleceğe yönelik olarak yapacağı katkılardan bazıları gerçekleşmiş sayılabilir. Örneğin doğrulama sorununda karmaşıklığı aşmak için geliştirilmiş olan yöntem endüstriyek uygulamada kullanılabilecek boyutta ayrıntılandırılmış ve bugün Lucent tarafından ticarileşmiş olan donanım doğrulayıcısı FormalCheck aygıtına entegre olmaya hazır duruma getirilmiştir. Bu çalışma başından sonuna kadar projede çalışmış olan H. Yenigün'ün Murray Hill, Lucent Technologies'de sürdürdüğü çalışmanın ürünü olup aynı zamanda da ODTÜ'de tamamlamış olduğu doktora tezinin çekirdeğini oluşturmaktadır.

Aynı şekilde projede başlatılmış olan ve SDL-COSPAN bileşik aygıtının HW/SW entegre tasarımı olarak son hale getirilmesi projede yer alan V. Levin tarafından *Lucent Technologies*'de sürdürülmektedir.

SDL Türkiye'de hemen hemen tüm telekom yazılımı ile ilişkili olan kuruluşlarca (ASELSAN, BAŞARI, ALCATEL, NETAŞ vb.) kullanılmaktadır. Bu nedenle özellikle SDT ve benzeri SDL ürünleri ile yakın ilişki içinde olan NOKIA, ERICCSON, NORTEL gibi dev telekom şirketlerinin desteğinde yürüyen araştırmaları ve özellikle çeşitli Avrupa ülkelerinde yürütülen standardizasyon ve uygulama etkinliklerini izleyip Türkiye'deki şirketlere bilgi ve know-how aktaracak araştırmalara şiddetle ihtiyaç duyulacaktır. Bu tür araştırmalar bu projenin doğal devamı olarak görülebilir.

#### 6 - EKLERÍN LÍSTESÍ

- Ek 1 COST 247 Preliminary Workshop

- Ek 2 COST 247 Proposal

- Ek 3 COST 247 Final Report

- Ek 4 Levent Santralı TELETAŞ Projesi (EEEAG Yazılım 2 Projesi)

- Ek 5 V. Levin, A. Sulimov, H. Yenigün and K. İnan,

"Preliminary Concepts for a C++ Animator Design for SDL 92",

published in Russian Academy of Sciences, Novosibirsk

Informatics Institute Journal (EEEAG Yazılım 2 Projesi)

- Ek 6 V. Levin, H. Yenigün and K. İnan,

"An Implementation of SDL 92 Communication Semantics",

Proceedings ISCIS X, Oct.30 Nov. 1, 1995, Kuşadası, Turkey,

pp. 457-464.

- Ek 7 O. Başbuğoğlu, K. İnan,

"Compiling SDL into the Finite State Specification Language

Cospan", Proceedings ISCIS X, Oct. 30 Nov. 1, 1995, Kuşadası,

Turkey, pp. 643-650

- Ek 8 V. Levin, E. Bounimova and K. İnan, "An Interface Implementation Using a Compiler Specification Method", Proceedings ISCIS XI, Nov.6-8, 1996, Antalya, Turkey, pp. 385-394

- Ek 9 V. Levin, E. Bounimova, O. Başbuğoğlu and K. İnan,

"A Verifiable Software/Hardware Co-design Using SDL and

COSPAN", Proceedings of the First COST 247 International

Workshop on Applied Formal Methods in System Design, June 1719,1996 Maribor, Slovenia, pp. 6-16

- Ek 10 H. Yenigün, K. Inan, "A Verifiable Software/Hardware Co-design Using SDL and COSPAN", Proceedings of the Second COST 247 International Workshop on Applied Formal Methods in System Design, June 18-19,1996 Zagrep, Croatia, pp. 11-16.

- **Ek 11** K. Inan, H. Ural, "Efficient Checking Sequences for Testing Finite State Machines", Journal of Information and Software Technology, vol. 41 1999, pp. 799-812.

- Ek 12 Tez Özetleri

### PROCEEDINGS OF THE PRELIMINARY WORKSHOP ON COST 247 PROJECT ON VERIFICATION/VALIDATION AND TESTING OF SOFTWARE USING FORMAL SPECIFICATION TECHNIQUES

2 - 4 December, 1992, Ankara-Turkey

This proceedings consists of the revised contributions of the participants of the COST 247 preliminary workshop held in Bilkent Hotel, Ankara, during 2-4 December, 1992. The proceedings also contains a revised version of the original proposal submitted to and accepted by the TCT of COST. The revised proposal has taken into account the views, experiences and research interest areas of the participants of the workshop.

The purpose of the workshop was to establish a preliminary focus on the main areas of interest of the potential participants of COST 247 before the formal commencement of the project. Consequently the contents of this proceedings does not necessarily reflect a technically coherent set of original articles or presentations of a specific area of research, rather it consists of documents reflecting the areas of interest and experience and organizational structure of various institutions ranging from research departments of coorporations to public or private research institutions to universities within 11 different European countries including Turkey. Whereas some of the presentations emphasize details of technical results, most are structured in terms of institutional identifications in terms of past and current research experience and position statements vis-a-vis COST 247.

At the concluding session of the workshop the participants were explicitly asked what their research areas of interest were in the context of COST 247. Below we itemize a resume of these areas based on the responses of the participating representatives of the institutions.

#### Preliminary Areas of Interest for COST 247

- (1) Conformance Testing (special emphasis on real world examples and exploitation of systematic divide-and-conquer and use of black-to-gray box information contents)

- (2) SDL '92 methodology (tool building, extensions, simulation and verification for object oriented specs., intermediate petri-net modeling etc.)

- (3) Simulation (both logical and performance simulations using FDTs)

- (4) Real-time specification (semantics and verification issues)

- (5) Case studies to analyze and evaluate tools

- (6) Complexity relief techniques for finite state verification

- (7) Investigating relations between specification styles vs. verification and implementations, between verification vs. conformance testing.

- (8) Specification assessment by reviews

- (9) Hardware (VLSI) verification (symbolic or finite state)

The revised version of the COST 247 proposal reflects the areas of interest given above, but is formulated in a somewhat more general language to allow a space for other potential COST 247 participants interested in formal verification/validation techniques.

There has been a consensus within participants on the view that practical applications and reviews of techniques should reflect the problems of real life and not simplistic pet examples of restricted academic interest. This, of course, does not preclude in the research agenda of COST 247 untackled theoretical issues that may bear relevance and promise for future applications.

In terms of the use of existing specification languages interest was mostly on SDL - as the most commonly used tool in industry with a new version SDL '92 on the way - and LOTOS, although there was one representative that expressed interest on the use of ESTELLE as the formal language tool to develop performance simulation models from formal specifications. Again this does not preclude the use of other specification formalisms - such as special real time formalisms - in the research agenda.

The preliminary workshop on COST 247 is believed to have served its purpose. Namely, representatives from a wide ranging set of institutions and nations have converged on areas of research relevant to the application of formal techniques to verification/validation and related problems of software engineering. Thus the management committee, in its first meeting for COST 247, shall be in possession of a preliminary document and the anticipation of the members based on this document shall be of considerable assistance to set the detailed research agenda for COST 247.

February 4, 1993

Prof. Dr. Kemal Inan Coordinator of the workshop and COST 247 Electrical & Electronics Engineering Dept. Middle East Technical University Ankara, Turkey

## GENERAL DESCRIPTION OF THE PROJECT (revised version, February 4, 1993)

#### 1 - Purpose

The purpose of the project is the coordination of national efforts to analyze classify and come up with new and efficient techniques and tools for concurrent software verification/validation, mostly in the context of existing standardized formal software specification languages; apply and test the results on selected realistic problems in contemporary distributed communication architectures. The emphasis of the research shall be on the applicability of techniques/tools to realistic hence complex examples.

#### 2 - Objective

Presently three formal specification languages, SDL, ESTELLE and LOTOS have become a part of international standards. Among these, SDL is the most commonly used one in communication industries and present research efforts are along the direction of industrializing the other two, especially LOTOS. In addition to these languages there is a considerable amount of specification languages and techniques for concurrent systems suggested by academic or other research bodies. An interesting example is the COSPAN specification language developed in AT&T for which a timing verification tool is recently implemented and is reported to be operational.

A crucial aspect of a formal description method is the technique/tool used to verify/validate a given formal specification against another given formal representation. On the other hand realistic and complex problems do not easily allow for exhaustive verification or symbolic proof systems used for verification and the usual industrial practice is to be content with logical simulation using reasonable simulation scenarios to verify a specification in some vague sense. Similarly generating conformance test sequences for complex examples is again based on suggestive scenarios of functional divide-and-conquer types. A principal objective of this research project is to investigate the possibility of tackling complex problems by studying the problem-specific, language-specific and style-specific aspects of existing simulation, verification and testing methods and suggest innovative and relatively more systematic techniques/tools especially exploiting the decomposability properties - of validation for complex and preferably future-oriented architectures such as mobile and high performance networks. The results of the project will further the efficiency of software production cycle for complex distributed systems.

Most automated verification techniques used for complex formal languages are based on mapping the original specification into some intermediate model such as a finite state machine or a petri-net (or some finite state  $\omega$ -automaton when liveness problems are of concern), and apply the verification tool to the simplified model. Both the mapping involved and the complexity reduction techniques used for the simplified model are problem, language and specification-style dependent and require careful classification efforts to match the validation technique to the underlying problem. By focusing the research efforts to particular but representative selected examples, it may be possible to evaluate the efficiency of validation for the existing techniques, exhibit their limitations and suggest new and more effective approaches for the specific representative cases.

In addition to the review of validation and testing methodology for large realistic problems the research agenda shall also allow for the study of selected current theoretical and practical problems of interest. One such current research area is the area of real time semantics and verification. Concrete examples of industrial real time specification problems shall be of considerable value in order to differentiate between and evaluate numerous real time semantics and verification techniques that have appeared in the literature. Some of the recent research results (see remarks on COSPAN above) on real time, finite state verification using versions of temporal logic are already being applied to realistic examples and worth further investigation.

#### 3 - Study Method

The study shall involve different specification and verification methods applied to representative examples involving specification refinement steps, timed specification (software or hardware), dynamical architectures such as in mobile networks, performance simulation from formal specifications etc. The three year study shall consist of the following steps (diversity of topics may lead to seperate working groups):

Phase 1 (year 1)

#### (a) Complex systems

- characterization of source material relevant to realistic verification and validation problems

- characterization of source material on conformance test generation with special emphasis on gray box assumptions

- selection of specification examples and, if possible, exchange of specifications written in a particular language (SDL, LOTOS) for the purposes

of joint review of styles, tools (e.g. new styles and/or tools for SDL '92), verifiability and testability

#### (b) Real time systems

- characterization of source material on real time semantics and validation with an emphasis on practical verifiability

- choosing exemplary real time specification and verification problems (could be software or hardware).

- review of tools for real time verification

#### (c) Performance Simulation using FDTs

- Suggestions for a framework for using FDTs for stochastic timed (performance) simulation in the context of a specific language

- Design and implementation of a performance simulator based on the given FDT

- (d) Other research problems in verification (hardware verification, use of theorem provers etc.)

Phase 2 (year 2)

#### (a) Complex systems

- Review and classification of specification style, verification, implementation, testing and other (possibly language or problem specific) kinds of problems that arise in <u>complex</u> examples and suggestions for improved methodology, techniques and tools

- Preparing the framework for applying improved methodologies or techniques or preliminary design of an improved tool for the kind of complex examples in question. This may be in the area of disciplined specification, verification, implementation (code generation) or conformance test generation

#### (b) Real time systems

- Experimentation of real time specification and verification using a selected language/tool on the problems selected

- Review of the theoretical and practical aspects based on the results of experimentation and suggestions for more efficient techniques/tools

#### (c) Performance Simulation using FDTs

- Design and implementation of a performance simulator based on the given FDT (Cont')

- Experimentation on the developed performance simulator on a given example

- (d) Other research problems in verification

Phase 3 (year 3)

#### (a) Complex systems

- Choosing and experimenting on examples to apply the improved methodology and techniques and/or implementation of new tools for such purposes

- Review and exchange of the results obtained on complex systems

(b) Real time systems

- Design and partial implementation of verification tool(s) for general or specific kinds of real time specification problems

- (c) Performance Simulation using FDTs

- Review and evaluation of the performance simulator and developing a unified theoretical framework for performance specification and verification

- (d) Other research problems in verification

#### 4 - Forms of Cooperation

The suggested cooperation within the project shall require the national delegates to:

- attend the meetings of the Management Committee: two to four meetings annually

- participate in setting up an active programme fitting with the objectives and the timing of the project

- coordinate the software requirements, tool exchange and experimentation examples for the national working groups.

- exchange the theoretical or empirical results of the national working group studies

- try to inform the national working groups on the results of the ongoing EC projects on formal methods

## **COST 247 Final Report**

COST 247 was originally conceived of in 1992 and a preliminary workshop was held in Ankara, Turkey in December 1992. In this workshop there were representatives from industry, research organizations and universities from 10 different member countries of COST and the proceedings of this workshop contained position statements, including institutional settings and research interests of potential participants in the project. Broadly based on the outcome of this workshop the actual proposal was presented to COST during 1993 and was open to the signatures of member country representatives during 1993 after it was officially approved by COST. The inaugural meeting for the action was held in Brussels during December 1993 which has set the official starting date for the action.

The administrative body of the action, namely the management committee (MC), consists of the action chairman (K. Inan, Turkey), action vice-chairman (S. Budkowski, France), chair of working group 1 (WG1) on E-LOTOS (enhanced LOTOS) standardization activities (H. Garavel, France), chair of WG2 on verification and analysis of formal specifications (J. F. Groote, Netherlands), chair of WG3 on conformance testing of communication software based on formal methods (K. Tarnay, Hungary), chair of WG4 on simulation and performance models using formal description techniques (P. Dembinski, Poland), and 2 delegates from each member country (the chair persons above are part of the 2 delegate teams from each country).

During the total duration of the action - four years after a one year extension request that was accepted in 1996 - the following activities took place:

## (I) MC meetings and regular technical presentations

1st (inaugural) MC meeting : December 9,1993, Brussels, Belgium,

2nd MC meeting: 14,15 March, 1994, Utrecht, Netherlands,

3rd MC meeting: 19,20 September, 1994, Evry, France,

4th MC meeting: 9,10 February, 1995, Berlin, Germany,

5th MC meeting: 12,13 June, 1995, Warsaw, Poland,

6th MC meeting: 26,27 October, 1995, Budapest, Hungary,

7th MC meeting: 12,13 February, 1996, Madrid, Spain,

8th MC meeting: 17,18 June, 1996, Maribor Slovenia,

9th MC meeting: 4,5 November, 1996, Antalya, Turkey,

10th MC meeting: 18,19 June, 1997, Zagrep, Croatia,

11th MC meeting: 15,16 October, 1997, Stirling, UK,

#### (II) Workshops

- (i) Preliminary workshop on COST 247, 10-13 December, 1992, Ankara, Turkey

- (ii) WG1 workshop on E-LOTOS , 19,20 July, 1994, Brighton, UK,

- (iii) WG3 workshop on conformance testing, 7,8 September, 1995, Evry, France,

- (iv) COST 247 1st International Workshop on Applied Formal Methods In System Design , 17-19 June, 1996, Maribor, Slovenia,

- (v) WG3 workshop on conformance testing, 9-11 September, 1996, Darmstadt, Germany

- (v) COST 247 2nd International Workshop on Applied Formal Methods in System Design , 18 19 June 1997, Zagreb, Croatia.

- (vi) WG3 workshop on conformance testing, 8-10 September, 1997, Cheju, Korea

#### (III) Publications

(i) Proceedings of 1st International Workshop on Applied Formal Methods In System Design , June 1996, Maribor, Slovenia,

(ii) Proceedings of 2nd International Workshop on Applied Formal Methods In System Design, June 1997, Zagrep, Croatia, (iii) Special COST 247 issue of the journal Science of Computer Programming, vol. 29, No. 1 & 2, July 1997, under the theme "Methods of Software Design: Techniques and Applications" edited by J. F. Groote (WG2 chairman) and M. Rem.

#### (IV) Short Term Missions

(i)

Host : Prof. Ken Turner, Stirling University, UK.

Visitor: Prof. G. Csopaki, Budapest University, Hungary

Date of visit : 3-10 August, 1996

Nature of the work : Modeling digital logic in SDL and HW/SW codesign

(ii)

Host: Steve Schneider, Royal Holloway University, London, UK Visitors (COST 247): Guy Leduc (Liege University), Juan Quemada (Technical University of Madrid), Luis Llana (University of Complutens, Madrid),

Other participants: Lac Leonard (University of Liege), Gualberto Garbay (Technical University of Madrid), Alan Jeffrey (University of Sussex), Jim Davies (University of Reading), Jeremy Brians (University of Reading)

Date of visit : November 13-18, 1994

Nature of work : Converging towards a real-time extension of LOTOS (iii) Host : G. Leduc

Visitors (COST 247): Hubert Garavel (INRIA, Rhones-Alpes), Alan Jeffrey (University of Sussex)

Other participants: Mihaela Sighireanu ( INRIA Rhones-Alpes), Ricardo Pena (University of Complutens, Madrid), Charles Pecheur (University of Liege)

Date of visit : April 22-25,1996

Nature of work : Setting down the basis for the new data types in E-LOTOS

### (V) International Conferences with joint COST 247 participation

IFIP PSTV 13-15 June, 1995, Warsaw, Poland

IFIP IWTCS, 7-10 September, 1995, Evry, France.

Eleventh International Symposium on Computer an Information

Sciences(ISCIS XI) 4-7 November, 1996, Antalya, Turkey.

IFIP IWTCS, 8-10 September, 1997, Cheju, Korea.

#### (VI) Standardization Activities

E-LOTOS standardization activities in former CCITT and present ITU

The rest of the final report are the abstracts of all the papers presented at the technical sessions and/or workhops of COST 247.

## Description

of the joint project of TÜBİTAK SR&DC with ALCATEL-TELETAŞ

## Review of a Design for Centrex - Levent System Using SDL

The project involves the detailed design of the "Centrex" facilities to be integrated into the existing rural switch Levent designed and produced by ALCATEL-TELETAS. The project objectives are stated below.

- (1) The SDL specification of the Centrex features integrated into the existing Levent switch shall be generated. The SDL specification of the features that are relevant to Centrex and that already exist in Levent shall be covered in the final integrated SDL specifications. In case the complete detailed design SDL specifications of the Centrex functions require beyond a 1 man-year effort either a relevant subset shall be covered or the necessary additional human resource shall be recruited subject to the availability of such human resource and the mutual agreement between TELETAŞ and TUBITAK.

- (2) The entire detailed design shall be analyzed (simulation, verification) making use of the tool SDT available in TUBITAK Software Research and Development Center. The outcome of this study shall be reported to TELETAŞ.

- (3) A separate part of the final report shall consist of methodological considerations. In particular throughout the process of writing and analyzing SDL specifications all the bottlenecks and/or suitability of different specification styles or approaches shall be taken into consideration in order to come up with concrete suggestions related to general software methodology that yields maximum efficiency in speed, quality and flexibility (modularity etc.) of the final software product.

- (1) The long term mission of the project is methodological. In particular this project is viewed to be an initial industrial exercise to assess the feasability of a new methodology for software production based on plug-in modularity as in hardware design. Current research efforts in industrial communication software production have focused on the use of object oriented techniques in order to achieve modularity, code re-usability and prototyping. The new standard for SDL, namely SDL '92, is endowed with object oriented facilities and testing the use of these facilities in the context of concrete industrial design examples is of substantial interest to communication and software companies as far as speed and efficiency of software production is involved. In TUBITAK a seperate research team is currently implementing an SDL'92 simulator and is familiar in depth with the associated features of SDL'92. Therefore although the specifications and analysis for Centrex shall be implemented making use of the existing SDL'88 language, effort shall be spend on the design of the object structure (i.e. class hierarchy and object library) for the Centrex example in terms of the concepts of SDL'92. A current European research project that parallels the vision above albeit a closed one is an EUREKA project that focuses on

generating the necessary libraries and the additional process objects in the context of the language C++. The only partners in this industrial project are Bristol IIP and Grenoble IIP.

In order to meet its objectives the following procedure shall be adopted throughout the project:

- (1) There shall be at least 2 points of synchronization between TUBITAK and TELETAŞ in the project:

- (i) After the completion of the top level architecture design by TELETAŞ the outcome shall be disseminated to the TUBITAK research group and from there on both parties shall pursue the detailed design independently. The estimated time for this point of synchronization is the end of June 1994.

- (ii) After the completion of the detailed SDL design specifications the parties shall exchange their versions and a common SDL specification shall be adopted as a result of a mutual consent based on their experiences and design considerations. From there on there shall only be a single SDL specification for further analysis by TUBITAK and for implementation by TELETAŞ. The estimated time for this phase of synchronization is November 1994.

- (2) In addition to these two points of synchronization TUBITAK shall produce 3-monthly reports on the progress of the work carried out and a final conclusive report that contains all the relevant findings and results related to the project summarized above.

- (3) Throughout the project communication of the parties shall be established through an operational communication link (e-mail+ftp, etc.). All the technical discussions as well as software and/or document transforms shall preferably make use of this link.

- (4) TELETAS shall supply TUBITAK with the technical details of the Levent exchange and other relevant information whenever necessary.

- (5) Since the project shall be carried out in the context of the international COST 247 project TUBITAK shall make best use of exploiting the international contacts (workshops, short term missions, etc.) according to the possible demands of TELETAS.

The project shall be a 1 man-year project starting as of June 1, 1994. Any decision to extend the human resource beyond the 1 man-year limit is subject to the mutual agreement between TELETAŞ and TUBITAK.

# PRELIMINARY CONCEPTS FOR A C++ ANIMATOR DESIGN FOR SDL 92 1 1

V. Levin, <sup>2</sup> A. Sulimov <sup>3</sup>, H. Yenigün and K. İnan <sup>4</sup>

#### Abstract

Preliminary considerations for a C++ animator design for SDL 92 are presented as the starting point for the corresponding project. The design involves compiling SDL 92 into C++ code. C++ has been chosen as the target code in a hope to capture the object oriented features of SDL 92 in a straightforward manner. The paper emphasises this point just after the top level considerations.

Keywords: Communication Software, Specification Languages, Compilers, Object Orientation

#### 1 Introduction

SDL (Specification and Description Language) is a formal specification language which is a joint CCITT-ISO standard [1, 2]. Originally conceived for telephony network specification in early 1970ies it was later extended to incorporate data communication systems. Recently the SDL 88 version was updated and a new standard called SDL 92 was issued. SDL 92 incorporates new features that gives it a strong object orientation flavor and for that reason hopes have been invested in it as a productive CASE tool to be used in communication software methodologies .

Possibly owing to its simplicity as practiced by the engineers-in-the-field, SDL is a widely used formal specification language in large communication industries, especially compared to its other two rival formal specification languages LOTOS [3, 4] and ESTELLE [5, 6] which are also CCITT-ISO standards. This is one pragmatic reason for focusing on a software platform to be designed around SDL. Another reason lies in the nature of the complexity of modern communication systems. Whereas rapid developments in electronic hardware and communication media technologies such as fiber optic reduced the costs of mass standardized produced components. The same cannot be stated for the residing software in these components. The complexity of the software for such highly distributed and heteregenous systems are mostly due to distributed communication architectures, heteregenuity of interfaces, existence of multivendor hardware and software environments etc.

<sup>&</sup>lt;sup>1</sup>Research supported by the Scientific and Technical Research Council of Turkey (TÜBİTAK) Projects EEEAG Yazılım 2 and COST 247

<sup>&</sup>lt;sup>2</sup>presently with the Software Research and Development Center (SRDC) of TÜBİTAK, Ankara, Turkey, on leave from the Keldysh Institute, Moscow, Russia.

<sup>&</sup>lt;sup>3</sup>During March - August 1994 he was with SRDC, TÜBİTAK, presently he is at the Institute for Informatics, Russian Academy of Sciences, Novosibirsk, Russia.

<sup>4</sup>both are with the SRDC, TÜBİTAK, Ankara, Turkey.

Producing and maintaing software for such systems can be both time consuming and subject to unexpected errors. A formal tool like SDL 92 possessing object oriented features such as data encapsulation, code re-usability etc. is hoped to answer some of the key needs of current software technologies.

The present paper describes an initial effort along the direction explained in the paragraph above. Exploiting the similarity in the object oriented features of SDL 92 and the language C++, results of a preliminary compiler design are reported. As a first step in establishing a software architecture around SDL 92 it was decided to implement the animator together with the SDL graphical editor, GR/PR and PR/GR converters and other graphical or similar tools required for practical operationality. Future steps shall incorporate building tools such as verifier/validator, code generator for specified lower level platforms, test sequence generator, TTCN [7] editor etc.

1

An animator of a distributed system is a software that has the capability of executing possible sequences of execution of a communicating system. In particular an animator based on SDL generates any feasible sequence of executions of a distributed system with concurrently operating and communicating components formally specified in SDL. Unlike sequential software, errors in concurrent software usually stem from unimagined but possible execution orders of its concurrently operating components. An animator is the simplest validation tool that supports an operational confidence on the specified software by executing typical message exchange scenarios on the specified system. A thorough verification can be done either by a computer aided symbolic proof system or via an exhaustive finite state verifier provided that the computational resources can cope with the system complexity. In terms of the logical priority of the software platform mentioned above, the animator is higher up on the hierarchy since tools like verifier, test sequence validator or code generator shall all make use of the animator in order to generate all or desired execution sequences. Structurally speaking these advanced tools have to make use of and be based on an intermediate (common) core data (process) representation which also forms the backbone of the animator [8].

In the next section we briefly describe the characteristic features of the language SDL 92. In section 3 we present an outline of the SDL-isomorphic C++ structures that capture various aspects of SDL 92 constructs and additional C++ constructs that are used for the purpose of animation and maintaining the synchronization semantics of SDL SDTdefinitions.

### 2 An Outline of SDL 92

In this section we present a brief guided tour of SDL 92. The level of details is no more than to give the reader a flavor of the language and the reader is referred to [9] as a detailed and well-guided source and [2] as the formal standard definition of SDL 92.

SDL has two isomorphic syntactical definitions: graphical and textual. The graphical syntax SDL/GR is suggestive of the architecture of the communication system specified

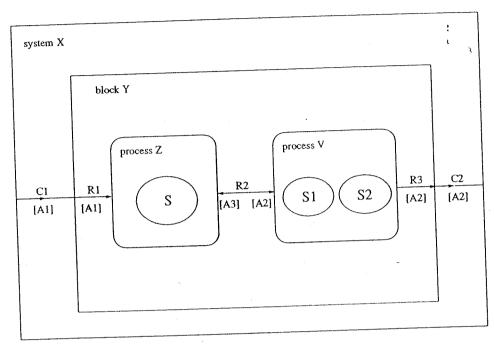

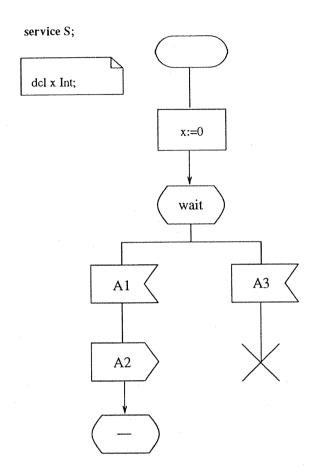

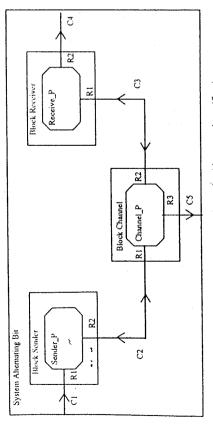

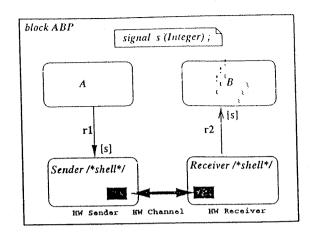

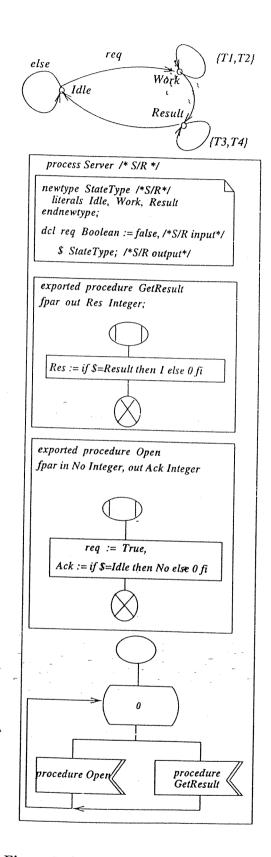

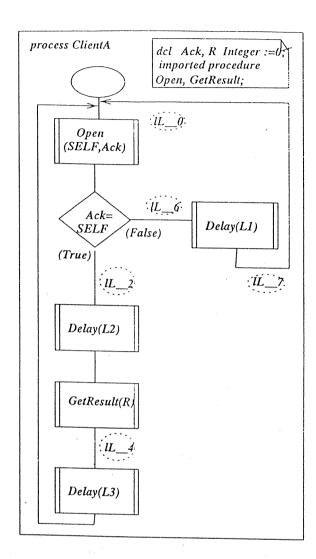

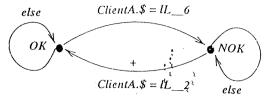

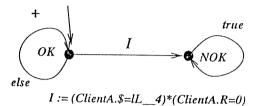

Figure 1: The SDL specification X

and hence much more preferred by the engineers-in-the-field as a tool for specification. An SDL system is composed of SDL blocks as seen in Figure 1. Blocks can be nested and they usually model geographically coherent functional units of a system. Blocks are connected via directed communication channels which model communication links connecting geographically seperated communication units. In SDL a communication channel is defined as a FIFO queue. Unless the channel is specified to be delay-free, the underlying FIFO queue is assumed to be infinite whereas a delay-free channel is a zero length queue forcing spontaneous synchronization on its two end points. Each channel is allowed to carry a set of signals. A signal name signifies a communication message of a specific type with possible parameters of a desired data structure. Time delays occuring in channels are arbitrary so that SDL semantics nondeterministically allow for all execution sequences corresponding to delays within channels that occur arbitrary in space (different channels) and time (different instances).

The innermost unit of a possibly nested hierarchical block structure is called an SDL process. Processes within a block are connected via signal routes which are delay-free channels. Every process in SDL has a Pid (process identification). Processes can dynamically be spawned by other processes. In the Figure 1 the block V is nested inside the system X. Channels from and to the environment are specified by C1 and C2 whereas signal routes R1,R2 and R3 connect processes Y and Z within the block V to each other and to the external channels. Signal name lists for each of the channels and the signal routes are specified, for example channel C1 carrying the signal A1 etc.

Notwithstanding some exceptions such as dynamic process creation, procedure calls etc., processes in SDL can be thought of as generalized finite state machines. Part of the global

state of an SDL process - see input queue below - consists of a location (generalized state) within a generalized finite state transition diagram together with the current value of its internal variables. Each process has a distinct infinite input signal queue that receives signals from other processes via signal routes or channels. Thus the current contents of the input queue constitutes the remaining part of the global state of the process.

The graphical syntax that defines an SDL process is a program flow diagram of communication (read or write) or internal execution sequences. A communication execution is either reading a signal from the input queue of the process or sending a signal to a signal route or a channel that is eventually destined to another process within the system. A simple internal execution is typically an (task) assignment statement or a logical branching. More complex executions involve spawning a child process or calling a procedure. An SDL procedure defined within an SDL process is like a separate SDL process that shares the input queue of the process and may share the variables defined within the calling process. The calling process is frozen until the procedure process terminates and returns to the calling instance of the original calling process.

SDL 92 differs from its previous version SDL 88 in a number of respects. First, instances of SDL entities (e.g. blocks and processes) are differentiated from types of entities. The graphical symbols used for instances and types of entities also differ. In the terminology of object orientation types correspond to classes whereas instances correspond to objects. By defining only the additional transitions for a given process type, new subtype processes can be defined using the inheritance mechanism. Overriding of methods (transitions) within the subtypes is also allowed by using virtual markings for the transitions of the parent process. All this is hoped to make future life easy for a communication software department by reducing the software specification and design methodology to a plug-in type of hardware methodology by an appropriate use of a communication oriented class hierarchy and object library.

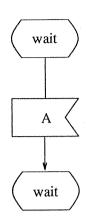

A useful SDL construct is a service block defined within a process. A process can be conceived to consist of one or more service blocks. A service block within a process is in fact like an independent process except that it shares the common input queue and some of the variables of the process. The signals consumed (read) by different service blocks within a process are disjoint and therefore no contention for input can take place. Service blocks operate in a disciplined interleaving order whereby every service block moves from one SDL state (a name given to the states where signals from the input queue are read and consumed) into another while all the remaining service blocks are kept frozen at their respective SDL states. The moving service block is uniquely determined by the contents of the current and common input queue. Service partitioning is useful in designing processes that actually perform concurrent tasks using disjoint sets of messages and sharing the communication buffering resources (input queues).

Finally it is worth noting that SDL has a complicated semantics principally because of its complex and difficult-to-implement synchronization mechanisms. To take an extreme example, if the type of a destination process and a set of channels and/or signal routes are

given then SDL semantics demand that this signal reaches to one such process instance of the type specified nondeterministically provided that currently such an instance exists and a link consisting of channels and signal routes from the outputting source to the instance in question exists that make use of at least one element of the given channel and signal route set  $^5$ .

As to be witnessed in the next section the SDL 92 to C++ translation is not a simple conversion of class and object structures of SDL 92 into the corresponding object oriented structures of C++ and requires intermediate control process structures to meet the animation requirements and to maintain conformance to the SDL semantics.

### 3 C++ Structure of the SDL 92 Animator

Underlying the conceptual intermediate data structure that in turn is translated into C++ structures is a CSP-like process algebra  $^6$  called ERPAL [10, 11]. The abstraction involved in converting SDL programs into C++ structures therefore consists of two steps: the first step is converting the entire operationality of the SDL animator into a new process expression in ERPAL that incorporates auxiliary control processes as well as translations of the original SDL processes and the second step involves converting the ERPAL processes into C++ structures. However because ERPAL has no object orientation features and the intermediate ERPAL steps above can be dissolved within the final transformation into C++ it is preferable to explain the direct translation primitives into C++ and refer to the intermediate process abstractions whenever relevant.

The C++ animator for SDL 92 consists of two parts. The first part consists of general control processes and structures that are common to all SDL 92 programs. In particular there is the process called ControlManager that manages the entire animation steps, another process ShowManager controls the visualization of the animation. Other auxiliary control structures are included in a support library of C++ classes.

The second part of the animator consists of the classes that correspond to the actual block and process types, channels, signal routes etc. of the actual SDL 92 program. The class-that corresponds to a process type in C++ - which in fact is an ERPAL process - is more general than and somewhat different from an SDL process.

More specifically for every process type defined in SDL 92 (there may be no current instance of it!) there exists an ever-present ERPAL process represented by a C++ class called the *PiSet* manager or simply PiSet for that type. This process is responsible for creating, deleting and in general book-keeping (such as keeping a list of the Pid's of all the

<sup>6</sup>An important point to note here is the kind of synchronization semantics used by ERPAL which is rendezvous type that can model the buffered queue synchronization of SDL.

<sup>&</sup>lt;sup>5</sup>In the opinion of the authors of this article this is a very peculiar and a global routing constraint which should fall within the responsibility of the design specifications rather than the synchronization semantics of a language.

live instances) all the instances of the processes of that type. In particular all messages terminating in and emanating from instances of a given process type go through the PiSet process of the given type. The principal use of this ERPAL control construct is to satisfy the synchronization semantics of SDL.

A plain SDL process type consisting of a single service in SDL 92 transforms into two ERPAL processes operating in parallel corresponding to two C++ classes. One of these is the actual body of the SDL process and the second one is a process called an *input port* process that manages the input queue of the process. If the process consists of several service blocks than each service block is modeled by a distinct ERPAL process communicating (synchronizing) with the common input queue manager process.

Every SDL channel is also modeled as an ERPAL process with a single variable of generic queue type. All the processes above are related to each other via repeated use of a universal parallel synchronization operator of ERPAL. Synchronization in the SDL context has a simplifying aspect: no process can be blocked on an outputting operation and for every act of outputting there corresponds a unique input operation of filling a channel slot or an input queue slot of a given process - or, of course, losing of a message occurs if no process can synchronize with the output operation. In other words mutual consent for synchronization is not required as in a general rendezvous type of synchronization and every output transition uniquely determines the outcome of the corresponding synchronization move.

Similarly each SDL procedure defined within a process is modeled by a separate ERPAL process that interacts with the calling process via a recursive use of ERPAL sequential (or stack) operator. This operator is similar to Hoare's sequential operator ";" or the sequential operator ">>" of LOTOS [4].

This completes the outline of the process based description of the SDL 92 animator. Before we present the C++ structures for the constructs above we briefly mention two different, yet important, hierarchical structures in SDL 92 to C++ conversion. The first hierarchy is the architectural hierarchy of the communication system specified. At the top of this hierarchy is the entire system represented by the SDL system block as in Figure 1. Nested blocks and channels and signal routes within blocks represent the functional hierarchy of the system specified. The lowest atomic elements of this hierarchy are the SDL processes or more precisely service blocks or active procedures incorporated in the processes. The manner in which this hierarchy is captured in the C++ image consists of nesting of classes within classes. Referring to the example given in Figure 1 the C++ classes corresponding to the process type Y and signal routes R1 to R3 are defined within the C++ class corresponding to the block type V. The explanation for the second hierarchy , namely that of the C++ classes is postponed to the next section.

### 4 Representation of SDL 92 constructions in C++

### 4.1 Functional and Class Hierarchies of the C++ Code

The C++ structure corresponding to an SDL 92 program consists of two parts :

- 1. an input-dependent part that constitutes the C++ images of SDL constructions,

- 2. an input-independent part that is necessary for the purposes of animation.

The input-dependent part produced by the compiler preserves the first kind of systemic hierarchy explained in the previous section. It does so by mapping the nested hierarchical SDL entities  $^7$  into a similarly nested set of C++ classes. Observe that the SDL hierarchy explained in the previous section can be visualized as a tree with nodes as SDL entities and branches as the nesting relations. The compiler can then be viewed as a transformer of this tree into its isomorphic image tree where the transformed nodes are the corresponding C++ classes. There are some exceptions to this rule. For example variables, which are entities that are nested inside a process which is another entity, are not mapped into C++ classes. Rather they are defined as variables within the nesting C++ class.

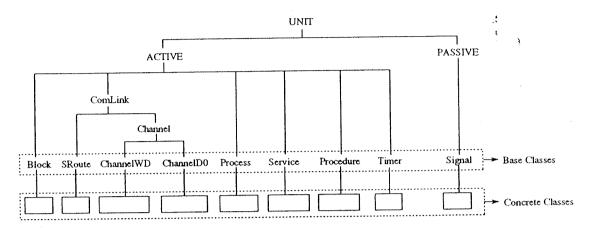

We shall call SDL entities that are mapped into C++ classes SDL units. Among these SDL units we further make active and passive unit distinction. An active SDL unit is one that correspond to an ERPAL process. Namely, an entity that has a property of evolving in time (i.e. it has a state). System, block, channel, signal route, process, service, procedure and timer constitute active SDL units. Passive SDL units, on the other hand, are signals and user defined data types.

Let an SDL unit be referred to as a self-instantiated unit if the instance of its creation always coincides with that of the unit that embraces it. In this sense system, block, channel, signal route and service are self-instantiated SDL units whereas, in general, process, procedure, timer and signal are not self-instantiated units. A self-instantiated SDL unit is statically instantiated if it is created in the beginning of the animation process. In this sense with the exception of service, all self-instantiated units are statically instantiated. In case of a self-instantiated unit Y, the C++ object representing its instance is created and bound to the corresponding pointer PY within the constructor of the embracing C++ class CX.

Figure 2 below explains the next hierarchical structure, namely the class (inheritance) hierarchy mentioned in the previous section. It depicts the class hierarchy structure of the C++ image of SDL programs. Here the classes named *base* classes correspond to <u>abstractions</u> of concrete C++ classes corresponding to concrete SDL units.

Figure 2 contains only the image classes of the SDL units. The set of all C++ classes generated by the compiler are greater than this image set. In particular there are two

<sup>&</sup>lt;sup>7</sup>In SDL the term entity is used for SDL constructs such as system, block, process, signal, variable etc.

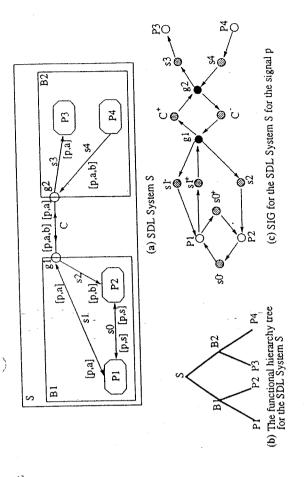

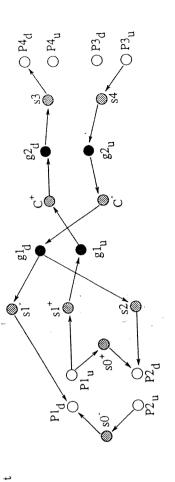

Figure 2: Class Hierarchy

important C++ classes on the level of the base classes that are generated for the purposes of animation dynamics. These correspond to the following process types mentioned in section 2: input port process for managing the input queue of a process and PiSet process for managing the instances of an SDL process type.

The top level class in Figure 2 has two methods as defined by the C++ code below :

```

typedef unsigned int card;

typedef card Idcode;

class Unit {

public:

virtual Idcode    idcode () = 0;

virtual char*         name () = 0;

}; // Unit

```

These methods represent identification and naming of units. The method name returns a string given in the SDL program as the name of a unit. The method idcode returns a cardinal number which uniquely identifies the unit considered. Both methods are concretized in the concrete classes derived from the base ones. The example below shows an outline of the C++ code corresponding to the SDL system given in Figure 1.

Example 1

```

{ return "A1"; };

name ()

char*

}; // A1

class A2 : public Signal {

public:

idcode () { return 2; };

Idcode

{ return "A2"; };

name ()

char*

}; // A2

class Y : public Block {

public:

idcode () { return 3; };

Idcode

{ return "Y"; };

char*

name ()

class A3 : public Signal {

public:

idcode () { return 4; };

Idcode

name ()

{ return "A3"; };

char*

. . .

}; // A3

class Z : public Process {

public:

idcode () { return 5; };

Idcode

{ return "Z"; };

char*

name ()

. . .

}; // Z

}; // Y

}; // X

```

### 4.2 Animation methods

Animation of an SDL program makes use of two animation methods: ask and go. The ask method simply implements searching for all the next events that may be executed in an SDL entity whereas the go method actually implements the execution of the event given as the argument of go. C++ objects that make use of these methods are the animated objects which correspond to SDL active units and process instances sets. So, the methods ask and go are virtual within the base classes ActiveUnit and PISet. In the tree of animated objects the leaves may be services, channels or active procedures.

The ask and go methods propagate right through the tree of animated objects. More precisely in the case of the ask method applied to node of the tree the method is recursively passed down to the children until the leaves and the result is accumulatively passed on to the original node. Once the user selects an event out of the possible next events offered by

the ask method it first locates the object where this event lies and executes the method go at that object. Depending on the possible mode of use, these methods can be invoked by the user explicitly or can be invoked automatically and subordinate to some execution directive - such as execute all invisible events until the next visible (communication) event.

### 4.3 Implementing Visibility and Scoping

Implementing the visibility and scoping rules of SDL are based on the functional hierarchy of the nested C++ classes mentioned earlier. In SDL system, block, process, service and procedure are referred to as scope units and the name of an entity defined in a such a scope unit can be visible not only in this unit but also inside the nested scope units. As explained above, in our C++ representation, SDL units are represented by classes whereas other SDL entities (variables, synonyms) are represented by C++ variables. They are declared (as data members) inside those C++ classes which represent the SDL scope units defining the corresponding SDL entities (variables, synonyms). Unfortunately whereas the hierarchy of the nested C++ classes preserves and therefore automatically implements the visibility and scoping semantics corresponding to SDL units the same is not true for C++ variables corresponding to SDL entities given by variables and synonyms. Since the visibility and scoping semantics for the variables defined within C++ classes do not match the similar semantics for the SDL entities that they represent, additional measures are required for a correct implementation.

Referring to Figure 1 above and using the SDL rules the signal names A1 and A2 are visible on the top level of system X and inside its inner block Y as Y does not redefine these signals. On the other hand the signal name A3 is visible inside block Y and, in particular, inside process Z, but not visible outside block Y since the definition of this signal is encapsulated by block Y. Correspondingly referring to the code given in Example 1 above, the signal classes A1 and A2 are visible on the top level of system class X and within block class Y. Signal class A3 is visible inside block class Y and, in particular, inside process class Z, but not outside Y.