# EFFICIENT INTEGRATED DC-DC CONVERTERS FOR ULTRA-LOW VOLTAGE ENERGY HARVESTERS

A THESIS SUBMITTED TO

### THE BOARD OF GRADUATE PROGRAMS

OF

## MIDDLE EAST TECHNICAL UNIVERSITY, NORTHERN CYPRUS CAMPUS

BY

### HERATH MPC JAYAWEERA

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE

### DEGREE OF MASTER OF SCIENCE

IN

THE

## SUSTAINABLE ENVIRONMENT AND ENERGY SYSTEMS

AUGUST 2017

Approval of the Board of Graduate Programs

Prof. Dr. Oya Yerin Güneri Chairperson

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Assist. Prof. Dr. Carter Mandrik Program Coordinator

This is to certify that we have read this thesis and that in our point it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Assoc. Prof. Dr. Ali Muhtaroğlu Supervisor

### **Examining Committee Members**

| Prof. Dr. Haluk Külah               | EEE Dept.                  |  |

|-------------------------------------|----------------------------|--|

|                                     | METU                       |  |

| Assoc. Prof. Dr. Tayfun Nesimoğlu   | EEE Program<br>METU NCC    |  |

| Assoc. Prof. Dr. Mustafa Murat Özer | Physics Group<br>METU NCC  |  |

| Assoc. Prof. Dr. Dizem Arifler      | Physics Group.<br>METU NCC |  |

# ETHICAL DECLARATION

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Herath Mudiyanselage Pradeep Chamara Jayaweera

Signature

:

#### ABSTRACT

# EFFICIENT INTEGRATED DC-DC CONVERTERS FOR ULTRA-LOW VOLTAGE ENERGY HARVESTERS

Herath Mudiyanselage Pradeep Chamara Jayaweera

M.S. Sustainable Environment and Energy Systems Program

Supervisor : Assoc. Prof. Dr. Ali Muhtaroglu

August 2017, 104 pages

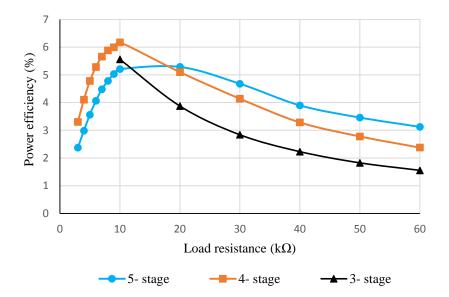

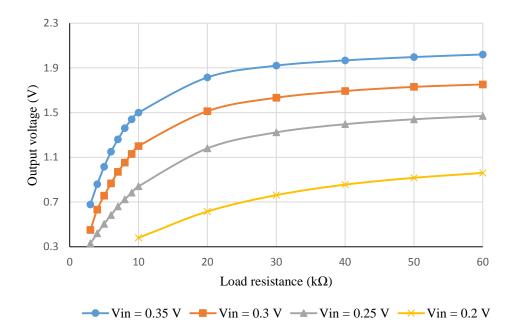

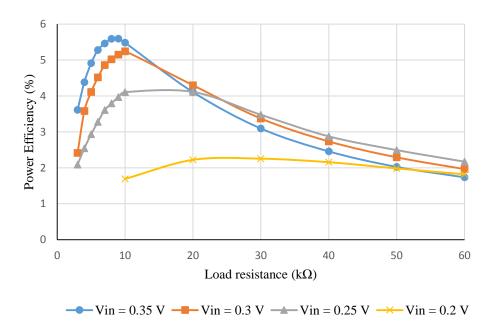

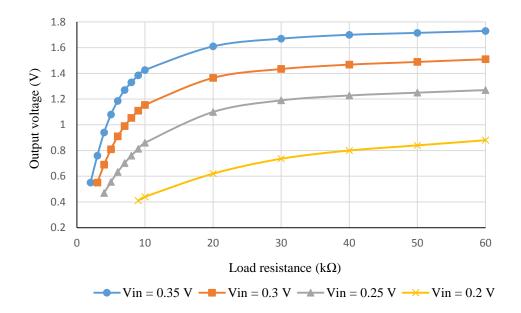

The self-starting on-chip fully integrated ultra-low voltage DC-DC converters for energy harvesting applications presented in literature generally have low efficiency and output power capacity. Any improvement in DC-DC converter circuits in terms of energy efficiency, output power, self-starting modes, and voltage gain will contribute significantly to the widespread application of energy harvesters. Two novel fully integrated, self-starting, ultra-low voltage DC-DC converter topologies and model based optimization methodologies for these converters are studied in this thesis for efficient micro-power energy harvesting applications. According to the pre-layout simulations in standard UMC 180nm CMOS technology, the proposed 3-, 4-, and 5-stage DC-DC converter with voltage doubling LC oscillator can achieve 47.9%, 51.5%, 51.7% efficiency, and deliver 343  $\mu$ W at 1.02 V output, 385  $\mu$ W at 1.39 V output, and 454 µW at 1.65 V output respectively for 0.2 V input. The voltage quadrupling LC tank coupled DC-DC converter with 4 and 3 stages can achieve 33% and 31% efficiency while delivering 1193 µW at 2.18 V output, and 778 µW at 1.77 V output respectively for 0.2 V input. The measurements from the fabricated test chip for the first topology indicate major deviations from the simulations, i.e. the measured simulation peak efficiency is < 7% at 0.2 V input. Comprehensive design validation and analysis is presented for the discrepancy, which results in post-layout simulations of a new model that can be correlated to silicon observations. The fixes to the design and layout have been taped out as part of a second revision of the test chip to overcome the problems. The post-layout simulations for the new design achieve a peak efficiency of 41.5% at 1.54 V output, and 41% at 1.27 V output with 5 and 4 stages respectively for 0.2 V input. The theoretical analysis and optimization methods presented in this thesis are verified through simulations in Cadence environment.

Keywords: DC-DC converter, energy efficiency, charge pump circuit, LC tank oscillator.

# ULTRA-DÜŞÜK VOLTAJLI ENERJİ TOPLAYICILARI İÇİN ETKİN ENTEGRE EDİLMİŞ DC-DC DÖNÜŞTÜRÜCÜLER

Herath Mudiyanselage Pradeep Chamara Jayaweera

Yüksek Lisans, Sürdürülebilir Çevre ve Enerji Sistemleri Programı

Tez Yöneticisi: Doç. Dr. Ali Muhtaroglu

Temmuz 2017, 104 sayfa

Literatürde sunulan enerji toplama uygulamaları için kendi kendine çalışan tam entegre ultra düsük voltajlı DC-DC dönüstürücüler, genellikle düsük verimlilik ve çıkıs gücü kapasitesine sahiptirler. DC-DC dönüştürücü devrelerinde enerji verimliliği, çıkış gücü, kendiliğinden çalışma modları ve voltaj kazanımı açısından sağlanabilecek herhangi bir gelişme, enerji toplayıcı uygulanmalarının yaygınlaşmasına önemli ölcüde katkıda bulunacaktır. Bu tezde, verimli mikro güç enerji toplama uygulamaları için, iki özgün tam entegre, kendi kendine çalışan, ultra-düşük voltajlı DC-DC dönüştürücü topolojileri ve modüle dayalı optimizasyon metodolojileri incelenmiştir. Standart UMC 180 nm CMOS teknolojisindeki düzen öncesi simülasyonlara göre, önerilen 3-, 4- ve 5-aşamalı LC osilatörlü voltaj katlama DC-DC dönüştürücüsü için sırasıyla, % 47.9, % 51.5, % 51.7 verimlilik sağlanabilir ve 0.2 V giriş için sırasıyla 1.02 V çıkışta 343 µW, 1.39 V çıkışta 385 µW ve 1.65 V çıkışta 454 µW sağlayabilir. 4 ve 3 kademeli DC-DC dönüstürücüye bağlanan voltaj dört katına çıkartan LC tankı, sırasıyla % 23 ve % 31 verimlilik elde edilirken, 0.2 V giris icin sırasıyla 2.18 V cıkısta 1193 uW ve 1.77 V çıkışta 778 µW alınmıştır. İlk topoloji için imal edilen test yongasından alınan ölçümler, simülasyonlardan büyük sapmalara işaret etmektedir, diğer bir değişle, ölçülen simülasyon pik verimi, 0.2 V girişinde < %7'dir. Kapsamlı tasarım geçerliliği ve analizi, tutarsızlık icin sunulmustur; bu, silikon gözlemleriyle iliskilendirilebilen veni bir model sonrası düzen simülasyonuna neden olmuştur. Tasarım ve yerleşimdeki düzeltmeler, sorunların üstesinden gelmek için test yongasının ikinci revizyonunun bir parçası olarak kaydedilmiştir. Yeni tasarım için düzen sonrası simülasyonlar, 5 ve 4 aşamalarda 0.2 V giriş için sırasıyla, 1.54 V çıkış için % 41.5 ve 1.27 V çıkış için % 41 pik verimleri elde edilmiştir. Bu tezde sunulan teorik analiz ve optimizasyon yöntemleri, Cadence ortamında simülasyonlarla doğrulanmıştır.

Anahtar kelimeler: DC-DC dönüştürücü, enerji verimliliği, Şarj pompa devresi, LC tank osilatörü.

# **DEDICATION**

To my loving wife, Parents, Brother, Sister, and My supervisor

For their unconditional assistance and inspiration.

### ACKNOWLEDGEMENTS

I would like to offer my first and foremost appreciation to my supervisor, Dr. Ali Muhtaroğlu for his encouragement, expert advice and guidance throughout each step of my research and M. Sc. studies. His constant trust and assistance inspired me in the most important moments making the right decision, and I'm glad that I have worked with him.

I am also grateful to the other members of my thesis committee, Assoc. Prof. Dr. Tayfun Nesimoglu, Prof. Dr. Haluk Külah, Assoc. Prof. Dr. Mustafa Murat Özer, and Assoc. Prof. Dr. Dizem Arifler for their suggestions, comments, guidance, and encouragement throughout the research and review process.

I want to thank all my SEES program teachers for provided a solid background to enhance my scientific analysis, model-based analysis for optimization, and research ethics.

My special thanks go to Manula Pathirana from the University of Virginia – USA, for introducing me to Dr. Ali Muhtaroglu, and his valuable help during many stages of my research. I want to thank Hassan Uluşan from METU Ankara for his help in micro IC layout and test IC soldering. I am also grateful to Dr. Gamze Öncül from METU-NCC for her guidance in English writing. I appreciate the help of VLSI research group members Muhammad Saleh and Hamed Osouli, for their help and encouragement.

The Europractice and IMEC supports are gratefully acknowledged.

Special thanks to all teaching assistants and teachers in physics department METU NCC for providing a pleasant environment to pursue my research studies during TA duties.

I appreciate the unconditional help of my loving wife, parents, brother, and sister, who encouraged me in the successful completion of my research and thesis.

# **TABLE OF CONTENTS**

| ETHIC  | AL DECLARATION iii                                            |

|--------|---------------------------------------------------------------|

| ABSTI  | RACTiv                                                        |

| ÖZ     | V                                                             |

| DEDIC  | CATIONvi                                                      |

| ACKN   | OWLEDGEMENTSvii                                               |

| TABL   | E OF CONTENTS viii                                            |

| LIST C | DF TABLESxi                                                   |

| LIST C | DF FIGURESxii                                                 |

| NOME   | NCLATURE                                                      |

| 1 IN   | TRODUCTION1                                                   |

| 1.1    | Background1                                                   |

| 1.2    | Common energy harvesting techniques                           |

| 1.3    | Problem associated with the energy harvesting techniques      |

| 1.4    | DC-DC converters                                              |

| 1.5    | DC-DC converter efficiency                                    |

| 1.6    | Objectives of the thesis                                      |

| 1.7    | Thesis outline                                                |

| CHAP   | ΓER 214                                                       |

| 2 BA   | CKGROUND14                                                    |

| 2.1    | Introduction                                                  |

| 2.2    | DC-DC converter fundamentals                                  |

| 2.3    | Switch mode charge pump topologies for DC-DC converter design |

| 2.4    | CMOS charge pump circuits for DC-DC converter applications    |

| 2.5  | Oscillator circuit for the DC-DC converter design          |    |

|------|------------------------------------------------------------|----|

| 2.5  | 1 Ring oscillator circuit                                  | 27 |

| 2.6  | LC tank oscillators                                        | 30 |

| 2.7  | DC-DC converter modeling and optimization                  | 34 |

| CHAP | TER 3                                                      |    |

| 3 PR | OPOSED OSCILLATOR ARCHITECTURE                             |    |

| 3.1  | Introduction                                               | 37 |

| 3.1  | 1 Negative resistance generator                            |    |

| 3.1  | 2 LC tank real losses                                      |    |

| 3.1  | 3 Oscillator phase noise                                   | 40 |

| 3.2  | Voltage doubling LC tank oscillator                        | 41 |

| 3.2  | 1 Basic operation of oscillator                            |    |

| 3.2  | 2 Model based circuit analysis                             | 43 |

| 3.2  | 3 Characteristics of UMC 180 CMOS process                  | 44 |

| 3.3  | Voltage quadrupling LC tank oscillator                     | 47 |

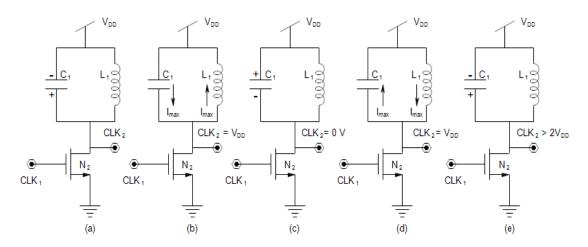

| 3.3  | 1 Basic operation                                          | 47 |

| 3.3  | 2 Modal based circuit analysis                             | 49 |

| 3.3  | 3 Characteristics of UMC 180 CMOS process                  | 52 |

| CHAP | TER 4                                                      |    |

| 4 PR | OPOSED DC-DC CONVERTER ARCHITECTURE                        |    |

| 4.1  | Introduction                                               | 55 |

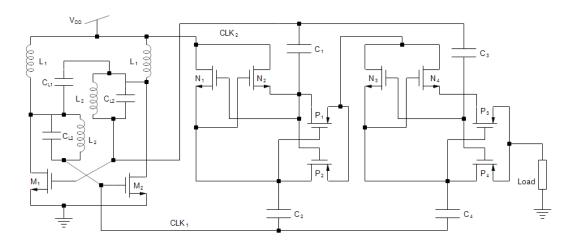

| 4.2  | Charge pump circuit                                        | 56 |

| 4.3  | DC-DC converter architecture with voltage doubling LC tank | 57 |

| 4.3  | 1 Charge pump coupled LC tank oscillator frequency         | 58 |

| 4.3  | 2 DC-DC converter model                                    | 61 |

| 4.3  | 3 DC-DC converter optimization                             | 63 |

| 4.3.3.   | 1 Simplified half circuit model for impedance matching            | 63  |

|----------|-------------------------------------------------------------------|-----|

| 4.3.3.   | 2 Simplified half circuit model for power calculations            |     |

| 4.3.3.   | 3 Optimization methodology                                        | 66  |

| 4.3.4    | Model verification by simulations                                 | 67  |

| 4.4 Vo   | ltage quadrupling LC tank coupled DC-DC converter architecture    | 72  |

| 4.4.1    | Simplified half-circuit model for impedance matching              | 73  |

| 4.4.2    | Optimization methodology                                          | 74  |

| 4.4.3    | Simulation results                                                | 75  |

| CHAPTER  | R 5                                                               | 78  |

| 5 DESIG  | GN VALIDATION                                                     | 78  |

| 5.1 Intr | roduction                                                         |     |

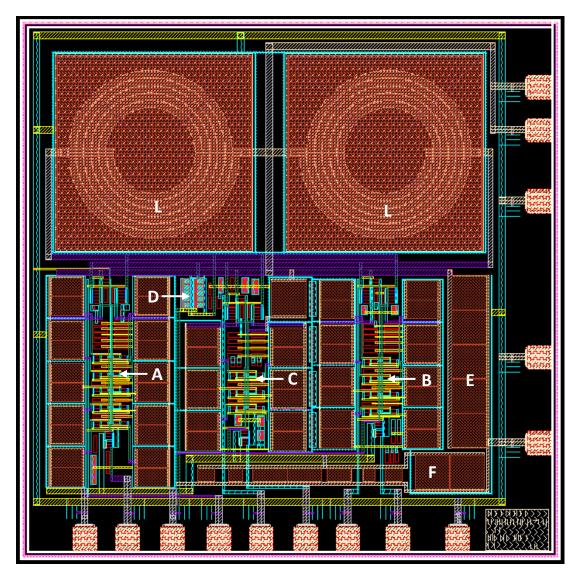

| 5.2 Tes  | st chip design and layout                                         |     |

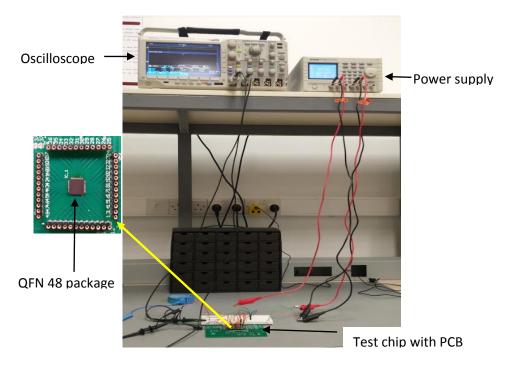

| 5.3 Exp  | perimental setup for system validation                            | 79  |

| 5.4 Ch   | aracterization                                                    |     |

| 5.4.1    | Post-layout simulations with parasitic capacitance extraction     |     |

| 5.4.2    | Post-layout simulations with parasitic LRC extraction             |     |

| 5.4.3    | Experimental results                                              |     |

| 5.5 Co   | rrelation across the model, simulations, and experimental results |     |

| 5.5.1    | Model correction for post-layout simulations                      |     |

| 5.5.2    | Verification by Simulation                                        |     |

| 5.6 Enl  | nanced multi-stage DC-DC converter                                | 96  |

| 5.7 Per  | formance comparison with literature                               |     |

| CHAPTE   | R 6                                                               | 102 |

| 6 THES   | IS CONCLUSION                                                     | 102 |

| 6.1 Fut  | ure work                                                          |     |

| REFEREN  | NCE                                                               |     |

# LIST OF TABLES

| Table 1.1. Power density comparison of energy sources used for energy harvesting.                       |

|---------------------------------------------------------------------------------------------------------|

| Table 3.1. Voltage doubling LC tank parameters.    45                                                   |

| Table 3.2. Voltage quadrupling LC tank parameters.    53                                                |

| Table 4.1. The design parameters of voltage doubling LC tank connected DC-DC      converter.      67    |

| Table 4.2. The design parameters of voltage quadrupling LC tank connected DC-DC      converter.      75 |

| Table 5.1. The design parameters of the full system.    81                                              |

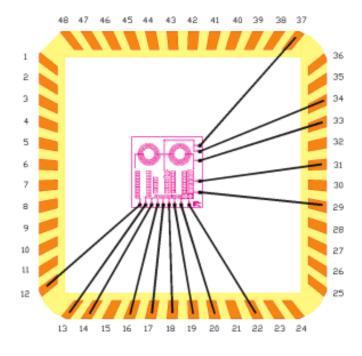

| Table 5.2. Pin description of the fabricated IC.    82                                                  |

| Table 5.3. Comparison with ultra-low voltage DC-DC converters in literature101                          |

| Table 6.1. Summary of the implemented circuits.       102                                               |

# LIST OF FIGURES

| Figure 1.1. (a) Solar cell for photovoltaic, and (b) thermocouple for thermoelectric, energy harvesting |

|---------------------------------------------------------------------------------------------------------|

| Figure 1.2. (a) Piezoelectric energy harvester, (b) electrostatic energy harvester, to convert          |

| kinetic energy into electrical energy                                                                   |

| Figure 1.3. (a). Electromagnetic vibration energy harvester, (b) RF energy harvester                    |

| Figure 1.4. Block diagram of the energy harvester interface                                             |

| Figure 1.5. Block diagram of linear DC converter10                                                      |

| Figure 1.6. Block diagram of the switch mode DC-DC converter11                                          |

| Figure 2.1. The block diagram of a switch mode DC-DC converter for energy harvesting applications       |

| Figure 2.2. Energy accumulation of the energy storage device in the DC-DC converter 17                  |

| Figure 2.3. The energy transferring from energy storage device to load capacitor of the DC-             |

| DC converter                                                                                            |

| Figure 2.4. Cockcroft-Walton charge pump                                                                |

| Figure 2.5. Two-stage of two phase cascade voltage doubler charge pump circuit [42]19                   |

| Figure 2.6. Makowski charge pump topology20                                                             |

| Figure 2.7. The voltage step-up ladder charge pump architecture [45]20                                  |

| Figure 2.8. Two-stage of dual phase cascade DC output voltage doubler charge pump circuit               |

|                                                                                                         |

| Figure 2.9. Dickson charge pump circuit with diode switches                                             |

| Figure 2.10. Dickson charge pump with NMOS switches                                                     |

| Figure 2.11. A two stage NCP-2 charge pump                                                              |

| Figure 2.12. Dual charge transfer branch MOSFET cross connected charge pump                             |

| Figure 2.13. Basic block diagram of an oscillator [62]                                                  |

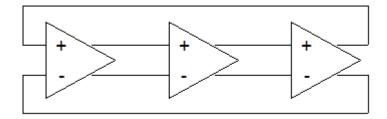

| Figure 2.14. A five stage CMOS ring oscillator                                                          |

| Figure 2.15. Differential delay cell ring oscillator                                                  |

|-------------------------------------------------------------------------------------------------------|

| Figure 2.16. A conventional SCL differential cell29                                                   |

| Figure 2.17. An oscillator as a two port network                                                      |

| Figure 2.18. PMOS LC tank based VCO [66]32                                                            |

| Figure 2.19. Differential complementary oscillator with cross coupled NMOS and PMOS pair.             |

| Figure 2.20. Transformer feedback VCO                                                                 |

| Figure 2.21. Half-circuit model for the transformer feedback VCO35                                    |

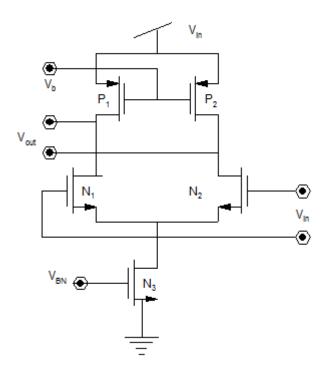

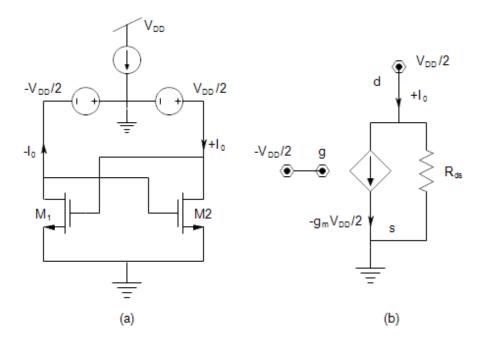

| Figure 3.1. (a). Differential cross coupled NMOS pair, (b). M2 NMOS at differential state. 38         |

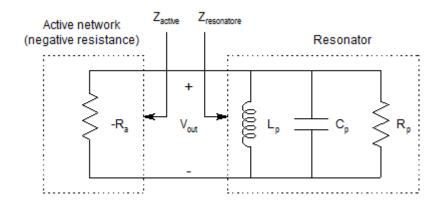

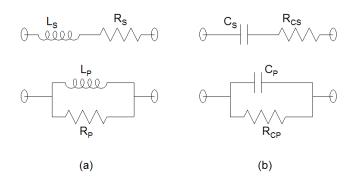

| Figure 3.2. The series-parallel combination of (a) LR circuit, (b) CR circuit                         |

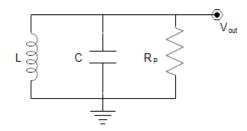

| Figure 3.3. LC tank oscillator with ideal components40                                                |

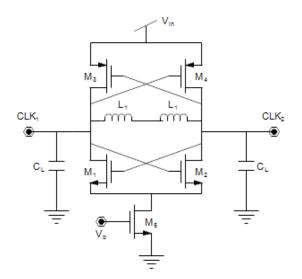

| Figure 3.4. Voltage doubling LC tank oscillator                                                       |

| Figure 3.5. Half circuit analysis for the voltage doubling oscillator42                               |

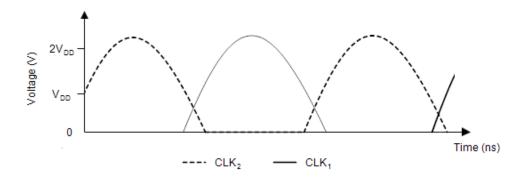

| Figure 3.6. Voltage doubling LC tank output wave form43                                               |

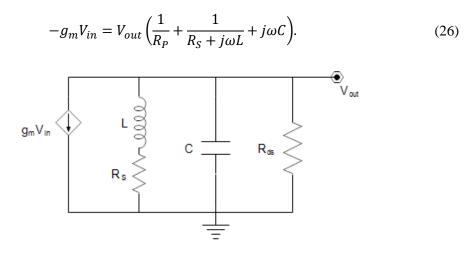

| Figure 3.7. Small signal half-circuit model of the LC tank oscillator43                               |

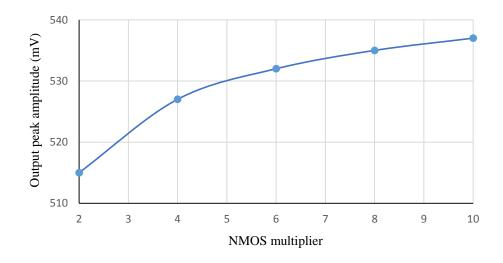

| Figure 3.8. The variation of oscillator peak amplitude with NMOS multiplier45                         |

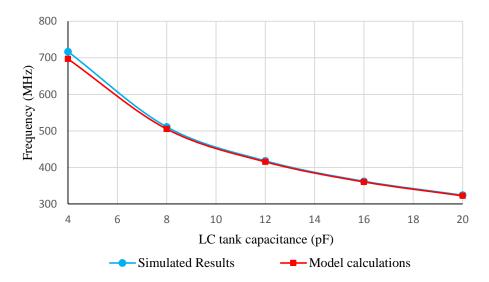

| Figure 3.9. The variation of the oscillation frequency with LC tank capacitance46                     |

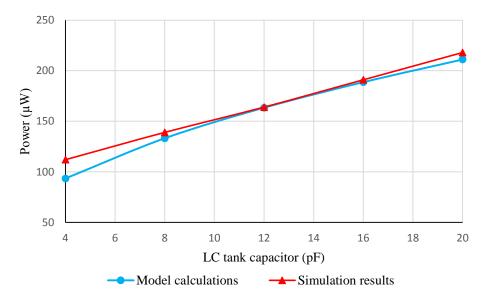

| Figure 3.10. The variation of LC tank power consumption with tank capacitance46                       |

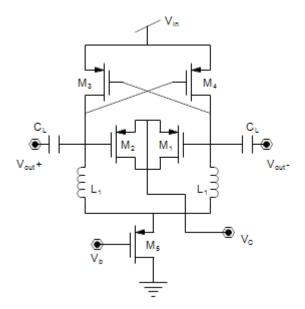

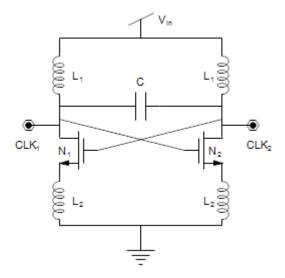

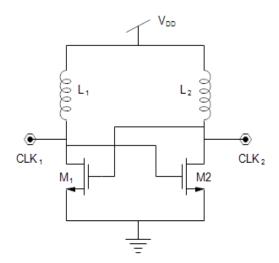

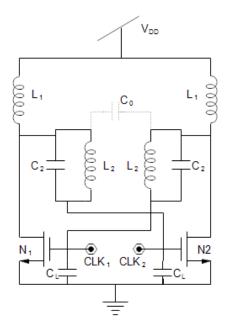

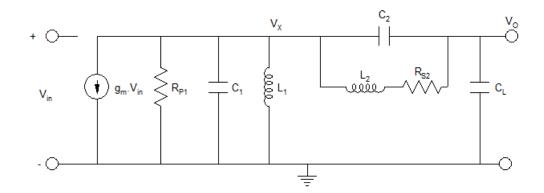

| Figure 3.11. Voltage quadruple LC tank based oscillator47                                             |

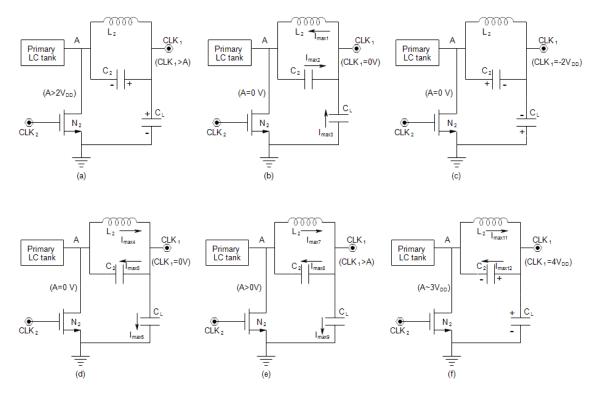

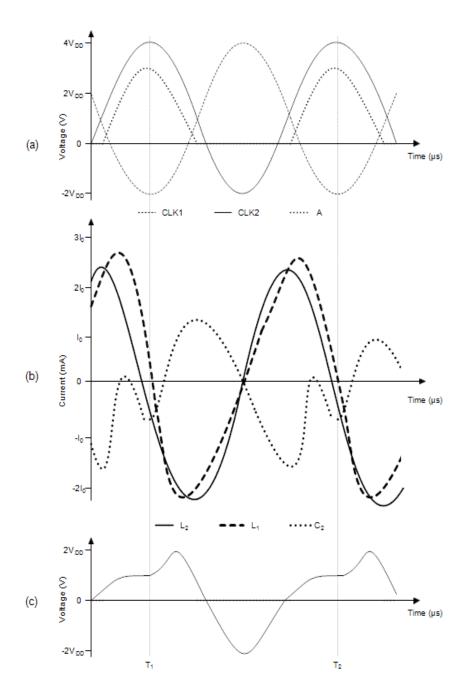

| Figure 3.12. Half circuit analysis for the secondary oscillator                                       |

| Figure 3.13. The characteristic curves for the voltage quadrupling LC tank                            |

| Figure 3.14. Simplified small-signal half-circuit model of the voltage quadrupling LC tank oscillator |

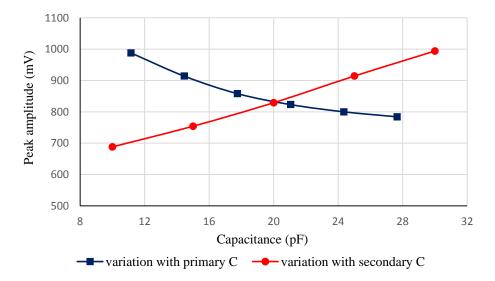

| Figure 3.15. The variation of peak amplitude with LC tank capacitors                                  |

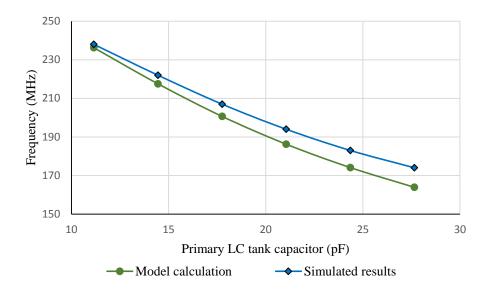

| Figure 3.16. The variation of oscillation frequency with primary LC tank capacitance54                |

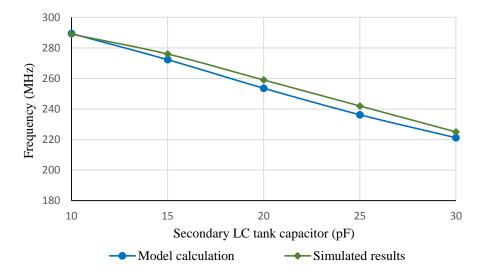

| Figure 3.17. The variation of oscillation frequency with secondary LC tank capacitor54                |

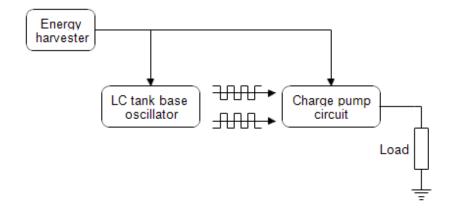

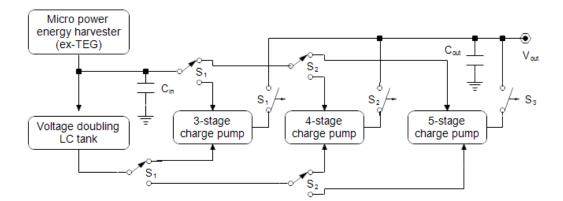

| Figure 4.1. Block diagram of proposed DC-DC converter                                                              |

|--------------------------------------------------------------------------------------------------------------------|

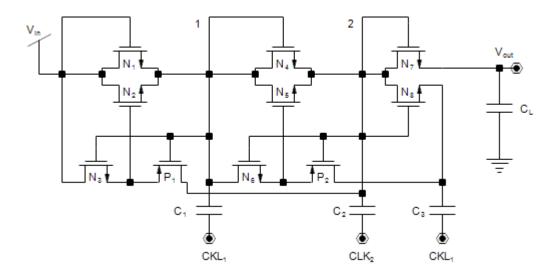

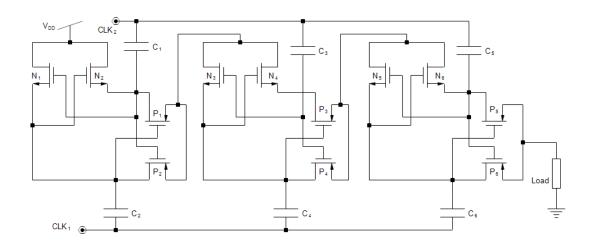

| Figure 4.2. Cross-coupled MOSFET charge pump                                                                       |

| Figure 4.3. Two stage DC-DC converter with voltage doubling LC tank oscillator                                     |

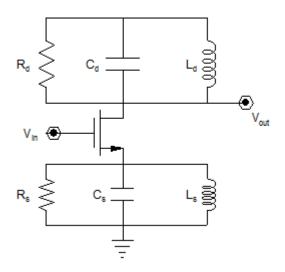

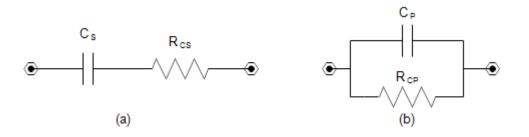

| Figure 4.4. Series and parallel RC circuit                                                                         |

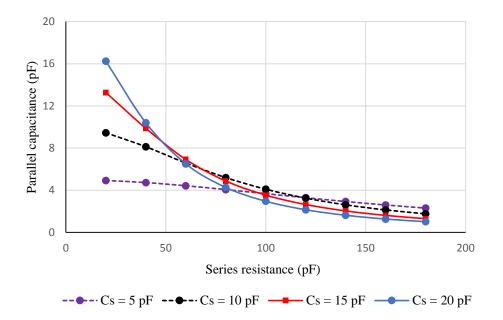

| Figure 4.5. The variation of parallel capacitance with series resistance for different series capacitance          |

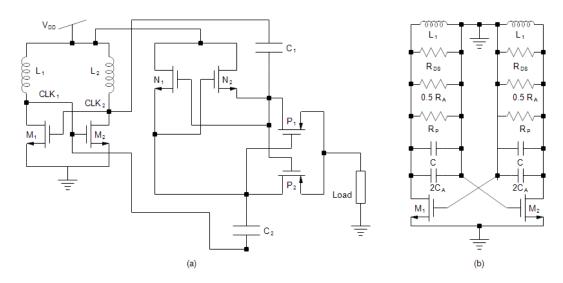

| Figure 4.6. (a) Single stage DC-DC converter, (b) enhanced LC tank model for the single stage DC-DC converter      |

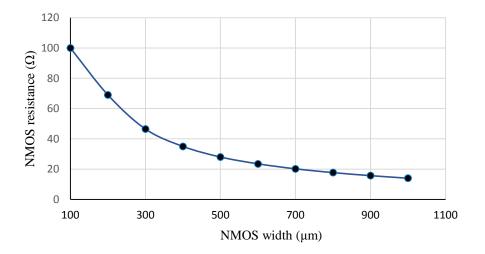

| Figure 4.7. Variation of NMOS resistance with NMOS width ( $L = 240 \text{ nm}$ )60                                |

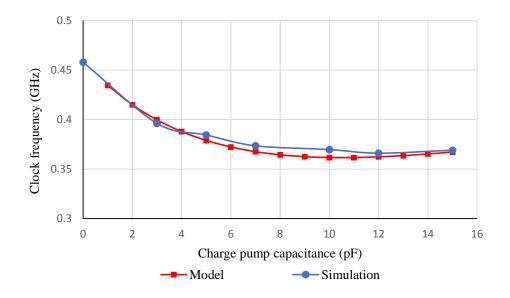

| Figure 4.8. The variation of clock frequency with charge pump capacitance61                                        |

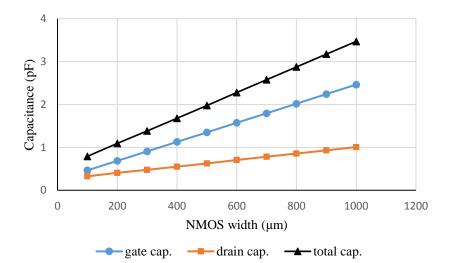

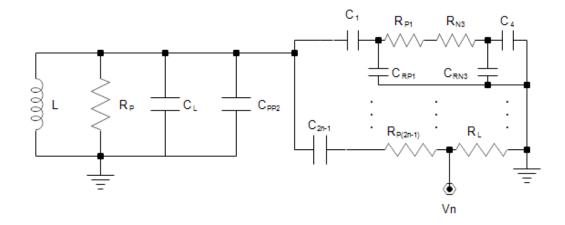

| Figure 4.9. The lumped element half circuit model of the n-stage DC-DC converter                                   |

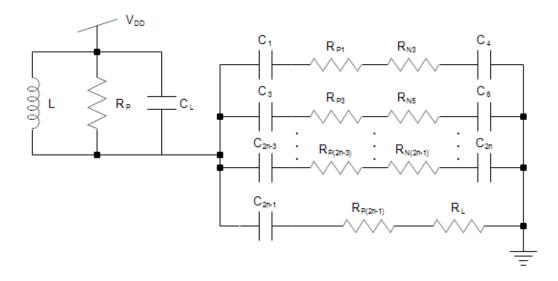

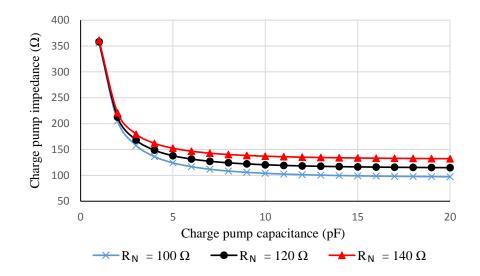

| Figure 4.10. The variation of charge pump impedance with charge pump capacitors63                                  |

| Figure 4.11. The variation of NMOS capacitance with NMOS width                                                     |

| Figure 4.12. Half circuit model of a DC-DC converter for power analysis                                            |

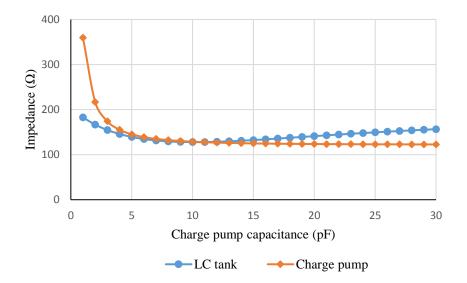

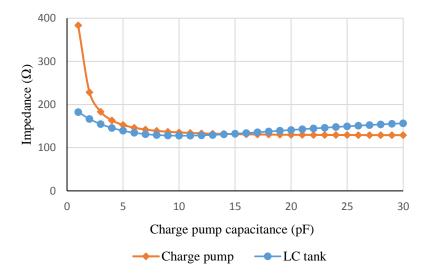

| Figure 4.13. The variation of impedance with charge pump capacitance at 2 k $\Omega$ load68                        |

| Figure 4.14. The variation of impedance with charge pump capacitance at 10 k $\Omega$ load68                       |

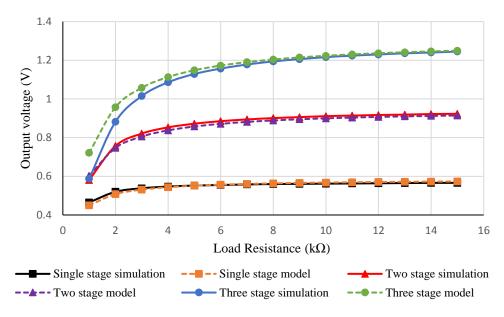

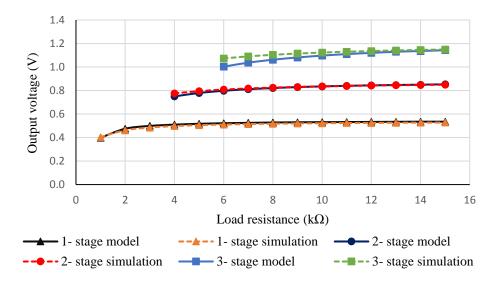

| Figure 4.15. The variation of output voltage with load resistance for 1-3 stages                                   |

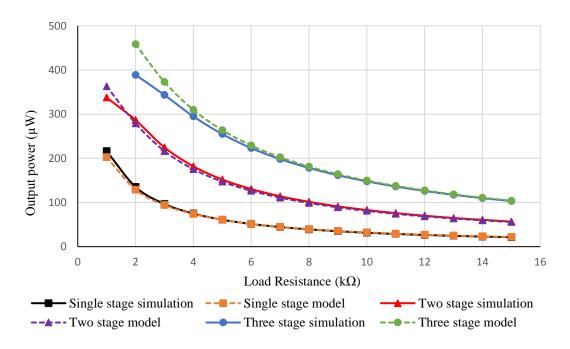

| Figure 4.16. The variation of output power with load resistance for 1-3 stages                                     |

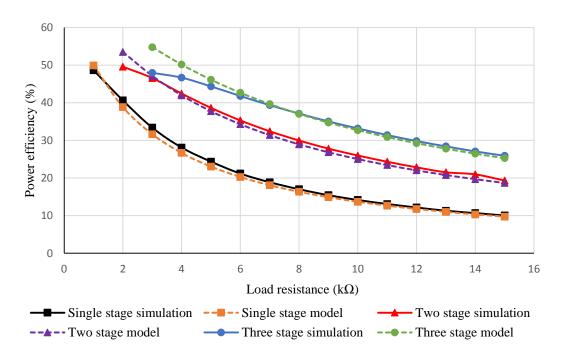

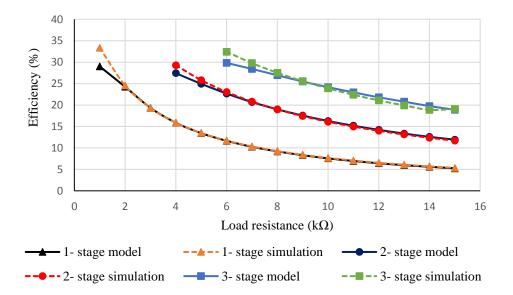

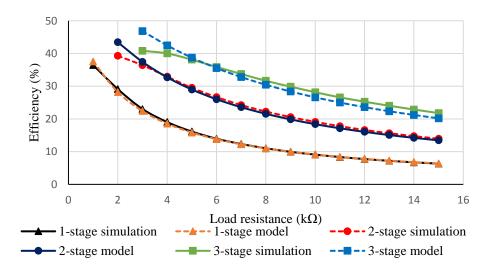

| Figure 4.17. The variation of power efficiency with load resistance for 1-3 stages70                               |

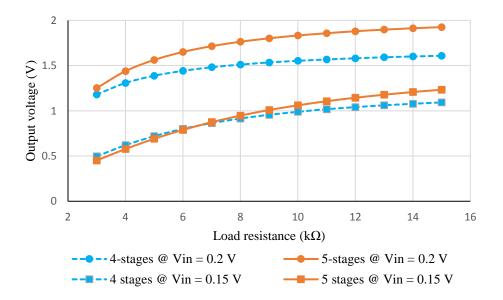

| Figure 4.18. Variation of output voltage with load resistance for 4 & 5 stages @ 0.2 V, 0.15 V inputs              |

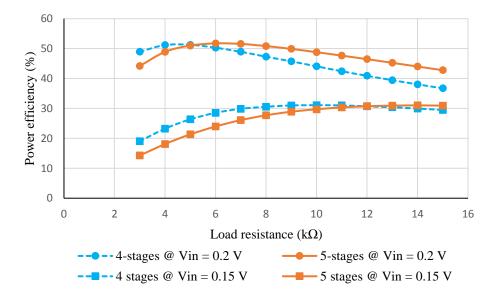

| Figure 4.19. Variation of power efficiency with load resistance for 4 & 5 stages @ 0.2 V, 0.15 V inputs            |

| Figure 4.20. Two stages of the DC-DC converter with voltage quadrupling LC tank72                                  |

| Figure 4.21. The lumped element half circuit model of the n-stage DC-DC converter with voltage quadrupling LC tank |

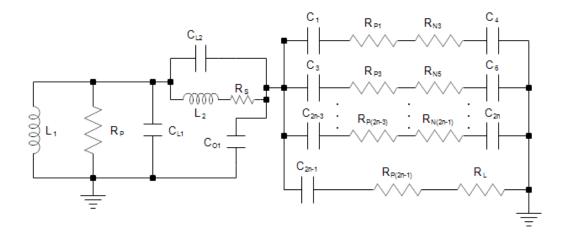

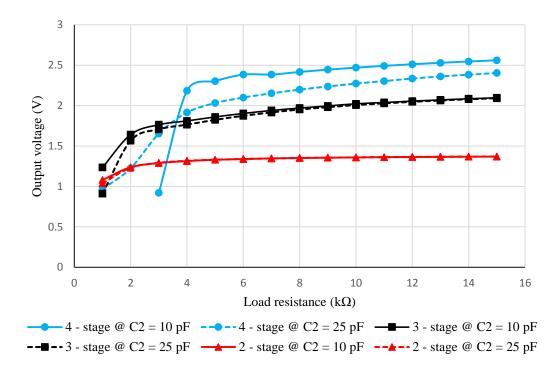

| Figure 4.22. The variation of output voltage with load resistance and secondary resonator capacitor value for 2-4 stages |

|--------------------------------------------------------------------------------------------------------------------------|

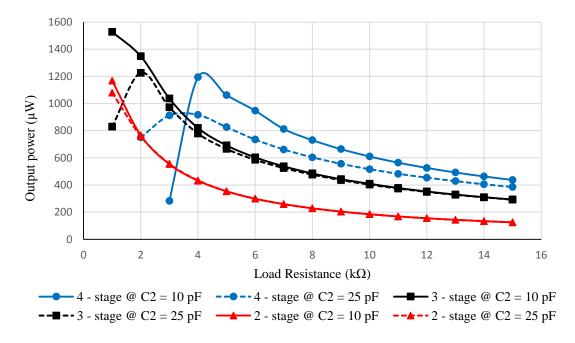

| Figure 4.23. The variation of output power with load resistance for 2-4 stages                                           |

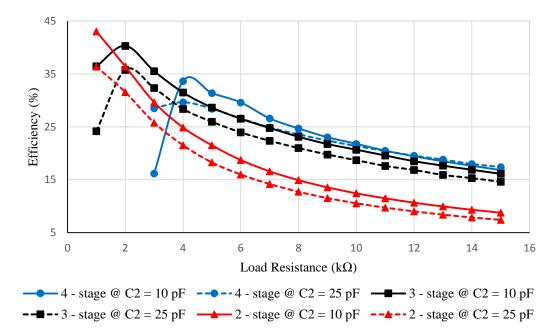

| Figure 4.24. The variation of efficiency with load resistance for 2-4 stages                                             |

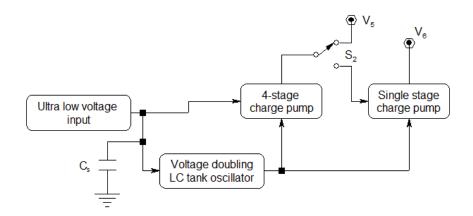

| Figure 5.1. Block diagram of full chip design                                                                            |

| Figure 5.2. Test circuit layout with PAD connections                                                                     |

| Figure 5.3. LC tank NMOS cross-coupled pair80                                                                            |

| Figure 5.4. The bonding diagram of the fabricated IC82                                                                   |

| Figure 5.5. Experimental setup for the system validation                                                                 |

| Figure 5.6. The screen shot of oscilloscope output for the 5-stage DC-DC converter                                       |

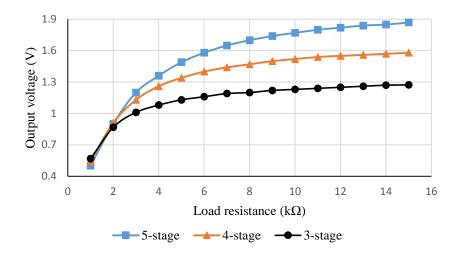

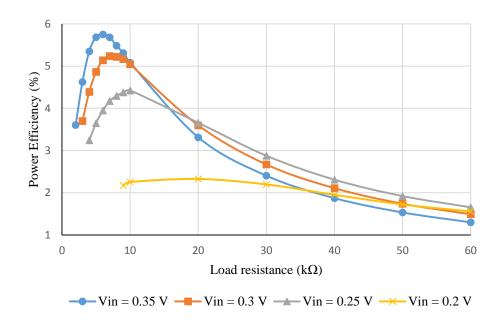

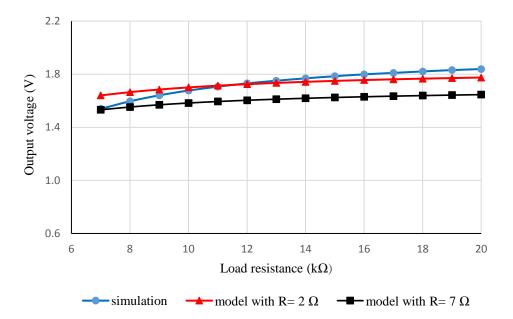

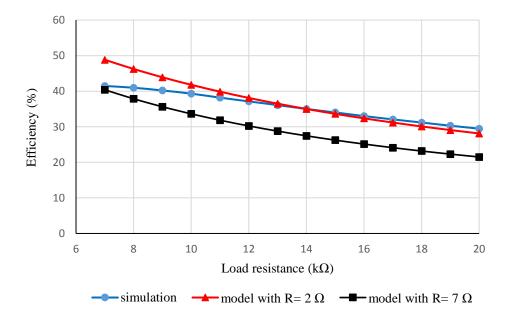

| Figure 5.7. The variation of system output with load resistance (only C extraction)                                      |

| Figure 5.8. The variation of system efficiency with load resistance (only C extraction)84                                |

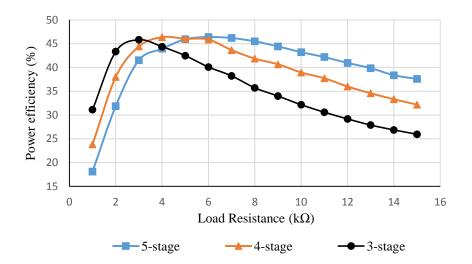

| Figure 5.9. The variation of system output with load resistance (LRC extraction)85                                       |

| Figure 5.10. The variation of system efficiency with load resistance (LRC extraction)85                                  |

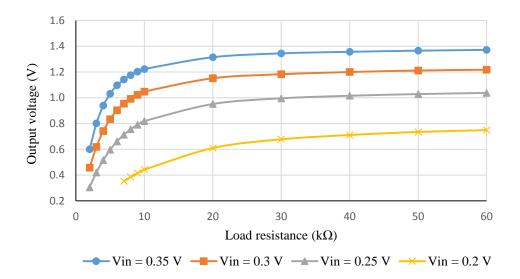

| Figure 5.11. The variation of 5-stage DC-DC converter output voltage with load                                           |

| resistance                                                                                                               |

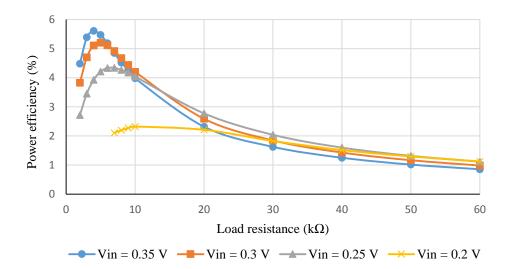

| Figure 5.12. The variation of 5-stage DC-DC converter efficiency with load resistance86                                  |

| Figure 5.13. Variation of 4-stage DC-DC converter output voltage with load resistance87                                  |

| Figure 5.14. Variation of 4-stage DC-DC converter efficiency with load resistance                                        |

| Figure 5.15. Variation of 3-stage DC-DC converter output voltage with load resistance88                                  |

| Figure 5.16. Variation of 3-stage DC-DC converter efficiency with load resistance                                        |

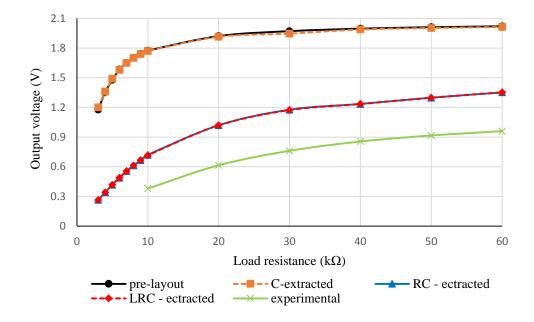

| Figure 5.17. Variation of 5-stage DC-DC converter output voltage with load resistance for pre-                           |

| layout simulation, post-layout simulation (C-extracted, RC-extracted, and LRC-extracted),                                |

| and experimental measurement at 0.2 V input                                                                              |

| Figure 5.18. Variation of 5-stage DC-DC converter efficiency with load resistance for pre-                               |

| layout simulation, post-layout simulation (C-extracted, RC-extracted, and LRC-extracted),                                |

| and experimental measurement at 0.2 V input                                                                              |

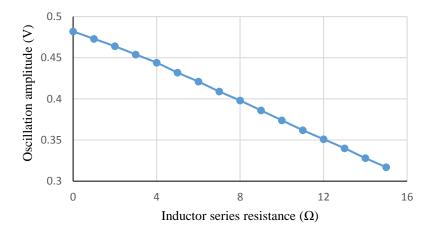

| Figure 5.19. The variation of DC-DC converter oscillation amplitude with inductor series resistance                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

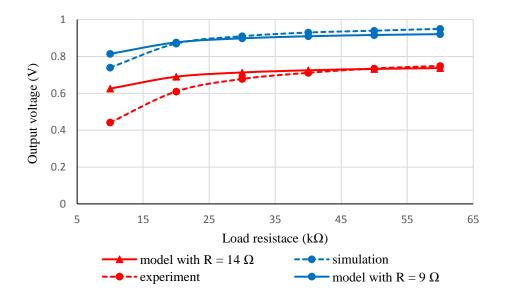

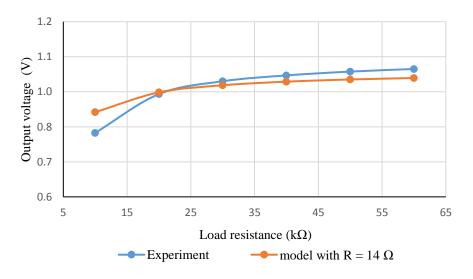

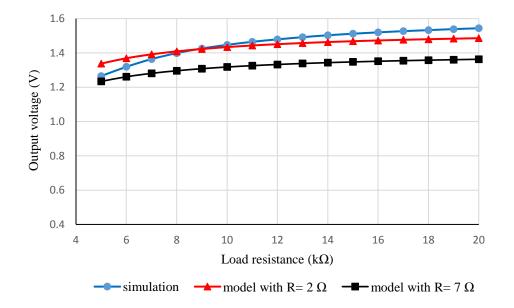

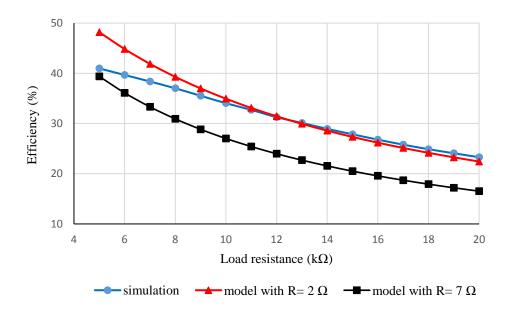

| Figure 5.20. The variation of 3-stage DC-DC converter output voltage with load resistance (simulation, experiment, and model results)                |

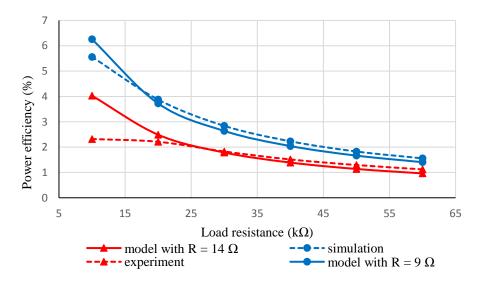

| Figure 5.21. Variation of 3-stage DC-DC converter efficiency with load resistance (simulation, experiment, and model results)                        |

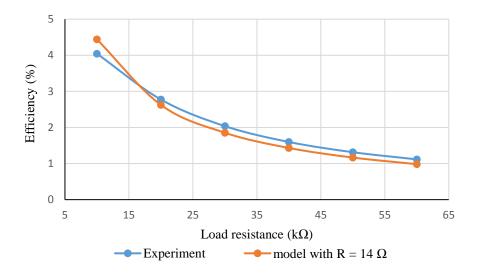

| Figure 5.22. The variation of 3-stage DC-DC converter output voltage with load resistance at 0.25 V input (post-layout simulation and model results) |

| Figure 5.23. The variation of 3-stage DC-DC converter efficiency with load resistance at 0.25 V input (post-layout simulation and model results)     |

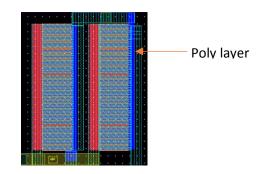

| Figure 5.24. The variation of DC-DC converter output voltage with load resistance at 0.2 V input (small Poly layout)                                 |

| Figure 5.25. The variation of DC-DC converter power efficiency with load resistance at 0.2 V input (small Poly layout)                               |

| Figure 5.26. The variation of DC-DC converter output voltage with load resistance for 0.2 V input (large Poly layout)                                |

| Figure 5.27. The variation of DC-DC converter power efficiency with load resistance for 0.2 V input (large Polly layout)95                           |

| Figure 5.28. Block diagram of multi stage DC-DC converter96                                                                                          |

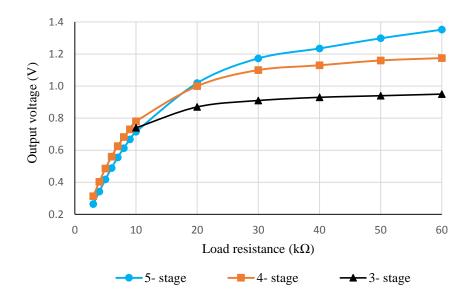

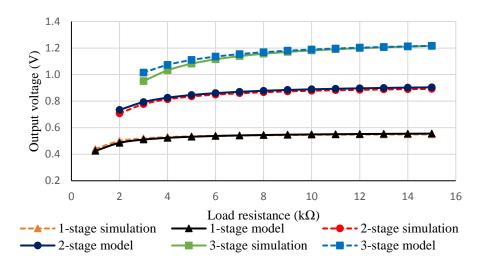

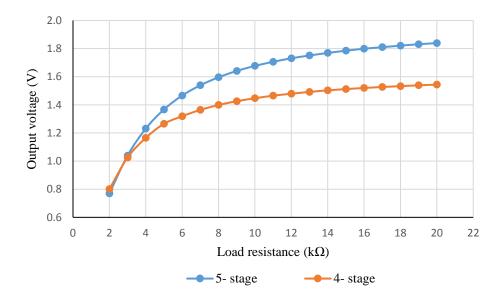

| Figure 5.29. The variation of output voltage with load resistance of enhanced design97                                                               |

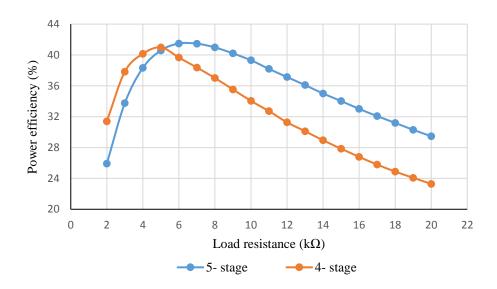

| Figure 5.30. The variation of power efficiency with load resistance for enhanced design97                                                            |

| Figure 5.31. The 5-stage DC-DC converter output voltage variation with load resistance at 0.2 V input (simulation and model results)                 |

| Figure 5.32. The 5-stage DC-DC converter efficiency variation with load resistance at 0.2 V input (simulation and model results)                     |

| Figure 5.33. The 4-stage DC-DC converter output voltage variation with load resistance at 0.2 V input (simulation and model results)                 |

| Figure 5.34. The 4-stage DC-DC converter efficiency variation with load resistance at 0.2 V input (simulation and model results)                     |

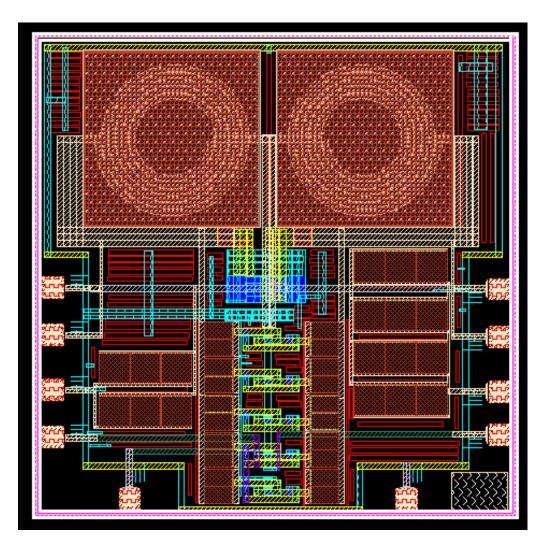

Figure 5.35. Die layout photo of enhanced circuit with PAD connections......100

# NOMENCLATURE

| С                          | Capacitance (pF)                                  |  |  |

|----------------------------|---------------------------------------------------|--|--|

| Р                          | Power                                             |  |  |

| Ι                          | Current                                           |  |  |

| f                          | frequency                                         |  |  |

| η                          | Efficiency (%)                                    |  |  |

| MOSFET                     | Metal Oxide Semiconductor Field Effect Transistor |  |  |

| NMOS                       | N-type Metal Oxide Semiconductor                  |  |  |

| PMOS                       | P-type Metal Oxide Semiconductor                  |  |  |

| Low_Vt                     | Low threshold voltage                             |  |  |

| $\mathbf{V}_{\mathrm{in}}$ | İnput voltage                                     |  |  |

| $\mathbf{V}_{t}$           | Threshold voltage                                 |  |  |

| gm                         | Transconductance                                  |  |  |

| W                          | Width (µm)                                        |  |  |

| L                          | Inductor (nH)                                     |  |  |

| $V_{\text{DD}}$            | Source voltage                                    |  |  |

| R <sub>s</sub>             | Series resistance                                 |  |  |

| R <sub>P</sub>             | Parallel resistance                               |  |  |

| Cs                         | Series capacitance                                |  |  |

| C <sub>P</sub>             | Parallel capacitance                              |  |  |

| P <sub>T</sub>             | Total power                                       |  |  |

| $V_{PP}$                   | Peak to peak voltage                              |  |  |

| TE                         | Thermoelectric                                    |  |  |

# **CHAPTER 1**

### **1** INTRODUCTION

#### 1.1 Background

The concept of smart cities under the paradigm of "sustainable development" boosts up the use of wearable electronic devices especially for communication, health care, and security applications as well as Internet of Things (IoT) applications. Along with the enhancement of consumer electronics (CE) and machine-to-machine (M2M) technology, the wireless interconnection of portable devices, which is one pillar of IoT, has become ubiquitous to increase efficient utilization. According to CISCO and several other organizations, the estimated minimum number of IoT device usage at 2020 is 50 billion [1]. The majority of IoT devices and consumer electronics including wearable electronic devices are wireless due to inconvenience and expense of wiring. Examples include wireless sensor networks with thousands of sensor nodes like WiseNet developed by CSEM [2] and others discussed by Yang [3] and Wagle [4]. However, an individual wireless device requires a temporary power reservoir such as a button cell battery. As a result, there are a number of ultra-low power wireless sensor protocols like ad-hoc networks [5] and intelligent sensor systems [6] in order to minimize the power consumption and utilize the battery usage.

In the past few decades, the evolution of batteries in terms of higher power density has made them more feasible for use in mobile electronic applications. Use of batteries may significantly increase system cost (including maintenance and replacement cost), however, and may be impractical in some of the implantable, portable and wireless system applications. Battery replacement is expensive, time-consuming, and inconvenient. Examples include on-body sensor nodes used for the chronic disease monitoring and treatments such as pacemakers [7], implantable pressure sensors [8], wireless transmission for the analysis [9], and thousands of smart sensor node networks for the IoT applications [10]. On the other hand, different subcircuits in an electronic system require different voltage levels for proper operation. The size and weight of the consumer electronic device increase in proportion to the number of batteries. In addition, the short lifespan of rechargeable batteries in mobile electronic devices (range of 2-4 years) results in an exponentially increasing amount of e-waste [11].

Despite the evolutional enhancement in quality of life through the technological advancement, the disproportional abundance of waste electronic and electric equipment (E-waste) emerges

as the fastest growing waste issue in the world [12], [13]. Computer related discarded appliances including IoT devices, and mobile electronic devices have been the dominant ewaste components during last decades due to their short lifespan. E-waste includes appliances that comprise of batteries, power cords, printed circuit boards with lead (Pb) soldering, and wires. Small scale batteries consist of different toxic materials and chemicals. The improper disposal or recycling can cause to seep or disintegrate these toxic compounds into the environment including heavy metals like Lithium, Nickel, lead, copper, and Cadmium, and toxic pollutants like LiClO<sub>4</sub>, LiPF<sub>6</sub> and LiBF<sub>4</sub> [14], [11]. But currently, 90% of discarded lithium-ion batteries which are used in consumer electronics (CE) are disposed to the environment without proper recycling as e-waste [15]. The discarded battery related hazards can be significant in next few years due to the massive abundance of mobile electronic applications. For instance, in 2014, China's (world largest lithium-ion battery manufacturer and consumer) estimated lithium-ion battery export is 1.32 billion which represents a 16.8% increase compared to the previous year [16]. Open burning of PCBs and PWBs (printed wire board) which are the major components of electronic devices [17] and wires has contributed to release hazardous chemicals, which potentially caused environmental pollution including the river water, air, and soil of the burning area [18]. The manufacturer to end-user transportation and recycle process also contributed to the fossil fuel combustion which causes the environmental pollution. Therefore, a global effort is ongoing in size reduction combined with low power consumption in order to enhance the lifespan and minimize the environmental hazard. Reduction of power consumption benefits systems by lowering battery size and minimizing the emission of greenhouse gasses due to the use of fossil fuels for grid power generation and transportation. Implementation of fully integrated circuit architecture leads to size reduction of the system and to elimination of wires, PCBs and PWBs in microelectronics. Therefore, smart device revolution along with sustainable developments triggers the necessity for integrated, lightweight, green-power solution with long lifetime as an alternative to the monolithic batteries.

One feasible green energy replacement for the battery is energy harvesting from ambient sources to directly power electronic devices (self-powering). As the development of very large scale integration (VLSI) technology allows downscaling of the power consumption and area of the integrated circuit devices, small-scale energy harvesting techniques become feasible in powering smart electronic devices. Furthermore, micro- to milli-power harvesting systems allow elimination of grid connection and rechargeable batteries to advance the energy autonomy of mobile electronic devices [19].

#### **1.2** Common energy harvesting techniques

There are several types of promising small scale energy harvesting techniques including solar, kinetic, thermal, fuel cell, bio mass, piezoelectric, and electromagnetic. Solar, thermoelectric, kinetic, and electromagnetic energy harvesting are four most common small-scale ambient energy scavenging techniques developed in last few decades. The source for the ambient energy harvesting depends on the application. For example, the human body is the most usual energy harvesting source for the wireless body area network (implantable sensor node). The kinetic and thermal are the usual kind of techniques used in human body generated power for mobile applications [20] e.g. wearable sensor networks and computing microchips.

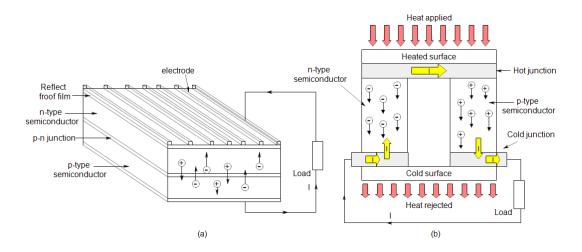

The solar or photovoltaic energy emerged as a viable technique due to the successful ongoing research effort on sustainable green energy solutions for the increasing energy demand. Photovoltaic cells have the property to convert incident light into electricity through charge separation of two materials with different conduction mechanism [21]. These two materials are composed of P-type semiconductor and N-type semiconductor, which enable charge flow in one direction as shown in Figure 1.1(a). Because solar cells work as a flux sensitive voltage limited current source [22]. The power density of a typical solar cell in outdoor at noon is 15 mW/cm<sup>2</sup> [22] and is limited to several tens of  $\mu$ W/cm<sup>2</sup> (typically 10  $\mu$ W/cm<sup>2</sup> [23]) for the indoor applications due to the limited solar flux density. Summing voltage through series connection of the solar cells makes high output voltage feasible. But the necessary area is also increased with the number of solar cells. Despite the availability and ease of access, solar energy harvesting has poor energy security. Due to the dramatic variation of the source power, an energy storage reservoir such as a battery or a super capacitor is necessary to prevent a power failure.

Thermoelectric energy harvesting technique uses the phenomena of Seebeck effect to convert thermal energy into electrical energy. The pyroelectric materials have the property to generate an electrical charge with the temperature gradient. There have been a number of ongoing successful research efforts to implement large scale thermoelectric energy harvesting techniques. For example, waste thermal energy of vehicle exhaust and industrial processes can generate electrical energy using thermoelectric harvesting technique [24]. The lack of moving parts in the thermoelectric generators along with reliability and scalability make them ideal for small scale energy harvesting [25]. The thermoelectric generator consists of a series array of thermocouples [26] which generate voltage difference across the two terminals due to the temperature gradient as shown in Figure 1.1. (b).

Figure 1.1. (a) Solar cell for photovoltaic, and (b) thermocouple for thermoelectric, energy harvesting.

The thermopiles of the thermocouple consist of p-type and n-type semiconductors to generate a voltage drop across the p-n junction due to the different mobility of charge carriers, which are stimulated and flow from high-temperature terminal to low-temperature terminal. The generated voltage is proportional to the temperature difference (V= $\alpha$ .  $\Delta T$ ). The proportionality constant ( $\alpha$ ) is the Seebeck coefficient of the thermoelectric material. Despite the inverse proportionality between Seebeck coefficient with conduction electron density, the highest Seebeck coefficients have been observed in semiconductors. Since the highest observed Seebeck coefficient is limited to at most hundreds of microvolts per Kelvin [27], a large temperature gradient is necessary to generate tens and hundreds of milli-Volts in small area. Recent development of the microelectronic technology utilizes the feasibility to fabricate the micro-technological thin film substrate thermoelectric generators. The first microtechnological thermoelectric generator was fabricated by Rowe and co-workers with the leg dimension of 4.5 mm x 20  $\mu$ m x 0.4  $\mu$ m and 530  $\mu$ V/K Seebeck coefficient [28]. Due to the limited Seebeck coefficient of the thermoelectric generators, the output voltage of the thermocouple is in the range of 20-400 mV at most for typical environment conditions [29]. The temperature gradient of the thermoelectric generator is a function of the ambient temperature. Therefore, voltage boost up converter with temporary energy receiver is essential for the system applications.

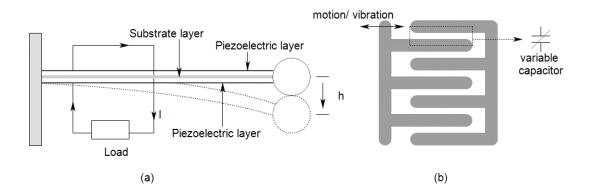

The energy extracted from the mechanical movement in the environment can be converted into electrical energy through kinetic energy harvesting techniques. The most commonly available form of environmental kinetic energy is vibration, which can be converted into electrical energy using piezoelectric, electrostatic and electromagnetic, techniques [30]. The electromagnetic harvesting method is commonly used in macro scale wind and hydro generators. The environmental kinetic energy is used to rotate the coil, which is placed in the magnetic field to induce current on the coil following Faraday's law. Printed coils and permanent magnets are utilized for the micro scale harvesting techniques. Converted output voltage level depends on the magnetic field strength, number of turns of the coils and rate of change of the flux (rotational speed of the mass/spring). Piezoelectric materials can generate an electric charge when the substrate is squeezed or stretched [31] as shown in Figure 1.2. (a). The generated voltage is proportional to the substrate stress. The oscillator system connected to the piezoelectric material cantilever generates AC voltage with irregular amplitude. Electrostatic energy harvesting mechanism is based on varying the capacitance of a fully charged capacitor, as illustrated Figure 1.2. (b). Change in capacitance produces a voltage across the capacitor terminals to keep the voltage or charge of the capacitor constant. The utilization of on-chip MEMS variable capacitors makes electrostatic converter more attractive compared to electromagnetic methods due to the lack of bulky inductors. However, it is necessary to have a temporary power reservoir such as a battery for the initialization of the capacitor charge.

Figure 1.2. (a) Piezoelectric energy harvester, (b) electrostatic energy harvester, to convert kinetic energy into electrical energy.

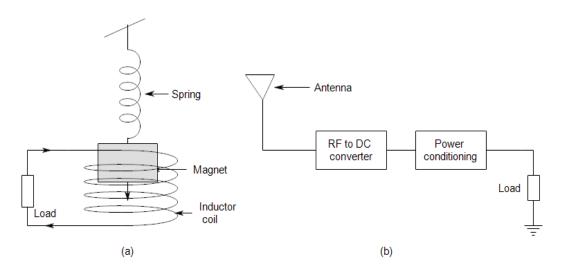

The vibration of the permanent magnet attached spring can be used to generate the electromagnetic electricity as illustrated in Figure 1.3. (a). The rate of change of magnetic flux through the inductive coil generates the electric current through the coil, following the Faradays law.

Figure 1.3. (a). Electromagnetic vibration energy harvester, (b) RF energy harvester.

The current environment consists of billions of electromagnetic waves due to the development of wireless communication and broadcasting. RF wave harvesters contain three main components to harvest electrical energy as shown in Figure 1.3. (b): Antenna to receive the high-frequency EM waves, AC to DC converter to convert the captured signals into electric current, and voltage step-up converter with the regulator to boost up the voltage for the usable range.

### **1.3** Problem associated with the energy harvesting techniques

The common phenomena of the ambient energy harvesting system are the infinite lifetime compared to the environmental hazardous short lifetime batteries as illustrated in Table 1.1.

| Energy harvesting mechanism |                    | Power density-one year             | Power density-ten year            |

|-----------------------------|--------------------|------------------------------------|-----------------------------------|

|                             |                    | lifetime                           | lifetime                          |

| Solar-outdoor [32]          |                    | 30 - 5 mW/cm <sup>2</sup>          | $30 - 5 \text{ mW/cm}^2$          |

| Solar-indoor [33]           |                    | 13- 88 µW/cm <sup>2</sup>          | 13-88 $\mu$ W/cm <sup>2</sup>     |

| Vibration                   | Piezoelectric [34] | $1500 \mu\text{W/cm}^3$            | $1500 \mu\text{W/cm}^3$           |

|                             |                    | @ 10 m/s <sup>2</sup> acceleration | $@ 10 \text{ m/s}^2$ acceleration |

|                             | Electrostatic [35] | 133 µW/cm <sup>3</sup> @ 1.3 kHz   | 133 µW/cm <sup>3</sup> @ 1.3 kHz  |

| Thermal [36]                |                    | $60 \ \mu W/cm^3$                  | $60 \ \mu W/cm^3$                 |

|                             |                    | @ 5 °C gradient                    | @ 5 °C gradient                   |

| Batteries                   | non-rechargeable   | $45 \ \mu W/cm^3$                  | $3.5 \mu\text{W/cm}^2$            |

| [31]                        | rechargeable       | $7 \ \mu W/cm^3$                   | 0                                 |

Table 1.1. Power density comparison of energy sources used for energy harvesting.

But there are three common adverse characteristics of the ambient energy harvesters which have to be taken care of in mobile applications.

- The harvester output is unregulated.

- The generated output power is interrupted and not continuously steady state.

- The average output power is limited in the range of at most few tens of mW, and the output voltage is typically at most couple of hundreds of mV.

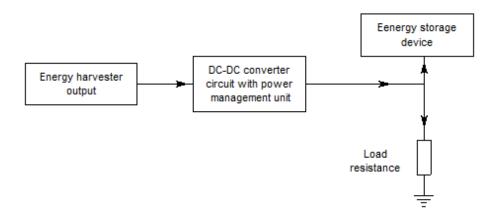

Since the harvester output is a function of the corresponding environment parameter (e.g. ambient temperature for the thermoelectric generator), the energy harvester cannot be used for direct powering of the electronic devices. For example, a small scale thermoelectric generator '1MD02-035-03TEG' with the hot side at 35 °C and at 55 °C generates 0.07 V, 1 mW and 0.24 V, 10 mW optimum output respectively while cold side is at 27  $^{\circ}$ C. Any reduction in the hot side temperature causes a corresponding drop in the output voltage and possible shut down of the electronic device. Therefore, the harvester output is often connected to a small temporary storage used in mobile applications such as capacitors, super capacitors, and small rechargeable batteries. But the harvester output is too low to charge these components up to the required voltage levels. The minimum sink voltage for the typical rechargeable battery is around 1 V [37] which can be 4-10x of the output voltage level of the micropower harvester. The monocrystalline silicon solar cell 'TG18.5 BR' has 500 mV output at outdoor applications with a light intensity of 100 mW/cm<sup>2</sup> [38]. But the output voltage of the typical single solar cell is limited to at most 200 mV in dark office environment [39] The small scale (centimeter range) piezoelectric device generates alternative voltage with milliwatt range at typical ambient conditions [40]. Hence the AC to DC converter is necessary for kinetic energy harvesting application for the mobile electronic powering. The RF energy harvester also needs an AC-DC converter for the electronic applications. But the typical output voltage level of these single stage AC-DC converters is limited to 200 mV at ambient conditions. The output voltage level of these converters can be boosted up using stages of charge pumps, which decrease the efficiency of the system. Low efficiency leads to increase in power dissipation and causes heating problems, which are important in implantable microelectronic applications. Therefore, a power management unit is necessary between harvester interface and the electric load as shown in Figure 1.4.

Figure 1.4. Block diagram of the energy harvester interface.

Employing the energy management unit of the energy harvester array through a direct current to direct current (DC-DC) converter offers voltage boost up method to generate the DC voltage to drive the load. Therefore, an integrated DC-DC converter enhances the mobile electronic application by reducing the battery area or even completely replacing the battery from energy harvester prototype. But the existing low voltage DC-DC converters are relatively low in performance; few high-performance implementations are built from discrete components such as bulky inductors and capacitors and are usually limited in charge delivery at a low input voltage and poor output characteristics at low load resistance.

#### **1.4 DC-DC converters**

DC-DC converters are widely used in almost all portable electronic devices like laptops, MP3 players, mobile phones, and other wearable electronic devices. The smart electronic devices comprise of several sub-circuits with different operational load voltage. Therefore, the DC-DC converter circuits are used to convey the necessary voltage level for the load resistance from the main power reservoir like a battery or an energy harvester. A good commercial DC-DC converter should satisfy the following requirements;

- Low cost

- Good steady state performance (constant output voltage for ripple input)

- Minimum start-up conditions

- Ability to self-start

As all other smart devices, the DC-DC converter should be lightweight, small in scale, high in efficiency, low in cost, to be competitive in the market. As a result, the best solution in terms of economy is integrated design with high efficiency. The steady state performance is the output characteristics of the DC-DC converter with the different conditions at the inputs. A

good design should deliver maximum power and maximum output voltage level for the given conditions. The output variation should be minimal. The output characteristic variation like efficiency, charge delivery, output level for different load conditions, should be within a specific range for the considerable range of input. Availability of minimum start-up condition with self-starting capability increases the number of possible microelectronic applications.

DC-DC converters are categorized into two groups according to the conversion direction of the design: Step up converters and step down converters. The step down DC-DC converters are commonly used for electronic applications that recharge batteries through the grid connection. Examples include the standard 12 V laptop battery step down to 5 V to power USB ports and keyboard through the step-down converter. The requirement and popularity of the step-up DC-DC converter arises with switching the source from grid power to the sustainable green power for the smart applications. Hence, DC boost up converters are popular in energy harvester applications due to the limited source voltage. There are few step-up converter applications available in past generation portable electronic devices. For example, a 3 V battery operates portable radio which has an audio amplifier with 5 V supply for the proper operation. In order to have a long battery life, the efficiency of the DC-DC converter should be high to minimize the power losses in addition to avoiding heating problems.

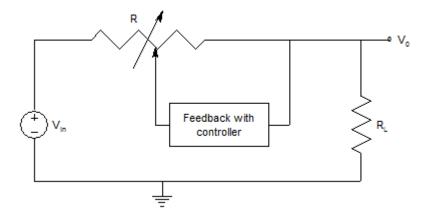

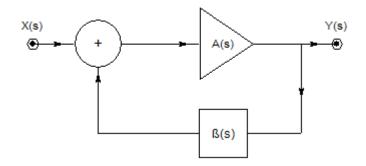

There are two fundamental types of DC-DC voltage converters. The first type is linear conversion based on the voltage divider using the array of resistors also known as linear regulators. The block diagram of the linear voltage converter is shown in Figure 1.5. Variable resistor (R) can be replaced with a MOSFET in the linear region for on-chip integration. The feedback with control system adjusts the variable resistor to keep output at a constant voltage regardless of the load variation. The main drawbacks of this linear DC converter are the significant power dissipation and the fact that it achieves only step down conversion. Therefore, the efficiency of the linear DC converter depends on the variable resistor and the current through the feedback loop. The current through the feedback loop is low and the power dissipation of the controller is small. The advantage of area reduction and cost benefit compared to the distinctive battery usage results in wide usage of the linear DC converters for different electronic circuit applications.

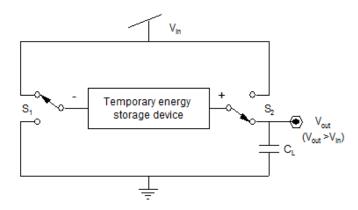

Figure 1.5. Block diagram of linear DC converter.

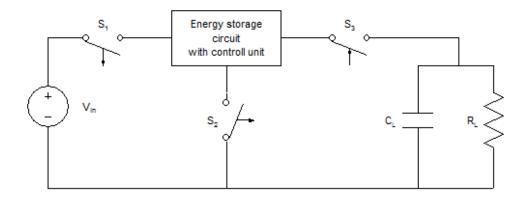

The second type is switch mode DC converters, which are nonlinear. Unlike the linear DC converters, the switch mode DC-DC converters consist of switches, energy storage devices like capacitors and inductors as shown in Figure 1.6. The switches are an extension of the control unit of the DC-DC converter, which regulates the energy accumulation in temporary storage devices and then feeds them into the load. MOSFETs are used as switches to improve the integration and performance of the conversion in terms of switching speed and energy loss. Depending on the temporary energy storage devices used, the switch mode DC-DC converters can be categorized into two groups: The first type consists of only capacitors as the energy storage device, the second type consists of both capacitors and inductors as energy storage devices. The first type is smaller in scale compared to the second type due to the lack of bulky inductors. The main advantage of the switch mode DC-DC converter is the possibility of achieving both up conversion and down conversion using proper controller unit implementation and topology adjustments according to the application. In addition, the switched mode DC-DC converter efficiency is higher than the linear DC converters due to lack of large resistance in series with the load. Through proper selection of device parameters and switching frequency according to the application goal, the converter can be implemented as a low cost, fully integrated module with the lightweight and small scale to satisfy the economic requirement of the market. Using temporary energy storage devices, like capacitors, together with switching mechanism minimizes the output variation due to the effect of noise and input variations. Therefore, the switch mode DC-DC converter can achieve high steady state performance. Implementing a feedback loop with control unit can improve the dynamic characteristics of the converter. Therefore, the switch mode DC-DC converters are more advanced compared to the typical linear DC-DC converters.

Figure 1.6. Block diagram of the switch mode DC-DC converter.

### **1.5 DC-DC converter efficiency**

Power efficiency is one of the main characteristics of the electronic devices to evaluate the feasibility of use for the applications. In low power energy harvesting, high efficiency is necessary to minimize the energy losses and transfer the maximum power to the load. The power efficiency ( $\eta$ ) of DC-DC converter can be expressed as,

$$\eta = \frac{P_{out}}{P_{in}} \times 100\% = \frac{V_{out}.I_{out}}{V_{in}.I_{in}} \times 100\%,$$

(1)

where  $P_{out}$  is the output power and  $P_{in}$  is the input power. The input power can be expressed as the product of source current ( $I_{in}$ ) and the source voltage ( $V_{in}$ ) while output power is the product of sink current ( $I_{out}$ ) and sink voltage ( $V_{out}$ ). The main lossy component in the linear DC-DC converter is the variable resistor. If the feedback loop current is negligible, the efficiency of the linear DC converter can be simplified as the ratio of output voltage and input voltage. Due to the buck conversion property, the efficiency is low in linear DC converter. The efficiency of the switching DC-DC converter is a function of the circuit component parameters, switching frequency, and input voltage. Because in high-speed, low-cost integrated DC-DC converter, switches are implemented with MOSFETs, and they have a finite resistance which contributes to the energy loss. The internal resistance of the inductor also plays a part in the energy loss as a function of the square of current through the inductor multiplied with the self-resistance of the inductor. The capacitor energy loss is a function of operational frequency (f), capacitance (C), and the voltage change across the capacitor (V), as,

$$P_{Cap.\ loss} = CV^2 f. \tag{2}$$

In order to achieve a good design, proper optimization is necessary with consideration of efficiency, power delivery, and circuit area. To facilitate the optimization, a good circuit model is essential. There are few research papers presented in the literature to address the design optimization of the DC-DC converter to increase the performance. In applications with low input voltage, however, the performance of the MOSFET switches decreases. Especially in ultra-low power energy harvesting applications, the output of the energy harvester is limited to at most couple of hundreds of mV, typically less than the threshold voltage of the MOSFET. As a result, most of the published research implementations and design architectures in regards to the DC-DC converters are less applicable for the low voltage operation. Even when such designs function, the efficiency is drastically small compared to the theoretical predictions or analysis. Hence, highly efficient, novel DC-DC converter topology with design optimization methodology is necessary for the ultra-low voltage sources such as small energy harvesters.

#### **1.6** Objectives of the thesis

The goal of this work is to design a fully integrated, self-starting, highly efficient, ultra-low voltage step-up DC-DC converter with high output power capacity for energy harvesting applications. The circuit is implemented in 180 nm standard CMOS technology with only on-chip circuit components. A comprehensive list of objectives of the thesis is as follows:

- Study and recognize the main drawbacks of the existing DC-DC converter circuits.

- Implement a fully integrated oscillator design, which can self-start at the input voltage  $(V_{in})$  of 0.2±50% to generate two out-of-phase periodic signals with amplitude  $\geq 2 \times V_{in}$ .

- Implement a DC-DC converter based on an integrated charge pump circuit to deliver maximum output voltage and power.

- Propose and implement novel methods to model the DC-DC converter in order to analytically optimize and enhance the performance in terms of efficiency and output power. Validate the model based results with circuit simulations with extracted parasitics in UMC 180 nm process technology.

- Layout, fabricate, and validate a DC-DC converter test chip to characterize performance with different input voltage levels and load resistances. Analyze the discrepancy between simulations and measurements for further improvement of circuits and associated models.

Design of voltage regulators and maximum power point tracking (MPPT) control circuits are not within the scope of this thesis.

#### 1.7 Thesis outline

The remaining part of the thesis is organized as follows: The basic principle of the voltage step-up DC-DC converter is described in chapter 2 including charge pump circuit techniques for integrated voltage step-up, and different types of oscillator circuits to stimulate charge-pumps. A literature review to identify advantages and drawbacks of the existing low voltage oscillators and charge pumps is also discussed in this chapter.

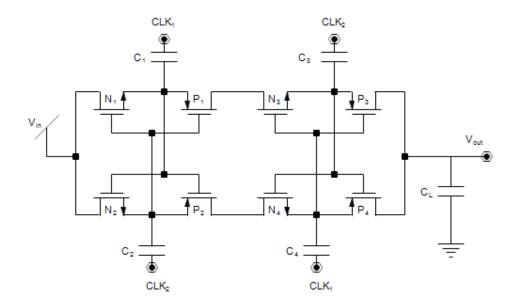

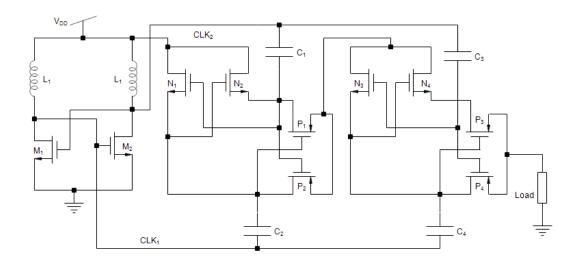

Chapter 3 discusses two different novel LC tank oscillator designs, and features of these oscillators. A model based analysis is presented for the working principles, oscillation frequency and power efficiency calculations. Simulation results are presented for the verification of the model.

In chapter 4, two fully integrated DC-DC converter designs are presented, which are optimized for energy harvesting applications with higher power at ultra-low input voltage levels, compared to other solutions in the literature. The detailed model based analysis is also provided to determine the variation of clock frequency with circuit component parameters. Model based power consumption analysis the DC-DC converter topology with voltage doubling LC tank is also presented in this chapter. An optimization methodology is presented for high power delivery under the constraint of design area, and the model is verified through simulation results.

Chapter 5 presents the proposed test chip design and layout of the multi-stage DC-DC converter. The comparison of the measurements, simulations, and model based analytical results is presented. Based on major deviations observed in measurements due to previously ignored parasitic effects, a re-built model with more accurate layout parameters is used for post-layout simulation results to match silicon results.

Conclusions and future work are presented in Chapter 6.

### **CHAPTER 2**

## 2 BACKGROUND

#### 2.1 Introduction

Smart low power wearable electronic systems and smart IoT applications are the current trend of new generation. Most often, the small scale batteries are the power source for such tiny circuits and dominate the volume of the package [41]. As a result, the power source (typically a battery) is a critical factor for portability and lightweight of the device. The small button cell batteries like 'Duracell DA 13 (features - 7.9 mm×5.4 mm, 290 mAh)' and 'Duracell DA 675 (features - 11.6 mm×5.4 mm, 290 mAh)' are currently used for portable micropower applications like wearable wireless medical devices. However, the individual output voltage of these small battery cells is limited to a maximum of 1.4 V, which is below the operational voltage of most micro power loads (most of the standard microcontrollers operate in a range of 1.8 V to 3.6 V) [41]. In the majority of circuit designs, the power requirement of different sub-circuits in main hardware is different and impossible to feed on the main battery without a power management unit. Use of discrete batteries for each sub-circuit is impractical as they increase the cost of product, size, and weight. Therefore, utilizing energy harvesting coupled with voltage boost up unit for direct powering or recharging the main battery is an essential need for the next generation of microelectronic portable and smart devices. The problem associated with energy harvesting is the generated low voltage at ambient conditions, which is on the order of a couple of hundreds of millivolts, and which is not sufficient to fulfill the load voltage requirement. Therefore, the harvester output voltage has to be boosted up to a certain voltage level to compensate the load power requirement. Switch mode DC-DC converters are utilized to boost low DC input into a higher level of DC voltage. The problem related to the DC-DC converter is the sharp performance degradation for the lower input voltage. The on-chip micro scale DC-DC converter circuits consist of low power MOSFETs with operating threshold voltage of couple of hundred of millivolts, but usually, the ambient energy harvester output is below the threshold voltage of the common and economical standard CMOS fabrication process, like 180 nm technology. As a result, through the evidence of previous works, self-starting, high performance, fully integrated, ultra-low voltage DC-DC converter implementation is a big challenge.

There are two types of switch mode DC-DC converters, categorized according to the energy storage element.

• Capacitive based DC-DC converters

Capacitors are the temporary energy storage elements in capacitive based DC-DC converters. The function of these capacitors is to store and deliver charge from one stage to next stage, according to a switching mechanism. Therefore, the DC-DC converter voltage gain has a positive relationship with capacitor size and converter stages, but large capacitors cause a significant amount of energy dissipation. Large capacitors need large space on the chip, which is critical in the fully integrated process. Hence, an optimization methodology is necessary for the on-chip capacitive based DC-DC converter architecture to achieve the design goal.

• Inductive based DC-DC converters

Inductors are the temporary energy storage elements in inductive based DC-DC converters. They also boost up the DC supply by integrated switching mechanism. Advanced inductor based DC-DC converters consist of many capacitors and inductors to store energy in the form of charge and magnetic field, respectively. The essential large area for the inductors is the main disadvantage of inductive based DC-DC converter architecture. For the best DC output with minimum ripple, the operational switching frequency is necessary to be at least in MHz range. As a result, inductance should be within the range of a couple of tens of nH while capacitance in pF range. Perhaps the connectors of the discrete inductors generate significant capacitance and inductance in Pico and Nanoscale, respectively. Due to the advances in integration, tolerance in component parameters, cost, area, and lightweight, the on-chip inductors are more reliable for the ultra-low voltage DC-DC converter design.

Integration of inductors and capacitors are critical for the feasibility of on-chip DC-DC converter design in micro-scale area with significant cost saving for the wearable micro power electronic applications. Unlike RF integrated inductors, the inductance of the DC-DC converters should be much larger and have lower self-resistance. For the best performance, the parasitic capacitance and the inductance of on-chip inductors and capacitors should be minimum. As a result, designing on-chip inductors and capacitors for the DC-DC converter is a big challenge.

### **2.2 DC-DC converter fundamentals**

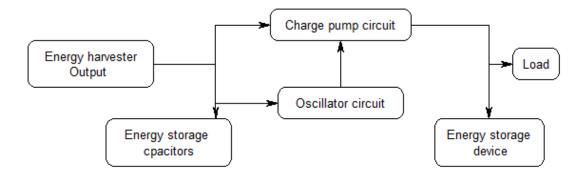

Figure 2.1 illustrates the block diagram of a conventional switched mode DC-DC converter for low voltage energy harvesting applications. The output voltage of the energy harvester is varied with the ambient condition. Therefore, the energy storage capacitor is necessary to prevent the voltage ripple at the input terminal of the DC-DC converter. The DC-DC converter consists of two sub-circuits: Oscillator circuit and charge pump circuit. The oscillator circuit generates the necessary clock signals to drive the switching MOSFETs. The clock signal can work as a charge source for the energy storage elements. The advanced oscillators are feasible with high gain amplitude oscillations. They boost up the DC-DC converter output and achieve high efficiency with fewer circuit components. The DC-DC converter output is parallel connected with the load resistance and energy storage devices such as small rechargeable batteries or supercapacitors. The energy storage device is necessary to secure the power requirement of the load in case of the failure of energy harvester in unexpected critical environmental condition. Once the load is inactive, the energy storage device will charge and store energy for compensating power failure.

Figure 2.1. The block diagram of a switch mode DC-DC converter for energy harvesting applications.

Power efficiency, minimum start-up voltage, high power output, response to input voltage variation, output voltage ripple, and area are the basis for evaluating the performances of DC-DC converter topology. In general, the efficiency and on-die area are the most important parameters of the on-chip micro power DC-DC converters. This is because a highly efficient design has minimum power dissipation and maximum load power for a given input. If the power dissipation is high, even with sufficient output power, the design should employ a cooling system to prevent heating. The area downscaling increases the feasibility of DC-DC converter usage in applications like body area network and IoT.

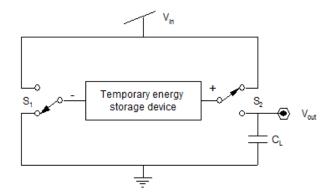

The switch mode DC-DC converter consists of energy storage devices and switching mechanism for energy accumulation as illustrated in Figure 2.2. Once S1 and S2 are grounded and connected to the source voltage, respectively, the charge will flow through the energy storage device and accumulate energy on it. Most often, fully integrated or partially integrated capacitors are the temporary energy storage elements for the DC-DC converter. As a result, there is always an energy loss, which is proportional to the switching frequency of the DC-DC converter. The opposite state of S1 and S2 switches make the series connection of source, energy storage device, and load capacitor as depicted in Figure 2.3. In the case of the capacitor as the temporary storage device, neglecting the losses, the load capacitance can be charged to Vout  $= 2 \times Vin$ . The high-speed switching is necessary for DC voltage at the output node. Therefore, switches are replaced from MOSFETs for higher performance of the DC-DC converter. The switches are driven by a pair of clock signals with optimal frequency for minimum ripple at the output.

Figure 2.2. Energy accumulation of the energy storage device in the DC-DC converter.

Figure 2.3. The energy transferring from energy storage device to load capacitor of the DC-DC converter.

### 2.3 Switch mode charge pump topologies for DC-DC converter design

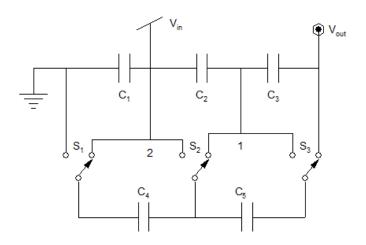

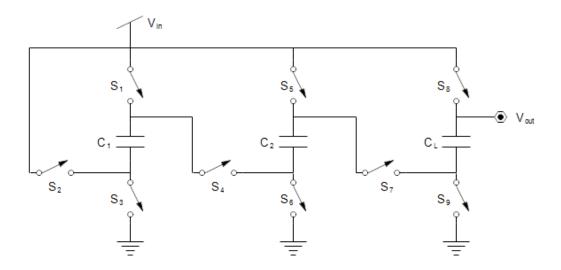

The development of the microelectronic architecture with integrated CMOS design has increased the attention to different charge pump topologies to enhance the performance in ultra-low voltage applications. The enhanced versions of basic charge pump topologies are used for the DC-DC converter applications. The schematic of the Cockcroft-Walton charge pump circuit, which is one of the primary charge pump circuits, consists of capacitors and switches as shown in Figure 2.4. Once S<sub>1</sub> and S<sub>2</sub> switches are connected to ground and node 2, respectively, C<sub>1</sub> and C<sub>4</sub> will accumulate charge from the source voltage (V<sub>in</sub>). When the switches change the state, C<sub>2</sub> and C<sub>4</sub> will be parallel to each other; each of them will charge to V<sub>in</sub>/2. Then, S<sub>1</sub> and S<sub>2</sub> switches are connected to ground and node 2, respectively, C<sub>4</sub> and C<sub>5</sub> will charge to Vin and V<sub>in</sub>/4 respectively. Finally, V<sub>out</sub> will reach  $3V_{in}$  after several switching states if all the charge pump capacitors are identical. This charge pump topology is low in efficiency at a given load condition, compared to the alternative charge pump topologies. The charge pump performance is adversely proportional to the charge pump stages.

Figure 2.4. Cockcroft-Walton charge pump.

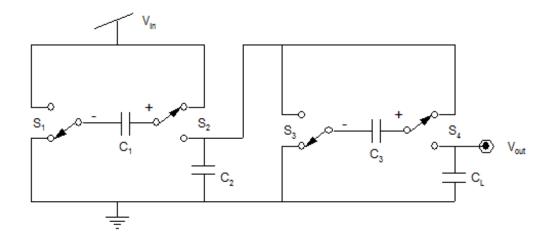

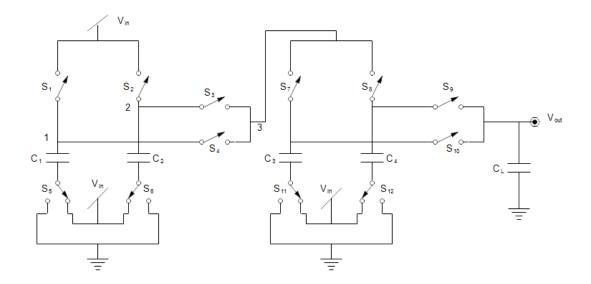

Two phase cascade voltage doubling charge pump is another basic charge pump which consists of dual capacitors and switches in each stage as shown in Figure 2.5. The configuration of  $S_1$  ground and  $S_2$  source connection allows accumulating energy on  $C_1$  in the form of charge. The opposite connection of switches makes the series array of the source,  $C_1$ , and  $C_2$ . Therefore,  $C_2$  will reach  $2V_{in}$  for the ideal capacitors. Similarly, fully charge  $C_2$  is the source of  $C_3$  capacitor.  $C_3$  will charge to  $V_{in}$  (if  $C_2 = C_3$ ) when  $S_3$  is grounded and  $S_2$  and  $S_4$  are connected to  $V_{in}$  and  $C_2$ , respectively. Opposite switching states allow  $C_3$  in series with  $C_L$ ,  $C_1$ , and  $V_{in}$  to achieve  $V_{out} = 4V_{in}$ . For the ideal circuit components, the peak voltage at  $S_2$  and  $V_{out}$

is  $2 \times V_{in}$  and  $4 \times V_{in}$ , respectively. Therefore, the voltage gain of the N stage two-phase cascade voltage doubling charge pump is 2N. In CMOS process, switches are replaced with MOSFETs that are controlled for high-speed switching to achieve minimum ripple at output nodes. The leakage current of the charge pump is the main drawback of the design. The parasitic capacitance also contributes to decreasing the voltage gain of the topology.

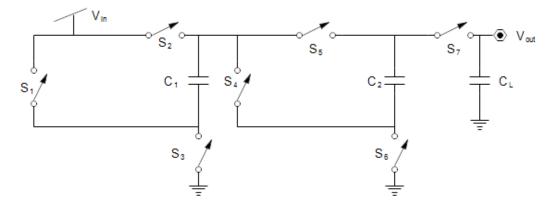

Figure 2.5. Two-stage of two phase cascade voltage doubler charge pump circuit [42]. Makowski proposed a dual phase charge pump topology; each stage consisting of a single capacitor and three switches as illustrated in Figure 2.6. The N stage charge pump is composed of N+1 capacitors and 3N+1 switches. S<sub>2</sub>, S<sub>3</sub>, S<sub>4</sub>, and S<sub>7</sub> switches are operated synchronously while S<sub>1</sub>, S<sub>5</sub>, and S<sub>6</sub> are opposite. Once S<sub>2</sub>, S<sub>3</sub> are closed, and S<sub>1</sub>, S<sub>5</sub> are open, C<sub>1</sub> capacitor accumulates energy from the source and reaches Vin. Then, S2, S3 open and S1 turn-off to achieve 2V<sub>in</sub> at the output of the first stage. Simultaneously S<sub>5</sub>, S<sub>6</sub> turn-off, and S<sub>4</sub> will open. Therefore, first stage output works as a source for the second stage. Similarly, two switches in each stage have the same operation while others switch in opposite direction. Hence, an antiphase dual clock system can be replaced in CMOS architecture to drive the MOSFET switches. The maximum voltage gain of the N stage of Makowski charge pump is N+1. Makowski topology requires the least number of capacitors to achieve the given voltage gain compared to the other existing topologies [43]. The charge pump stages for a given voltage gain can be calculated using the Fibonacci number described in [43], but determination of the switching frequency, capacitor sizes, and switched MOSFET parameters for the maximum efficiency is critical. Despite the high voltage gain, the Makowsky topology has low efficiency compared to the Dickson charge pump circuit [44].

Figure 2.6. Makowski charge pump topology.

The three-stage of the voltage step-up ladder charge pumps circuit consists of 9 switches and three capacitors as shown in Figure 2.7. The switches  $S_2$ ,  $S_4$ , and  $S_7$  are synchronized, and are switched off-phase with the other switches. Once  $S_2$ ,  $S_4$ , and  $S_7$  open, then  $C_1$  and  $C_2$  capacitors will charge from the source voltage. When  $S_2$ ,  $S_4$ , and  $S_7$  are off, the flying capacitors are in series with each other and  $V_{in}$ . Therefore, the output is the summation of the voltage across all flying capacitors and the source. The N stage ladder circuit can achieve a maximum gain of 2N at open circuit condition.

Figure 2.7. The voltage step-up ladder charge pump architecture [45].

Unlike the other existing switch mode charge pump topologies, the dual phase cascade DC output voltage double charge pump has the minimum ripple output at each stage. Each stage of the circuit consists of six switches and two capacitors to maintain the DC output and voltage gain at each stage.

Two-stage of dual phase cascade DC output charge pump topology has four output switches as depicted in Figure 2.8. The operation of the S<sub>1</sub> switch is opposed to the S<sub>2</sub> while S<sub>1</sub> and S<sub>2</sub> are synchronous with S<sub>4</sub> and S<sub>3</sub> respectively. Once S<sub>1</sub> and S<sub>2</sub> are open and closed correspondingly, S<sub>6</sub> and S<sub>5</sub> will connect to ground and V<sub>in</sub> respectively. Therefore, the charge will flow through the C<sub>2</sub> capacitor and accumulate energy on it. Then switch S<sub>1</sub> will be turned off while S<sub>2</sub> is open. At the same time, the grounded S<sub>5</sub> will allow the accumulation of charges on the C<sub>1</sub> capacitor. Simultaneously, the voltage at the node-2 will reach to 2V<sub>in</sub> due to the series connection of fully charged C<sub>2</sub> and V<sub>in</sub>. At this time the switch S<sub>3</sub> will turn-on while S<sub>4</sub> is turned-off to achieve 2V<sub>in</sub> at the output (node-3) of the first stage. At the opposite configuration of the switches, the series connection of Vin and fully charged C<sub>1</sub> allows the 2V<sub>in</sub> at the output of the first stage. Simultaneously, C<sub>2</sub> will start to accumulate energy on it. As a result, the node-3 is at DC voltage throughout the operation of the switching mechanism. The output switches in each stage reduce the leakage current and back-flow current in the system. Therefore, the charge deliverability and efficiency are higher than the other charge pump topologies.

Figure 2.8. Two-stage of dual phase cascade DC output voltage doubler charge pump circuit.

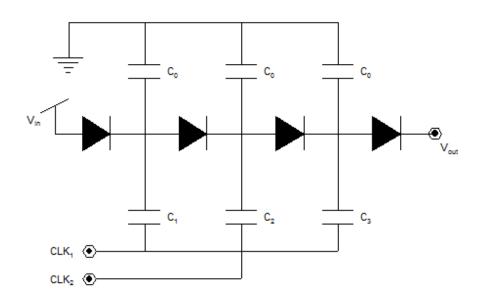

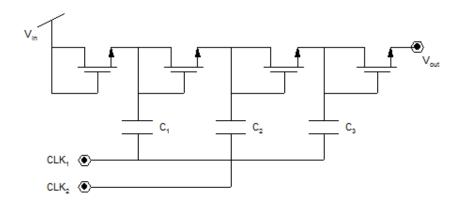

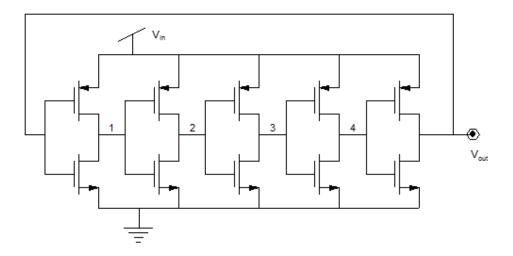

### 2.4 CMOS charge pump circuits for DC-DC converter applications

CMOS charge pump circuits are used for low power memory devices and analog electronic devices like flash memories, DRAM, EEPROM, etc. [46]. Cockcroft and Walton have proposed the first charge pump topology for high power electronic applications [47]. This design consists of mechanical switches to operate the charge transferring between corresponding capacitors on each stage. In 1976, Dickson proposed an advanced version of