# INVESTIGATION OF PARALLEL-CONNECTED GAN E-HEMT VSI-BASED SERVO DRIVES

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

HÜSEYIN YÜRÜK

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ELECTRICAL AND ELECTRONICS ENGINEERING

JANUARY 2022

### Approval of the thesis:

### INVESTIGATION OF PARALLEL-CONNECTED GAN E-HEMT VSI-BASED SERVO DRIVES

submitted by HÜSEYIN YÜRÜK in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Halil Kalıpçılar<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>        |  |

|---------------------------------------------------------------------------------------------------|--|

| Prof. Dr. İlkay Ulusoy<br>Head of Department, <b>Electrical and Electronics Engineering</b>       |  |

| Assoc. Prof. Dr. Ozan Keysan<br>Supervisor, Electrical and Electronics Engineering, METU          |  |

|                                                                                                   |  |

| Examining Committee Members:                                                                      |  |

| Assist. Prof. Dr. Emine Bostancı<br>Electrical and Electronics Engineering, METU                  |  |

| Assoc. Prof. Dr. Ozan Keysan<br>Electrical and Electronics Engineering, METU                      |  |

| Assist. Prof. Dr. Erhan Demirok<br>Electrical and Electronics Engineering, Dokuz Eylül University |  |

| Prof. Dr. Işık Çadırcı<br>Electrical and Electronics Engineering, Hacettepe University            |  |

| Prof. Dr. Muammer Ermiş<br>Electrical and Electronics Engineering, METU                           |  |

|                                                                                                   |  |

Date: 19.01.2022

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Surname: Hüseyin Yürük

Signature :

#### ABSTRACT

### INVESTIGATION OF PARALLEL-CONNECTED GAN E-HEMT VSI-BASED SERVO DRIVES

Yürük, Hüseyin Ph.D., Department of Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Ozan Keysan

January 2022, 138 pages

Nonlinearities in voltage source inverters (VSIs) are thought to be the primary cause of output voltage distortions which cause low-order harmonics in the output current. These nonlinearities also considerably degrades control performance and system stability for low-speed applications with low-inductance motors, particularly when the system operates in the low-torque area. The impact of the nonlinearities on the phase current and current control of a silicon (Si) metal-oxide-semiconductor field-effect transistor (MOSFET) based VSI are examined in this thesis using a coreless permanent magnet synchronous motor (PMSM). To address this issue, a gallium nitride (GaN) enhancement-mode high electron mobility transistor (E-HEMT) based VSI is proposed. Based on the results, a GaN E-HEMT VSI-based servo drive is being developed to replace its Si MOSFET VSI-based counterpart. It is about half the size of the previous one, allowing for the use of two servo drives in parallel rather than one for redundancy. The use of parallel-connected servo drives offers the benefit of increased torque capacity, reliability, redundancy, and modularity. Smaller variances in the system clocks of the separate microcontrollers, asynchronous pulse width modulation (PWM) carrier signals, and hardware differences, on the other hand, might

cause non-identical output voltages of the parallel modules, resulting in circulating currents. These circulating currents limit parallel operation, increase power consumption, induce imbalanced power distribution, and degrade control performance. A fault-tolerant parallel-connected GaN E-HEMT VSI based servo drive scheme is proposed to reduce the circulating currents and to eliminate the need for extra inductors at the output and separate DC supplies at the input of the inverters. Various experimental tests are conducted with up to six parallel-connected servo drives and a PMSM for validation.

Keywords: nonlinearity in VSIs, dead time, coreless PMSMs, GaN E-HEMT VSIbased servo drive, parallel-connected VSIs

### PARALEL BAĞLI GAN E-HEMT VSI TABANLI SERVO SÜRÜCÜLERİN İNCELENMESİ

Yürük, Hüseyin Doktora, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Ozan Keysan

Ocak 2022, 138 sayfa

Çıkış akımında düşük dereceli harmoniklere neden olan çıkış gerilimi bozulmalarının birincil nedeninin gerilim kaynağı eviricilerindeki (VSIIer) doğrusal olmayan yapılar olduğu düşünülmektedir. Bu doğrusal olmama durumları ayrıca, özellikle sistem düşük torklu alanda çalıştığında, düşük endüktanslı motorlara sahip düşük hızlı uygulamalar için kontrol performansını ve sistem kararlılığını önemli ölçüde düşürür. Doğrusal olmayan yapıların, bir silikon (Si) metal-oksit-yarı iletken alan etkili transistör (MOSFET) tabanlı VSInin faz akımı ve akım kontrolü üzerindeki etkisi, bu tezde çekirdeksiz bir sabit mıknatıslı senkron motor (PMSM) kullanılarak incelenmiştir. Bu sorunu ele almak için, bir galyum nitrid (GaN) geliştirme modlu yüksek elektron hareketli transistör (E-HEMT) tabanlı VSI önerilmiştir. Sonuçlara dayanarak, Si MOSFET VSI tabanlı yerine muadili GaN E-HEMT VSI tabanlı bir servo sürücü geliştirilmiştir. Bir öncekinin yaklaşık yarısı büyüklüğündedir ve yedeklilik için bir servo sürücü yerine paralel olarak iki servo sürücünün kullanılmasına izin verir. Paralel bağlı servo sürücülerin kullanımı, artan tork kapasitesi, güvenilirlik, yedeklilik ve modülerlik avantajı sunar. Ayrı mikrodenetleyicilerin sistem saatlerindeki küçük farklılıklar, asenkron darbe genişlik modülasyonu (PWM) taşıyıcı sinyalleri ve donanım farklılıkları ise paralel modüllerin özdeş olmayan çıkış gerilimlerine neden olabilir ve bu da dolaşan akımlara neden olabilir. Bu dolaşan akımlar paralel çalışmayı sınırlar, güç tüketimini arttırır, dengesiz güç dağılımına neden olur ve kontrol performansını düşürür. Hataya toleranslı paralel bağlı GaN E-HEMT VSI tabanlı bir servo sürücü şeması, dolaşan akımları azaltmak ve invertörlerin çıkışında ekstra indüktör ve girişinde ayrı DC besleme ihtiyacını ortadan kaldırmak için önerilmiştir. Doğrulama için altı adede kadar paralel bağlı servo sürücü ve bir PMSM kullanılarak çeşitli deneysel testler gerçekleştirilmiştir.

Anahtar Kelimeler: VSI'lerde doğrusal olmayan yapılar, ölü zaman, çekirdeksiz PMSM'ler, GaN E-HEMT VSI tabanlı servo sürücü, paralel bağlı VSI'ler To My Family

#### ACKNOWLEDGMENTS

The author would like to thank his supervisor, Assoc. Prof. Dr. Ozan Keysan, for his direction, support, criticism, motivation, and insight during the project.

The author wishes to express his gratitude to the members of his defense committee: Assist. Prof. Dr. Emine Bostancı, Assist. Dr. Erhan Demirok, Prof. Dr. Işık Çadırcı, and Prof. Dr. Muammer Ermiş.

The author would also like to thank his colleagues Dr. Barış Ulutaş, Onur Satılmış and Buğra Yasir Arslan for their assistance, and Aselsan Inc. for providing the facilities needed to complete this study.

The author wishes to express his gratefulness to his parents for their love, encouragement, and support entire of his life.

The author could not have finished the thesis without the unending love, support, and patience of his wife, Seda. This work is dedicated to her, as well as to their daughter Zeynep and son Sarper.

### TABLE OF CONTENTS

| A  | BSTRA | ACT                                                                    |

|----|-------|------------------------------------------------------------------------|

| Öź | Ζ     | vii                                                                    |

| A  | CKNO  | WLEDGMENTS                                                             |

| T/ | ABLE  | OF CONTENTS                                                            |

| LI | ST OF | TABLES                                                                 |

| LI | ST OF | FIGURES                                                                |

| LI | ST OF | ABBREVIATIONS                                                          |

| LI | ST OF | SYMBOLS                                                                |

| Cl | HAPTI | ERS                                                                    |

| 1  | INTR  | ODUCTION                                                               |

|    | 1.1   | Motivation and Scope of the Thesis 1                                   |

|    | 1.2   | The Outline of the Thesis                                              |

| 2  | NON   | LINEARITIES FOR SI MOSFET AND GAN E-HEMT BASED VSIS 11                 |

|    | 2.1   | Introduction                                                           |

|    | 2.2   | Nonlinearity Analysis of SI MOSFET-Based VSI                           |

|    | 2.3   | Experimental Study on SI MOSFET-Based VSI                              |

|    | 2     | .3.1 Observation of Current Harmonics as a Result of Nonlinear Effects |

|   | 2.3.2     | Relationships Between Switching Frequency and Nonlinearities                              | 23 |

|---|-----------|-------------------------------------------------------------------------------------------|----|

|   | 2.3.3     | The Calculation of the Compensation Function                                              | 30 |

|   | 2.3.4     | Experimental Results of the Compensation of the Nonlinearity                              | 32 |

|   | 2.4 Exp   | erimental Work with GaN E-HEMT Based VSI                                                  | 33 |

|   | 2.4.1     | Nonlinearities in GaN E-HEMT Based VSI: Effects of Switch-<br>ing Frequency and Dead Time | 33 |

|   | 2.4.2     | Nonlinearities in GaN E-HEMT Based VSI: Phase Current Harmonic Distortions                | 37 |

|   | 2.4.3     | Current Control Bandwidth Measurements of the GaN E-HEMT<br>Based VSI                     | 39 |

|   | 2.5 Pow   | er Loss and Cost Comparison                                                               | 40 |

|   | 2.6 Chap  | pter Summary                                                                              | 46 |

| 3 | GAN E-HE  | EMT VSI-BASED SERVO DRIVE DESIGN                                                          | 49 |

|   | 3.1 Intro | oduction                                                                                  | 49 |

|   | 3.2 Wid   | e Bandgap Semiconductor: Gallium Nitride E-HEMT                                           | 49 |

|   | 3.2.1     | History                                                                                   | 49 |

|   | 3.2.2     | GaN HEMT Structure                                                                        | 50 |

|   | 3.2       | .2.1 Cascode GaN HEMT                                                                     | 50 |

|   | 3.2       | .2.2 True Normally off GaN HEMT                                                           | 51 |

|   | 3.2.3     | Material Properties                                                                       | 52 |

|   | 3.2.4     | Third Quadrant Operation                                                                  | 54 |

|   | 3.2.5     | Current Collapse Effect                                                                   | 55 |

|   | 3.2.6     | Short Circuit Behavior                                                                    | 56 |

|   | 3.2.7     | High $dv/dt$ and Switching Frequency $\ldots \ldots \ldots \ldots$                        | 57 |

|   | 3.2.8     | Importance of Layout Design                                              | 57 |

|---|-----------|--------------------------------------------------------------------------|----|

|   | 3.3 GaN   | E-HEMT VSI-Based Servo Drive Design                                      | 58 |

|   | 3.3.1     | The Inverter Card of the GaN E-HEMT VSI-based Servo Drive                | 60 |

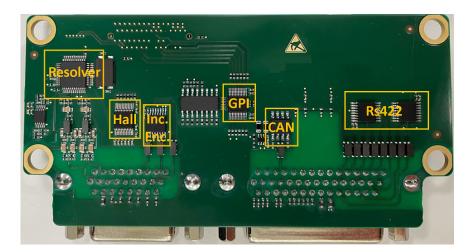

|   | 3.3.2     | The DSP Card of the GaN E-HEMT VSI-based Servo Drive .                   | 64 |

|   | 3.3.3     | The Interface Card of the GaN E-HEMT VSI-based Servo Drive               | 65 |

|   | 3.3.4     | The GaN E-HEMT VSI-based Servo Drive                                     | 65 |

|   | 3.3.5     | Load Tests of the GaN E-HEMT VSI-based Servo Drive                       | 66 |

|   | 3.3.      | 5.1 Efficiency Determination of the GaN E-HEMT VSI-<br>based Servo Drive | 66 |

|   | 3.3.      | 5.2 Thermal Analysis of the GaN E-HEMTs of the Servo Drive               | 72 |

|   | 3.3.6     | Conducted Emission Tests of the GaN E-HEMT VSI-based Servo Drive         | 75 |

|   | 3.4 Conc  | lusion                                                                   | 77 |

| 4 |           | CONNECTED GAN E-HEMT VSI-BASED SERVO DRIVES                              | 81 |

|   | 4.1 Intro | duction                                                                  | 81 |

|   | 4.2 Circu | lation Current Due to Asynchronous Carrier Signals                       | 83 |

|   | 4.2.1     | Region (I)                                                               | 86 |

|   | 4.2.2     | Region (II)                                                              | 88 |

|   | 4.2.3     | Region (III)                                                             | 88 |

|   | 4.2.4     | Region (IV)                                                              | 90 |

|   | 4.2.5     | Simulation Results                                                       | 92 |

|   | 4.3 Expe  | rimental Work                                                            | 94 |

|    | 4.3.1      | Effect of Clock Inconsistencies Between Individual Micro-<br>controllers  |

|----|------------|---------------------------------------------------------------------------|

|    | 4.3.2      | Comparison with Simulation Results                                        |

|    | 4.3.3      | Block Schema of the Parallel Operation                                    |

|    | 4.3.4      | Dynamic Performances of the Parallel Operation 100                        |

|    | 4.3.4      | 4.1 Startup Condition                                                     |

|    | 4.3.4      | 4.2 Step Torque Disturbance                                               |

|    | 4.3.4      | 4.3 Chirp Torque Disturbance                                              |

|    | 4.3.4      | 4.4 Step Speed Reference                                                  |

|    | 4.3.5      | Faulty Conditions of the Slaves                                           |

|    | 4.3.       | 5.1 Turning Off the Slave-#3 During Operation 103                         |

|    | 4.3.:      | 5.2 Opening the Output of Phase <i>A</i> of the Slave-#2 During Operation |

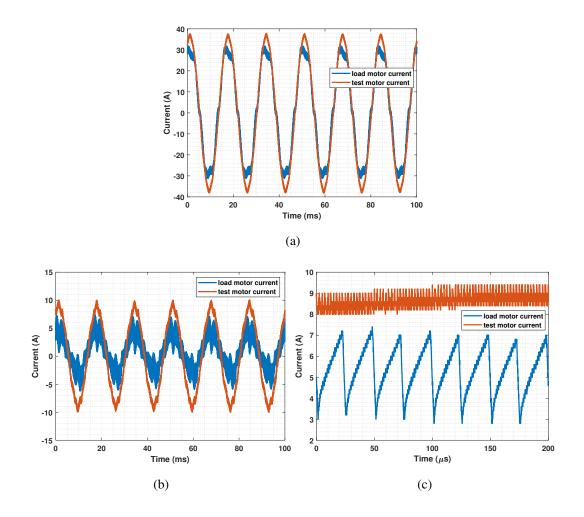

|    | 4.3.6      | Efficiency Comparison: Parallel vs. Single Operation 105                  |

|    | 4.3.7      | Current Ripple Comparison                                                 |

|    | 4.4 Chap   | ter Summary                                                               |

| 5  | CONCLUS    | IONS                                                                      |

|    | 5.1 A Sho  | ort Synopsis of the Thesis                                                |

|    | 5.2 Litera | ature Contributions                                                       |

|    | 5.3 Prosp  | pects for the Future                                                      |

| RI | EFERENCES  |                                                                           |

| AI | PPENDICES  |                                                                           |

| А  | PUBLICAT   | IONS ARISING FROM THE THESIS                                              |

| CURRICULUM VITAE |  | . 137 |

|------------------|--|-------|

|------------------|--|-------|

### LIST OF TABLES

### TABLES

| Table 2.1 F  | PMSM Parameters                                                                                                         | 21 |

|--------------|-------------------------------------------------------------------------------------------------------------------------|----|

|              | Phase Current Harmonic Distortions [%] at 10 Hz and 40 Hz Elec-         Reference Speed at No Load                      | 23 |

|              | Phase Current Harmonic Distortions [%] at 10 Hz and 40 Hz Elec-<br>Reference Speed at No Load with GaN E-HEMT based VSI | 38 |

| Table 2.4 H  | Parameters used in loss calculations                                                                                    | 44 |

| Table 2.5 I  | Power Losses of the Leg $A$ at some of the operating points $\ldots$                                                    | 46 |

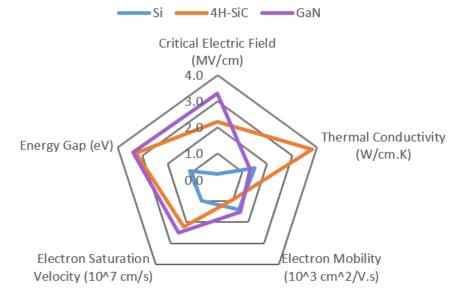

| Table 3.1 t  | test caption                                                                                                            | 54 |

| Table 3.2 H  | Features of GaN E-HEMT VSI based Servo Drive                                                                            | 60 |

| Table 3.3 A  | Available GaN E-HEMTs                                                                                                   | 62 |

| Table 3.4 H  | PMSM and Experimental Setup Parameters                                                                                  | 68 |

| Table 3.5 S  | Servo Drive Parameters                                                                                                  | 69 |

| Table 3.6 H  | Experimentally Efficiency Calculation Procedure                                                                         | 70 |

| Table 3.7 A  | Analytically Efficiency Calculation Procedure                                                                           | 71 |

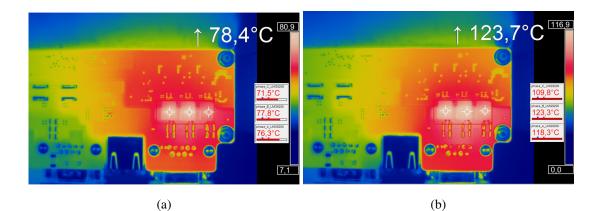

| Table 3.8 C  | Common Parameters for Thermal Experiment Tests                                                                          | 75 |

| Table 3.9    | Thermal Experiment Tests Parameters                                                                                     | 75 |

| Table 3.10 7 | Thermal Tests, $T_C$ of GaN E-HEMTs of the Servo Drive $\ldots$                                                         | 77 |

| Table 4.1 | Simulation Circuit Parameters                                 |

|-----------|---------------------------------------------------------------|

| Table 4.2 | Motor Drive and PMSM Parameters                               |

| Table 4.3 | Parameters of Experimental Setup for Efficiency Comparison of |

| Paral     | lel vs. Single Operation                                      |

| Table 4.4 | Efficiency Calculation of the Single Operation                |

| Table 4.5 | Efficiency Calculation of the Parallel Operation              |

| Table 5.1 | Experimental Parameters of the Studies in the Literature      |

### LIST OF FIGURES

### FIGURES

| Figure 1.      | 1 The block diagram of the nonlinearity problem                                                                            | 4  |

|----------------|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.      | 2 test caption                                                                                                             | 5  |

| Figure 1.      | .3 The simplified block diagram of two servo drives connected in arallel.                                                  | 6  |

| Figure 1.      | 4 test caption                                                                                                             | 7  |

| Figure 1.      | 5 test caption                                                                                                             | 8  |

| Figure 2.      | 1 Si MOSFET-based VSI PMSM drive block schema                                                                              | 15 |

| Figure 2.<br>V | 2 Gate signals and leg A output voltages of the SI MOSFET-based<br>/SI                                                     | 15 |

| Figure 2.      | 3 Voltage errors in the legs as a result of VSI nonlinearities                                                             | 18 |

| Figure 2.      | Voltage errors in $\alpha$ - $\beta$ reference frame as a result of VSI nonlin-<br>arities.                                | 19 |

| Figure 2.      | Voltage errors in $d$ - $q$ reference frame as a result of VSI nonlin-<br>arities.                                         | 19 |

| Figure 2.      | 6 Experimental setup with Si MOSFET-based VSI                                                                              | 21 |

| Figure 2.      | Phase current $i_a$ , $d$ - $q$ reference frame current $i_d$ and $i_q$ and their requency spectrums in open-loop control. | 22 |

| Figure | 2.8            | $i_d$ current and $u_d$ voltage, Si MOSFET-based VSI at $f_{sw} = 10$                                                                                                                                 |    |

|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|        | kHz t          | o 100 $kHz$                                                                                                                                                                                           | 24 |

| Figure |                | $u_d$ voltage versus $i_d$ current, Si MOSFET-based VSI at $f_{sw} = 10$<br>o 100 kHz                                                                                                                 | 25 |

| Figure | rent, a        | Closed-loop time domain response of $i_{dref}$ and measured $i_d$ curt<br>t $f_{sw} = 100 \ kHz$ , Si MOSFET-based VSI. (a) without any offset<br>Set at linear region (c) offset at nonlinear region | 26 |

| Figure | 2.11<br>100 ki | Frequency response of $i_{dref}$ and measured $i_d$ current, at $f_{sw} = Hz$ , at nonlinear and linear regions, Si MOSFET-based VSI                                                                  | 27 |

| Figure |                | $u_d$ voltage versus $i_d$ current, with varying motor shaft speed and 100 kHz, Si MOSFET-based VSI.                                                                                                  | 27 |

| Figure |                | Variation of the apparent resistance value along the nonlinear at $f_{sw} = 100 \ kHz$ .                                                                                                              | 29 |

| Figure |                | Current control open-loop at linear and nonlinear regions at 100 kHz                                                                                                                                  | 29 |

| Figure |                | The effect of the nonlinear region on the position control loop at $100 \ kHz$                                                                                                                        | 30 |

| Figure |                | The sections of the $i_d$ current and $u_d$ voltage graph at $f_{sw} = 20$                                                                                                                            | 31 |

| Figure |                | $u_d$ voltage versus $i_d$ current graph with fitted curves at $f_{sw} = 20$                                                                                                                          | 31 |

| Figure |                | The 100 $Hz i_d$ reference and the measured $i_d$ values with and ut the nonlinearity compensation, Si MOSFET-based VSI                                                                               | 32 |

| Figure | $i_d$ in t     | Chirp signal from 10 $Hz$ to 250 $Hz$ $i_d$ reference and measured<br>ime domain, Si MOSFET-based VSI. (a) without compensation<br>th compensation                                                    | 33 |

|        |                |                                                                                                                                                                                                       |    |

| Figure | 2.20         | Chirp signal from $10 Hz$ to $250 Hz i_d$ reference and measured                                                                                                                                                 |    |

|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|        | $i_d$ with   | and without compensation in frequency domain, bode diagram,                                                                                                                                                      |    |

|        | Si MO        | SFET-based VSI                                                                                                                                                                                                   | 34 |

| Figure | 2.21         | Experimental setup for GaN E-HEMT based VSI                                                                                                                                                                      | 35 |

| Figure |              | $u_d$ and $i_d$ with time, GaN E-HEMT based VSI at $f_{sw} = 10 \ kHz$<br>$kHz$ , $t_{dead}$ 20 ns and 100 ns                                                                                                    | 36 |

| Figure | $t_{dead} =$ | $u_d$ voltage versus $i_d$ current, at $f_{sw} = 10 \ kHz$ to $100 \ kHz$ ,<br>= 20 ns and 100 ns, GaN E-HEMT based VSI and Si MOSFET-<br>VSI at $f_{sw} = 100 \ kHz$ and $t_{dead} = 1\mu s.$                   | 37 |

| Figure | $i_d$ , at j | Chirp signal from 10 $Hz$ to 250 $Hz i_d$ reference and measured<br>$f_{sw} = 100 \ kHz$ in time domain, GaN E-HEMT based VSI. (a)<br>0 $ns$ dead time (b) with 100 $ns$ dead time $\ldots \ldots \ldots \ldots$ | 38 |

| Figure | $f_{sw} =$   | Frequency response of the $i_{dref}$ and measured $i_d$ current, at 100 kHz, with 20 ns and 100 ns dead time, GaN E-HEMT VSI and Si MOSFET-based VSI at nonlinear region.                                        | 39 |

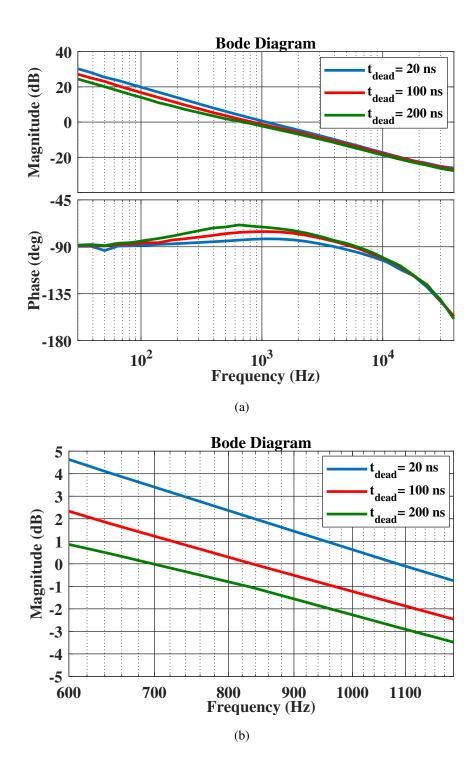

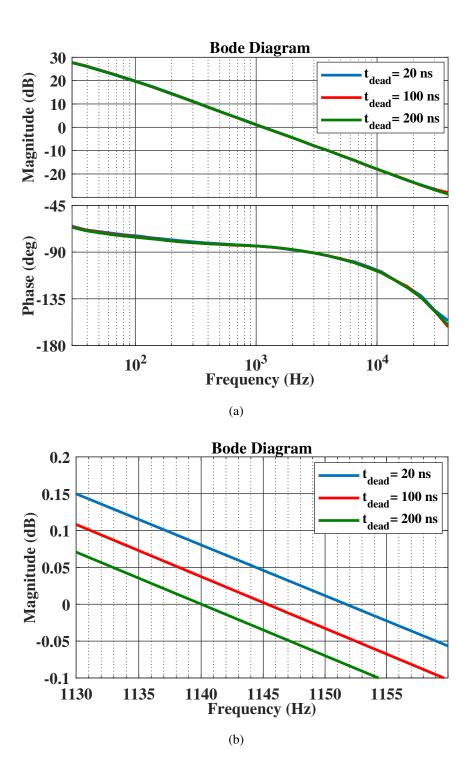

| Figure | rent co      | The open-loop frequency response characteristics of the $i_d$ cur-<br>ontrol loop at $f_{sw} = 100 \ kHz$ , GaN E-HEMT based VSI. (a) gain<br>ase (b) gain zoomed at zero-crossing dB                            | 41 |

| Figure | rent co      | The open-loop frequency response characteristics of the $i_q$ cur-<br>ontrol loop at $f_{sw} = 100 \ kHz$ , GaN E-HEMT based VSI. (a) gain<br>ase (b) gain zoomed at zero crossing dB                            | 42 |

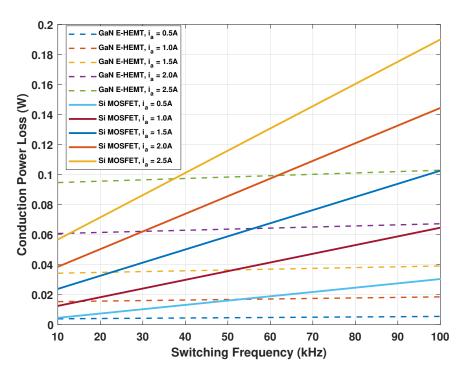

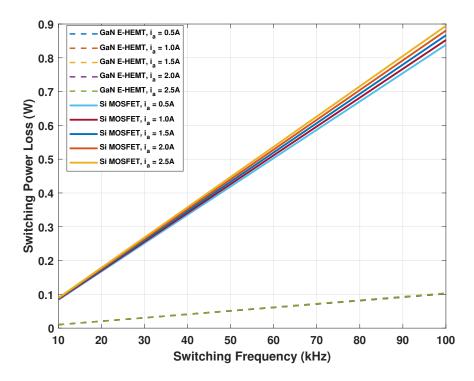

| Figure |              | Conduction power losses of the leg A for Si MOSFET and GaN                                                                                                                                                       | 44 |

| Figure |              | Switching power losses of the leg A for Si MOSFET and GaN                                                                                                                                                        | 45 |

| Figure | 2.30         | Total power losses of the leg $A$ for Si MOSFET and GaN E-HEMT.                                                                                                                                                  | 45 |

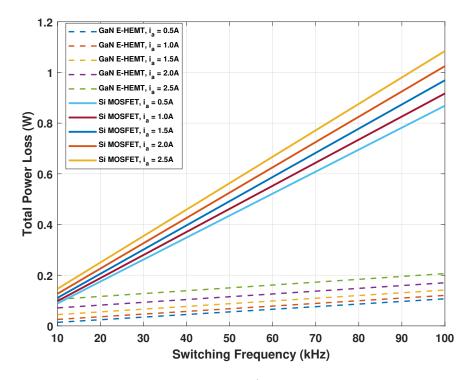

| Figure 3.1  | Cascode GaN HEMT, low voltage Si MOSFET in series with                       |    |

|-------------|------------------------------------------------------------------------------|----|

| deplet      | ion mode GaN HEMT (D-HEMT)                                                   | 51 |

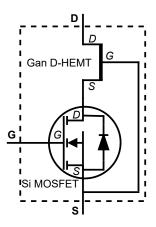

| Figure 3.2  | The true normally OFF GaN HEMT by p-GaN gate method (a)                      |    |

| zero o      | r negative gate bias to turn-off (b) positive gate bias to turn-on $\ . \ .$ | 53 |

| Figure 3.3  | Material Properties of Si, SiC and GaN                                       | 54 |

| Figure 3.4  | Dimensions of the servo drives:(a) The Si MOSFET VSI-based                   |    |

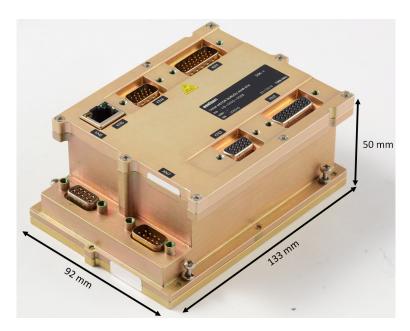

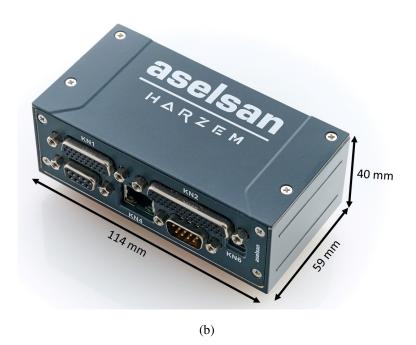

| servo       | drive (b) The GaN E-HEMT VSI-based servo drive                               | 59 |

| Figure 3.5  | The basic functions of the cards of the GaN E-HEMT VSI-based                 |    |

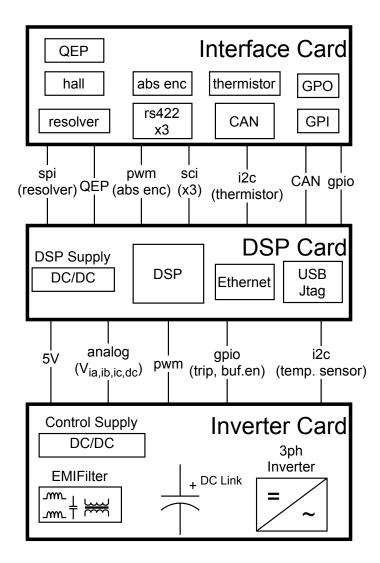

| servo       | drive and the signals between them                                           | 61 |

| Figure 3.6  | The block diagram of the inverter card and the signals between               |    |

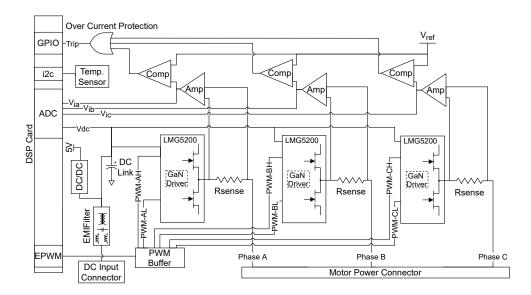

| the inv     | verter and DSP cards of the GaN E-HEMT VSI-based servo drive.                | 63 |

| Figure 3.7  | The inverter card of the GaN E-HEMT VSI-based servo drive                    |    |

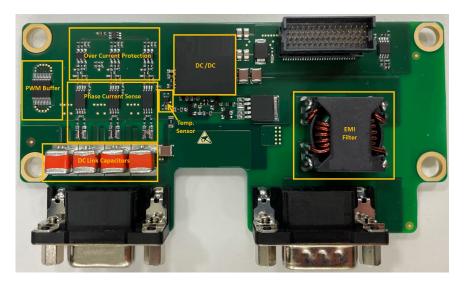

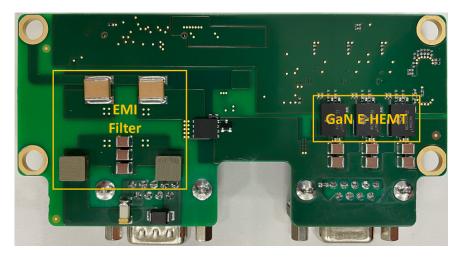

| (a) top     | o side (b) bottom side                                                       | 64 |

| Figure 3.8  | The DSP card of the GaN E-HEMT VSI-based servo drive                         | 65 |

| Figure 3.9  | The interface card of the GaN E-HEMT VSI-based Servo Drive .                 | 66 |

| Figure 3.10 | Inside view of the GaN E-HEMT VSI-based servo drive (a)                      |    |

| Front       | view (b) Back view                                                           | 67 |

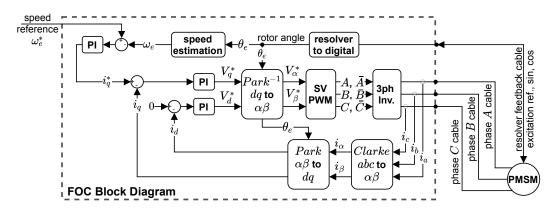

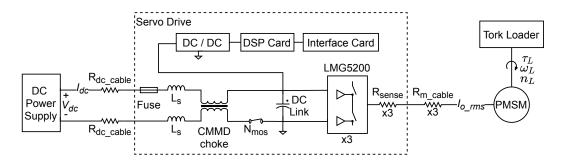

| Figure 3.11 | The block schema of the FOC to control the PMSM                              | 68 |

| Figure 3.12 | The block diagram of the test setup for efficiency evaluation of             |    |

| the Ga      | aN E-HEMT VSI-based servo drive.                                             | 68 |

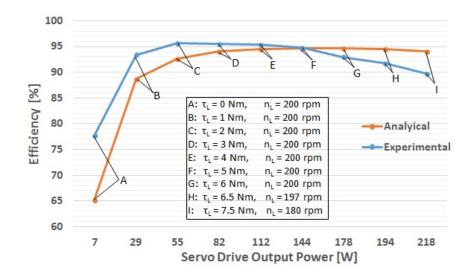

| Figure 3.13 | mycaption                                                                    | 70 |

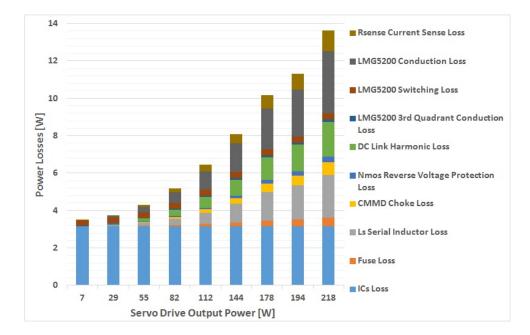

| Figure 3.14 | The loss distributions of the parts of the GaN E-HEMT VSI-                   |    |

| based       | servo drive at $24V$                                                         | 72 |

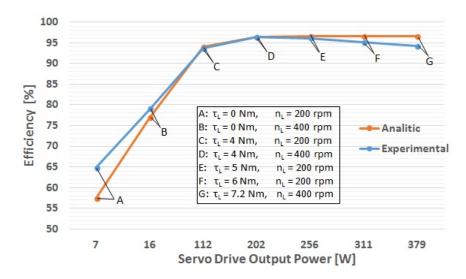

| Figure |          | The efficiency estimation of the GaN E-HEMT VSI-based servo at $48V$ . The blue line is the efficiency based on the experimental |    |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------|----|

|        |          | , and the orange line is the efficiency based on the analytical ations.                                                          | 73 |

|        | Calcula  |                                                                                                                                  | 15 |

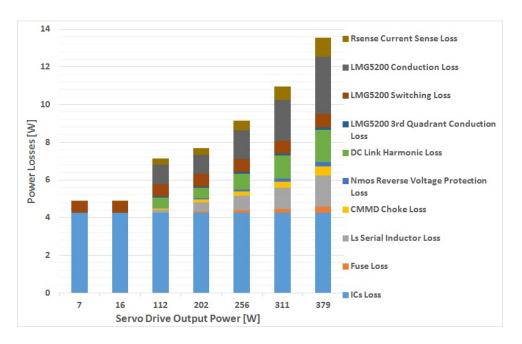

| Figure |          | The loss distributions of the parts of the GaN E-HEMT VSI-                                                                       |    |

|        | based s  | servo drive at $48V$                                                                                                             | 73 |

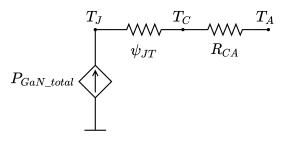

| Figure | 3.17     | The simplified equivalent thermal circuit to calculate the junc-                                                                 |    |

|        | tion ter | mperature of the GaN E-HEMTs                                                                                                     | 74 |

| Figure | 3.18     | Thermal images at steady state of the GaN E-HEMTs of the                                                                         |    |

|        | servo c  | drive (a) test-#1 (b) test-#2 (c) test-#3 (d) test-#4                                                                            | 76 |

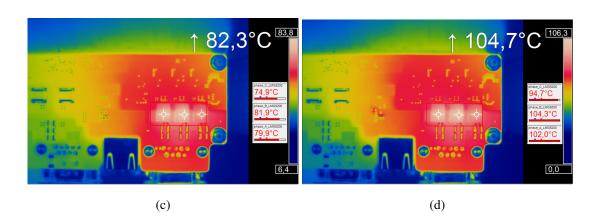

| Figure | 3.19     | The equivalent EMI filter circuit of the power input of the GaN                                                                  |    |

|        | E-HEN    | MT VSI-based servo drive                                                                                                         | 78 |

| Figure | 3.20     | The conducted emission test setup for the GaN E-HEMT VSI-                                                                        |    |

|        | based s  | servo drive                                                                                                                      | 78 |

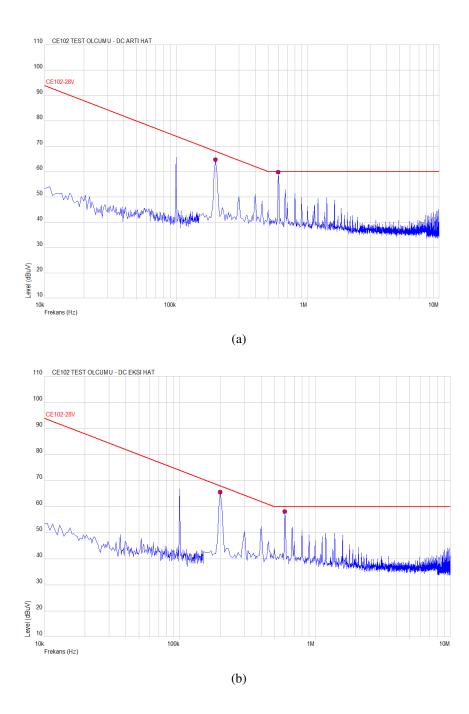

| Figure | 3.21     | CE102 test results of the GaN E-HEMT VSI-based servo drive                                                                       |    |

|        | (a) pov  | ver lead (b) return                                                                                                              | 79 |

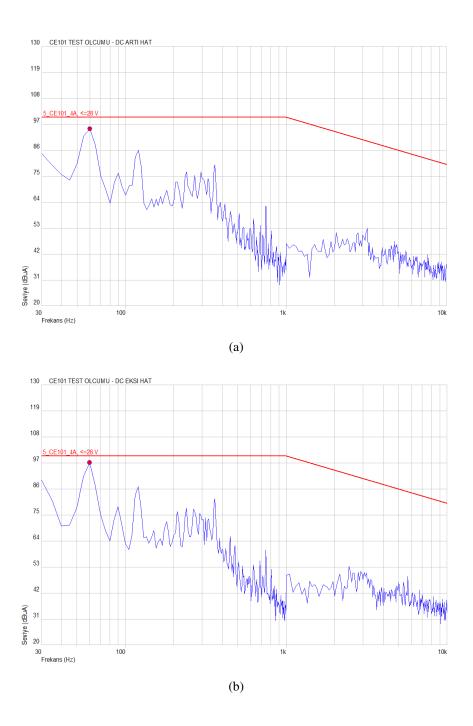

| Figure | 3.22     | CE101 test results of the GaN E-HEMT VSI-based servo drive                                                                       |    |

| C      | (a) pov  |                                                                                                                                  | 80 |

|        |          |                                                                                                                                  |    |

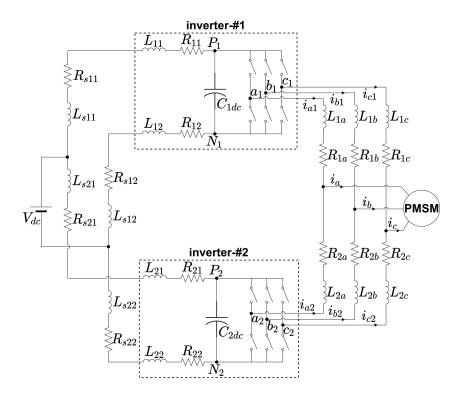

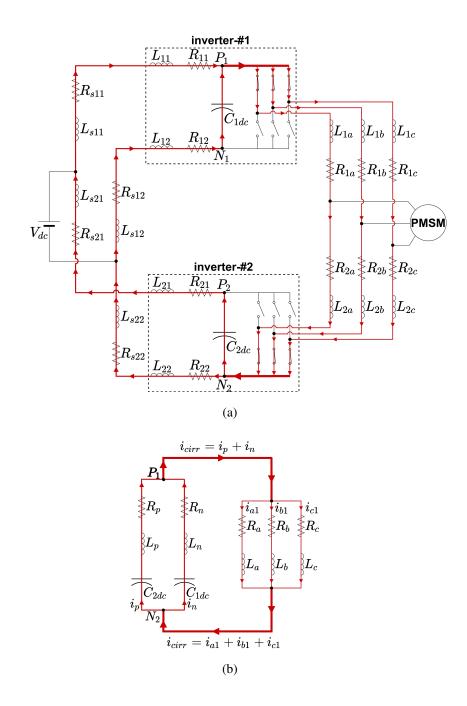

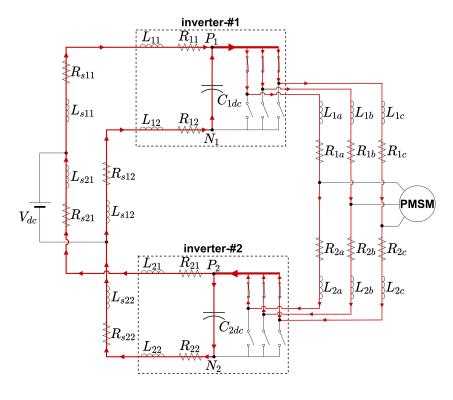

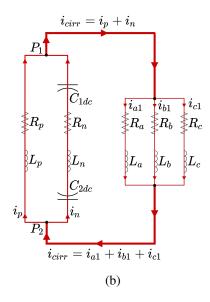

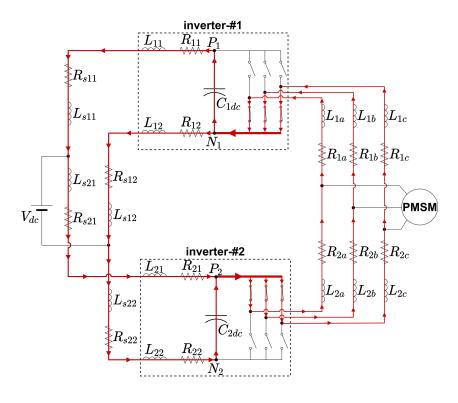

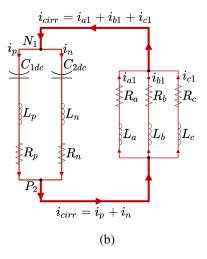

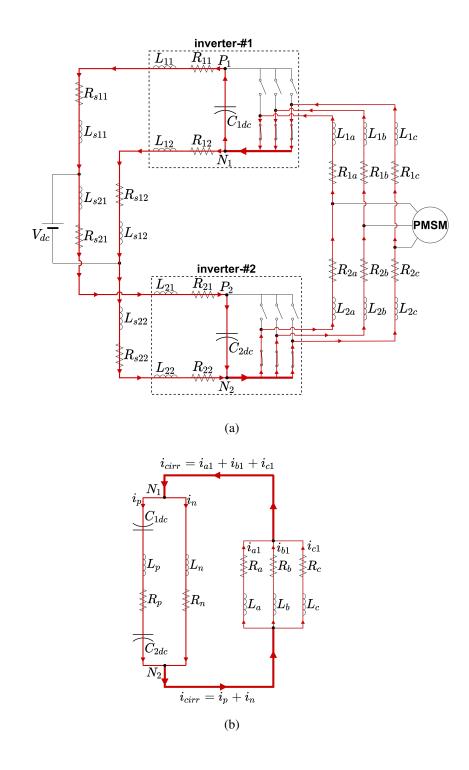

| Figure | 4.1      | Circuit diagram of the parallel-connected inverters and PMSM                                                                     | 84 |

| Figure | 4.2      | The phase angle difference between carrier signals of the parallel-                                                              |    |

|        | connec   | cted inverters is $90^{\circ}$ .                                                                                                 | 85 |

| Figure | 4.3      | (a) The circulation current path when the phase angle difference                                                                 |    |

|        | betwee   | en carrier signals is $90^\circ$ , region (I) (b) Equivalent circuit of the                                                      |    |

|        | circula  | tion current path                                                                                                                | 87 |

| Figure | 4.4      | (a) The circulation current path when the phase angle difference                                                                 |    |

|        | betwee   | en carrier signals is $90^{\circ}$ , region (II) (b) Equivalent circuit of the                                                   |    |

|        | circula  | tion current path                                                                                                                | 89 |

| Figure | (a) The circulation current path when the phase angle difference                      | e       |

|--------|---------------------------------------------------------------------------------------|---------|

|        | between carrier signals is $90^\circ$ , region (III) (b) Equivalent circuit of the    | 9       |

|        | circulation current path                                                              | 90      |

| Figure | .6 (a) The circulation current path when the phase angle difference                   | e       |

|        | between carrier signals is $90^\circ$ , region (IV) (b) Equivalent circuit of the     | e       |

|        | circulation current path                                                              | 91      |

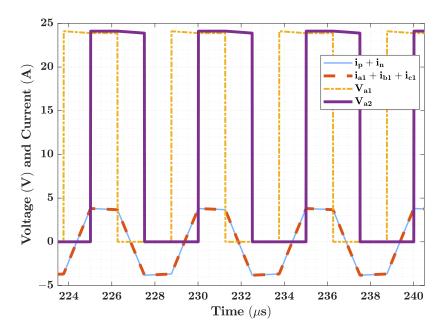

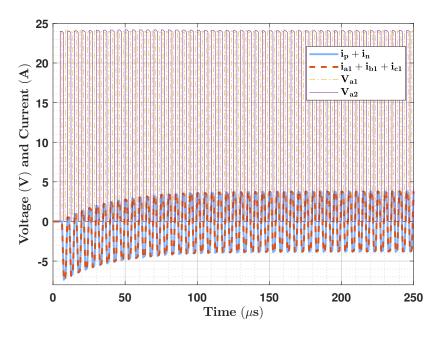

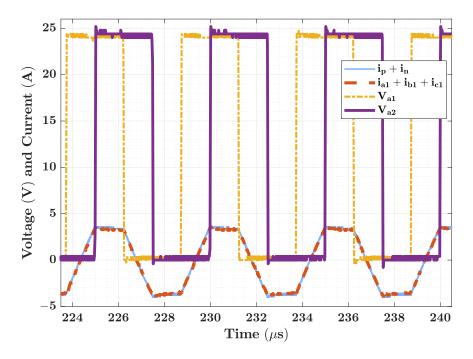

| Figure | .7 Simulation results when the phase angle difference between car-                    | -       |

|        | ier signals is $90^{\circ}$ and the switching frequency is $200 \ kHz$ at steady-sta  | ate. 92 |

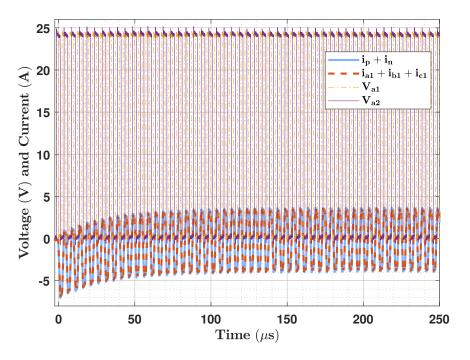

| Figure | .8 Simulation results during startup with 90° phase angle difference                  | e       |

|        | between carrier signals and the switching frequency is $200 \ kHz$                    | 94      |

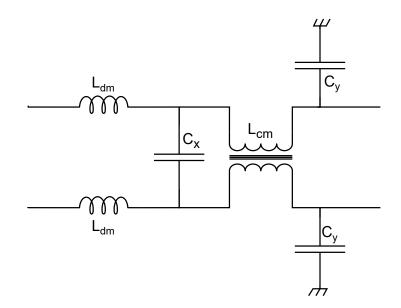

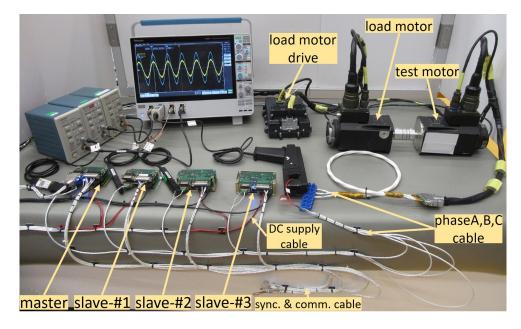

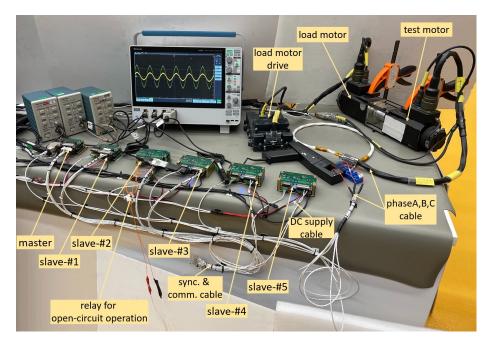

| Figure | .9 Experimental setup with four parallel-connected GaN E-HEMT                         | [       |

|        | VSI-based servo drives                                                                | 95      |

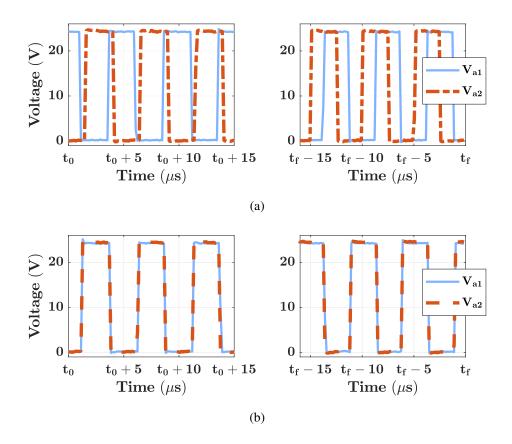

| Figure | .10 $V_{a1}$ and $V_{a2}$ waveforms (a) without synchronization (b) with syn-         | -       |

|        | chronization where $t_0 = 0$ and $t_f = 200000 \ \mu s.$                              | 96      |

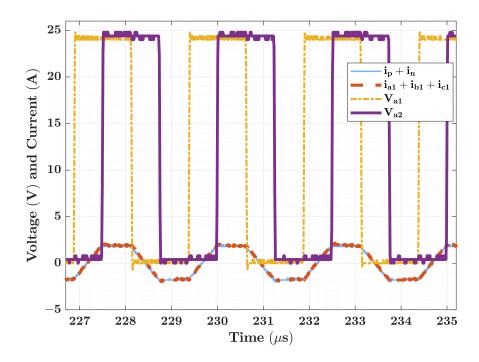

| Figure | E.11 Experimental results when the phase angle difference between                     | 1       |

|        | carrier signals is $90^{\circ}$ and the switching frequency is $200 \ kHz$ at steady- | -       |

|        | state                                                                                 | 98      |

| Figure | .12 Experimental results during startup with 90° phase angle differ-                  | -       |

|        | ence between carrier signals and the switching frequency is $200 \ kHz$ .             | . 98    |

| Figure | Experimental results when the phase angle difference between                          | ı       |

|        | carrier signals is $90^{\circ}$ and the switching frequency is $400 \ kHz$ at steady- | -       |

|        | state                                                                                 | 99      |

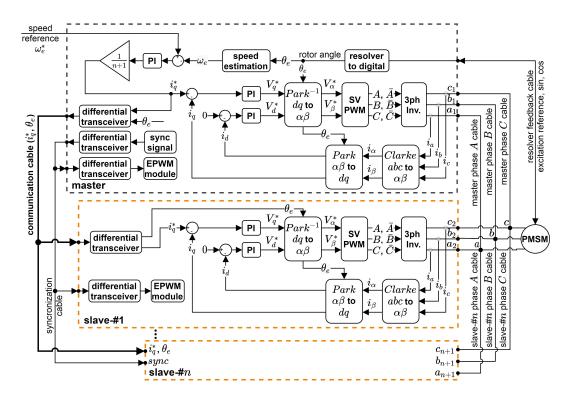

| Figure | .14 The overall block schema of the parallel operation of servo driv                  | ves.100 |

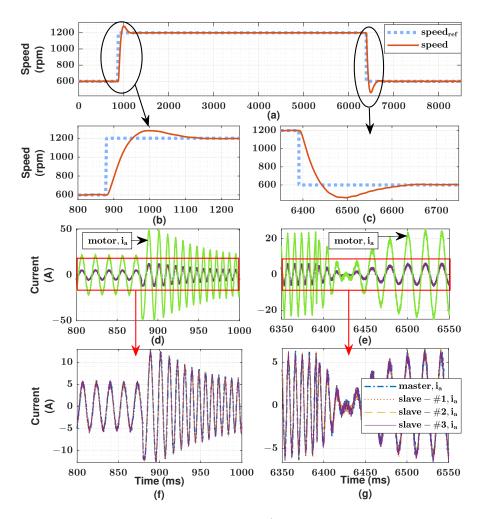

| Figure | .15 Speed of the PMSM and phase A currents of servo drives and                        | 1       |

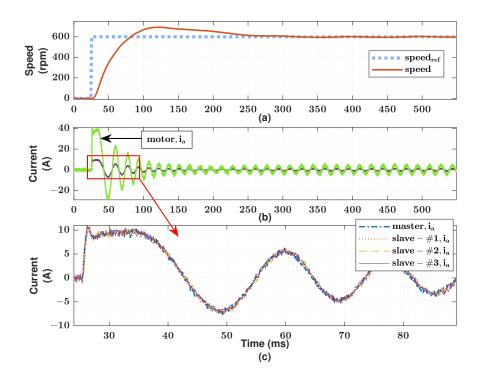

|        | PMSM at startup                                                                       | 101     |

| Figure | .16 Speed of the PMSM and phase A currents of servo drives and                        | 1       |

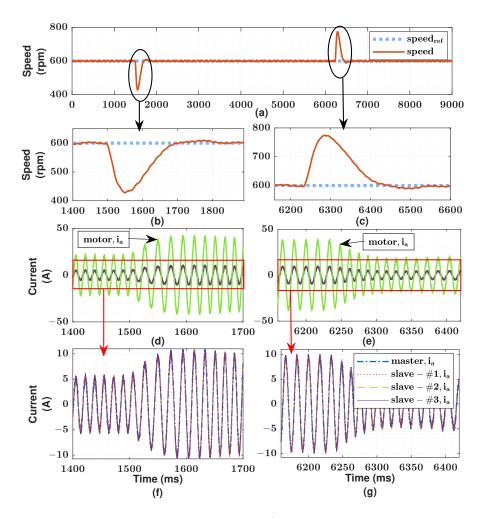

|        | PMSM with step torque disturbance                                                     | 102     |

| Figure     | 4.17                      | Speed of the PMSM and $i_q$ currents of servo drives with chirp                              |

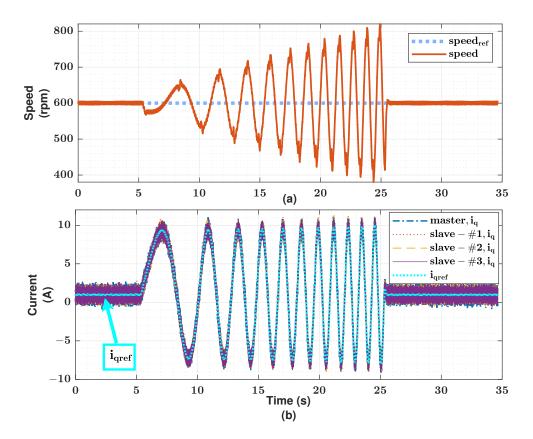

|------------|---------------------------|----------------------------------------------------------------------------------------------|

|            | torque                    | disturbance $(0.1Hz \text{ to } 1.0Hz \text{ at full load})$                                 |

| Figure     | 4.18                      | Speed of the PMSM and phase A currents of servo drives and                                   |

|            | PMSM                      | I with step speed reference variation                                                        |

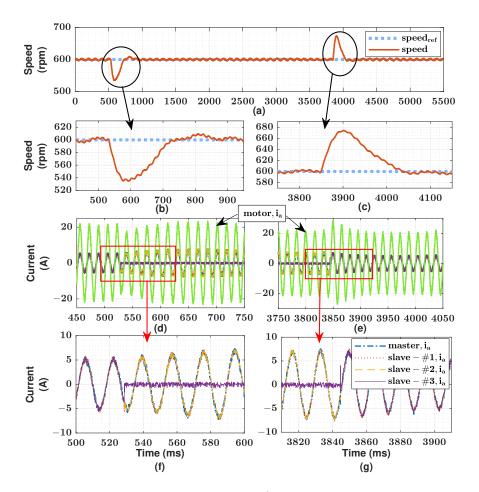

| Figure     | 4.19                      | Speed of the PMSM and phase A currents of servo drives and                                   |

|            | PMSM                      | I, slave-#3 goes to faulty and back to a healthy condition by man-                           |

|            | ually d                   | luring operation                                                                             |

| Figure     | 4.20                      | Experimental setup with six parallel-connected GaN E-HEMT                                    |

|            | VSI-ba                    | ased servo drives                                                                            |

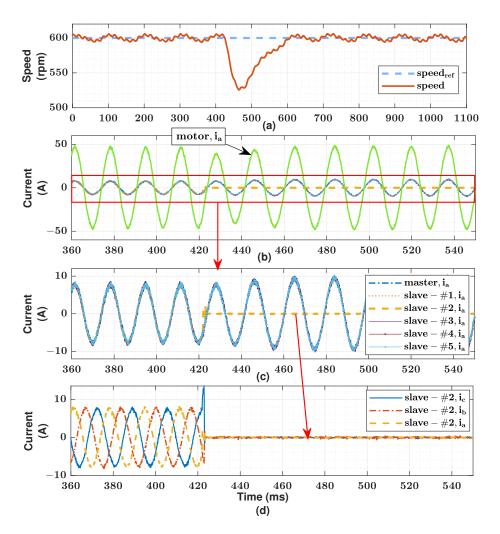

| Figure     | 4.21                      | Speed of the PMSM, phase A currents of servo drives and PMSM,                                |

|            | and ph                    | has currents of the slave-#2, phase $A$ of the slave-#2 is open-                             |

|            | circuite                  | ed by a relay during operation                                                               |

| <b>D</b> ' |                           |                                                                                              |

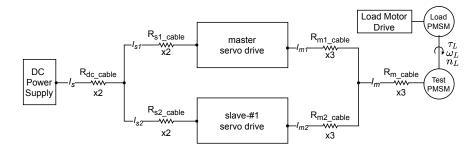

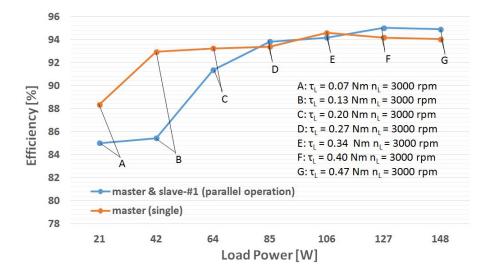

| Figure     | 4.22                      | The block diagram of the test setup for efficiency comparison of                             |

| Figure     |                           | The block diagram of the test setup for efficiency comparison of rallel and single operation |

| Figure     | the par                   |                                                                                              |

| U          | the par<br>4.23           | callel and single operation                                                                  |

| Figure     | the par<br>4.23<br>and pa | The results of the efficiency calculations of the single operation                           |

### LIST OF ABBREVIATIONS

| Two-dimensional Electron Gas                       |

|----------------------------------------------------|

| Alternating Current                                |

| Adaptive Linear Neuron                             |

| Aluminium Gallium Nitride                          |

| American Wire Gauge                                |

| Controller Area Network                            |

| Coupled Inductor                                   |

| Common Mode Inductor                               |

| Common Mode                                        |

| Direct Current                                     |

| Direct Current Leakage                             |

| Digital signal Processor                           |

| Depletion-Mode High Electron Mobility Transistor   |

| Enhanced Capture                                   |

| Enhancement-Mode High Electron Mobility Transistor |

| Electromagnetic Interference                       |

| Equivalent Series Resistance                       |

| Finite Element Analysis                            |

| Field Oriented Control                             |

| Figure of Merit                                    |

| Field Programmable Gate Array                      |

| Gallium Nitride                                    |

| Half-Bridge                                        |

| High-Frequency Circulating Current                 |

|                                                    |

| IC     | Integrated Circuit                                    |

|--------|-------------------------------------------------------|

| IGBT   | Insulated-Gate Bipolar Transistor                     |

| JTAG   | Joint Test Action Group                               |

| LiDAR  | Light Detection and Ranging                           |

| LMS    | Least Mean Square                                     |

| MISFET | Metal-Insulator-Semiconductor Field-Effect Transistor |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor     |

| PCB    | Printed Circuit Board                                 |

| PI     | Proportional Integral                                 |

| PMSM   | Permanent Magnet Synchronous Motor                    |

| PWM    | Pulse Width Modulation                                |

| RF     | Radio Frequency                                       |

| RMS    | Root Mean Square                                      |

| Si     | Silicon                                               |

| SiC    | Silicon Carbide                                       |

| SPWM   | Sinusoidal Pulse Width Modulation                     |

| SVPWM  | Space Vector Pulse Width Modulation                   |

| TVS    | Transient Voltage Suppression                         |

| USB    | Universal Serial Bus                                  |

| VSI    | Voltage Source Inverter                               |

| WBG    | Wide-Bandgap                                          |

| ZSCC   | Zero-Sequence Circulating Current                     |

| ZSV    | Zero-Sequence Voltage                                 |

### LIST OF SYMBOLS

| heta | Rotor Angle   |

|------|---------------|

| C    | Capacitance   |

| i, I | Current       |

| f    | Frequency     |

| L    | Inductance    |

| Q    | Charge        |

| Р    | Power         |

| R    | Resistance    |

| u, V | Voltage       |

| ω    | Angular Speed |

# Subscripts

| α       | Alpha Reference Frame             |

|---------|-----------------------------------|

| $\beta$ | Beta Reference Frame              |

| a       | Leg A Output of the Inverter      |

| b       | Leg $B$ Output of the Inverter    |

| С       | Leg $C$ Output of the Inverter    |

| d       | Quadrature D-axis Reference Frame |

| ds      | Drain to Source                   |

| e       | Electrical                        |

| g       | Gate                              |

| gd      | Gate to Drain                     |

| gs      | Gate to Source                    |

| q       | Quadrature Q-axis Reference Frame |

|         |                                   |

sd Source to Drain

sw Switching

# Superscripts

\* Reference

#### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1** Motivation and Scope of the Thesis

Permanent magnet synchronous motors (PMSMs) with a coreless structure that is wound on itself rather than on iron, offer benefits such as zero cogging, linear torque characteristics, and low inertia. These features make them a good candidate for applications such as gimbals, aerospace, robotics, unmanned systems, optic stabilizers, etc. where high-precision position control is required [1]. On the other hand, these motors have low inductance and low electrical time constant, which require a high switching frequency to reduce current ripple [2] and to obtain a high current control bandwidth.

For a specific target tracking radar application, due to target maneuvers and the beamwidth of the antenna, the system requirements are specified as a  $0.02^{\circ}$  tracking error for 5 Hz and 5° sinusoidal position reference. The following equations can be used to calculate the required bandwidth ( $f_{bw\_pos}$ ) of the position controller of the servo drive which feeds a PMSM coupled to an antenna.

$$\theta = A \sin (wt)$$

$$\dot{\theta} = -Aw \cos (wt)$$

$$\ddot{\theta} = -Aw^{2} \sin (wt)$$

$$\tau = J\ddot{\theta}$$

$$k_{p} = \tau \Delta \theta$$

$$f_{bw\_pos} = \frac{1}{2\pi} \sqrt{\frac{k_{p}}{J}}$$

(1.1)

where  $A = 5\pi/180 \ rad$ ,  $w = 2\pi5 \ rad/s$ , the inertia of the antenna  $J = 0.005 \ kgm^2$ .

From these equations, the required torque  $\tau = 0.43 Nm$ , the required position controller gain  $k_p = 1233.7 Nm/rad$  and the required position controller bandwidth  $f_{bw\_pos} = 79.06 Hz$  are calculated. To be on the safe side, the target position controller bandwidth is taken as 100 Hz. As a general rule of thumb, for a cascade control scheme, the bandwidth of the inner loops should be about ten times higher than the outer loop. So, following this rule of thumb, the required speed and current controller bandwidth are approximately 1 kHz and 10 kHz, respectively. In the same manner, the target switching frequency of the servo drive is set to 100 kHz during the thesis.

Two types of inverters, voltage source inverters (VSIs) and current source inverters (CSIs), are considered for the servo drive. VSIs have DC-link capacitors to achieve a constant voltage at the outputs. On the other hand, CSIs have DC-link inductors to deliver a constant current to the loads. The power switches of the VSIs should have bidirectional current conduction capability and block forward voltage [3]. Hence, commercial power switches such as Si MOSFETs and GaN E-HEMTs are suitable for VSIs. The current conduction of the power switches in CSIs is unidirectional, but the power switches should block reverse polarity voltage as well. Thyristors meet the v-i requirements of CSIs, but they are mainly used for medium-high voltage and power applications [4]. The power switches stated above should be used either back to back connected, which introduces complexity to the gate driver, or in series with a diode. In both cases, CSIs need six additional power switches, which increases the conduction losses and also the size of the inverter. The DC-link inductor of the CSIs helps to limit the current when the motor phases are short-circuited, but it negatively affects the dynamic response of the system [5]. With the help of output filter capacitors, CSIs have nearly sinusoidal voltages at the outputs. This is an advantage for the EMI problem and also reduces over-voltage problems on the terminals of the motor compared with the VSI case [6]. However, since the servo drive is supplied from a low voltage battery, typically 24V, in the target tracking radar application, there will not be such a voltage at the terminals of the motor to cause the insulation to wear off, even in the case of VSI. Based on the comparisons above, in the thesis, VSI is preferred for the servo drive due to its lower size and higher dynamic response, and it is more appropriate for low-voltage and low-power applications.

In the application, the target switching frequency of the servo drive was set to  $100 \ kHz$ . But, as the switching frequency increases, the effects of the time-related terms in the nonlinearity in VSIs also increase. The key causes of output voltage distortions in VSIs are nonlinearities such as

- dead time,

- switching time,

- delay time,

- voltage drops on the power switches,

- parasitic capacitances.

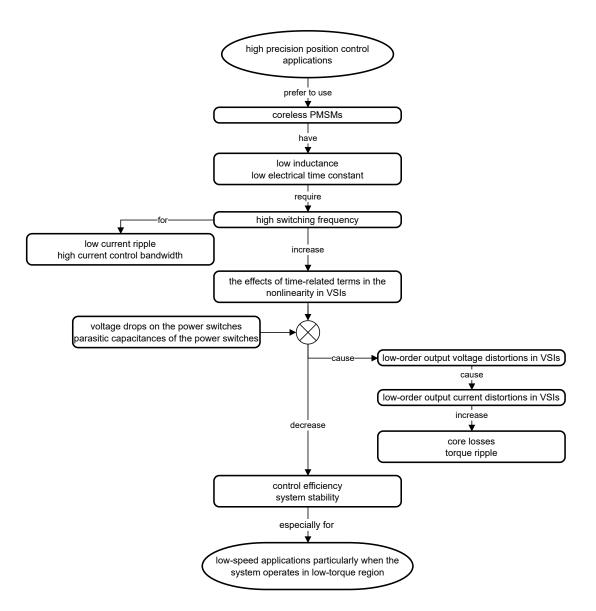

Low-order harmonics in the output current are caused by these distortions, which raise core losses and cause torque ripples [7–10]. Due to the nonlinearities in VSI, control efficiency and system stability degrade significantly in low-speed applications with low-inductance motors, particularly when the system operates in the low-torque region. In Fig. 1.1, the problem is also depicted as a block diagram.

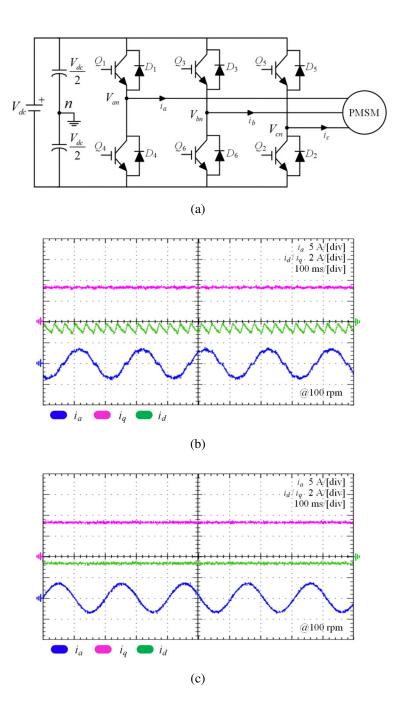

Fig. 1.2a shows an IGBT-based VSI driving a PMSM and the impact of the dead time, which is one of the nonlinearity factors of the VSIs, on the phase current and the quadrature currents is shown in Fig. 1.2b ([11]). The dead time is compensated by a least-mean-square algorithm ([11]) and the compensation results are given in Fig. 1.2c.

The effects of these nonlinearities on the phase current and current control of the Si MOSFET-based VSI are studied in this work using a coreless PMSM. The influence of the nonlinearities on the current control bandwidth is investigated. This effect should be considered before tuning linear controllers to achieve high-bandwidth current control in zero-crossing regions. In this thesis, a GaN E-HEMT-based VSI is suggested as a solution to this issue. Following that, advancements in the current control mechanism are illustrated by analyzing experimental findings obtained with GaN E-HEMT and Si MOSFET-based VSIs. It is shown that GaN E-HEMT-based VSI is a better option for applications requiring high bandwidth control.

Figure 1.1: The block diagram of the nonlinearity problem.

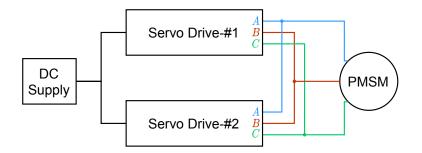

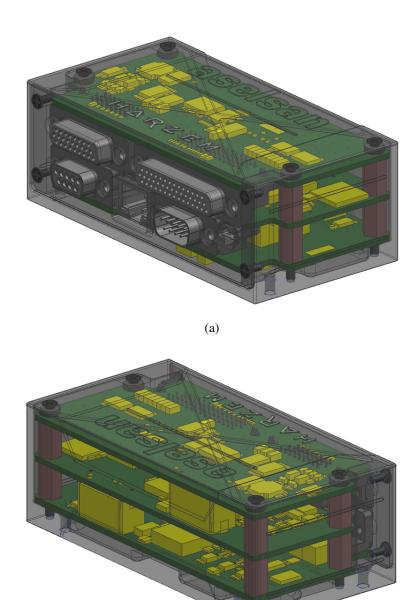

Considering the results of this work, a GaN E-HEMT VSI-based servo drive is designed to replace its Si MOSFET VSI-based counterpart. The size of the designed servo drive is about half of the previous one. This and the fast switching capability of the GaN E-HEMT makes it possible to use two parallel servo drives instead of one to increase redundancy, as shown in Fig. 1.3.

Using parallel-connected servo drives has many benefits [12], including increased torque (hence power output) capacity, reliability, redundancy, and modularity. Smaller variations in the system clocks of the individual microcontrollers, asynchronous PWM carrier signals, and hardware differences, on the other hand, will cause the output

Figure 1.2: (a) IGBT-based VSI to drive a PMSM. (b) Phase A current  $(i_a)$  and quadrature axis currents  $(i_d, i_q)$  without dead time compensation (c) with dead time compensation (Figures are taken from: [11])

voltages of the parallel modules to be non-identical, resulting in circulating currents between inverters [13], [14]. These circulating currents restrict parallel operation, add extra power dissipation, disrupt power transfer, and reduce control efficiency [15–17].

Figure 1.3: The simplified block diagram of two servo drives connected in parallel.

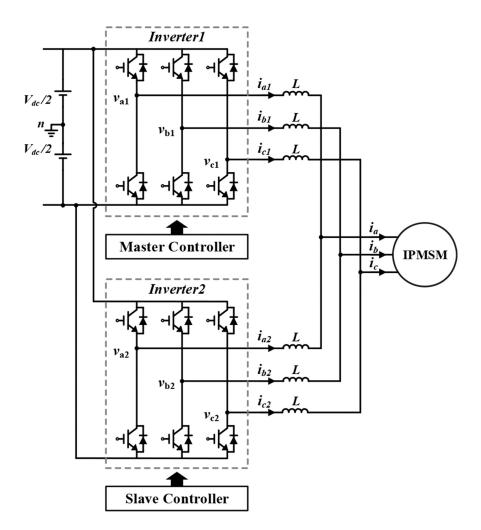

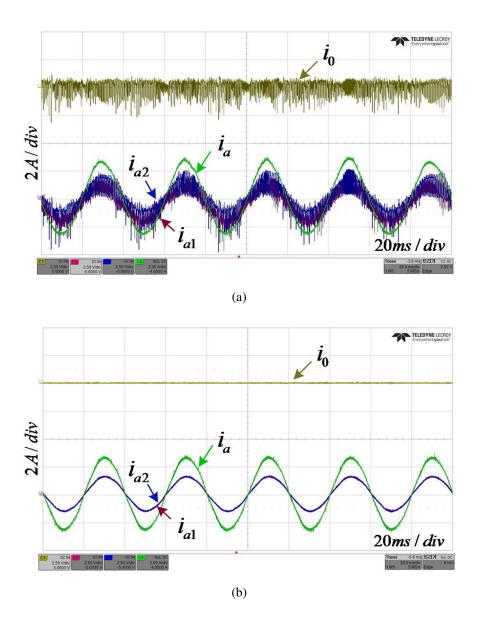

To better visualize, the structure of the two parallel-connected inverters is shown in Fig. 1.4 ([18]). Fig. 1.5a ([18]) depicts the circulating current between inverters caused by asynchronous PWM carriers. The circulating current is decreased using a high-frequency voltage compensation technique, as seen in Fig. 1.5b ([18]).

Separated DC supplies, extra inductors at the outputs, PWM techniques, changed control approaches, and other strategies have been suggested in the literature to minimize circulating currents. In this study, a fault-tolerant parallel-connected GaN E-HEMT VSI-based servo drive system, which removes the requirement for extra inductors and separate DC supplies while allowing the use of a conventional PI current control and a standard SVPWM method is presented. By synchronizing the carrier signals, the circulating current generated by the phase mismatch between carrier signals of the parallel-connected inverters is removed. By increasing the switching frequency without adding extra inductors to the output of the inverters, the circulating current caused by inherent hardware variations is reduced. Up to six servo drives are connected in parallel and tested under various situations using a 24V PMSM to investigate the performance of the proposed approach. The results demonstrate that parallel operation not only enhances the system's torque capacity but also its modularity, flexibility, reliability, and redundancy.

#### **1.2** The Outline of the Thesis

Chapter 2 presents the background information on the nonlinear components in the Si MOSFET-based VSI-fed PMSM drive. Next, the effect of changing the switching frequency on nonlinearities is investigated using an  $i_d$  current controller. The impact

Figure 1.4: The structure of the two parallel-connected inverters (Figure is taken from: [18]).

of the change in apparent resistance along the nonlinear region on the stability of cascaded control loops is studied. The WBG GaN E-HEMT based VSI is used to analyze the influence of switching frequency and dead time on nonlinearity. For the GaN E-HEMT based VSI-fed PMSM drive with various dead time values, the bandwidth measurements of the  $i_d$  and  $i_q$  control loops are provided. Finally, the power losses and costs of GaN E-HEMTs and Si MOSFETs are determined and compared with an application.

In Chapter 3, first, a basic overview of GaN E-HEMTs is provided. The significance of the layout as well as the problems of high dV/dt and high switching frequency are highlighted. Then, some details on a three-phase, two-level GaN E-HEMT VSI-based

Figure 1.5: Phase A currents  $(i_{a1}, i_{a2})$  of each inverter and the high-frequency circulating current  $(i_0)$  (a) without compensation (b) with compensation (Figures are taken from: [18])

servo drive design are provided. The servo drive's card compositions and functionalities are discussed, and finally, the servo drive's load and emission tests are demonstrated.

In Chapter 4, the circulating current path produced by asynchronous carrier signals is examined case by case, and the circulating current simulation outputs are discussed. Following that, the problem of clock differences across separate microcontrollers is shown, and a solution is provided. The suggested parallel servo drive system's functioning is explained, and finally, the results of dynamic performances under various situations are demonstrated.

In Chapter 5, the conclusion and recommendations for future work are provided.

#### **CHAPTER 2**

#### NONLINEARITIES FOR SI MOSFET AND GAN E-HEMT BASED VSIS

#### 2.1 Introduction

In industrial applications, PWM VSIs are commonly used to drive PMSMs. The nonlinearites in VSI create low-order output voltage distortions. The effect of these distortions on the output voltage depends on the switching frequency, modulation index, and output frequency. These voltage distortions cause low-order harmonic components in the inverter's output current and distort the current waveform, particularly in the current zero-crossing regions. This reduces power efficiency and increases torque ripple [7–10]. The nonlinearities in VSI have also an impact on the control efficiency of low-speed applications, especially when the system is operating in the low-torque zone. For gimbal applications, for example, when disturbances such as g-force are not present, low torque with a speed approaching zero is required during the tracking of a distant object. A high-performance PMSM VSI-fed drive can be accomplished by utilizing high current bandwidth regulation and the minimization of VSI nonlinearity effects.

In the literature, various nonlinearity compensation methods for PWM VSIs are discussed, with an emphasis on dead time compensation. Compensation techniques can be classified as either hardware-based which needs additional circuits or softwarebased.

A voltage measurement circuit is designed in [19] to calculate the real pole voltage by using the time measurement module (eCAP) of the DSP. From this information, the average output voltage is calculated for every switching cycle, and it is compared to the reference voltage. The difference is applied in the next loop to compensate for

the effect of dead time. In [20], the phase voltages are scaled using hardware and given to the controller as an input to calculate the actual duty cycles. The difference between the actual and desired duty cycle is calculated and utilized as an input to the dead time distortion shaping algorithm, which compensates for both the dead time effect and the parasitic capacitance effect. A diode-conduction detector is designed in [21] to identify the polarity of the phase current by measuring the diode voltage and comparing it to a reference. When the phase current is flowing out of the leg, only the top switch is utilized, and the current is freewheeling from the diode of the bottom switch. It is vice versa when the phase current is flowing in. The dead time issue is eliminated since the technique does not require dead time to function. An FPGA is used in [22]. During the zero voltage states, the phase currents of the inverter are oversampled and the phase current slopes are calculated by using the linear least mean squares regression. With these inputs, the FPGA predicts the phase currents of the next switching cycle. A look-up table that is constructed off-line holds needed compensation times according to predicted currents, and the duty cycles of switches are updated to compensate for the dead time effect.

Software-based methods can be categorized by

- monitoring sixth harmonics and multiples in quadrature axis currents,

- using a wide bandwidth current controller,

- compensating for average voltage error in each switching period.

Because dead time generates sixth harmonics and multiples in quadrature axis currents in the d-q frame, a revised repetitive controller, which is preferred for rejecting periodic signals, is used in [23]. The current loop's closed-loop gain is increased at those frequencies. The controller is modified by changing the periodicity as a function of the PMSM's angular speed and it is added in cascade to the PI current controller. The quadrature d-q frame real voltages are computed using the PMSM model and measured phase currents in [24]. The reference d-q frame voltages are then calculated using reference quadrature currents while assuming no dead time. The difference is then added to the reference voltages to remove the dead time effect. An adaptive single-frequency noise canceller filter is designed by using the least mean square (LMS) algorithm to reduce the sixth harmonic of the quadrature currents in the d-q frame for FOC and V/f control in [11] and [25], respectively. The cyclical disturbances in the d-q reference frame are compensated by the iterative learning strategy in [26]. The learning patterns are constructed off-line for a specific operating output frequency and stored in the memory to be used later for that operating frequency. By using a look-up table that shows a relation between the rotor angle and distorted voltage in the d-q reference frame, the disturbance voltages are estimated in the d-q reference frame by an adaptive linear neuron-based (ADALINE) algorithm [27]. In [28], based on the harmonic analysis and the Extended Kalman filter algorithm, the magnitude of the voltage error is estimated by using the model of the PMSM in the quadrature axis d-q frame. The polarity detection is based on estimated quadrature currents during the zero crossing regions.

The performance of wide-bandwidth current controllers with an experiment is examined in [29] to reject disturbances induced by inverter nonlinearities. Complex PI, symmetrical optimum, and pole placement current controllers are designed for a PMSM and the symmetrical optimum current controller provides the best results among them.

In [30], a graphical approach is utilized to compensate for average voltage errors in each switching period. Voltage drops, turn-on and off times of the power switches, and dead time parameters of the inverter are measured offline and used in the voltage compensation algorithm. To find the direction of the phase currents during zerocrossing regions, a current observer is designed by using a discrete model of a PMSM. The reference voltages are updated for each switching period according to the voltage compensation method.

The purpose of this chapter is to examine the effects of nonlinearities in the zerocrossing regions of the d axis quadrature current of Si MOSFET and GaN E-HEMT VSI-based servo drives. In the d-axis, an offline compensation function for Si MOS-FET VSI-based servo drive is designed to reduce nonlinearities. But it is difficult to obtain a valid compensation function for each input voltage, for all motor speeds, and for all environmental conditions. However, by using the GaN E-HEMT VSI-based servo drive, the nonlinearities in the zero-crossing regions of the d axis quadrature current are reduced without any compensation method. How nonlinearities influence current control bandwidth is also demonstrated in the chapter.

#### 2.2 Nonlinearity Analysis of SI MOSFET-Based VSI

In this part, the nonlinearities in a Si MOSFET-based VSI are analyzed by comparing ideal and actual phase output voltages. The voltage errors on the phases are transformed first to the  $\alpha$ - $\beta$  frame by the Clarke transform, then to the d-q frame by the Park transform. Then Fourier analysis is performed to analyze harmonics of the phase output voltage distortions caused by nonlinearities in the VSI.

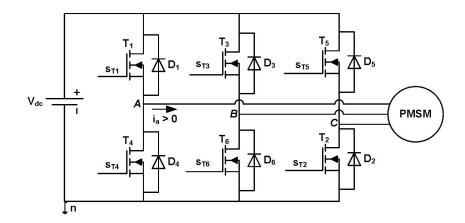

In an ideal case, a switch is assumed to have a zero switching time and a zero voltage drop while in conduction. Fig. 2.1 depicts a standard Si MOSFET-based VSI-fed PMSM. The top row of Fig.2.2 shows the gate signals of the leg A,  $T_1$ , and  $T_4$  Si MOSFETs, and the second row of the figure shows the ideal midpoint voltage,  $V_{an}$ . However, voltage drops occur on power switches when they are in conduction and they have finite turn-on and off times. Their gate drives also have turn-on and turn-off propagation delay times. To prevent the cross-conduction of the leg of the VSI, a dead time is inserted into the corresponding PWM signals of the upper and lower switches. The third and fourth rows of Fig.2.2 show these situations.

Where;

$\mathrm{t}_{\mathrm{dead}}$  : the dead time

$t_{on}$  : turn on delay + rise time of the gate drive/Si MOSFET

$t_{\rm off}$  : turn off delay + fall time of the gate drive/Si MOSFET

$V_{ds}$ : drain to source voltage of the Si MOSFET

$\mathrm{V}_{\mathrm{FWD}}$  : voltage of the free wheeling diode

$\mathrm{T}_{\mathrm{on}}$  : ON time of the upper Si MOSFET

$T_{\rm PWM}$  : time period of the PWM

The forms of the falling and rising edges of the leg voltage are affected by the deadtime interval [31]. Furthermore, because of the output capacitance of the power device, the rise and fall periods of the leg voltage will vary depending on the phase

Figure 2.1: Si MOSFET-based VSI PMSM drive block schema

Figure 2.2: Gate signals and leg A output voltages of the SI MOSFET-based VSI

current direction and magnitude [32]. For the sake of convenience, the leg voltage transition is considered instantaneous in this study. All transistors in VSI are supposed to have identical properties, and all inverter legs are considered to be symmet-

rical. This allows the inverter to be analyzed for just one leg. The phase current is also assumed to not alter the sign during the study time.

During the dead time interval, the current flows through the freewheeling diode  $D_4$  when the phase current is greater than zero and through the freewheeling diode  $D_1$  when the phase current is less than zero. Because the output voltage is affected by the direction of the current, an uncontrollable zone is introduced.

The total voltage difference  $\Delta V_{an}$  between the ideal  $V_{an}$  and the actual  $V_{an}$  can be determined as follows:

when  $i_a > 0$ :

$$\Delta V_1 + \Delta V_7 = -(T_{PWM} - T_{on} - t_{dead} - t_{on})(V_{ds})$$

$$\Delta V_2 = -(t_{off})(V_{dc} + V_{ds})$$

$$\Delta V_3 = -(t_{dead} - t_{off} + t_{on})(V_{FWD} + V_{dc})$$

$$\Delta V_4 = -(T_{on} - t_{dead} - t_{on})(V_{ds})$$

$$\Delta V_5 = (t_{off})(V_{dc} - V_{ds})$$

$$\Delta V_6 = -(t_{dead} - t_{off} + t_{on})(V_{FWD})$$

$$\Delta V_{i_a>0} = \Delta V_1 + \Delta V_2 + \Delta V_3 + \Delta V_4 + \Delta V_5 + \Delta V_6 + \Delta V_7$$

(2.1)

where  $\Delta V_1$  to  $\Delta V_7$  are depicted in Fig. 2.2.

$$\Delta V_{i_a>0} = V_{ds}(-T_{PWM} + 2t_{dead} + 2t_{on} - 2t_{off}) + V_{dc}(-t_{dead} - t_{on} + t_{off}) + V_{FWD}(-2t_{dead} - 2t_{on} + 2t_{off})$$

(2.2)

The following formula can be used to measure the voltage error  $\Delta V$  over a period:

$$\Delta V = \frac{\Delta V_{i_a > 0}}{T_{PWM}} \tag{2.3}$$

when  $i_a < 0$ :

$$\Delta V_{1} + \Delta V_{7} = (T_{PWM} - T_{on} - t_{dead} - t_{on})(V_{ds})$$

$$\Delta V_{2} = -(t_{off})(V_{dc} - V_{ds})$$

$$\Delta V_{3} = (t_{dead} - t_{off} + t_{on})(V_{FWD})$$

$$\Delta V_{4} = (T_{on} - t_{dead} - t_{on})(V_{ds})$$

$$\Delta V_{5} = (t_{off})(V_{dc} + V_{ds})$$

$$\Delta V_{6} = (t_{dead} - t_{off} + t_{on})(V_{FWD} + V_{dc})$$

$$\Delta V_{i_{a}<0} = \Delta V_{1} + \Delta V_{2} + \Delta V_{3} + \Delta V_{4} + \Delta V_{5}$$

$$+ \Delta V_{6} + \Delta V_{7}$$

$$(2.4)$$

$$\Delta V_{i_a < 0} = -(\Delta V_{i_a > 0}) \tag{2.5}$$

After calculating the volt-second area differences  $\Delta V_{i_a>0}$  when  $i_a > 0$  and  $\Delta V_{i_a<0}$ when  $i_a < 0$ , the overall voltage error  $\Delta V_{an}$  can be expressed as follows:

$$sign(i_{a}) = \begin{cases} -1, & \text{if } i_{a} < 0\\ 1, & \text{if } i_{a} > 0 \end{cases}$$

(2.6)

$$\Delta V_{an} = sign(i_a)\Delta V \tag{2.7}$$

where  $\Delta V$  is defined in equation (2.3).

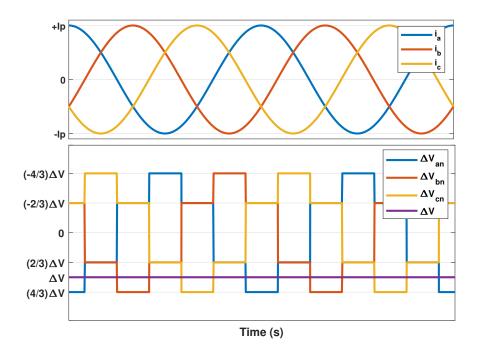

Assuming the PMSM is Y-connected, the overall voltage errors of the legs can be stated as follows [11]. The associated voltage errors are illustrated in Fig. 2.3 to better visualize them by using ideal phase currents where  $I_p$  is the peak phase current value.

$$\begin{bmatrix} \Delta V_{an} \\ \Delta V_{bn} \\ \Delta V_{cn} \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & \frac{-1}{3} & \frac{-1}{3} \\ \frac{-1}{3} & \frac{2}{3} & \frac{-1}{3} \\ \frac{-1}{3} & \frac{-1}{3} & \frac{2}{3} \end{bmatrix} \begin{bmatrix} sign(i_a)\Delta V \\ sign(i_b)\Delta V \\ sign(i_c)\Delta V \end{bmatrix}$$

(2.8)

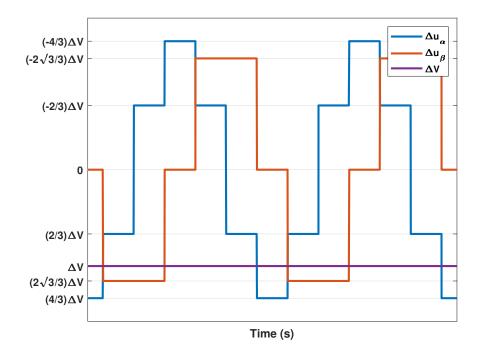

Through the use of transforms by Clarke and Fourier [33], phase voltage errors in the  $\alpha$ - $\beta$  reference frame can be given as follows and it is illustrated in Fig. 2.4:

Figure 2.3: Voltage errors in the legs as a result of VSI nonlinearities.

$$\begin{bmatrix} \Delta u_{\alpha} \\ \Delta u_{\beta} \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & \frac{-1}{3} & \frac{-1}{3} \\ & & \\ 0 & \frac{2}{\sqrt{3}} & \frac{-2}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} \Delta V_{an} \\ \Delta V_{bn} \\ \Delta V_{cn} \end{bmatrix} = \frac{4}{\pi} \Delta V \begin{bmatrix} \sin \dot{\theta}_e t + \sum_{k=6n-1}^{\infty} \frac{\sin k \dot{\theta}_e t}{k} + \sum_{k=6n+1}^{\infty} \frac{\sin k \dot{\theta}_e t}{k} \\ -\cos \dot{\theta}_e t + \sum_{k=6n-1}^{\infty} \frac{\cos k \dot{\theta}_e t}{k} - \sum_{k=6n+1}^{\infty} \frac{\cos k \dot{\theta}_e t}{k} \end{bmatrix}$$

(2.9)

where n=1,2,3... and  $\dot{\theta}_e$  is the electrical angular speed.

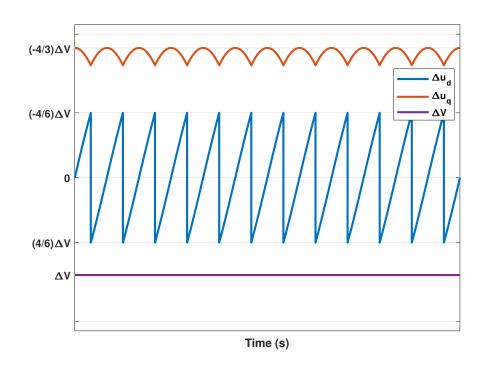

The following are the synchronous rotating d-q frame voltage errors after implementing the Park transform and are depicted in Fig. 2.5.

$$\begin{bmatrix} \Delta u_d \\ \Delta u_q \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} \Delta u_\alpha \\ \Delta u_\beta \end{bmatrix} = \frac{4}{\pi} \Delta V \begin{bmatrix} \frac{12}{35} \sin 6\dot{\theta}_e t + \frac{24}{143} \sin 12\dot{\theta}_e t + \dots \\ -1 + \frac{2}{35} \cos 6\dot{\theta}_e t - \frac{2}{143} \cos 12\dot{\theta}_e t + \dots \end{bmatrix}$$

(2.10)

The current distortion in the d-q reference frame can then be determined as:

$$\begin{bmatrix} \Delta i_d \\ \Delta i_q \end{bmatrix} = \frac{4}{\pi} \Delta V \begin{bmatrix} \frac{12}{35Z_6} \sin(6\dot{\theta}_e t - \phi_6) + \dots \\ \frac{-1}{R_s} + \frac{2}{35Z_6} \cos(6\dot{\theta}_e t - \phi_6) + \dots \end{bmatrix}$$

(2.11)

Figure 2.4: Voltage errors in  $\alpha$ - $\beta$  reference frame as a result of VSI nonlinearities.

Figure 2.5: Voltage errors in *d*-*q* reference frame as a result of VSI nonlinearities.

$L_s$  denotes stator inductance,  $R_s$  denotes stator resistance,  $m=6,12,18...,Z_m$  and

$\phi_m$  are given as:

$$Z_m = \sqrt{R_s^2 + (m\dot{\theta}_e L_s)^2}$$

$$\phi_m = \tan^{-1} \frac{m\dot{\theta}_e L_s}{R_s}$$

The output voltage disturbances introduced by nonlinearities contribute  $5^{th}$  and  $7^{th}$  harmonics to the phase current as well as to the  $\alpha$ - $\beta$  reference frame currents in the stationary reference frame, as shown by Equations (2.9) to (2.11). By applying the Park transform, it is obtained that the phase voltage distortions also introduce the  $6^{th}$  harmonic and its multiples of the fundamental output frequency on the d and q currents. This condition creates ripples in the phase currents as well as the d-q currents. The resulting torque pulsations limit the performance of the controller.

#### 2.3 Experimental Study on SI MOSFET-Based VSI

In this part, nonlinearities in VSI are investigated experimentally by using a Si MOSFETbased VSI.

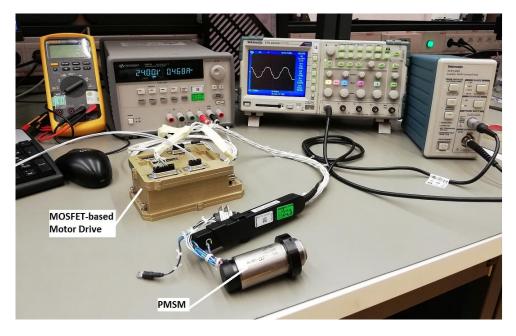

The Si MOSFET-based 3-phase, 2-level VSI-based servo motor drive is used to control a coreless type low inductance PMSM. The servo motor drive is comprised of TrenchFET Si MOSFETs (SUM90N10), a 3-phase gate driver (IRS2336), and a floating-point microcontroller (F28335). By considering the dynamic electrical time parameters of the gate driver and Si MOSFETs in the VSI, dead time is set to 1  $\mu$ s during the experiments.

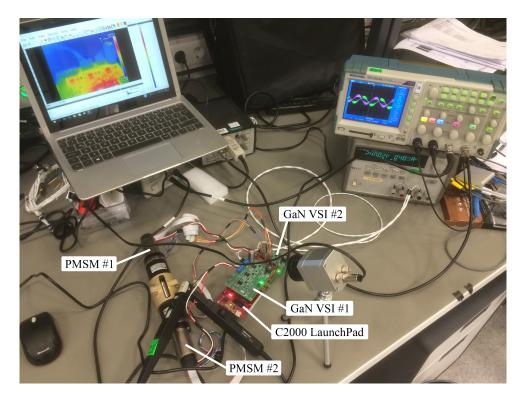

Table 2.1 lists the motor parameters, and Fig. 2.6 depicts the experimental setup.

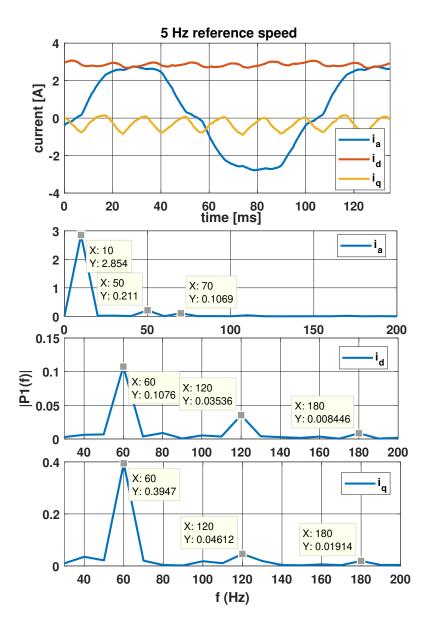

#### 2.3.1 Observation of Current Harmonics as a Result of Nonlinear Effects

To observe the harmonics in the phase current and the d-q reference frame currents that are caused by the nonlinearities of the VSI, the motor is driven at a speed of 5 Hz mechanical speed. To get rid of the audible noise, the recommended switching frequency ( $f_{sw}$ ) is given as a minimum of 20 kHz [34]. Therefore, the switching

| Parameters           | Value      |

|----------------------|------------|

| Rated voltage        | 24 V       |

| Rated torque         | 63.3 mNm   |

| Rated speed          | 16700 rpm  |

| Rated current        | 5.45 A     |

| Torque constant      | 12.8 mNm/A |

| Inductance (l-l)     | 29.5 μH    |

| Resistance (1-1)     | 0.248 Ω    |

| Number of pole pairs | 2          |

| Rated power          | 100 W      |

Table 2.1: PMSM Parameters

Figure 2.6: Experimental setup with Si MOSFET-based VSI.

frequency of the VSI is set to  $20 \ kHz$ , which is also sufficient to observe these harmonics.

As seen in Fig. 2.7, nonlinear effects primarily generate  $5^{th}$  and  $7^{th}$  harmonics in phase currents, as well as  $6^{th}$  and its multiple harmonics in d-q reference frame currents.

Figure 2.7: Phase current  $i_a$ , d-q reference frame current  $i_d$  and  $i_q$  and their frequency spectrums in open-loop control.

Phase currents are measured using a power analyzer to see how the fundamental output frequency  $f_o$  value affects phase current distortion. The phase voltage error  $\Delta V$ occurs  $\frac{h}{2}$  times during the half-cycle of output voltage, where  $h = \frac{f_{sw}}{f_o}$  and the difference can be calculated as  $A_{diff} = h\Delta V$ . Therefore, as  $f_o$  is increased, the distortion of the phase voltage decreases, which in turn reduces the distortion of the phase current. Table II shows the percentages of harmonic distortion values of the measured phase currents when the PMSM is operating at 5 Hz and 20 Hz mechanical speeds, that is, 10 Hz and 40 Hz electrical speeds, respectively.

| <b>Current Harmonics</b> | @10 Hz | @40 Hz |

|--------------------------|--------|--------|

| $5^{th}$                 | 7.42   | 4.67   |

| $7^{th}$                 | 3.75   | 2.06   |

| $11^{th}$                | 1.27   | 0.17   |

| $13^{th}$                | 0.04   | 0.70   |

| $17^{th}$                | 0.57   | 1.02   |

| $19^{th}$                | 0.21   | 0.60   |

| $THD_{I}$                | 8.52   | 5.43   |

Table 2.2: Phase Current Harmonic Distortions [%] at 10 Hz and 40 Hz Electrical Reference Speed at No Load

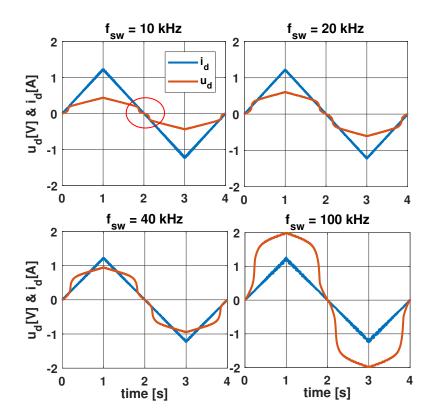

#### 2.3.2 Relationships Between Switching Frequency and Nonlinearities

In this part, by using the  $u_d$ - $i_d$  graph, the effect of the switching frequency on the nonlinearity is investigated. This part also demonstrates how the current controller bandwidth changes according to the operating region in the  $u_d$ - $i_d$  graph.

The d-q reference frame voltage equations of the PMSM are indicated in (2.12). where;

- $u_d$  : d axis voltage

- $u_q$ : q axis voltage

$L_d$ : *d* axis inductance

$L_q$ : q axis inductance

$\lambda_{\rm f}$ : the permanent magnet flux linkage

$\rho$ : the derivative operator

Note that, for surface mount cylindrical rotor PMSM,  $L_d$  and  $L_q$  are identical and denoted as  $L_s$ .

$$\begin{bmatrix} u_q \\ u_d \end{bmatrix} = \begin{bmatrix} R_s + L_q \rho & \dot{\theta}_e L_d \\ -\dot{\theta}_e L_q & R_s + L_d \rho \end{bmatrix} \begin{bmatrix} i_q \\ i_d \end{bmatrix} + \begin{bmatrix} \dot{\theta}_e \lambda_f \\ 0 \end{bmatrix}$$

(2.12)

Figure 2.8:  $i_d$  current and  $u_d$  voltage, Si MOSFET-based VSI at  $f_{sw} = 10 \ kHz$  to  $100 \ kHz$ .

The standard PI current control approach is used to investigate the influence of switching frequency on nonlinearity. To reach zero speed, the  $i_q$  current reference is set to 0 to minimize the influence of the back electromotive force (emf) voltage  $(\dot{\theta}_e \lambda_f)$  part. Furthermore, to mitigate the influence of the inductance  $L_s$  on the output, the  $i_d$  current reference is varied slowly enough that the  $L_d\rho i_d$  term is close to zero.

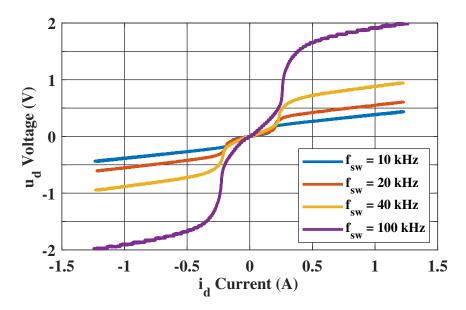

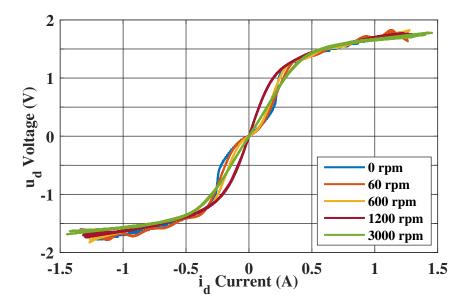

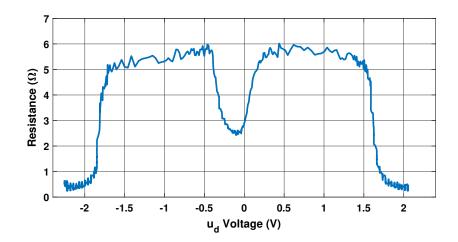

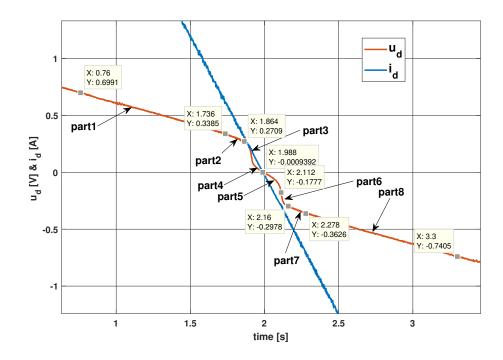

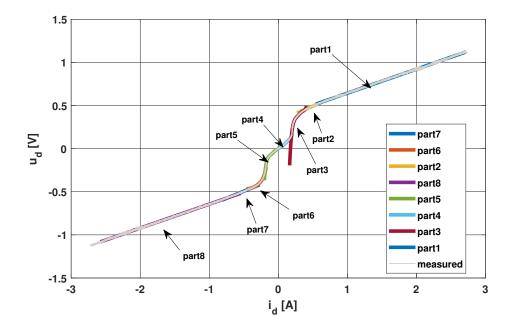

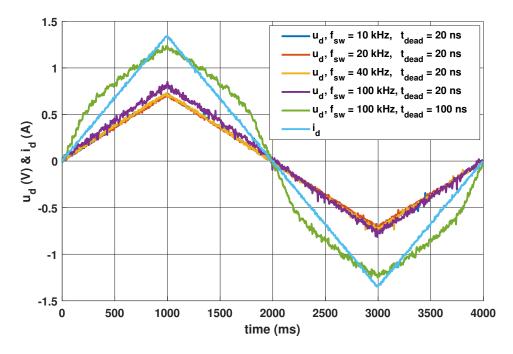

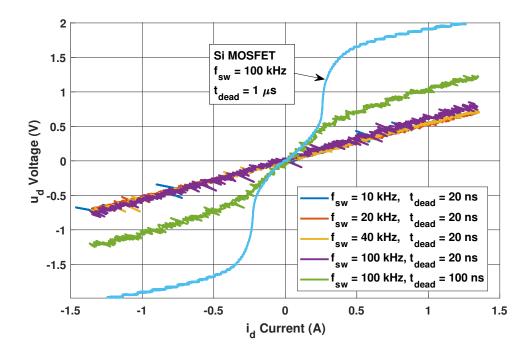

In the ideal scenario, the necessary  $u_d$  voltage equals  $R_s i_d$  for a given  $i_d$  current. However, this equation is not linear because of the nonlinearity of the system, which degrades the performance and reliability of the control system. Nonlinearity is particularly evident in zero-crossing regions of the  $i_d$  current and is exacerbated by increasing the switching frequency, as depicted in Fig. 2.8 and Fig. 2.9. It should be noted that the experimental findings presented in the figures indicate the combined effect from the microcontroller's PWM outputs to the microcontroller's current readings, which includes parasitic output capacitance, turn on/off time, delay time, dead time, voltage drops on different modules, and so on.

Figure 2.9:  $u_d$  voltage versus  $i_d$  current, Si MOSFET-based VSI at  $f_{sw} = 10 \ kHz$  to  $100 \ kHz$ .

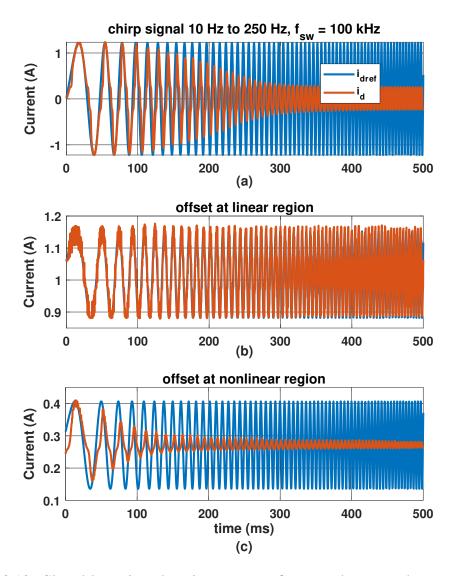

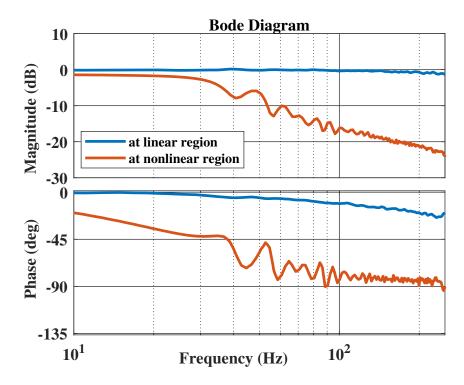

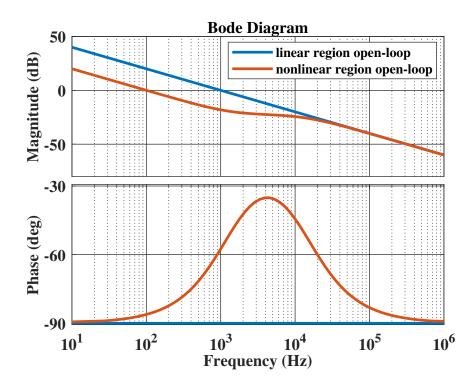

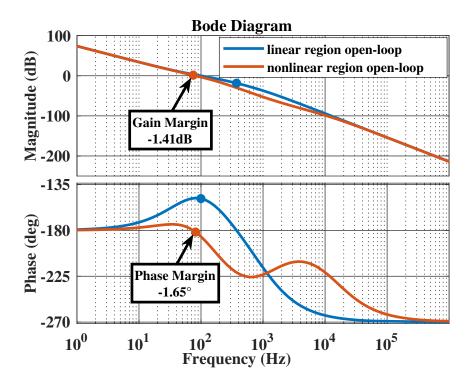

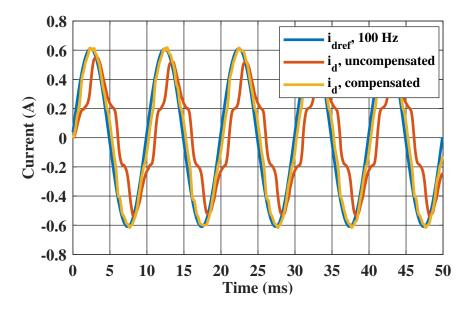

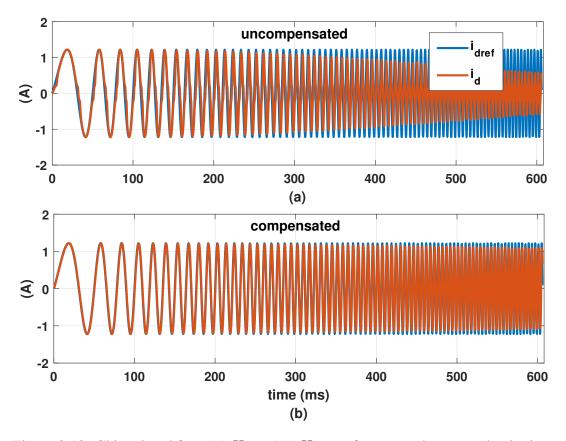

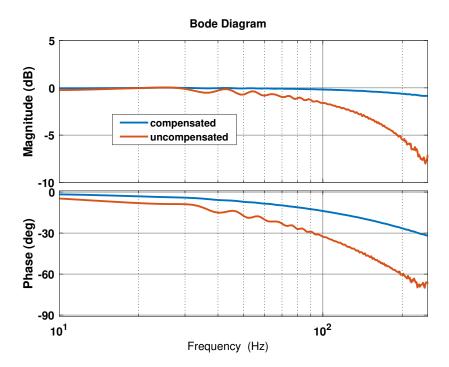

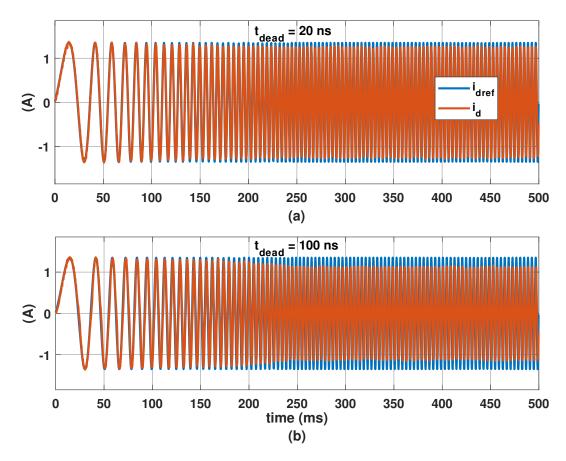

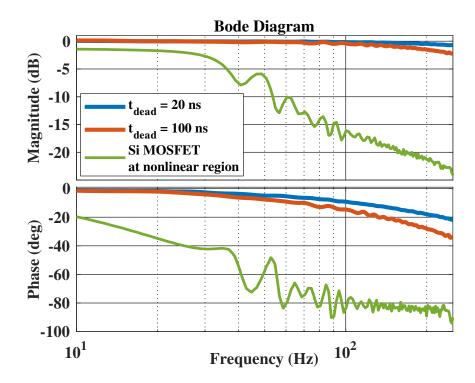

To evaluate the influence of nonlinearity, a chirp signal ranging from 10 Hz to 250 Hz is used as the  $i_d$  reference at  $f_{sw} = 100 \ kHz$ . While the current controller's bandwidth is built to be about  $1 \ kHz$ , as presented in Fig. 2.10a, it cannot follow the reference signal at frequencies greater than 30 Hz. Then, on the  $i_d$  reference chirp signal, an offset current is applied such that  $u_d$  versus  $i_d$  acts as a linear system in this region (Fig. 2.10b). In this linear region, the  $i_d$  reference chirp signal, causing the device to enter the nonlinear region (Fig. 2.10c). As can be seen, the reference signal cannot be followed in this region. It can be concluded that the controller bandwidth changes according to the operating region in the  $u_d$ - $i_d$  graph. The bode diagram illustrates this issue as well, which can be seen in Fig. 2.11.