## A GENERAL FRAMEWORK FOR THE DETERMINISTIC MEDIUM ACCESS ON THE CONTROLLER AREA NETWORK

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

MURAT AKPINAR

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ELECTRICAL AND ELECTRONICS ENGINEERING

JUNE 2022

## Approval of the thesis:

### A GENERAL FRAMEWORK FOR THE DETERMINISTIC MEDIUM ACCESS ON THE CONTROLLER AREA NETWORK

submitted by **MURAT AKPINAR** in partial fulfillment of the requirements for the degree of **Doctor of Philosophy in Electrical and Electronics Engineering Department, Middle East Technical University** by,

| Prof. Dr. Halil Kalıpçılar<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>     |  |

|------------------------------------------------------------------------------------------------|--|

| Prof. Dr. İlkay Ulusoy<br>Head of Department, <b>Electrical and Electronics Engineering</b>    |  |

| Prof. Dr. Ece Güran Schmidt<br>Supervisor, <b>Electrical and Electronics Engineering, METU</b> |  |

| Prof. Dr. Klaus Werner Schmidt<br>Co-supervisor, Electrical and Electronics Engineering, METU  |  |

|                                                                                                |  |

| Examining Committee Members:                                                                   |  |

| Prof. Dr. Halit Oğuztüzün<br>Computer Engineering, METU                                        |  |

| Prof. Dr. Ece Güran Schmidt<br>Electrical and Electronics Engineering, METU                    |  |

| Prof. Dr. Bülent Tavlı<br>Electrical and Electronics Engineering, TOBB ETÜ                     |  |

| Prof. Dr. Ali Ziya Alkar<br>Electrical and Electronics Engineering, Hacettepe University       |  |

| Assoc. Prof. Dr. Mustafa Mert Ankaralı<br>Electrical and Electronics Engineering, METU         |  |

|                                                                                                |  |

Date: 13.06.2022

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Surname: Murat Akpınar

Signature :

#### ABSTRACT

## A GENERAL FRAMEWORK FOR THE DETERMINISTIC MEDIUM ACCESS ON THE CONTROLLER AREA NETWORK

Akpınar, Murat Ph.D., Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. Ece Güran Schmidt Co-Supervisor: Prof. Dr. Klaus Werner Schmidt

June 2022, 192 pages

This thesis proposes a general framework CANDS (Controller Area Network with Determinism and Synchronization support) for in-vehicle communication on CAN. CANDS features a hierarchy of novel clock synchronization (CS) algorithms with different levels of clock accuracy and implementation complexity. Moreover, CANDS realizes our original idea of weak time division multiple access (WTDMA) for deterministic bus access, while being fully compatible with the standard CAN protocol and its recent extensions.

CS methods within CANDS apply offset and drift correction. While offset correction is performed based on timestamps in periodic reference messages (RMs), drift correction is realized based on (1) the re-synchronization mechanism of the CAN bit timing; (2) drift estimates computed from periodic timestamps with RMs and (3) drift estimates determined in a discrete-time feedback control loop. Since accurate timestamps are essential for the CS performance, the thesis further develops a new timestamping (TS) method, which reduces the effect of uncertainties that are caused by the CAN bit timing, oscillator drifts and different cable lengths. Overall, clock accuracies below 100 ns are achieved in hardware experiments with our TS method and CS algorithms.

Benefiting from the achieved clock accuracy levels, the thesis next introduces WT-DMA as a new method for slotted medium access on CAN together with novel message scheduling algorithms for the assignment of time slots in WTDMA. WTDMA is realized in software and a certain degree of interference between adjacent time slots is tolerated with the usage of Carrier Sense Multiple Access/Collision Resolution (CSMA/CR) and the non-preemptive message transmission on CAN. Sufficient conditions for the correct operation of WTDMA are derived and its practicability is validated with comprehensive hardware experiments. Specifically, bus loads above 90% and deterministic message latencies in the order of hundreds of microseconds are achieved.

Keywords: controller area network, clock synchronization, drift compensation, experimental evaluation, timestamping, slotted bus access, determinism.

## CAN AĞI ÜZERİNDE DETERMİNİSTİK ORTAM ERİŞİMİ İÇİN GENEL BİR İŞ ÇERÇEVESİ

Akpınar, Murat Doktora, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Prof. Dr. Ece Güran Schmidt Ortak Tez Yöneticisi: Prof. Dr. Klaus Werner Schmidt

Haziran 2022, 192 sayfa

Bu tez ile genel bir iş çerçevesi olarak CANDS (Determinizm ve Senkronizasyon destekli Kontrolör Alan Ağı), CAN üzerinde araç içi iletişim için önerilmektedir. CANDS, farklı saat doğruluğu ve uygulama karmaşıklığına sahip yeni saat senkronizasyonu (CS) algoritmalarından oluşan bir hiyerarşiye sahiptir. CANDS, standart CAN protokolü ve son uzantıları ile tamamen uyumluyken, deterministik veri yolu erişimi için zayıf zaman bölmeli çoklu erişim (WTDMA) konusundaki orijinal fikrimizi gerçekleştirir.

CANDS içerisindeki CS yöntemleri, ofset ve kayma düzeltmesi uygular. Ofset düzeltmesi periyodik referans mesajları (RM) ile taşınan zaman damgalarına göre yapılırken, kayma düzeltmesi (1) CAN bit zamanlamasının yeniden senkronizasyon mekanizmasına; (2) periyodik zaman damgalarından hesaplanan kayma tahminlerine ve (3) ayrık zamanlı bir geri besleme kontrol döngüsünde belirlenen kayma tahminlerine göre gerçekleştirilir. CS performansı için doğru zaman damgaları gerekli olduğundan, bu tez ayrıca CAN bit zamanlamasının, osilatör kaymalarının ve farklı kablo uzunluklarının neden olduğu belirsizliklerin etkisini azaltan yeni bir zaman damgası (TS) yöntemi de geliştirir. Genel olarak, TS yöntemimiz ve CS algoritmalarımız ile yapılan donanım deneylerinde 100 ns ve altında saat doğrulukları elde edilmektedir.

Elde edilen saat doğruluğu sayesinde, CAN üzerinde ayrılmış ortam erişimi için WTDMA ve WTDMA zaman dilimlerinin atanması için yeni mesaj çizelgeleme algoritmaları önerilmektedir. WTDMA yazılımda gerçekleştirilir ve bitişik zaman dilimleri arasında belirli bir düzeyde girişime Taşıyıcı Algılama Çoklu Erişim/Çarpışma Çözümleme (CSMA/CR) ve CAN önleyici olmayan mesaj iletimi sayesinde izin verilir. WTDMA fikrinin doğru çalışması için yeterli koşullar ortaya konulmuş ve kapsamlı donanım deneyleri ile uygulanabilirliği doğrulanmıştır. Spesifik olarak, %90 üzerinde veri yolu yükleri ve birkaç yüz mikro saniye düzeyinde deterministik mesaj gecikmeleri elde edilmektedir.

Anahtar Kelimeler: controller area network, saat senkronizasyonu, kayma düzeltme, deneysel değerlendirme, zaman damgası, ayrılmış ortam erişimi, determinizm.

To my family

#### ACKNOWLEDGMENTS

Foremost, I would like to express my sincere gratitude to my advisors Prof. Dr. Şenan Ece Schmidt and Prof. Dr. Klaus Werner Schmidt who have supported me continuously with their motivation and immense knowledge.

Additional to my advisors, I would like to thank Prof. Dr. Halit Oğuztüzün, Assoc. Prof. Dr. Mustafa Mert Ankaralı and Prof. Dr. Cüneyt F. Bazlamaçcı for their positive attitudes and supportive comments during my thesis monitoring meetings. Moreover, I also thank the jury members of the thesis defense, Prof. Dr. Ali Ziya Alkar and Prof. Dr. Bülent Tavlı for their insightful comments and questions.

I would also like to express my gratitude to ASELSAN for the financial support to attend conferences and to take graduate courses. I also thank TUBITAK since some of the studies conducted in this thesis are supported by the Scientific and Technological Research Council of Turkey (TUBITAK) [Project Code 119E277].

I need to thank my friends, Ali, Savaş, Muhammet, Ahmet, Emre, Soysal, Tuğrul and Çağrı for their friendship for several years. In addition, I am also thankful to my friends at ASELSAN Sami, Bora, Çağrı, Onur, Koray and Ayhan for their enjoyable friendship.

I want to thank my second family -Sönmez family- for their encouraging support and warm behaviours. I should also give special credit to my mother Nezahat Akpınar, my father Ahmet Akpınar and my brother Mehmet Akpınar for their invaluable support in my entire life.

Above all, I would like to present my gratitude to my wife Gizem Sönmez Akpınar for her peerless support and I am grateful to every moment she stands by me. In my last words, I would like to express my love to our baby girl Eylül who will join our family soon.

# TABLE OF CONTENTS

| ABSTRACT .   |                                              |

|--------------|----------------------------------------------|

| ÖZ           | vii                                          |

| ACKNOWLED    | OGMENTS                                      |

| TABLE OF CC  | NTENTS                                       |

| LIST OF TABI | LES                                          |

| LIST OF FIGU | RES                                          |

| LIST OF ABBI | REVIATIONS                                   |

| CHAPTERS     |                                              |

| 1 INTRODUC   | CTION                                        |

| 2 PRELIMIN   | ARY WORK                                     |

| 2.1 CAN      | Protocol                                     |

| 2.1.1        | The Basic Concepts of CAN                    |

| 2.1.2        | CAN Message Transfer                         |

| 2.1.3        | CAN Bit Timing                               |

| 2.1.4        | CAN FD Protocol                              |

| 2.1.5        | CAN XL Protocol                              |

| 2.2 Clock    | x Synchronization on CAN and Related Work 15 |

| 2.2.1        | Local Clock and Clock Drift                  |

|   | 2.2.2     | Clock Synchronization on CAN              | 16 |

|---|-----------|-------------------------------------------|----|

|   | 2.2.3     | Gergeleit's Method                        | 19 |

|   | 2.2.4     | AUTOSAR Method                            | 21 |

|   | 2.3 Exper | rimental Setup                            | 22 |

|   | 2.3.1     | Evaluation of the fundamental CS methods  | 23 |

|   | 2.4 Time  | stamping on CAN and Related Work          | 25 |

|   | 2.5 Notat | ion                                       | 26 |

| 3 | THE GENE  | RAL FRAMEWORK                             | 29 |

|   | 3.1 Mess  | age Scheduling on CAN                     | 30 |

|   | 3.1.1     | Classical Scheduling and WCRT computation | 30 |

|   | 3.1.2     | Offset Scheduling                         | 31 |

|   | 3.2 TDM   | A and TTCAN                               | 32 |

|   | 3.2.1     | TDMA                                      | 32 |

|   | 3.2.2     | TTCAN                                     | 33 |

|   | 3.3 Discu | ussion                                    | 34 |

|   | 3.4 CAN   | DS Framework                              | 34 |

|   | 3.4.1     | Overview                                  | 35 |

|   | 3.4.2     | Parameter Discussion                      | 36 |

| 4 | TIMESTMA  | APING ON CAN                              | 39 |

|   | 4.1 Back  | ground                                    | 40 |

|   | 4.2 Com   | ponents of Timestamping on CAN            | 41 |

|   | 4.3 Unce  | rtainties Related to the CAN Bit Timing   | 42 |

|   | 4.4 TR Q  | puality using the SoF bit as TR Instant   | 43 |

|   | 4.5 | TR Q   | uality using the EoM as Trigger Instant                                    | 45 |

|---|-----|--------|----------------------------------------------------------------------------|----|

|   | 4.6 | Predic | ctable TR Instant                                                          | 46 |

|   | 4.7 | Times  | stamping Service Quality and Discussion                                    | 48 |

|   | 4.8 | Exper  | imental Evaluation of Timestamping on CAN                                  | 50 |

|   | 4   | .8.1   | Experimental Setup                                                         | 50 |

|   | 4   | .8.2   | Evaluation of the Timestamping Service Quality                             | 52 |

|   | 4   | .8.3   | The Evaluation of the SoF Bit as TR Instant                                | 54 |

|   | 4   | .8.4   | The Evaluation of the EoM as TR Instant                                    | 55 |

|   | 4   | .8.5   | Evaluation of the Predictable TR Instant                                   | 56 |

|   | 4   | .8.6   | Overall Comparison                                                         | 57 |

|   | 4.9 | Discu  | ssion and Conclusion                                                       | 57 |

| 5 | SOF | ΓWARE  | E-BASED CLOCK SYNCHRONIZATION METHODS ON CAN                               | 61 |

|   | 5.1 | Revis  | iting the AUTOSAR Offset Correction                                        | 62 |

|   | 5.2 | Revis  | iting the Gergeleit Offset Correction                                      | 64 |

|   | 5.3 | Impro  | oved Software-based Clock Synchronization Method on CAN                    | 65 |

|   | 5   | 5.3.1  | Improved Software-based Clock Synchronization                              | 66 |

|   | 5   | 5.3.2  | Analysis of the ISCS Method                                                | 70 |

|   | 5   | 5.3.3  | Evaluation of the ISCS Method                                              | 71 |

|   |     | 5.3.3  | B.1 Experimental Setup                                                     | 71 |

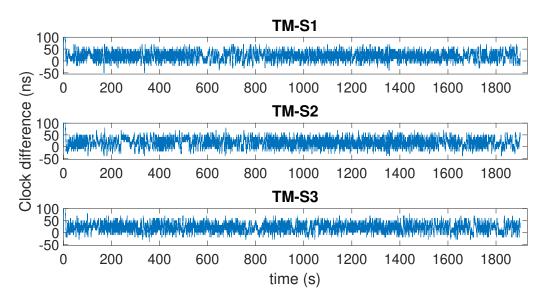

|   |     | 5.3.3  | B.2 Experimental Results                                                   | 72 |

|   | 5.4 |        | based Drift Correction Clock Synchronization for the Controller<br>Network | 75 |

|   | 5   | 5.4.1  | Drift Estimation based on RMs                                              | 75 |

|   |     |        |                                                                            |    |

|   | 5   | 5.4.2  | Experimental Setup and Evaluation                                       | 77  |

|---|-----|--------|-------------------------------------------------------------------------|-----|

|   | 5.5 |        | oller-based Clock Synchronization for the Controller Area Net-          | 78  |

|   | 5   | 5.5.1  | Basic Idea                                                              | 78  |

|   | 5   | 5.5.2  | Discrete-time Control Problem                                           | 80  |

|   | 4   | 5.5.3  | Experimental Setup                                                      | 81  |

|   | 4   | 5.5.4  | Basic Evaluation of the Existing CS methods                             | 82  |

|   | 5   | 5.5.5  | Implementation Details and Evaluation                                   | 83  |

|   | 5   | 5.5.6  | Initialization Phase                                                    | 85  |

|   | 5   | 5.5.7  | Further Evaluation with Initialization Phase                            | 86  |

|   | 5   | 5.5.8  | AUTOSAR CS Compatible Controller Model and Parameters .                 | 88  |

|   | 5.6 | Deper  | ndency of the CS on Timestamping Quality                                | 89  |

|   | 4   | 5.6.1  | Experimental Evaluation                                                 | 90  |

|   | 5.7 | Discu  | ssion and Conclusion                                                    | 93  |

| 6 |     |        | NCHRONIZATION FOR THE CONTROLLER AREA NET-<br>NG BIT TIMING INFORMATION | 95  |

|   | 6.1 | Basic  | Idea behind the Phase-error Based Drift Correction                      | 96  |

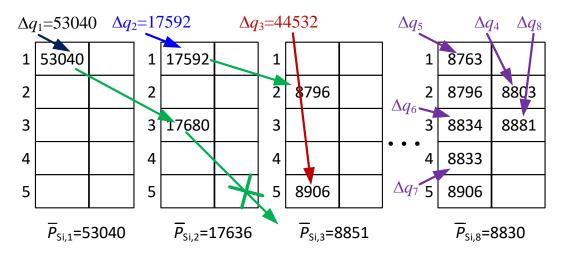

|   | 6.2 | Usage  | e of the Approximate GCD                                                | 98  |

|   | 6.3 | Appro  | oximate GCD-based Drift Correction                                      | 100 |

|   | 6.4 | Exper  | imental Evaluation                                                      | 104 |

|   | 6   | 5.4.1  | Implementation Details                                                  | 104 |

|   | 6   | 5.4.2  | Comprehensive Experimental Evaluation                                   | 106 |

|   | 6   | 5.4.3  | Start-up Phase                                                          | 110 |

|   | 6.5 | Start- | up Method for ACS-PEDC                                                  | 111 |

|   | 6   | .5.1   | Start-up Method                                        |

|---|-----|--------|--------------------------------------------------------|

|   | 6   | .5.2   | Start-up Evaluation                                    |

|   | 6.6 | Discu  | ssion and Conclusion                                   |

| 7 | WEA | K TDI  | MA ON CAN                                              |

|   | 7.1 | Assu   | mptions                                                |

|   | 7.2 | Proto  | col Definition                                         |

|   | 7.3 | Suffic | cient Conditions for Correct Operation of WTDMA        |

|   | 7.4 | Adva   | ntages of Our Method                                   |

|   | 7.5 | Expe   | rimental Evaluation                                    |

|   | 7   | .5.1   | Experimental Setup and Implementation of WTDMA 126     |

|   | 7   | .5.2   | Parameters and Performance Metrics                     |

|   | 7   | .5.3   | Message Set                                            |

|   | 7   | .5.4   | TDMA Operation and WCRTs                               |

|   | 7   | .5.5   | Evaluation of Computed Bounds                          |

|   | 7   | .5.6   | Usage of a Reduced Window Size                         |

|   | 7   | .5.7   | Independence of the CS Method                          |

|   | 7   | .5.8   | CAN Bus with Fault Injection                           |

|   | 7   | .5.9   | CAN Nodes with Non-Sync Messages                       |

|   | 7.6 | Discu  | ssion and Conclusion                                   |

| 8 | WTD | MA M   | IESSAGE SCHEDULING                                     |

|   | 8.1 | Back   | ground                                                 |

|   | 8.2 | Integ  | er Linear Programming for WTDMA Scheduling             |

|   | 8   | .2.1   | ILP for the First Step - Mini Time Slot Assignment 141 |

|    | 8           | .2.2   | ILP for the Second Step - Ultimate Offset Assignment 14                  | .4 |

|----|-------------|--------|--------------------------------------------------------------------------|----|

|    | 8.3         | The H  | Ieuristic Method for WTDMA Scheduling                                    | .9 |

|    | 8           | .3.1   | The Heuristic Method for the First Step - Mini Time Slot As-<br>signment | .9 |

|    | 8           | .3.2   | The Heuristic Method for the Second Step - Ultimate Offset<br>Assignment | 1  |

|    | 8.4         | Evalu  | ation of the WTDMA Scheduling Methods                                    | 3  |

|    | 8.5         | Discu  | ssion                                                                    | 6  |

| 9  | CON         | CLUSI  | ON                                                                       | 9  |

| RI | EFERE       | ENCES  |                                                                          | 3  |

| A  | PROC        | OFS IN | CHAPTER 5                                                                | 7  |

|    | A.1         | Clock  | Accuracy of Offset Correction                                            | 7  |

| В  | PROC        | OFS IN | CHAPTER 6                                                                | 1  |

|    | <b>B</b> .1 | Proof  | of Theorem 2                                                             | 1  |

|    | B.2         | Proof  | of Theorem 3                                                             | 3  |

|    | B.3         | Clock  | Accuracy of ACS-PEDC                                                     | 5  |

|    | B.4         | Start- | up algorithm                                                             | 7  |

| С  | PROC        | OFS IN | CHAPTER 7                                                                | 9  |

|    | C.1         | Proof  | of Theorem 5                                                             | 9  |

| CI | JRRIC       | CULUN  | 1 VITAE                                                                  | )1 |

# LIST OF TABLES

# TABLES

| Table 2.1 | Bounds on the frame bit length depending on $B_i$             |

|-----------|---------------------------------------------------------------|

| Table 4.1 | Dependency comparison                                         |

| Table 4.2 | The trigger quality comparison                                |

| Table 5.1 | Clock accuracy results                                        |

| Table 5.2 | Clock accuracy - overall comparison                           |

| Table 6.1 | Comparison of $\Delta c_{S3}$ for different experiments       |

| Table 6.2 | Maximum and mean PEO period detection times                   |

| Table 6.3 | Evaluation of $t_{2\mu s}$ depending on $U_{TM}$ and $d_{S3}$ |

| Table 7.1 | Message and schedule properties                               |

| Table 7.2 | Observed ratios of schedule violations                        |

| Table 7.3 | Properties of the modified messages                           |

| Table 8.1 | Example of CAN message set                                    |

| Table 8.2 | The $s_i$ values found by ILP                                 |

| Table 8.3 | Example of CAN message set                                    |

| Table 8.4 | Comparison of the success rate of the first step methods      |

|           |                                                               |

| Table 8.5 | Comparison of the run-times of the first step methods | 155 |

|-----------|-------------------------------------------------------|-----|

| Table 8.6 | The run-time comparison for H-S2 and ILP-S2           | 156 |

# LIST OF FIGURES

# FIGURES

| Figure 2.1          | CAN frame - standard format.                                               | 10 |

|---------------------|----------------------------------------------------------------------------|----|

| Figure 2.2          | CAN frame - extended format.                                               | 10 |

| Figure 2.3          | CAN bit segments.                                                          | 12 |

| Figure 2.4          | CAN-FD frame - standard format (11 bit ID)                                 | 13 |

| Figure 2.5          | CAN-FD frame - extended format (29 bit ID)                                 | 14 |

| Figure 2.6          | Illustration of RM transmissions compatible to Gergeleit's method.         | 19 |

| Figure 2.7<br>lowed | Illustration of clock difference when Gergeleit's method is fol-           | 20 |

| Figure 2.8<br>TOSA  | Illustration of the RMs (SYNC and FUP) according to AU-<br>R SW-CS method. | 21 |

| Figure 2.9          | The clock difference example in case of AUTOSAR CS method.                 | 22 |

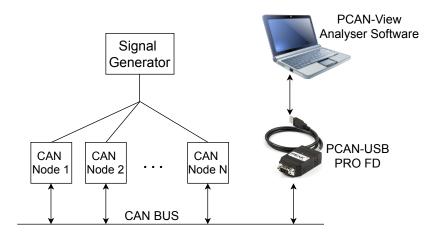

| Figure 2.10         | The general view of the experimental setup                                 | 23 |

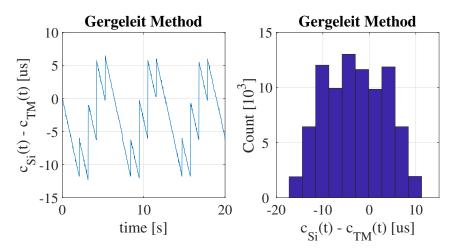

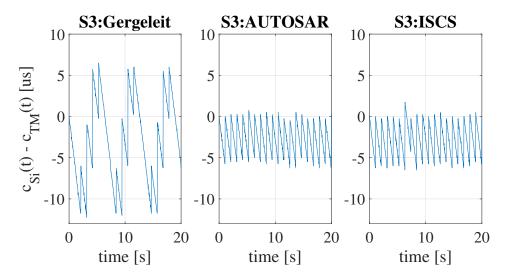

| Figure 2.11         | Clock difference measurement of S3: Gergeleit's method                     | 24 |

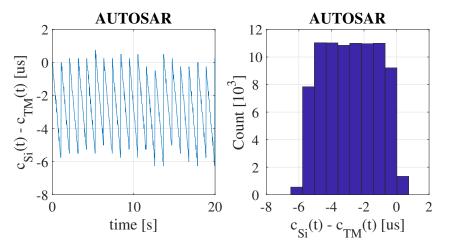

| Figure 2.12         | Clock difference measurement of S3: AUTOSAR                                | 24 |

| Figure 3.1          | TDMA with guard times                                                      | 32 |

| Figure 3.2          | Overview of the CANDS framework                                            | 36 |

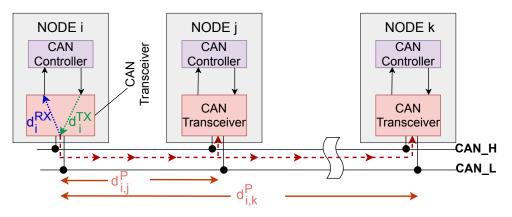

| Figure 4.1          | Signal propagation delays on the CAN bus                                   | 40 |

| Figure 4.2           | The components of the timestamping                                           | 41 |

|----------------------|------------------------------------------------------------------------------|----|

| Figure 4.3           | CAN bit timing synchronization uncertainty.                                  | 42 |

| Figure 4.4           | Possible time difference due to the oscillator drift                         | 43 |

| Figure 4.5           | Timing analysis of SoF bit TR instant.                                       | 44 |

| Figure 4.6           | Timing analysis of EOM TR instant                                            | 46 |

| Figure 4.7           | Timing analysis of the predictable TR instant                                | 48 |

| Figure 4.8           | Experimental setup                                                           | 51 |

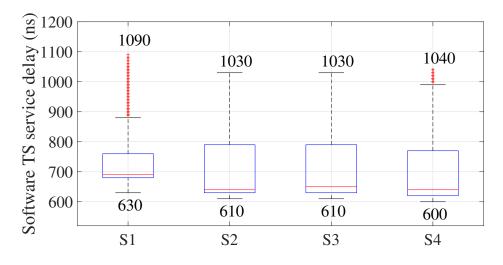

| Figure 4.9           | Software timestamp service delays on different nodes                         | 53 |

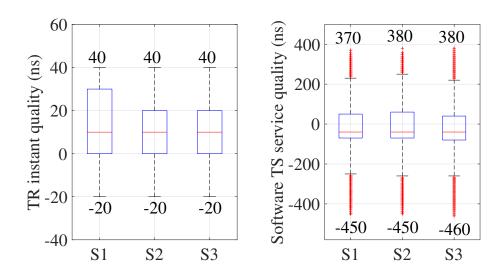

| Figure 4.10          | The quality measurements.                                                    | 53 |

| Figure 4.11          | SoF bit - the trigger quality evaluation.                                    | 54 |

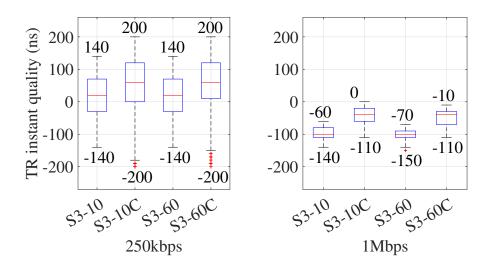

| Figure 4.12          | EoM - the trigger quality evaluation.                                        | 55 |

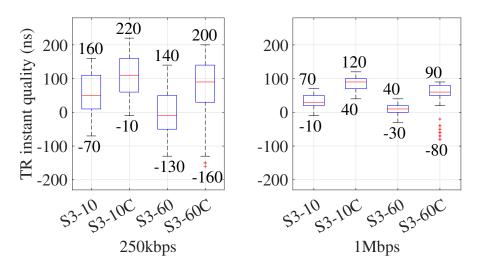

| Figure 4.13          | Predictable TR method - the trigger quality evaluation                       | 56 |

| Figure 5.1<br>curacy | Illustration of the Gergeleit's method with a timestamping inac-<br>$e_{TS}$ | 65 |

| Figure 5.2           | The simulation with random TS errors                                         | 65 |

| Figure 5.3           | Illustration of ISCS method                                                  | 69 |

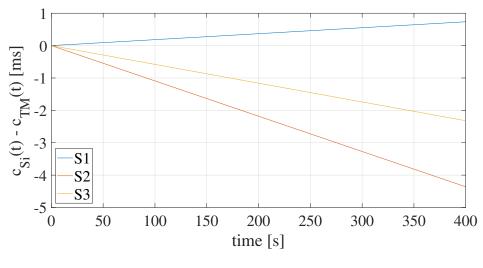

| Figure 5.4           | Clock drift                                                                  | 72 |

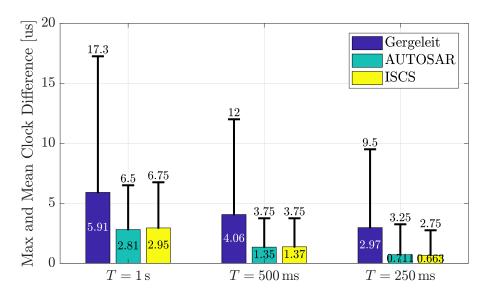

| Figure 5.5           | The dependency of the clock accuracy of S3 on the RM period                  | 73 |

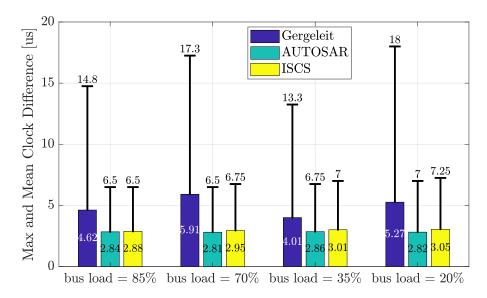

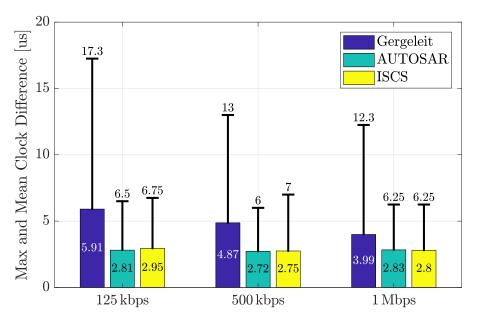

| Figure 5.6           | The dependency of the clock accuracy of S3 on the bus load                   | 74 |

| Figure 5.7           | The dependency of the clock accuracy of S3 on the bit rate                   | 74 |

| Figure 5.8           | The clock accuracy of S3 for different CS methods                            | 75 |

| Figure 5.9           | Computation of the LC update interval                                        | 76 |

| Figure 5.10            | Clock drift measurement for the experimental setup                                                 |

|------------------------|----------------------------------------------------------------------------------------------------|

| Figure 5.11            | Clock difference for the AUTOSAR method                                                            |

| Figure 5.12            | AUTOSAR-DC: Dependency on the RM period                                                            |

| Figure 5.13            | Feedback loop                                                                                      |

| Figure 5.14            | Clock drift                                                                                        |

| Figure 5.15            | Comparison of existing methods                                                                     |

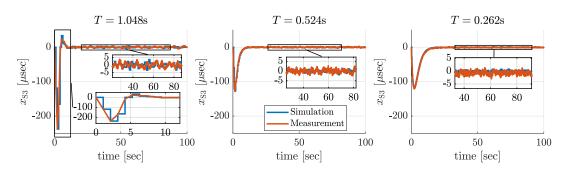

| Figure 5.16 of $T$ for | Comparison of simulation and measurements for different values<br>or $B = 250$ kbps and $U = 70\%$ |

| Figure 5.17<br>tion fo | Comparison of the control algorithm with and without initialization $B = 250$ kbps and $U = 70\%$  |

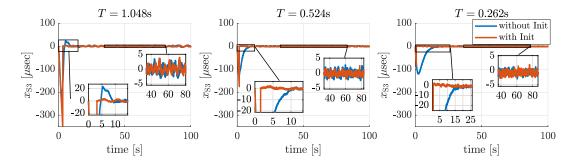

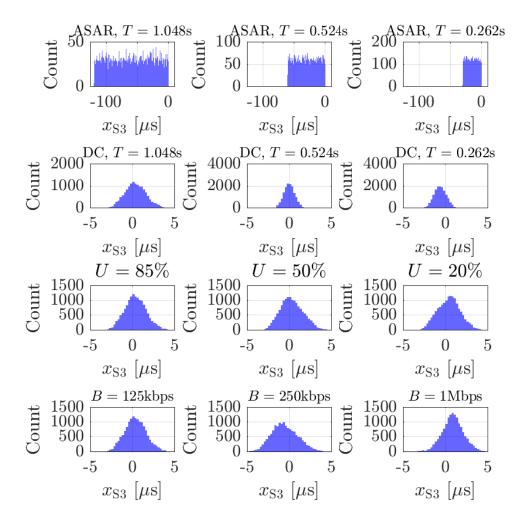

| Figure 5.18            | Clock differences for different parameters                                                         |

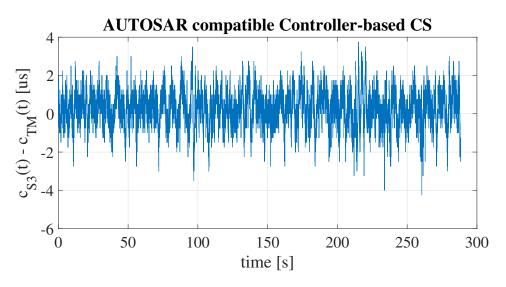

| Figure 5.19            | The clock difference results                                                                       |

| Figure 5.20            | The clock difference results                                                                       |

| Figure 6.1             | Illustration of the PEO detection                                                                  |

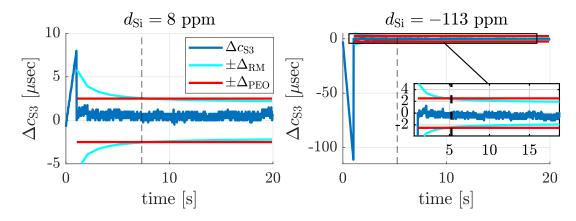

| Figure 6.2             | Example iterations of Algorithm 7 with table $v$                                                   |

| Figure 6.3             | The components of ACS-PEDC                                                                         |

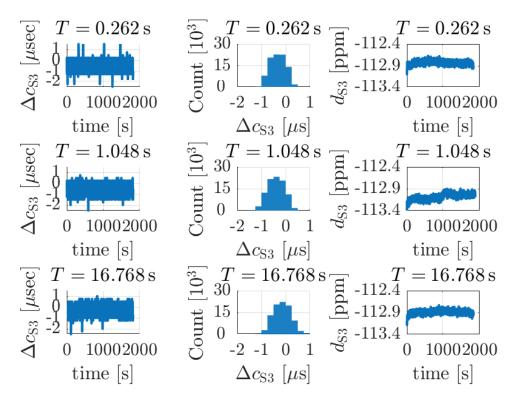

| Figure 6.4             | Measurements for different RM periods                                                              |

| Figure 6.5             | Measurements for a time-varying clock drift                                                        |

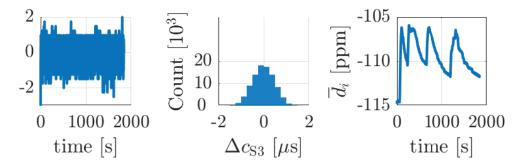

| Figure 6.6             | Start-up measurements for different drift values                                                   |

| Figure 7.1             | WTDMA notation and example illustration                                                            |

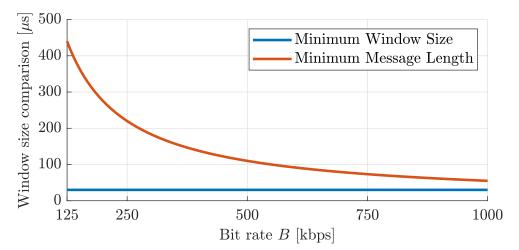

| Figure 7.2             | Minimum window size and minimum frame length                                                       |

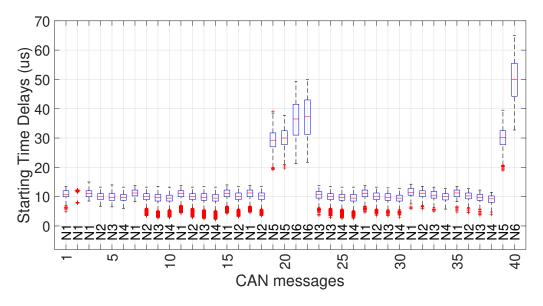

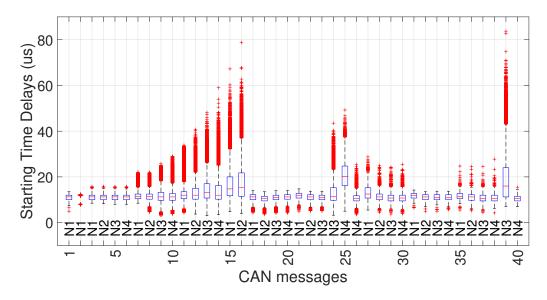

| Figure 7.3             | Starting time delays for a bit rate of $B = 250$ kbps                                              |

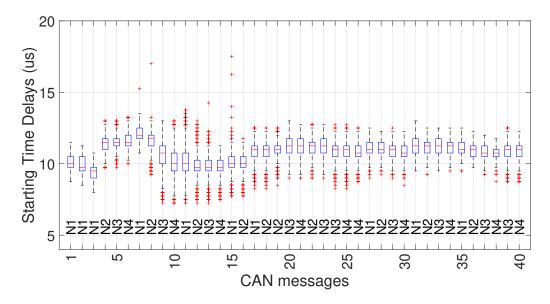

| Figure 7.4 | Starting time delays for a bit rate of $B = 1$ Mbps              |

|------------|------------------------------------------------------------------|

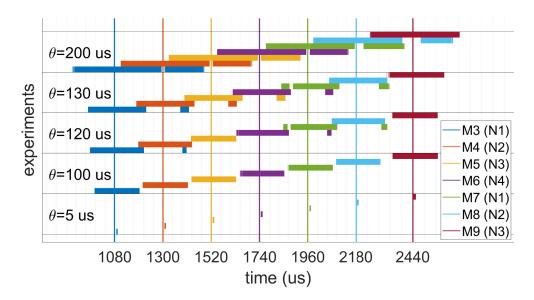

| Figure 7.5 | The distribution of starting times of messages                   |

| Figure 7.6 | The starting time delays of CAN messages - 250 kbps with smaller |

| windo      | w sizes                                                          |

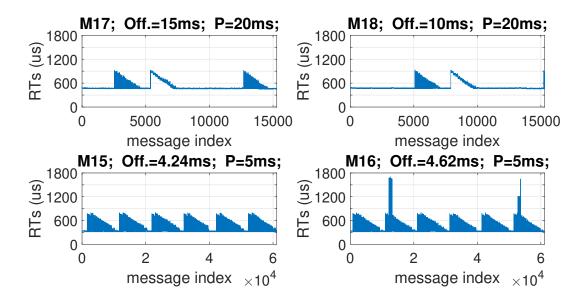

| Figure 7.7 | Response times of messages                                       |

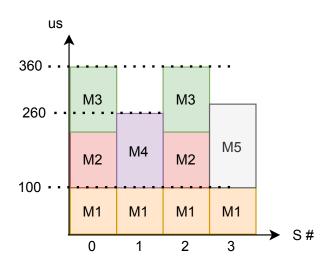

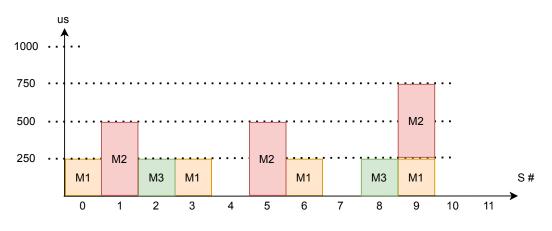

| Figure 8.1 | Example of mini time slot assignment                             |

| Figure 8.2 | Example of mini time slot schedule                               |

# LIST OF ABBREVIATIONS

| AGCD     | Approximate Greatest Common Divisor                          |

|----------|--------------------------------------------------------------|

| ACS-PEDC | Accurate Clock Synchronization method with Phase-Error based |

|          | Drift Correction                                             |

| ACK      | Acknowledgement                                              |

| BER      | Bit Error Rate                                               |

| CAN      | Controller Area Network                                      |

| CAN FD   | CAN with Flexible Data rate                                  |

| CAN XL   | CAN with Extended Length                                     |

| CRC      | Cyclic Redundancy Check                                      |

| СО       | Clock Oscillator                                             |

| CS       | Clock Synchronization                                        |

| CCIP     | CAN Controller IP                                            |

| COTS     | Commercial off-the-shelf                                     |

| CC       | CAN Controller                                               |

| CiA      | CAN in Automation                                            |

| CANDS    | Controller Area Network with Determinism and Synchroniza-    |

|          | tion support                                                 |

| DLC      | Data Length Code                                             |

| EI       | Environmental Instability                                    |

| EoM      | End of Message                                               |

| FPGA     | Field Programmable Gate Array                                |

| FUP      | Follow-up                                                    |

| GCD      | Greatest Common Divisor                                      |

| HR       | Hardware Register                                            |

| HP    | Hyper-Period                         |

|-------|--------------------------------------|

| ID    | Identifier                           |

| IDE   | Identifier Extension                 |

| IDS   | Intrusion Detection Systems          |

| IA    | Initial Accuracy                     |

| ILP   | Integer Linear Programming           |

| LC    | Local Clock                          |

| LTI   | Long Term Instability                |

| NTU   | Network Time Unit                    |

| NTP   | Network Time Protocol                |

| ODU   | Oscillator Drift Uncertainty         |

| PEO   | Phase Error Overflow                 |

| PEOD  | Phase Error Overflow Detection       |

| PLL   | Phase Locked Loop                    |

| PTP   | Precision Time Protocol              |

| ppm   | parts per million                    |

| QoS   | Quality of Service                   |

| RTR   | Remote Transmission Request          |

| RM    | Reference Message                    |

| RJW   | Re-synchronization Jump Width        |

| RT    | Response Time                        |

| RC    | Reference Clock                      |

| SDCC  | Software-defined CAN Controller      |

| SoF   | Start of Frame                       |

| SRR   | Substitute Remote Request            |

| SW-CS | Software-based Clock Synchronization |

| SIC   | Signal Improvement Capability        |

|       |                                      |

| SP    | Sample Point                  |

|-------|-------------------------------|

| TS    | Timestamping                  |

| TR    | Trigger                       |

| TDMA  | Time Division Multiple Access |

| TTCAN | Time Triggered CAN            |

| TQ    | Time Quantum                  |

| TQC   | TQ counter                    |

| ТМ    | Time Master                   |

| TSU   | Timestamping Unit             |

| WCRT  | Worst Case Response Time      |

| WTDMA | Weak TDMA                     |

### **CHAPTER 1**

#### **INTRODUCTION**

Modern vehicles comprise of several distributed electronic control units (ECUs) which require to exchange information continuously [1, 2, 3]. The communication between ECUs has been realized through the bus-based in-vehicle networks such as controller area network (CAN) [4], FlexRay [5], local interconnect network (LIN) [6] and media oriented systems transport (MOST) [7]. Furthermore, the complexity and diversity of the electronic devices continue to increase together with advanced safety, driver assistance and infotainment functions in new vehicles [1]. Thus, the deployment of various new ECUs has accelerated the demand for more efficient and high bandwidth in-vehicle communication solutions [3, 8, 9].

CAN is the most widespread in-vehicle network in modern cars. It supports a maximum bus speed of 1 Mbps at lengths of up to 40 m. Moreover, CAN provides high reliability at a low cost and low power consumption [1, 10, 11]. Thus, CAN is indispensable especially for the transmission of the data of real-time control applications which require low bandwidth but high real time Quality of Service (QoS) such as ABS, suspension and braking systems [1]. Furthermore, several leading automotive producers such as Volkswagen, BMW, Porsche, Audi and Tesla still continue to use CAN in their cars today [12]. Specifically, CAN is used in the drive system and adaptive cruise control system of Audi A-8 D5 which is the world's first level 3 autonomous car [12]. In addition, Tesla Model S/X/3 which are another leading autonomous cars also adopt CAN in their powertrain, chassis and body control systems [12].

The latest researches regarding the in-vehicle networks also show interest in the wireless solutions together with the automotive ethernet [11, 12]. The wireless communication between ECUs is discussed in the literature [2, 13] as an alternative to the wired in-vehicle networks. Even though it may offer an advantage in terms of cabling usage, the wireless in-vehicle communication does not seem feasible in the near future due to the concerns about its security and dependability for safety critical automotive systems [1]. On the other hand, it seems that Ethernet is very likely to be a significant component of the future in-vehicle networks even though it is not very widespread for now [1, 14, 11, 3]. Since Ethernet does not provide deterministic message transmission, the approaches IEEE 802.1Q, Auido Video Bridging (AVB) and TTEthernet [15] have been proposed to improve the real time communication capabilities of Ethernet for automotive networks. Nevertheless, ongoing studies show that Ethernet will not replace the existing communication links such as CAN and FlexRay, but rather performs together with them as the backbone for the next generation of in-vehicle communication links [1, 3].

Due to the continuing importance of CAN, the improvements on it are still ongoing. In order to increase the capabilities of the legacy CAN protocol, CAN with flexible data-rate (CAN FD) is proposed by Bosch [16] that enables higher bit rates up to 8 Mbps and longer message payloads as big as 64 bytes. Furthermore, CAN extended length (CAN XL) is still being studied to reach data rates more than 10 Mbps with message sizes up to 2048 bytes. Although the demand of higher bus speeds and the support for longer message sizes are addressed with the legacy CAN extensions CAN XL and CAN FD, the lack of clock synchronization (CS) between distributed nodes and security precautions are not considered in any of the CAN protocols yet. Therefore, there are several recent studies in the literature which introduce CS methods on CAN [17, 18, 19, 20] and intrusion detection systems (IDS) [21, 22, 23, 24, 25] for security of CAN. Furthermore, the support for deterministic bus access is introduced with Time Triggered CAN (TTCAN) protocol [26] on top of CAN. However, TTCAN is not used in the production cars, to the best of our knowledge, since it requires specific TTCAN controllers which are not compatible to the already deployed CAN networks.

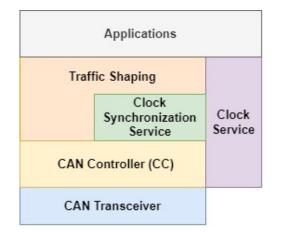

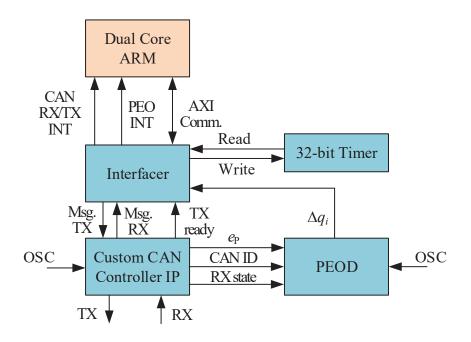

In this thesis, Controller Area Network with Determinism and Synchronization support (CANDS) framework is proposed. CANDS is fully compatible with the legacy CAN protocol and can be realized with the existing standard CAN controllers. It consists of different layers mainly to provide CS and deterministic bus access. Moreover, it can perform with different timestamping and CS methods. That is, different realizations of CANDS are possible according to the available hardware resources.

Within CANDS, there is a clock service unit that realizes the local time for the node and also offers a timestamping unit. CS methods as well as different timing-based intrusion detection systems on CAN generally depend on timestamps which are expected to be taken simultaneously at different nodes. In this thesis, a detailed analysis of existing TS methods which use the start-of-frame (SoF) bit and the end-of-message (EoM) reveals several shortcomings of these methods. Accordingly, a new predictable (TS) method is proposed by exploring and mitigating the identified disadvantages. Furthermore, hardware experiments are conducted to validate our analysis results. As the main outcome, our new TS method provides better TS quality than the existing TS methods.

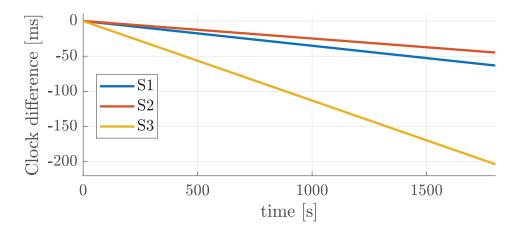

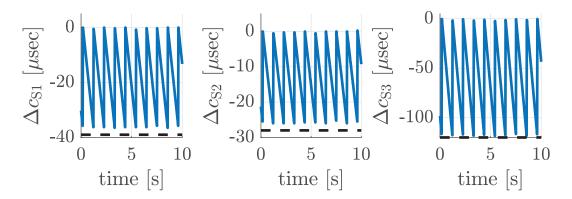

Regarding CS, this thesis introduces several new methods which enable advancements in terms of both offset correction and drift correction. Specifically, CS methods for CAN generally are based on periodic RMs that broadcasts the time information among the CAN nodes. The slave nodes perform offset correction whenever they receive the correct time information with RMs. In addition, the slave nodes may also estimate the clock drift with different approaches and hence perform drift correction in order to prevent the inevitable clock drift between RMs. Regarding the offset correction, AUTOSAR CS [27] and Gergeleit's method [28] are two leading CS methods on CAN. In this thesis, an Improved Software-based Clock Synchronization (ISCS) method is proposed that presents advantages by benefiting from the ongoing message transmission on CAN bus different from the existing methods. That is, ISCS method provides clock accuracy as well as AUTOSAR CS method while consuming the half of the bandwidth of AUTOSAR CS method. Furthermore, ISCS enables much better clock accuracy than Gergeleit's method even though it has the same bandwidth usage with Gergeleit's method. Additionally, clock drift estimation and drift correction methods are also developed in this thesis in order to mitigate the drift between RMs. Firstly, the drift estimation which is simply based on timestamps with RMs (RM-based CS) is introduced. Secondly, the controller-based CS methods which estimate the drift with a discrete-time feedback control loop are also developed. Thirdly, a novel Accurate Clock Synchronization with Phase Error based Drift Correction (ACS-PEDC) CS method that benefits from the internal bit timing of CAN is presented. The novelty of ACS-PEDC comes from the usage of inherent bit synchronization mechanisms of CAN protocol to estimate the clock drift, different than the other methods that are based on periodic timestamps. Thus, ACS-PEDC is not vulnerable to the TS inaccuracy while estimating the clock drift that is one of the important contributions. Furthermore, it has to be noted that the comprehensive hardware experiments are realized to present and compare the achieved clock accuracy results for the existing and proposed CS methods in this thesis. In addition, the dependency of CS performance on TS quality is experimentally shown for the first time in the literature.

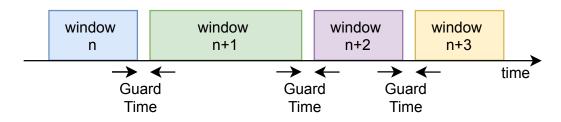

Additional to the advanced CS methods, a novel weak time division multiple access (WTDMA) model is proposed in this thesis in order to realize deterministic medium access on CAN. In particular, the deterministic medium access on CAN is desirable since it enables efficient bandwidth utilization and deterministic message RTs. Our WTDMA does not need to apply the guard times which are proposed for the conventional time division multiple access (TDMA) to handle the clock drift since WTDMA depends on the specific CAN protocol features such as the usage of Carrier Sense Multiple Access/Collision Resolution (CSMA/CR) and the non-preemptive message transmission on CAN. That is, the certain degree of conflicts between the successive time slots are allowed in our WTDMA and thus it is called as Weak TDMA. Furthermore, WTDMA model also considers the software delays additional to the clock inaccuracy which can result in that a message may miss the starting time of its allocated window in a WTDMA schedule. Thus, our WTDMA model can be realized in software and can work with existing standard CAN controllers, different from TTCAN. Specifically, the sufficient conditions for successful WTDMA implementation is provided such that the achieved clock accuracy plus the maximum software delay should be less than the minimum message window size. When the given condition is satisfied, the order of the messages according to the offline computed WTDMA schedule is guaranteed to be followed on the bus and hence the RTs of the messages is mostly determined by the transmission times of the messages which is desired with the deterministic bus access. That is, the message RTs in the order of hundreds of microseconds are achievable for the practical bit rates of 250 kbps. Moreover, WTDMA can cooperate with any existing CS methods and the requirement for CS accuracy loosens for lower CAN bit rates since the minimum message window size gets longer. In summary, WTDMA model is the first time triggered enhancement of CAN protocol that presents a flexible TDMA model which depends on the achievable clock accuracy, the maximum software delays and minimum message window sizes. Moreover, it has to be noted that the practicability of the WTDMA is confirmed with detailed hardware experiments where bus loads up to 100% is achieved successfully with deterministic bus access on CAN.

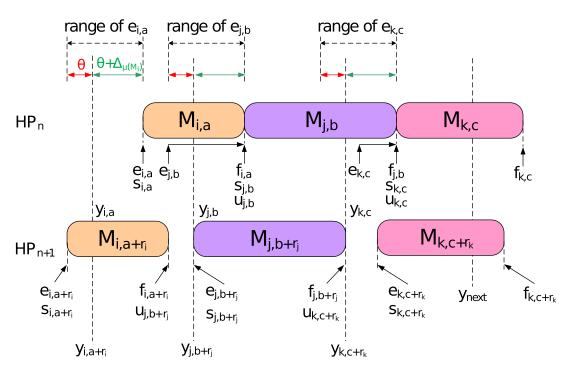

After the introduction of WTDMA model, WTDMA scheduling methods which are used offline to determine the allocated windows for each message are required. Thus, WTDMA scheduling methods that define the windows and assign CAN messages to those windows are also developed in this thesis. Specifically, the WTDMA scheduling problem is first formulated as Integer Linear Programming (ILP) problem. Secondly, the heuristic methods are developed as alternative to ILP-based WTDMA scheduling method. Moreover, it is shown that the proposed WTDMA scheduling methods are able to provide feasible results with several challenging CAN message set examples which are constructed in line with the practical CAN applications.

It further has to be noted that this thesis covers materials that is either published in a paper or submitted for publication. The main contributions of the thesis are listed together with the relevant chapters and publications as follows:

- Chapter 4: M. Akpinar and K. W. Schmidt, "Predictable Timestamping for the Controller Area Network Evaluation and Effect on Clock Synchronization Accuracy," IEEE Transactions on Systems, Man and Cybernetics: Systems, Under Review.

- Chapter 5: M. Akpınar, E. G. Schmidt, and K. W. Schmidt, "Evaluation of clock synchronization algorithms for controller area network," in Signal Processing and Communications Applications Conference, pp. 1–4, May 2020 [29].

- Chapter 5: M. Akpınar, K. W. Schmidt, and E. G. Schmidt, "Improved clock synchronization algorithms for the controller area network (CAN)," in Interna-

tional Conference on Computer Communication and Networks, pp. 1–8, IEEE, 2019 [17].

- Chapter 5: M. Akpınar, E. G. Schmidt, and K. Werner Schmidt, "Drift correction for the software-based clock synchronization on controller area network," in 2020 IEEE Symposium on Computers and Communications (ISCC), pp. 1–6, 2020 [18].

- Chapter 6: D. E. Arkadaş, M. Akpınar, E. G. Schmidt, and K. Werner Schmidt, "Clock Synchronization for the Controller Area Network using Bit Timing Information," in Signal Processing and Communications Applications Conference, pp. 1–4, May 2022 [30].

- Chapter 6: M. Akpınar, K. W. Schmidt, and E. G. Schmidt, "Highly Accurate Clock Synchronization with Drift Correction for the Controller Area Network," IEEE Transactions on Parallel and Distributed Systems, Accepted [31].

- Chapter 7: M. Akpınar, K. W. Schmidt, and E. G. Schmidt, "Weak TDMA for the Deterministic Medium Access on the Controller Area Network," IEEE Transactions on Intelligent Transportation Systems, Under Review.

In brief, the thesis is organized as follows. Chapter 2 introduces the background related to the CAN protocol and the existing CS and timestamping methods on CAN. The conventional message scheduling on CAN and deterministic bus access with TTCAN are explained together with our CANDS framework in Chapter 3. Chapter 4 evaluates the existing TS methods together with our new predictable TS method. In Chapter 5, ISCS, RM-based CS and the controller based CS methods are introduced. The dependency of the CS methods on TS quality is also presented in Chapter 5. Afterwards, Chapter 6 presents ACS-PEDC method that enables precise drift estimates. The WTDMA model and its verification with hardware experiments are presented in Chapter 7 and WTDMA scheduling methods are introduced in Chapter 8. Lastly, Chapter 9 presents the concluding remarks.

### **CHAPTER 2**

#### PRELIMINARY WORK

In this chapter, the background related to the CAN protocol is introduced. That is, the basic principles of CAN protocol, the message formats and CAN bit timing are explained. Moreover, CAN FD and CAN XL which are extensions of the CAN protocol to provide higher bus speed and larger message payloads are also mentioned. Afterwards, the existing CS methods for CAN are introduced, since a global clock is missing in the CAN protocol. Additionally, local clock (LC) and clock drift concepts that are related to CS applications are described. The fundamental CS methods for CAN that are Gergeleit's method [28] and AUTOSAR CS [27] are explained in detail. Then, the general information about the experimental setup that is used throughout this thesis is provided and the preliminary evaluations of Gergeleit's method [28] and AUTOSAR CS methods on CAN depend on the usage of timestamps that are assumed to be taken simultaneously at different nodes. Thus, the existing timestamping methods for CAN and their availability in the existing CAN controllers are also discussed in this chapter. Lastly, the scheduling model notation that is followed in this thesis is presented.

## 2.1 CAN Protocol

CAN [4] is the most prominent in-vehicle communication bus in modern cars [32, 33, 22, 24]. Apart from the automotive industry, it has also been used in different industrial applications to provide communication between distributed components [33]. Specifically, CAN is still indispensable for safety critical components such as engine control, transmission control, braking, steering and suspension control that require high real-time quality of service (QoS) [22, 20, 1]. After the first introduction in the mid 1980s, the advancement of the legacy CAN protocol is yet ongoing with extensions such as CAN FD [16] in 2012 and CAN XL [34] starting from 2018. In particular, CAN XL will offer data rates above 10 Mbps and payloads of up to 2048 bytes [20, 34] to meet the stringent demand of contemporary real-time applications. Due to the continuing importance of CAN, the recent literature is highly interested in possible improvements for CAN such as advanced CS [17, 18, 20] and security methods [22, 32, 24]. Hereby, the recent progress in CS potentially paves the way for the deterministic medium access on CAN which is highly desired to provide efficient bandwidth utilization and deterministic message RTs [35, 36, 37].

#### 2.1.1 The Basic Concepts of CAN

The communication on the CAN bus is realized with fixed format messages. The length of a message can change according to its payload that is allowed to be between 0 and 8 bytes. The bit rates up to 1 Mbps is supported on CAN protocol. Even though the bit rate can be set as different values in different systems according to requirements, it must be uniform and fixed within a given system. That is, the nodes are able to differentiate the bits on the bus since they know the predefined bit duration.

According to CAN protocol, any node can start sending a message when the bus is idle and the ongoing message is received by all nodes simultaneously. Moreover, each message has a unique identifier (ID) that defines the meaning of the message. That is, the nodes can decide to use or ignore the received messages according to their IDs. Additionally, all receivers that successfully receive the transmitted message notify the transmitter node by an acknowledgement.

The bus level can be logic '1' (recessive) and logic '0' (dominant). In case of simultaneous transmission by multiple nodes, the bus level is determined like a wired-AND implementation such that the bus value will be dominant if at least one node transmits a '0' bit (dominant). Additional to the wired-AND mechanism, the message priorities which are determined by unique message IDs are employed on CAN. When multiple nodes start sending messages on the bus, the bus arbitration is resolved by bitwise arbitration based on the message priorities. During the arbitration, a transmitter node reads the bus level and compares it to the bit level which it is sending. If the levels are equal, it continues with sending the next bit. If the levels are not the same, it decides that the arbitration is lost and stops transmitting the following bits. Thus, the transmitter node which is trying to send the message with the highest priority (with the lowest ID value in binary) wins arbitration and continues to send it, whereas the other nodes in the arbitration give up transmitting and start receiving the message. That is, the bus access conflict is resolved without a performance penalty regarding the data and bandwidth loss in CAN protocol.

#### 2.1.2 CAN Message Transfer

There are four different frame types such as data frame, remote frame, error frame and overload frame. The error frame can be transmitted by a node if it detects an error on the message transfer. The overload frame can be used to provide an extra time delay between the last and the following data and remote frames. Moreover, a node can request the transmission of the data frame with the same ID by sending the remote frame. The data frame is used to transmit the data from a transmitter to the receivers. Hereby, the data and remote frames support both standard frame format and extended frame format which have 11 bit ID and 29 bit ID, respectively.

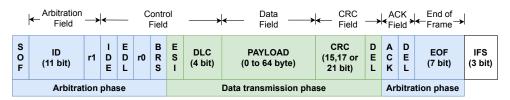

A data frame consists of seven different fields such as start of frame field, arbitration field, control field, cyclic redundancy check (CRC) field, acknowledgement (ACK) field and end of frame field. While the bus is idle, any CAN node can start transmitting a frame with the start of frame (SoF) bit that is always a dominant bit, which results in a falling edge on the CAN bus. Since multiple nodes can attempt transmitting a frame at the same time, the arbitration is resolved during the arbitration field which is different for standard (Fig. 2.1) and extended (Fig. 2.2) formats. In standard format, the arbitration field has an 11 bit ID and the remote transmission request (RTR) bit as seen in Fig. 2.1.

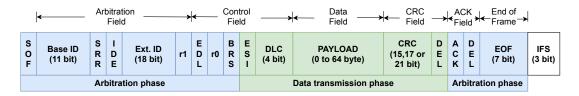

However, the arbitration field consists of a 29 bit ID, the Substitute Remote Request (SRR) bit, the Identifier Extension (IDE) bit and the RTR bit in extended format as seen in Fig. 2.2. The 11 bit Base ID in standard format is lengthened with 18 more Extended ID bits in extended format in order to support more CAN messages with

|             | ← Arbitration<br>Field → ← Control → ← Data<br>Field → ← Field → ← Field → ← Field → ← Frame → |             |             |    |                |                          |                 |             |             |             |                |                |  |

|-------------|------------------------------------------------------------------------------------------------|-------------|-------------|----|----------------|--------------------------|-----------------|-------------|-------------|-------------|----------------|----------------|--|

| S<br>O<br>F | ID<br>(11 bit)                                                                                 | R<br>T<br>R | I<br>D<br>E | r0 | DLC<br>(4 bit) | PAYLOAD<br>(0 to 8 byte) | CRC<br>(15 bit) | D<br>E<br>L | A<br>C<br>K | D<br>E<br>L | EOF<br>(7 bit) | IFS<br>(3 bit) |  |

Figure 2.1: CAN frame - standard format.

unique message IDs.

| ← Arbitration<br>Field |                     |             |             | $\rightarrow$       |             |    |    |                |                          |                 |             | ←End of<br>←Frame→ |             |                |                |

|------------------------|---------------------|-------------|-------------|---------------------|-------------|----|----|----------------|--------------------------|-----------------|-------------|--------------------|-------------|----------------|----------------|

| S<br>O<br>F            | Base ID<br>(11 bit) | S<br>R<br>R | I<br>D<br>E | Ext. ID<br>(18 bit) | R<br>T<br>R | r1 | r0 | DLC<br>(4 bit) | PAYLOAD<br>(0 to 8 byte) | CRC<br>(15 bit) | D<br>E<br>L | A<br>C<br>K        | D<br>E<br>L | EOF<br>(7 bit) | IFS<br>(3 bit) |

Figure 2.2: CAN frame - extended format.

RTR bit is dominant in the data frames and recessive in the remote frames. In both standard and extended formats, RTR bit is sent as the last bit of the arbitration field. SRR bit is transmitted as a recessive bit in the extended format at the same position of the RTR bit in the standard format to substitute it. Thus, an arbitration among the standard and extended frames which have the same base ID is resolved such that the standard frame continues to its transmission on the bus. In order to distinguish the standard and extended formats the value of the IDE bit is used whose position is the same in both formats. The IDE bit is dominant in the standard format and belongs to the control field. On the contrary, it is recessive and belongs to the arbitration field in the extended format.

The 6 bit control field follows the arbitration field for both standard and extended formats. In the standard format, the first bit of the control field is dominant as IDE bit whereas it is recessive as reserved R1 bit in the extended format. The following bits in the CAN frames are the same both for the extended and standard formats. A reserved bit (r0) and data length code (DLC) are sent within the control field before the data field that carries the payload of the CAN message. DLC indicates the number of bytes within the payload and the number of bytes can change from 0 to 8 bytes. The CRC field that follows the payload consists of 15 bit CRC sequence and a recessive bit as CRC delimiter. The CRC sequence is used to check the validity of the ongoing message transmission by all nodes. Afterwards, the transmitter sends a recessive bit

and all receivers which receive the frame successfully send a dominant bit in the first bit of the ACK field. The second bit of the ACK field is recessive and called as ACK delimiter. Then, the transmitter continues with seven more recessive bits as the end of frame field before 3 recessive bits as inter frame spacing (IFS) that takes place before a new frame can be transmitted.

It has to be noted that during the arbitration and ACK fields, multiple nodes can access the bus by sending different bit values. However, the parts of the CAN frame where falling edges on the CAN bus can be generated only by a single node are highlighted in white in Fig. 2.2 and 2.1.

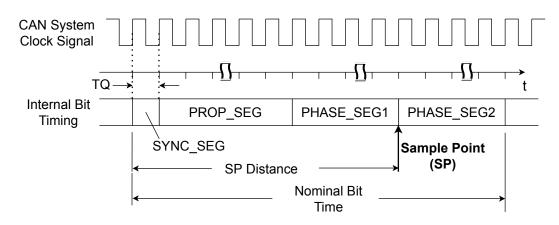

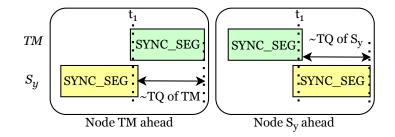

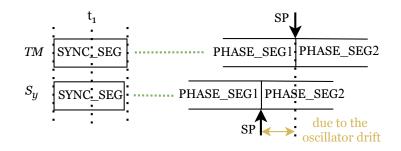

## 2.1.3 CAN Bit Timing

The CAN controller of each node maintains a CAN system clock. The CAN system clock signal is generally derived from a clock oscillator (CO) and its period is named as Time Quantum (TQ). Writing  $f_{CO,N}$  and  $T_{CO,N}$  for the nominal CO frequency and period, respectively, the nominal duration  $T_{TQ,N}$  of a TQ is  $T_{TQ,N} = n_{TQ,N} \cdot T_{CO,N}$ .

The CAN bit timing is organized in four segments denoted as SYNC\_SEG, PROP\_SEG, PHASE\_SEG1 and PHASE\_SEG2 as illustrated in Fig. 2.3. For each CAN node N, the length of each segment is given as a number of TQs, which is fixed during runtime and whose range of values is specified in the CAN standard [4].

The TQs are counted by a TQ counter (TQC) and the SYNC\_SEG consists of one TQ and PROP\_SEG, PHASE\_SEG1 and PHASE\_SEG2 can be programmed from 1 up to 8 TQs [4]. Thus, the minimum possible length of one TQ is one twenty-fifth of the nominal bit time. Each CAN node samples the bus value at the sample point (SP) and the ratio of the SP distance to the nominal bit time is advised to be around 87.5% [38].

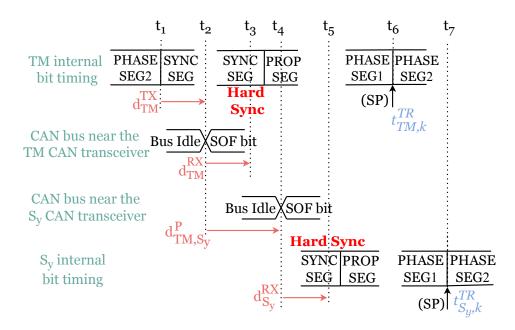

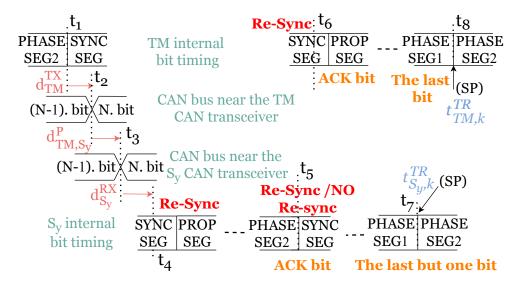

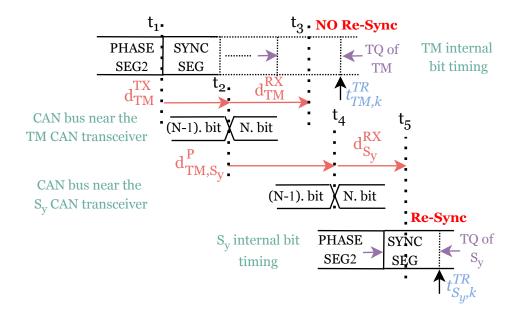

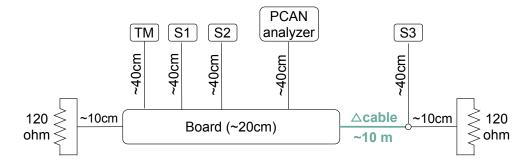

There are two internal bit timing synchronization mechanisms on CAN [4] within the CAN controller. In this way, the successful message transfer is provided by CAN protocol even though CAN nodes do not send and receive the bits in a synchronous way. Hard synchronization is realized at the beginning of a CAN message such that all nodes observing a falling edge when the bus is idle restart their internal bit timing

Figure 2.3: CAN bit segments.

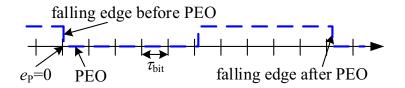

with SYNC\_SEG. That is, all nodes restart their TQC as 1 whenever they detect a SoF bit on the bus. Furthermore, the nodes apply re-synchronization during the message transmission when they receive a falling edge different from SoF bit on the bus. We write  $Q_{F,N}$  for the value of the TQC, where CAN node N observes a falling edge and  $\#_{TQ,N}$  for the total number of TQs in node N per one bit. Hereby, TQC counts from 1 to  $\#_{TQ,N}$  and returns to 1 after it reaches to  $\#_{TQ,N}$ , unless an internal bit timing synchronization is performed. Then, the phase error

$$e_{\mathrm{P},N} = \begin{cases} Q_{\mathrm{F},N} - 1 & \text{if falling edge is after SYNC\_SEG} \\ Q_{\mathrm{F},N} - 1 - \#_{\mathrm{TQ},N} & \text{otherwise} \end{cases}$$

(2.1)

captures the deviation of  $Q_{F,N}$  from TQC=1 (SYNC\_SEG). That is, based on the value of  $e_{P,N}$ , re-synchronization shortens PHASE2 of N by  $|e_{P,N}|$  if  $e_{P,N} < 0$  (the CO frequency of N is slow compared to the transmitter node) and lengthens PHASE1 by  $e_{P,N}$  if  $e_{P,N} > 0$  (the CO frequency of N is fast compared to the transmitter node). Hereby, enough re-synchronization instants (falling edges) during a CAN message are provided by the bit stuffing mechanism, which adds a bit of the opposite value after five consecutive bits with the same value. The correction amount is limited by the configurable re-synchronization jump width (RJW). Only a node transmitting a '0' bit does not perform re-synchronization of re-synchronization with a falling edge created by itself. It has to be emphasized that the bit timing mechanism on CAN only provides synchronization relative to the SoF bit of each CAN frame and cannot directly be used for CS of LCs of different CAN nodes.

#### 2.1.4 CAN FD Protocol

To improve the bandwidth of current CAN bus, BOSCH has introduced a new high bandwidth CAN bus called CAN FD in 2012 [16] through two major improvements: 1) increase of bit rate (more than 1 Mbps) and 2) increase of payload sizes (up to 64 bytes). CAN FD is standardized internationally in ISO 11898-1:2015 and it supports higher bit rates in a part of the data frame. Hereby, the CAN-FD controllers can also take part in standard CAN communication since the new CAN-FD frame formats make use of the reserved bits on CAN.

Figure 2.4: CAN-FD frame - standard format (11 bit ID).

In the standard CAN-FD frame (with 11 bit ID) as seen in Fig. 2.4, extended data length (EDL) bit is transmitted as a recessive bit after the IDE bit. Moreover, the RTR bit in CAN frame is replaced with a dominant reserved r1 bit since there are not CAN-FD remote frames. EDL bit is used to differentiate the CAN and CAN-FD frames since r0 bit in CAN frames are sent as a dominant bit unlike the EDL in CAN-FD. Then, a reserved r0 bit follows the EDL bit in the CAN-FD frame. Afterwards, bit rate switch (BRS) bit is sent. If the value of BRS is recessive, faster bit rate is applied during the data transmission phase. However, the same bit rate is used during the data transmission and arbitration phase, if its value is dominant. The duration before the BRS bit and after the CRC delimiter bit is named as the arbitration phase in CAN-FD and the same bit rates with CAN are supported. On the contrary, during the data transmission phase bit rates higher than 1 Mbps are supported by CAN-FD.

The extended CAN-FD frame is also presented in Fig. 2.5 where EDL bit is sent after reserved r1 bit which takes place instead of the RTR bit in the extended CAN frame.

The remaining bits after the EDL bit are exactly the same in standard and extended CAN-FD frames and have similar functions that are described for CAN messages in Section 2.1.2. Differently, the length of the CRC sequence can be 15, 17 or 21

Figure 2.5: CAN-FD frame - extended format (29 bit ID).

bits in CAN-FD. Furthermore, CAN-FD frames can transmit payload up to 64bytes, different from CAN frames. Thus, the DLC values from 9 to 15 (in binary) are defined in CAN-FD for payload lengths of 12, 16, 20, 24, 32, 48 and 64 bytes respectively. The DLC values from 0 to 8 (in binary) are still represent the payloads from 0 to 8 bytes like CAN.

After installation of the nodes applying CAN-FD that enables higher bit rates, it is seen in practice that the existing high-speed CAN transceivers achieve bit rates of 2 Mbps with a linear network topology and bit rates of 5 Mbps with a point-to-point communication. Different from the existing high-speed CAN transceivers, the bit rates up to 5 Mbps is achieved with signal improvement capability (SIC) transceivers even on networks that follow star topology with long stub lines. Thus, SIC transceivers allow building more complex network topologies at higher communication bit rates since it reduces the ringing effects that are caused by reflections on a network. Therefore, the sampling of bits gets more robust when SIC transceivers are used. Moreover, CAN in Automation (CiA) has released the CiA 601-4 standard proposal specifying the ringing suppression in CAN FD star and hybrid topology networks by using CAN SIC transceivers [39].

# 2.1.5 CAN XL Protocol

The future of CAN might also offer interesting potentials. The next generation of CAN will be CAN XL [34] whose development process is still ongoing. This version will offer data rates more than 10 Mbps and a significantly enlarged payload of up to 2048 byte, while retaining the media access scheme of CAN and backward compatibility with the previous CAN FD version [40].

#### 2.2 Clock Synchronization on CAN and Related Work

#### 2.2.1 Local Clock and Clock Drift

The local time of a CAN node is commonly realized by a LC, which consists of a hardware register (HR) that is incremented using periodic ticks from a CO [41, 42]. The resolution of node N's LC is defined by the nominal frequency  $f_{\text{CO},N} = 1/T_{\text{CO},N}$  of the CO and the number of CO ticks  $n_{\text{HR},N}$  per HR increment. That is, one tick of the HR corresponds to a time duration  $T_N = n_{\text{HR},N} \cdot T_{\text{CO},N} = n_{\text{HR},N}/f_{\text{CO},N}$ . We write  $N_N(t)$  for the value of node N's HR value at time t. The maximum value of  $N_N$  depends on the width of the hardware register and hence determines the maximum time represented by the LC.

It has to be noted that the LCs of different CAN nodes are not expected to hold the same time value since two different COs cannot provide periodical ticks with exactly the same rate [41]. In particular, the actual frequency of a CO generally deviates from  $f_{CO,N}$  due to short term, long term and environmental frequency instability effects [43, 44]. Measuring such deviations in ppm (parts per million), the frequency instability is in the order of 50 ppm for fabrication errors, 5 ppm per year for aging and 150 ppm (within -40°C and 125°C) for temperature variations [45]. That is, the actual CO frequency  $f_N$  of node N is time-varying and can be written in the form

$$f_N(t) = f_{\text{CO},N} \cdot (1 + k_{\text{IA},N} + k_{\text{LTI},N} + k_{\text{EI},N}(t)).$$

(2.2)

Here,  $k_{\text{IA},N}$  is the initial accuracy (IA) based on fabrication errors,  $k_{\text{LTI},N}$  is the long term frequency instability (LTI) due to aging and  $k_{\text{EI},N}(t)$  represents the timevarying environmental instability (EI) depending on temperature, pressure, humidity and noise from the voltage supply [41, 46, 47]. Then, the local time  $c_N(t)$  of node N's LC is determined by

$$c_N(t) = N_N(t) \cdot T_N = \left\lfloor \int_0^t \frac{f_N(\tau)}{n_{\mathrm{HR},N}} d\tau \right\rfloor \cdot T_N,$$

(2.3)

whereby  $\lfloor \bullet \rfloor$  is the floor operation. Due to the frequency instability, the LC of each CAN node diverges from real time.

We define the clock difference of node N with respect to a reference clock (RC)

which is accepted to equal to the real time as

$$\Delta c_N(t) = c_N(t) - c_{\rm RC}(t). \tag{2.4}$$

When we consider that real time is given by the LC value  $c_{\text{TM}}$  of a given TM, it holds that  $c_{\text{RC}}(t) = c_{\text{TM}}(t)$ . Accordingly, the clock offset of node N in HR ticks is  $\Delta N_N(t) = N_N(t) - \left\lfloor \frac{c_{\text{TM}}(t)}{T_N} \right\rfloor$ . Then, the maximum value  $\max_t |\Delta c_N(t)|$  describes the accuracy of the LC  $c_N$ . Furthermore, the clock drift  $d_N$  of node N is the rate of change of  $\Delta c_N(t)$  and can be approximated for small values of  $\tau$  as

$$d_N(t) = \frac{d}{dt}(\Delta c_N(t)) \approx \frac{\Delta c_N(t) - \Delta c_N(t-\tau)}{\tau}.$$

(2.5)

## 2.2.2 Clock Synchronization on CAN

Modern vehicles that have to be considered as safety-critical cyber-physical systems, require highly accurate CS among their distributed computing devices to synchronize actions of different nodes [48, 49, 1, 19, 20]. Since CAN is the predominant in-vehicle communication bus, it is highly relevant to support CS for CAN which does not provide a global time notion between the nodes [50]. Moreover, accurate global clocks enable more deterministic medium access and hence decrease message latencies on CAN [51, 35, 52].

Network Time Protocol (NTP) and IEEE 1588 Precision Time Protocol (PTP) [53] are the most distinguished time synchronization protocols for computer networks. The proposed protocols have been also used for different communication networks with modifications due to the differences between the network structures [54]. For example, EtherCAT utilize Distributed Clock which is similar to PTP [55]. Moreover, IEEE 802.1AS time synchronization standard [56] which sends synchronization data based on a PTP profile was specified for IEEE 802 networks. Additionally, the IEEE 802.1AS was analyzed for Ethernet based in-vehicle networks in [57]. However, the low-cost CAN cannot rely on those CS protocols due to its network structure and limited bandwidth [18, 19, 20].

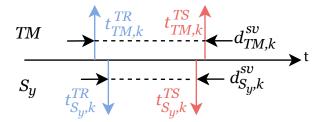

Existing CS algorithms for CAN use timestamps that are taken simultaneously by all nodes on a CAN bus. A time master (TM) node (infrequently) transmits periodic RMs

with its timestamp. Slave nodes perform offset correction whenever receiving a RM and optionally drift correction between RM receptions. That is, the clock accuracy of CS algorithms for CAN directly depends on the quality of the timestamps.

Without a dedicated hardware timestamping unit, the quality of the timestamps is mostly determined by inevitable software jitters until the time instant when the timer value is recorded as a timestamp. On the contrary, hardware timestamps provide more promising performance for CS applications at the expense of a dedicated hardware unit that takes timestamps with a known and constant delay. Hardware timestamping units are not very common in already deployed CAN controllers due to the lack of its standardization in the past. However, CiA 603 document which defines the hardware timestamps for CS on CAN was published in 2017 [58]. After its standardization, Bosch developed its M CAN CAN IP with an extra hardware timestamping unit (TSU) which is able to take hardware timestamps at the SoF bit and also at the end of a frame. Moreover, there are some CAN modules [59, 60] that support hardware timestamps even before the standardization of the hardware timestamps for CS applications on CAN. However, it has to be noted that the practicability of the existing timestamping units in [59, 60] is questionable for having precise timestamps since the timestamp width is only 16 bit and the resolution can not be better than one CAN bit time.

Another important unit is the timer module for CS applications. In the cost sensitive automotive domain, the MCUs generally do not have timer modules with a property of the rate correction. Thus, the rate correction must be handled in software by adding/-subtracting 1 tick from the timer value manually. Accordingly, the timer value must be read first. Then, the new value should be calculated and should be written into the timer register. Furthermore, the time duration between the read and write functions should be compensated while deciding the new value for the timer register. Although special attention should be performed in software to compensate the time duration, the rate correction seems practicable in software with standard timer modules at the expense of an extra software load. On the contrary, some commercial off-the-shelf (COTS) MCUs [61] already provides an IEEE 1588-enabled Ethernet interface with a high precision timer module with rate correction. In the work [19], the usage of the timer's rate capability for the purpose of CS on CAN is presented.

Considering the properties of the commonly used MCUs in the automotive industry, the timer modules with rate correction and CiA 603 compatible hardware timestamping units are considered as extra hardware support in this thesis. Additionally, the CS implementations on CAN which do not require the extra hardware support is called as software-based CS (SW-CS) methods. Hereby, it has to be noted that similar classification is also followed in the literature [40, 43].

The underlying algorithm for several SW-CS methods that are based on timestamps inside the periodic RMs is proposed in [28] in 1994. It can be implemented in software without requiring any extra hardware support and uses one RM per synchronization round. Furthermore, the AUTOSAR-compliant CS method [27] that is the simplified version of PTP has been introduced for CAN. It proposes using two successive RMs as SYNC and Follow Up (FUP) to achieve better CS at the expense of the extra bandwidth consumption for CS messages. It has to be noted that the AUTOSAR CS method is also realizable on software. In a recent work [40], the AUTOSAR CS method is implemented on software with an improvement that aims to increase the software timestamping quality by using filtering. Moreover, the rate correction depending on the timestamps is also applied together with the offset correction. In this paper, the best clock accuracy that is reported experimentally is in the order of  $50 \,\mu s$  when synchronization round is 0.1 ms.

On the contrary, the hardware based CS methods have advantages over software based CS implementations for example better timestamping quality and easiness at applying rate correction. In 1994, a special hardware mechanism is proposed by Turski [62] to take hardware timestamps at the SoF bit of a RM. Additionally, the same approach is also adopted in orthogonal clock subsystem (OCS) for CAN [43]. In order to realize those methods, the existing CAN controllers have to be modified such that they signal the instant of the SoF bit to trigger taking the timestamps. Moreover, TTCAN level 2 provides a global clock among the CAN nodes and achieves an accuracy in the order of one CAN bit time. TTCAN CS realization also depends on specific hardware units that means modifications of the CAN protocol. Additionally, in a recent work [19], the SYNC and FUP messages are used similar to the AUTOSAR CS method and rate correction is applied by using the IEEE 1588 timer with rate correction for the purpose of CS on CAN. Moreover, in the same work, a PI control loop is introduced

to adjust the timer's clock rate. However, the design details about the controller is missing in the paper.

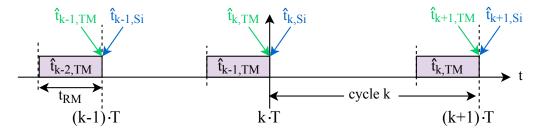

## 2.2.3 Gergeleit's Method

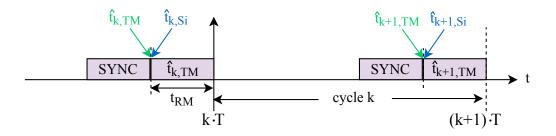

The RM transmission scheme compatible to the SW-CS method by Gergeleit [28] is illustrated in Fig. 2.6. RMs (gray boxes) with the message duration  $t_{\rm RM}$  are sent by TM with a period T and received synchronously by any CAN node (slaves and Master) at  $t_k = k \cdot T$ , k = 0, 1, ... With each RM reception at  $t_k$ , TM and each slave Si take a timestamp of their respective LC  $\hat{t}_{k,\rm TM}$  and  $\hat{t}_{k,\rm Si}$ . TM then transmits  $\hat{t}_{k,\rm TM}$  with the next RM such that each slave Si receives this timestamp at  $t_{k+1} = (k + 1) \cdot T$ . The difference between the received value  $\hat{t}_{k,\rm TM}$  and the stored value  $\hat{t}_{k,\rm Si}$  is then used to perform the clock update

$$c_{\rm Si}(t_{k+1}^+) = c_{\rm Si}(t_{k+1}^-) + \hat{t}_{k,\rm TM} - \hat{t}_{k,\rm Si}.$$

(2.6)

Here,  $c_{Si}(t_{k+1}^-)$  and  $c_{Si}(t_{k+1}^+)$  represent the LC value of Si before and after the update, respectively.

To this end, the application of Gergeleit's method requires the transmission of one RM in each synchronization cycle k.

Figure 2.6: Illustration of RM transmissions compatible to Gergeleit's method.

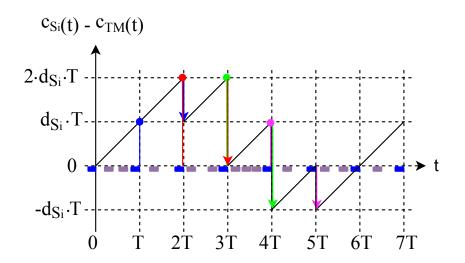

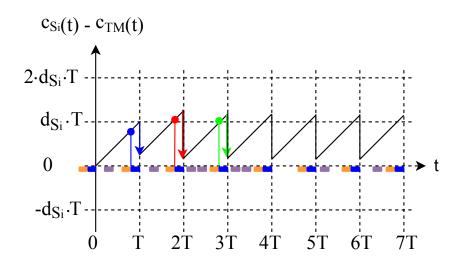

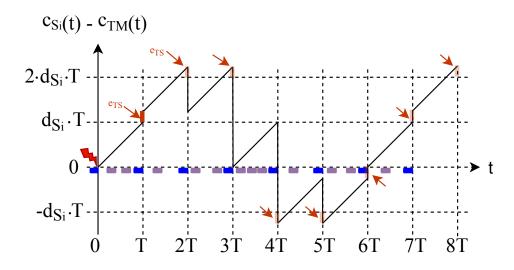

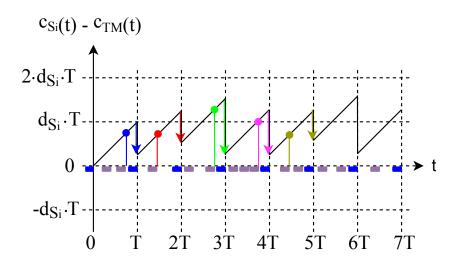

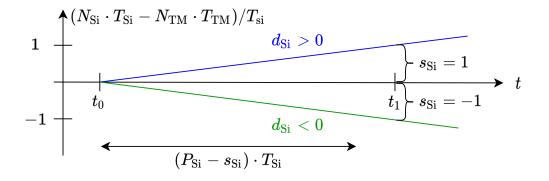

The clock difference when the method in [28] is followed is presented in Fig. 2.7. Specifically, the figure shows the clock difference of the TM and a slave node Si. The period of RMs is T and the drift of the Si clock is  $d_{Si}$  with respect to the clock of TM. Thus, a time difference of  $d_{Si} \cdot T$  is observed between two successive RMs. The blue boxes in Fig. 2.7 represent the RMs and the gray ones are regular messages transmitted on the bus.

Figure 2.7: Illustration of clock difference when Gergeleit's method is followed.

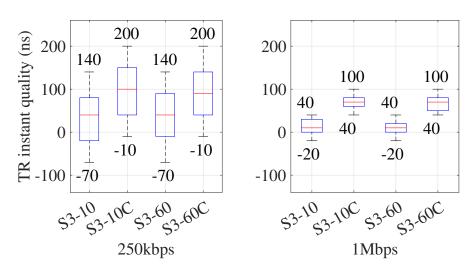

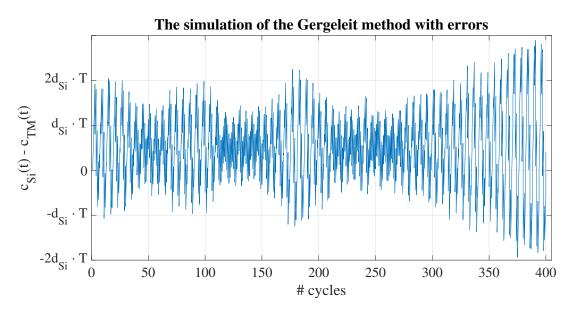

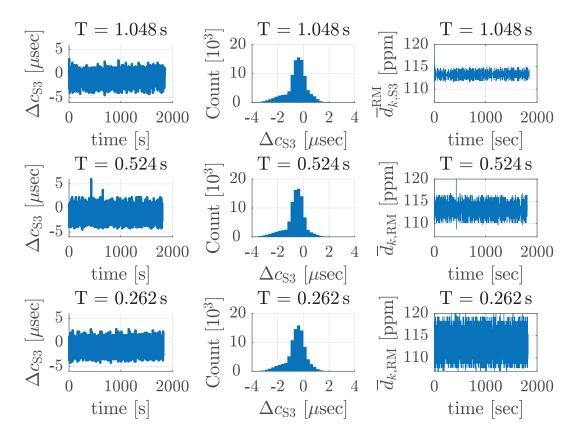

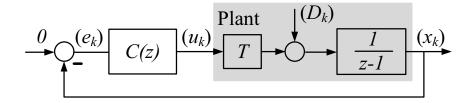

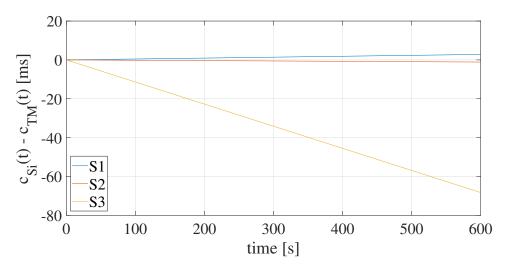

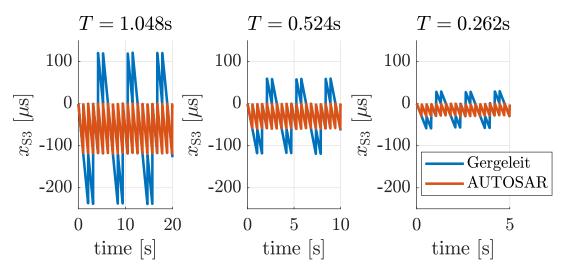

For example, at time  $2 \cdot T$  the slave node makes a clock correction according to the timestamp taken at time T. Since the clock difference at T is  $d_{Si} \cdot T$ , the slave clock value is reduced by this value at time  $2 \cdot T$ . It can be seen that the maximum clock difference is  $d_{Si} \cdot 2 \cdot T$ , which equals the theoretical upper limit guaranteed by the method in [28]. In addition, it has to be emphasized that the method in [28] cannot always fully compensate the actual clock difference right before the current RM. This is due to the additional clock drift between taking the timestamp of the previous RM and sending the timestamp in the current RM.