## COMPACT AND FLEXIBLE NTRU IMPLEMENTATION ON FPGA

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF INFORMATICS OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

SINAN EMIR KORKMAZ

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN CYBER SECURITY

AUGUST 2022

Approval of the thesis:

## COMPACT AND FLEXIBLE NTRU IMPLEMENTATION ON FPGA

submitted by SINAN EMIR KORKMAZ in partial fulfillment of the requirements for the degree of Master of Science in Cyber Security Department, Middle East Technical University by,

Prof. Dr. Deniz ZEYREK BOZŞAHİN Dean, Graduate School of Graduate School of Informatics

Assoc. Prof. Dr. Cihangir TEZCAN Head of Department, **Cyber Security**

Assoc. Prof. Dr. Cihangir TEZCAN Supervisor, **Cyber Security Department, METU**

### **Examining Committee Members:**

Prof. Dr. Ali Aydın SELÇUK Computer Engineering Dept., TOBB ETÜ

Assoc. Prof. Dr. Cihangir TEZCAN Cyber Security Dept., METU

Prof. Dr. Banu Günel KILIÇ Information Systems Dept., METU

Date: 23.08.2022

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Surname: Sinan Emir KORKMAZ

Signature :

#### ABSTRACT

#### COMPACT AND FLEXIBLE NTRU IMPLEMENTATION ON FPGA

KORKMAZ, Sinan Emir M.S., Department of Cyber Security Supervisor: Assoc. Prof. Dr. Cihangir TEZCAN

August 2022, 78 pages

At the dawn of quantum computing, our most trusted cryptosystems are at significant risk. All vastly used and standardized public-key algorithms such as RSA and ECC were designed to withstand the attacks from classical computers by using integer factorization and discrete logarithm problems. However, quantum computers can generate the whole solution space for these problems that contains all the possible keys and reduce it to the correct key in polynomial time. Therefore, we need to start using a new public key encryption algorithm before the first full-scale quantum computer starts to work. To select this new algorithm, NIST organized a competition in 2016. They received 59 submissions in the field of encryption. With the passing rounds, algorithms are heavily investigated according to security and performance metrics by researchers all around the globe.

In this thesis work, we focused on the NTRU, one of the third-round candidate algorithms. This lattice-based algorithm uses Shortest Vector Problem as the encryption function and has the ability to provide secrecy against quantum computers. We worked on the hardware implementation of the NTRU. By implementing an algorithm on FPGA, we can benefit from gate-level parallelism and design algorithm-specific logical blocks. We implemented encryption, decryption, and data processing modules with our proposed improvements. The key generation module is not implemented because generated keys can be loaded manually and have a long life of usage. Our design focuses on resource optimization and flexibility. These properties enabled us to provide a suitable solution for low-power embedded network devices.

Keywords: NTRU, FPGA, Post Quantum Cryptography, Public Key Cryptography, Cryptography

## NTRU ALGORİTMASININ FPGA ÜZERİNDE GERÇEKLENMESİ

KORKMAZ, Sinan Emir Yüksek Lisans, Siber Güvenlik Bölümü Tez Yöneticisi: Doç. Dr. Cihangir TEZCAN

Ağustos 2022, 78 sayfa

Kuantum bilgisayarların artan bir ivme ile geliştiği günümüzde, güvenli iletişimimizi sağlayan açık anatarlı şifreleme algoritmaları tehdit altındadır. Şu an kullandığımız, güvenirliğini ispat ederek standartlaşmış RSA ve ECC gibi algoritmaların klasik bilgisayar yapıları tarafından yapılan saldırılara karşı dayanımı yüksektir. Bu yeteneklerini çarpanlara ayırma ve ayrık logaritma problemleri sayesinde kazanmaktadırlar. Fakat, sahip oldukları eşsiz paralel işlem yeteneği ile kuantum bilgisayarlar bu algoritmalara ait bütün çözüm olasılıklarını aynı anda oluşturup doğru olana polinom zamanda indirgeyebilirler. Bu sebeple yeni bir açık anahtarlı şifreleme algoritmasına geçiş yapmamız gerekmektedir. Bu geçişi standardize edebilmek için American Standartlar ve Teknoloji Enstitüsü (NIST) bir yarışma düzenlemektedir. 2016 yılında başlayan ve 59 algoritmanın şifreleme alanında katıldığı bu yarışmanın her turunda katılımcı algoritmalarin güvenlik ve performans yetenekleri dünyanın her yerindeki bağımsız araştırmacılar tarafından incelenmektedir.

Bu tez çalışmasında 3. tur katılımcısı NTRU algoritması incelenmiş olup, alanda programlanabilir kapı dizisi (FPGA) üzerinde gerçeklenmiştir. NTRU algoritması çok boyutlu kafes yapısına sahiptir ve en kısa vektör sorusunu şifreleme fonksiyonu olarak kullanır. Bu sayede kuantum bilgisayarlara karşı güvenlik sağlayabilmektedir. Donanım üzerinde yapılan tasarımlar kapı seviyesinde paralelleştirme ve özel tasarlanmış mantıksal yapılardan faydalanabilirler. Şifreleme, şifrenin çözülmesi ve bilgilerin paketlenmesi işlemleri önerilen iyileştirmelerle gerçeklenmiştir. Şifre üretimi, üretilen şifrelerin uzun ömürleri ve elle yüklenebilecek olmaları sebebiyle tasarıma dahil edilmemiştir. Tasarım düşük kaynak tüketimi ve esneklik kriterlerine göre yapılmıştır. Bu kriterlere uyum sağlayarak ağ üzerinde çalışan düşük güçlü gömülü cihazlar için uygun bir çözüm oluşturulmuştur.

Anahtar Kelimeler: NTRU, FPGA, Açık Anahtarlı Şifreleme, Kuantum Sonrası Kriptografi, Şifreleme to my family

### ACKNOWLEDGMENTS

I wish to express my sincere gratitude to my thesis advisor Assist. Prof. Dr. Cihangir TEZCAN for the precious guidance and generous help that makes this work possible. Also, I want to especially thank him for introducing me to the world of Cryptography.

I want to thank my family and friends that support me unconditionally in every situation and give me the strength to continue.

I would like to thank TUALCOM for supporting this thesis. Working here is an excellent adventure as I am gaining new skills and gathering more knowledge.

## TABLE OF CONTENTS

| ABSTRACT                                                   |

|------------------------------------------------------------|

| ÖZ                                                         |

| ACKNOWLEDGMENTS                                            |

| TABLE OF CONTENTS                                          |

| LIST OF TABLES                                             |

| LIST OF FIGURES                                            |

| LIST OF ALGORITHMS                                         |

| LIST OF ABBREVIATIONS                                      |

| CHAPTERS                                                   |

| 1 INTRODUCTION                                             |

| 1.1       NIST Post Quantum Cryptography Challenge       2 |

| 1.2 NTRU                                                   |

| 1.3 Effects of Quantum Computers on Cryptography           |

| 1.4 Reasons to work on FPGA                                |

| 1.5 Other NTRU Implementations                             |

| 1.6 Our Contribution                                       |

| 2 QUANTUM COMPUTING                                        |

|   | 2.1  | Grover's Search Algorithm                | 17 |

|---|------|------------------------------------------|----|

|   | 2.2  | Shor's Algorithm                         | 18 |

| 3 | NTRU | J                                        | 19 |

|   | 3.1  | Lattice                                  | 20 |

|   | 3.2  | Shortest Vector Problem                  | 21 |

|   | 3.3  | Galois Field                             | 21 |

|   | 3.4  | Extended Euclidean Algorithm             | 22 |

|   | 3.5  | Key Generation                           | 24 |

|   | 3.6  | Encryption                               | 25 |

|   | 3.7  | Decryption                               | 27 |

| 4 | FIEL | D-PROGRAMMABLE GATE ARRAY                | 29 |

|   | 4.1  | Side-Channel Attack                      | 37 |

| 5 | IMPL | EMENTATION                               | 39 |

|   | 5.1  | Memory Scheme                            | 41 |

|   | 5.2  | Standalone Encryption                    | 43 |

|   | 5.3  | Standalone Decryption                    | 46 |

|   | 5.4  | Combined Encryption and Decryption       | 48 |

|   | 5.5  | Modulo by 3 Module                       | 51 |

|   | 5.6  | Modulo by 5 Module                       | 52 |

|   | 5.7  | Modulo by q                              | 53 |

|   | 5.8  | Serialization and Deserialization Module | 53 |

|   | 5    | .8.1 Switch Matrix                       | 54 |

|   | 5    | .8.2 Serialization                       | 55 |

|   | 5     | .3 Deserialization    | 5 | 58 |

|---|-------|-----------------------|---|----|

| 6 | RESU  | TS                    |   | 51 |

|   | 6.1   | Limitations           |   | 51 |

|   | 6.2   | mplementation Results |   | 52 |

|   | 6.3   | Siming Results        |   | 54 |

| 7 | CON   | LUSION                |   | 57 |

|   | 7.1   | Future Work           |   | 58 |

| R | EFERE | CES                   |   | 59 |

| А | PPENI | CES                   | 7 | 78 |

## LIST OF TABLES

## TABLES

| Table 1.1 | NIST PQC Timeline                                                                                         | 2  |

|-----------|-----------------------------------------------------------------------------------------------------------|----|

| Table 1.2 | NIST PQC Round 1 Submissions                                                                              | 3  |

| Table 1.3 | NIST PQC Round 2 Submissions                                                                              | 6  |

| Table 1.4 | NIST PQC Round 3 Submissions                                                                              | 6  |

|           | NTRUEncrypt security estimation according to Hoffstein in his 2017<br>e                                   | 11 |

|           | Quantum computer vs. classical computer comparison for breaking and required resources according to Orman | 15 |

|           | Required time for a quantum computer to break ECDLP and re-<br>d resources according to Orman             | 15 |

| Table 3.1 | Some of the recommended parameters                                                                        | 19 |

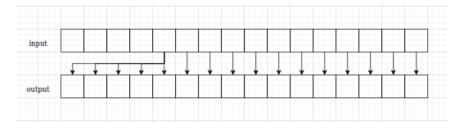

| Table 5.1 | Serialization example                                                                                     | 58 |

| Table 5.2 | Deserialization example                                                                                   | 59 |

| Table 6.1 | Possible target FPGAs from Xilinx and their resources                                                     | 61 |

| Table 6.2 | Possible target FPGAs from Intel and their resources                                                      | 62 |

| Table 6.3 | Resource utilizations of our modules                                                                      | 62 |

Table 6.4 Resource comparison between different implementations

63

# LIST OF FIGURES

## FIGURES

| Figure 1.1 | Unwanted information reveal                            | 8  |

|------------|--------------------------------------------------------|----|

| Figure 2.1 | Basic diagram of a quantum Computer                    | 14 |

| Figure 2.2 | Maximum utilized qbits in single system vs. years      | 16 |

| Figure 2.3 | Visual Representation of the Grover's Search Algorithm | 17 |

| Figure 3.1 | NTRU options security comparison                       | 20 |

| Figure 3.2 | Lattice Problems                                       | 21 |

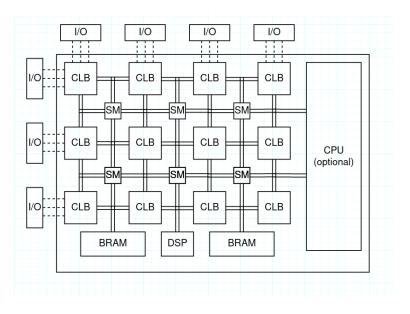

| Figure 4.1 | FPGA model representation                              | 29 |

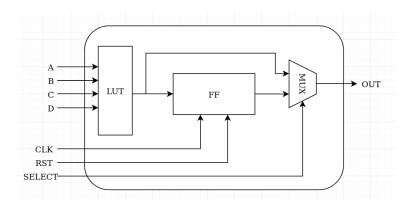

| Figure 4.2 | Simple model of CLB                                    | 30 |

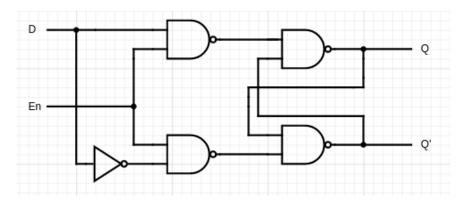

| Figure 4.3 | Inside of the Data Flip Flop                           | 30 |

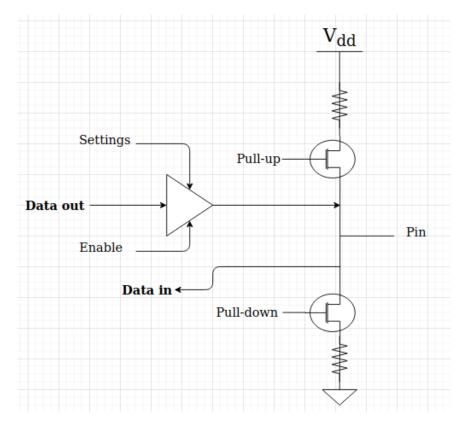

| Figure 4.4 | Basic electronic design of the FPGA IO port            | 31 |

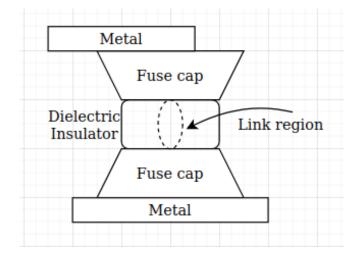

| Figure 4.5 | Anti fuse example                                      | 33 |

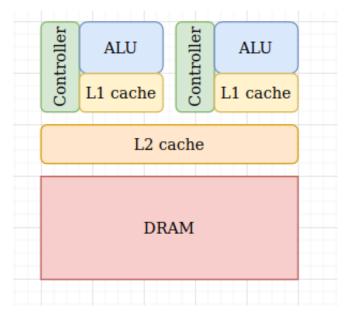

| Figure 4.6 | Sample CPU architecture                                | 34 |

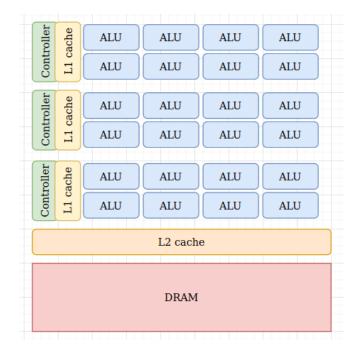

| Figure 4.7 | Sample GPU architecture                                | 35 |

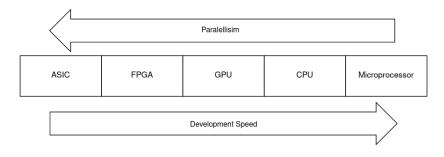

| Figure 4.8 | Parallelism vs. development Speed                      | 36 |

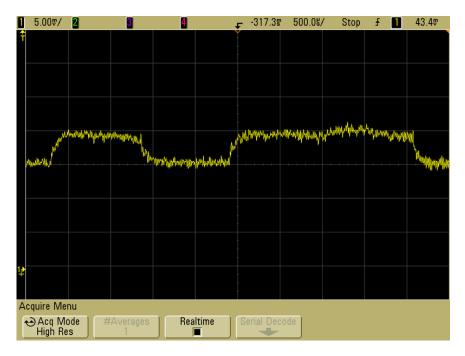

| Figure 4.9 | Current drawn while processing                         | 38 |

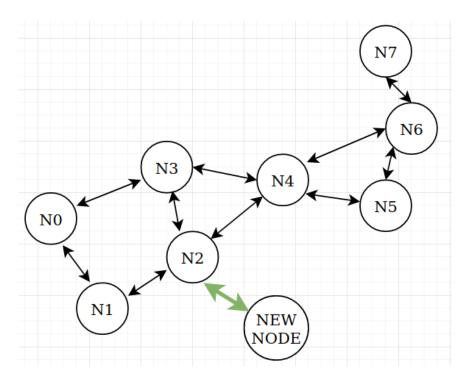

| Figure 5.1          | Representation of Mesh Network                                                                             | 40 |

|---------------------|------------------------------------------------------------------------------------------------------------|----|

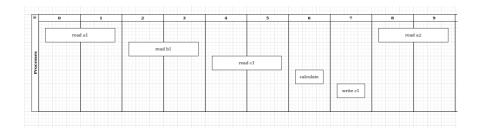

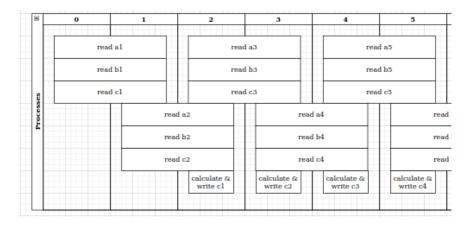

| Figure 5.2          | Serial and blocking operations                                                                             | 41 |

| Figure 5.3          | Parallel and pipelined operations                                                                          | 41 |

| Figure 5.4          | Data plan in the first RAM                                                                                 | 42 |

| Figure 5.5          | Contents of the memory while encrypting                                                                    | 44 |

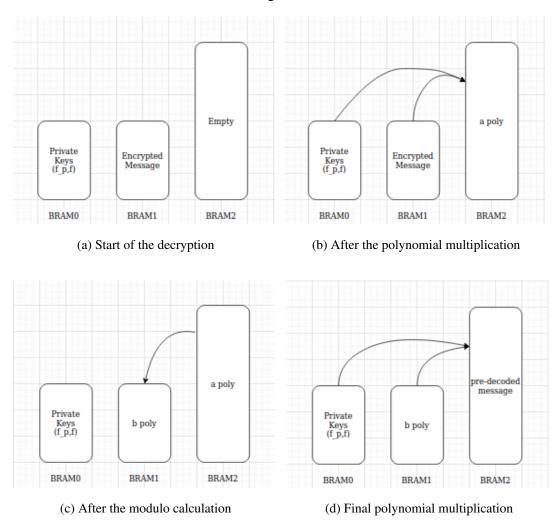

| Figure 5.6          | Contents of the memory while decrypting                                                                    | 46 |

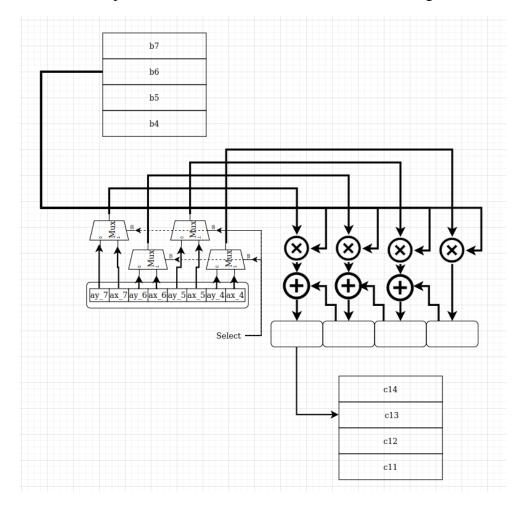

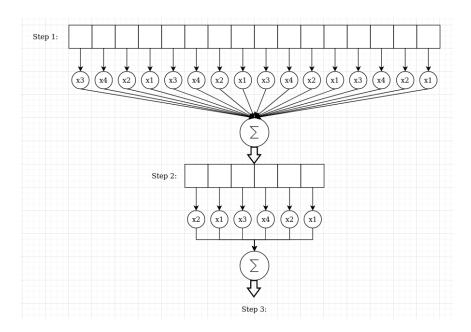

| Figure 5.7          | Polynomial calculation architecture                                                                        | 49 |

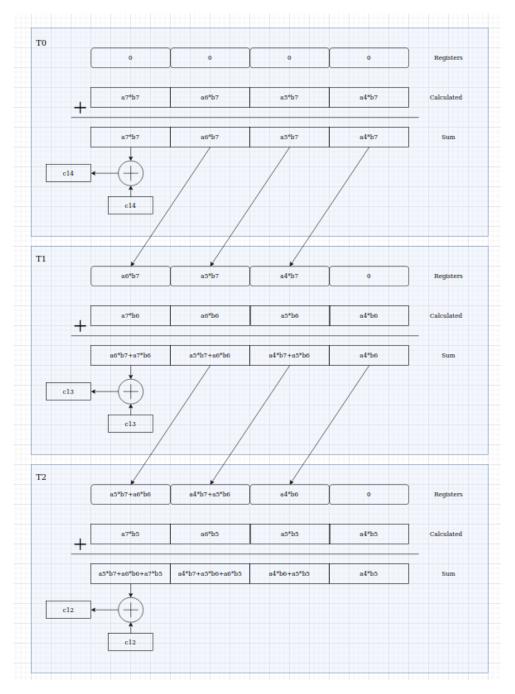

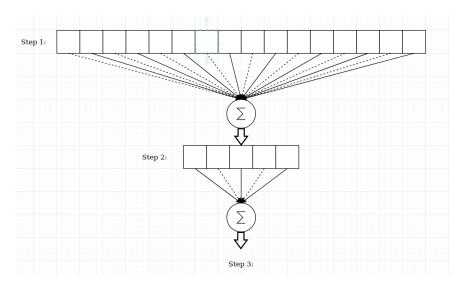

| Figure 5.8          | Shifter and adder module's contents with respect to time                                                   | 50 |

| Figure 5.9          | Mod3 module architecture                                                                                   | 52 |

| Figure 5.10         | Mod5 module architecture                                                                                   | 53 |

| Figure 5.11         | Mod q architecture                                                                                         | 53 |

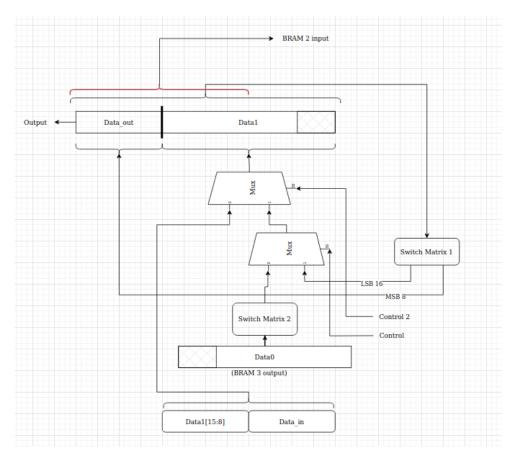

| Figure 5.12         | Combined Serialization and Deserialization Architecture                                                    | 54 |

| Figure 5.13         | Switch matrix design to make adjustable shifters                                                           | 55 |

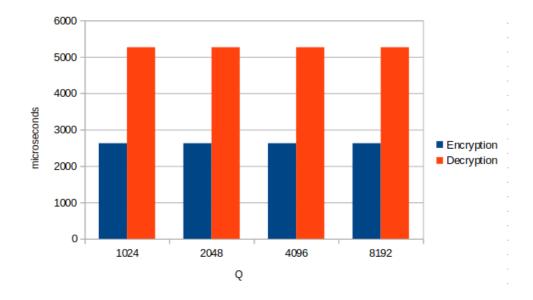

| Figure 6.1<br>sages | Visualization of time spent while encrypting and decrypting mes-<br>with respect to Q with a 100 MHz clock | 65 |

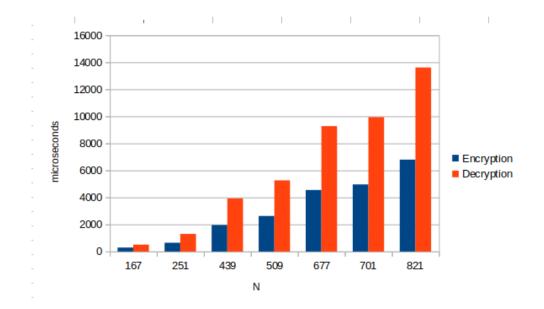

| Figure 6.2          | Visualization of time spent while encrypting and decrypting mes-                                           |    |

| sages               | with respect to N                                                                                          | 65 |

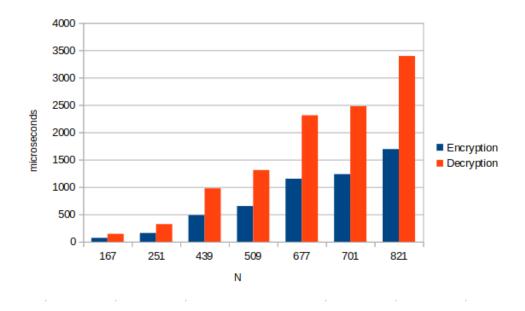

| Figure 6.3<br>combi | Visualization of time spent while encrypting and decrypting on ned architecture with respect to N          | 66 |

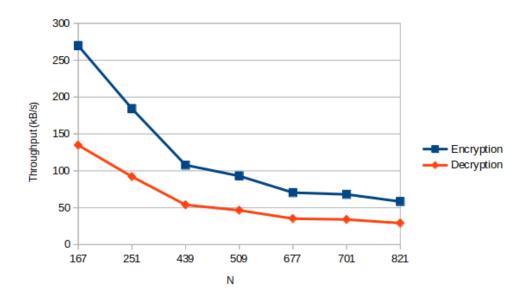

| Figure 6.4          | Throughput of encryption and decryption with respect to N                                                  | 66 |

## LIST OF ALGORITHMS

## ALGORITHMS

| Algorithm 1 | Extended Euclidean Algorithm      | 23 |

|-------------|-----------------------------------|----|

| Algorithm 2 | NTRU encryption algorithm on FPGA | 45 |

| Algorithm 3 | NTRU decryption algorithm on FPGA | 48 |

| Algorithm 4 | Serialization algorithm           | 57 |

| Algorithm 5 | Deserialization algorithm         | 60 |

# LIST OF ABBREVIATIONS

| ADC    | Analog to Digital Converter                           |

|--------|-------------------------------------------------------|

| AES    | Advanced Encryption Standard                          |

| ALM    | Adaptive Logic Modules                                |

| ALU    | Arithmetic Logic Unit                                 |

| ARM    | Advanced RISC Machines                                |

| ASCII  | American Standard Code for Information Interchange    |

| ASIC   | Application-Specific Integrated Circuit               |

| BRAM   | Block Random Access Memory                            |

| CISC   | Complex Instruction Set Computer                      |

| CLB    | Configurable Logic Block                              |

| CPU    | Central Processing Unit                               |

| CVP    | Closest Vector Problem                                |

| DAC    | Digital to Analog Converter                           |

| DFF    | Data Flip Flop                                        |

| DSP    | Digital Signal Processing                             |

| ECC    | Elliptic Curve Cryptography                           |

| EEA    | Extended Euclidean Algorithm                          |

| EEPROM | Electronically Erasable Programmable Read-Only Memory |

| EMI    | Electromagnetic Interference                          |

| FF     | Flip-Flop                                             |

| FPGA   | Field-Programmable Gate Array                         |

| GCD    | Greatest Common Divisor                               |

| GF     | Galois Field                                          |

| GPU    | Graphical Processing Unit                             |

|        |                                                       |

| HDL  | Hardware Description Language                  |

|------|------------------------------------------------|

| HSTL | High Speed Transceiver Logic                   |

| HSUL | High-Speed Unterminated Logic                  |

| I2C  | Inter-Integrated Circuit                       |

| IC   | Integrated Circuit                             |

| ΙΟ   | Input Output                                   |

| JTAG | Joint Test Action Group                        |

| KEM  | Key Exchange Mechanism                         |

| LSB  | Least Significant Bit                          |

| LUT  | Look-Up Table                                  |

| LVDS | Low Voltage Differential Signaling             |

| MSB  | Most Significant Bit                           |

| MUX  | Multiplexer                                    |

| NIST | National Institute of Standards and Technology |

| NTRU | Nth degree-Truncated Polynomial Ring Units     |

| PCI  | Peripheral Component Interconnect              |

| PLL  | Phase Locked Loop                              |

| qbit | Quantum bit                                    |

| QFT  | Quantum Fourier Transform                      |

| RAM  | Random Access Memory                           |

| RISC | Reduced Instruction Set Computer               |

| ROM  | Read Only Memory                               |

| RSA  | Rivest-Shamir-Adleman                          |

| RTOS | Real Time Operating System                     |

| SATA | Serial AT Attachment                           |

| SD   | Secure Digital                                 |

| SIMD | Single Instruction Multiple Data               |

|      |                                                |

| SISD  | Single Instruction Single Data              |

|-------|---------------------------------------------|

| SM    | Switch Matrix                               |

| SPI   | Serial Peripheral Interface                 |

| SRAM  | Static Random Access Memory                 |

| SSTL  | Stub Series Terminated Logic                |

| SVP   | Shortest Vector Problem                     |

| UART  | Universal Asynchronous Receiver-Transmitter |

| VHDL  | VHSIC Hardware Description Language         |

| VHSIC | Very High Speed Integrated Circuit          |

### **CHAPTER 1**

### **INTRODUCTION**

At the dawn of quantum computing, our most trusted cryptosystems are at significant risk. The level of secrecy reduction has to be addressed separately for different types of algorithms. Because while the effect of quantum computers on private key encryption algorithms may be ignored or easily overcome, it is catastrophic for the public key encryption algorithms.

Firstly, private key encryption algorithms such as Triple-DES and AES will lose their security level by half. An AES256 key attacked by a quantum computer can provide the same secrecy as an AES128 key attacked by a conventional computer (Bonnetain et al., 2019). By just increasing the key size, one can safely continue to use the current standard algorithms like AES. However, these algorithms need secret keys that have to be determined on a secure channel before communicating freely. In many real-life scenarios, having access to a medium that prevents eavesdropping or tampering is impossible.

Using a secret algorithm might come up to mind. Because even if the adversaries know the key, they will have no idea about how to use it. From a layman's perspective, we can ensure security by using a confidential algorithm. However, this security by obscurity approach is not accepted in many fields. According to the security assessments, the secret key has to be the only element that ensures secrecy in an open and well-known system. Using the security by obscurity approach keeps the attacker in the dark, but it will also keep the defenders in similar conditions. Without an open-source algorithm and open discussion platform like academia, the defenders cannot determine their algorithm's strengths and weaknesses. The current general practice for security is to use well-tested and standardized algorithms according to the secrecy needs. This practice is formalized by NIST by stating, "System security should not depend on the secrecy of the implementation or its components." (Scarfone et al., 2008)

Public key encryption algorithms are designed to communicate in an open world without any shared secret. Public key encryption algorithms use two different keys. One is shared with the world, and it can be used by anyone who wants to send a message to the key's owner. If this message is received by an adversary who knows the public key, there will not be a security breach because there is no practically possible way to extract the information from the encrypted message. This process can only be done by someone who knows the private key by using the trap function of the algorithm.

Increasing the key size to increase the security approach is impractical in the public

key cryptography algorithms while working against quantum computational devices. Because, in public key algorithms, we can change the time complexity of searching for the correct key by using quantum computers. However, in private key algorithms, the usage of quantum computers only enables us to make a reduction.

The underlying mechanism of quantum computers is storing many possibilities in their smallest units, which are named qbits, unlike the classical computers that can hold two possibilities in their bits. Quantum computers do not need to try the possible keys one by one while attacking an algorithm because they have the capability of working with multiple possibilities at the same time. By using Shor's Algorithm, quantum computers can generate a solution space containing all the possible keys and reduce it to the correct key in polynomial time for the problems of integer factorization and discrete logarithm. The polynomial time solution to our most used public key algorithms is the dead of the secrecy in today's communication practices. Therefore, we need to start using a new public key encryption algorithm before the first full-scale quantum computer is deployed.

## 1.1 NIST Post Quantum Cryptography Challenge

To select this new algorithm for standardization, NIST is organizing a competition. NIST Post Quantum Cryptography Competition was formally called for the proposals on January 03, 2017, and the deadline for round 1 submissions ended on November 30, 2017. You can see the complete timetable of the challenge in Table 1.1. The table was adapted from

https://csrc.nist.gov/Projects/post-quantum-cryptography/workshops-and-timeline

| April 2-3, 2015   | NIST held a Cybersecurity in a Post-Quantum |

|-------------------|---------------------------------------------|

|                   | World workshop                              |

| Feb 24-26, 2016   | NIST calls for submissions in PQCrypto 2016 |

| April 28, 2016    | NISTIR 8105 report was released             |

| Dec 20, 2016      | Formal call for Round 1 submissions         |

| Nov 30, 2017      | Deadline for Round 1 submissions            |

| Dec 4, 2017       | The Ship Has Sailed: The NIST Post-Quantum  |

|                   | Crypto "Competition" presentation at Asi-   |

|                   | aCrypt 2017                                 |

| Dec 21, 2017      | Round 1 contestants are announced           |

| Apr 11, 2018      | Let's Get Ready to Rumble - The NIST PQC    |

|                   | "Competition" presentation at PQCrypto 2018 |

| April 11-13, 2018 | 1. PQC Standardization Conference           |

| January 30, 2019  | Round 2 contestants are announced           |

| March 15, 2019    | 2. Round's submission packages deadline     |

| May 8-10, 2019    | Round 2 of the NIST PQC "Competition" -     |

|                   | What was NIST Thinking? presentation at     |

|                   | PQCrypto 2019                               |

#### Table 1.1: NIST PQC Timeline

| August 22-24, 2019 | 2. PQC Standardization Conference           |

|--------------------|---------------------------------------------|

| July 22, 2020      | Round 3 contestants are announced           |

| October 1, 2020    | 3. Round's submission packages deadline     |

| June 7-9, 2021     | 3. PQC Standardization Conference           |

| July 5, 2022       | Announcing which PQC candidates to be stan- |

|                    | dardized and the fourth round candidates    |

| 2022/2024          | Draft Standards Available                   |

Table 1.1 (continued).

The competition was categorized into three security levels according to an exhaustive key search method and scaled to the AES algorithm with key sizes of 128, 192, and 256 bits. A total of 59 encryption/KEM (Key Exchange Mechanism) and 23 digital signature algorithms are submitted (Moody, 2017). You can see submitted encryption algorithms in Table 1.2.

| Name             | Туре         | Result     | Source                   |  |

|------------------|--------------|------------|--------------------------|--|

| BIG QUAKE        | Code-based   | Eliminated | Bardet et al., 2017      |  |

| BIKE             | Code-based   | Passed     | Aragon, Barreto, et al., |  |

|                  |              |            | 2017                     |  |

| CFPKM            | Multivariate | Eliminated | Chakraborty et al.,      |  |

|                  |              |            | 2017                     |  |

| Classic McEliece | Code-based   | Passed     | Bernstein, Chou, et al., |  |

|                  |              |            | 2017                     |  |

| Compact-LWE      | Lattice      | Eliminated | D. Liu et al., 2017      |  |

| CRYSTALS-        | Lattice      | Passed     | Bos et al., 2018         |  |

| KYBER            |              |            |                          |  |

| DAGS             | Code-based   | Eliminated | Banegas et al., 2018     |  |

| Ding Key Ex-     | Lattice      | Eliminated | Ding et al., 2017        |  |

| change           |              |            |                          |  |

| DME              | Multivariate | Eliminated | Luengo et al., 2017      |  |

| Edon-K           | Code-based   | Withdrawn  | Gligoroski and Gjøs-     |  |

|                  |              |            | teen, 2017               |  |

| EMBLEM &         | Lattice      | Eliminated | Seo et al., 2017         |  |

| R.EMBLEM         |              |            |                          |  |

| FrodoKEM         | Lattice      | Passed     | Naehrig et al., 2017     |  |

| Giophantus       | Multivariate | Eliminated | Akiyama et al., 2017     |  |

| Guess Again      | Other        | Eliminated | Shpilrain et al., 2017   |  |

| HILA5            | Lattice      | Merged to  | Saarinen, 2017           |  |

|                  |              | Round5     |                          |  |

| HK17             | Other        | Withdrawn  | Hetch and Kamlofsky,     |  |

|                  |              |            | 2017                     |  |

Table 1.2: NIST PQC Round 1 Submissions

| HQC                 | Code-based | Passed                 | Melchor, Aragon, Bet-                                                                              |  |

|---------------------|------------|------------------------|----------------------------------------------------------------------------------------------------|--|

|                     |            |                        | taieb, Bidoux, Blazy,                                                                              |  |

|                     |            |                        | Deneuville, Gaborit,                                                                               |  |

|                     |            |                        | Persichetti, et al., 2017                                                                          |  |

| KCL                 | Lattice    | Eliminated             | Zhao et al., 2017                                                                                  |  |

| KINDI               | Lattice    | Eliminated             | El Bansarkhani, 2017                                                                               |  |

| LAC                 | Lattice    | Passed                 | Lu et al., 2018                                                                                    |  |

| LAKE                | Code-based | Merged to ROLLO        | Aragon, Blazy, et al., 2017b                                                                       |  |

| LEDAkem             | Code-based | Merged to<br>LEDAcrypt | Baldi et al., 2018                                                                                 |  |

| LEDApkc             | Code-based | Merged to<br>LEDAcrypt | Baldi et al., 2017                                                                                 |  |

| Lepton              | Code-based | Eliminated             | Y. Yu and Zhang, 2017                                                                              |  |

| LIMA                | Lattice    | Eliminated             | Albrecht, Lindell, et al., 2017                                                                    |  |

| Lizard              | Lattice    | Eliminated             | Cheon et al., 2018                                                                                 |  |

| LOCKER              | Code-based | Merged to<br>ROLLO     | Aragon, Blazy, et al., 2017a                                                                       |  |

| LOTUS               | Lattice    | Eliminated             | Le Trieu Phong et al., 2017                                                                        |  |

| McNie               | Code-based | Eliminated             | JL. Kim et al., 2018                                                                               |  |

| Mersenne-<br>756839 | Other      | Eliminated             | Aggarwal et al., 2017                                                                              |  |

| NewHope             | Lattice    | Passed                 | Alkim et al., 2016                                                                                 |  |

| NTRUEncrypt         | Lattice    | Merged to<br>NTRU      | Hoffstein et al., 2017                                                                             |  |

| NTRU-HRSS-<br>KEM   | Lattice    | Merged to<br>NTRU      | Hülsing et al., 2017                                                                               |  |

| NTRU Prime          | Lattice    | Passed                 | Bernstein et al., 2016                                                                             |  |

| NTS-KEM             | Code-based | Passed                 | Albrecht, Cid, et al., 2017                                                                        |  |

| Odd Manhattan       | Lattice    | Eliminated             | Plantard, 2017                                                                                     |  |

| Ouroboros-R         | Code-based | Merged to<br>ROLLO     | Melchor, Aragon, Bet-<br>taieb, Bidoux, Blazy,<br>Deneuville, Gaborit,<br>Hauteville, et al., 2017 |  |

| PQ RSA-             | RSA        | Eliminated             | Bernstein, Heninger, et                                                                            |  |

| Encryption          |            |                        | al., 2017                                                                                          |  |

| QC-MDPC KEM         | Code-based | Eliminated             | Yamada et al., 2017                                                                                |  |

| Ramstake            | Code-based | Eliminated             | Szepieniec, 2017                                                                                   |  |

| RLCE-KEM            | Code-based | Eliminated             | Wang, 2017                                                                                         |  |

| Round2              | Lattice    | Merged to<br>Round5    | Baan et al., 2017                                                                                  |  |

Table 1.2 (continued).

| RQC         | Code-based     | Passed     | Melchor, Aragon, Bet-<br>taieb, Bidoux, Blazy,<br>Deneuville, Gaborit,<br>and Zémor, 2017 |

|-------------|----------------|------------|-------------------------------------------------------------------------------------------|

| RVB         | Other          | Withdrawn  | Brands and Roellgen, 2015                                                                 |

| SABER       | Lattice        | Passed     | D'Anvers et al., 2018                                                                     |

| SIKE        | Elliptic Curve | Passed     | Azarderakhsh et al., 2017                                                                 |

| SRTPI       | Multivariate   | Eliminated | Peretz and Granot, 2017                                                                   |

| Three Bears | Lattice        | Passed     | Hamburg, 2017                                                                             |

| Titanium    | Lattice        | Eliminated | Steinfeld et al., 2017                                                                    |

Table 1.2 (continued).

Submissions can be categorized into the following algorithms according to their cryptographic primitives:

- Lattice-Based: One of the most popular algorithms for the NIST challenge's first round and have complete dominance in the third round. In these algorithms, the lattices are used as the encryption primitive or to prove the security of the underlining algorithm.

- Code Based: In these types of algorithms, we are using the error correcting codes (ECC) as cryptographic elements. Error Correcting Codes are designed to maintain a communication channel in a highly noisy environment. They carry out their missions by generating redundant information and adding it to the original messages. The most known examples are LDPC (Low-Density Parity-Check) and RS (Reed Solomon) codes. Because of their massive key sizes, they were not very popular in the field of cryptography. However, their immunity against quantum computers is making them popular now.

- Multivariate: These algorithms are based on the polynomials constructed by more than one variable. For example : P(x, y, z) = x<sup>3</sup> \* z + 3 \* x<sup>2</sup> \* y<sup>3</sup> \* z x \* z<sup>2</sup> + 1. Introduced by (Matsumoto & Imai, 1988). They show presence in the first stage of the challenge. However, all three multivariate-based algorithms are eliminated in this stage.

- RSA: Original integer factorization-based RSA algorithm participates with increased key sizes. It provides security by using a key that is big enough to resist a search attack carried out in polynomial time. Because of the massive keys, this method is impractical and eliminated in the first stage.

- Elliptic Curve: SIKE (Supersingular Isogeny Diffie–Hellman Key Exchange) algorithm's used elliptic curves as their primitives. Security against quantum computers comes with generating isogeny from the elliptic curves.

Second-stage submissions and their results are listed in Table 1.3.

| Name             | Туре           | Result     |

|------------------|----------------|------------|

| BIKE             | Code-based     | Alternate  |

|                  |                | Candidate  |

| Classic McEliece | Code-based     | Passed     |

| CRYSTALS-        | Lattice        | Passed     |

| KYBER            |                |            |

| FrodoKEM         | Lattice        | Alternate  |

|                  |                | Candidate  |

| HQC              | Code-based     | Alternate  |

|                  |                | Candidate  |

| LAC              | Lattice        | Eleminated |

| LEDAcrypt        | Code-based     | Eleminated |

| NewHope          | Lattice        | Eleminated |

| NTRU             | Lattice        | Passed     |

| NTRU Prime       | Lattice        | Alternate  |

|                  |                | Candidate  |

| NTS-KEM          | Code-based     | Passed     |

| ROLLO            | Code-based     | Eleminated |

| Round5           | Lattice        | Eleminated |

| RQC              | Code-based     | Eleminated |

| SABER            | Lattice        | Passed     |

| SIKE             | Elliptic Curve | Alternate  |

|                  |                | Candidat   |

| Three Bears      | Lattice        | Eleminated |

Table 1.3: NIST PQC Round 2 Submissions

While this thesis was in progress, the NIST announced CRYSTALS-KYBER as the first algorithm to be standardized at the end of round 3. You can see the submitted algorithms and their result in Table 1.4. Also, for digital signature purposes, CRYSTALS-DILITHIUM, FALCON, and SPHINCS+ algorithms will be standardized. While NIST decided on the first algorithm to standardize, the competition still continues, and it is in its fourth round with the reaming algorithms. These algorithms can be seen in Table 1.4

| Name             | Туре       | Result       |

|------------------|------------|--------------|

| BIKE             | Code-based | Passed       |

| Classic McEliece | Code-based | Passed       |

| CRYSTALS-        | Lattice    | Standardized |

| KYBER            |            |              |

| FrodoKEM         | Lattice    | Eleminated   |

| HQC              | Code-based | Passed       |

| NTRU             | Lattice    | Eleminated   |

| NTRU Prime       | Lattice    | Eleminated   |

Table 1.4: NIST PQC Round 3 Submissions

| NTS-KEM | Code-based     | Eleminated |

|---------|----------------|------------|

| SABER   | Lattice        | Eleminated |

| SIKE    | Elliptic Curve | Passed     |

Table 1.4 (continued).

Most of the participant algorithms are mathematically secure from the beginning of the first stages of the competition. However, their performance metrics are open to improvements. Also, the hardware implementation of these algorithms is highly important because many network-capable devices have to adapt to the new algorithm. With the increasing number of user devices, using specific logic blocks makes more sense than the CPU for server-like devices. Also, many embedded devices have to adopt the new standard algorithm to connect to a network. As this thesis work started long before the round 4 announcement, we chose the NTRU algorithm for development.

### **1.2 NTRU**

NTRU was designed as a property algorithm by Jeffrey Hoffstein, Jill Pipher, and Joseph H. Silverman. In 2013, it was released under GNU License. The algorithm uses latices and has the shortest vector problem as the underlying security primitive. The algorithm was a third-round participant in the NIST PQC Competition.

This algorithm has only three parameters named N, q, p. The parameter N defines the length of the polynomials. q, p parameters are used to determine the Galois Fields. Therefore, modulo operations are calculated according to these parameters.

## 1.3 Effects of Quantum Computers on Cryptography

As mentioned, quantum computers are the new era of computing devices. Up to them, we do not have a new method of computing. The improvements have come from increasing the clock speed, utilizing parallelism, or optimizing the algorithms. However, quantum computers let us use the superposition of physical systems. While classical computation devices can hold two possibilities in their smallest building blocks named bits, a quantum computer can hold all the possible states of their qbits. This will let us calculate all the possible results at the same time. The problem of handling everything at the same time is eliminating the wrong solutions from this superposition state. For this purpose, we have special algorithms and quantum circuits designed for these specific algorithms.

For cryptographic purposes, we are interested in two quantum algorithms: Grover's Search algorithm and Shor's algorithm. Grover's algorithm is an unconstructed search algorithm. This algorithm is important for us. Because by using that, a quantum computer can halve the security of any private key encryption algorithms. By oversimplifying the working mechanisms, Grover's algorithm does not try to generate the

solution. It tries to check every possible solution's correctness in a superposition. While generating a correct solution for a problem is hard, checking a solution's correctness might be easy. For example, solving a maze might require many trials and returns to the previous states. However, checking a list of orders and deciding if they are a solution to this maze is easy.

We use Shor's algorithm while factorizing integers. The integer factorization problem is the underlying security mechanism of the RSA. To briefly explain Shor's algorithm, we start with a random guess and check if it is a factor of the number N. When we fail, we do not select a new test number; the following test number is derived from the previous one with a rule. A quantum computer can generate all the numbers that will be generated by following this rule in a superposition. We can calculate the result of every generated number under modulo by N. After that, we collapse the superposition to a single result. However, the result contains periodic signals that generate the same output. If we feed this state to a Quantum Fourier Transform (QFT) module, we can find this period. The period and the selected random number then be used to factor the big integer (N).

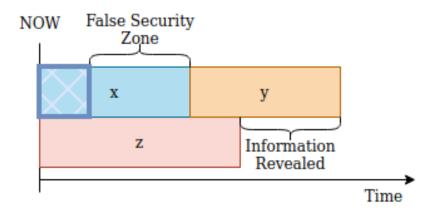

Grover's and Shor's algorithms are resource hungry in terms of qbits and gates, and we will not see a quantum computer that can risk our current public key encryption algorithms in the near future. However, the general practice for states is to keep the secrets for 25 or 50 years. Even if we do not have the technology today, we might gather the encrypted data at the moment and break them when quantum computers are ready to make the necessary calculations. With that limitations, we are required to mitigate a new quantum-safe algorithm as soon as possible. You can see this scenario in Figure 1.1. In this figure; x represents the time passed before mitigation, y is the required time before the information becomes public, and z is the time passed before the first full-scale quantum computer started to work.

Figure 1.1: Unwanted information reveal

#### 1.4 Reasons to work on FPGA

We selected our computational units as FPGAs (Field-Programmable Gate Array). Because they are the irreplaceable component of the military, aerospace, and communication areas, even if they are sometimes backed up by processors for the timeindependent computational workloads, many designs from these fields do not include an onboard processor because of the restrictions and security concerns. FPGAs have more resilience against temperature and radiation. They might generate countless high-speed communication ports as long as their IO (Input Output) port numbers let them. The FPGAs might have hundreds of IO ports. They can support high-speed parallel synchronized IO operations. This process is essential for reading the ADCs and feeding DACs used in communication and digital signal processing. Their incredible power in parallel architecture makes them a perfect fit for working with high computational loads in real-time systems. While normal processors have interrupt controllers to respond to the changing situation and support RTOSes (Real-Time Operating System) for time-bounded calculations, we can control everything in the FPGA within a one-clock beat precision. This response time beats everything that a processor can offer.

### 1.5 Other NTRU Implementations

(Bailey et al., 2001) is probably the first hardware implementation of the NTRU algorithm. The purpose of that paper is to investigate four aspects. Firstly, they compared Karatsuba-Ofman polynomial multiplication (Karatsuba & Ofman, 1962) and their first algorithm. According to their results, algorithm 1 outperforms the Karatsuba-Ofman algorithm. Secondly, the paper provides results for three different microprocessors, which are MC68EX328 Dragonball, Intel 80386, and 37MHz ARM7 performance comparisons. Thirdly, they provided closed source FPGA implantations that build on a fixed parameter and can only perform encryption. They used the parameters of (N, p, q) = (251, X + 2, 128). In that implementation, they defined the p as a polynomial. Because x + 2 and 128 are co-prime, this selection is valid.

(O'Rourke, 2002) only focuses on the polynomial multiplication process of the NTRU. Starting with software designs and comparison, they went forward to hardware and provided a scalable polynomial multiplier core design on FPGA. Their design uses the number of gates between 1483 and 19270 according to the selected parameters.

(Kaps, 2006) in that doctoral thesis, they focused on the different algorithms' power efficiencies and analyzed Rabin's Scheme (Rabin, 1979), NtruEncrypt, and ECC. The NTRU algorithm is implemented only for encryption, while the decryption part is discarded. The implementation for encryption uses 523 combinational elements and 2327 storage elements in their base design. But it might be increased up to 7000 and 9200, respectively, if the parallelization degree is increased. However, the parameters used are insufficient to provide reliable secrecy with a maximum of 61 bits of security against exhaustive search.

(Atici et al., 2008) is designed to be used in RFIDs and in the nodes of the sensor

networks. This purpose forced the implementation to be highly power efficient. The implementation is for ASICs and is focused on power consumption. But the evolution of the NTRU algorithm makes this design's parameters obsolete. The used parameters are N=167, q=128, and p=3. The design spends 1651 combinational and 8848 non-combinational elements for encryption and decryption.

(Kamal & Youssef, 2009) proposed a new approach by utilizing the statistical properties of the distance between the non-zero elements in the polynomials. Also, they provided speed improvements for encryption and decryption processes. They managed to increase the calculation speed by approximately 160%; furthermore, if the parallelization is increased, it can reach up to 216%. They used the parameters up to N= 251, q=128, p=3, which are insecure as general purpose cases. Their implementation spends 4838 FFs and 21654 LUTs.

(B. Liu & Wu, 2015) implemented a hardware multiplier for truncated polynomial rings using LFSRs (Linear feedback shift registers) and claimed the design has the best area-delay product. Their implementation uses 7294 logic elements, 3768 combinational elements, and 3526 registers.

(Farahmand et al., 2019) worked on a hardware and software co-design and compared the different approaches (RTL vs. HLs) to the full software implementation. The main goal of this design was speed. This design's encryption parameters have to be decided before the synthesis process. They used a minimum of 44257 LUTs and 29655 FFs, and for increased security, 76972 LUTs and 49674 FFs were spent.

(Wera, 2020) focuses on IoT devices. Therefore one of the design criteria is compactness. That design supports big polynomials for security, but changing the parameters in runtime is not possible.

(Keersmaekers, 2021) replaces costly polynomial multiplications with NTT (Number Theoretic Transform). This improves the time complexity. However, it doubles the polynomial sizes. Because NTRU was not designed according to this transformation.

(H. Yu et al., 2021) focuses on the performance comparison between FPGA and GPU architectures. As expected, FPGAs can perform better with increasing parallelism. To get the best performance, they increased the resource utilization and spent half of the resources of a high-end FPGA (Stratix V).

(Dang et al., 2021) compares CRYSTALS-Kyber, NTRU, and Saber according to their performances. To do that, they implemented these algorithms on hardware.

(Hoffstein et al., 2017) investigates the security promises of the algorithm with different parameters and messages. You can see the simplified results in Table 1.5

### **1.6 Our Contribution**

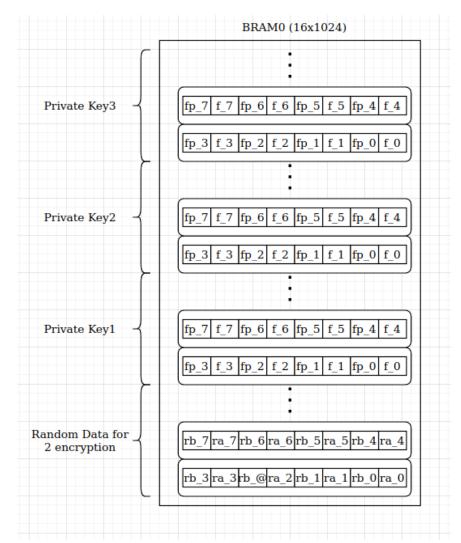

In this thesis work, we targeted FPGA-based embedded network devices. As these devices' resources are utilized for their own missions, our implementation needs to be minimal. To succeed, we stored data in RAMs. Contrary to many implementations,

| Ν   | q    | Original Security Estimate | search cost |

|-----|------|----------------------------|-------------|

| 401 | 2048 | 112                        | 145         |

| 439 | 2048 | 128                        | 147         |

| 593 | 2048 | 192                        | 193         |

| 743 | 2048 | 256                        | 256         |

Table 1.5: NTRUEncrypt security estimation according to Hoffstein in his 2017 article

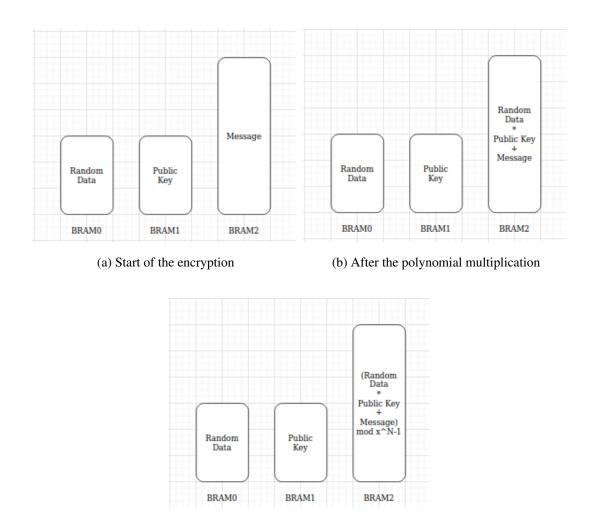

we make the polynomial multiplication in serial. With that method, we were able to decrease the needed data at every cycle and did not have to store the coefficients in FFs. This helps us to develop a flexible architecture to support different parameters. One word of memory can hold our four coefficients. As we can reach four coefficients at the same time, we are able to speed up the serial calculation with a small shifter and adder module. Also, by compressing the data, we stored different keys in RAM without spending additional resources. That technique decreases the costly flash operations before communicating with other devices that have different capabilities or are using different parameters. As we are targeting network devices, we have to be ready for fragmented packets. In this scenario, we can partially process the data, contrary to waiting for the remaining part. Lastly, we implemented a serializer and deserializer module for packing the NTRU's word size information to bytes to increase the efficiency of the communication channel.

#### **CHAPTER 2**

#### QUANTUM COMPUTING

The first computation devices were analog. They made calculations by generally rotating disks, roads, shafts, and gears. One of the well-known early analog computers is the "Antikythera mechanism". By using this hand-powered solar system model, the Ancient Greeks were able to calculate astronomical events years in advance (Efstathiou & Efstathiou, 2018). With the evolution of technology, the paradigm shifted to electronic devices. In these devices, the decisions are given by the voltage levels, not by the gear positions. From their emergence, they have been improved drastically, starting from vacuum tubes; now we have a few atoms wide transistors. The computation power that we have today might be enough to sustain a modern world's needs. However, tomorrow's world requires new techniques. Quantum computing is the new horizon.

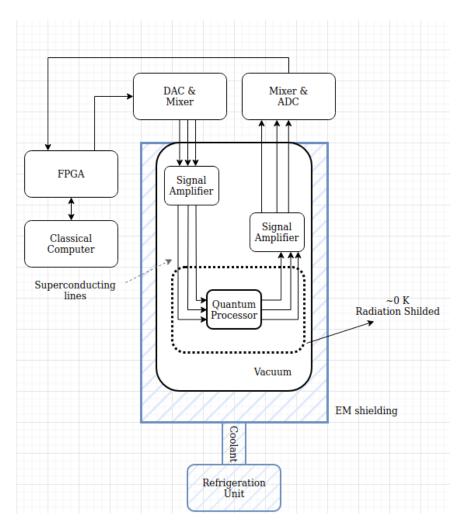

Quantum computers use quantum superposition and quantum entanglement to work. These properties let a quantum computer hold every possible state of the qbits and make calculations on every possibility at the same time. While quantum computers will bring new horizons, they will not replace classical computational devices. The classical computers were designed as self-sufficient systems. However, a quantum computer needs many other complex systems to operate; even one of the helper systems is a classical computer. You can see an example diagram of the quantum computer in Figure 2.1. To control the qbits, we are using microwave signals. The signals are generated and read by analog components with the help of FPGAs. FP-GAs in the systems are connected to a classical computer for the calculations. Also, the classical computer works as an interface module. (Sanders, 2017)

Many research centers and companies around the world are currently trying to increase the qbit numbers of quantum computers. While we have many quantum computers with small qbits, making a quantum computer with many more qbits is still a serious challenge. We cannot combine qbits like we have combined the classical processor cores in a CPU. Combining quantum computers like combining processors in a server or cloud does not work either. All of the qbits in the system have to be a part of a single circuit.

We stated that quantum computers could store multiple possibilities on their qbits. Storing the data is meaningless on its own. Because when we need to receive the results from the quantum computers, it will give out one of the random states. In an unprocessed quantum system, all the probabilities of the states are equal. To get meaningful results from quantum computers, we need to manipulate the possibilities. This manipulation process requires additional qbits and gates. In (Orman, 2021), they

Figure 2.1: Basic diagram of a quantum Computer

investigated the qbit requirements to break the standardized public key encryption algorithms and provide time comparisons between classical computers and quantum computers. The classical computer selected for that study was Intel's Xeon Gold 6130. This processor has 16 physical cores that operate at 2100 MHz. The result of that study can be summarized in Table 2.1 for RSA. Also, they provided calculations for ECC. You can see the results in Table 2.2

Maintaining the entangled quantum states is named quantum coherence. Also, we can define quantum coherence as the evaluation of how much the system obeys the pure coherent states, not the probability distributions of the states. As quantum coherence is highly difficult to maintain, the researchers developed different methods like using ion traps, optical traps, superconductive circuits, or using semiconductors as carriers to maintain the coherence. However, quantum decoherence can still occur with interference from outside. Quantum computers generally work in isolation with near 0-kelvin temperatures to avoid the spontaneous self-decoherence effect. While it can happen destructively, we also need quantum decoherence to get the result of the calculations. After the possibilities are arranged to collapse the superposition to the

|          | bit size | qbits<br>logical | qbits<br>physical | Toff<br>gates | Quantum<br>device | Classical device  |

|----------|----------|------------------|-------------------|---------------|-------------------|-------------------|

|          |          |                  |                   |               | time (h)          | time (h)          |

| RSA 240  | 797      | 2406             | 8M                | 150M          | 1                 | $8.766 * 10^{6}$  |

| RSA 1024 | 1024     | 3092             | 10M               | 400M          | 1.5               | $7.305 * 10^8$    |

| RSA 2048 | 2048     | 6189             | 20M               | 2700M         | 7                 | $5,264*10^{18}$   |

| RSA 3072 | 3072     | 9287             | 40M               | 9900M         | 13                | $1,930*10^{25}$   |

| RSA 4096 | 4096     | 12386            | 50M               | 23000M        | 20                | $4,387 * 10^{30}$ |

Table 2.1: Quantum computer vs. classical computer comparison for breaking RSA and required resources according to Orman

Table 2.2: Required time for a quantum computer to break ECDLP and required resources according to Orman

|          | qbits q |                   | Toff   | Quantum  |

|----------|---------|-------------------|--------|----------|

| bit size | logical | qbits<br>physical | gates  | device   |

|          |         | physical          | gates  | time (h) |

| 224      | 2042    | 6M                | 84.3 B | 288      |

| 256      | 2330    | 7M                | 126 B  | 432      |

| 384      | 3484    | 10M               | 452 B  | 1440     |

| 521      | 4719    | 14M               | 1140 B | 3840     |

correct solution, we need to break the entanglement of the system. Before making another calculation, we need to establish the quantum coherence again. The time spent while doing that is also a critical criterion while evaluating quantum computers.

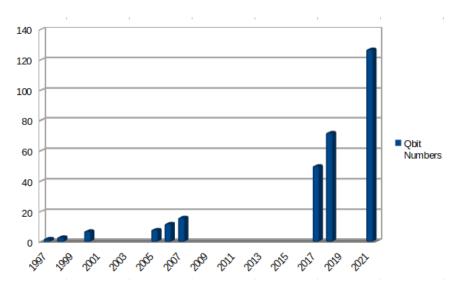

You can see the maximum number of qbits in one system according to years in Figure 2.2. The exponential increasing trend might indicate they will be ready for full-scale computations in the not far future. IBM is expecting to active Osprey with 433 qbits in 2022, Condor with 1,221+ qbits in 2023, and Kookaburra with 4,158+ qbits in 2025, according to their roadmap (Gambetta, 2022). While many research centers and private companies are trying to increase the qubit numbers in the system, there are active researches to optimize the quantum algorithms to decrease the qbit requirements. (Roetteler et al., 2017) in that article, they optimized Shor's algorithm for working on the discrete logarithm. The results of that article are used in (Orman, 2021).

Figure 2.2: Maximum utilized qbits in single system vs. years

Quantum computers can be epoch-making in the following areas:

- **Cryptography:** With the help of Shor's and Grover's algorithms, quantum computers have significant effects on all the well-known encryption algorithms. The result can be ignored in the private key encryption algorithms because doubling the key size can restore the previous security level. However, currently, standardized public key encryption algorithms will not be able to provide security. Because from classical computers' perspective, their underlying problem is non-polynomial. On the contrary, a functional quantum computer can solve these problems in polynomial time.

- Search Problems: There is no way to optimize unstructured search problems while using classical computers. The time complexity of this process is O(N). But, using Grover's algorithm on a quantum computer, the time complexity will be dropped to  $O(\sqrt{N})$ .

- **Quantum Systems Simulation:** As the behavior of the atomic and molecular particles are tough to predict. Classical computers use massive resources to do the calculations; however, a quantum computer might be able to achieve this task effectively.

- **Computer-aided Chemistry and Biology:** Processes like genome sequencing and designing job-specific proteins are taking too much time. Because these systems are not constructed with basic rules and resemblance in the construction of the blocks does not guarantee similarity of the functionality. In the future, quantum computers might replace supercomputers in this area.

### 2.1 Grover's Search Algorithm

Grover's algorithm works in unstructured search spaces. For classical computers, this job has a time complexity of O(N). Because there is no way to optimize this process, and the only way to guarantee success is to try every possibility. However, quantum computers can do this job with  $O(\sqrt{N})$  time complexity by using Grover's Search Algorithm. This algorithm was developed by Lov Grover in 1996 (Grover, 1996). Because Grover's Algorithm does not use any internal structure of the dataset, it can be used in most search problems and can improve the performance quadratically. In this section, we will explain Grover's Search Algorithm without getting deep into the quantum circuits.

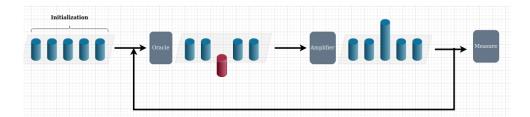

In this algorithm, we have a black box module named Oracle. We show the possibilities as quantum states like  $|0\rangle$ ,  $|1\rangle$ ,  $|2\rangle$ ,  $|3\rangle$ , ...,  $|7\rangle$ . For this example, we have eight different states. The oracle adds a negative phase to the correct solution state. We can represent our oracle in a matrix form.

| -        | Γ1 | 0 | 0 | 0                                                                  | 0 | 0 | 0 | [0 |

|----------|----|---|---|--------------------------------------------------------------------|---|---|---|----|

| oracle = | 0  | 1 | 0 | 0                                                                  | 0 | 0 | 0 | 0  |

|          | 0  | 0 | 1 | $egin{array}{c} 0 \\ 0 \\ -1 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{array}$ | 0 | 0 | 0 | 0  |

|          | 0  | 0 | 0 | -1                                                                 | 0 | 0 | 0 | 0  |

|          | 0  | 0 | 0 | 0                                                                  | 1 | 0 | 0 | 0  |

|          | 0  | 0 | 0 | 0                                                                  | 0 | 1 | 0 | 0  |

|          | 0  | 0 | 0 | 0                                                                  | 0 | 0 | 1 | 0  |

|          | 0  | 0 | 0 | 0                                                                  | 0 | 0 | 0 | 1  |

At this point, we generated a correct solution pattern. We still do not know the solution. But, now we can check whether a solution is correct or not. After we feed our oracle with the solutions, the correct one still has the same possibility of the wrong states. But, the correct solution has a phase difference. The generated solution space is fed into the amplification unit. The amplification unit will increase the possibility of the correct state while decreasing the possibilities of the wrong states. We need to repeat this process several times to increase the possibility of the correct state before collapsing the superposition. The Grover's algorithm's visual representation is provided in Figure 2.3.

Figure 2.3: Visual Representation of the Grover's Search Algorithm

#### 2.2 Shor's Algorithm

Peter Shor developed this algorithm in 1994 (Shor, 1994). For classical computing devices, our best way to factorize a number is General Number Field Sieve with  $O(e^{1.9(\log N)^{1/3}(\log \log N)^{2/3}})$  time complexity (Pomerance, 1996). This complexity is big enough to accept that RSA is secure for practical key sizes like 3072 bits. While running on a quantum computer, Shor's algorithm has a time complexity of  $O(\log N)$ . This reduction makes today's trustworthy RSA encryption completely insecure for a future with quantum computers.

In Shor's algorithm, we are transforming the problem of integer factorization to frequency determining. Assumed, we are trying to factorize the number N. Firstly, we need to pick a random number g; it should be less than N. If we are not extremely lucky, gcd(N,g) will be equal to 1. After that, we can take our unsuccessful guess and convert it to a better one by calculating the new guess by  $g_{new} = g^{p/2} + 1$ . If we try all the p values, we will find a common factor with a 37.5% chance. For classical computers, following this algorithm does not make any performance improvements. In contrast, quantum computers can make miracles with the following steps.

A quantum computer can calculate every exponent of a number at the same time with a gate. However, the resultant information is not functional yet. Because all these values are in a superposition, and if we want a result, the superposition will collapse to a random state. You can see this process in Equation 2.1. After that, we will feed this superposition to another gate that can calculate the difference between each state and m \* N. You can see the result of this gate in Equation 2.2. There will be periodically repeating numbers in the results.

$$|1\rangle + |2\rangle + |3\rangle + |4\rangle + \dots \Rightarrow |1,g\rangle + |2,g^2\rangle + |3,g^3\rangle + |4,g^4\rangle + \dots$$

(2.1)

$$|1,g\rangle + |2,g^2\rangle + |3,g^3\rangle + |4,g^4\rangle + \dots \Rightarrow |1,a\rangle + |2,b\rangle + |3,c\rangle + \dots + |8,a\rangle + |15,a\rangle + \dots + |22,a\rangle + \dots$$

(2.2)

After that, we collapse the result to a random state and feed it to the QFT module Equation 2.3. This module will find the periodicity of the input. The result will be equal to 1/p. If the *p* is even we can calculate the  $g^{p/2} + 1$ . If the calculated value is not a multiple of N, it will share a factor with it, and we can calculate the GCD with EEA.

$$|1,g\rangle + |8,a\rangle + |15,a\rangle + \dots + |22,a\rangle + \dots \Rightarrow |1/7\rangle$$

(2.3)

In the above example, we showed the quantum states of Shor's algorithm while factorizing a number that satisfies  $gcd(N,7) \neq 1$ .

## **CHAPTER 3**

### NTRU

NTRU (Nth degree-Truncated Polynomial Ring Units) algorithm was developed in 1996 by three mathematicians, Jeffrey Hoffstein, Jill Pipher, and Joseph H. Silverman (Hoffstein et al., 1998). Firstly, it was a proprietary algorithm owned by Security Innovation and distributed under paid licenses. In 2013, NTRU was released under GNU Public License (GPL) and became open source. Daniel Bernstein, Chitchanok Chuengsatiansup, Tanja Lange, and Christine van Vredendaal released a changed version of NTRU which named NTRUPrime. They changed the algebraic structure of the original NTRU algorithm with worries about security vulnerabilities in 2006. However, through the NIST PQC challenge, no attack was found to exploit these worries. In the third round, the NTRU was a finalist, and NTRUPrime was an alternate candidate. However, they both could not see round four. An NTRU-based digital signature algorithm, Falcon, will be standardized.

NTRU algorithm has three parameters, and they are (N, p, q). The parameter N defines the length of polynomials used in the encryption. p and q values are used in the modulo calculations. Even though these parameters can be selected freely, some parameters are optimized for efficiency and investigated more heavily for their security promises. For example, establishing q as a power of 2 converts the modulo process to binary "and" gates. If we take p as a small prime number, we can quickly write a hardware accelerator for the modulo. Some of the most used ones are listed in Table 3.1. The usage of the parameters is explained in the following sections with numeric examples.

NTRU algorithm uses Shortest Vector Problem (SVP) for cryptographic functions. SVP is lattice-based, unlike RSA's integer factorization or ECC's discrete logarithm.

| Security Margin | Ν   | р | q    |

|-----------------|-----|---|------|

| 128 bit         | 509 | 3 | 2048 |

| 192 bit         | 677 | 3 | 2048 |

| 256 bit         | 821 | 3 | 4096 |

| 256 bit         | 701 | 3 | 8192 |

Table 3.1: Some of the recommended parameters

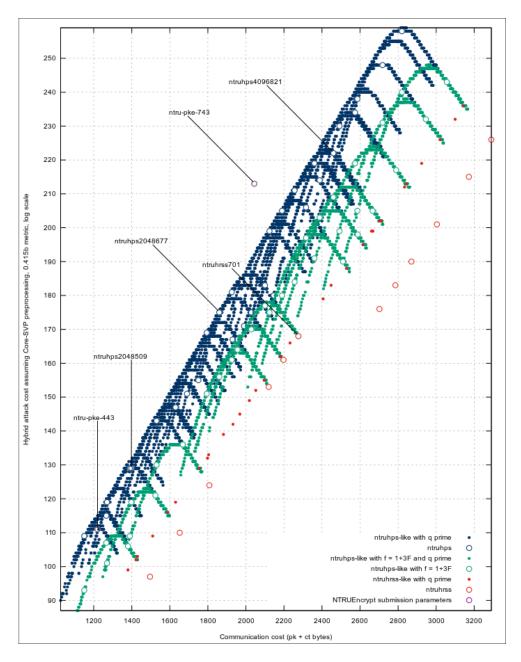

Figure 3.1: NTRU options security comparison

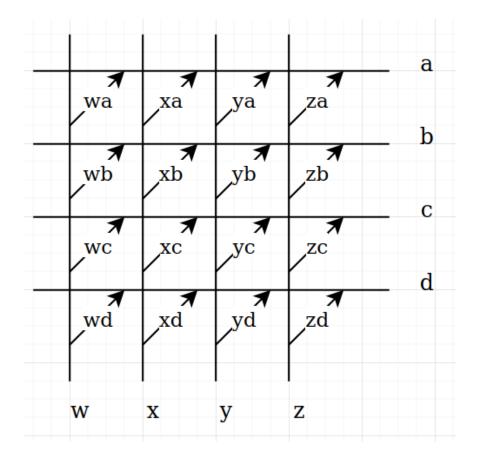

# 3.1 Lattice

Lattice is the space of possible vectors that can be generated from the given basis vectors using only integer coefficients. The more mathematical definition can be provided with  $L \subset \mathbb{R}^n$ ,  $\mathbf{b}_1, \ldots, \mathbf{b}_n \in \mathbb{R}^n$ ,  $L = \left\{ \sum a_i \mathbf{b}_i : a_i \in \mathbb{Z} \right\}$ . For example, for (7,4) and (3,5) basis vectors, our lattice includes (17,13), (4,-1), but (3,7) cannot be a part of our lattice.

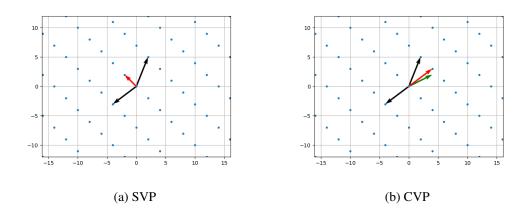

Figure 3.2: Lattice Problems

## 3.2 Shortest Vector Problem

With a provided lattice basis vectors, the Shortest Vector Problem is trying to find the non-zero  $\vec{u}$  that minimizes the  $|\vec{u}|$ . SVP is a sub-problem of the Closest Vector Problem (CVP). In CVP, a random  $\vec{w}$  is also provided with basis vectors and trying to find the  $\vec{u}$  that minimizes the  $|\vec{u} - \vec{w}|$ . So, CVP can be transformed to SVP by selecting  $\vec{w} = \vec{0}$ . You can see the visual representations of SVP and CVP in Figure 3.2.

For example, if basis vectors are given as  $\vec{b_1} = (66, 216, 131)$ ,  $\vec{b_2} = (73, 207, 113)$ , and  $\vec{b_3} = (28, -48, -84)$  the shortest vector in this lattice should be  $\vec{u} = (-2, 0, 1)$ with  $|\vec{u}| = 2.08$ . To get  $\vec{u}$ , we should select  $a_1 = 1219$ ,  $a_2 = -1208$ ,  $a_3 = 276$ . With that coefficients we can satisfy the equation  $\vec{u} = \vec{b_1} * a_1 + \vec{b_2} * a_2 + \vec{b_3} * a_3$ .

## 3.3 Galois Field

The name was given in honor of French mathematician Évariste Galois. The Galois Fields have finite number of elements in them. The elements in this kind of field should satisfy the following field axioms.

- 1. Associativity of "+" and "\*":  $\forall a, b, c \exists F$  (a+b)+c = a + (b+c)(a\*b)\*c = a\*(b\*c)

- 2. Commutativity of "+" and "\*":  $\forall a, b \exists F$ a + b = b + a

a \* b = b \* a

- 3. Identity of "+" and "\*":  $\forall a \exists F$  a + 0 = aa \* 1 = a

- 4. Inverse of "+" and "\*":  $\forall a \exists F$  a + (-a) = 0 $a * (a^{-1}) = 1$  if  $a \neq 0$

- 5. Distributivity of "\*" over "+" and "+" over "\*": ∀ a, b, c ∃ F a \* (b + c) = a \* b + a \* c (a + b) \* c = a \* c + b \* c

In Figure 3.1, you can see the effect of the different parameters. This graph is taken from the supplementary materials of the NTRU's NIST PQC round 3 submission package.

The following sections will provide numeric examples of how the NTRU algorithm work. The parameters are selected as N = 17, p = 3, q = 64. These parameters are too weak for real-life data security purposes; they are selected to be used in demo calculations. The calculations are provided to help the users to familiarize themself with the NTRU and provide a better understanding by showing the numeric examples. Before starting the key generation process, we will explain the Extended Euclidean Algorithm because it will be used while generating the keys.

# 3.4 Extended Euclidean Algorithm

The Euclidean Algorithm calculates the greatest common divisor (GCD) of two numbers with an iterative approach. With the Extended Euclidean Algorithm, we can calculate the GCD with x and y coefficients that satisfies the equation a \* x + b \* y =GCD(a, b). EEA is an iterative algorithm. We start by dividing the bigger integer by the smaller integer. In iterative cycles, we divide the divisor by the remainder until we find a constant value as a quotient. The algorithm is expressed in Algorithm 1:

# Algorithm 1: Extended Euclidean Algorithm

**Initialization:** a = num1b = num2s2 = 1t2 = 0s1 = 0t1 = 11 while  $r \neq 0$  do 2 q = int(a/b)r = a - b \* q3 s = s2 - q \* s14 t = t2 - q \* t15 a, b = b, r6 s2, t2, s1, t1 = s1, t1, s, t7 8 end 9 gcd(num1, num2) = a

In a numeric example, we will take the inverse of polynomial  $x^4 + x^3 + x^2 + 1$  with respect to  $x^3 + 1$  in the GF(7). To solve this problem with EEA, we need to convert the equation to  $a * (x^4 + x^3 + x^2 + 1) + b * (x^3 + 1) = 1 \mod 7$ . Some polynomials are underlined to flag them for the next steps. They will be regarded as variables in the backtracking algorithms.

$$\underline{(x^4 + x^3 + x^2 + 1)} = \underline{(x^3 + 1)} * (x + 1) + \underline{(x^2 - x)}$$

(3.1)

$$\underline{(x^3+1)} = \underline{(x^2-x)} * (x+1) + \underline{(x+1)}$$

(3.2)

$$\underline{(x^2 - x)} = \underline{(x+1)} * (x-2) + 2$$

(3.3)

We calculated the  $GCD(x^4 + x^3 + x^2 + 1, x^3 + 1) = 2$ . To find the inverses, GCD should be equal to 1. Therefore, we need to multiply both sides of the equation by 4 before finalizing the calculations. To get  $4 * 2 = 1 \mod 7$ . Before proceeding we need to rewrite these equations (3.1) to (3.4), (3.2) to (3.5) and (3.3) to (3.6).

$$\underline{(x^4 + x^3 + x^2 + 1)} - \underline{(x^3 + 1)} * (x + 1) = \underline{(x^2 - x)}$$

(3.4)

$$\underline{(x^3+1)} - \underline{(x^2-x)} * (x+1) = \underline{(x+1)}$$

(3.5)

$$\underline{(x^2 - x)} - \underline{(x + 1)} * (x - 2) = 2$$

(3.6)

We substitute the x + 1 in the (3.6) with the (3.5).

$$\underline{(x^2 - x)} - (\underline{(x^3 + 1)} - \underline{(x^2 - x)} * (x + 1)) * (x - 2) = 2$$

(3.7)

$$\underline{(x^2 - x)} * (x^2 - x - 1) - \underline{(x^3 + 1)} * (x - 2) = 2$$

(3.8)

Now, we need to write the equation (3.4) into (3.10).

$$(\underbrace{(x^4 + x^3 + x^2 + 1)}_{(x^4 + 1)} - \underbrace{(x^3 + 1)}_{(x^4 + 1)} * (x + 1)) * (x^2 - x - 1) - \underbrace{(x^3 + 1)}_{(x^4 + 1)} * (x - 2) = 2 \quad (3.9)$$

$$\underline{(x^4 + x^3 + x^2 + 1)} * (x^2 - x - 1) + \underline{(x^3 + 1)} * (-x^3 + x + 3) = 2$$

(3.10)

The last step is to make it compatible with the defined Galois Field.

$$\underbrace{(x^4 + x^3 + x^2 + 1)}_{(x^4 + x^2 + 1)} * (x^2 - x - 1) + \underbrace{(x^3 + 1)}_{(x^4 + 1)} * (-x^3 + x + 3) = 2 \mod 7 \quad (3.11)$$

We will multiply the two sides of the equation by 4.

$$\underbrace{(x^4 + x^3 + x^2 + 1)}_{(3.12)} * (4 * x^2 - 4 * x - 4) + \underbrace{(x^3 + 1)}_{(3.12)} * (-4 * x^3 + 4 * x + 12) = 8 \mod 7 \pmod{7}$$

With taking the modulo.

$$\underbrace{(x^4 + x^3 + x^2 + 1)}_{(x^4 + x^2 + 3 + x + 3)} + \underbrace{(x^3 + 1)}_{(x^3 + 1)} * (3 + x^3 + 4 + x + 5) = 1 \mod 7 \quad (3.13)$$

The inverse of the  $(x^4+x^3+x^2+1)$  is equal to  $(4*x^2+3*x+3)$  under  $(3*x^3+4*x+5)$  on GF(7).

# 3.5 Key Generation

Like all public key algorithms, there are two sets of keys, public and private. To generate these keys, two parties have to agree on the parameters. These parameters are named (N,p,q) and can be shared on an unsecured channel or used as fixed numbers for the implementations. After parameters are selected, we need to generate two polynomials called (f,g) as our key generators. The key generation steps are listed below.

• We need to randomly select f polynomial. The degree of the polynomial should be equal to or smaller than N-1, and its coefficients should be one of these integers (-1,0,1). Also, the selected f polynomial should have inverses under both p and q. We will name the inverse polynomials as  $f_p$ ,  $f_q$ . The inverses can be formulated as

$$f_p * f = 1 \pmod{p}$$

$$f_q * f = 1 \pmod{q}$$

If the inverses do not exist, we need to generate a new f polynomial and calculate the inverses again.

As mentioned above, we will be using the NTRU(N = 17, p = 3, q = 64) parameters to generate our public and private keys. We started by randomly selecting the f and g functions.

$$f(x) = -x^{16} - x^{15} + x^{12} + x^{11} + x^9 + x^8 - x^5 - x^3 + x^2$$

$$g(x) = x^{15} + x^{14} - x^{13} - x^{12} - x^{11} + x^{10} - x^9 + x^8 - x^7 - x^6 + x^5 + x^4 - x^3 - x^2 + x + 1$$

Before we continue with inverse function calculations, we might check if the function's coefficients are balanced. f(x) has 5 ones and 4 negative ones, g(x) has 8 ones and 8 negative ones. To calculate the inverse functions, we can use the Extended Euclidean Algorithm. The numeric calculations can be carried out in subsection Extended Euclidean Algorithm.

$$f'_p(x) = -x^{15} - x^{14} - x^{13} - x^{12} - x^{11} - x^{10} - x^8 - x^7 - x^5 + x$$

$$\begin{aligned} f_q'(x) &= -28 * x^{16} - 23 * x^{15} + 22 * x^{14} - 14 * x^{13} + 16 * x^{12} \\ &- 23 * x^{11} + 8 * x^{10} + 32 * x^9 - 26 * x^8 - 27 * x^7 - 29 * x^6 - 22 * x^5 \\ &+ 5 * x^4 + 11 * x^3 - 18 * x^2 - 25 * x + 14 \end{aligned}$$

We can calculate the preliminary h(x) with multiplying  $p, f'_q(x), g(x)$

$$\begin{split} h_{pre}(x) &= -20 * x^{31} - 25 * x^{30} + 17 * x^{29} - 15 * x^{28} + 29 * x^{27} \\ &+ 4 * x^{26} + 26 * x^{25} - 22 * x^{24} - 14 * x^{23} - 29 * x^{22} - 2 * x^{21} + 2 * x^{20} \\ &+ 17 * x^{19} + 10 * x^{18} - 12 * x^{17} - x^{16} - 31 * x^{15} + 8 * x^{14} + 20 * x^{13} \\ &+ 6 * x^{12} - 18 * x^{11} + 13 * x^{10} - 25 * x^9 + 21 * x^8 + 23 * x^7 + 12 * x^6 \\ &+ x^5 + 27 * x^4 + 12 * x^3 + 21 * x^2 + 31 * x - 22 \end{split}$$

The last step to finish the key generation is taking the modulo of  $h_{pre}(x)$  under  $x^{17} - 1$ .

$$h(x) = -x^{16} - 31 * x^{15} - 12 * x^{14} - 5 * x^{13} + 23 * x^{12} + 31 * x^{11} - 22 * x^{10} - 21 * x^{9} - 17 * x^{8} + x^{7} - 2 * x^{6} - 28 * x^{5} + 25 * x^{4} + 14 * x^{3} - 26 * x^{2} - 23 * x + 30$$

- After  $f_q$  is calculated, we can generate our public key and finish the key generation process.  $h = p * f_q * g$

- Private keys :  $f, f_p, g$ Public key: h

### 3.6 Encryption